# FPGA-basierte aktive Unterdrückung der elektromagnetischen Störungen einer aktiven Leistungsfaktorkorrektur (PFC) durch die Injektion von modulierten Sinussignalen

M.Sc. Andreas Bendicks, TU Dortmund, Arbeitsgebiet Bordsysteme

M.Sc. Axel Peters, TU Dortmund, Arbeitsgebiet Bordsysteme

Prof. Dr.-Ing. Stephan Frei, TU Dortmund, Arbeitsgebiet Bordsysteme

Dipl.-Ing. Marc Wiegand, Leopold Kostal GmbH & Co. KG, Lüdenscheid, Deutschland

Dipl.-Ing. Norbert Hees, Leopold Kostal GmbH & Co. KG, Lüdenscheid, Deutschland

# 1 Einleitung

Eine aktive Leistungsfaktorkorrektur (englisch: Power Factor Correction, PFC) ist eine typische Eingangsstufe vieler am Stromnetz betriebenen Geräte. Die aktive PFC sorgt durch geeignete Regelkreise für eine Stromentnahme, welche die gleiche Kurvenform und Phasenlage wie die Netzspannung besitzt. Dadurch kommt es zu einer Minimierung der Blind- und Verzerrungsleistung und zu einer Maximierung des namensgebenden Leistungsfaktors. Der Ausgang der PFC ist dabei in der Regel eine Gleichspannung. In aktiven PFCs werden üblicherweise hochfrequent schaltende Transistoren eingesetzt. Diese Schaltvorgänge sorgen für elektromagnetische Störungen, welche sich sowohl leitungsgebunden als auch abgestrahlt ausbreiten können. Die daraus resultierende Störemission muss reduziert werden, damit es zu keinen Funktionsbeeinträchtigungen anderer Geräte kommt. Zur Reduktion der ins Netz einkoppelnden leitungsgebundenen Störungen werden üblicherweise passive Filterstrukturen eingesetzt, welche jedoch häufig groß, schwer und teuer sind. Aktive Verfahren zur Störunterdrückung können zu einer Reduktion des Filteraufwands beitragen und damit bauraum- und gewichtsreduzierte Systeme ermöglichen. Im Rahmen des Beitrags wird ein neues aktives Verfahren vorgestellt, um gezielt einzelne Schaltharmonische mithilfe von jeweils einem modulierten Sinussignal zu unterdrücken.

Einleitend werden aktive EMV-Filter und die Störunterdrückung mithilfe von synthetisierten und synchronisierten Gegenstörsignalen als zwei Verfahren zur aktiven Störunterdrückung vorgestellt. Das zweite Verfahren wird im Rahmen dieses Beitrags erstmalig auf eine PFC angewendet. Es wird herausgearbeitet, dass die Störungen der betrachteten PFC aus modulierten Schaltharmonischen bestehen. Damit kann eine aktive Störunterdrückung durch eine Injektion von modulierten Sinussignalen erfolgen. Zur Realisierung wird eine selbstadaptierende Methode aus der aktiven Lärmkompensation (Akustik) auf einem FPGA-System implementiert und systematisch für die Anwendung auf die PFC untersucht. Die optimierte Implementierung wird anhand einer realen PFC evaluiert. Der Beitrag endet mit einer Zusammenfassung und einem Ausblick.

# 2 Verfahren zur aktiven Störunterdrückung

Im Folgenden werden zwei grundsätzliche Verfahren zur aktiven Störunterdrückung vorgestellt. Aktive EMV-Filter stellen dabei eine etablierte und bereits häufig diskutierte Methode dar. Die aktive Störunterdrückung mithilfe von synthetisierten und synchronisierten Gegenstörmethoden ist eine deutlich neuere Methode, welche im Rahmen dieses Beitrags weitergehend untersucht wird.

# 2.1 Aktive EMV-Filter (AEF)

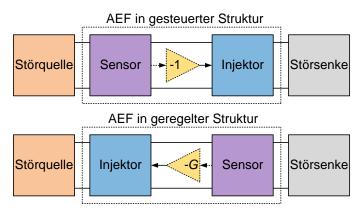

Aktive EMV-Filter (AEF) zur aktiven Störunterdrückung verwenden üblicherweise analoge Schaltungen in gesteuerten oder geregelten Strukturen (Bild 1), um ein Gegenstörsignal aus den gemessenen Störungen zu generieren [1,2]. Gesteuerte Strukturen invertieren die störquellenseitig gemessenen Störungen und injizieren dieses Signal störsenkenseitig. Idealerweise tritt eine destruktive Interferenz auf, wodurch die Störungen ausgelöscht werden. Geregelte Strukturen messen die verbleibenden Störungen störsenkenseitig, invertieren und verstärken diese und injizieren das resultierende Signal störquellenseitig wieder in das System. Durch den geschlossenen Regelkreis werden die Störungen an der Störsenke minimiert. Aus beiden Strukturen resultieren jedoch systematische Einschränkungen, da die Störungen und Gegenstörungen z.B. aufgrund von begrenzten Verstärkungs-Bandbreiten-Produkten [1,2] und unvermeidlichen Verzögerungszeiten [3] niemals exakte Gegenteile voneinander sind.

Bild 1: Strukturen von aktiven EMV-Filtern

# 2.2 Aktive Störunterdrückung von (quasi-)periodischen Störungen mithilfe von synthetisierten und synchronisierten Gegenstörsignalen

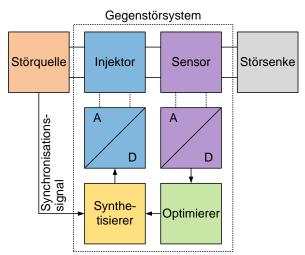

Zur Aufhebung dieser systematischen Begrenzung wurde in [4] ein neues Verfahren vorgestellt, in welchem synthetisierte Gegenstörsignale zur aktiven Störunterdrückung verwendet werden. In Bild 2 ist die grundlegende Struktur abgebildet. Die Signalsynthese kann für (quasi-)periodische Störungen mithilfe von Sinussignalen erfolgen, welche jeweils eine Harmonische eliminieren. Komplexe Amplituden- und Phasengänge (samt Verzögerungszeiten) können dabei durch passende Amplituden und Phasen kompensiert werden. Zur Bestimmung der richtigen Parameter kann ein Optimierer eingesetzt werden, welcher die vom Sensor gemessenen Reststörungen minimiert. Um eine Synchronisation zwischen den Störungen und Gegenstörungen zu erzielen, ist ein Synchronisationssignal notwendig. In leistungselektronischen Systemen eignen sich dazu beispielsweise die Ansteuerungssignale der Leistungstransistoren. Das gefundene Gegenstörsignal wird über einen geeigneten Injektor in das System eingekoppelt. Zur Realisierung der Signalsynthese und -optimierung bieten sich digitale Signalverarbeitungssysteme an. In dem Fall sind Analog-Digital- und Digital-Analog-Wandler zur Verknüpfung der Systeme notwendig.

Bisher wurde dieses Verfahren auf stationär betriebene DC/DC-Wandler angewendet, welche periodische Störungen verursachen. Aufgrund dieser Periodizität haben die Gegenstörsysteme ausreichend Zeit, optimale Amplituden- und Phasenwerte zu finden und

zu diese einzustellen. So ist es beispielsweise in [5] möglich gewesen, das Gegenstörsignal mithilfe eines adaptiven FPGA-Systems sukzessive aus 100 Sinussignalen zu konstruieren. Im Rahmen dieses Beitrags soll das Verfahren auf eine (quasi-)stationär betriebene PFC angewendet werden. Im Gegensatz zu einem DC/DC-Wandler wird das Tastverhältnis der Leistungstransistoren hier jedoch im Verlauf einer Netzperiode variiert (mehr dazu in Kapitel 3). Daher muss das Gegenstörsystem permanent den Störungen der PFC folgen. Dies hat zur Folge, dass die Konvergenzgeschwindigkeit des Verfahrens nun eine zentrale Größe darstellt, welche im Rahmen dieses Beitrags genauer untersucht wird.

**Bild 2:** Aktive Störunterdrückung mithilfe von synthetisierten und synchronisierten Gegenstörsignalen

# 3 Problemstellung bei einer aktiven Leistungsfaktorkorrektur

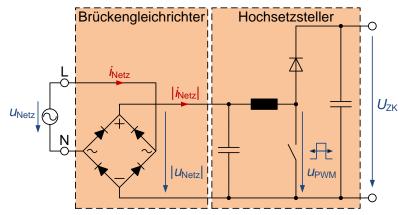

In diesem Beitrag soll die aktive Störunterdrückung mithilfe von synthetisierten Gegenstörsignalen auf eine Boost-PFC angewendet werden, welche im Wesentlichen aus einem Brückengleichrichter und einem Hochsetzsteller (engl. boost converter) besteht (Bild 3). Der Brückengleichrichter richtet die Wechselspannung des Stromnetzes  $u_{\rm Netz}(t)$  zu einer pulsierenden Gleichspannung  $|u_{\rm Netz}(t)|$  gleich. Das Tastverhältnis des Hochsetzstellers wird dabei durch unterlagerte Regelkreise im Verlauf einer Netzperiode derart moduliert, dass die Zwischenkreisspannung  $U_{\rm ZK}$  konstant ist und der Eingangsstrom  $i_{\rm Netz}$  der Netzspannung  $u_{\rm Netz}$  ohne Phasenverschiebung folgt.

Bild 3: Schaltplan einer typischen Boost-PFC

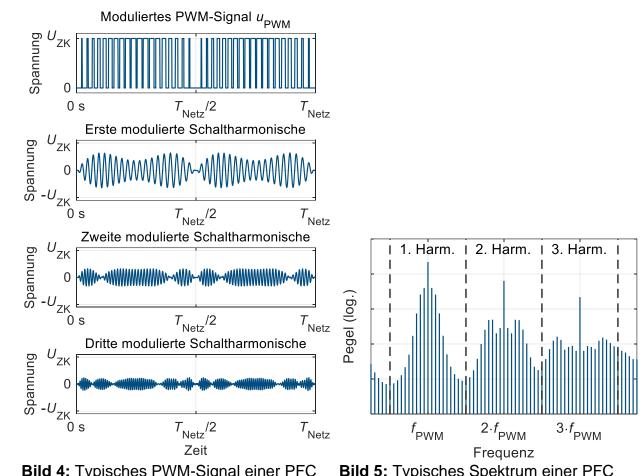

Ein typischer Verlauf des resultierenden PWM-Signals  $u_{PWM}(t)$  ist in Bild 4 (oben) dargestellt, wobei die Schaltfrequenz zur besseren Anschaulichkeit deutlich geringer als üblich gewählt wurde. Dieses PWM-Signal resultiert in dem Spektrum aus Bild 5. Die Schaltfrequenz  $f_{PWM}$  und die zugehörigen Oberwellen sind deutlich zu erkennen. Zusätzlich führt die Änderung des Tastverhältnisses im Verlauf einer Netzperiode zu einer großen Anzahl an Seitenbandharmonischen [6]. Diese Seitenbandharmonischen haben einen so geringen Abstand (z.B. 50 Hz), dass sie mit üblichen Messbandbreiten (beispielsweise 9 kHz) nicht sichtbar sind. Werden die Schaltharmonischen mit ihren zugehörigen Seitenbandharmonischen (wie in Bild 5 angedeutet) wieder in den Zeitbereich überführt (Bild 4), ist es ersichtlich, dass das PWM-Signal aus modulierten Sinussignalen besteht. Damit ist es grundsätzlich möglich, die Störungen der PFC durch die Injektion von modulierten Sinussignalen zu unterdrücken.

Bild 4: Typisches PWM-Signal einer PFC Bild 5: Typisches Spektrum einer PFC

#### 4 Algorithmus zur Unterdrückung einer Schaltharmonischen und ihrer Nebenbandharmonischen

Im Folgenden wird ein Algorithmus vorgestellt, welcher sich zur aktiven Unterdrückung von einzelnen Schaltharmonischen samt der Seitenbandharmonischen eignet. Als erstes wird die Grundstruktur beschrieben und auf einem FPGA-System implementiert. Daraufhin wird die Schrittweite als einer der entscheidenden Parameter für die Konvergenzgeschwindigkeit untersucht. Für eine systematische Analyse wird dazu erst ein periodisches PWM-Signal mit konstantem Tastverhältnis und daraufhin ein typisches PWM-Signal einer PFC betrachtet. Diese Betrachtung ermöglicht einen ersten Funktionsnachweis und eine Aussage über die idealen Parameter, welche in der Praxis eingesetzt werden können.

#### 4.1 **Grundlegende Struktur**

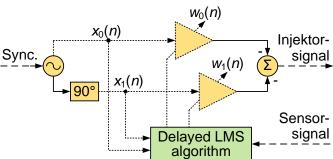

Der Algorithmus basiert auf dem "single-frequency adaptive notch filter" mit dem "delayed LMS algorithm", welcher im Bereich der aktiven Lärmkompensation bereits weit etabliert ist [7]. In [4] wurde der Algorithmus erstmalig zur Unterdrückung der Schaltharmonischen eines DC/DC-Wandlers eingesetzt. In [5] wurde dieser Algorithmus um eine sukzessive Signalgenerierung erweitert. Die Realisierung ist in beiden Fällen mithilfe eines programmierbaren FPGA-Evaluierungssystems erfolgt.

Die grundsätzliche Struktur des Algorithmus ist in Bild 6 skizziert. Zur aktiven Unterdrückung einer Harmonischen wird ein Orthogonalsystem bestehend aus Cosinus- und Sinussignalen mit der entsprechenden Frequenz aufgespannt. Dies wird durch ein geeignetes Synchronisationssignal mit der Leistungselektronik synchronisiert. Es gelten damit

$$x_0(n) = A \cdot \cos\left(2\pi \frac{kf_{\text{PWM}}}{f_c} \cdot n\right) \tag{1}$$

$$x_0(n) = A \cdot \cos\left(2\pi \frac{kf_{\text{PWM}}}{f_{\text{s}}} \cdot n\right)$$

und

$$x_1(n) = A \cdot \sin\left(2\pi \frac{kf_{\text{PWM}}}{f_{\text{s}}} \cdot n\right),$$

(2)

wobei A eine beliebige Amplitude (hier 1 V), k die aktuell betrachtete Harmonische,  $f_{PWM}$ die Schaltfrequenz,  $f_s$  die Abtastrate und n die diskrete Zeitbasis beschreiben. Dieses Orthogonalsystem wird mit den Faktoren  $w_0(n)$  und  $w_1(n)$  gewichtet und überlagert, um einen Sinus mit einer beliebigen Amplitude und Phase und einer Frequenz von  $kf_{\mathrm{PWM}}$  zu erzeugen. Die Invertierung des Signals ist zur Konsistenz mit der weitergehenden Theorie berücksichtigt.

Bild 6: "Single-frequency adaptive notch filter" mit "delayed LMS algorithm"

Mit der oben beschriebenen Struktur kann ein Sinussignal mit beliebiger Phase und Amplitude im laufenden Betrieb des Gegenstörsystems erzeugt werden. Die Faktoren  $w_0(n)$  und  $w_1(n)$  müssen so bestimmt werden, dass die zu unterdrückende Harmonische minimiert wird. Dies kann mithilfe des "delayed LMS algorithm" erfolgen. Der Algorithmus minimiert das Least-Mean-Squares-Problem mithilfe eines Gradientenabstiegsverfahrens. Die rekursive Berechnungsvorschrift des Algorithmus lautet

$$w_0(n+1) = w_0(n) + \mu \cdot x_0(n-\Delta) \cdot e(n)$$

und

$$w_1(n+1) = w_1(n) + \mu \cdot x_1(n-\Delta) \cdot e(n)$$

, (4)

wobei  $\mu$  die Schrittweite und e(n) die vom Sensor gemessenen Reststörungen darstellen. Der Algorithmus aktualisiert die Gewichte damit rekursiv mit jedem neuen Datensatz. Bei einer Implementierung auf einem FPGA-System kann die Aktualisierung aufgrund der hohen Parallelisierbarkeit und der kurzen Berechnungszeiten zu jedem Abtastzeitpunkt durchgeführt werden. Daher kann eine Signalanpassung in Echtzeit erfolgen. Für die Stabilität des Algorithmus muss die Verzögerungszeit beachtet werden, die das Gegenstörsignal von der Injektion bis zur Sensormessung benötigt. Dazu wird die geschätzte Verzögerungszeit  $\Delta$  im Algorithmus berücksichtigt. Die Konvergenzgeschwindigkeit kann durch eine größere Abweichung zwischen der geschätzten und realen Verzögerungszeit deutlich reduziert werden. Daher ist eine exakte Berücksichtigung notwendig. Nachfolgend wird der Einfluss verschiedener Schrittweiten  $\mu$  (bei einer annähernd idealen Schätzung von  $\Delta$ ) auf die Konvergenzgeschwindigkeit untersucht. Für weitere Details, Beschreibungen und Quellen wird auf die umfangreiche Zusammenfassung [7] verwiesen.

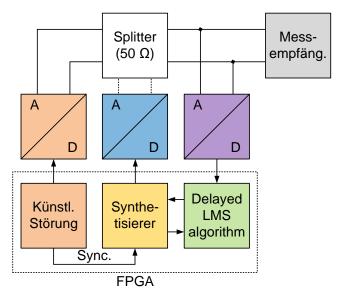

# 4.2 Testsystem zur Untersuchung der Schrittweite

Zur Evaluation des Einflusses der Schrittweite  $\mu$  des "delayed LMS algorithm" auf die Qualität der aktiven Störunterdrückung wird ein klar definiertes Testsystem entsprechend Bild 7 untersucht. Der vorgestellte Algorithmus ist auf dem FPGA-Evaluationssystem Red Pitaya STEMlab 125-14 implementiert. Zusätzlich werden durch den FPGA künstliche Störungen erzeugt. Dies hat den Vorteil, dass eine perfekte Synchronisation zwischen den Signalen sichergestellt wird. Zusätzlich können so spezielle Störsignale zur Untersuchung eingestellt werden. Die Störungen und Gegenstörungen werden durch D/A-Wandler in die analoge Domäne überführt und in einem 50  $\Omega$ -Splitter überlagert. Die verbleibenden Störungen werden A/D-gewandelt und von dem Optimierer zur Anpassung des Gegenstörsinus verwendet. Das System verwendet eine Abtastrate von 125 MS/s. Die Gegenstörsignale werden ebenfalls mit dieser Rate angepasst. Die verbleibenden Störungen werden durch einen Messempfänger bewertet. Dieser verwendet eine Messbandbreite von 9 kHz, eine Messzeit von 50 ms und den Mittelwertdetektor.

**Bild 7:** Testsystem zur Untersuchung der Schrittweite  $\mu$  für verschiedene Testsignale

# 4.3 Untersuchung der Schrittweite für ein periodisches PWM-Signal

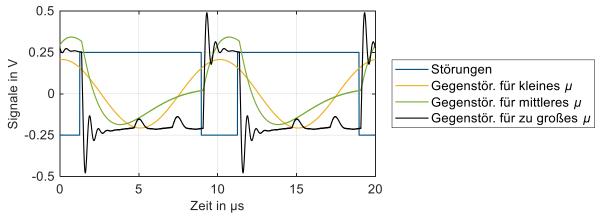

Zunächst wird ein periodisches PWM-Signal mit einer Amplitude von 0,5 V, einem konstanten Tastverhältnis von 77 % und einer Schaltfrequenz von 100 kHz generiert. Zur Untersuchung wird die Schrittweite  $\mu$  in einem sehr weiten Bereich variiert. Zur besseren

Anschaulichkeit sind simulierte Gegenstörsignale für die Grundwelle und verschiedene Schrittweiten in Bild 8 dargestellt. Es kann festgestellt werden, dass das Gegenstörsignal für sehr kleine Schrittweiten (hier bis zu 6,7·10<sup>-5</sup>) einem Sinussignal entspricht. Wird die Schrittweite jedoch weiter erhöht, wird der Algorithmus immer empfindlicher auf die Störungen. Dadurch kommt es zu einer Übermodulation, wodurch das Gegenstörsignal von dem Sinus abweicht. Da der Algorithmus dabei ungenauer oder sogar instabil wird, verschlechtert sich das Gegenstörergebnis.

**Bild 8:** Simulierte Gegenstörsignale für ein periodisches PWM-Signal und unterschiedliche Schrittweiten  $\mu$

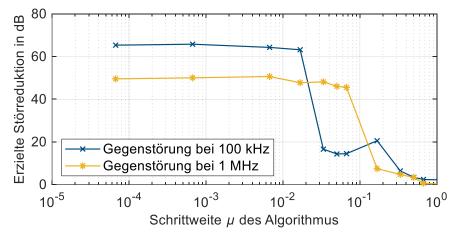

Dies kann in den Labormessungen mit dem Messempfänger (Bild 9) bestätigt werden. Bei zu hohen Schrittweiten ist der Algorithmus unpräzise und wenig effektiv. Bei geringen Schrittweiten können hohe Störungsreduktionen von über 60 dB für 100 kHz und 50 dB für 1 MHz erzielt werden. Hierbei macht es den Anschein, dass die aktive Störunterdrückung bei geringen Frequenzen effektiver ist. Dies ist jedoch nicht der Fall, wie in [8] untersucht wurde. Die geringere erzielte Störreduktion ist damit zu begründen, dass die Störung bei der zehnten Harmonischen deutlich geringer als bei der Grundwelle ist. Da der Algorithmus die Störungen bis in den Rauschgrund der A/D- und D/A-Wandler unterdrückt, existiert eine Untergrenze für die Reststörungen. Sind die ursprünglichen Störungen geringer, resultiert damit auch eine geringere Störreduktion. Aus diesen Messungen kann gefolgert werden, dass kleine Schrittweiten vorteilhaft sind, um eine präzise Störunterdrückung zu realisieren. Die reduzierte Konvergenzgeschwindigkeit stellt aufgrund der Periodizität der Störungen keine Einschränkung dar.

**Bild 9:** Gemessene Störreduktion bei 100 kHz und 1 MHz für das periodische PWM-Signal und unterschiedliche Schrittweiten  $\mu$

# 4.4 Untersuchung der Schrittweite für das PWM-Signal der PFC

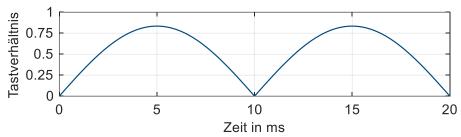

Nun soll die aktive Störunterdrückung für das PWM-Signal einer PFC untersucht werden. Dazu wird auf dem FPGA-System ein künstliches PWM-Signal erzeugt, bei welchem das Tastverhältnis entsprechend Bild 10 variiert wird. Dieses Tastverhältnis bezieht sich dabei auf den Schaltknoten des Hochsetzstellers (vgl. Bild 3).

Bild 10: Beispielhafter Verlauf für das Tastverhältnis des PWM-Signals in einer PFC

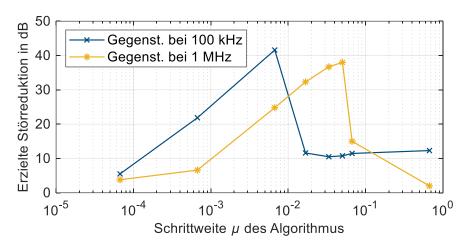

In Bild 11 ist die erzielbare Störreduktion für unterschiedliche Schrittweiten  $\mu$  dargestellt. Aus der vorhergehenden Untersuchung für das periodische PWM-Signal ist es bereits ersichtlich, dass der Algorithmus für zu große Schrittweiten unpräzise oder sogar instabil wird. Nichtsdestotrotz kann hier festgestellt werden, dass die erzielbare Störreduktion für zu geringe Schrittweiten abnimmt. Das ist plausibel, da der Algorithmus den Änderungen des PWM-Signals folgen muss. Ist die Schrittweite zu klein, konvergiert der Algorithmus zu langsam und die Effektivität nimmt ab. Damit ergeben sich optimale Schrittweiten von  $6.7 \cdot 10^{-3}$  für 100 kHz und  $5.0 \cdot 10^{-2}$  für 1 MHz, bei denen der Algorithmus möglichst schnell und ohne Übermodulationen oder Instabilitäten konvergiert. Für die Harmonische bei 1 MHz ist eine größere Schrittweite notwendig, da die Modulationsrate mit der Ordnung der Harmonischen steigt (vgl. Bild 4). Bei der Messung mit dem Spitzenwertdetektor können ähnliche Ergebnisse erzielt werden, welche nur um wenige dB geringer sind. Dies lässt sich darauf zurückführen, dass der Algorithmus insbesondere bei schnellen Änderungen des Tastverhältnisses kurzzeitig schlechtere Ergebnisse liefert. Diese werden durch den Spitzenwertdetektor stärker gewichtet als durch den Mittelwertdetektor.

**Bild 11:** Gemessene Störreduktion bei 100 kHz und 1 MHz für das PWM-Signal einer PFC und unterschiedliche Schrittweiten  $\mu$

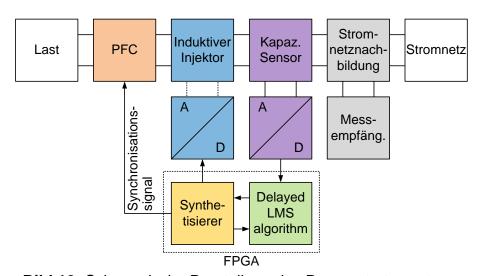

## 5 Demonstrator

In Bild 12 ist der schematische Aufbau des Demonstratorsystems dargestellt. Als PFC wird das Evaluationssystem IPP60R190P6 von Infineon mit einer Schaltfrequenz von 100 kHz verwendet. Die PFC wird mit einer ohmschen Last betrieben, an welcher eine Leistung von etwa 223 W umgesetzt wird. Die Gegentaktstörungen des Systems werden mithilfe einer Stromnetznachbildung und eines Messempfängers gemessen. Der Messempfänger verwendet weiterhin eine Messbandbreite von 9 kHz, eine Messzeit von 50 ms und den Mittelwertdetektor. Das Gegenstörsystem ist ebenfalls weiterhin auf einem Red Pitaya STEMlab 125-14 implementiert. Es soll die Grundwelle bei 100 kHz aktiv unterdrückt werden. Dazu wird die vorher als ideal bestimmte Schrittweite  $\mu$  von 6,7·10<sup>-3</sup> verwendet. Zur Synchronisation der Systeme gibt der FPGA der PFC den Takt vor. Zur Injektion der Gegenstörungen wird ein induktiver Übertrager verwendet. Dieser ist mit einem EMV-Ringferrit und einem Windungsverhältnis von 2:2 realisiert. Die Reststörungen werden durch einen kapazitiven Spannungssensor (RC-Hochpass) gemessen.

Bild 12: Schematische Darstellung des Demonstratorsystems

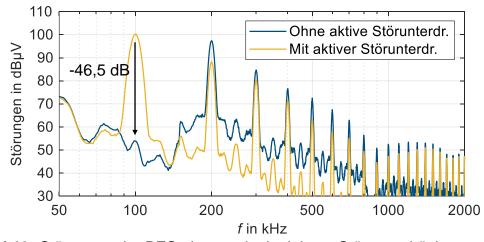

Die Messergebnisse für das Testsystem sind in Bild 13 dargestellt. Die Grundwelle der Störungen konnte erfolgreich um 46,5 dB reduziert werden. Nichtsdestotrotz kann festgestellt werden, dass die höheren Harmonischen um einige dB erhöht werden. Dies deutet darauf, dass das Gegenstörsystem nicht nur einen Sinus, sondern auch Oberwellen injiziert. In den Voruntersuchungen in Abschnitt 4.4 konnten für die Schrittweite  $\mu$  von

Bild 13: Störungen der PFC ohne und mit aktivem Störunterdrückungssystem

6,7·10<sup>-3</sup> jedoch keine signifikanten Oberwellen identifiziert werden. Daher liegt die Vermutung nahe, dass die Oberwellen durch nichtlineare Effekte des Systems verursacht werden. In weiterführenden Arbeiten sind damit nicht nur die Signalgenerierung, sondern ebenfalls die Injektoren und Sensoren weitergehend zu untersuchen. Dieser Effekt war in den Messungen mit dem Spitzenwertdetektor noch stärker ausgeprägt.

# 6 Zusammenfassung und Ausblick

Im Rahmen des Beitrags wurde ein Verfahren vorgestellt, um die elektromagnetischen Störungen einer Leistungsfaktorkorrektur mithilfe von modulierten Sinussignalen zu unterdrücken. Dazu wurde ein Algorithmus aus der aktiven Lärmkompensation auf einem FPGA-System implementiert und für die Anwendung optimiert. Anhand einer realen PFC wurde gezeigt, dass die Grundwelle (100 kHz) der Störungen erfolgreich um etwa 46,5 dB reduziert werden konnte. Es ist abzusehen, dass auch bei höheren Frequenzen (z.B. 1 MHz) ähnliche Ergebnisse erzielt werden können. Das Verfahren kann damit zu einer Reduktion des passiven Filteraufwands beitragen, wodurch der Bauraum und das Gewicht des Gesamtsystems reduziert werden kann. In den Untersuchungen an der realen PFC wurde festgestellt, dass die Störungen bei höheren Harmonischen durch das Gegenstörsystem erhöht werden können. Dies wird auf nichtlineare Effekte des Koppelsystems zurückgeführt. Daher sind für diese Anwendung weitergehende Untersuchungen an den Sensoren und Injektoren notwendig, um diese Einflüsse zu minimieren und die Effektivität des Störunterdrückungsverfahrens weiter zu verbessern.

## Literatur

- [1] Y.-C. Son, S.-K. Sul: "Generalization of active filters for EMI reduction and harmonics compensation". In *IEEE Transactions on Industry Applications*, Vol. 42, Nr. 2, S. 545-551, März/April 2006

- [2] N. K. Poon, J. Liu, C. K. Tse, M. H. Pong: "Techniques for input ripple current cancellation: classification and implementation [in smps]". In *IEEE Transactions on Power Electronics*, Vol. 15, Nr. 6, S. 1144–1152, 2000

- [3] B. Arndt, P. Olbrich, H. Reindl, C. Waldera: "Breitbandiger aktiver Hybrid-Filter für Kfz-Anwendungen". In *EMV Düsseldorf*, Düsseldorf, Deutschland, 20.-22.02.2018, S. 432-438

- [4] A. Bendicks, T. Dörlemann, S. Frei, N. Hees, M. Wiegand: "FPGA-basierte aktive Gegenkopplung der Schaltharmonischen von leistungselektronischen Systemen". In *EMV Düsseldorf*, Düsseldorf, Deutschland, 20.-22.02.2018, S. 652-661

- [5] A. Bendicks, T. Osterburg, S. Frei, M. Wiegand, N. Hees: "Wide-frequency EMI suppression of stationary clocked systems by injecting successively adapted cancellation signals". In *EMC Europe*, Barcelona, Spanien, 02.-06.09.2019, S. 36–41

- [6] D. G. Holmes, T. A. Lipo: "Pulse Width Modulation for Power Converters: Principles and Practice". Auflage 1, Wiley-IEEE Press, 2003

- [7] S. M. Kuo, D. R. Morgan: "Active noise control: a tutorial review". In *Proceedings of the IEEE*, Vol. 87, Nr. 6, S. 943–975, Juni 1999

- [8] A. Bendicks, T. Dörlemann, S. Frei, N. Hees, M. Wiegand: "Development of an adaptive EMI cancellation strategy for stationary clocked systems". In *EMC Europe*, Amsterdam, Niederlande, 27.-30.08.2018, S. 78-83