# Dissertation

submitted to the Combined Faculty of Natural Sciences and Mathematics of Heidelberg University, Germany for the degree of **Doctor of Natural Sciences**

Put forward by

### Vitali Karasenko

born in: Kryvyi Rih, Ukraine

Oral examination: 2020 May  $27^{\rm th}$

# Von Neumann bottlenecks

$\mathbf{in}$

# non-von Neumann

## computing architectures

A generic approach

**Referees:**

Dr. Johannes Schemmel (Heidelberg University) Prof. Dr. Ulrich Brüning (Heidelberg University) Neue Blicke durch die alten Löcher.

Georg Christoph Lichtenberg

#### Abstract

Der Begriff "neuromorphe Hardware" bezieht sich auf eine breite Klasse von Rechenmaschinen, die verschiedene Aspekte von kortikaler Informationsverarbeitung nachzubilden suchen. Sie instanziieren Neuronen, entweder physikalisch oder virtuell, die über zeit-singuläre Impulse (Spikes) miteinander kommunizieren. Die vorliegende Arbeit präsentiert eine generische Implementation eines Punkt-zu-Punkt (P2P) Kommunikationsprotokolls, welches gut geeignet ist, die besonderen Anforderungen an die Ein-/Ausgabe von neuromorphen Computern im Bezug auf spikebasierte Kommunikation zu erfüllen, insbesondere im Kontext von beschleunigten analogen Systemen. Ein solches Protokoll wurde auf dem neuesten Chip der neuromorphen BrainScaleS-2-Architektur namens HICANN-X implementiert, wo es ihn mit einem benutzergesteuerten FPGA verbindet. Bidirektionale Spikeraten von bis zu 250 MHz zusammen mit mehreren datenflussgesicherten Speicher- und Konfigurationskanälen werden über  $8 \times 1 \,\mathrm{Gbit \, s^{-1}}$  low voltage differential signaling (LVDS) double-data rate (DDR) Serialisierer ermöglicht. Da die vorgelegte Protokollfamilie unabhängig von der Implementation der Serialisierer ist, ist sie auch jenseits von neuromorpher Hardware anwendbar, etwa um die Modularisierung von Zielvorhaben zu unterstützen, oder um die Entwicklung von generischen Protokollbrücken zu ermöglichen.

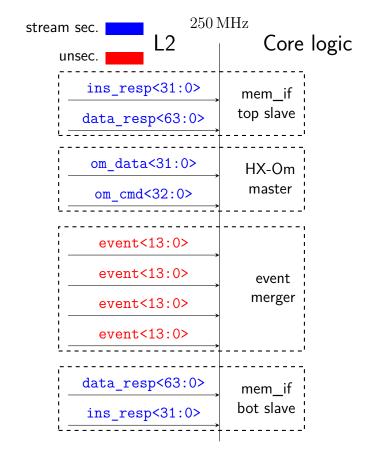

The term "neuromorphic" refers to a broad class of computational devices that mimic various aspects of cortical information processing. In particular, they instantiate neurons, either physically or virtually, which communicate through time-singular events called spikes. This thesis presents a generic register-transferlevel (RTL) implementation of a point-to-point (P2P) chip interconnect protocol that is well-suited to accommodate the unique I/O requirements associated with event-based communication, especially in the case of accelerated mixed-signal neuromorphic devices. A physical realization of such an interconnect was implemented on the most recent version of the BrainScaleS-2 neuromorphic hardware architecture—the HICANN-X system—to facilitate a high-speed bi-directional connection to a host FPGA. Event rates of up to 250 MHz full-duplex as well as several stream-secured configuration and memory interface channels are transported via  $8 \times 1 \,\mathrm{Gbit \, s^{-1}}$  low voltage differential signaling (LVDS) double-data rate (DDR) serializers. As the presented approach is entirely independent of the serializer implementation, it has applications beyond neuromorphic computing, such as enabling the separation of concerns and aiding the development of serializerindependent protocol bridges for system design.

# Contents

| T        | Tnt  | troduction                                                                               | 1          |

|----------|------|------------------------------------------------------------------------------------------|------------|

| T        | 1110 | troduction                                                                               | T          |

| 1        | Mot  | tivation and Outline                                                                     | 3          |

| <b>2</b> | Que  | eues                                                                                     | 7          |

|          | 2.1  | Protocol tunneling                                                                       | 14         |

|          | 2.2  | Example: OCP tunneling                                                                   | 15         |

| 3        | Stat | te of the Art                                                                            | 21         |

|          | 3.1  | Raw Serialization                                                                        | 21         |

|          |      | 3.1.1 Line Codes $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 23         |

|          | 3.2  | Gigabit Transceivers                                                                     | 24         |

|          | 3.3  | PCI Express                                                                              | 25         |

|          |      | 3.3.1 Monolithic Design                                                                  | 25         |

|          |      |                                                                                          | 26         |

|          |      | 3.3.3 PHY                                                                                | 26         |

|          | 3.4  | Conclusion                                                                               | 27         |

| II       | In   | nplementation 3                                                                          | <b>3</b> 1 |

| 4        | Gen  | neric Hardware                                                                           | 33         |

|          | 4.1  | Sum Types                                                                                | 34         |

|          |      | 4.1.1 A software example                                                                 | 34         |

|          |      | 4.1.2 HDL implementation                                                                 | 35         |

|          |      | 4.1.3 Sum Type Queues                                                                    | 38         |

| <b>5</b> | The  | e Universal Translator 4                                                                 | 43         |

|          | 5.1  | Encoding scheme                                                                          | 43         |

|          |      | 5.1.1 Encoding sum types                                                                 | 49         |

Page

### CONTENTS

|   |               | 5.1.2 CRC                                                                                                                                                     | 50       |

|---|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|   | 5.2           | UT sender                                                                                                                                                     | 51       |

|   |               | 5.2.1 Client interface                                                                                                                                        | 53       |

|   |               | 5.2.2 PHY interface                                                                                                                                           | 53       |

|   |               | 5.2.3 Derived constants                                                                                                                                       | 55       |

|   |               | 5.2.4 Data path                                                                                                                                               | 57       |

|   |               | 5.2.5 Control path $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 5$                                                                         | 59       |

|   | 5.3           | UT receiver                                                                                                                                                   | 51       |

|   |               | 5.3.1 Data path $\ldots \ldots \ldots$        | 55       |

|   |               | 5.3.2 Control path $\ldots \ldots \ldots$     | 66       |

|   | 5.4           | Synthesis Example                                                                                                                                             | 37       |

|   |               | 5.4.1 Experiment Setup $\ldots \ldots \ldots$ | 58       |

|   |               | 5.4.2 Results $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $.$                                                                              | 71       |

|   | 5.5           | Conclusion                                                                                                                                                    | 72       |

| 6 | Stre          | eam secure Queues 7                                                                                                                                           | <b>5</b> |

|   | 6.1           | -                                                                                                                                                             | 75       |

|   | 6.2           | -                                                                                                                                                             | 76       |

|   | 6.3           |                                                                                                                                                               | 78       |

|   |               |                                                                                                                                                               |          |

| Π | II            | HICANN-X 8                                                                                                                                                    | 1        |

| 7 | Ove           | rview 8                                                                                                                                                       | 3        |

| • | 7.1           |                                                                                                                                                               | 33       |

|   | 7.2           |                                                                                                                                                               | 35       |

|   | 7.3           | 0                                                                                                                                                             | 37       |

| 8 | $\mathbf{PH}$ | V 8                                                                                                                                                           | <b>9</b> |

| 0 | 8.1           |                                                                                                                                                               | )0       |

|   | 8.2           |                                                                                                                                                               | )1       |

|   | 8.3           | 0                                                                                                                                                             | )5       |

|   | 0.0           |                                                                                                                                                               | )8       |

| 9 | ни            | CANN-X communication infrastructure 10                                                                                                                        | 1        |

| 5 | 9.1           | Downstream                                                                                                                                                    |          |

|   |               |                                                                                                                                                               |          |

|   | 9.1<br>9.2    | Upstream                                                                                                                                                      |          |

| 9  | 9 HICANN-A communication infrastructure |                        |  |  |  |  |

|----|-----------------------------------------|------------------------|--|--|--|--|

|    | 9.1                                     | Downstream             |  |  |  |  |

|    | 9.2                                     | Upstream               |  |  |  |  |

|    | 9.3                                     | Testing and Evaluation |  |  |  |  |

|    |                                         | 9.3.1 Events           |  |  |  |  |

|    |                                         | 9.3.2 ARQ              |  |  |  |  |

|    |                                         |                        |  |  |  |  |

| 10 | Con                                     | clusion                |  |  |  |  |

# Part I Introduction

### Chapter 1

# Motivation and Outline

The human thirst for knowledge was always accompanied by a desire to process and store information throughout the ages. From mechanical devices like the Antikythera mechanism (Jian-Liang and Hong-Sen, 2016) or Charles Babbage's Difference engine (Swade, 2002), through electromechanical devices, such as the famous Bombe computers (Smith, 2014), to modern complementary metal-oxide-semiconductor (CMOS) processors, both the architecture and realization of computers evolved with our understanding of the universe, as well as the mathematical grasp of information processing itself. While the modern computing landscape is dominated by devices that track their ancestry to the von Neumann architecture (von Neumann, 1993), the realization that the mammalian brain is both a very powerful computer, and also works based on entirely different principles, has always fueled research looking to complement or even replace von Neumann machines with biologically inspired devices.

Attempts to realize *neuromorphic computers* have increased in recent years following both the rekindled interest in artificial neural networks (ANN), as well as the decline of single-threaded performance growth. Starting in the early 2000's, the semiconductor industry found itself in an increasingly paradoxical situation: as Moore's law steadily provided more and more usable transistors per area, it became harder and harder to get the same computing performance boost from them as processor core frequencies peaked at around 3-4 GHz, mostly due to thermal reasons. While conventional computers marched on to leverage the extremely high transistor counts of modern CMOS manufacturing technologies for multi-core processors (together with a paradigm shift towards concurrent programming), neuromorphic devices seek to build inherently parallel computing architectures based on small building blocks (neurons) that exchange activation events (spikes) through a routing bus fabric.

The initial vision of Carver Mead (Mead, 1990) was interpreted and implemented in many ways by various research labs that explored the utility, feasibility and scalability of different approaches to neuromorphic computing. We could not hope to provide a comprehensive review of the various proposed architectures, but rather point to literature, such as (Furber, 2016; Indiveri et al., 2011; Thakur et al., 2018). We will however point out a core challenge that these devices all have to face, namely the immense amounts of data that they are capable of producing and consuming, both locally on chip, as well as externally when connecting to a host computer or forming a larger system.

I/O has always been the Achilles heel in computation regardless of the underlying architecture. The speed at which a computational unit can process data has significantly outmatched the speeds at which this data can be made available. This is the *von Neumann bottleneck*, which has only become more pronounced since its first observation sometime in the 1970's, after the speed increase of transistor logic started to outpace the bandwidth improvements of chip interconnects. Neuromorphic devices suffer from the von Neumann bottleneck as well, but we will argue that they require a different way of addressing it than conventional von Neumann architectures in Chapter 7. The availability of chip interconnect technology, both commercially and in literature, is heavily biased by the strong drive to focus on the needs of conventional processor architectures due to their sheer dominance for the last fifty years.

While neuromorphic computers, as prominent examples of non-von Neumann architectures, are in the exploratory stage of finding optimal implementations, as well as carving ecosystem niches, now is also a good time to start thinking about how an optimized communication infrastructure for neuromorphic hardware might look like, which represents the core topic of this work. To this end however, we have taken a generic approach and will first lay the groundwork by discussing how any digital devices exchange data from a high-level perspective and introduce both the concept of Queues as well as abstract methods to bundle and transport their data between chips in Chapter 2.

In Chapter 3 we focus on the state of the art, i.e, various serializer technologies and their ability to serve as tunnels for Queues. We will see how more accessible technologies often lack desired features for generic data transport, while high-end interconnects tend to be monolithic in nature, which makes them fast and feature-rich, but at the expense of flexibility when used in non-conventional scenarios.

Part II introduces a generic method to tunnel arbitrary bundles of Queues through virtually any kind of serializer using hardware description language (HDL) implementations of sum types and the Universal Translator (UT) encoding scheme. We discuss not only the method itself, but also motivate the immense benefits offered by the generic approach as opposed to a monolithic bespoke solution, as it orthogonalizes many design choices and simplifies verification, thus freeing development time to add features or fine-tune parameters. In particular, we describe a generic method to transform almost any module interface into a bundle of Queues which can then be serialized via the UT. This opens up the possibility to build serializer-independent feature-rich bridges for common bus interfaces, which can streamline the development effort for open-source hardware.

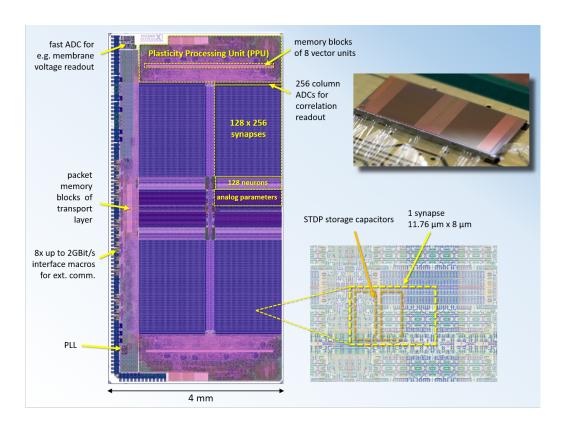

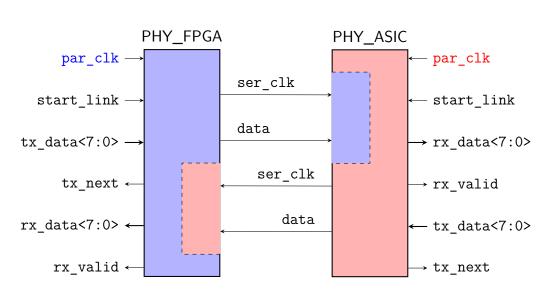

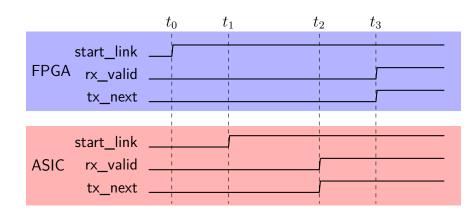

Lastly, Part III describes the communication infrastructure for the currentgeneration neuromorphic hardware at the Electronic Vision(s) group in Heidelberg, which was successfully manufactured and already used for various experiments. It uses the concepts and modules introduced previously to create a complex bi-directional interconnect between the neuromorphic chip and a host field programmable gate array (FPGA) using an independently provided serializer. Here, we leveraged the generic, yet powerful sum type technique to implement features like link layer channel bonding, link health checking and failure resistant configuration while also providing a bi-directional high transaction rate event transport channel between the devices.

1 MOTIVATION AND OUTLINE

# Chapter 2

### Queues

Like with virtually any system, designing hardware begins at the block diagram level. The design is broken down into sub-modules, each performing some task, which pass information between each other. *Information passing* is somewhat ambiguous in this setting, so let us clarify further.

Figure 2.1: Example block diagram with three modules. The arrows represent the direction in which the modules pass information between each other

On one hand, especially in RTL design, we define the direction of information flow by which side of a wire the driver is. This is also reflected in RTL code during module declaration in statements such as 'output logic valid' where the qualifying statement {input/output} describes whether the module is sender or receiver of information on that port. This is, however, not that simple when attempting to precisely define the direction of information passing in a more general context.

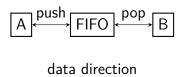

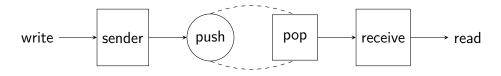

To illuminate the issue, let us first discuss one of the simplest non-trivial circuits that has a clear direction of data flow, the first-in-first-out buffer (FIFO) module. Its main purpose is to provide a *blocking interface* between two modules so that data may pass from one to the other. An example block diagram is shown in Figure 2.2, the declaration of a possible SystemVerilog interface can be found in Listing 1. We notice that the modports **push** and **pop** are each bi-directional, i.e, they feature both **input** and **output** ports in their declaration. This is of course necessary to provide a blocking interface

to the FIFO, which requires information exchange from the FIFO to the user to notify it that it is ready for the next transaction. Still, from a transactional point of view we define the direction of a FIFO to be from the **push** modport to the **pop** modport.

Figure 2.2: A FIFO connecting modules A and B. Module A connects at the push side of the FIFO, and module B at the pop side. Hence the data flow is from module A to module B

Usually, the term FIFO refers to a particular implementation involving some memory and control logic that stores data from the **push** modport into memory and presents data read from memory to the **pop** modport of the module. To be able to talk about directional information transfer between modules in an implementation-free manner, we introduce the following definition:

**Definition 2.0.1. Queues** Any pair of interfaces (a, b) that respectively perform identical functionality to a **push** and **pop** modport of a FIFO interface belongs to a *Queue* which we will write as Q(a, b). The following parameters are associated with any Queue:

- **latency** as the expected time between a data push into the Queue and its arrival at the pop interface.

- **throughput** as the expected number of transactions across the Queue per unit of time.

- **depth** as the maximum amount of in-flight transactions within the Queue.

This definition explicitly includes pairs of interfaces that are not in the same clock domain or even the same device. It obviously follows that any FIFO module is an implementation of a Queue that stays within a device<sup>1</sup>. We further categorize Queues depending on the admissible transaction patterns between their endpoints.

<sup>&</sup>lt;sup>1</sup>But not necessarily in the same clock domain as in the case of asynchronous FIFOs

```

interface fifo_if(

input logic wrclk,

rdclk

);

parameter int WIDTH = 1;

logic full, push, wrinit, empty, pop, rdinit;

logic [WIDTH-1 : 0] wrdata, rdata;

modport push (

input full,

output wrinit, push, wrdata

);

modport pop (

input empty,

output rdinit, pop, rdata

);

modport fifo (

output full, empty, rdata,

input wrinit, rdinit, push, pop, wrdata

);

```

#### endinterface;

Listing 1: Example of a parameterized FIFO interface with the modport fifo being accessed by the FIFO module itself, push by the user on the write side and pop by the user on the read side. The signals wrinit and rdinit perform the initialization of the FIFO at its respective side. The behavior is implementation-dependent, but generally defines a point in time after which transactions at the push modport correlate with transactions at the pop modport. The WIDTH parameter allows to re-size the FIFO to fit any message in any format by casting it into a packed bit-array of the appropriate size.

**Definition 2.0.2. Stream-secured Queues** A Queue that is guaranteed to show the same sequence of data at its output as the sequence of data pushed into it is stream-secure. The following parameters are additionally associated with any such Queue:

• mean time to failure (MTTF) as the expected time duration at which the above guarantee will be broken.

This definition seems unnecessary at first glance when coming from the usual FIFO perspective, as indeed any correctly implemented FIFO will always fall under this category because we usually operate under the presumption that data can never be corrupted on-chip in RTL design methodologies. On the other hand, the concept of a Stream-secured Queue appears naturally in the context of data transfers between devices where it is usually accepted that a wide range of effects can corrupt transactions and extra care needs to be taken to ensure that these can be detected, discarded and ultimately repaired. Stream-secured queues are usually discussed in the context of their implementation within a *Transport Layer* of some interconnect, where this functionality usually resides. The MTTF denotes the expected timescales at which one of the following error cases may happen:

- The pop interface stops emitting words that are in-flight.

- The **push** interface is never ready to accept new words.

- Data is re-ordered or otherwise corrupted.

As we will see later when considering implementations of stream secured Queues, the first case is usually due to an internal breakdown of the transport mechanism within the Queue. Blocking on the **push** side can be also either due to transport issues or because the **pop** side is never accessed which means stalls once the Queue depth is reached. Data corruption is the worst case and usually well guarded against, as for all practical purposes this case must never happen. In some sense, we much rather prefer for a Queue to stall than to start emitting wrong data, because while we can establish timeouts to detect stalls, there is no way to detect data corruption within a presumed secured Queue except adding meta data which amounts to tunneling a stream secured Queue through another.

We keep the definition purposefully implementation-free and simply note that a user does not necessarily need to know the precise implementation or internal behavior as long as she is provided with the guarantee that all transactions are appearing in-order at the receiving end.

Relaxing the requirements on data integrity, we introduce the

**Definition 2.0.3. word-secured Queues** A Queue that has a macroscopic probability to re-order or drop words, but provides a guarantee that individual words are correctly transported, is called word-secure. The following parameters are additionally associated with any such Queue:

• mean time to stream corruption (MTTSC) as the expected time duration at which a word-secured Queue deviates from a stream-secured Queue.

We point out the obvious implication that any stream-secured Queue is also word-secure but not necessarily vice versa. Because stream-security is a combination of two properties, namely that data is neither lost nor permuted, the loss of any of these automatically downgrades the Queue to be at most word-secured. We deem it impractical for our purposes to further sub-divide the classification into cases where messages can be either lost or permuted because these properties are highly implementation-dependent. Still, any implementation of a word-secured Queue should be done in awareness of the distinction.

At last, we define the

**Definition 2.0.4. Unsecured Queues** A Queue that can neither guarantee stream-, nor word security is called unsecured.

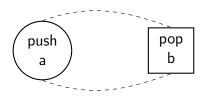

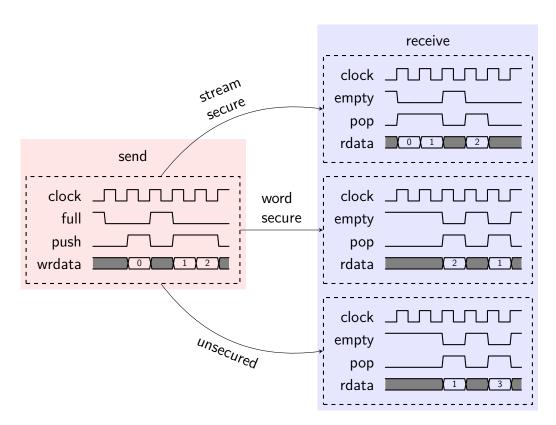

Example transaction patterns are shown in Figure 2.4.

Figure 2.3: A conceptual diagram of a Queue A(a, b). Data is transported from the push interface to the pop interface in a blocking manner.

Figure 2.4: Example transactions of different types of Queues. The colored regions separating the send and receive side of the Queue emphasize that the interfaces can reside in different clock domains or devices. For the word- and unsecured Queues only the best case scenario is shown where data is fetched out of the pop interface as soon as new data arrives.

To motivate these definitions, let us now briefly discuss some of their possible realizations in the context of chip interconnects. As we have mentioned previously, moving data between chips is considered to be unsecured unless extra precautions are taken as we will see in Chapter 3. To improve the security of such a Queue, internal mechanisms like checksumming may be introduced during data transport. This additional data provides redundant information that can be used to verify the integrity of the message at the receiving end which then can filter out messages it deems to be corrupt, making the Queue word-secured. Because checksumming can only drop erroneous data but can neither restore nor correct it by itself, additional measures must be taken to achieve stream security. Error correction techniques are usually distinguished into forward error correction (FEC) and backward error correction (BEC) depending on whether they need additional information by the sender or can use already received, redundant data for word recovery.

We will further note a few other properties of Queues.

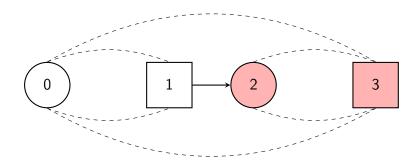

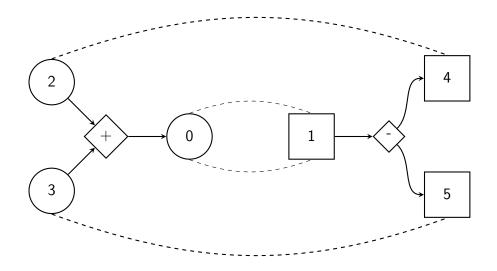

If a Queue Q is composed out of a series of Queues  $Q_N = [Q_0, Q_1, \ldots, Q_n]$ , the security of Q is at most the security of the lowest secured  $Q_i$  in  $Q_N$  (see Figure 2.5).

Figure 2.5: An example of Queue concatenation. Q(0, 1) and Q(2, 3) form together Q(0,3). Because Q(2,3) is unsecured, so is Q(0,3) regardless of the security of Q(0,1). Interfaces 1 and 2 are directly connected, thus forming a trivially stream secured Queue.

A collection of Queues with endpoints in the same hardware domain can be tunneled via a single Queue and additional circuitry for encoding and multiplexing (see Figure 2.6).

Figure 2.6: An example of a Queue sum. Q(2, 4) and Q(3, 5) are formed via Q(0, 1) and additional logic that merges their data such that it can be distinguished and split after transport. We call it a sum because the words of Q(0, 1) transport data from either Q(2, 4) or Q(3, 5).

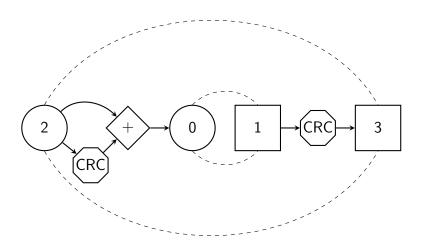

Finally, it is always possible to increase the security of a Queue by adding

circuitry at the end points without any further information about the Queue itself (see Figure 2.7). A common method is to generate metadata from the outer Queue and then summing it together with the Queue content itself into a tunnel that is less secure than required.

Figure 2.7: An example of Queue enhancement. Q(2,3) is word-secured although Q(0,1) is not due to additional logic that derives cyclic redundancy check (CRC) words which are then added together with the data of Q(2,3). At the receiving side is then a filter that filters the incoming data for correct CRC and then passes it to the **pop** interface after stripping any checksum information. Note that no interface need to be modified to achieve this upgrade in transport security.

### 2.1 Protocol tunneling

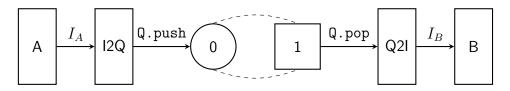

Now that the groundwork is laid out we can begin to discuss transporting higher-level protocols in terms of Queues. Any module provides access to its inner state via ports that are grouped into interfaces such as the FIFO interface shown in Listing 1. A module often provides several interfaces which is a convenient way to achieve *separation of concerns*, as for example in the FIFO module case the **push** interface usually does not need to know about the **empty** flag that is exposed on the **pop** interface. Interfaces can always be split into a *master* and a *slave* side which simply denotes the direction of transactions passing through them. For example, a FIFO module is the slave at its **push** interface as the direction of the transaction is into it, while the opposite happens at the **pop** interface, where data is being read out of the FIFO thereby making it the master. When we talk about protocol tunneling we mean the case where some module A tries to access another module B that may reside neither in the same clock domain nor on the same device altogether. This is achieved by placing circuitry that accepts the request of A acting as the slave, and transports it in some way to the target clock domain where it acts as a master towards B. Any response of B is then transported in the reverse manner towards A. An interface is called *blocking* if there are handshake signals that are not part of the request itself but rather notify the master and slave that a request has been made. If an interface is not blocking there can be no certainty that a transaction has been successfully registered by the slave unless so guaranteed by the specification. It should be clear by now that any interface can be faithfully represented using one or several Queues and hence can be tunneled as long as the communication infrastructure implements Queue sums.

Figure 2.8: Structural view of an interface tunnel between modules A and B. Module A connects via its interface  $I_A$  to an adapter interface to queues (I2Q) which translates the transaction into a series of messages which it puts into the tunneling Queue Q via the push interface. These messages are then assembled by the queues to interface (Q2I) module into a request to module B via  $I_B$ .

### 2.2 Example: OCP tunneling

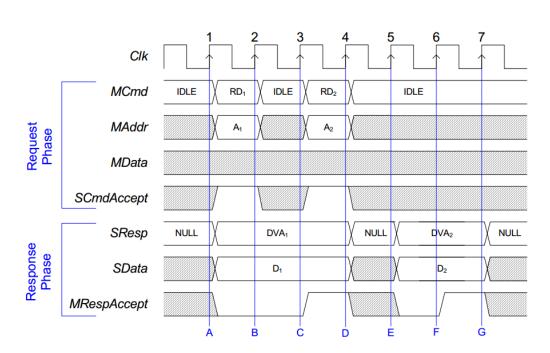

The Open Core protocol (OCP) is a popular standardized bus protocol for interconnecting modules on a chip. While more recent protocols like Advanced eXtensible Interface (AXI) are now more commonly used, it is functionally very similar and can serve as a fitting example to demonstrate its tunneling via Queues. The interface is comprised of two sub-interfaces called Bus-Master, which performs an address-mapped request, and BusSlave which responds to these requests.

Figure 2.9: Example OCP transactions.

Conceptually, a module performs a blocking request transaction at the BusMaster interface into the bus and receives a response at the BusSlave interface some time later<sup>2</sup>. Looking at Figure 2.9 it is fairly easy to see that the BusMaster interface can be thought of in terms of two Queues Cand D, while the BusSlave is represented by one Queue in the opposite direction. We have a Queue C whose messages contain the combination of the Fields MCmd and MAddr and a Queue D that contains the MData field. The response side is modeled by a Queue S that contains the SData field. Because Queues can be blocking, their interface already contains the handshake of the OCP interface which is represented by the 'MCmd != IDLE && SCmdAccept' condition, and even allows us to remove the IDLE symbol from the MCmd field in C. Similarly, as long as the SResp field only contains the symbols  $\{NULL,$ DVA} which simply model a handshake together with the MRespAccept field, the data in S does not need to contain it because it is already a blocking interface. While it is also possible to represent the BusMaster interface with just a single Queue, that approach also misses on the opportunity to realize that a push into D is only necessary if the command was a write, while a push into C is always necessary. Two Queues represent the interface more faithfully, clearly and efficiently and only need trivial logic to model the transaction besides the Queues themselves as can be seen in Listing 3

$<sup>^2\</sup>mathrm{E.g},$  the master and slave modports respectively in Listing 2

```

interface Bus_if #(

parameter int addr_width,

parameter int data_width,

parameter int sdata_width

) ( input logic Clk );

//Request Phase ports

enum{IDLE, RD, WR} MCmd;

hereis[data_width_1:0] MData

```

logic[data\_width-1:0] MData, logic[addr\_width-1:0] MAddr; logic SCmdAccept;

```

//Response Phase ports

```

```

enum{NULL, DVA} SResp;

logic [sdata_width-1:0] SData;

logic MRespAccept;

modport master(

input Clk,

output MAddr, MCmd, MData, MRespAccept,

input SCmdAccept, SData, SResp

);

modport slave(

input Clk,

input MAddr, MCmd, MData, MRespAccept, MByteEn,

output SCmdAccept, SData, SResp

);

endinterface

```

Listing 2: Example OCP interface declaration. The ports are prefixed with either 'M' or 'S' to indicate whether they are driven by the master or slave modport.

```

//BusMaster logic

assign C.wrdata = '{Bus.MCmd == READ, BusMAddr};

assign D.wrdata = Bus.MData;

assign SCmdAccept = C.push;

always_comb

begin

C.push = 1'b0;

D.push = 1'b0;

if ( Bus.MCmd != IDLE && !C.full ) begin

if ( Bus.MCmd == READ )

C.push = 1'b1;

else if ( !D.full ) begin

C.push = 1'b1;

D.push = 1'b1;

end if

end if;

end

//BusSlave logic

assign Bus.SResp = !S.empty;

assign Bus.SData = S.rdata;

assign S.pop = MRespAccept;

```

Listing 3: An example SystemVerilog implementation of a module that acts as a Slave on an OCP Bus interface and translates the transactions into three Queues C, D and S.

The reverse process, namely the construction of an OCP interface out of three Queues is entirely symmetric. Listing 4 shows an example HDL implementation of the necessary control logic. Note how no sequential logic is needed here either, and yet the interfaces are blocking and will for instance wait until data in D is available before asserting 'Bus.Mcmd = WR' if data in the command Queue C has been interpreted as containing a write instead of a read.

#### 2.2 EXAMPLE: OCP TUNNELING

```

//BusMaster logic

//highest bit encodes read-not-write, the rest is MAddr

assign Bus.MAddr = C.rdata[$high(C.rdata-1):0];

assign Bus.MData = D.wrdata;

assign C.pop = Bus.SCmdAccept && Bus.MCmd != IDLE;

always_comb

begin

Bus.MCmd = IDLE;

D.pop = 1'b0;

if ( !C.empty) begin

if ( C.rdata[$high(C.rdata)] ) begin

Bus.MCmd = RD;

else if ( !D.empty ) begin

Bus.MCmd = WR;

D.pop = Bus.SCmdAccept;

end

end if;

end

//BusSlave logic

assign S.wrdata = Bus.SData;

assign S.push = !S.full && SResp == DVA;

assign MRespAccept = S.push;

```

Listing 4: An example SystemVerilog implementation of translating three Queues C, D and S into an OCP interface Bus.

#### 2 QUEUES

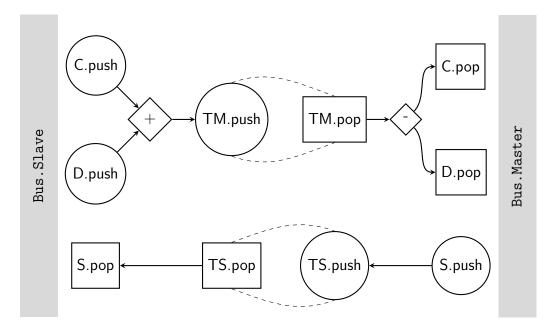

Figure 2.10: Example Queue diagram of an OCP tunnel. Since data flows in two directions during the **request** and **response** phase, at least one tunnel per direction is needed. Queues C and D are merged into TM which acts as a tunnel and ensures the necessary security. Queue TS tunnels the OCP slave responses contained in S and also provides suitable security.

The point of this exercise is to demonstrate that when it comes to protocol tunneling a simple yet generic and comprehensive design flow can be established. The design process must address the following questions:

- How many Queues are needed?

- What security do the Queues require?

- What is the available serialization method?

In this thesis we will demonstrate that it is possible to build a link layer that efficiently satisfies these design parameters using generic modules. But first, let us discuss the various techniques for data transport between devices that are currently in use.

# Chapter 3

# State of the Art

Any information-processing device, be it a brain or a chip, needs a way to communicate with the outside world to be deemed useful. For chips, this usually means talking to other devices via some protocol. As we outlined earlier, an *interconnect* needs to at least facilitate the tunneling of a Queue across chip boundaries for a point-to-point connection. *Communication* usually implies a bi-directional information exchange, so if the protocol is not bi-directional by nature, it needs to be instantiated twice on the device, as a sender and receiver respectively. Here, we will review some common interconnects and technologies that connect chips and compare their strengths and weaknesses in implementation and performance. We will focus on P2P connections because as it is the main application we are interested in, and thus omit discussing protocols like Ethernet which were designed to be easily routable through anonymous networks.

### 3.1 Raw Serialization

This technique is probably the simplest way to exchange data between chips. It consists of a shift register of some width that is continuously shifted out by the sender. The shifted out bit is then connected to a general purpose In/Out (GPIO) pin and an internal counter ensures that the next parallel word is loaded into the shift register when the last bit has been sent. Since the data does not have any clocking information, the sender and receiver side of the link must be externally synchronized, which usually means sharing the clock via a dedicated pin. Adding a bit of complexity, the serializer can be upgraded to DDR mode by shifting the data on both edges of the clock. And, of course, the data can be transmitted using the LVDS standard to improve electrical characteristics.

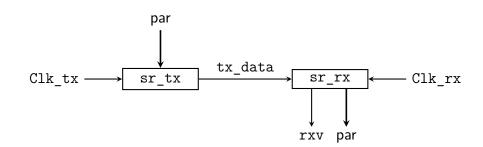

Figure 3.1: Shift register based serializer pair block diagram. Parallel data is loaded into sr\_tx which shifts it bitwise into sr\_rx via the tx\_data wire. After the appropriate number of bits is shifted into sr\_rx it asserts rxv to notify the user that a word is available. Clk\_tx and Clk\_rx must be synchronized to ensure correct data capture.

The obvious upside of raw serializers is their simplicity. They are very easy to implement, do not require external IP, and are small both in the gate- and pin count. More complex protocols can build upon raw serializers and simply use them as their PHY layer. An important advantage is the arbitrary width of the shift register, which aids the *separation of concerns* by not imposing any restrictions on the encoding scheme of the upper layer protocols.

However, using raw serializers also has quite a few drawbacks.

The speed is limited by the phase alignment between the clock and the data pins. While internal delays can be in principle compensated for in the chip, the external wire lengths on the PCB are not known in advance and impose a mismatch between the clock and data edges. When not compensated for by using programmable delay circuits—which add to the device cost either because of development effort or IP licensing costs—the serializer will only reliably work up to bit rates significantly below the worst possible delay mismatch.

If programmable delays are used, there has to be a way to calibrate the link by sampling the data until a known pattern is recognized. This in turn implies that after reset the link is at first in a training phase for some time until the receiver has calibrated the delays to reliably sample the training pattern. Only then should the link transmit payload data. A robust synchronization and transition between these link phases is best achieved via bi-directional communication between link partners which makes duplex connections all the more useful. Runtime variations such as temperature and voltage drifts can also affect the phase relationship between data and clock significantly, which makes it not only nearly impossible to statically compensate for it at the receiver, but also suggests constant link monitoring and/or re-training if necessary to ensure the best quality of service (QoS).

Raw serialization is also vulnerable to bit-errors, both on the clock and

data pins. If the data pin is corrupted, i.e, sampled incorrectly at the receiver, the transmitted word has a bit flip at the respective position after de-serialization. If however the clock pin is corrupted, the receiver loses the word synchronization with the sender and de-serializes garbage data until the link is reset. A related problem is how to find the correct word boundary in the first place after the link is powered on. Furthermore, the interface that a raw serializer provides is not automatically blocking, as there is no way to distinguish between active and idle link states at the reception side. This can be achieved by e.g turning off the sampling clock (Clk\_rx in Figure 3.1) as is done for instance in the Joint Test Action Group (JTAG), Serial Peripheral Interface (SPI) and similar interconnects<sup>1</sup>.

Therefore, while raw serialization is a good technique to build upon more complex protocols, it is not suitable as a reliable high-speed link by itself and is the prototype implementation of an unsecured Queue whose MTTF strongly depends on the data rate.

#### 3.1.1 Line Codes

Line codes are a popular technique to address some of the problems mentioned previously. While they represent a large family of different encoding schemes, we will discuss the 8b/10b (Widmer and Franaszek, 1983) encoding specifically as a commonly used way to imprint higher-level information onto raw binary data. A review of various line codes can be found in, e.g, (Schouhamer Immink, 2001).

The 8b/10b encoding takes, as the name suggests, 8b blocks of data and encodes them into 10b code words. The mapping is chosen such that DCbalance is maintained within two encoded words, and aims to avoid long runs of ones and zeroes. The encoding also defines several code words that have no corresponding data words, but still obey the above criteria. These control symbols can be used to find word boundaries as well as signal the begin and end of a data transmission. They also allow for a decoupling of the client interface from the SerDes logic, since the SerDes can autonomously inject comma symbols that indicate a link idle state when no client data is available which can then be filtered out by the receiver. This decoupling also allows for different clock domains for the SerDes and the client, and consequently also some, albeit limited, choice in data width. The encoding also helps detect bit errors, as there are many 10 bit sequences that are

<sup>&</sup>lt;sup>1</sup>Speaking of these, we will not discuss either protocol further as they are barely a step up from raw serialization and do very little—if at all—encoding that aids link security. While they certainly have their use, we will regard them as unsecured Queues at most and use them as such as building blocks for a more secure and feature rich link.

considered illegal by the scheme, so they can be recognized as such at the receiver. However, many bit errors remain undetected, hence one should not rely too much on code word security if data integrity is absolutely essential.

The 8b/10b encoding is still widely used in a variety of communication systems. Still, it is important to understand that it is an encoding for PHY layer data, and should be used in conjunction with a link layer protocol. The PHY layer should contain the 8b/10b codecs, and use the control symbols to perform tasks like word synchronization, idle commas and packet delimiting upon link layer requests. The link layer uses a suitable interface to transmit its data serialized to bytes which are encoded as data words at the PHY layer.

From our perspective, a serializer that employs line coding can be regarded as a weakly word-secured Queue. Comma characters provide the blocking interface regardless of whether the clock is running and the illegal data characters will catch certain kinds of bit errors.

### 3.2 Gigabit Transceivers

An evolution from raw serializers, multi-gigabit transceiver (MGT)s are now the backbone of almost all high-speed serial protocols. The use of clock-data recovery (CDR) eliminates the need for a dedicated clock pin and thus the phase alignment problem. Virtually all MGTs employ a scrambling line code, be it 8b/10b or something more modern like the 64b/66b variant to increase bit efficiency. This is important to ensure the phase-locked loop (PLL) used in CDR sees enough transitions to properly lock while also providing the benefits outlined in Section 3.1.1, such as flow control via comma symbols.

While MGTs are common in most modern FPGAs, where they are widely used, they appear less frequently in ASICs. This is mostly owed to their complexity which is necessary to achieve the high bit rate that sets the MGTs apart from more simple SerDes approaches as discussed e.g in Section 3.1. Exacerbated by the sorely underdeveloped Open Source space for hardware design, it is often a rather expensive endeavor for a design team to procure an MGT macro since they will either have to develop it in-house or purchase from an IP vendor. Still, MGTs are currently the only feasible choice to achieve high data rates over a low pin count, and are thus the preferred PHY layer choice for virtually all modern high-speed communication protocols.

### **3.3** PCI Express

Designing and implementing a custom Transport Layer protocol is not always necessary. There are several suitable standards defining a high-speed full stack communication protocol between devices using MGTs as PHYs. Here, we will briefly discuss the perhaps most ubiquitous high-speed device interconnect, the PCI Express protocol. It will serve as the main point of comparison to our work, so we must first evaluate Peripheral Component Interconnect Express (PCIe) from a conceptual point of view.

The design philosophy behind PCIe was to specify a scalable featurecomplete general-purpose interconnect architecture. The user communicates over the interconnect via transaction layer packets (TLPs) that have a fixed definition. Additionally defined data link layer packets (DLLPs) transport protocol-internal information and implement features like flow control, data integrity and error handling. The Physical Layer then serializes the TLPs and DLLPs using one or several MGTs which employ 8b/10b encoding and also handles tasks like link training. The Base Specification Document (Group, 2010) provides an in-depth description of the interconnect.

#### 3.3.1 Monolithic Design

While PCIe aims to provide a general-purpose interconnect, there are still applications which do not fit well into its design space. PCIe is not intended to be a customizable protocol apart from offering several backwards-compatible versions which mostly concern the number of lanes and their speed. Therefore, all available implementations, both commercial and Open Source<sup>2</sup>, offer PCIe as a monolithic block in a take-it-or-leave-it fashion. This is a reasonable design decision since for instance, if one designs a custom accelerator that is used by an off-the-shelf desktop computer via its PCIe slot, the PCIe block instantiated in the accelerator must be fully compatible to the desktop which is easier to ensure in a monolithic specification. On the other hand, if, for example, we want to build an ASIC that is connected to an FPGA, we fully control both sides of the interconnect and are thus free to choose a protocol that fits our needs best. And while PCIe certainly fulfills its promise of being a general-purpose interconnect, there may be constraints like power, area, I/O or latency that make technology desirable which allows for tradeoffs in these areas while still offering a static user interface. It is important however to not fall into the Not Invented Here mentality and, if possible,

<sup>&</sup>lt;sup>2</sup>There are only FPGA-based Open Source PCIe implementations, which instantiate hard MGTs for the PHY layer.

evaluate the desired features compared with their counterpart defined in the PCIe specification.

#### **3.3.2** User Interface

PCIe is a byte-aligned protocol at all layers, which is not surprising since an 8-bit byte is typically the smallest accessible unit in most CPU architectures and programming languages. It also naturally follows that the user-side data path can be somewhat parameterized to a width that is also commonly found in the microprocessor world as long as it is still byte-aligned. Typical use cases are 32 or 64 bit wide user data paths which simultaneously fit the common granularity of most current programming models and keep the user clock at manageable speeds while still achieving high throughput.

Packet types are encoded via the first byte in a TLP, with currently 20 such types being defined. These packet types facilitate transactions in 4 address spaces, Memory, I/O, Configuration and Message. While the packet types and the corresponding address spaces provide an interface that can be used to transport almost any kind of data over any network topology, it comes at a cost of rather high overhead independently of the actual application particularly for small transaction sizes. All user packets are also secured via a replay buffer and a CRC to ensure stream coherence, which is an important feature but also rather costly in terms of protocol timings, bit efficiency and hardware usage. If we again evaluate PCIe by its capability to tunnel Queues, we find that it provides facilities to tunnel many of them by either distinguishing them via Packet types, or address spaces since any suitably formatted TLP can be interpreted as a push into the corresponding Queue. PCIe guarantees stream security without the option of downgrading in exchange for performance or hardware real-estate, and also forces at least byte alignment for the Queue width. It is also not suitable for transporting small transactions due to the high overhead within a TLP.

#### 3.3.3 PHY

As mentioned previously, PCIe relies upon MGT serializers which use scrambling<sup>3</sup> to transmit and receive Transaction Layer and Link Layer packets. Their behavior is strictly specified including the link training procedure and the supported speeds. *Channel bonding* is also implemented at the PHY layer, allowing for increased throughput at the cost of higher I/O footprint. It works by distributing the individual bytes of a TLP in an alternating pat-

$<sup>^{3}</sup>$ Both the 8b/10b code, as well as its 128b/130b variant in recent versions

tern on the available lanes during transmission. The obvious benefit is that no two TLPs can overtake each other during serialization because only one TLP is transmitted at a time. Furthermore, adding links not only improves the throughput, but also the latency of the link. As a drawback however, the PHY layer needs to make sure that all the individual lanes are delay-aligned during link training to exclude the possibility of a faulty reconstruction of the packet at the receiving side. Only 1,2,4,8 and 16 lanes per link are currently supported since these allow for easy distribution of the TLP and DLLP in a byte-wise fashion.

### 3.4 Conclusion

When looking at the individual solutions to transporting data from one chip to another, we notice two sharp extremes. Those who have the resources, both financial and in the design space, will often opt for a proven solution and use one of the common high-speed serial protocols like PCIe, Universal Serial Bus (USB) or Serial AT Attachment (SATA). These projects often afford a practical point of view that it is more efficient to adopt an existing ecosystem even if it does not fit the bill exactly instead of building a custom solution. This adaptation however makes it hard to build a well parameterized design because requirements like word alignments and data segmentation are now an important consideration to make. When the requirements of the core logic are too much at odds with the interconnect, an intermediate layer is built which will attempt to translate the interface of the core logic into the user interface of the interconnect. These adapters are often treated as an afterthought and are prone to being buggy and inefficient in both chip realestate and encoding.

On the other end of the spectrum we find projects that choose to build a custom interconnect to serve their needs. There are many reasons to do so, ranging from lacking the means to procure a suitable IP or not being able to fit the block into the chip real-estate, to determining that the user interface is too much at odds with that of the core logic. In most of these cases the design team will start from a bottom-up approach, i.e, they will pick a suitable serializer and then build the rest of the Link and Transaction Layer from there to ultimately connect to the core logic. This approach often runs into the realization that the finished interconnect will have to replicate many of the core features of, say, PCIe, but still being different enough that reusing existing modules is impractical or outright impossible in the case of commercial IP blocks. Since the design and verification of blocks like PCIe nodes takes many person-years, the design team is then often forced to implement a solution that is sub par in both feature scope or even performance. Thus, these projects often end up with interconnects that are not thoroughly verified, lack features, extensibility and parametrization, and have their relative simplicity and thus small chip real-estate footprint as the only upside.

To improve upon this situation where a group is stuck between the choice of either adopting a big monolithic block that is not parameterizable in any meaningful way or trying to build something in-house that stands almost no chance of competing against foreign IP, we can formulate the requirements for a desirable solution as a consequence of the previous discussion.

**Modularity** The layers in the interconnect should be clearly separated and easily modifiable and even exchangeable with minimal changes to the surrounding layers.

Serializer independence The interconnect should provide a simple and generic interface towards the PHY layer which enforces minimal requirements on how data is transported over the air gap. In particular, this interface must admit free parametrization of the data width that is passed between the PHY and the link layer to account for any serialization ratio. The link layer must be able to optionally generate idle characters upon request if the PHY expects a continuous stream of user data after initialization. The link layer must also be able to optionally generate and inject CRCs for any subset of data packets in case the PHY layer does not provide data integrity checking on its own. It should be possible to go from a simple shift register to an MGT as a PHY layer via simple parameter adjustments. Together with the *Modularity* requirement, this also implies that low level electrical properties like line emphasis should be encapsulated at this level such that the user side of the serializer entirely consists of synchronous digital logic.

**Channel Bonding** The interconnect should be able to take advantage of multiple links if they cannot be merged already at the PHY layer. This should be reflected as a simple parameter with a wide range and must be transparent to the user interface.

**User interface** The user interface must be able to tunnel any number of independent Queues of any configuration as described in Chapter 2 in both directions. It should be trivial to add or delete a Queue, adjust its width or change the configuration from e.g unsecured to stream-secured independently from all others.

**Synthesis-friendliness** The design should be easy to pipeline in order to simplify implementation. Where possible, there should be free parameters which can gradually trade performance for chip real-estate.

**Performance** While we obviously desire a high throughput and low latency for our application, we acknowledge that no design with such a high grade of flexibility can ever hope to achieve the performance of an optimized monolithic design like PCIe. Therefore, we downgrade performance considerations to *best effort* for any given parametrization with the expectation that a well-fitting parametrization will make up for the overhead incurred in adapting to a better, but worse-fitting interconnect.

### 3 STATE OF THE ART

# Part II Implementation

## Chapter 4 Generic Hardware

For scientific progress to occur, it is not enough to criticize why the state of the art is lacking and subsequently propose a seemingly superior solution; One has to actually demonstrate this superiority. We have spent quite some pages to criticize the current options for device communication while being purposefully vague about implementation details of how generic Queue tunneling can actually be achieved. Such an achievement rests on two legs, RTL description and simulation and subsequent successful synthesis in either an FPGA or application-specific integrated circuit (ASIC). Designing hardware comes with the perhaps peculiar caveat that not everything that should be in theory possible is actually possible in practice which as we noted before often impedes scientific progress. There is a plethora of reasons why that holds true and mundane problems like budgetary and/or timing constraints during development or tool immaturity are surely a contributing factor to the reputation of hardware designers being overly conservative in relying on proven designs instead of innovation.

In particular, we observe a lack of the equivalent of what is called *generic* programming in the software world, a design philosophy where the RTL description is so deeply parameterized that a particular parametrization can result in drastically more different circuitry than one observes by changing e.g the width or depth of a FIFO. As we will see however, this is a necessary feature of our design because there is otherwise no way to construct an efficient yet generic Queue tunnel<sup>1</sup>. When we look at the properties of Queues described in Chapter 2, most of them correspond to straightforward well known implementations. The FIFO interface is a very popular archetype and is widely used in all kinds of module interfaces and of course also in de-

<sup>&</sup>lt;sup>1</sup>We have pointed out before how PCIe achieves generic tunneling by having fixed headers for packet type and address space which are big enough for any application yet are often wasteful because not all functionality is used in a particular design

vice interconnects. Really, the only intriguing implementation question is posed in Figure 2.6: How can we write an RTL description of some number of queues which can differ both in their widths and security level such that their data can be tunneled via a single queue and still be distinguishable at the receiving end?

## 4.1 Sum Types

#### 4.1.1 A software example

Let us for a moment step back and answer this question from a more abstract perspective that programming languages can give us, particularly when they strive for clarity above implementation. FIFO objects are present in most programming languages, we point to the  $\mathtt{std}::$ queue in C++ as an obvious example. They can be used to transport and buffer messages between agents in different parts of a program. Generic programming in C++ allows us to create a  $\mathtt{std}::$ queue of any type we like which gives us freedom of choosing any fitting data structure to serve as an atomic message between agents and then simply declare a  $\mathtt{std}::$ queue on it.

```

// example message declaration

struct message {int a; double d;};

// declare a queue of messages

std::queue<message> q;

```

Now let us assume that we actually have two different message types that we want to transport via a single Queue:

```

// declare message type A

struct messageA {int a; double d;};

// declare message type B

struct messageB {char a; float d; long c};

// declare a queue of messages A and B

// what do we template on?

std::queue<???> tunnel;

```

It is obvious that we need a new type in the above code snippet that is derived from both messageA and messageB in the above example. This type must satisfy two properties: It must be big enough to contain either messageA or messageB and it must contain additional information that allows us to find out which type it is currently holding. These derived types are called *Sum Types* or tagged unions and are dual to the more commonly known *Product Types* such as structs and tuples. Sum Types were added in C++17 under the name of std::variant<>, which lets us complete the above code snippet:

```

// declare message type A

struct messageA {int a; double d;};

// declare message type B

struct messageB {char a; float d; long c};

// declare a queue of messages A and B

std::queue<sdt::variant<messageA, messageB>> tunnel;

```

This code gives us a Queue that contains a sequence of messages which can each be either messageA or messageB. Trying to add to the Queue a type that is neither messageA nor messageB will fail to compile which improves code correctness. C++ Variants can be queried about the type they are currently containing via the std::visit free function which then provides the splitting mechanism that allows us to de-multiplex the messages into individual Queues after tunneling.

#### 4.1.2 HDL implementation

The question now becomes whether it is possible to create the same kind of Sum Type abstraction as e.g std::variant<> in a synthesizeable HDL. We will see that this is indeed possible if we are willing to sacrifice some type safety. Let us begin with a SystemVerilog example:

```

// declare message type A

typedef struct packed

{

logic[1:0] a;

logic[3:0] b;

} messageA_t;

// declare message type B

typedef struct packed

{

logic[3:0] a;

messageA_t b;

logic c

} messageB_t;

```

Recall that the only base type of any synthesizeable HDL is logic which represents a single bit and hence either a single FlipFlop or wire in hardware. Any higher order types like arrays, tuples or structs are simply for human readability and do very rarely bear any real correspondence to the resulting circuit after synthesis. Although HDLs like SystemVerilog have types like int or byte these are nothing more than aliases for logic[31:0] and logic[7:0] respectively. Ultimately, any synthesizeable HDL data type has a direct correspondence to a bit vector of the appropriate size which is why the following can be always done:

We can freely assign both a bit vector to a packed struct of arbitrary field layout and vice versa as long as the total number of bits matches in both objects. There is no fundamental reason that can prevent us from doing so because the synthesized logic can only consist of binary functions and FlipFlops which have no further structure; Any attempt to prevent the designer from doing the above is the result of higher order reasoning about the design which is for example what code linters try to do. This is ultimately the reason why FIFO modules or interfaces only have a WIDTH parameter and are very rarely templated on types, although newer versions of SystemVerilog offer this feature; While the data\_{in,out} port signifies the amount of bits that are accessed or stored at a time, their higher-level structure is irrelevant to the implementation and is merely syntax sugar. All of this is to say that it suffices being able to create Sum Types of bit arrays of variable lengths because that is the only property that is still present after synthesis.

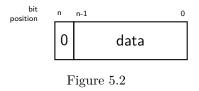

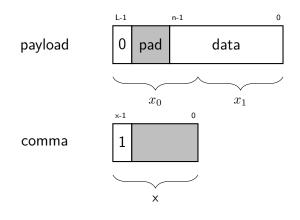

As noted previously, a sum type needs to be able to hold any of the types it is derived on together with information on what it currently holds. A suitable representation is therefore a struct with the fields data and tag. To be able to construct sum types out of an arbitrary amount of parent types we can use a list that contains the sizes of the individual parents.

Since we are ultimately dealing with bit arrays of varying length, the data field is again a bit array with the greatest length of the parent types. The tag field will then simply contain the index of the parent type in the type list. Thus, we can now finally write down a SystemVerilog implementation of the sum type for messageA\_t and messageA\_t as follows:

```

typedef struct packed

{

logic [$clog2($size(typelistAB))-1:0] tag;

logic [$max(typelistAB)-1:0] data;

} sumAB_t;

```

Because we derived the sum type from a list it also inherits some very useful properties which we list here. **Slicing and Concatenation** Two sum types can be merged to form a new flattened sum type. The type list of the resulting sum type is simply the concatenation of its parents.

As an example, assume that sumAB\_t represents the two message types that a single client which might be the master side of a bus adapter as described in Figure 2.10 speaks. We can merge two of these clients into a single Queue by forming a concatenated sum type like so:

```

localparam int

twoclientsAB [2*$size(typelistAB)] = '{2{typelistAB}};

```

After deriving the sum type struct out of the type list in the usual manner shown above, we now have a framework of creating Queues that can fit an arbitrary number of clients with an arbitrary number of message types. The reverse process, namely creating two sum type out of one is also directly equivalent to slicing the original type list into two children lists. Simple logic can then be built that assigns the data into the two children and also appropriately offsets the tag fields for easy and type safe de-multiplexing.

**Scalar operations** We can also just as easily modify sum types by doing element-wise operations on the individual elements in the underlying type list. The most useful of these is element-wise addition which corresponds to extending the parent types with an extra field.

#### 4.1.3 Sum Type Queues

Because the sum type is again simply a collection of bits we can now trivially construct a FIFO interface for it using the template introduced in Listing 1:

```

fifo_if

#(

.width($size(sumAB_t))

) fifoAB (

.wrclk(),

.rdclk()

);

```

Example pushes into the FIFO may look like this:

```

//write messageA_t into fifo

assign fifo.wrdata = '{ '0, '{2'b01, 4'ha}};

assign fifo.push = ~fifo.full;

```

Similarly, the de-multiplexing of the FIFO output could look like the following snippet:

```

messageA_t messageA;

messageB_t messageB;

logic [$size(typelistAB)-1:0] messages valid;

sumAB_t message_read;

assign message_read = fifo.rdata;

assign messageA = message read.data[$bits(messageA t)-1:0];

assign messageB = message_read.data[$bits(messageB_t)-1:0];

always_comb

begin

messages valid = '0;

if (~fifo.empty) begin

case (message read.tag)

0: messages valid[0] = 1'b1;

1: messages_valid[1] = 1'b1;

endcase

end

end

```

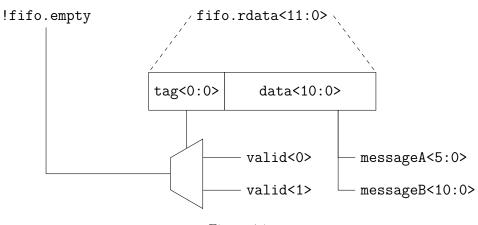

The above de-multiplexing logic translates into the circuit shown below:

Figure 4.1

Comparing the HDL code in Listing 5 with the RTL circuit in Figure 4.1 we can discuss some of the benefits of generic hardware. On one hand, the RTL code manages to express the de-multiplexing of a sum type into the individual parent types without loss of generality. Changing the parent types will correctly propagate through the design after synthesis which is owed mostly to the fact that a SystemVerilog **struct packed** keyword provides us with automatic conversions to and from bit vectors<sup>2</sup>. Also, in case the sum type is modified to contain more parent types, adapting the de-multiplexing is as simple as adding a statement that casts the data into some new parent type as well as an additional branch in the case statement to generate the respective **valid** signal. It is even possible to create a de-multiplexer that will automatically create additional branches using **generate** loops, as long as it is parameterized not on the sum type but rather the underlying type list since it contains all the necessary information.

All of this is achieved without sacrificing hardware efficiency; The synthesized RTL circuit looks exactly as expected with no resources wasted. Recall as a contrast the user interface of a PCIe interconnect. As we have discussed in Section 3.3, it provides fields to distinguish between the payload data which can be used to implement the tag field of a sum type. However, both the data type field as well as the payload data itself have a fixed width. If the actually required tag is smaller than the data type field, resources are wasted and bits are unnecessarily transported wasting bandwidth. In the rather unlikely case that the tag field is too small some additional encoding must be employed to provide the missing information. As we also discussed,

<sup>&</sup>lt;sup>2</sup>Languages like VHDL which tend to frown upon such liberal features require a bit more work in that for every type one must also additionally specify the casting functions to and from bit vectors.

#### 4.1 SUM TYPES

the fixed width of the payload data in PCIe can result in an inefficient bit usage of the data field of the sum type depending on the parents with potentially some additional encoding logic required.

This leads us to a more general issue; We have now created a hardware domain where modules communicate with each other via arbitrary messages that are passed through FIFO interfaces with a structured way to combine and split messages where necessary. However, This simple view hinges on the requirement that each FIFO **push** or **pop** transaction produces exactly one message that can be either a singleton type or some sum type that can be processed further. As long as we are staying on-chip this is a manageable albeit somewhat cumbersome restriction. Virtually any synthesis tool flow provides us with FIFOs with parameterizable data widths of a wide range that can in principle accommodate almost any use case. To be useful in the context of chip interconnects, where as we have seen we often do not have the choice to freely parameterize the user interface, we must find a way to generically serialize sum types into a stream of words with a wide range of widths.

### 4 GENERIC HARDWARE

## Chapter 5 The Universal Translator

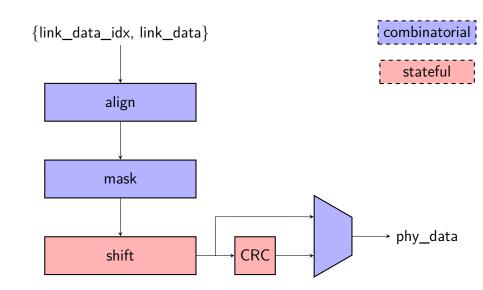

We present here an implementation of a generic RTL module pair for the encoding and decoding of any sum type into words of any width. Colloquially, the names UT sender and receiver have been established for them to emphasize their truly awesome parameterizeability. Looking again to the software world, the UT implements functionality similar to boost::serialize() which can translate any C++ object into a byte stream and vice versa. This comparison is however not completely apt because the UT must be able to deal with blocking as well as non-blocking stream interfaces as well as arbitrary data widths and not only bytes.

Figure 5.1: UT sender connecting to a receiver via a Queue. write and read are arbitrary sum types as described in Section 4.1, the width of the Queue is a free parameter.

## 5.1 Encoding scheme

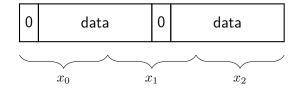

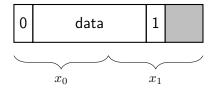

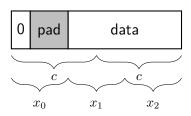

There are indeed many ways to encode information into a stream of symbols. One such way is for example the 8b10b encoding which we have discussed earlier. There, 8 bit data words are encoded into 10 bit symbols or code words. Disregarding the nice electrical properties that the scrambling provides and the error detection, the encoding also gives us a structure that we can use to meaningfully encode data. This is because the 8b10b encoding also defines several special symbols which can be used to denote the BEGIN (B), END (E) and IDLE (I) phases of a transaction together with DATA (D[]) symbols that denote payload. We can then begin to define datagrams which get encoded as a string of such characters.

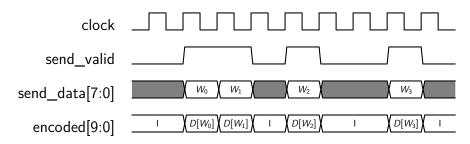

As an illustration, we show a timing diagram of a blocking 8b10b encoder that translates user bytes into code words.

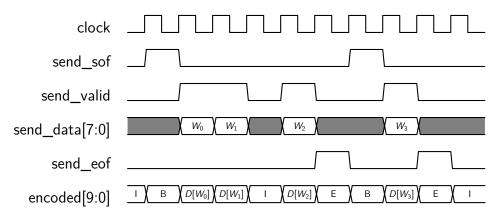

In this example, we have no way to distinguish whether a higher level object is constituted of the sequence  $[W_0, W_1]$  or just the single byte  $[W_0]$ . Because this encoding scheme only cares about the integrity of the individual code words, any information that lets the user group several bytes into a larger data structure must be implemented using the payload. Alternatively, we can use the aforementioned BEGIN and END characters to introduce framing into the coding scheme. We can extend the user send interface to include start-of-frame (SOF) and end-of-frame (EOF) ports that signal framing information to the encoder.

This interface allows the sender to clearly communicate which data words form a data structure using the BEGIN and END symbols. It is even possible to insert IDLE symbols during a frame transition to indicate a pause in transmission.

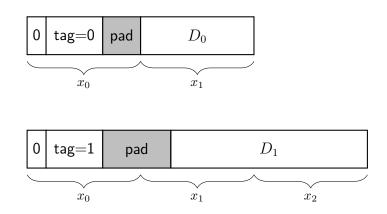

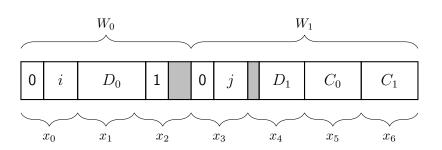

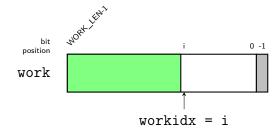

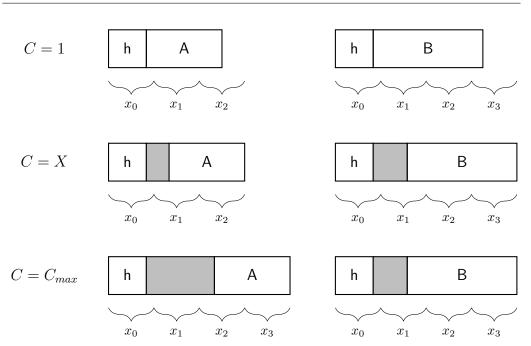

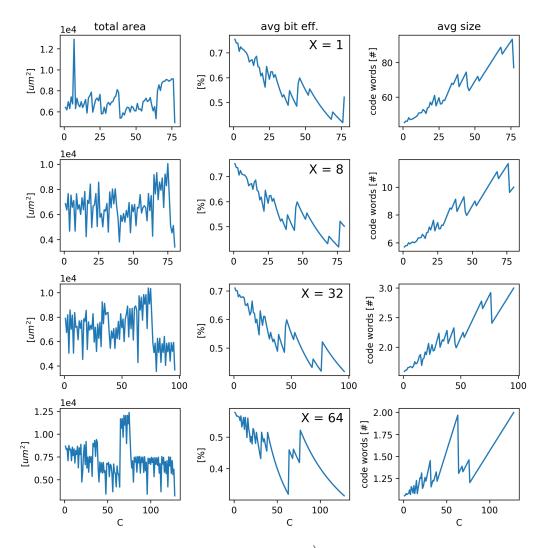

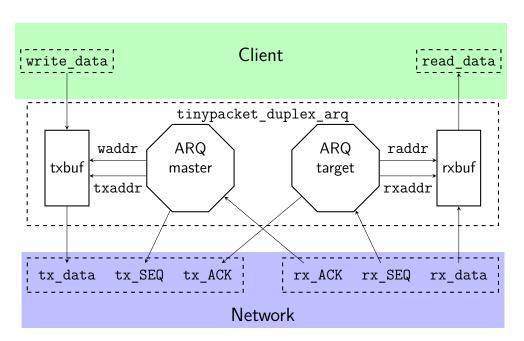

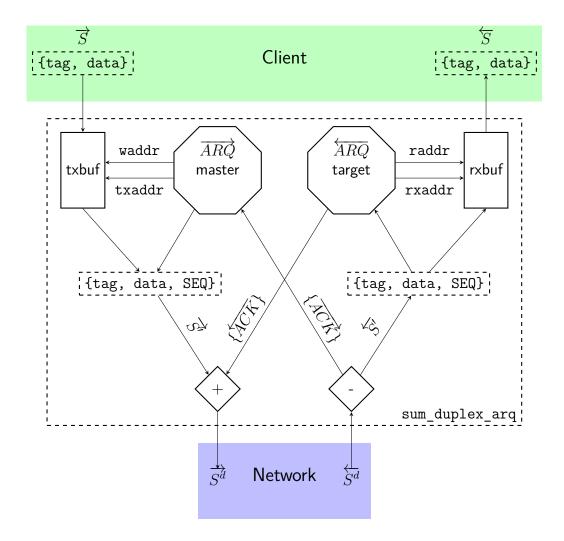

Note however, that there isn't any reason to keep the 8b10b encoding for the data words during a frame from an encoding point of view since an individual symbol doesn't really carry useful meaning anymore by itself. In fact, the entire scheme seems unnecessarily wasteful in encoded bits since we are expending 3 code words of 10 bit each to transmit 8 bit of payload in the worst case.<sup>1</sup> Often, these overhead concerns are brushed away by the observation that in the limit of long frames the bit efficiency converges to 80%. Still, this puts the burden on the user to make sure to create frames that are big enough which often requires one or several additional protocol layers that provide the user with a convenient interface while ensuring optimal packing and data alignment at the lower encoding level. These layers must be keenly aware of the underlying encoding and are almost always required to be altered or replaced entirely if the interface changes either at the user or PHY layer. And, as always, we are left with the problem that the PHY must be able to coherently transmit the 10 bit code words which can otherwise mean further bit efficiency losses and additional logic if, for example, the PHY uses an analog bit encoding that results in 3 bit symbols.