International Journal of Electrical and Computer Engineering (IJECE) Vol. 8, No. 4, August 2018, pp. 2054~2062 ISSN: 2088-8708, DOI: 10.11591/ijece.v8i4.pp2054-2062

**D** 2054

# Low Noise Amplifier using Darlington Pair At 90nm Technology

# Rashmi Singh, Rajesh Mehra

Department of Electronics and Communication, National Institute of Technical Teachers Training and Research, Chandigarh City, Chandigarh, India

| Article Info     | ABSTRACT                                                           |

|------------------|--------------------------------------------------------------------|

| Article history: | The demand of low noise amplifier (LNA) has been rising in today's |

Received Aug 4, 2017 Revised Jan 8, 2018 Accepted Jan 15, 2018

#### Keyword:

Cascade Circuit simulation CMOS Darlington pair Low noise amplifier Wideband The demand of low noise amplifier (LNA) has been rising in today's communication system. LNA is the basic building circuit of the receiver section satellite. The design concept demonstrates the design trade off with NF, gain, power consumption. This paper reports on with analysis of wideband LNA. This paper shows the schematic of LNA by using Darlington pair amplifier. This LNA has been fabricated on 90nm CMOS process. This paper is focused on to make comparison of three stage and single stage LNA. Here, the phase mismatch between these patameters is quantitavely analyzed to study the effect on gain and noise figure (NF). In this paper, single stage LNA has demonstrated 29 dB measured gain, while the three stages LNA has demonstrated 29 dB measured gain. Here, LNA designed using darlington pair shows low NF of 3.3-4.8 dB, which comparable to other reported single stage LNA. Hence, findings from this paper suggest the use of single stage LNA designed using Darlington pair in transceiver satellite applications.

Copyright © 2018 Institute of Advanced Engineering and Science. All rights reserved.

#### Corresponding Author:

Rashmi Singh, Department of Electronics and communication, National institute of Technical Teachers Training and Research, Chandigarh, City-Chandigarh, India. Contecter.rashmi@gmail.com

#### 1. INTRODUCTION

Currently, expanding use of high data rate wireless communication systems, high resolution radars, millimeter-wave (mm-wave) trans-receivers, medical devices and other radio communication systems have highlighted the applications of low noise amplifier (LNA) to achieve better sensitivity and low noise figure [1]-[10]. In recent, based on the demand for requirement to amplify very week signal, low noise amplifier (LNA) has been used like signal coming from a satellite [1]-[10]. Power of satellite is very limited and designers want to pick up a 20 watt signal from miles to miles away. The signal is very week because it is coming from long distance, so, designers have to amplify that signal [2], [3]. Designers can't use normal amplifier because normal amplifier itself has noise that can mask the real signal. So Designers have shown to choose LNA which have been suggested to possess less inductors, capacitors and also low noise transistors. A LNA amplifies a very week signal without degrading its signal to noise ratio (SNR) [4]-[6]. Normally LNA generates power gain of 100 (20dB) while decreasing the SNR by a factor of 2. Normal amplifier increases the power of both the signal and noise in signal. LNA minimizes the extra noise [5], [6].

The LNA, which uses complex matching networks is suggested to possess a large number of inductors or transmission lines that may consumes a large chip area and need of large amount of DC power [8]-[17]. In earlier reported topology of LNA, there are discernible problems of requiring a high voltage supply and high power consumption. Further, for a better high data rate, there is need of a maximization of the relative bandwidth at high carrier frequencies. Appreciably in case of mobile

applications, a significant reduction of DC power consumption is favourable. In some instances, maximum gain can be achieved in highest gain mode, but these success compromise the linearity and noise figure [10]-[20]. This paper proposes a three stage LNA using cascode connection. In three stage LNA, two stages are cascode and one is Darlington pair amplifier. This circuit required less power consumption and low voltage supply as compared to the conventional one.

#### 2. RESEARCH METHOD

#### 2.1. Basic staructure of LNA

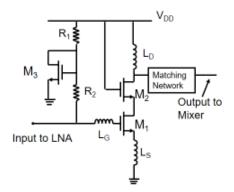

The low noise amplifier (LNA) is referred as the first participating block in a receiver and LNA has ben suggested to contribute in bringing better performance specifically the sensitivity of wireless communications systems. The cascode architecture has been suggested to bring a significant amount of isolation of input – output. In the next, the transistor M2 separates another component Miller capacitance [1]-[10]. Here, Input Impedance has been shown to be derived from utilizing the source degeneration inductor Ls. Another component Gate inductor Lg initiates the frequency resonance. Further, in the same schematic model, the tuning granularity is shown to be obtained by the network with matching output [8]-[10]. The matching network in the output is the combination of varactor and satellite. The impedance in the load is converted into one parameter of subsequent stage as input impedance by using a LC network [11]. If matching network is properly designed then it transfer the maximum power up to load. If input voltage to the varactor (DC) is varied, then frequency of the output is shown to be matched with a different frequency [12], [13]. Figure 1 shows the basic architecture of LNA.

Figure 1. Basic architecture of low noise amplifier

#### 2.2. Noise figure

The variation in the signal to noise ratio (SNR) variation has been suggested to be created due to radio frequency (RF) signal chain component and that variation is measured by NF and noise factor (F) [14], [15]. In case of NF and F, the minimum value is indicated to better performance because such specifications specify the amplifier or radio receiver presentation and capability [16]-[20]. The of noise power in output of any device to the portion of there of attributable to thermal noise in input terminalis called noise factor and at that point the standard value of noise temperature is 290k. Further, the NF has been described as the ratio of original output noise to the remaining noise in a setting, where device is not able to introduce any noise. Further, the signal over noise ratio of input to signal to noise ratio of output may also be described as the NF. Here, the NF or F is denoted by unit decibels (dB) [16]-[20].

$$NF = \frac{SNR_{in}}{SNR_{out}} = \frac{S_{in}/N_{in}}{S_{out}/N_{out}}$$

(1)

Noise factor as a function of a device

$$NF = \frac{N_{device} + G \cdot N_{source}}{G \cdot N_{source}}$$

(2)

G=Power gain of the device.

### 2.3. CMOS LNA

To confine the decay of the signal-to-ratio (SNR), several reports suggest that high gain and a minimum low NF should be attributed to first stage of an RF receiver for ultra-wideband (UWB) systems [21]. Further, high gain and a low NF LNA have also been indicated to be one of characteristics of LNA [22], [23]. Since the noise specific of the front end of an RF receiver is calculated with the help of LNA.

It has been observed that basic requirements for designing wideband LNAs could be such as flat and wideband gain, high gain and low NF in comparison to complete UWB frequency band at low power consumption. In connection with attachment of an antenna port, it is suggested for wideband 50  $\Omega$  input matching [24], [25]. Essentially, three main different methods of wideband matching are available. But, these described topologies have been faced with some difficulties like high NF (the resistive termination, the common gate) and large chip area (the band pass LC filter). In present context, for achieving wideband input matching sparing the above mentioned problems in LNA, there is a preference for calculation of the two frequency matching method. In recent times, researchers have also been reported to be engaged in appreciable with reference to the circuit topologies of wideband LNAs like resistive shunt feedback topologies and distributed topologies. Further, these studies have shown relevance based on their greater wideband characteristics. It is also suggested that resistive shunt feedback amplifiers can demonstrate appreciable wideband input matching and gain [21]-[25].

Here, reported novel method of designing of input matching suggests a spontaneous matching method. Where Darlington-pair is considered to show maximum gain compared to the whole operating band evincing low power consumption. In the current era of technology advancement in wireless communication systems and wireless sensors utilized for Internet of Things (IOT) supported the overwhelming responses for the applications of wideband low noise blocks and thse low noise blocks are shown to deonstarte less chip area and reduced requierement of power [24]-[27].

To suffice the requirements of in wireless communication systems and wireless sensors, RF circuits without inductor are significantly suggested by focusing on the indystry and acamedia need. In a clear comparison to traditional RF circuits, the inductor less RF circuits is suggested to need smaller chip area. Nevertheless, inductor less RF faces some drwbacks as the relatively high NF and low linearity. In consequence, available devices including MOSFETs, resistors, etc., which are suggested to work as an alternate toinductive devices may show high noise power and additionally it may cause supply-voltage headroom issue [26], [27].

# 2.4. Cascode amplifier

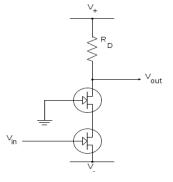

When common emitter stage is coupled with common base stage, the whole configuration is called two stage cascode amplifiers. Above configuration has more input –output isolation, high input impedance. In such configuration, there is suggestion about the output impedance, and higher gain or high bandwidth when compared to single stage amplifier. In current applications cascode can be designed by two transistors (BJT or FET), where common emitter or common source work as the first block and common base or common gate used as the second block. The cascode amplifier enhances the isolation between input and output (reduces reverse transmission). Such observation has been linked to the fact about the absence of coupling between output and input terminal. Hence, such amplifier excludes the chance of Miller effect. Therefore, it may contribute to a significantly enhanced bandwidth [28]. Figure 2 shows the basic circuit of cascode amplifier.

Figure 2. Basic circuit of cascode amplifier

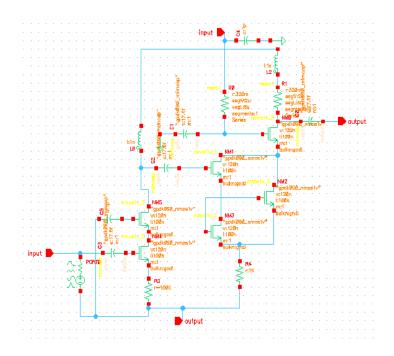

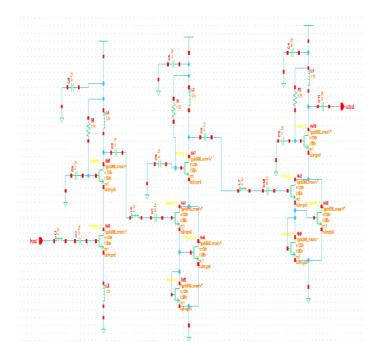

# 2.5. Circuit diagram

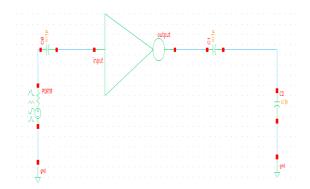

Two frequency matching process is used which is beneficial to get wideband input matching. The design process includes impedance matching at two frequencies simultaneously which is used for wideband input matching. A schematic diagram of the single stage LNA which has wideband is given in Figure 3. The cutoff frequency should be increased to improve the gain at higher frequency and relatively parasitic capacitances should be decreased [12] M1 ( $160\mu\Omega$ ) and M2 ( $160\mu\Omega$ ) and W1 ( $160\mu$ m) and W2 ( $240\mu$ m) [12]. In this paper, W1 ( $150\mu$ m) and W2 ( $300\mu$ m) so that W2/W1=2 and we can increase the gain of amplifier with low power consumption. A symbolic representation of single stage LNA used for simulation is presented in Figure 4.

Figure 3. Schematic diagram of the conventional pair amplifier

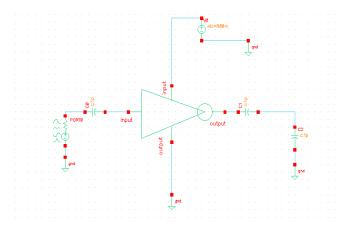

Figure 4. Symbolic representation of single stage LNA used for simulation

In Figure 5, the front end receiver has been shown to have basic block, which is called as LNA. To enhance the receiver chain sensitivity, the LNA should have minimum noise factor (NF). The cascade amplifier that provides better isolation and noise matching with source generation that is inductive and is used LNA. Figure 5 presents the circuit model of the proposed 3 stage LNA. Here, first stage is used for better noise factor i.e. cascade amplifier. The Darlington cascade amplifier is used to obtain high ft and gain in case of subsequent stages.

Further, this schematic model explains that the output matching network of each stage is evenly supplied with a short stub. This short-tub is in next comprehended by micro strip-line inductors to resonance the dependent of transistor to amplify the gain up to 60 GHz. In the above schematic diagram in Figure 6, an input matching network (IMN) is used to do noise matching with capacitor (C1) in series with transmission line inductor (LT1). ACCORDING TO paper 21 M1, LT1, LT2 are set so that to minimize input return loss (S11) and also decrease the NF at frequency 60 GHZ. In this paper return loss is minimized but NF is increased in case of three stage LNA.

Figure 5. This diagram depicts the representative model of three stage low noise amplifier

Figure 6. Symbolic representation of 3 stage LNA used for simulation

# 3. RESULTS AND DISCUSSION

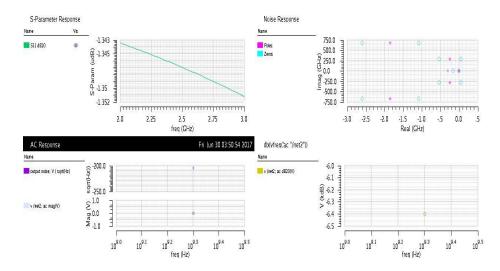

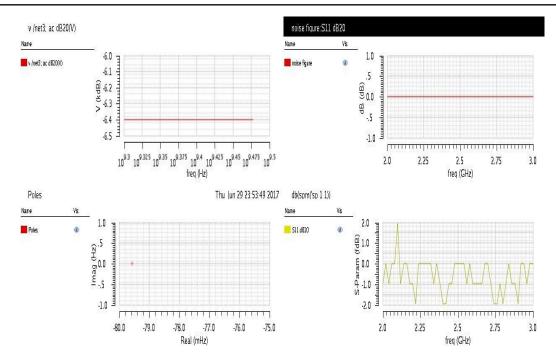

The S parameters of the LNA from 50 GHz are shown to be analyzed by an Agilent N5247A vector network analyser. Further, the S parameters from 67-90 GHz recorded with an R&S ZVA67 vector network analyser plus R&S ZVA-Z90E E-band extension module [30]. In the present paper, S parameter (S11) is calculated at 90nm using cadence virtuoso analog design environment which is shown in Figure 7(a). The maximum gain is 17.7 dB at 67 GHz [30]. In this paper, maximum gain in case of single stage is 23 dB and in case of three stage it is 29 dB. Hence, in our case, we find 32 percent improvement in gain as compared to the previous work reported for single stage LNA [30]. The measured bandwidth of the LNA increases and S parameters (S11 and S22) shift to low frequencies at some extent. This is seen as disadvantages to the single

stage LNA as reported in [30]. At the same time, we report that S parameter (S11) remains constant with respect to frequency level. The measured NF 5.4-7.4 dB and simulated NF is 4.7-5.3 dB. In the present paper, the NF in case of single stage is 3.3-4.8 dB and in case of three stage it is 8.1-8.9 dB. As compared to previous work [30], we report that in case of single stage LNA, there is an improvement of simulated NF by a decrease up to 25%. It is concluded that by increasing the number of stages, NF increases.

Figure 7. The figure shows the sub window of responses of single stage low noise amplifier. (a) s-parameter (b) pole zero response (c) AC response (d) noise response.

In the present paper, noise responses are also given in Figure 7(b), which shows the number of poles and zeroes in single stage LNA. A reported LNA demonstrates a measured small signal gain higher than 12 dB and measured NF is 6 dB [31]. In a paper, authors report the NF is high and low gain modes are about 5 and 13.5 dB respectively. In the low gain mode, the NF of proposed LNA can become worse [32]. In the present paper, we noticed that in the low gain mode the NF remained constant that shows that single stage LNA is in good condition. The high conversion gain and gain tuning capability are shown to record a large BB signals change compared to a large RF input power range [32]. The present circuit has the highest conversion gain of 47 dB. In case of a circuit consuming 120 mW DC power, a paper reported on the value of the measured minimum NF is 10.7 dB (double side band) is among the lowest reported values when circuit consumes 120 mW DC power. In our case, we found the NF of single stage LNA of 3.3-4.8 dB, which makes it relevant and useful. A circuit of 190 GHz receiver is designed using LNA and integrated in a 130 nm SiGe BiCMOS technology [33].

The high gain of LNA lowers the NF of an overall receiver [2]. The chosen gate widths of the Darlington pair amplifier are 160  $\mu$ m (M1), 160  $\mu$ m (M2), 80  $\mu$ m (M3) [2]. In this paper the chosen gate widths of the Darlington pair amplifier are 180  $\mu$ m (M1), 180  $\mu$ m (M2), 90  $\mu$ m (M3). The NF of the LNA is 2.85-4.5 dB and gain is 21DB [2]. In this paper the NF in case of single stage is 3.3-4.8 dB and gain is 23dB.

A LNA is suggested to include a minimum NF for heightened sensitivity of the receiver chain. As suggested earlier, the cascade amplifier can obtain a better NF than the Darlington cell. Because, the Darlington cell enhances fT and current gain which is equivalent to the bias current, the Darlington cell cascade amplifier displays better gain in comparison to the cascade amplifier [1]. In this paper Darlington amplifier is used to design LNA to increase the gain and lower down the NF and observed NF is 7.1-8.2dB [1]. In the present paper, we obtained NF of value 8.1-8.9 dB which is supported by other reported three stage LNA [1]. From Table 1, it is concluded that the NF is increased in amplifier if we increase the number of stages and gain flatness is also tough but gain and bandwidth is improved and SNR is also decreased. So, single stage LNA is preferred if we need low NF especially in case of satellite communication.

Figure 8. The figure shows the sub window of responses of three stage low noise amplifier, (a) s-parameter (b) pole zero response (c) AC response (d) noise response.

| Table 1. This Table Compares and Relates the Reported Data with Newly Measured Data. These Values are |

|-------------------------------------------------------------------------------------------------------|

| Calculated by Expending Calculator on Cadence Analog Tools of GPDK 90nm Technology                    |

| Calculated by Experiance Calculator on Calcule That of Tools of CTER yound Technology |           |       |           |       |                      |                           |  |  |

|---------------------------------------------------------------------------------------|-----------|-------|-----------|-------|----------------------|---------------------------|--|--|

| Parameter                                                                             | Single    | stage | Three     | stage | Proposed work single | Proposed work three stage |  |  |

|                                                                                       | paper [1] |       | paper [2] |       | stage                |                           |  |  |

| POWER GAIN (db)                                                                       | 21        |       | 28        |       | 23                   | 29                        |  |  |

| BANDWIDTH (ghz)                                                                       | 8         |       | 14        |       | 7                    | 15                        |  |  |

| NOISE FIGURE (db)                                                                     | 2.85-4.5  |       | 7.1-8.2   |       | 3.3-4.8              | 8.1-8.9                   |  |  |

| Process                                                                               | 180nm     |       | 90ni      | n     | 90nm gpdk            | 90nm gpdk                 |  |  |

|                                                                                       | Cmos      |       | Cmo       | DS    |                      |                           |  |  |

#### 4. CONCLUSION

Compares the three stages LNA and single stage LNA. Numerous significant constraints of respective amplifiers are calculated based on simulation outcomes and the consequences are presented in this paper for a fast qualitative comparison. Power gain of single stage LNA is 23dB and of three stages is 29db. Noise figure of single stage LNA is 3.3-4.8dB and that of three stages LNA is 8.1-8.9dB. Bandwidth of single stage LNA is 7GHz and that of three stages is 15GHz. This finding supports several existing attempts to design LNA with low noise figure and high bandwidth and showing potential applications in transceiver design. This paper proposes a three stage LNA using cascode connection. In three stage LNA, two stages are cascode and one is Darlington pair amplifier. This circuit required less power consumption and low voltage supply as compared to the conventional one.

#### ACKNOWLEDGEMENTS

The authors acknowledge the facilities and support extended from the Department of Electronics and communication, National institute of Technical Teachers Training and Research, Chandigarh, City-Chandigarh, India.

#### REFERENCES

[1] Kuei-Cheng Lin, Hwann-Kaeo Chiou, Kuan-Hsiu Chien, Tsung-Yu Yang, Po-Chang Wu, Chun-Lin Ko, Ying-Zong Juang, "A 4.2-mW 6-dB Gain 5-65-GHz Gate-pumped Down- conversion Mixer using Darlington cell for 60-GHz CMOS Receiver," *IEEE Transaction on Microwave Theory and Techniques*, 2013, vol. 61, no. 4, pp. 1516-1522.

- [2] J.- S. Paek, B. Park and S. Hong, "CMOS LNA with Darlington pair for UWB system," *Electronics Letters*, 2006, vol. 42, no. 16, pp. 913-914.

- [3] M. Khurram, S. M. Rezaul Hasan, "3-5 GHz Current-Reuse gm boosted CG LNA for Ultra wideband in 130-nm CMOS," *IEEE Trans. on VLSI Systems*, 2012, vol. 20, no. 3, pp. 400-409.

- [4] Ro-Min Weng, Chun-Yu Liu, Po-Cheng Lin, "A Low-Power Full-Band Low-Noise Amplifier for Ultra-Wideband Receivers," *IEEE Trans. on MTT*, 2010, vol. 58, no. 8, pp. 2077-2083.

- [5] Ching-Piao Liang *et al.*, "Analysis and Design of Two Low-Power Ultra Wideband CMOS Low-Noise Amplifiers with Out-Band Rejection," *IEEE Trans. on MTT*, 2010, vol. 58, no. 2, pp. 277-286.

- [6] J.-F. Chang, Y.-S. Lin., "0.99 mW 3-10 GHz common-gate CMOS UWB LNA using T-match input network and self-body-bias technique," *Electronics Letters*, 2011, vol. 47, no. 11, pp. 658-659.

- [7] Tran Van Hoi, Ngo Thi Lanh, Nguyen Xuan Truong, Nguyen Huu Duc, Bach Gia Duong, et al., "Design of a Front-End for Satellite Receiver," *International Journal of Electrical and Computer Engineering (IJECE)*, 2016, vol. 6, no. 5, pp. 2282-2290.

- [8] L. Ma, Z. G. Wang, J. Xu and N. M. Amin., "A High-Linearity Wideband Common-Gate LNA with a Differential Active Inductor," *IEEE Trans. on Circuits and Systems II*, 2017, vol. 64, no. 4, pp. 402-406.

- [9] Z. A. Djennati, K. Ghaffour., "Noise Characterization in InAlAs/InGaAs/InP pHEMTs for Low Noise Applicationst," *International Journal of Electrical and Computer Engineering (IJECE)*, 2017, vol. 7, no. 1, pp. 176-183.

- [10] Kamil Pongot, Abdul Rani Othman, Zahriladha Zakaria, Mohamad Kadim Suaidi, Abdul Hamid Hamidon, J.S. Hamidon, Azman Ahmad, "Design and Analysis High Gain PHEMT LNA for Wireless Application at 5.8 GHz", *International Journal of Electrical and Computer Engineering (IJECE)*, 2015, vol. 5, no. 3, pp. 611-620.

- [11] A. Amin, M. S. Islam, M. A. Masud, M. N. H. Khan. "Design and Performance Analysis of 1.8 GHz Low Noise Amplifiers for Wireless Receiver Application", *Indonesian Journal of Electrical Engineering and Computer Science (IJEECS)*, 2017, vol. 6, no. 3, pp. 656-662.

- [12] M. Parvizi et al, "A Sub-mW, Ultra-Low-Voltage, Wideband Low Noise Amplier Design Technique", IEEE Trans. on VLSI Systems, 2015, vol. 23, no. 6, pp. 1111-1122.

- [13] M. Parvizi, K. Allidina and M. N. El-Gamal, "Short Channel Output Conductance Enhancement Through Forward Body Biasing to Realize a 0.5 V 250 W 0.6-4.2 GHz Current-Reuse CMOS LNA", *IEEE J. of Solid-State Circuits*, 2016, vol. 51, no. 3, pp. 574-586.

- [14] R-F. Ye, T-S. Horng, and J-M. Wu, "Two CMOS Dual-Feedback Common-Gate Low-Noise Amplifiers With Wideband Input and Noise Matching", *IEEE Trans. on MTT*, 2013, vol. 61, pp. 3690-3699.

- [15] S. Shekhar, J. S. Walling, and D. J. Allstot, "Bandwidth Extension Techniques for CMOS Ampliers", *IEEE J. Solid-State C.*

- [16] J. Kim and J. Silva-Martinez, "Low-power, low-cost CMOS direct conversion receiver front-end for multi standard applications," *IEEE J. Solid-State Circuits*, 2013, vol. 48, no. 9, pp. 2090-2103.

- [17] M.-T. Lai and H.-W. Tsao, "Ultra-low-power cascaded CMOS LNA with positive feedback and bias optimization," *IEEE Trans. Microwave*, Theory Techniques, 2013, vol. 61, no. 5, pp. 1934-1945.

- [18] F. Belmas, F. Hameau, and J.-M. Fournier, "A low power inductorless LNA with double Gm enhancement in 130 nm CMOS," *IEEE J. Solid-state Circuits*, 2012, vol. 47, no. 5, pp. 1094-1103.

- [19] E. A. Sobhy, A. A. Helmy, S. Hoyos, K. Entesari, E. Sanchez-Sinencio, "A 2.8-mW sub-2-dB noise-figure inductorless wideband CMOS LNA employing multiple feedback," *IEEE Trans. Microwave Theory Techniques.*, 2011, vol. 59, no. 12, pp. 3154-3161.

- [20] M. Parvizi, K. Allidina, and M. N. El-Gamal, "An ultra-low-power wideband inductor less CMOS LNA with tunable active shunt-feedback," *IEEE Trans. Microwave Theory Technique*, 2016, vol. 64, no. 6, pp. 1843-1853.

- [21] F. Bruccoleri, E. A. M. Klumperink, and B. Nauta, "Wide-band CMOS low-noise amplifier exploiting thermal noise canceling," *IEEE J. Solid-state Circuits*, 2004, vol. 39, no. 2, pp. 275-282.

- [22] W.-H. Chen, G. Liu, B. Zdravko, and M. A. Niknejad, "A highly linear broadband CMOS LNA employing noise and distortion cancellation," *IEEE J. Solid-State Circuits*, 2008, vol. 43, no. 5, pp. 1164-1176.

- [23] S. C. Blaakmeer, E. A. M. Klumperink, D. M. W. Leenaerts, and B. Nauta, "Wideband balun-LNA with simultaneous output balancing, noise-canceling and distortion-canceling," *IEEE J. Solid-State Circuits*, 2008, vol. 43, no. 6, pp. 1341-1350.

- [24] J. Shim, T. Yang, and J. Jeong, "Design of low power CMOS ultra wide band low noise amplifier using noise canceling technique," *Micro Electron. J.*, 2013, vol. 44, no. 9, pp. 821-826.

- [25] K.-H.ChenandS.-I.Liu, "Inductor less wideband CMOS low-noise amplifiers using noise-canceling technique," *IEEE Trans. Circuits Syst. I*, Reg. Papers, 2012, vol. 59, no. 2, pp. 305-314.

- [26] H. Wang, L. Zhang, and Z. Yu, "A wideband inductorless LNA with local feedback and noise cancelling for low-power low-voltage applications," *IEEE Trans. Circuits Syst. I*, Reg. Papers, 2010, vol. 57, no. 8, pp. 1993-2005.

- [27] B. Razavi, "Low-noise amplifier," in RF Microelectronics, 2nd ed. Beijing, China: Publishing House of Electronics Industry, 2012, pp. 263-266.

- [28] T. H. Lee, "Noise," in The Design of CMOS Radio-Frequency Integrated Circuits, 2nd ed. Beijing, China: Publishing House of Electronics Industry, 2012, pp. 259-262.

- [29] B. Razavi, "Noise," in Design of Analog CMOS Integrated Circuits. Beijing, China: China Machine Press, 2013, pp. 212-213.ircuits, 2006, vol. 41, no. 11, pp. 2424-2439.

- [30] Yiming Yu, Huihua Liu, Yunqui Wu, Kai Kang, "A 54.4-90GhZ low-noise Amplifier in 65nm CMOS", IEEE Journal of Solid-State Circuits, 2017, vol. 52, no. 11.

- [31] Denizhan Karala, Mikko Varonen, Dristy Parveg, Ali Vahdati, Kari A, I, Halonen, "A 53-117 GhZ LNA in 28nm FDSOI CMOS", *IEEE Microwave and Wirelwss Componenets letters*, 2017, vol. 27, no. 2.

- [32] Yuan Chai, XiaoKang Niu, Long He, Lianming Li, Tie Jun Cui, "A 60 GhZ CMOS Broadband Receiver with Digital calibration 20-to-75 db gain and 5db noise figure", *IEEEE Transaction on Microwave Theory and Techniques*, 2017, vol. 65, no. 10.

- [33] David Fritsche, Gregor Tretter, Paul Starke, Carrado Carta, Frank Ellinger, "A low power SiGe BiCMOS 190GhZ receiver with 47 db conversion Gain and 11db Noise figure for ultrastage bandwidth applications", *IEEE Transaction on Microwave Theory and Techniques*, 2017, vol. 65, no. 10.

# **BIOGRAPHIES OF AUTHORS**

**Er. Rashmi Singh** is presently a M.E student from National Institute of Technical Teachers Training and Research, Chandigarh India. She has obtained her B. Tech from U. P. Technical university luck now, India in 2005. She is having seven years of teaching and research experience. Her areas of interest include VLSI Design and Advanced Digital Signal Processing. She has been credited with IEEE xplore papers, DOI: 10.1109/IOTA.2016.7562696 and DOI: 10.1109/ICEEOT.2016.7755385 Mail.id contecter.rashmi@gmail.com.

**Dr. Rajesh Mehra** is currently associated with Electronics and Communication Engineering Department of National Institute of Technical Teachers' Training & Research, Chandigarh, India since 1996. He has received his Doctor of Philosophy in Engineering and Technology from Panjab University, Chandigarh, India in 2015. Dr. Mehra received his Master of Engineering from Panjab University, Chandigarh, India in 2008 and Bachelor of Technology from NIT, Jalandhar, India in 1994. Dr. Mehra has 20 years of academic and industry experience. He has more than 325 papers to his credit which are published in refereed International Journals and Conferences. Dr. Mehra has guided 75 ME thesis. He is also guiding 02 independent PhD scholars. He has also authored one book on PLC & SCADA. Dr. Mehra is member of IEEE and ISTE.