#### American University in Cairo

## **AUC Knowledge Fountain**

Theses and Dissertations

6-1-2018

## Identifying worst case test vectors for FPGA exposed to total ionization dose using design for testability techniques

Mohamed Sami Abdelwahab

Follow this and additional works at: https://fount.aucegypt.edu/etds

#### **Recommended Citation**

#### **APA Citation**

Abdelwahab, M. (2018). *Identifying worst case test vectors for FPGA exposed to total ionization dose using design for testability techniques* [Master's thesis, the American University in Cairo]. AUC Knowledge Fountain.

https://fount.aucegypt.edu/etds/1349

#### MLA Citation

Abdelwahab, Mohamed Sami. *Identifying worst case test vectors for FPGA exposed to total ionization dose using design for testability techniques*. 2018. American University in Cairo, Master's thesis. *AUC Knowledge Fountain*.

https://fount.aucegypt.edu/etds/1349

This Thesis is brought to you for free and open access by AUC Knowledge Fountain. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of AUC Knowledge Fountain. For more information, please contact mark.muehlhaeusler@aucegypt.edu.

#### The American University in Cairo

#### School of Sciences and Engineering

# IDENTIFYING WORST CASE TEST VECTORS FOR FPGA EXPOSED TO TOTAL IONIZATION DOSE USING DESIGN FOR TESTABILITY TECHNIQUES

#### A Thesis Submitted to

**Electronics and Communications Engineering Department**

in partial fulfillment of the requirements for the degree of Master of Science

by Mohamed Sami Yusuf Abdelwahab

under the supervision of Prof. Ahmed Abou-Auf May/2018 To my father & mother

#### **ACKNOWLEDGMENTS**

I would like to express my sincere gratitude and appreciation to my advisor Prof. Ahmed Abou-Auf for his continuous support, guidance, and patience throughout my thesis and related research.

I would also like to thank Eng. Mostafa Mahmoud for his assistance throughout my research.

I would also like to acknowledge Prof. Yehea Ismail and Eng. Shady Agwa from Center for Nanoelectronics and Devices for their assistance in my research.

I would like to acknowledge my examiners Prof. Ihab Talkhan and Prof. Yehea Ismail for their comments on my thesis.

Finally, I would like to thank my program director Prof. Karim Seddik for his assistance throughout my thesis.

#### **ABSTRACT**

The American University in Cairo, Egypt

TID testing

Name: Mohamed Sami Yusuf Abdelwahab

Supervisor: Prof. Ahmed Abou-Auf

Electronic devices often operate in harsh environments which contain a variation of radiation sources. Radiation may cause different kinds of damage to proper operation of the devices. Their sources can be found in terrestrial environments, or in extra-terrestrial environments like in space, or in man-made radiation sources like nuclear reactors, biomedical devices and high energy particles physics experiments equipment. Depending on the operation environment of the device, the radiation resultant effect manifests in several forms like total ionizing dose effect (TID), or single event effects (SEEs) such as single event upset (SEU), single event gate rupture (SEGR), and single event latch up (SEL).

TID effect causes an increase in the delay and the leakage current of CMOS circuits which may damage the proper operation of the integrated circuit. To ensure proper operation of these devices under radiation, thorough testing must be made especially in critical applications like space and military applications. Although the standard which describes the procedure for testing electronic devices under radiation emphasizes the use of worst case test vectors (WCTVs), they are never used in radiation testing due to the difficulty of generating these vectors for circuits under test.

For decades, design for testability (DFT) has been the best choice for test engineers to test digital circuits in industry. It has become a very mature technology that can be relied on. DFT is usually used with automatic test patterns generation (ATPG) software to generate test vectors to test application specific integrated circuits (ASICs), especially with sequential circuits, against faults like stuck at faults and path delay faults. Surprisingly, however, radiation testing has not yet made use of this reliable technology.

In this thesis, a novel methodology is proposed to extend the usage of DFT to generate WCTVs for delay failure in Flash based field programmable gate arrays (FPGAs) exposed to total ionizing dose (TID). The methodology is validated using MicroSemi ProASIC3 FPGA and cobalt 60 facility.

#### TABLE OF CONTENTS

| 1.  | Summary                                     | 1  |

|-----|---------------------------------------------|----|

| 2.  | Radiation effects review                    | 3  |

| 2.  | 1 Radiation sources                         | 3  |

|     | 2.1.1 Terrestrial environment               |    |

|     | 2.1.2 Space                                 |    |

|     | 2.1.3 Man-made radiation                    |    |

| 2.  | 2 Radiation effects mechanisms              |    |

| 2.  | 3 Radiation resultant effect                |    |

|     | 2.3.1 Total Ionization Dose effects         |    |

|     | 2.3.2 Single-Event effects                  | 11 |

| 3.  | Total Ionizing Dose effect in CMOS circuits | 13 |

| 3.  | 1 TID effect in MOS transistor              | 13 |

|     | 3.1.1 Threshold voltage shifts              | 15 |

|     | 3.1.2 Carriers mobility degradation         |    |

|     | 3.1.3 Induced leakage current               |    |

| 3.  | 2 TID effect in floating gate MOS           |    |

|     | 3.2.1 Floating gate MOS                     |    |

|     | 3.2.2 Threshold voltage shift               |    |

| 2   | 3.2.3 Propagation delay degradation         |    |

|     | 3 TID testing                               |    |

| 4.  | Design for testability                      |    |

|     | 1 Ad-hoc Design for Testability             |    |

| 4.  | 2 Scan design                               |    |

|     | 4.2.1 Muxed D scan design                   |    |

|     | 4.2.2 Clocked scan design                   |    |

|     | 4.2.3 LSSD                                  |    |

| 4   | 4.2.4 Enhanced scan design                  |    |

|     | 3 Logic Built-in self-test (BIST)           |    |

| 4.  | 4 Path delay testing                        |    |

|     | 4.4.2 Path delay test methodologies         |    |

|     | •                                           |    |

| 5.  | WCTV generation for ASIC and FPGA           |    |

|     | 1 WCTV for ASICs                            |    |

| 5.  | 2 WCTV for FPGA                             | 66 |

| 6.  | Methodology                                 |    |

| 6.  | 1 Failure analysis                          | 68 |

| 6.  |                                             |    |

| 6.  | 3 WCTV generation for sequential circuits   | 74 |

| 7.  | Experimental results                        | 83 |

| 7.  |                                             |    |

| 7.  | •                                           |    |

| 8.  | Conclusion and future work                  | 90 |

| 8.  |                                             |    |

| 8.  |                                             |    |

|     |                                             |    |

| кет | erences                                     | 92 |

#### LIST OF FIGURES

| Figure 1: Flux of neutrons in the terrestrial environment as a function of altitude                                                                                     |              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Figure 2: Schematic illustration of three main sources of radiation in space                                                                                            |              |

| Figure 3: Coulomb interaction between charged particle and an atom                                                                                                      |              |

| Figure 4: Physical phenomena in general solid and dielectric induced by high energy charged Figure 5: Lattice displacement due to radiation effect                      |              |

| Figure 6: Band diagram of an n-type MOS biased at positive voltage                                                                                                      |              |

| Figure 7: Linear energy transfer for protons and electrons as a function of particle energy                                                                             |              |

| Figure 8: Illustration of the oxide charge traps on n and p channel MOSFETs                                                                                             |              |

| Figure 9: Illustration of the effect of the interface traps on n and p channel MOSFETs                                                                                  |              |

| Figure 10: Illustration of the decrease in the threshold voltage shift with the scaling down                                                                            |              |

| oxide                                                                                                                                                                   |              |

| Figure 11: Mobility of carriers normalized to the pre-irradiation values as a function of inte                                                                          |              |

| density for devices with high and low interface traps and oxide charge traps densities                                                                                  |              |

| Figure 12: Gate oxide leakage current versus gate voltage for a non-irradiated capacitor and an                                                                         | n irradiated |

| capacitor to 5.3 Mrad(Si)                                                                                                                                               |              |

| Figure 13: cross section of a) n-channel transistor with LOCOS isolation and b) n-channel trans                                                                         | isistor with |

| STI isolation                                                                                                                                                           |              |

| Figure 14: Normalized increased standby current in CMOS shift registers manufactured                                                                                    |              |

| process as a function of the TID dose in krad                                                                                                                           | 22           |

| Figure 15: a) Illustration of drain source leakage path in a n-channel MOSFET and b) its cause                                                                          |              |

| charges in the isolation oxide                                                                                                                                          |              |

| Figure 16: Impact of STI radiation damage on the current-voltage characteristics of n-channel fabricated in TSMC 180 nm CMOS process                                    |              |

| Figure 17: Leakage path between two adjacent n-channel transistors                                                                                                      |              |

| Figure 18: Leakage path between the source of n-channel MOSFET and the n-well of                                                                                        |              |

| MOSFET                                                                                                                                                                  |              |

| Figure 19: Example of how interdevice leakage can increase the standby current of an inve                                                                               | erter chain. |

| Path (a) represents the leakage path between two n-channel MOSFETs. Path (b) rep                                                                                        | resents the  |

| leakage path between the drain of n-channel MOSFET and the n+ well of p-channel MO                                                                                      |              |

| Figure 20: I-V curves for parasitic field-oxide and gate-oxide transistors showing the increase                                                                         |              |

| standby currents caused by the leakage in the field oxides                                                                                                              |              |

| Figure 21: a) Layout of the switch element for the flash-based FPGA. b) Schematic showing                                                                               |              |

| section X-X'                                                                                                                                                            |              |

| Figure 22: Schematic of the floating gate transistor in flash-based FPGA                                                                                                |              |

| Figure 23: Energy band diagram for the floating MOS transistor for the high threshold voltage case, showing the radiation mechanisms that affects the threshold voltage |              |

| Figure 24: Energy band diagram for the floating MOS transistor for the low threshold                                                                                    |              |

| "programmed" case, showing the radiation mechanims that affects the threhold voltage                                                                                    |              |

| Figure 25: TID effect on the high threshold voltage flash cell                                                                                                          | 31           |

| Figure 26: TID effect on the low threshold voltage flash cell                                                                                                           |              |

| Figure 27: Experiment threhold voltage versus total dose for both low threshold and high                                                                                |              |

| voltage flash cells and model prediction (dashed line)                                                                                                                  |              |

| Figure 28: Experimental propagation delay versus total dose for 1000 inverter string                                                                                    |              |

| Figure 29: Propagation delay experimental data compared to SPICE simulation prediction                                                                                  |              |

| unbiased case                                                                                                                                                           |              |

| Figure 30: Propagation delay experimental data compared to SPICE simulation predictions for                                                                             |              |

| case                                                                                                                                                                    | 34           |

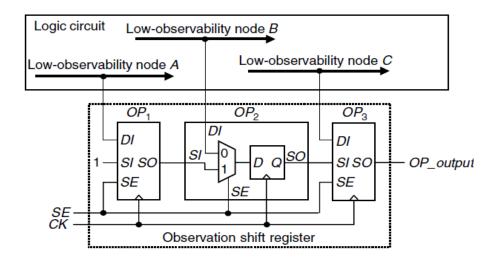

| Figure 31: Example of an observation point insertion                                                                                                                    | 38           |

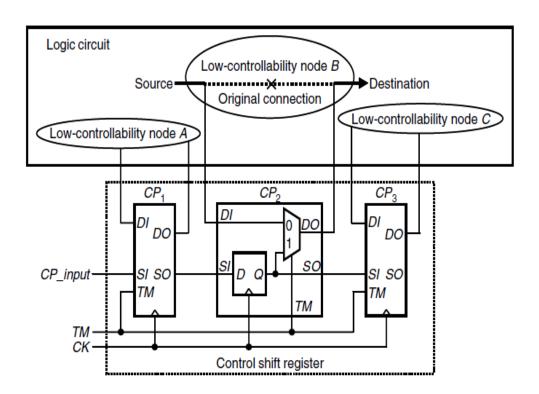

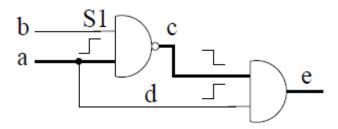

| Figure 32: Example of a control point insertion                                                                                                                         |              |

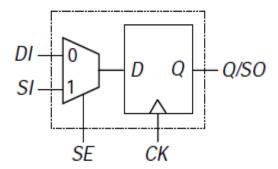

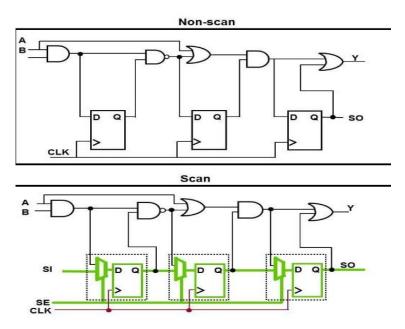

| Figure 33: Illustration of a muxed D scan cell                                                                                                                          |              |

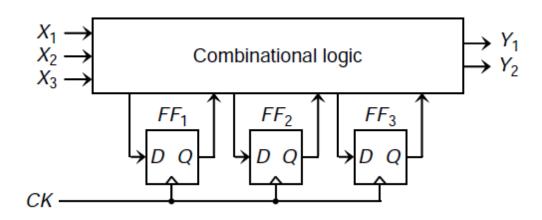

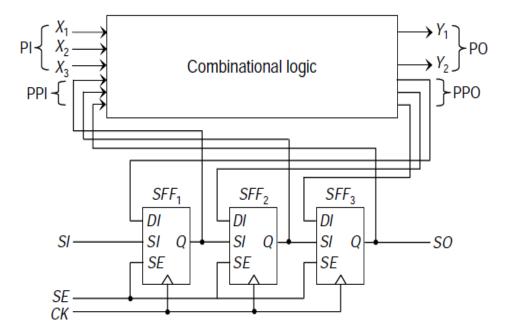

| Figure 34: An example of a sequential circuit                                                                                                                           | 41           |

| Figure 35: Corresponding muxed D full scan circuit of the sequential circuit in figure 34                                                                               |              |

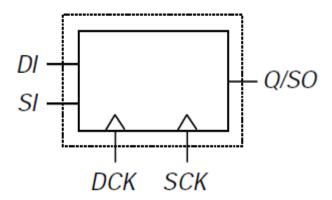

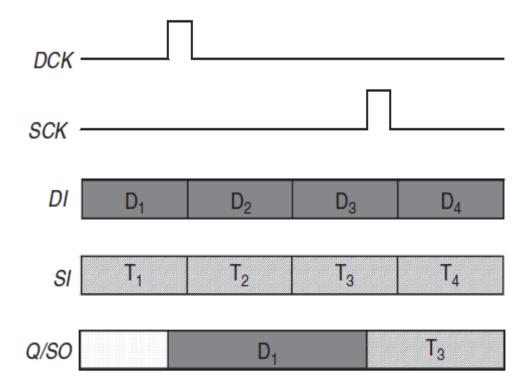

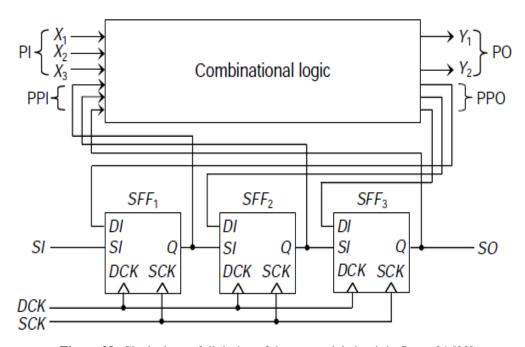

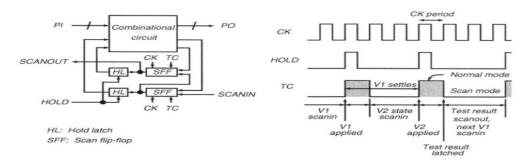

| Figure 36: Illustration of clocked scan cell                                                                                                                            |              |

| Figure 38: Clocked scan full design of the sequential circuit in figure 34                                                                                              |              |

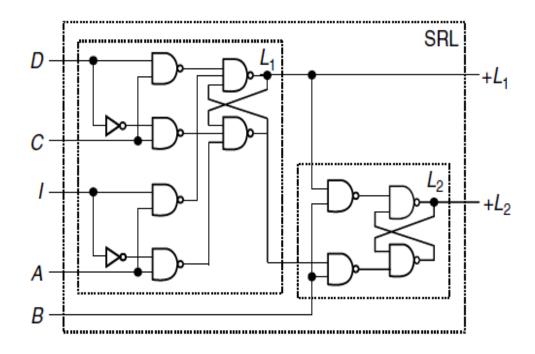

| Figure 39: Illustration of the polarity-hold shift register latch (SRL)                                                                                                 |              |

|                                                                                                                                                                         |              |

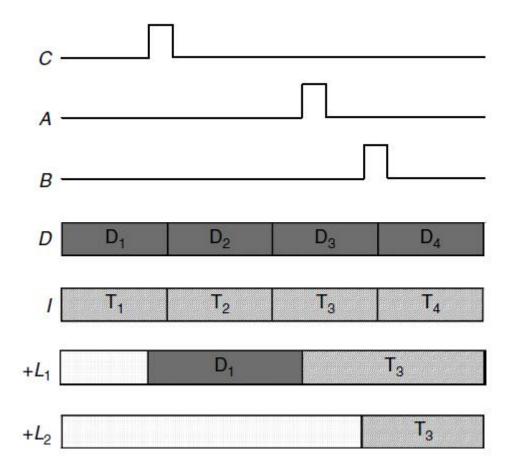

| Figure 40: Example of the waveform of the operation of the polarity-hold SRL scan cell               | 46      |

|------------------------------------------------------------------------------------------------------|---------|

| Figure 41: LSSD using single latch design for the sequential circuit in Figure 34                    | 47      |

| Figure 42: LSSD double latch design of the sequential circuit in Figure 34                           | 47      |

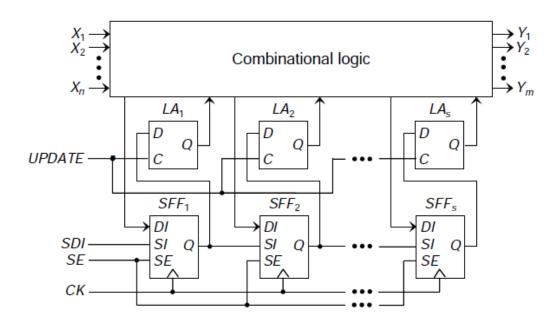

| Figure 43: An example of an enahnced scan design                                                     | 48      |

| Figure 44: Common logic BIST system                                                                  | 50      |

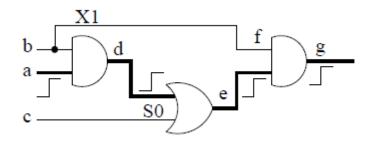

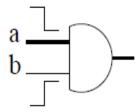

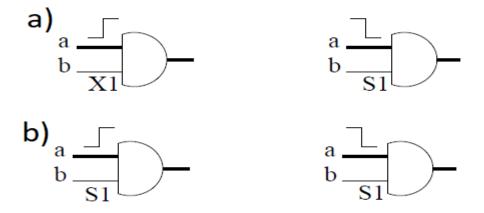

| Figure 45: Robust sensitization criterion for an AND gate                                            | 53      |

| Figure 46: An example of a robust testable path delay fault                                          | 53      |

| Figure 47: An example of non-robust sensitization of an AND gate                                     | 54      |

| Figure 48: An example of a non-robust testable path delay fault                                      | 54      |

| Figure 49: An example of functional sensitization of an AND gate                                     | 55      |

| Figure 50: An example of a functional sensitizable path delay fault                                  | 56      |

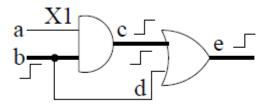

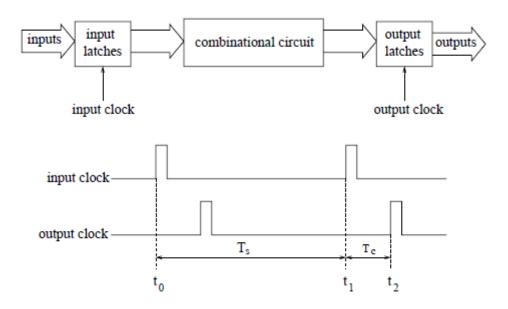

| Figure 51: Slow-clock combinational test methodology                                                 | 57      |

| Figure 52: Normal-scan sequential test methodology                                                   | 58      |

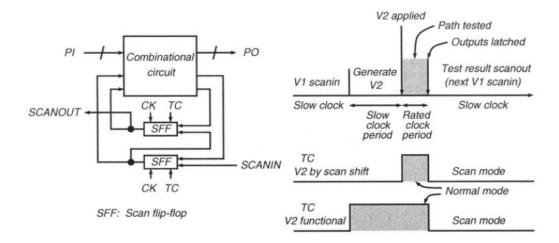

| Figure 53: Enhanced-scan test methodology                                                            | 59      |

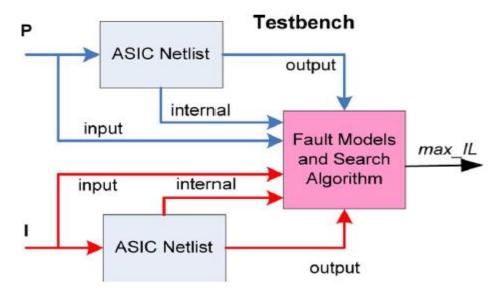

| Figure 54: Testbench setup to identify worst case test vectors for leakage current failure in ASICs. | 61      |

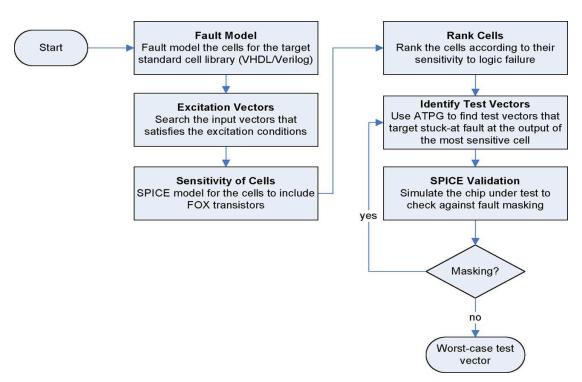

| Figure 55: Flow diagram to identify worst case test vector for ASICs                                 | 63      |

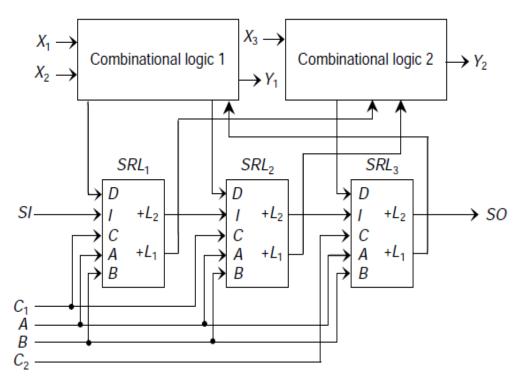

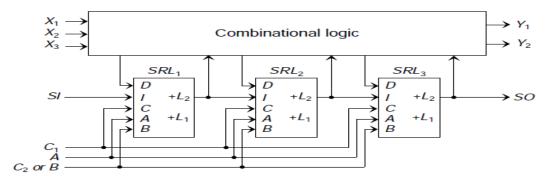

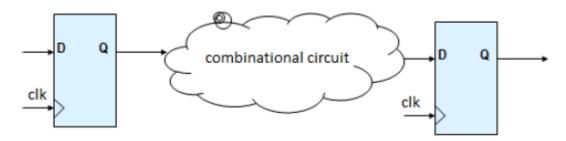

| Figure 56: Synchronous circuit's model                                                               |         |

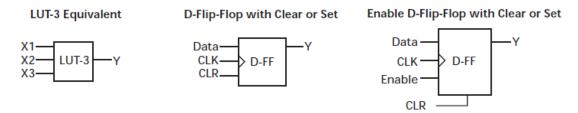

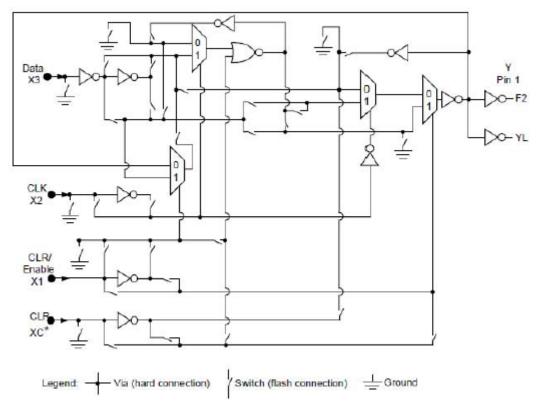

| Figure 57: Various configurations of VersaTile                                                       | 69      |

| Figure 58: Schematic diagram of a VersaTile                                                          |         |

| Figure 59: Transistor level of a FG switch                                                           |         |

| Figure 60: Conditions of an AND gate for: a) normal robust sensitization and b) modified r           | obust   |

| sensitization for WCTV generation                                                                    | 75      |

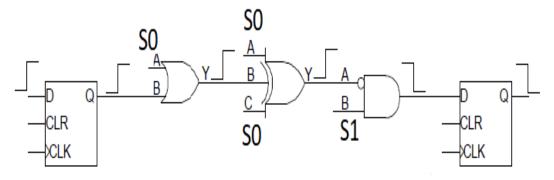

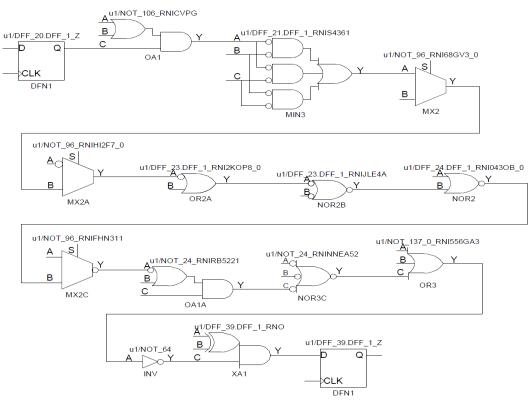

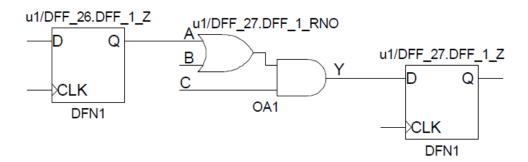

| Figure 61: An example of a sequential circuit and its corresponding muxed D scan design              | 77      |

| Figure 62: An example of a script to set the fault type to path delay fault                          | 77      |

| Figure 63: An example of a ".asci" file describing a path in a design                                | 78      |

| Figure 64: Part of an example of the generated file by FastScan describing the procedure and test pa | itterns |

| for testing a path delay fault                                                                       | 79      |

| Figure 65: An example of a Verilog code describing a scan cell                                       | 80      |

| Figure 66: Proposed technique to test a path by modifying off-inputs of cells along the path         | 81      |

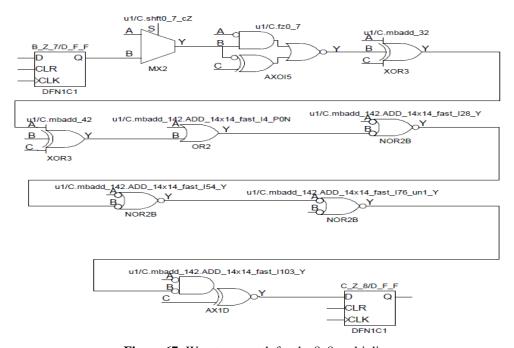

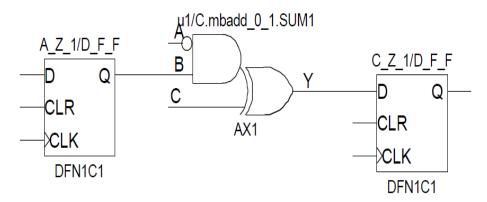

| Figure 67: Worst-case path for the 8x8 multiplier                                                    |         |

| Figure 68: Best-case path for the 8x8 multiplier                                                     | 85      |

| Figure 69: Worst-case path for S1423 circuit                                                         | 87      |

| Figure 70: Best-case path for S1423 circuit                                                          | 88      |

#### LIST OF TABLES

| Table I: Estimated number of FG switches along the paths from every in        | nput to | the |

|-------------------------------------------------------------------------------|---------|-----|

| output of a NOR3 cell                                                         |         | 73  |

| Table II: Estimated number of FG switches along the paths from every in       | nput to | the |

| output of a OR3 cell                                                          |         | 73  |

| Table III: Summary of the total dose experimental results of the 8x8 multiple | lier    | 86  |

| Table IV: Summary of the total dose experimental results of the S1423 circu   | uit     | 89  |

#### LIST OF ABBREVATIONS

ASIC Application Specific Integrated Circuits

ATE Automatic Test Equipment

ATPG Automatic Test Pattern Generation

BIST Built-In Self-Test

CMOS Complementary Metal Oxide Semiconductor

CUT Circuit Under Test

DFT Design For Testability

EDA Electronic Design Automation

FG Floating Gate

FPGA Field Programmable Gate Arrays

IC Integrated Circuit

LFSR Linear Feedback Shift Register

LSSD Level Sensitive Scan Design

MOS Metal Oxide Semiconductor

MOSFET Metal Oxide Semiconductor Filed Effect Transistor

ORA Output Response Analyzer

RILC Radiation Induced Leakage Current

RTL Register Transfer Level SEE Single Event Effect

SEGR Single Event Gate Rupture

SEL Single Event Latch up

SEU Single Event Upset

SRAM Static Random Access Memory

SRL Shift Register Latch

SSI Small Scale Integration

STA Static Timing Analysis

STI Shallow Trench Isolation

TID Total Ionizing Dose

TPG Test Pattern Generator

VLSI Very Large Scale Integration WCTV Worst-Case Test Vector

## Chapter 1

## Summary

Electronic devices may be exposed to several sources of ionizing radiation. The radiation sources can be found in terrestrial, extra-terrestrial and man-made radiation environments. In terrestrial environment, the sources can be neutrons found in the atmosphere, or alpha particles emitted from defects inside chip's materials. In extra-terrestrial environment, such as space the sources can be trapped particles around the Earth's atmosphere, particles originating from the sun, or high energy galactic cosmic rays' particles. The man-made radiation environments include nuclear reactors, biomedical devices, and high energy particles physics experiments equipment.

The radiation sources can cause several forms of damage to the correct operation of electronic devices under radiation. Depending on the radiation source and the environment which the device operates in, several radiation resultant effects can occur. The resultant effects can cause permanent or temporary failures in the device exposed to radiation. These effects can manifest in the form of single-event effects such as single-event upset, single-event gate rupture, and single-event latch-up, or total ionizing dose effect.

For the proper design of electronic devices exposed to radiation sources, a standard test procedure must be applied to ensure proper operation of devices under radiation. MIL-STD-883, method 1019 i.e. the standard test procedure to test electronic devices under radiation emphasizes the use of worst-case test vectors (WCTVs) in the testing procedure. However, worst-case test vectors are not used in radiation testing due to the difficulty in generating such vectors for complex circuits.

Several efforts have been made to identify worst-case test vectors for ASICs [1]-[6], however, there has been no effort to identify worst-case test vectors for FPGA except [7]. This effort only works on combinational circuits or sequential circuits characterized by the presence of flip-flops at the primary inputs and outputs of the circuit. However, these conditions are very rare as most designs are composed from

complex sequential circuits. The problem of testing sequential circuits is their lack of controllability and observability in the internal registers.

Design for testability (DFT) has been proposed since decades to overcome this problem by replacing the normal registers in a design by scan cells. This will result in an increase of the controllability and observability of the internal registers. However, DFT techniques were only used for ASIC, hence FPGA macro libraries do not include scan cells as DFT was not meant for FPGA designs.

In this thesis, a novel methodology is proposed to generate WCTV for flash-based FPGA exposed to total-ionizing-dose effect. Also, two techniques are proposed to test FPGA designs using the generated WCTV. The first technique depends on altering the normal FPGA design flow to include scan cells which are not found in the FPGA macro libraries. The second technique depends on the reprogram ability of FPGA to make the off-inputs along the target path to be test have non-controlling value to propagate a transition along the path without being masked.

The methodology is validated by implementing different design using Microsemi ProASIC3 A3P125-208PQFP flash-based FPGAs and total dose using Cobalt 60 radiation facility. The experimental results show the significance of using WCTV in total-dose testing of FPGA devices.

The rest of the thesis is organized as follows. Chapter two includes a review on different radiation sources and effects. Chapter three focuses in the TID effect on CMOS circuits and floating gate MOS transistor which are the switch elements in flash-based FPGA. Chapter four introduces a review on DFT basics and path delay testing. Chapter five discusses the previously developed efforts to generate WCTV of ASICs and FPGAs. Chapter six introduces the novel proposed methodology to identify WCTV for sequential circuits in flash-based FPGA using DFT techniques. Chapter seven contains the experimental results done to validate the proposed methodology. Finally, the thesis ends by chapter eight which concludes the work done in this thesis and gives some outlines of future work that may be done.

## **Chapter 2**

#### Radiation effects review

Electronic devices often operate in harsh environments which contain a variety of radiation sources. These radiation sources may cause different kinds of damage to the proper operation of the devices. Their sources can be found in terrestrial environments due to neutrons which are found in the atmosphere, or alpha particles which are emitted from defects found inside chips materials. They are also found in extra-terrestrial environments like space due to trapped particles around the Earth's atmosphere, particles which originated from the sun and high energy galactic cosmic rays' particles. Also, there are sources of radiation which originated from artificial manmade radiation found in nuclear reactors, biomedical devices and high energy particles physics experiments equipment.

The basic concept of ionizing radiation is that it transfers an amount of energy to the material exposed to its source. This deposited energy can cause a variation of effects in electronic devices such as faults in memory bits, increase in leakage current and increase in delay which can cause a total functional failure of the device.

### 2.1 Radiation sources

Since electronic devices are widely used in many environments including terrestrial, extra-terrestrial and man-made artificial radiation environments, an analysis of their characteristics is needed in order for these devices to operate properly in this environment.

### 2.1.1 Terrestrial environment

Neutrons found in Earth's atmosphere and alpha particles emitted from defects inside integrated circuit (IC) material are the most important sources of radiation in the terrestrial environment.

Atmospheric neutrons originate from the interaction between the galactic cosmic rays and the outer layers of Earth's atmosphere. Although they are not charged,

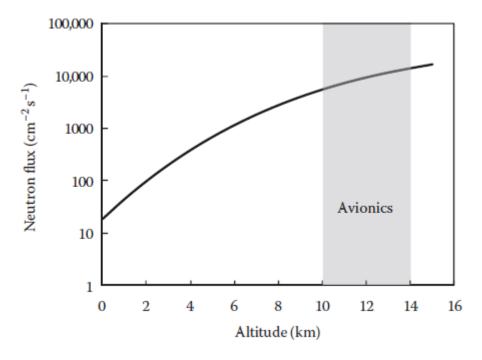

they can transmit energy to the target materials as they are able to trigger some nuclear reactions. As cosmic rays enter the Earth's atmosphere, they interact with oxygen and nitrogen and generate particles including protons, muons, neutrons and pions. The number of originated particles first increases and then decreases as the cosmic rays enter the atmosphere. This is because the atmosphere shielding dominates over the multiplication effect. As shown in Figure 1, the atmospheric neutron flux increases with altitude and reaches a peak value at approximately 15 Km. That is the altitude in which avionics operate, and this is why avionics electronic devices are most threatened by neutrons [8].

Figure 1: Flux of neutrons in the terrestrial environment as a function of altitude [8].

Another source of radiation are the alpha particles which are emitted as a result of the radioactive decay of defects inside chip material. Elements such as Uranium, Thorium, Platinum and Hafnium, which are used intentionally in the fabrication of Integrated Circuits (IC) or can be unwanted defects in the chip material, are the source of alpha particles. These elements or defects are the most responsible source for soft errors occurring in electronic devices. As the technology advances and the feature size of IC decreases, the soft errors induced by alpha particles are becoming more important than those induced by atmospheric neutrons. Also, particles like muons are gaining

more attention as they can cause threats to Complementary Metal Oxide Semiconductor (CMOS) circuits with the continuous decrease in the device dimensions [9].

## **2.1.2** Space

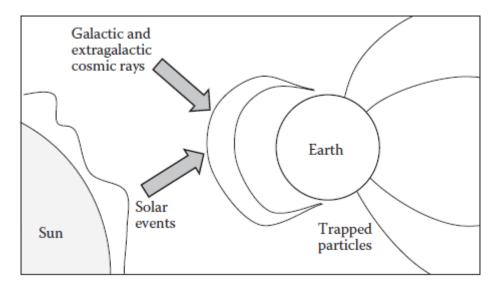

Space is one the harshest environments that electronic devices can operate in, and it is also one of the most complex environments as it contains all kinds of natural nuclei, from protons to Uranium. As shown in Figure 2, the three main sources of these particles are:

- 1. High energy galactic cosmic rays.

- 2. Solar particle events

- 3. Particles trapped in the magnetospheres of other planets

Figure 2: Schematic illustration of three main sources of radiation in space [8].

Galactic Cosmic Rays (GCRs) have a spectrum that extend to very high energies. As the name suggests, GCRs come from outside the solar system, although their source and acceleration method are not yet completely clear. They have probably been accelerated to the speed of light for millions of years and have travelled many times across the galaxy. For the most part they are made of protons, but they can include all kinds of elements. Their energy can reach a very high level, up to  $10^{11}$  GeV, which makes them very penetrating and impossible to shield with reasonable amounts of materials. Some of the GCRs interact and emit gamma rays, and that is how we can know that they have passed through the galaxy.

The sun is the second source of space ionizing particles. Their energies can reach values greater than 10 MeV, and their fluxes depend on the solar activity cycle. Solar activity is cyclic, which changes its value from high activity every 7 years and low activity every 4 years. Two events occur in the solar activity cycle. The first is solar particle events, which consist of solar flares and coronal mass ejections, and the second one is loss of mass in the sun, which causes some protons and electrons to escape the sun's gravity and acquire high energy. These protons and electrons have a magnetic field which in turn can interact with planetary magnetic fields.

Earth's magnetospheres are objects which originated from the interaction between the magnetic field of the solar wind and the Earth's own magnetic field, which has two components, an intrinsic one and an external one from the solar wind. The Earth's magnetic field forms a natural barrier against high energy solar wind flow. With the interaction between the solar flares and the solar wind with the Earth's magnetic field, some electrons are trapped inside the Earth's magnetosphere. Due to the interaction between the galactic cosmic rays and Earth's magnetic field, some protons are trapped in the magnetosphere of Earth. These particles which have energies up to 5 MeV and 800 MeV, once trapped inside Earth's magnetosphere move in spiral lines bouncing from one pole to another. Also, these particles form a radiation belt around the Earth called the Van Allen radiation belt. It consists of two belts; the outer belt which is made for the most part of electrons which have an energy up to 10 MeV, and an inner belt which is made of both electrons and protons and has protons with energy of about 100 MeV and electrons with energy in the range of hundreds of KeV.

Due to the complexity of the space environment, it is very difficult to assess the amount of ionizing radiation hitting a system in space, and it is also dependent on the cycle of solar activity. Furthermore, the exact amount of radiation that affects a specific electronic device depends on its location inside the spacecraft or satellite that is operating in due to the shielding effect of the materials used. In a context like space, one cannot just overdesign the electronic systems because the addition of this weight when applied to spacecraft or satellites has a high cost. Furthermore, these devices lack the power to support overdesigned electronic systems. This is why complex simulation

tools and models are used to predict the dose affecting the devices and design them within the appropriate margins[8]

#### 2.1.3 Man-made radiation

Another source of ionizing radiation can be artificially man-made, such as biomedical devices and high energy particles physics experiment equipment. In fact, doses that may exceed 100 Mrad(Si) are expected in the planned upgrade of the Large Hadron Collider (LHC) at CERN in Switzerland. To be able to compare this value, most missions in space by the National Aeronautics and Space Administration (NASA) expect a dose of less than 100 Krad(Si). That is why the design of devices in this equipment is characterized by the use of dedicated rad-hard libraries which have a layout that is made specially to avoid the problems of standard design and ultimately to withstand the high levels of radiation found in these environments.

Nuclear power plants are another source of man-made radiation. For example a fusion reactor like the one found in ITER neutral beam test facility, electronic devices are expected to be hit by large fluxes of neutrons of energies up to 14 MeV, the doses expected in the ITER environment can reach a value of 50 rad(Si) in one operating hour [10].

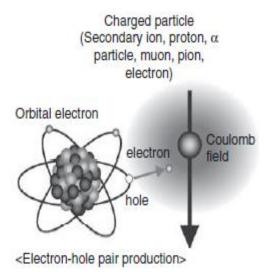

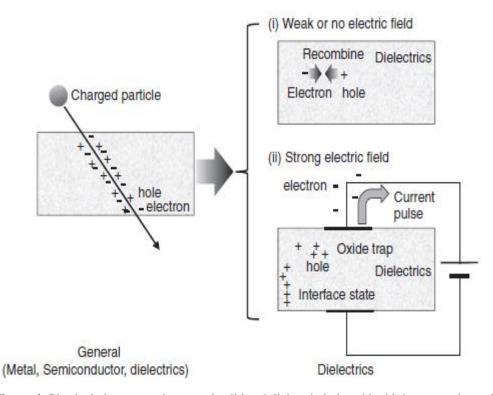

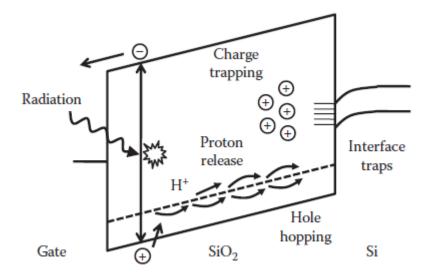

## 2.2 Radiation effects mechanisms

To analyze and design electronic devices to operate in radiation environments, one must study the radiation effect mechanism on the target material. Figure 3 shows one of these mechanisms, which occurs when a charged particle comes close to an atom. Due to the Coulomb force associated with the secondary particle, some electrons from the target atom get extracted, which in turn produces electron-hole pairs. In the case where the target material is metal, due to the high mobility of electrons and holes and because there is no band gap, the electrons and holes recombine immediately without causing any observable radiation effect. For dielectric materials like SiO<sub>2</sub>, depending on the applied electric field, an accumulation of holes in the dielectric can occur which may result in parasitic energy levels inside or on the surface of the oxide, resulting in the Total Ionization Dose (TID) effects as shown in Figure 4 [11].

Figure 3: Coulomb interaction between charged particle and an atom [11]

**Figure 4:** Physical phenomena in general solid and dielectric induced by high energy charged particle[11]

Another radiation effect mechanism is illustrated in Figure 5. The radiation effect starts with the displacement of lattice atoms in the target material due to the collision of particles including photons and neutrons. This displacement can cause dislocation loops and interstitials, which in turn results in some changes in the characteristics of the target material [11].

Figure 5: Lattice displacement due to radiation effect [11].

#### 2.3 Radiation resultant effect

The resultant effect of the radiation mechanisms mentioned before depends on the type of radiation source that the target material has been exposed to, and the environment in which the device operates.

## 2.3.1 Total Ionization Dose effects

TID is defined as the amount of energy transferred to the target material due to ionization radiation. The unit of measurement is rad, which is an amount of energy equal to 100 ergs transferred to one gram of the target material. Due to the dependency of the amount of energy transferred onto the target material, the radiation dose is usually followed by the target material. Another unit of measurement for TID is gray (Gy), one rad is equal to 100 Gy. The main effects of TID in electronic devices are positive charge trapping (holes) in the insulation layer, and the generation of interface states in the insulation layer [8]. TID effects can be observed in electronic devices operating in space and in man-made radiation environments such as the ones in nuclear power plants or high energy particles physics experiment labs.

One of the most susceptible materials to TID is the silicon oxide (SiO<sub>2</sub>) which is one of the most essential parts in the Metal Oxide Semiconductor (MOS) structure. The band diagram for an n-type MOS structure on a p-substrate and biased at positive voltage is illustrated in Figure 6.

Figure 6: Band diagram of an n-type MOS biased at positive voltage [8]

Due to the transferred energy from the radiation to the silicon dioxide, some electron-holes pairs are generated inside the SiO<sub>2</sub>. Some of these pairs are quickly recombined again in the oxide in a process called initial recombination. The amount of pairs that go through this process depends on the applied electric field, the transferred energy and the type of charged particle i.e. the source of radiation. The remaining pairs which survive the initial recombination process are called charge yield. The electrons in these pairs are attracted to the positive biased gate because of their high mobility, while the holes which are heavier and have lower mobility are attracted slowly compared to the speed of electrons to the silicon substrate. The holes remaining near their points of generation cause negative voltage shift in the characteristics of the MOS device, such as the threshold voltage [12].

As the holes which survived the initial recombination process are attracted to the silicon substrate, they move in a hopping transformation which depends on temperature and the applied electric field. This hopping process is called polaron hopping. The holes movement can take from about  $10^{-17}$  seconds at room temperature and much longer at lower temperatures.

The holes continue their hopping movement until they reach the Silicon/Silicon Oxide (SiO<sub>2</sub>) interface in case the gate is biased at a positive value. Some holes go to the Silicon substrate, and some others are trapped in defects sites whose density is higher near the Silicon/Silicon Oxide (SiO<sub>2</sub>) interface. These trapped holes can cause

permanent negative voltage shift in the characteristics of the MOS structure. This can cause a voltage shift in the threshold voltage and inversion of the channel which may cause leakage current to flow in the OFF state, leading to an increase in the static power of the integrated circuits. The number of trapped holes depends on the number of holes that survive the initial recombination process, and the quality of the oxide [8][12].

When holes are trapped near the Si/SiO<sub>2</sub> or during the hopping process, some hydrogen ions (protons) can be released. These hydrogen ions arrive at the interface which cause the generation of interface traps. These interface traps can exchange carriers with the channel, and their occupancy depends on the position of the Fermi level at the interface. The creation of these traps is much slower than the charge accumulation due to the trapped holes near the interface, but it also depends on the applied electric field. Interface traps can cause a positive shift in the threshold voltage of the NMOS transistor and a negative voltage shift in the threshold voltage of the PMOS transistor. It can also affect the mobility of the transistor which in turn decreases its current capability and causes timing degradation of the integrated circuits [8][12].

## 2.3.2 Single-Event effects

Single-Event effects (SEE) are caused by the passage of high-energy particles (heavy ion) through sensitive regions of an electronic device. They can be classified into two categories depending on their effects. Soft, in which the damage is not permanent e.g. soft errors in memory circuits, and hard in which the damage is irreversible e.g. the rupture of the dielectric in the gate. Some other SEE may or may not cause damage depending on the operation of the electronic device, such as in the case of a single-event latch-up, in which the time to cut the power supply after the occurrence of the event decides whether or not there is damage to the device [8].

Some of the main SEE are [8][13]:

#### 1- Single-event upset (SEU):

A soft SEE which is characterized by the flipping of the value of a single bit in a memory due to a single ionizing particle. It is also known as soft error. It is important to mention that the correct value of the memory bit can restored by rewriting the bit again i.e. the damage is not permanent.

#### 2- Single-event gate rupture (SEGR):

A hard SEE which is characterized by the rupture of the gate of a MOSFET, in which this rupture or damage is irreversible or permanent.

#### 3- Single-event latch-up (SEL):

A SEE that its damage depends on the operation of the circuit after being exposed to radiation. It is characterized by the activation of parasitic bipolar structures in CMOS circuits, which leads to a sudden increase in supply current. Depending on the time taken to cut the power source of the circuit, there may or may not be damage to the device.

## **Chapter 3**

## **Total Ionizing Dose effect in CMOS circuits**

Total Ionizing Dose effect "TID", which affects electronic devices operating in radiation environments like space and man-made radiation environment found in nuclear reactor, can cause several physical damages on the correct operation of CMOS circuits. These damages are due to the ionizing-radiation effect on the material used in the fabrication of CMOS circuits, specially the MOS structure. In this chapter, some of the damages caused by the "TID" effect on MOS transistors are illustrated, as well as TID testing techniques.

## 3.1 TID effect in MOS transistor

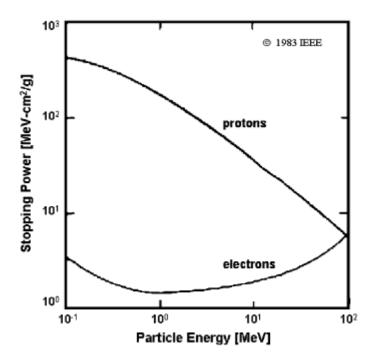

When MOS transistors are exposed to ionization radiation, electron-hole pairs are generated by the interaction of the high-energy particles with the atoms of the dielectric (SiO<sub>2</sub>). The density of the generated electron-hole pairs along the track of the high-energy particles exposed to the target material, is directly proportional to the energy transferred to the target material. Linear energy transfer (LET) or stopping power which expresses the loss of energy per unit length (dE/dx), is related to the energy that enters a discrete plane of the target material ( $\Delta E_E$ ) and the radiation energy that leaves material plane ( $\Delta E_L$ ) by the following equation [14]

$$\Delta E_L(\gamma) = \Delta E_E(\gamma) \exp\left(-\frac{\mu_{en}}{\rho}\rho\Delta x\right) \tag{1}$$

where  $\mu_{en}/\rho$  is the mass attenuation coefficient of the target material,  $\rho$  is the target material density, and  $\Delta x$  is the thickness of the target material. The LET for protons shows a monotonic decrease with increasing energy of protons, while in the case of electrons, the LET decreases as a function of particle energy for energies below 1 MeV, while it increases for higher energies as shown in Figure 7 [15].

Figure 7: Linear energy transfer for protons and electrons as a function of particle energy [15]

The electrons generated along the track of the charged particles are mostly swept rapidly toward the gate (positive charge side), due to their high mobility, while the holes with lower mobility are swept in a relatively slow motion compared to the electrons, to the oxide-Silicon (SiO<sub>2</sub>/Si) interface. A fraction of the holes moving toward SiO<sub>2</sub>/Si interface will get trapped, which results in the formation of positive oxide-trap charges [16].

In addition to the oxide traps, interface traps can also be generated at the SiO<sub>2</sub>/Si interface. These interface traps are a result of the interaction between the hydrogen ions that can drift to the interface. The interface traps generation process occurs in a longer time compared to the oxide charges generation process. They act as energy levels within the silicon band-gap. Interface traps can be negative or positive, depending on the location of the Fermi level at the interface, if the Fermi level at the interface is below the trap energy, it acts as a donor and the interface trap is positively charged, and if the Fermi level at the interface is above the trap energy, it acts as an acceptor and the interface trap is negatively charged. Positive interface traps causes negative threshold voltage shifts for p-channel transistors, while negative interface traps causes positive threshold voltage shifts for n-channel transistors [12].

Due to the oxide charges and interface traps, degradation of the MOS transistors characteristics occurs. Most common and critical degradations are threshold voltage shifts, mobility degradation and induced leakage current in CMOS devices.

## 3.1.1 Threshold voltage shifts

For MOS transistors, the total threshold voltage shifts due to TID is the sum of the threshold voltage shifts due to both oxide charge traps and interface traps which can be expressed by the following equation

$$\Delta V_{th} = \Delta V_{ot} + \Delta V_{it} \tag{2}$$

where  $\Delta V_{ot}$  is the threshold voltage shift due to oxide charge traps, and  $\Delta V_{it}$  is the threshold voltage shift due to interface traps. They can be determined by the following equation:

$$\Delta V_{ot,it} = \frac{-1}{C_{ox} t_{ox}} \int_0^{t_{ox}} \rho_{ot,it}(x) x dx \tag{3}$$

where  $\rho_{ot,it}(x)$  is the charge distribution of radiation-induced oxide charge traps or interface traps. For positive charges, the threshold voltage shift is negative, in contrast, for negative charges, the threshold voltage shift is positive [12].

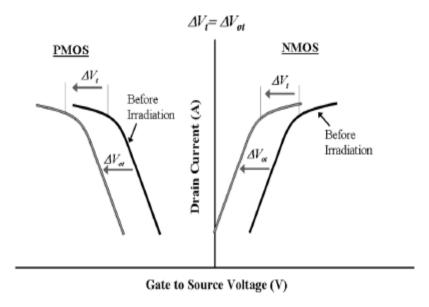

The effect of oxide charge traps is illustrated in Figure 8. For n-channel MOSFET, the oxide charge traps shift the  $V_{\rm gs}$  bias point by a negative value, which results in a reduction of the threshold voltage and in an increase of the drive current and the off-state current. For p-channel MOSFET, the oxide charge traps also shifts its bias point by a negative value, which results in an increase in the threshold voltage and a reduction of the drive and off-state currents [15].

Figure 8: Illustration of the oxide charge traps on n and p channel MOSFETs [15].

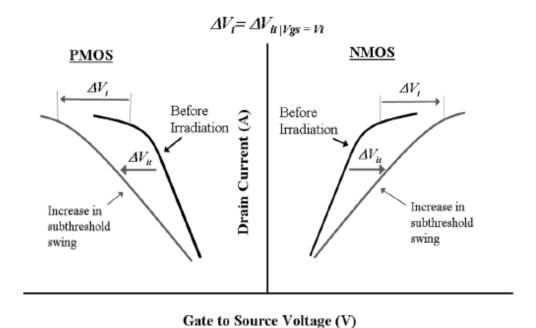

The effect of interface traps is illustrated in Figure 9. Interface traps cause an increase in the subthreshold swing of both n and p channel MOSFETs. Figure 9 also shows that the threshold voltage is also impacted by the interface traps, for n channel MOSFET interface traps cause a shift in the threshold voltage by a positive value, while for a p channel MOSFET interface traps cause a shift in the threshold voltage by a negative value [15].

Figure 9: Illustration of the effect of the interface traps on n and p channel MOSFETs [15]

The effect of oxide charge traps on the threshold voltage shift can have a little neutralization at high dose rate and short time, while the effect of interface traps won't have enough time to build up. So, for high dose and short time, the shift in the threshold voltage can be large and negative for both n and p channel MOSFETs. For n-channel MOSFET large negative shift in the threshold voltage can lead to an increase in the leakage static power of the integrated circuit, which can lead eventually to a failure in the integrated circuit [12].

At moderate dose rates, the effect of oxide charge traps can have some neutralization, and interface traps can occur. Therefore, the threshold voltage shift due to both oxide charge traps and interface traps can be large. For n-channel MOSFET the threshold voltage shift due to oxide charge is negative, while the threshold voltage shift due to interface traps is positive, thus, they compensate each other, and even if the individual threshold voltage shift is large, the net threshold voltage shift can be small, and the failure level of the integrated circuit due to radiation can be relatively high. For p-channel MOSFET, the threshold voltage shift due to oxide charge traps and interface traps has a negative value, therefore, they add to each other unlike the n-channel MOSFET case [12].

Radiation induced charge buildup decreases rapidly with the decrease in the oxide thickness, and the threshold voltage shift is directly proportional to the oxide thickness by the following equation [15]

$$\Delta V_{ot} \propto t_{ox}^2 \tag{4}$$

This relation indicates that with the advancement in CMOS technology and the scaling down of the oxide thickness, the threshold voltage shift is reduced. Instead, charge trapping in the shallow trench isolation (STI) dielectrics, which thickness is much larger than that of the gate oxide, has become more dangerous threat in modern CMOS technologies. As a result, interface traps and oxide charge traps in the thin gate oxides are not a concern, and the total dose effects are dominated by oxide charge traps in the field oxides even at low dose of radiation [12][15].

**Figure 10:** Illustration of the decrease in the threshold voltage shift with the scaling down of the gate oxide [17]

Other factors that can affect the value of the threshold voltage shift are the transistor dimensions (width "W" and length "L") and the device type. The narrower the width (W), the larger is the magnitude of the threshold voltage shift, this is valid for both n and p channel MOSFETs, and for width values larger than about 1  $\mu$ m, the threshold voltage value should not be critical. Also, the shorter the length (L) of the transistor, the larger is the magnitude of the threshold voltage shift. For larger values of width (W) and length (L) of the transistor, the value of the threshold voltage shift is small and there is no important dependency on the transistor size [18].

## 3.1.2 Carriers mobility degradation

Interface traps and oxide charge traps have other effects in addition to threshold voltage shift that can affect MOS transistors. They can affect the carries mobility in the

MOS device. These effects can cause degradation in the drive capabilities of the MOS transistor, degrading the timing parameters of an integrated circuit, which may cause timing failure in the electronic circuit operation.

During the oxide charge traps formation process, holes which survived the initial recombination process are attracted to the silicon substrate. The holes transport through the Silicon Oxide (SiO<sub>2</sub>) by a process called "Polaron hopping" which depends on the temperature and the applied electric field. Polaron causes an increase in the effective mass of the holes and a decrease in the holes mobility [12].

Like oxide charge traps, interface traps will also exchange charges with an adjacent silicon layer, but unlike oxide charge traps, interface traps are located exactly at the interface. Hence, there is no barrier to trapping and detrapping of carriers in the near surface silicon. That is why interface traps can have a significant effect on the mobility of the carries in the MOS device [15].

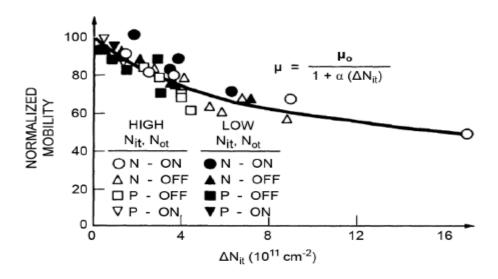

Both oxide charge traps and interface affects the mobility of carriers in a MOS transistor, but as illustrate in Figure 11, interface traps have a first order effect on the effective mobility of carriers of a MOS transistor, while oxide charge traps have a much weaker effect. This is due to the fact that scattering of carriers from interface traps is much more efficient than the more distant oxide charge traps in causing mobility degradation of carriers in a MOS transistor [17].

**Figure 11:** Mobility of carriers normalized to the pre-irradiation values as a function of interface traps density for devices with high and low interface traps and oxide charge traps densities [17]

## 3.1.3 Induced leakage current

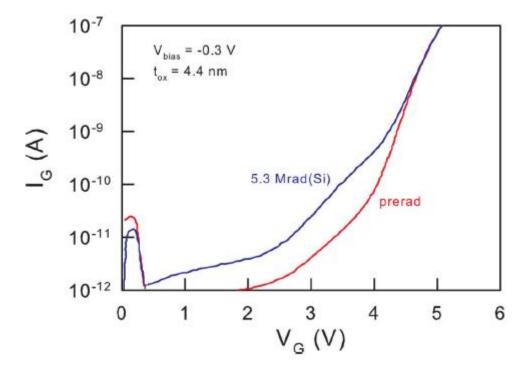

In commercial CMOS technologies, another phenomenon resulting from the damage of the TID effect on the transistors, is the radiation induced leakage current (RILC). Basically, this phenomenon depends on two damaging mechanisms that happens to CMOS circuits exposed to TID effect. The first mechanism is the threshold voltage due to the silicon dioxide charge traps, and the second mechanism is the built-up charges in the filed oxide p-substrate. This phenomena is illustrated in Figure 12, which is a plot of the gate leakage current, versus gate voltage, for a non-irradiated p-substrate capacitor and a capacitor irradiated to 5.3 Mrad(Si) with Co-60 gamma rays at a gate bias of 0.3 V[12].

**Figure 12:** Gate oxide leakage current versus gate voltage for a non-irradiated capacitor and an irradiated capacitor to 5.3 Mrad(Si) [12]

With the technology scaling down, the gate oxide thickness tends to ultra-thin oxides, which makes modern IC less susceptible to radiation damage, but the filed oxides of advanced commercial technologies are still much thicker than the gate oxides and the radiation response increases proportionally with the oxide thickness. Thus, the

effect of field oxides is the most dominant effect of TID and its effect is the main concern and radiation problem of these modern technologies [12].

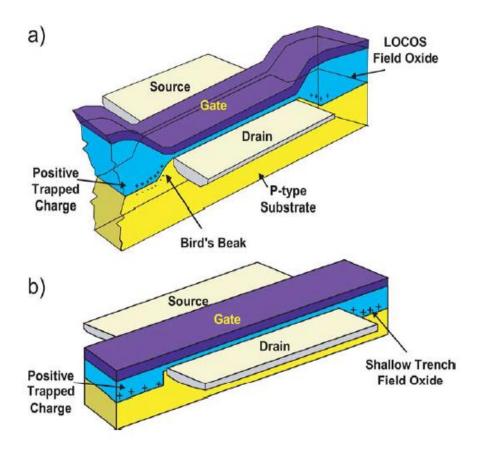

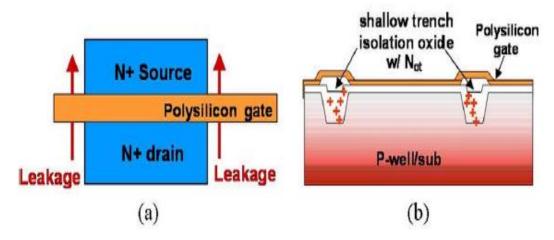

There are two common types of filed oxides used in the manufacturing of CMOS circuits, which are different in their formation method and their shape. The first type is local oxidation of silicon (LOCOS), which has been replaced by commercial IC manufacturers with the second type "shallow-trench isolation (STI)" for advanced submicron technologies. Figure 13(a) shows a cross section of an n-channel transistor with LOCOS isolation, showing the built-up charges in the area called "bird's beak region". Figure 13(b) shows a cross section of an n-channel transistor with STI isolation, showing the built-up charges [12].

Figure 13: cross section of a) n-channel transistor with LOCOS isolation and b) n-channel transistor with STI isolation [12]

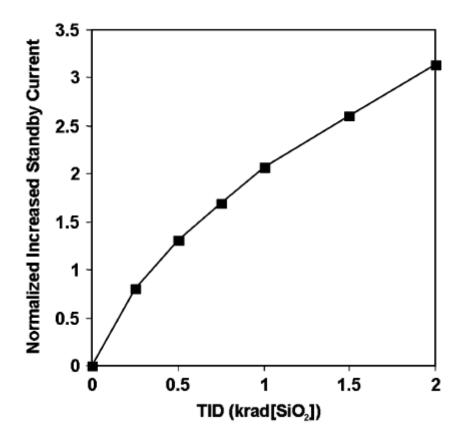

Radiation induced leakage current in shallow-trench isolation (STI) oxides is typically caused due to the exposure of high fluxes of ionizing radiation. Micro-doses of damage caused by a single ion strike have also been observed in submicron CMOS technologies. Induced leakage current in STI can cause an increase in the standby current in modern CMOS integrated circuits. The increase of the standby current of CMOS shift registers which are manufactured in a commercial 130 nm process is illustrated in Figure 14 [15].

**Figure 14:** Normalized increased standby current in CMOS shift registers manufactured in 130 nm process as a function of the TID dose in krad [15]

The induced leakage current in the STI oxide which causes an increased in the standby current in the integrated circuits is caused by the leakage paths created because of the built-up charges by the TID effect. These leakage paths include: drain to source leakage in a single n-channel MOSFET, drain to source leakage between two n-channel transistors, and source to well leakage between different devices. The mechanism for these leakage paths are the same, it is basically because of the positively charged oxide traps invert an adjacent p-type silicon layer, which enables the flow of current from isolation region to another [15].

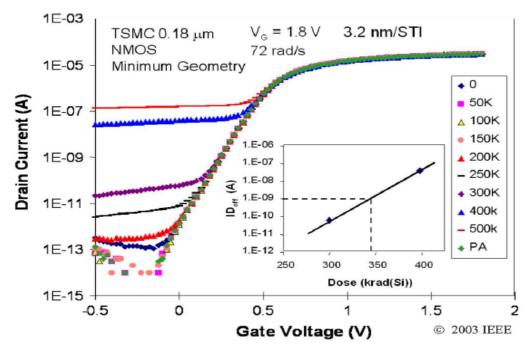

In the drain to source leakage path, built-up charges in the isolation dielectric at the interface along the sidewalls of the STI oxide are the cause of the creation of a leakage path, which becomes the most significant cause to the standby current in n-channel MOSFET as illustrated in Figure 15. The impact of the STI radiation damage on the standby current for a n-channel MOSFET manufactured by a 180 nm process by the Taiwan Semiconductor Manufacturing Company (TSMC) is shown in Figure 16. The data shows a significant increase in the drain source current above 200 krad(SiO<sub>2</sub>), and the drain source current reaches a value above 100 nA at 500 krad(SiO<sub>2</sub>) of total dose [15].

Figure 15: a) Illustration of drain source leakage path in a n-channel MOSFET and b) its cause; built-up charges in the isolation oxide [15]

**Figure 16:** Impact of STI radiation damage on the current-voltage characteristics of n-channel MOSFET fabricated in TSMC 180 nm CMOS process [15]

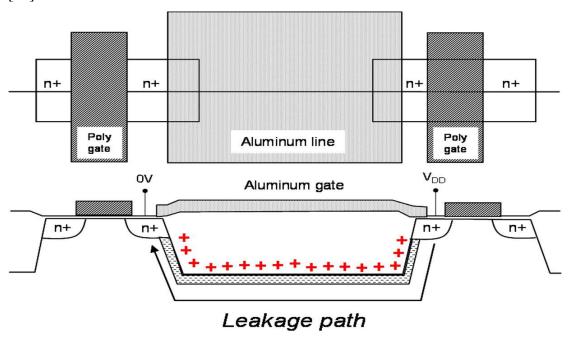

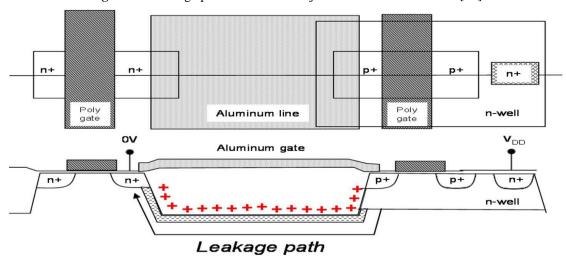

For the drain to source leakage between two n-channel transistors, and source to well leakage between different devices, the leakage paths are interdevice paths between two adjacent n-channel transistors or between the n+ drain/source of one n-channel transistor and the n-well of an adjacent p-channel transistor, unlike the case for the drain source leakage in which the leakage path is in the same device. The leakage path between two n-channel transistors is illustrated in Figure 17, and the leakage path between an n-channel transistor and a p-channel transistor is illustrated in Figure 18 [15].

Figure 17: Leakage path between two adjacent n-channel transistors [15]

**Figure 18:** Leakage path between the source of n-channel MOSFET and the n-well of p-channel MOSFET [15]

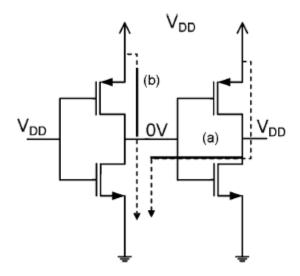

The leakage paths between two different devices can be observed in the example of two inverters chain shown in Figure 19. Path (a) drains current from V<sub>DD</sub> to ground because of the leakage path between the drains of two adjacent n-channel MOSFETs. This path is completed by the p-channel MOSFET in the second inverter and the n-channel MOSFET in the first inverter. Path (b) also drains current from V<sub>DD</sub> to ground because of the leakage path between the drain of the n-channel MOSFET of the first inverter to the n+ well of the p-channel MOSFET of the first inverter. This path is completed by the n-channel MOSFET of the first inverter [15].

**Figure 19:** Example of how interdevice leakage can increase the standby current of an inverter chain. Path (a) represents the leakage path between two n-channel MOSFETs. Path (b) represents the leakage path between the drain of n-channel MOSFET and the n+ well of p-channel MOSFET [15]

The effect of the leakage current caused by the field oxides can be modeled as a parasitic field-oxide transistor which is in parallel with the gate-oxide transistor. Consider the case at the edges of the gate transistor where the gate polysilicon overlaps with the field oxide, the parasitic parallel field-oxide transistor is formed by the gate polysilicon, a portion of the field-oxide and the source and the drain of the gate transistor. As illustrated in Figure 20, during the preirradiation, the threshold voltage of the parasitic field-oxide is relatively large due to the large thickness of the field oxide, but with the radiation and the charge built-up process in the field oxide, a negative threshold voltage shift occurs in the parasitic field-oxide transistor, which shifts its drain to source leakage current versus the gate to source voltage curve to the left. If the value of this threshold voltage shift is high enough, it can cause an increase in the

"OFF" state leakage current of the gate transistor, which can prevent the gate transistor from being completely turned off. This effect can add significantly to the standby current of an integrated circuit [12].

**Figure 20:** I-V curves for parasitic field-oxide and gate-oxide transistors showing the increase in the standby currents caused by the leakage in the field oxides [12]

# 3.2 TID effect in floating gate MOS

Field programmable gate arrays (FPGA) have become one of the most important devices in the electronic industry, with its high logic density, fast deployment, and reprogram ability, FPGA is the best choice for projects with limited budget and resources, and tight schedules. Flash based FPGA has advantages over other technologies like SRAM, of being re-programmable and nonvolatile. To analyze the radiation effect on flash-based FPGA, an analysis of the radiation effect in the switch

element, which consists of floating gate MOS, is required. In fact, the radiation response of the floating gate MOS is the dominant response in flash-based FPGA [19].

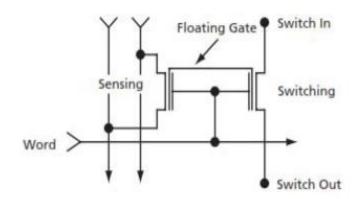

#### 3.2.1 Floating gate MOS

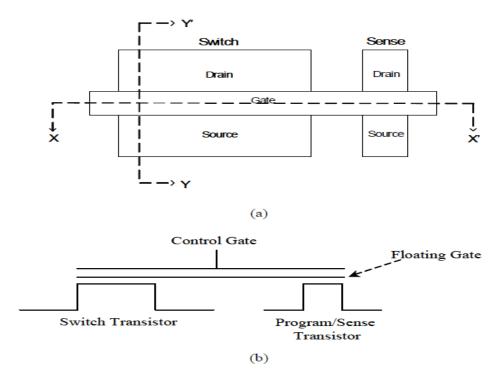

Flash-based FPGA switch element consists of two floating gate NMOS transistors as illustrated in Figure 21. The first transistor, which is called the switch transistor, is responsible for turning on or off the data path, the other transistor, which is called the program/sense transistor, is responsible for programming the floating gate voltage and sensing the current during threshold voltage measurement. The switch and the program/sense transistors have the same control gate and the same floating gate. Depending on the threshold voltage, the switch transistor can be turned on or off. This threshold voltage is determined by the charge stored in the floating gate by a mechanism called Fowler-Nordheim tunneling through the thin gate oxide during the process of programming and erasing the FPGA. To turn the switch transistor on, a low threshold voltage must be programmed in the floating gate, and to turn the switch transistor off, a high threshold voltage must be "erased" in the floating gate [19].

**Figure 21:** a) Layout of the switch element for the flash-based FPGA. b) Schematic showing the cross section X-X' [20]

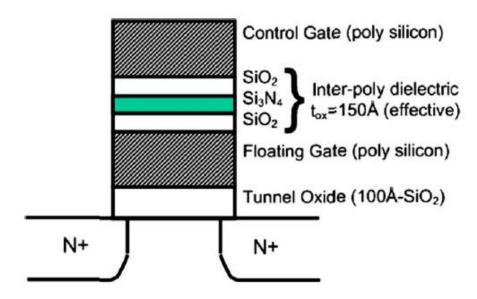

Figure 22 shows the structure of the floating gate transistor. It is an NMOS transistor with a tunnel oxide, which is composed of silicon dioxide, and between the floating gate, which is composed of poly silicon, and the control gate, which is also composed of poly silicon, there exists a layer of inter-poly oxide-nitride-oxide (ONO) composite dielectric [19].

Figure 22: Schematic of the floating gate transistor in flash-based FPGA [20]

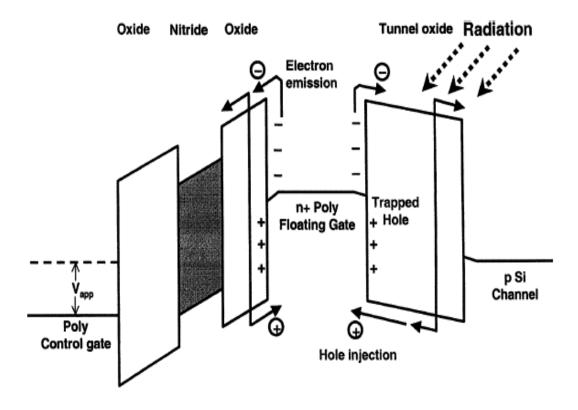

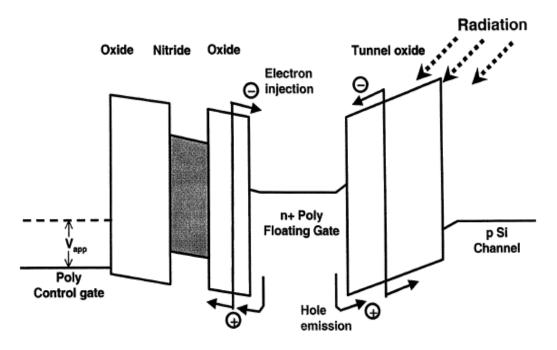

The energy band diagrams for the floating fate MOS for the high and low voltage threshold cases are illustrated in Figure 23 and 24, respectively. For the high threshold voltage or the "erased" state case, the threshold voltage of the transistor is affected by three mechanisms which are induced by the radiation: holes which are injected into the floating gate, trapped holes in the oxides, and emission of electrons over the poly-silicon/oxide barriers. When radiation hits the floating gate MOS, some electron-hole pairs are generated, which cause, depending on the applied electric field, injection and trapping of holes in the floating gate and the oxides, by increasing the electric field the number of tapped and injected holes increases. These trapped and injected holes result in a decrease in the threshold voltage. When the energy of photons caused by the radiation exceeds the potential barrier, electron emission occurs, which also cause a reduction in the threshold voltage [19].

**Figure 23:** Energy band diagram for the floating MOS transistor for the high threshold voltage or "erased" case, showing the radiation mechanisms that affects the threshold voltage [19]

**Figure 24:** Energy band diagram for the floating MOS transistor for the low threshold voltage or "programmed" case, showing the radiation mechanims that affects the threhold voltage [19]

The relation between the threshold voltage of the floating gate MOS transistor and the electronic charge stored on the floating gate can be determined by the following equation:

$$V_{th} = V_{si} + \frac{Q_{fg}d_{ono}}{\epsilon_{ox}} \tag{5}$$

where  $V_{si}$  is the threshold voltage determined by processing and it is a function of many variables including the dielectric thickness;  $Q_{fg}$  is the net electronic charge per unit area stored on the floating gate;  $d_{ono}$  is the effective oxide-nitride-oxide (ONO) thickness;  $\epsilon_{ox}$  is the oxide permittivity [19].

## 3.2.2 Threshold voltage shift

The threshold voltage shift in the floating gate MOS transistor is mainly due to three radiation induced mechanisms: injection of holes into the floating gate, trapped holes into the oxide, and electrons emission over the poly-silicon/oxide barriers. The holes injected and trapped into the floating gate and the oxide are due to the generated electron-hole pairs generated from the radiation, and the electron emission occurs if the photons induced by the radiation have more energy than the potential barrier. These three phenomena cause a reduction in the threshold voltage shift of the floating gate MOS transistor. The dependency of the threshold voltage on the radiation can be determined by the following relation:

$$V_{th}(\gamma) = C_0 + BV_{bias} + [C_1 - BV_{bias}] \exp(-A\gamma)$$

(6)

where  $\gamma$  is the total ionizing dose,  $V_{bias}$  is the control gate bias, and  $C_0$ ,  $C_1$ , B and A are physical constants [20].

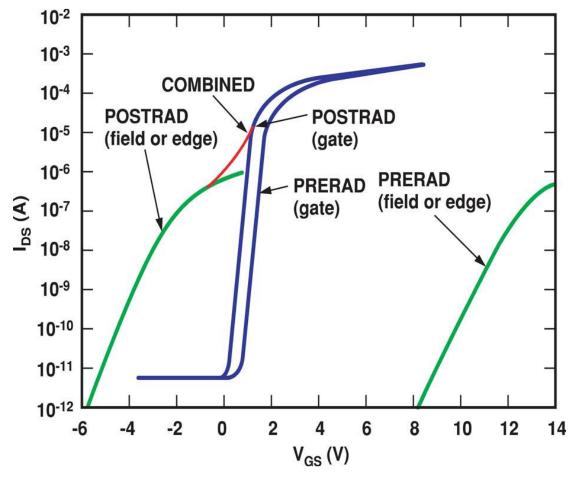

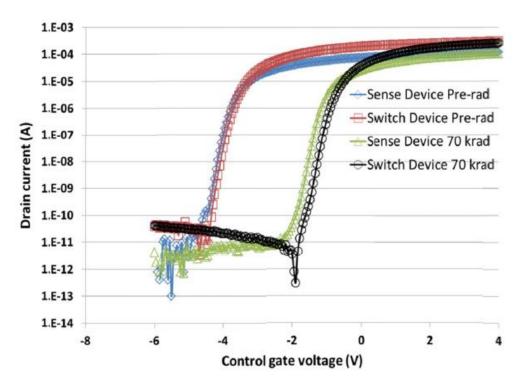

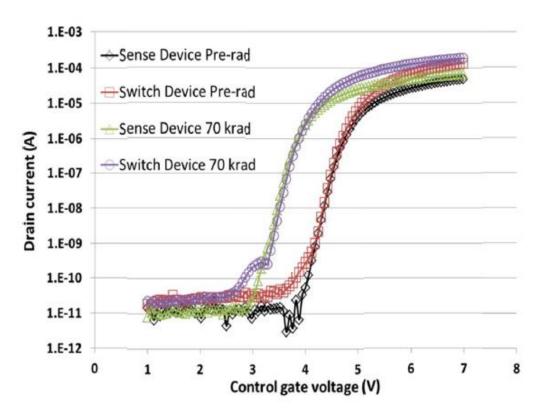

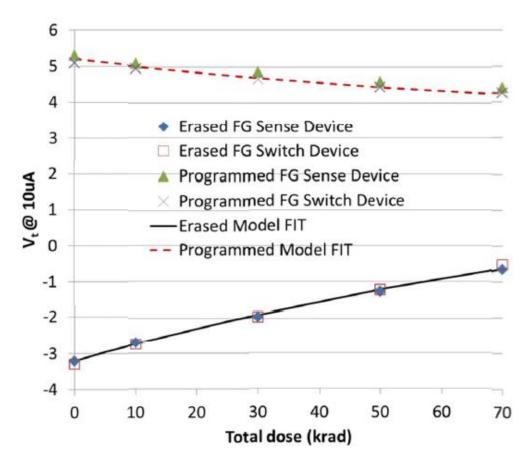

The  $I_d$  versus  $V_g$  curves for the high threshold or "erased" state flash cell before and after irradiation is illustrated in Figure 25, and Figure 26 shows the curves for the low threshold voltage or "programmed" state flash cell. Figure 27 shows the threshold voltage of both "erased" and "programmed" state flash cell, showing experimental data fitting to the model determined by equation (6) [20].

Figure 25: TID effect on the high threshold voltage flash cell [20]

Figure 26: TID effect on the low threshold voltage flash cell [20]

**Figure 27:** Experiment threhold voltage versus total dose for both low threshold and high threshold voltage flash cells and model prediction (dashed line) [20]

#### 3.2.3 Propagation delay degradation

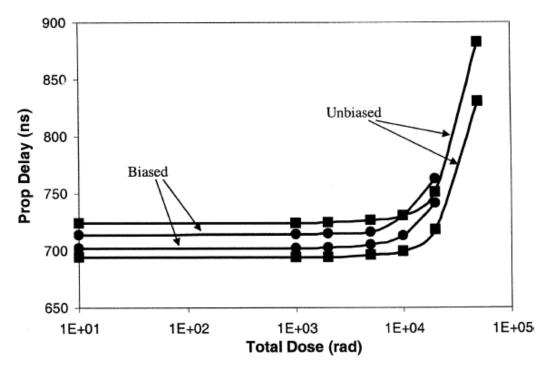

The threshold voltage shift in the floating gate MOS transistor of flash-based FPGA, affects the circuit parameters, one of the most important aspects of the effects of the threshold-voltage shift, is the degradation in the propagation delay. Propagation delay versus total dose experiment was conducted on a 1000-stage inverter string on a second-generation flash-based FPGA, named ProASICPLUS APA family. The experimental data for the propagation delay for both biased and unbiased cases is illustrated in Figure 28. As shown in Figure 28, the propagation delay degradation seems to have a total-dose threshold, this threshold has a higher value for the unbiased case than the biased radiation case [19].

Figure 28: Experimental propagation delay versus total dose for 1000 inverter string [19]

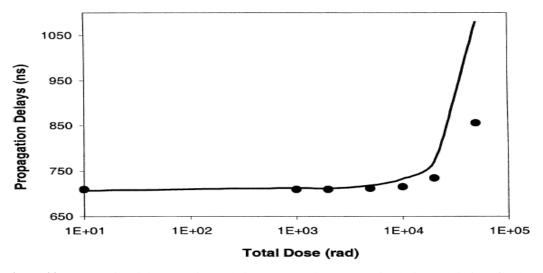

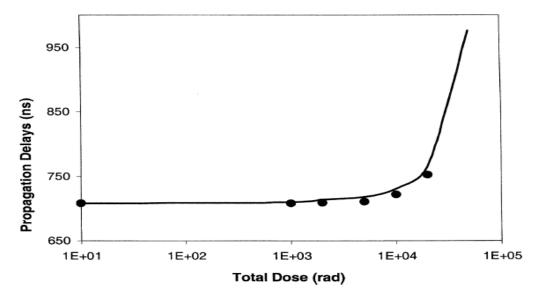

The comparison between the SPICE simulation prediction and the actual experimental data of the propagation delay for unbiased and biased radiation conditions are shown in Figure 29 and 30, respectively. As shown in the figures, the experimental data fits the simulation prediction for the biased radiation condition, but the experimental data has less degradation than the simulation prediction for the unbiased radiation condition [19].

**Figure 29:** Propagation delay experimental data compared to SPICE simulation predictions for the unbiased case [19]

**Figure 30:** Propagation delay experimental data compared to SPICE simulation predictions for the biased case [19]

Also, one of the factors that affects the propagation delay degradation, is the placement and routing of the VersaTiles in the FPGA fabric. The study in [21] shows that for accumulated total ionizing dose over 20 krad(Si), the placement and routing of VersaTiles in the critical path, seems to play a significant role in determining the percentage of the propagation delay degradation.

#### 3.3 TID testing

Understanding the nature of testing equipment and environment is crucial to successfully simulate the real radiation effect, that is why the determination of the nature and specifications of radiation sources is an important issue. Also, the testing techniques should be standardized by testing procedure to ensure the reliability of the applied test. For total ionizing dose (TID) effect testing, the MIL-STD-883, method 1019 is the standard test that should be followed in TID testing, also Gamma sources (especially cobalt-60 Co<sup>60</sup>) are commonly used in TID testing.

The MIL-STD-883, method 1019, used in TID testing, emphasizes to use test vectors which should cause the worst radiation effect in the tested devices (worst case test vectors "WCTV"). However, it is very difficult to generate these worst-case test vectors due to the complexity of the designs. Actually, most TID testing don't use WCTVs due to the difficulty of generating these vectors [7].

#### **Chapter 4**

## **Design for testability**

With the tremendous advances in the manufacturing technology of electronic devices, integrated circuits can now have billions of transistors that operate at very high ranges of frequency that can reach the gigahertz range. These advances pose more difficulties for chips testing for several reasons. The increased clock frequency requires automatic test equipment (ATE) that can operate in the same range of circuit under test (CUT). This is because stuck-at faults tests, which are the most common model used in digital circuits, have more effectiveness when they are applied at the circuit's rated clock speed. Those ATE that can operate at these high ranges of frequency, can have a very high cost, which make the testing of such devices very expensive. Also, the increased amount of input and output ports in integrated circuits, especially microprocessors which represents the leading edge in the VLSI technology trend, increase the cost of ATE required to test such devices, and it can also cause a high increase in the testing execution time. Another factor that affects the complexity of chip testing is the increased transistor density: the higher the transistor count, the higher the complexity of testing. This is due to the increase in the internal modules inside the same chip. These internal modules become more difficult to access which in turn makes it more difficult to generate test patterns [22][23].

In the early stages of the history of manufacturing integrated circuits, the design and test phases were regarded as two separate functions, which were done by two separate groups of engineers. During the design phase, the design engineer's job was to ensure that the required functionality is implemented based on the design specifications, without any concerns about how this device will be tested after the manufacturing. While, during the test phase, the test engineer's job was to find a way to test the manufactured device in an effective way within a reasonable time. This approach worked well in the small scale integrated circuits (SSI) where the integrated circuits consisted of combinational circuits or simple finite state machines. But, with the advance in technology and the movement toward the very large scale integrated circuits

(VLSI) era, this approach could not keep up with the increased circuit complexity. Another approach was introduced in the early 1980s to test VLSI devices, which relied on fault simulation to measure the fault coverage of the supplied functional patterns. Functional patterns were developed to test design with long sequential depth, by stimulating all internal states and detecting all possible manufacturing defects. But, this approach failed to increase the fault coverage beyond 80% and the manufactured devices suffered from low quality. That is why it became clear that more attention should be paid to design devices with high fault coverage, as many devices were good from the functionality point of view, but failed in performance point of view due to the high-test cost or low quality. This has led to the introduction of the Design For Testability (DFT) engineering in the industry [24].

The first problem that DFT tried to solve was to find simpler method to stimulate and access all internal states of sequential designs and to increase the fault coverage. Many methods of testability measure and ad hoc testability enhancement were introduced for this purpose. They were mainly used to increase the circuit's controllability and observability. Controllability is defined as the difficulty in setting a certain signal to a certain value. Observability is defined as the difficulty in observing the state of a certain signal. However, these methods failed to reach high fault coverage that exceeds 90% for large designs. This was due to the fact that generating test patterns for sequential circuits is much harder than the case of combinational circuits, even with the aid of these testing methods. The problem in generating test patterns for sequential circuits is due to the existence of many internal states in the design which are difficult to set or observe from external pins. This led to the adoption of structured DFT techniques to control and observe these internal states by providing direct external access to memory elements. These reconfigured memory elements are called "scan cells". By introducing them in the design, the problem of generating test patterns for sequential circuits becomes a problem of generating test patterns for combinational circuits. Many innovative algorithms were already developed to address this problem [24].

Design with scan cells became the most popular structured DFT technique. This design called "scan design" is implemented by replacing all or selected memory

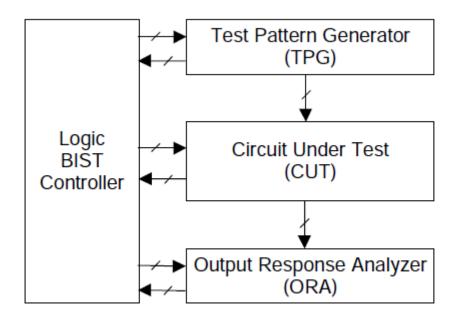

elements with scan cells, each having additional input called "scan input" and one additional output called "scan output". By connecting the scan output of one cell to the scan input of the next cell, a "scan chain" is created. Many scan designs and scan architectures have been proposed. A design where all the memory elements are transformed into scan cells is called "full-scan design", where a design with almost all memory elements are transformed into scan cells is called "almost full-scan design". A design where some memory elements are selected to be transformed into scan cells is called "partial-scan design". Although, scan designs improved quality, diagnosability, and testability of designs, it is becoming inefficient to test deep submicron on nanometer VLSI designs. because of the increased cost of traditional test schemes using automatic test patterns generation (ATPG) software, and it is becoming hard to maintain high fault coverage for these nanometer designs from chip level to the board and system level. This led to a new approach that combines the scan design with the logic built in self-test (BIST). In this architecture, the circuits that generate test patterns to test the CUT and to analyze the output responses are all embedded in the chip or on the same board where the chip resides. Logic BIST is crucial safety critical and mission critical applications which can be found in defense/aerospace, automotive, and banking industries [22][24].

## 4.1 Ad-hoc Design for Testability

Initially, numerous ad hoc techniques were proposed to enhance the testability of designs. These techniques involved making local adjustments to designs to improve their testability. While these techniques resulted in some improvements in the testability of designs, their main drawback was that they were local and not systematic. This means that they cannot be generalized for any design and they have to be repeated in a different manner for every design, which will produce unpredictable results [24].

Ad hoc techniques depend on good design practices learned from experience, some of which are [23]:

1- Avoid asynchronous logic feedback:

Feedback in the combinational circuit can cause oscillation for some inputs,

which makes the generation of test patterns by automatic programs difficult

for these circuits. This is because test generation algorithms are only known to work with acyclic combinational circuits.

#### 2- Initializable flip flops:

The initialization of flip flops can be easily done by adding a clear or reset input pin in the design.

#### 3- Avoid large number of fan-in: