#### American University in Cairo

### **AUC Knowledge Fountain**

Theses and Dissertations

2-1-2015

# Evaluation and implementation of a 5-level hybrid DC-DC converter

Farid Khaled El-Sehrawy

Follow this and additional works at: https://fount.aucegypt.edu/etds

#### **Recommended Citation**

#### **APA Citation**

El-Sehrawy, F. (2015). *Evaluation and implementation of a 5-level hybrid DC-DC converter* [Master's thesis, the American University in Cairo]. AUC Knowledge Fountain.

https://fount.aucegypt.edu/etds/187

#### **MLA Citation**

El-Sehrawy, Farid Khaled. *Evaluation and implementation of a 5-level hybrid DC-DC converter.* 2015. American University in Cairo, Master's thesis. *AUC Knowledge Fountain.*

https://fount.aucegypt.edu/etds/187

This Thesis is brought to you for free and open access by AUC Knowledge Fountain. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of AUC Knowledge Fountain. For more information, please contact mark.muehlhaeusler@aucegypt.edu.

Evaluation and Implementation of a 5-Level Hybrid DC-DC Converter

### THE AMERICAN UNIVERSITY IN CAIRO

#### SCHOOL OF SCEINCE AND ENGINEERING

# EVALUATION AND IMPELEMENTATION OF A 5-LEVEL HYBRID DC-DC CONVERTER

A thesis submitted in partial fulfillment of the requirements for the degree of the Master of Science

in

Electronics and Communications Engineering ECNG Department, School of Sciences and Engineering

*By*:

Farid El-Sehrawy

Under the supervision of:

Prof. Yehea Ismail

December 2015

### **ACKNOWLEDGEMENTS**

First, I would like to express my sincere gratitude to my thesis advisor, Prof. Yehea Ismail, for his continuous support in my studies and research, for his patience, motivation, and immense knowledge. His guidance helped me during my research and thesis writing.

My sincere thanks also go to Prof. Ali Darwish, Prof. Hassanein Amer, and Prof. Mohab Anis, for pushing me to my limits and always challenging me to become better. I could not have done it without their guidance throughout my undergraduate and graduate paths.

Special thanks to my colleague Eng. Abdallah Amgad, for helping and being patient with me throughout my research; I cannot thank you enough. I want to deeply thank my colleagues Eng. Seif Ghoneim, Eng. Rana Maraashly, Eng. Taher Kotb, and Eng. Mohamed Mazloum for their motivation and assistance.

I want to sincerely thank Mrs. Gehan Kamel, Mrs. Lidya Magdy, and Ms. Nehal Hussein, for their immense help in facilitating the logistics of my academic process. I also want to thank Engr. Roshdy and Engr. Ehab for their help during my experimental work and for their patience.

Finally, I would like to immensely thank my family for their immeasurable support and infinite encouragement during my entire academic career. I would like to thank my parents in particular, for always pushing me to improve, and guiding me throughout my life. I want to thank my brother and sister for being there for me whenever I needed them. I want to thank my wife, for always believing in me.

#### The American University in Cairo

### Abstract

#### School of Sciences and Engineering

#### Electronics and Communications Engineering Department

#### Master of Science

### Evaluation and Implementation of a 5-Level Hybrid DC-DC Converter

#### by Farid El-Sehrawy

In this work, a hybrid voltage regulator topology is analyzed, implemented, and evaluated. The common topologies of DC-DC converters have proven to be lacking in some aspects, such as integrability for buck converters, or maximum efficiency for switched-capacitor regulators. The hybrid topology tackles these shortcomings by combining the advantages of switched-capacitor and inductor-based voltage regulators.

A 5-level buck converter is evaluated, implemented, and compared to other converter implementations using the same components. The 5-Level Buck converter can achieve 5 different levels, allowing it to cover 4 operation regions, each between 2 levels. Accordingly, it covers a wide range of output voltages. By reducing the voltage difference at the inductor input, the 5-level buck converter can use smaller inductor compared to both 3-level and conventional buck converters which makes it cheaper, smaller in size, and much more efficient. Simulations show proper functionality of the 5-Level topology, while putting restrictions on the inductor size, efficiency, and component footprint (or total converter area).

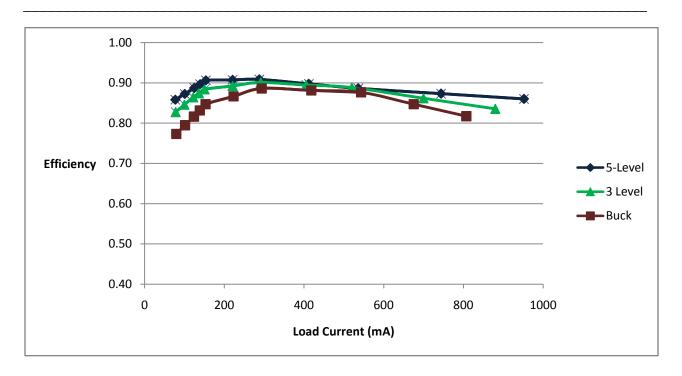

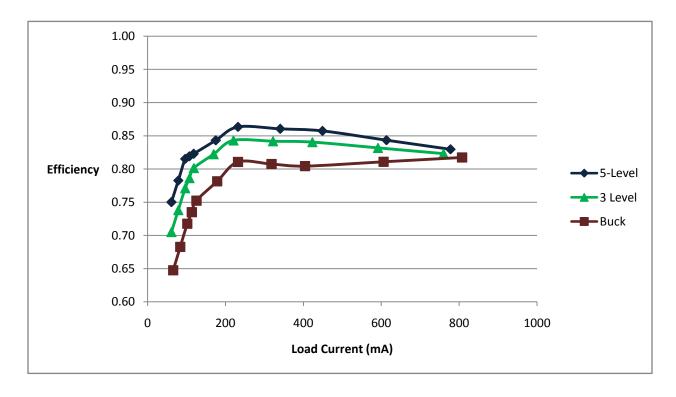

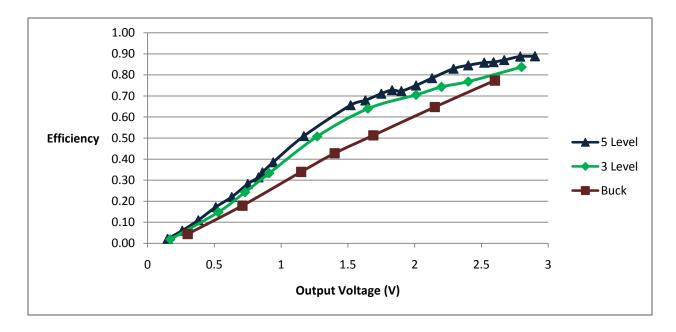

A test PCB is implemented for verification of the functionality and experimental measurements show that for the same switching frequency and inductor size, the 5-level buck converter achieves up to 15% efficiency improvement over a conventional buck converter and a 3-level buck converter at certain output voltage ranges. Peak efficiency of 94% has been

achieved by the 5-Level hybrid converter, which includes all external switching and conduction losses. The proposed hybrid topology proved to yield high conversion efficiency even in the face of component size limitations, which indicates potential benefit in using multilevel converters for several off-chip as well as on-chip applications.

# **CONTENTS**

| Ack  | nowledg  | gements    |                                     | 11  |

|------|----------|------------|-------------------------------------|-----|

| Abs  | tract    |            |                                     | iii |

| Con  | tents    |            |                                     | v   |

| List | of Figu  | res        |                                     | X   |

| List | of Table | es         |                                     | XV  |

| List | of Abbi  | eviations  |                                     | xvi |

| 1    | Intro    | duction    |                                     | 1   |

|      | 1.1      | Motivation | on                                  | 1   |

|      | 1.2      | Challeng   | jes                                 | 4   |

|      | 1.3      | Approach   | h                                   | 6   |

|      | 1.4      | Scope of   | `Work                               | 6   |

| 2    | Back     | ground     | ••••••                              | 8   |

|      | 2.1      | Introduct  | tion to Voltage Regulators          | 8   |

|      | 2.2      | Switched   | d-Capacitor Converters              | 9   |

|      | 2        | .2.1 SCVI  | R Control Mechanisms                | 10  |

|      |          | 2.2.1.1    | SCVR Topology Control               | 11  |

|      |          | 2.2.1.2    | Frequency Modulation                | 11  |

|      |          | 2.2.1.3    | SCVR Digital Capacitance Modulation | 12  |

|      |          | 2.2.1.4    | SCVR Switch Modulation              | 14  |

|      | 2.       | .2.2 Switc | ched Capacitor Converter Loss Model | 14  |

| 2.2     | .2.1 Conduction Losses                    | 15 |

|---------|-------------------------------------------|----|

| 2.2     | .2.2 Switching Losses (Gate Drive Loss)   | 15 |

| 2.2     | .2.3 Parasitic Losses                     | 16 |

| 2.2     | .2.4 Regulation Losses                    | 16 |

| 2.2.3   | Other SCVR Loss Models                    | 17 |

| 2.2     | .3.1 Slow Switching Limit                 | 17 |

| 2.2     | .3.2 Fast Switching Limit                 | 18 |

| 2.2     | .3.3 Model Limitations                    | 18 |

| 2.2.4   | Benefits and Drawbacks of SCVRs           | 19 |

| 2.2.5   | Applications of SCVRs                     | 19 |

| 2.3 Buo | ck Converter                              | 19 |

| 2.3.1   | Control Mechanisms.                       | 21 |

| 2.3     | .1.1 Buck Duty Cycle Modulation           | 21 |

| 2.3     | .1.2 Deadtime                             | 21 |

| 2.3.2   | Buck Converter Loss Model                 | 23 |

| 2.3.3   | Benefits and Drawbacks of Buck Converters | 24 |

| 2.3.4   | Applications of Buck Converters           | 24 |

| 2.4 Tra | ditional Converters Comparison            | 25 |

| 2.5 Hyl | brid Converters                           | 25 |

| 2.5.1   | Hybrid Converter Topologies               | 26 |

| 2.5.2   | Ultradynamic Voltage Regulation           | 28 |

| 2.5     | .2.1 Hysteretic Control Limitations       | 29 |

|   | 2.6 | Ch      | apter Summary                                         | .29 |

|---|-----|---------|-------------------------------------------------------|-----|

| 3 | Des | sign of | a High-Power 5-Level 8-State Hybrid Voltage Regulator | 31  |

|   | 3.1 | Int     | roduction                                             | 31  |

|   | 3.2 | Co      | onverter Architecture                                 | 31  |

|   |     | 3.2.1   | SCVR Topology                                         | .32 |

|   |     | 3.2.2   | Control Signals                                       | 34  |

|   |     | 3.2     | 2.2.1 Phase-Interleaving Technique                    | .35 |

|   | 3.3 | Op      | perating Point                                        | 37  |

|   |     | 3.3.1   | Operating Voltage                                     | 38  |

|   | 3.4 | Cia     | rcuit Loss Model                                      | 39  |

|   |     | 3.4.1   | SSL and FSL Optimization                              | .39 |

|   |     | 3.4.2   | Switching Losses Minimization                         | 40  |

|   | 3.5 | Sir     | mulations                                             | .41 |

|   | 3.6 | Co      | ontrol Mechanism                                      | 44  |

|   |     | 3.6.1   | Deadtime Implementation in the Control Signal         | .45 |

|   | 3.7 | Co      | omponent Selection                                    | 45  |

|   |     | 3.7.1   | Switches                                              | 45  |

|   |     | 3.7.2   | Capacitors                                            | 46  |

|   |     | 3.7.3   | MOSFET Drivers                                        | 47  |

|   |     | 3.7.4   | Inductance                                            | .48 |

|   | 3.8 | Op      | otimization and Layout Considerations                 | 48  |

|   | 3.9 | PC      | CB Implementations                                    | .49 |

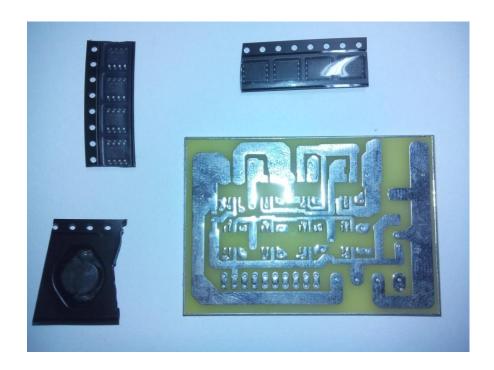

|   |     | 3.9.1   | First PCB                                             | 49  |

|   | 3.9.1.1        | First PCB Components                | 49 |

|---|----------------|-------------------------------------|----|

|   | 3.9.1.2        | First PCB Results                   | 50 |

|   | 3.9.1.3        | First PCB Conclusion                | 50 |

|   | 3.9.2 Seco     | ond PCB                             | 51 |

|   | 3.9.2.1        | Second PCB Components               | 51 |

|   | 3.9.2.2        | Second PCB Results                  | 53 |

|   | 3.9.2.3        | Second PCB Conclusion               | 54 |

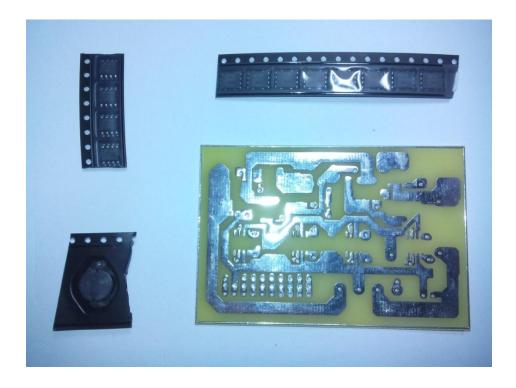

|   | 3.9.3 Thir     | rd PCB                              | 54 |

|   | 3.9.3.1        | Third PCB Components                | 54 |

|   | 3.9.3.2        | Third PCB Results                   | 55 |

|   | 3.9.3.3        | Third PCB Conclusion                | 55 |

|   | 3.9.4 Four     | rth PCB                             | 56 |

|   | 3.9.4.1        | Fourth PCB Components               | 56 |

|   | 3.9.4.2        | Fourth PCB Results                  | 58 |

|   | 3.9.4.3        | Fourth PCB Conclusion               | 58 |

|   | 3.9.5 Fifth    | 1 PCB                               | 59 |

|   | 3.9.5.1        | Fifth PCB Components                | 59 |

|   | 3.9.5.2        | Fifth PCB Results                   | 61 |

|   | 3.9.5.3        | Fifth PCB Conclusion                | 62 |

|   | 3.10 Chapter   | Summary                             | 63 |

| 4 | Results and Di | scussion                            | 64 |

|   | 4.1 5-Level    | Hybrid Testing and Measurements     | 64 |

|   | 4.1.1 Volt     | tage at the Inductor (Vx) Waveforms | 64 |

|       |       | 4.1    | .1.1    | 0-0.25Vin Operation Region                       | 64 |

|-------|-------|--------|---------|--------------------------------------------------|----|

|       |       | 4.1    | .1.2    | 0.25-0.5Vin Operation Region                     | 65 |

|       |       | 4.1    | .1.3    | 0.5-0.75Vin Operation Region                     | 66 |

|       |       | 4.1    | .1.4    | 0.75-Vin Operation Region                        | 68 |

|       | 4     | 1.1.2  | Flying  | g Capacitors Operation                           | 71 |

|       | 4     | 1.1.3  | Deadt   | time Waveforms                                   | 72 |

|       | 4.2   | Otl    | her Co  | nverter Implementations                          | 74 |

|       | 4     | 1.2.1  | Buck    | Converter Implementation Measurements            | 74 |

|       | 4     | 1.2.2  | 3-Lev   | el Hybrid Converter Implementation               | 76 |

|       |       | 4.2    | 2.2.1   | 3-Level Hybrid First Operation Region Waveforms  | 76 |

|       |       | 4.2    | 2.2.2   | 3-Level Hybrid Second Operation Region Waveforms | 78 |

|       | 4.3   | Ou     | tput V  | oltage Ripples Measurements                      | 79 |

|       | 4.4   | Per    | rforma  | nce Comparison Between Converters                | 81 |

|       | 4.5   | Ch     | apter S | Summary                                          | 84 |

| 5     | Con   | clusio | n and   | Future Work                                      | 85 |

|       | 5.1   | Co     | nclusio | on                                               | 85 |

|       | 5.2   | Fu     | ture W  | ork                                              | 86 |

| Refer | ences |        |         |                                                  | 88 |

# **LIST OF FIGURES**

| 1.1 | OLPC XO Laptop Motherboard                                                         | 2  |

|-----|------------------------------------------------------------------------------------|----|

| 2.1 | Switched-Capacitor voltage regulator operating in two phases (top), where switches |    |

|     | 1,3 are on in phase 1 (bottom left), and switches 2,4 on in phase 2 (bottom right) | 10 |

| 2.2 | Five possible topologies that can be integrated in one switched capacitor          |    |

|     | voltage regulator circuit using only 6 capacitors and 13 switches                  | 11 |

| 2.3 | Multiple Topology switched capacitor voltage regulator with efficiency peaks at    |    |

|     | ideal no-load voltages                                                             | 12 |

| 2.4 | Capacitance Modulation Circuit using limited number of capacitors for multiple     |    |

|     | flying capacitance value based on input vectors                                    | 13 |

| 2.5 | Capacitance modulation output voltage change due to reference change               | 14 |

| 2.6 | Conventional buck converter (top) operating in two phases, phase 1 (bottom left)   |    |

|     | and phase 2 (bottom right)                                                         | 20 |

| 2.7 | Insufficient deadtime added to signals (top left), excessive deadtime added to     |    |

|     | signals (top right), optimized deadtime added to signals (bottom)                  | 22 |

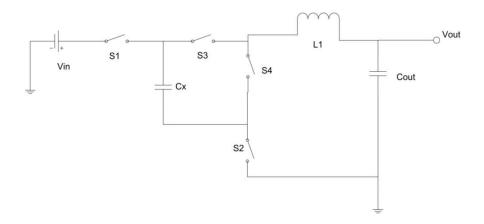

| 2.8 | 3-Level Buck Converter                                                             | 27 |

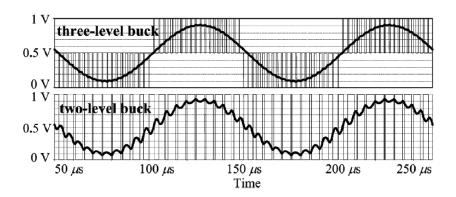

| 2.9 | 3-Level Buck Converter Output ripples vs. Conventional Buck output ripples         | 27 |

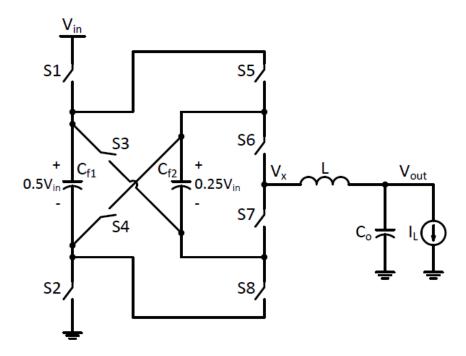

| 3.1 | Adapted 5-Level Hybrid Converter circuit structure                                 | 33 |

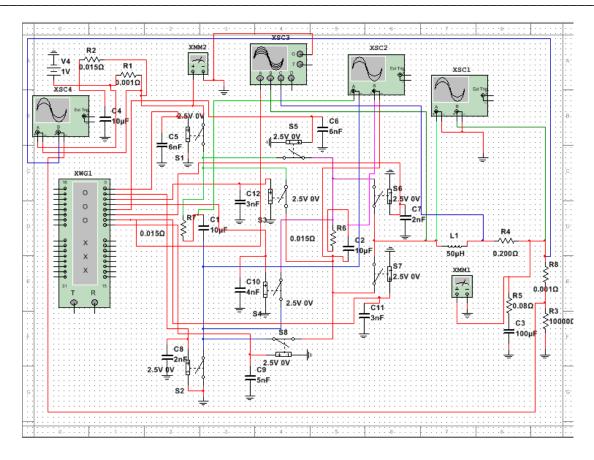

| 3.2 | Multisim 14 circuit schematic including all parasitics and simulation tools        | 42 |

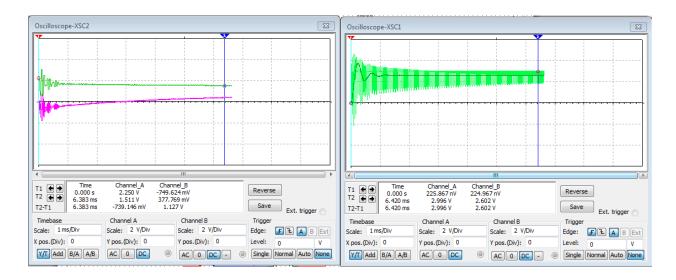

| 3.3  | Simulated transient voltage on flying capacitors (left) and transient output voltage vs. voltage at the inductor (right)        | 42 |

|------|---------------------------------------------------------------------------------------------------------------------------------|----|

|      |                                                                                                                                 | 42 |

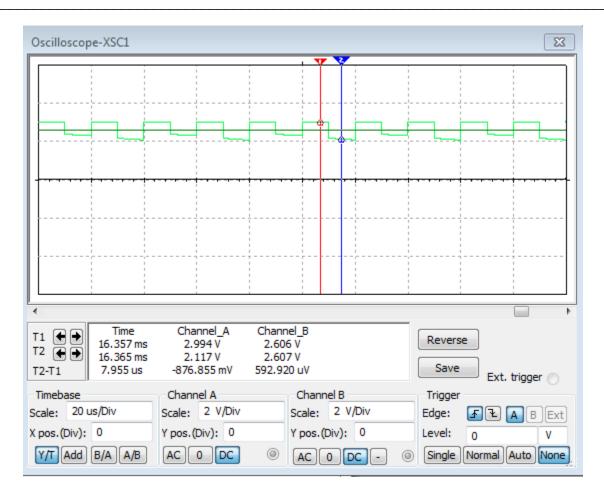

| 3.4  | Simulated steady-state voltage on flying capacitors with C1 voltage = $0.5Vin$ and C2 voltage = $0.25Vin$ at $Vin = 3V$         | 43 |

| 3.5  | Output voltage vs. voltage at the inductor ( $Vx$ ) in the $0.75$ - $1Vin$ operation region with $Vin = 3V$                     | 44 |

| 3.6  | First MOSFET drivers Printed Circuit Board                                                                                      | 52 |

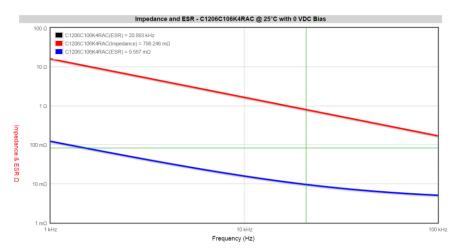

| 3.7  | Flying Capacitor Equivalent Series Resistance (m $\Omega$ ) vs. Frequency (Hz)                                                  | 53 |

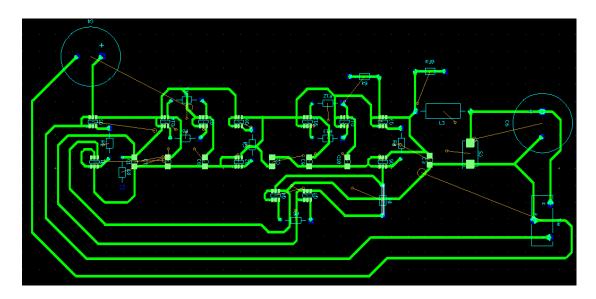

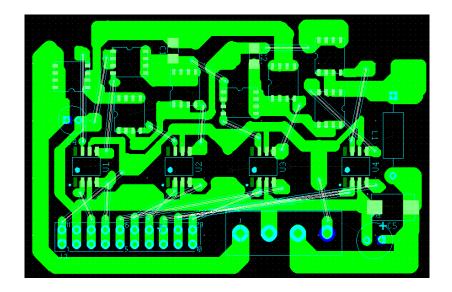

| 3.8  | Printed Circuit Board #2 Layout.                                                                                                | 53 |

| 3.9  | Printed Circuit Board #3 Layout.                                                                                                | 55 |

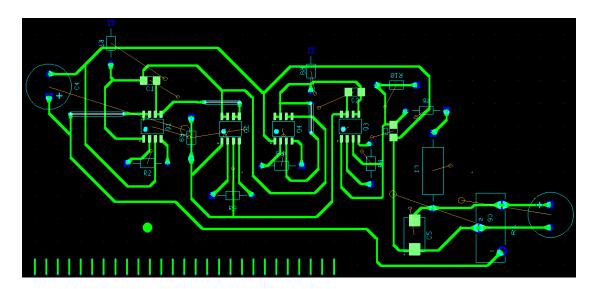

| 3.10 | Printed Circuit Board #4 Layout.                                                                                                | 57 |

| 3.11 | Printed Circuit Board #4 before components mounting.                                                                            | 57 |

| 3.12 | Completed Printed Circuit Board #4 with US quarter dollar for scale                                                             | 58 |

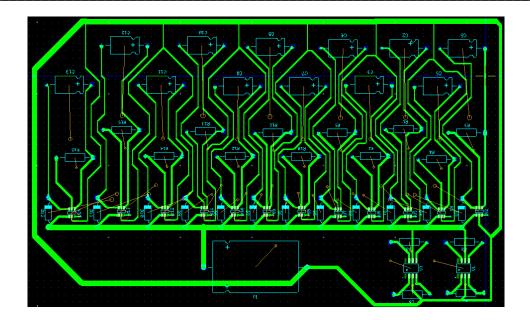

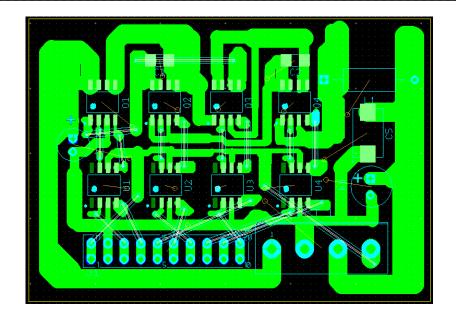

| 3.13 | Printed Circuit Board #5 layout.                                                                                                | 60 |

| 3.14 | Printed Circuit Board #5 before components installation.                                                                        | 60 |

| 3.15 | Completed Printed Circuit Board #5 with US quarter dollar for scale                                                             | 61 |

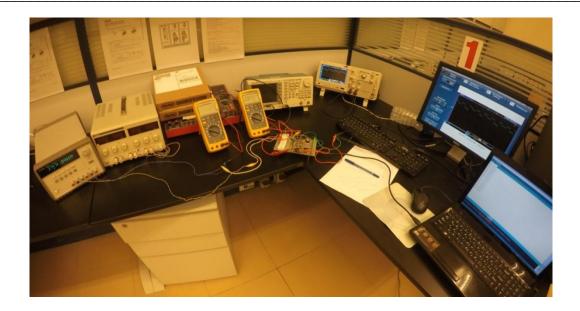

| 3.16 | Test setup with the converter Printed Circuit Board #5, microcontroller, peripheral decoupling capacitors, and load resistances | 61 |

| 3.17 | Workstation used for testing                                                                                                    | 62 |

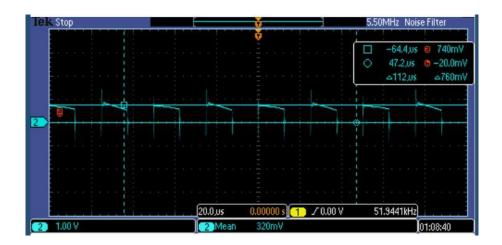

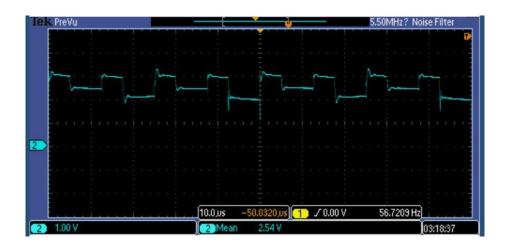

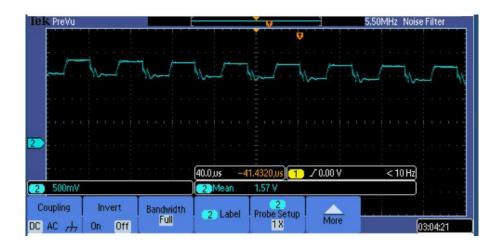

| 4.1  | Voltage at the Inductor ( <i>Vx</i> ) for the <i>0-0.25Vin</i> operation region with 50% duty cycle.                            | 65 |

| 4.2  | Voltage at the Inductor ( <i>Vx</i> ) for the <i>0-0.25Vin</i> operation region with 25% duty cycle.                            | 65 |

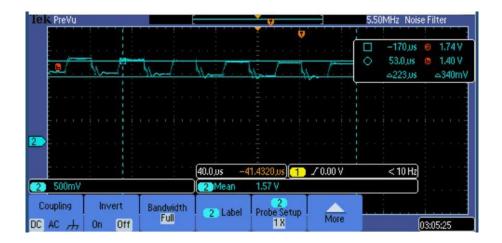

| 4.3  | Voltage at the Inductor ( $Vx$ ) for the $0.25$ - $0.5Vin$ operation region with 40% duty cycle.                                 | 66 |

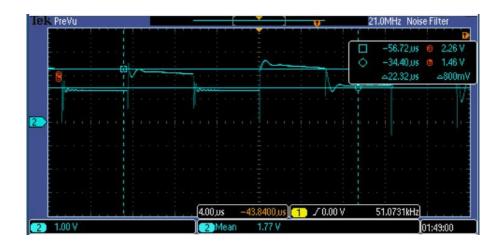

|------|----------------------------------------------------------------------------------------------------------------------------------|----|

| 4.4  | Voltage at the Inductor ( $Vx$ ) for the $0.25$ - $0.5Vin$ operation region with 40% duty cycle with cursors                     | 66 |

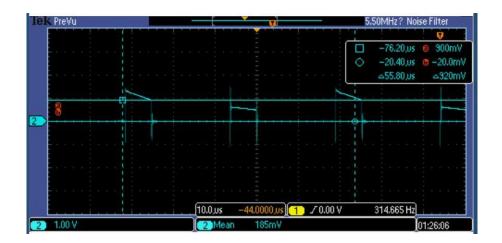

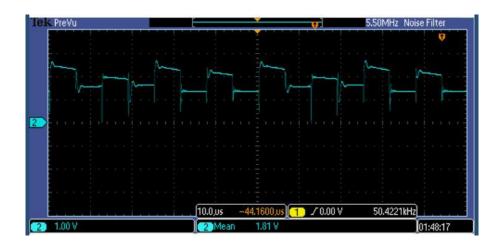

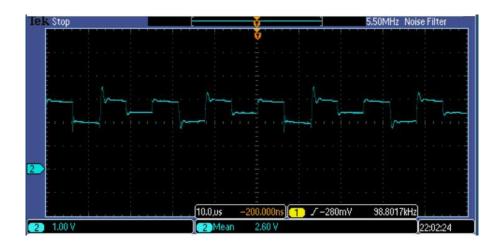

| 4.5  | Voltage at the Inductor ( $Vx$ ) for the $0.5$ - $0.75Vin$ operation region with 50% duty cycle.                                 | 67 |

| 4.6  | Voltage at the Inductor ( $Vx$ ) for the $0.5$ - $0.75Vin$ operation region with 50% duty cycle with cursors                     | 67 |

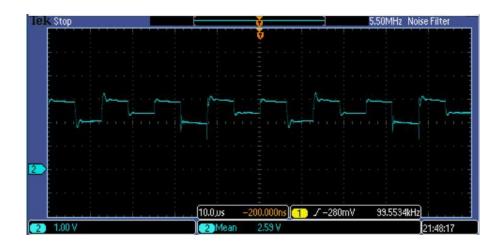

| 4.7  | Voltage at the Inductor ( <i>Vx</i> ) for the <i>0.5-0.75Vin</i> operation region with 25% duty cycle                            | 68 |

| 4.8  | Voltage at the Inductor ( $Vx$ ) for the $0.5$ - $0.75Vin$ operation region with 75% duty cycle.                                 | 68 |

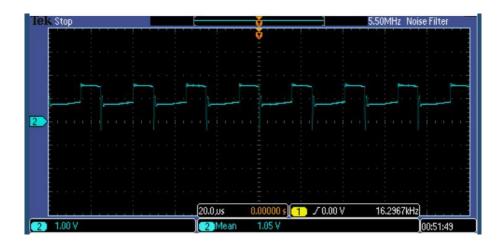

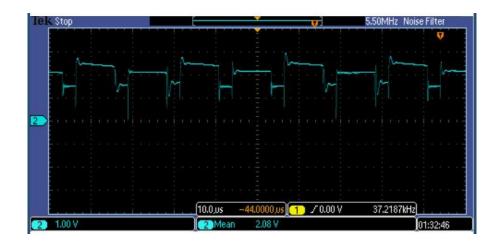

| 4.9  | Voltage at the Inductor ( <i>Vx</i> ) for the 0.75-1Vin operation region with 50% duty cycle                                     | 69 |

| 4.10 | Voltage at the Inductor ( $Vx$ ) for the $0.75$ - $1Vin$ operation region with 50% duty cycle with cursors on average            | 69 |

| 4.11 | Voltage at the Inductor ( $Vx$ ) for the $0.75$ - $1Vin$ operation region with 50% duty cycle with cursors on both output levels | 70 |

| 4.12 | Voltage at the Inductor ( $Vx$ ) for the $0.75$ - $1Vin$ operation region with 25% duty cycle.                                   | 70 |

| 4.13 | Voltage at the Inductor ( $Vx$ ) for the $0.75$ - $1Vin$ operation region with 75% duty cycle.                                   | 71 |

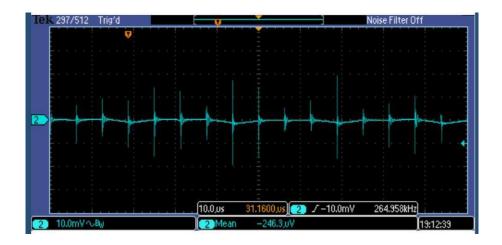

| 4.14 | Voltage on flying capacitor C1                                                                                                   | 71 |

| 4.15 | Voltage on flying capacitor C1 with cursors                                                                                      | 72 |

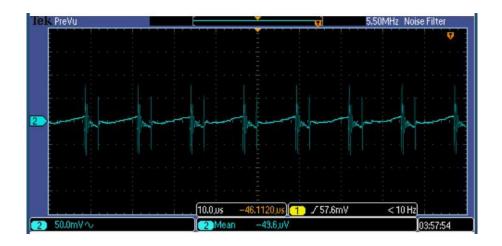

| 4.16 | Voltage on flying capacitor C2 with cursors                                                                                      | 72 |

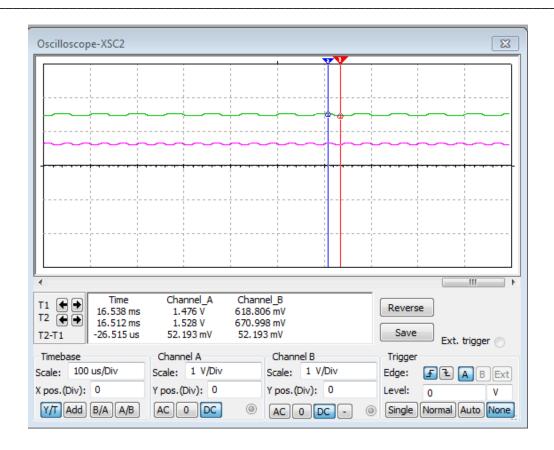

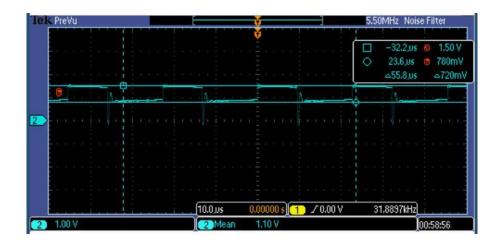

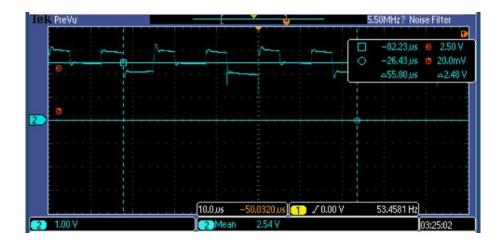

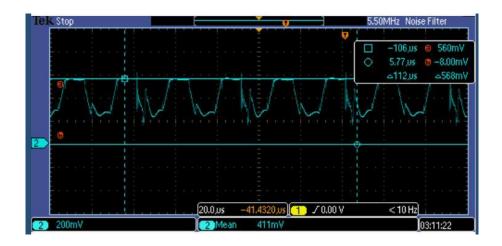

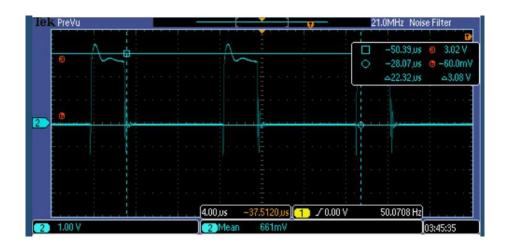

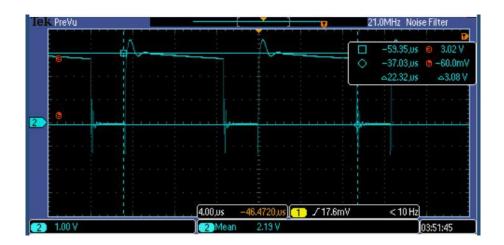

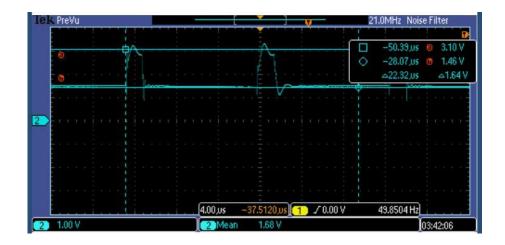

| 4.17 | Voltage at the inductor $(Vx)$ of the 5-Level hybrid operating                         |

|------|----------------------------------------------------------------------------------------|

|      | at 0.5-0.75Vin without deadtime                                                        |

| 4.18 | Voltage at the inductor $(Vx)$ of the 5-Level hybrid operating                         |

|      | at 0.5-0.75Vin with deadtime                                                           |

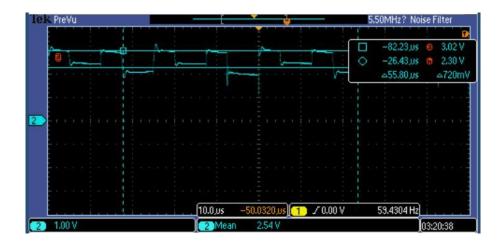

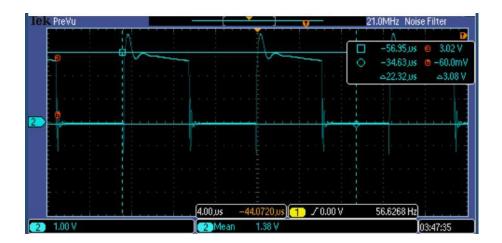

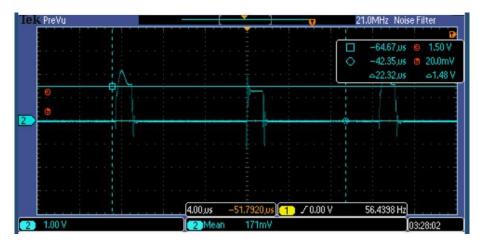

| 4.19 | Voltage at the inductor $(Vx)$ of the 5-Level hybrid operating                         |

|      | at 0.75-1Vin without deadtime                                                          |

| 4.20 | Voltage at the inductor $(Vx)$ of the 5-Level hybrid operating                         |

|      | at 0.75-1Vin with deadtime74                                                           |

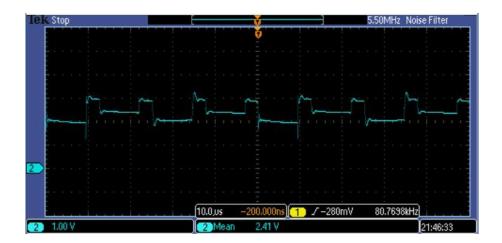

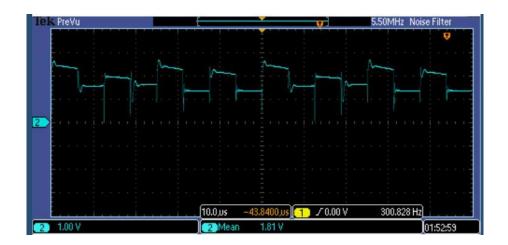

| 4.21 | Voltage at the inductor $(Vx)$ for a Buck converter with 25% duty cycle with cursors75 |

| 4.22 | Voltage at the inductor $(Vx)$ for a Buck converter with 50% duty cycle with cursors75 |

| 4.23 | Voltage at the inductor $(Vx)$ for a Buck converter with 75% duty cycle and cursors76  |

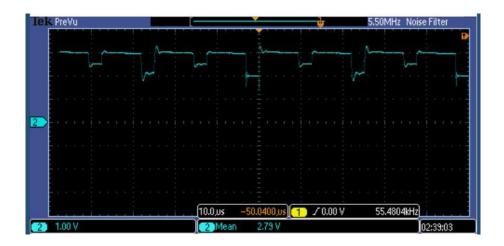

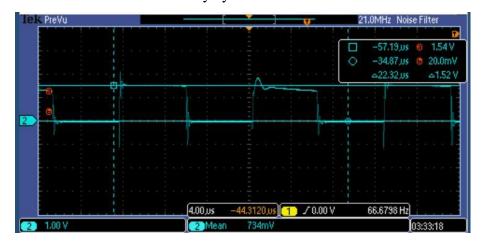

| 4.24 | Voltage at the inductor of a test 3-Level converter in the first                       |

|      | operation region at 25% duty cycle with cursors                                        |

| 4.25 | Voltage at the inductor of a test 3-Level converter in the first                       |

|      | operation region at 50% duty cycle                                                     |

| 4.26 | Voltage at the inductor of a test 3-Level converter in the first                       |

|      | operation region at 75% duty cycle with cursors                                        |

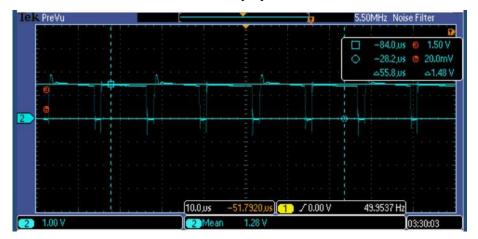

| 4.27 | Voltage at the inductor of a test 3-Level converter in the second                      |

|      | operation region at 25% duty cycle with cursors                                        |

| 4.28 | Voltage at the inductor of a test 3-Level converter in the second                      |

|      | operation region at 50% duty cycle with cursors                                        |

| 4.29 | Voltage at the inductor of a test 3-Level converter in the second                      |

|      | operation region at 75% duty cycle with cursors                                        |

| 4.30 | Conventional Buck output voltage ripples                                               |

| 4.31 | 5-Level Hybrid Buck output voltage ripples                                                                                | 80 |

|------|---------------------------------------------------------------------------------------------------------------------------|----|

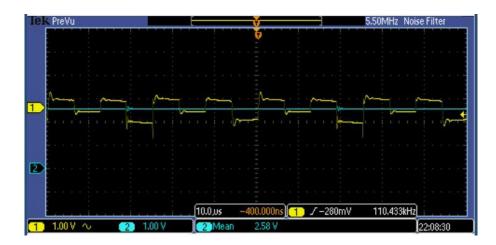

| 4.32 | Voltage at the inductor $(Vx)$ vs $Vout$ for a 5-Level hybrid converter operating in the $0.75$ - $1Vin$ operation region | 80 |

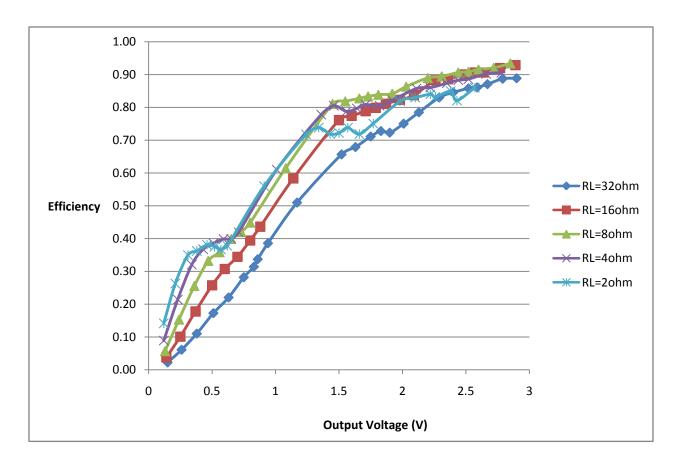

| 4.33 | Efficiency vs. Output voltage (V) of the 5-Level Hybrid at multiple load resistances ( $\Omega$ ) with $Vin=3V$           | 81 |

| 4.34 | Efficiency vs. Load Current (mA) of the 5-Level hybrid converter at multiple output voltages (V)                          | 82 |

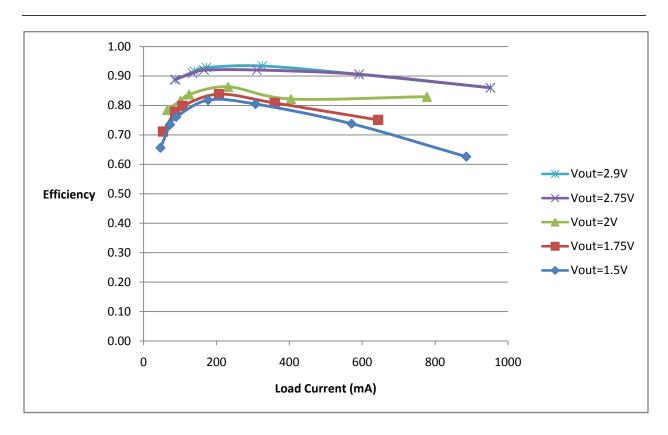

| 4.35 | Efficiency vs. Load Current (mA) of the three converter types at <i>Vout</i> =2.5V with <i>Vin</i> =3V                    | 83 |

| 4.36 | Efficiency vs. Load Current (mA) of the three converter types at <i>Vout</i> =2V with <i>Vin</i> =3V                      | 83 |

| 4.37 | Efficiency vs. Output Voltage (V) of the three converter types at a Load resistance of $32\Omega$                         | 84 |

# LIST OF TABLES

| 2.1 | Performance comparison between traditional SCVRs and Buck converters                                                  | 25 |

|-----|-----------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | Switch Configurations providing each Voltage Level                                                                    | 34 |

| 3.2 | Switch Configurations in the Four Operation Regions                                                                   | 35 |

| 3.3 | Components used for Printed Circuit Board #1                                                                          | 49 |

| 3.4 | Components used for Printed Circuit Board #2                                                                          | 51 |

| 3.5 | Components used in Printed Circuit Board #3                                                                           | 54 |

| 3.6 | Components used in Printed Circuit Board #4                                                                           | 56 |

| 3.7 | Components used for Printed Circuit Board #5                                                                          | 59 |

| 3.8 | Comparison between different Metal-Oxide Silicon Field-Effect Transistor switches used in all Printed Circuit Boards. | 63 |

| 5.1 | Performance Comparison between Traditional Converters and the 5-Level Hybrid                                          | 86 |

# LIST OF ABBREVIATIONS

**DC** Direct Current

**PCB** Printed Circuit Board

POL Point-of-Load

MEP Minimum Energy Point

**RF** Radio Frequency

VR Voltage Regulator

**UDVS** Ultra Dynamic Voltage Scaling

**SCVR** Switched Capacitor Voltage Regulator

**LDR** Low Dropout Regulator

**PFM** Pulse Frequency Modulation

**CCM** Continuous Conduction Mode

**DCM** Discontinuous Conduction Mode

**MOSFET** Metal-Oxide Silicon Field-Effect Transistor

**ESR** Equivalent Series Resistance

**FSL** Fast Switching Limit

SSL Slow Switching Limit

**FPGA** Field-Programmable-Gate-Array

# Chapter 1

## **INTRODUCTION**

#### 1.1 Motivation

With the increasing advances in technology, several trends have dominated the electronics industry. One such trend is the reduction of size, and the increase in performance of consumer electronic devices. These advancements in size, performance, and power efficiency are the pillars of the move towards mobile devices, driving them to become more powerful, smaller, and lighter.

Accordingly, portable devices have become the new norm in modern day consumer electronics. Devices such as mobiles, tablets, and laptops are continuously being improved in order to compete in what has grown into a billion dollar industry. The market for these devices has even expanded to be the dominant type of consumer electronics. This driving force has molded the scientific community's incentives towards rapidly advancing modern technology to keep up with the increasing demand and growing market size. The main limitation to the continuing advancement in mobile devices is power management.

Mobile devices, tablets, and laptops are generally battery powered, and their processing modules are power sensitive. This creates a difficulty since the battery output voltage decreases as it is discharged over time. Accordingly, a voltage regulation mechanism is essential, which is satisfied by the use of bulky DC-DC converters. These converters also have high requirements on efficiency and power rating in order to obtain high power conversion while maintaining long battery lifetime.

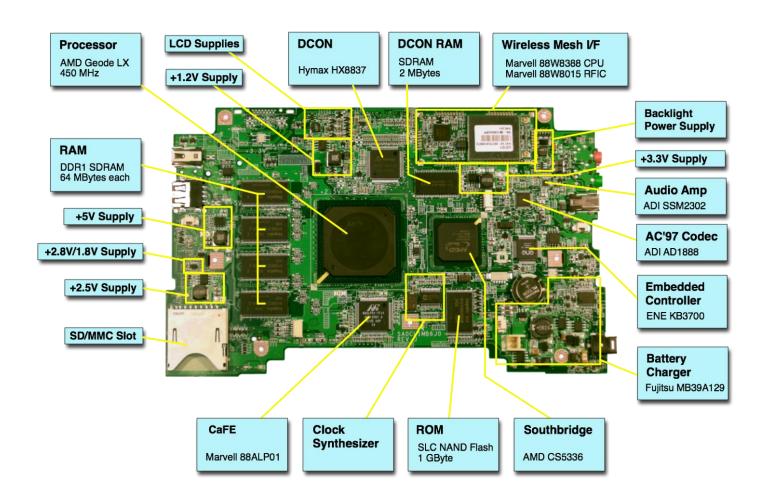

The DC-DC converter is then one of the main components in a power management module, and the bulkiest, due to the use of large inductors, and the need for several converters within the device. For instance, Figure 1.1 shows a laptop's motherboard, which is dominated by power management modules, including the eight different DC-DC converters in the voltage supplies and the battery charger [1].

Figure 1.1: OLPC XO Laptop Motherboard [1].

The multitude of DC-DC converters in one motherboard is caused by the trend of placing the converter at the point of load (POL), which enables the transfer of the intermediate bus voltage into the voltage required by the particular load [2]. POL converters allow a significant reduction in voltage drops across power distribution networks, and in turn, increased efficiency. However, using multiple POL converters also leads to increased area. One method of overcoming this challenge is the use of compact DC-DC converters with minimally-sized components. It is shown in Figure 1.1 that the component dominating the area of each converter is the inductor, as it occupies about 25% of the total area of the 2.5V supply, 50% of the total area of the 5V supply, and 30% of the total area of the 3.3V supply. It is predicted that the number of supply voltages within the motherboard, and even the integrated circuit (IC), is increasing since different modules utilize different voltages to reach their maximum performance with highest efficiency [3]. Since the largest component in the DC-DC converters is the inductor, reducing its size needs to be prioritized in order to effectively minimize the total converter size.

Another demand for DC-DC converters, aside than compact size, is programmability, which allows varying the output voltage of the converter. This was implemented a number of times in the literature, due to its usefulness [4]. Programmable DC-DC converters have been implemented in small areas, in order to remain relevant for use in portable and handheld applications [5] [6]. Several regulation control methods have been implemented where the target has been dynamic performance through the optimization of the supply voltage [7]. It has also been used to obtain a lower voltage for standby mode in some applications, in order to minimize static power consumption, and to increase the supply voltage when the application is active and requires higher performance.

The need for an ultradynamic, fast response regulator is one of the main forces pushing for more research into DC-DC converters with increased performance. Ultradynamic, fast regulators are useful when considering low-power applications with minimum energy requirements. These applications contain logic elements that calculate the optimum supply voltage required for the application to function with the least power consumption.

One main method of optimizing the voltage supply to satisfy the performance and power consumption needs is to change it according to a weighted algorithm, where higher performance would require a higher supply voltage, at the expense of power consumption. On the other hand, a reduction in power consumption would require a lower supply voltage, at the expense of performance. There exists an operating voltage at which the total energy consumed by a digital circuit is minimized. This operating point, often referred to as the Minimum Energy Point (MEP), is only achievable with an ultradynamic regulator that can reach many supply voltages with minimal error, and with very small delay between two levels [8]. Tracking the MEP is currently a trend in modern circuits to optimize power consumption by dynamically changing the operating voltage to desired performance, which requires versatile DC-DC converters with large range of conversion ratios and with high performance throughout the range [7]. Changes in the MEP are based on factors such as load requirements and environmental conditions such as temperature. Energy savings due to MEP tracking have been reported to reach 50-100%, especially with circuits whose power losses are dominated by leakage.

Another application for ultradynamic DC-DC converters is envelope tracking for radio frequency (RF) applications [9]. These applications are very sensitive to voltage variations, and therefore require output voltage accuracy for envelope tracking up to very insignificant errors. Additional voltage sensitive applications include implantable medical devices and wearable medical electronics. These devices constantly take measurements periodically, and their batteries are changed after long time periods. DC-DC converters with compact size are essential to their design, while maintaining accurate supply voltages for accurate biometric measurements. Also, high efficiency is essential to maximize battery life. Accordingly, the main criteria for medical electronics are size, efficiency, and minimized output voltage ripples.

#### 1.2 Challenges

Since portable devices have dominated the consumer electronics industry, the demand for technologies fitting their criteria has increased. As mentioned earlier, modern day applications have high requirements, in terms of efficiency and size in particular. Therefore, DC-DC converters have a set of defined metrics based on which they are measured.

First, there is the voltage range and conversion ratio, which determines the range of operation of the DC-DC converter and the ratio between the input and output voltages. Secondly, the rated load current range determines if the converter can function at high load or low load applications. Also, the total converter area and power density both factor in the converter selection criteria for different applications. Other criteria, such as the operating conditions, allow matching a defined converter to specific applications, in order to obtain maximized performance and optimized design. These conditions include maximum output voltage ripples, frequency of operation, thermal management, and reliability [10]. Other important aspects for converters include PCB profile (height) of components on board, where the limitation is usually the inductor size, if the circuit requires an inductor [11]. These factors determine the capability of integrating the converter and its potential applications.

This creates an important metric for DC-DC converters, which is labeled the total converter area. This area takes into account the PCB height, and it is always preferable to decrease the height in order to fit power supplies in smaller, more compact devices. For instance, handheld devices are constantly getting smaller in size with the sacrifice being shorter lasting power supplies. This occurs because decreasing the inductor size significantly affects overall efficiency in a traditional buck converter, which is the most commonly used DC-DC converter in the industry.

Not only is converter area important for decreasing the device size, it is important to be able to integrate multiple converters instead of just one on a board. Many devices require different voltages for different modules on the same PCB. This necessitates multiple, DC-DC converters. This also applies to some chips, which require a similar concept labeled distributed, on-chip DC-DC converters. Optimizing a distributed power delivery network requires optimizing the number of converters, the capacitance of each converter, and the design layout [12]. Distributed on-chip DC-DC converters also give a boost to the efficiency by reducing IR losses in the interconnects. It has been proven that a reduction in the IR drop by 74% could be achieved using distributed DC-DC converters compared to lumped designs [13]. This concept can be extended to higher power converters that are found on PCBs. However, implementing them can

be challenging if each converter takes up a considerable area. The alternative becomes using a Switched-Capacitor DC-DC converter, which are generally limited by their low efficiency. Hence, area reduction of the more common and efficient converter, the Buck Converter, becomes necessary. The Buck converter's area limitation results from the use of a large inductor with a high quality factor, which is complicated to implement on-chip with high efficiency. Consequently, optimizing the Buck converter design promises better integration without a large compromise in efficiency.

#### 1.3 Approach

First, the traditional DC-DC converters found in the industry and literature are explained and analyzed. According to the analysis, a hybrid converter topology that combines the advantages of common switched capacitor voltage regulators (SCVR) and Buck converters becomes necessary to achieve higher performance with a reduction in size. The loss models of common converters are each analyzed, and the main sources of loss are targeted and eliminated, therefore resulting in efficient converters by using smaller inductors. After finding a suitable design, it is then implemented and tested against the industry gold standard in order to prove its advantages. The targeted applications are portable, handheld devices, but the concept can be extended to other applications including on-chip implementations.

#### 1.4 Scope of Work

Analyzing the literature is necessary before determining the design methodology and techniques. First, a background on voltage regulators in general is presented. The more common types of regulators are introduced and explained in detail. Next, their loss models are analyzed for optimization. Then, a comparison between the advantages and disadvantages of these converters is presented. This allows their limitations to be addressed and an improved topology that solves the problems faced by traditional converters can be developed. Afterwards, the hybrid converter topology and the regulation techniques for it are introduced and discussed. Then, the PCB implementation process of the hybrid converter is described. Finally, the results are shown

and discussed, followed by a conclusion of the research findings and their impact on the power electronics industry.

# Chapter 2

## **BACKGROUND**

#### 2.1 Introduction to Voltage Regulators

Various types of voltage regulators (VR) exist in the literature. However, two main types dominate the industry: linear regulators, also called Low-Dropout Regulators (LDR), and switched regulators.

Linear regulators consist of resistive elements and operate by dissipating some of the input power in order to produce a reduced output voltage. These regulators suffer from very limited efficiency, which is constrained by the conversion ratio. Due to the high power dissipation in the LDR circuitry, thermal management requirements are important for protecting the regulator from damage. Yet, linear regulators offer very simple circuitry and relatively small area, making them appealing for compact designs with flexible power requirements.

Switched regulators function by transferring charge discontinuously in order to provide a decreased voltage at the output. Switching regulators are composed of an active switching element and a passive charging element. Switching regulators offer much higher efficiencies than linear regulators, with the cost being area and complexity.

The two common topologies of switched regulators are Switched-Capacitor voltage regulators (SCVRs) and the Buck converter. Both converters use switching elements but differ in the charge storing element being used. The SCVR uses capacitors to transfer charge from the input to the output, while the Buck converter uses an inductor to perform the voltage conversion. Each one of the converters has advantages over the other in terms of efficiency, area, and complexity, making them suitable for different applications.

For any converter, there exists a regulation stage, or a control stage, which is responsible for maintaining a steady output voltage that is regulated from the input voltage. It is required that the output voltage tracks a certain reference voltage that is assumed to be lower than the input voltage, assuming a step-down converter. The most common control techniques can be used with either SCVRs or Buck converters; therefore, both would be applicable to hybrid converters.

Hence, control mechanisms for all converter types need to be explored to optimize both the

2.2 Switched-Capacitor Converters

conversion and control stages.

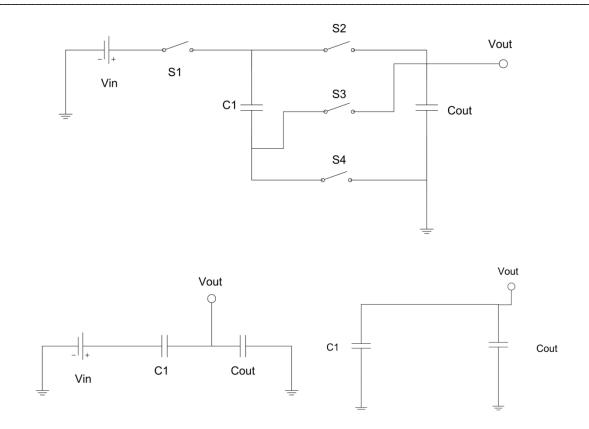

SCVRs use charge transfer capacitors to move charge from the input to the output, while varying the connections between the capacitors in order to produce a different voltage at the output. The SCVR usually operates in two phases, where some of the switches connecting the capacitors are on at one phase, with the rest being on at the second (or more) phase. Figure 2.1 shows an example of a switched-capacitor converter operating in two phases, with some switches turning on during the first phase, with the other switches turning on during the second phase. In the first phase, the capacitors are connected in series to have the input voltage divided on the capacitors, and they are then connected in parallel during the second phase, in order to obtain a decreased output voltage with an increased output current (which maintains a high efficiency). SCVR applications include wireless sensor node converters, energy harvesters, ultracompact energy storage conversion [14]. The SCVR can be optimized by finding limits for the output resistance and efficiency, which allows comparison of SC converters, for more accurate topology selection methods [15].

Figure 2.1. Switched-Capacitor voltage regulator operating in two phases (top), where switches 1, 3 are on in phase 1 (bottom left), and switches 2, 4 on in phase 2 (bottom right).

#### 2.2.1 SCVR Control Mechanisms

First, the control methods in SCVRs range from frequency modulation, topology control, to digital capacitance modulation, and switch modulation. Equation (2.1) shows the relationship between the output resistance of the converter, *Rout*, and many factors that come into play when optimizing the efficiency, and could also be used to change the conversion ratio [14]. It is shown that the output resistance is proportional to the on-resistance of the switches  $R_{on}$ , and inversely proportional to the switching frequency  $F_{SW}$ , flying capacitance  $C_i$ , and the duty cycle  $D_i$ , which are all flexible for optimization and modulation. Since the output resistance is inversely proportional to the output voltage, virtually unlimited combinations could be implemented to obtain ultradynamic voltage scaling (UDVS).

$$R_{out} \propto \frac{1}{c_i F_{sw}} + 2 \frac{R_{on}}{D_i} \tag{2.1}$$

#### 2.2.1.1 SCVR Topology Control

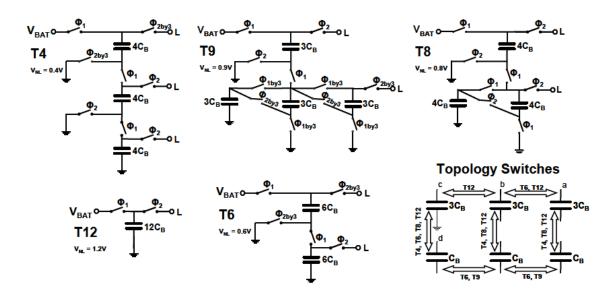

The clear technique of changing conversion ratios on a SCVR is changing the topology by changing the switching to make different combinations of the capacitors in different phases. This is implemented heavily in the literature due to its efficiency and the minimalistic additional control circuitry. For instance, a circuit is implemented in [4] where 5 topologies are available for controlling 5 different conversion ratios. The overhead circuitry is very minimalist, while the output range is increased dramatically. It is shown in Figure 2.2 that several topologies are easily attainable by changing the switch configurations.

Figure 2.2. Five possible topologies that can be integrated in one SCVR circuit using only 6 capacitors and 13 switches [4].

#### 2.2.1.2 Frequency Modulation

The most efficient form of output regulation for both Buck converters and Switched-Capacitor converters is Pulse Frequency Modulation (PFM), as it changes the operating point of the converter as a whole, without causing significant losses. In the Buck converter, it allows maintaining the same efficiency, while adjusting the frequency according to the load power required, in which the frequency increases as the load current increases. The same implementation is possible for SCVRs; however, it is not only used to regulate the current output with changing loads, but also to change the output voltage (and conversion ratio) on the same

load by decreasing the frequency to provide a smaller output. Frequency modulation has also been referred to as SSL modulation, since it directly enhances or degrades the SSL impedance.

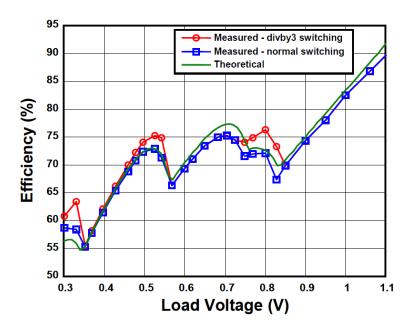

This technique, used in [4], provides more conversion ratios at the expense of the efficiency, since SCVRs are sensitive to producing output voltages that are far from the ideal noload voltage of the topology in use. This is shown in Figure 2.3 where the efficiency drops as the output voltage ratio moves further from the topology no-load voltage.

Figure 2.3. Multiple Topology SCVR with efficiency peaks at ideal no-load voltages [4].

#### 2.2.1.3 SCVR Digital Capacitance Modulation

Another method of changing the voltage conversion ratio is varying the flying capacitance value, which allows more charge to be transferred, therefore having a small but sometimes useful effect on output voltage. Yet, the main use of capacitance modulation has been to achieve regulated voltages over changes in load current, which is shown in [16]. Modifying the flying capacitance value is done by adding a series of switches and smaller capacitors, and varying the connections between the capacitors in order to make them in series or parallel. This is done in Figure 2.4, in which different switch combinations provide different values for the flying capacitance.

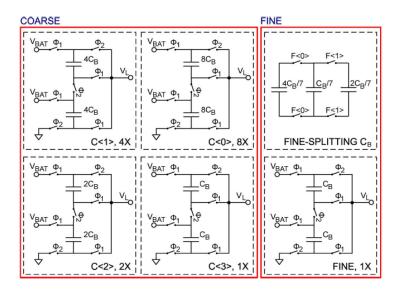

Figure 2.4. Capacitance Modulation Circuit using limited number of capacitors for multiple flying capacitance value based on input vectors [16].

Digital capacitance modulation is preferred to regulate output voltage over load changes due to its resilience to switching noise, which is an issue with Pulse Frequency Modulation (PFM). While PFM is a stable technique of voltage regulation with minimal losses, changing the frequency with load current changes produces varying switching noise in the input and output and is challenging to control. It is shown in Figure 2.5 that digital capacitance modulation provides smooth regulation over different load currents using many capacitance values. Yet, the disadvantage remains to be its overhead circuitry, since the control mechanism is more complex to implement, and the addition of more capacitors and switches, which inevitably has a drastic effect on the efficiency.

Figure 2.5. Capacitance modulation output voltage change due to reference change [16].

#### 2.2.1.4 SCVR Switch Modulation

Switch size is modulated by increasing the width of the switch in order to decrease the on-resistance, at the expense of increasing the gate capacitance. This produces an improvement in conduction losses, by minimizing the Metal-Oxide Silicon Field-Effect Transistors (MOSFET)  $R_{dson}$  while increasing the switching losses, which are directly affected by the switch gate capacitance. It requires very careful optimization to find the most efficient switch size for a particular converter based on the conversion ratio and the load current.

As a result, switch size modulation is not a very common mode of voltage regulation, due to its complexity as well as inefficiency in some aspects. That is mainly true for off-chip applications, while on-chip implementations have proved slight improvement over unmodulated switches [14] [16].

#### 2.2.2 Switched-Capacitor Converter Loss Model

The SCVR is characterized by having more components than a buck converter, and is therefore dominated by parasitic losses due to resistances and capacitances. A SCVR with

multiple topologies also suffers from complexity in modeling the different configurations of the switches and capacitors, and requires simplified modeling for accuracy. Complexity also results from the different control circuits, clock sources, and topology controllers [12].

Yet, the main sources of losses are consistent in all switched-capacitor converters, consisting of conduction losses, switching losses, parasitic losses, and regulation losses.

#### 2.2.2.1 Conduction Losses

Conduction losses result from charging a capacitor through a switch that has a known onresistance [4]. The power is lost in the switches while charging the flying capacitors can be expressed by Equation (2.2), where  $M_{sw}$  is a constant determined by converter topology,  $I_{out}$  is total current delivered by converter,  $R_{on}$  is switch resistance per unit width, and  $W_{sw}$  is switch width [12].

$$P_{cond} = M_{sw} \cdot \frac{I_{out}^2}{N_{nhase}} \cdot \frac{R_{on}}{W_{sw}}$$

(2.2)

It is shown that energy is lost through the switches, but the conduction losses also include energy lost on the capacitor equivalent series resistance (ESR) during each charge transfer to or from a capacitor. The energy loss, however, is minimized by having smaller AC voltage components, which is done by minimizing the voltage ripples and maximum voltage swing [15]. Conduction losses are also affected by the operating frequency, where low frequency results in high peak current which decreases efficiency [10].

#### 2.2.2.2 Switching Loss (Gate Drive Loss)

Gate drive loss, or switching loss, is the energy lost through switching the gate capacitances of the charge-transfer switches at every phase. These losses can be expressed by Equation (2.3), where n expresses the number of switches,  $C_{GSw}$  is the gate capacitance per switch,  $V_{dd}$  is the supply voltage, and  $F_{sw}$  is the switching frequency [17].

$$\boldsymbol{P}_{sw} = \boldsymbol{n} \cdot \left(\frac{1}{2}\right) \cdot \boldsymbol{C}_{GSw} \cdot \boldsymbol{V}_{dd}^{2} \cdot \boldsymbol{F}_{sw}$$

(2.3)

Another expression for switching loss can be derived for on-chip applications, where the switches can be designed differently. In Equation (2.4),  $N_{phase}$  represents the number of phases, n is the number of switches,  $F_{sw}$  is the switching frequency,  $C_{GSw}$  is the gate capacitance per unit width,  $W_{sw}$  is the width of the switch, and  $V_{dd}$  being the supply voltage [12].

$$P_{sw} = N_{nhase} \cdot n \cdot F_{sw} \cdot (C_{GSw} \cdot W_{sw}) \cdot V_{dd}^{2}$$

(2.4)

In this case, it can be seen that the switching losses are dependent on gate capacitance relative to the switch width, which affects both switch resistance and gate capacitance. It is also noted that the effect of the supply voltage is quadratic, giving it significant weight when optimizing. Also, the switching frequency affects both switching power and root mean square resistive conduction loss due to ripple current [18].

#### 2.2.2.3 Parasitic Losses

Parasitic losses comprise mainly of bottom plate capacitance, resulting from use of onchip capacitors which create a capacitance between the plate and the ground bottom plate. The losses occur due to the charging of the bottom plate parasitic capacitance of the charge transfer capacitors every charge cycle [4].

These parasitics are very dominant in on-chip applications, but do not apply to PCB or off-chip converters. Yet, the effects of bottom plate capacitance result in 20% more parasitics at the bottom plate, making the efficiency suffer significantly [8]. It can be observed from Equation (2.5) that parasitic losses are affected linearly by the topology  $M_p$ , the switching frequency  $F_{sw}$ , the bottom plate switching capacitance  $C_{GSw}$ , and the voltage swing on the capacitor  $V_{dd}$  [12].

$$P_{para} = M_p. F_{sw}. C_{GSw}. V_{dd}^2$$

(2.5)

#### 2.2.2.4 Regulation Losses

Regulation losses result from several factors, including the difference between the noload voltage and the loaded voltage. This loss is one of the main limitations to the efficiency in SCVRs. The relationship between energy from the battery to the energy delivered to the load is expressed in Equation (2.6), where  $E_L$  is the energy delivered to the load,  $E_B$  is the energy transferred from the battery,  $V_{NL}$  is the no-load voltage, and  $\Delta V$  is the deviation of the output voltage from the ideal no-load voltage [4].

$$\boldsymbol{E}_{L} = \boldsymbol{E}_{B}.\frac{\boldsymbol{v}_{NL} - \Delta \boldsymbol{V}}{\boldsymbol{v}_{NL}} \tag{2.6}$$

Control circuit power losses are also of concern when delivering ultra-low power levels. There are two components in control power losses, switching and leakage. The switching losses are also referred to as dynamic power losses while the leakage is referred to as static power losses.

#### 2.2.3 Other SCVR Loss Models

One loss model that has become very common when analyzing SCVRs is the one proposed by Seeman, where two limits are described that model the losses depending on the frequency of operation. The two limits, labeled the Slow Switching Limit (SSL) and the Fast Switching Limit (FSL) are characterized by one type of power loss dominating each limit. The low frequency output impedance (Slow switching limit impedance) increases with decreasing switching frequency, which limits the efficiency. It sets the maximum converter power and determines open-loop load regulation properties [19]. The fast switching limit impedance, however, is dominated by the switch on-resistance, interconnect parasitic resistances, capacitor/inductor ESR, and is frequency independent.

The main assumption of this method is two-phase converters; however, it can be applied to multi-phase converters.

#### 2.2.3.1 Slow Switching Limit

The charge flow per period (average current flow) defines the output impedance. The  $R_{SSL}$  is inversely proportional to capacitor size and switching frequency. It can be expressed in terms of capacitor loss, in which the sum of the energy lost through the capacitors is equal to the calculated loss associated with the output impedance for a given load.

#### 2.2.3.2 Fast Switching Limit

The other asymptotic limit is the FSL, where conduction loss dominates due to resistive elements. Capacitors don't reach equilibrium due to resistive losses. The FSL is characterized by the assumption of constant current flow between capacitors. The current in the switches increases with charge increase and with increasing the switching frequency. The R<sub>FSL</sub>is directly related to the on-resistance of the switches and the ESR of the components.

#### 2.2.3.3 Model Limitations

The main limitation to charge sharing losses dominating SSL is that the model assumes constant output voltage due to the existence of an output capacitance. However, if variable output is assumed, much higher efficiency could be allowed [20].

It is shown that the SSL is independent of the switch resistances and represents the summation of  $CdV^2$  over each capacitor in the converter where dV is the voltage swing on each capacitor. However, this SSL loss does not examine the case when the load is fully resistive (ideal load), where the output resistance is simply the switch resistance. As the switch resistance approaches 0, the losses are mathematically eliminated; this contradicts the concept that SSL resistance is independent of switch resistance.

As a result, it can be inferred that if the output voltage is not assumed constant, higher efficiency can be reached, but with increased output voltage ripples. It can be found from Equation (2.7) that increasing the output voltage ripples  $r_{output}$  increases efficiency by decreasing the output resistance.

$$R_{output} = R_{FSL} + \left(1 - \frac{r_{output}}{r_{max}}\right) \cdot R_{SSL}$$

(2.7)

This means that as output ripples approach the maximum ripples, the  $R_{SSL}$  decreases significantly and could be eliminated. On the other hand, at high values of load capacitance, all ripples disappear and the losses saturate to exactly the SSL specified by Seeman.

\_\_\_\_\_

# 2.2.4 Benefits and Drawbacks of SCVRs

The main advantage to using SCVRs is their ease of integrability when it comes to onchip applications, since they do not use inductors, which are generally more complex in on-chip applications. This allows higher integration capability at a relatively small area footprint, which is dominated by the capacitors. Techniques to design more area efficient capacitors using multiple layer parallel plates can be used in order to further reduce the effective area of SCVRs, and result in better overall integrability.

Yet, the shortcomings of traditional SCVRs lie in their inefficient power conversion, with their parasitics having a significant effect due to the charging and discharging losses. Traditional SCVRs also include extra control overhead, which generates high switching losses since there are generally many switches necessary for driving in order to obtain several output voltages.

# 2.2.5 Applications of SCVRs

SCVRs are most commonly found in on-chip applications due to their relatively simple integrability. They are also implemented in high voltage up-conversion in very specific automobile applications, where the inductor size requirements for an inductor-based converter would be too high, and a SCVR would be a more area efficient design. Nevertheless, SCVRs dominate on-chip DC-DC converters since new enabling technologies have allowed higher quality factor on-chip capacitors, which lead to better efficiencies, as opposed to inductor-based converters which are limited by low quality factor on-chip inductances.

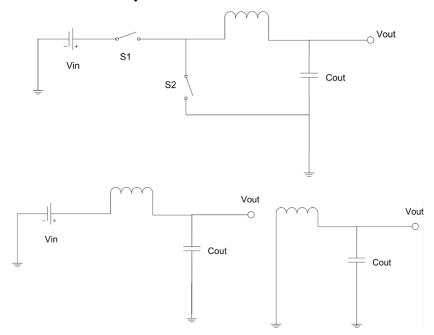

# 2.3 Buck Converter

The Buck converter, however, is an inductor-based DC-DC converter. It is more common for off-chip applications because it provides smaller overhead circuitry and lower control circuit power. It generally provides much higher efficiency than a SCVR, with the cost being the large area of the inductor [8]. Buck converters operate by alternating between two phases, one where the input voltage is connected directly to the load through an inductor, and the second phase where the circuit is closed with only the inductor in series with the load, as shown in Figure 2.6. During the first phase, the inductor is charged with current which is discharged in the second phase. The active switching element connecting the ground to the inductor which is turned on in

the second phase can be composed of a diode or a MOSFET transistor. Diodes have been used for simplicity in driving the signal, as well as for blocking any excess charge in the output capacitor from flowing back through the inductor at low load currents. Also, MOSFETs have been used in order to minimize the voltage drop caused by the high threshold voltage of the diodes (and the high on-resistance). Using a switch also allows higher efficiency, with the drawbacks being more complex circuitry, inefficiency at low load currents, and increased power lost in the control circuit. Instead of requiring a single clock source to drive the diode-based buck converter, a MOSFET-based buck converter requires two non-overlapping clock sources, as well as customized controllers to prevent current flowing from the output capacitor back through the inductor.

Depending on the load current, the Buck converter has two modes of operation: Continuous Conduction Mode (CCM) and Discontinuous Conduction Mode (DCM). In CCM, the voltage conversion ratio of the buck converter is equal to the duty cycle of the controller. As the duty cycle decreases, lower conversion ratios are attainable but at decreased efficiency. In the DCM mode of operation, the conversion ratio depends on the load, which means that the duty cycle affects the conversion ratio nonlinearly [11]. During DCM, losses caused by reflected current degrade the overall efficiency.

Figure 2.6. Conventional buck converter (top) operating in two phases, phase 1 (bottom left) and phase 2 (bottom right).

Several techniques to optimize the Buck converter exist, which aim to achieve higher performance by implementing small modifications to the existing design. For instance, one method aimed at applications with high currents and low voltages implements a synchronous MOSFET as a replacement for the diode found in regular buck converters. This aims to significantly reduce conduction losses, as MOSFETs have lower resistance than diodes with a high forward voltage. The MOSFETs in the bottom and top switches can then be driven using simple MOSFET drivers [21].

#### 2.3.1 Control Mechanisms

Buck converters are regulated by control methods such as duty cycle modulation and frequency modulation. Each of the mentioned control techniques is described in further detail in the following sections.

# 2.3.1.1 Buck Duty Cycle Modulation

Buck converters generally dominate duty cycle modulation since it is the main technique used in most Buck converters. Changing the duty cycle of the input voltage with respect to the ground voltage allows dynamic voltages and conversion ratios. This technique allows very high efficiency to be maintained over all voltage conversion ratios, assuming low load current. Varying the duty cycle allows variation of the output voltage while maintaining the same output signal form and frequency, which minimizes control circuit complexity, making it a more favorable control mechanism. However, there are also some limitations to the control signal's simplicity that need to be addressed.

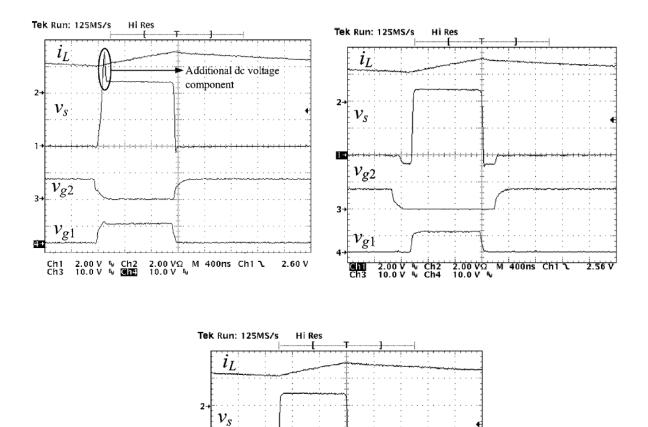

#### **2.3.1.2 Dead-time**

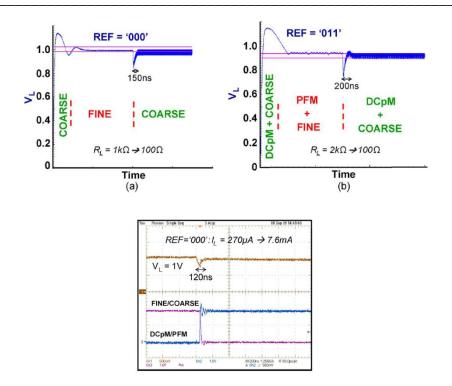

A crucial factor in voltage regulator control circuits is the dead-time algorithm used. Dead-time algorithm circuits prevent two switches from overlapping when they should not, which causes current spikes due to short circuit between the supply and the ground. This is done by providing a small period of time between switching two switches, instead of switching them both simultaneously. Without deadtime, some cases consist of the control signal containing non-overlapping signals, while the MOSFET drivers would have some variable delay, which would be the main cause of the short-circuit current spikes. In that case, dead-time compensation is

required to avoid the detrimental effects to the efficiency. Figure 2.7 shows the effect of deadtime elimination on current spikes, and how it improves the efficiency.

Figure 2.7. Insufficient deadtime added to signals (top left), excessive deadtime added to signals (top right), optimized deadtime added to signals (bottom) [22].

2.00 V % Ch2 2.00 VΩ 10.0 V % Ch4 10.0 V %

$v_{g2}$

Dead-time algorithms have been shown to improve efficiency by up to 12% in experimental prototypes [22]. Yet, increasing the dead-time between signals is only useful until the efficiency saturates, and increasing the dead-time further than that point results in decreased efficiency if the time is too high. As a result, dead-time is measured or analyzed based on

knowledge of the control signal variation, the MOSFET driver delay variations, and the cycle period.

#### 2.3.2 Buck Converter Loss Model

As for the Buck converter, the loss model includes much less components due to decreased complexity and decreased number of capacitors and switches. This allows reduced parasitics, allowing higher efficiency with the cost being the addition of a high quality factor inductor, which limits metrics other than the efficiency. Yet, some sources of losses remain the same also for the Buck converter, such as the conduction losses caused by the switch resistances and inductor ESR, the switching losses (gate drive losses) caused by the driving the switches, and the control circuitry losses.

In high load currents, power losses in a buck converter are dominated by conduction losses, where  $I_{load}$  is high enough to cause major losses in the parasitic resistances [23]. In moderate loads, however, the losses are dominated by the VI overlap and the current ripple induced conduction losses. This is generally the dominant source of loss in most buck converters. At very light loads, the power losses are dominated by gate drive losses, also called switching losses.

Another model suggested in [18] is that the output voltage of a Buck Converter is bound by Equation (2.8), where the duty cycle D, input voltage  $V_{in}$ , load resistance  $R_{load}$ , switch onresistance  $R_{on}$ , and inductor parasitic resistance  $R_{ind}$ , are all significant.

$$V_{out-DC} = D.V_{in}.\frac{R_{load}}{R_{load} + R_{ind} + R_{on}}$$

(2.8)

As a result, these parasitics and components are necessary for proper analysis and design for buck converters in order to accurately predict the output voltage. Yet, the Buck Output Voltage Equation assumes continuous mode operation using a synchronous rectifier that does not include a diode.

For further optimization, it is clear from Equation (2.9) that the ripple current,  $\Delta I$ , is proportional to voltage swing before the inductor  $V_{swing}$ , and inversely proportional to the switching frequency  $f_{sw}$  and the inductance L [18].

$$\Delta I = \frac{V_{swing}.D.(1-D)}{f_{sw}.L} \tag{2.9}$$

Therefore, in order to decrease the ripple currents, and in turn increase the efficiency, it is necessary to decrease the voltage swing before the inductor. That is possible by using switched-capacitor circuits to change the output level between two topologies. A hybrid topology would also combine the advantages of both the SCVR and the Buck Converter.

#### 2.3.3 Benefits and Drawbacks of Buck Converters

The buck converter has several advantages over the traditional SCVR, and of course some limitations. First, the buck converter is able to achieve much higher efficiencies, due to its simple design and control overhead circuitry. It is also relatively simple to implement because its components are mostly accessible. However, this comes with the limitations of its component size, due to the large inductor needed for obtaining high conversion efficiency. As it is discussed earlier, obtaining high conversion efficiency requires high switching frequency, a large inductor, and minimized voltage swing. The only factor that cannot be manipulated by traditional buck converters is the voltage swing, which constitutes a significant limitation.

# 2.3.4 Applications of Buck Converters

The buck converter's simple design and loss model have proven useful, as it is dominating the off-chip DC-DC converter industry. The high efficiency obtained with minimal overhead makes its advantages appealing for use in power electronics applications such as power supplies in most, if not all, mobile and portable devices.

Buck converters can be found in a majority of battery powered devices, since power conversion efficiency is a key criterion for power supply units in order to maximize battery life. They are dominant due to their simplicity in implementation with minimal control, since a square wave can be used to drive the converter and achieve very high efficiency, with the variation in output voltage being dependent on the duty cycle. Accordingly, the simplest DC-DC converter available for power supplies with high performance requirements is the buck converter, with its limitations being its significantly large area when compared to other converters.

# 2.4 Traditional Converters Comparison

A comparison is therefore necessary to evaluate the relative benefits of each type of converter and how it surpasses the performance of the other converter. This also clarifies the criteria for evaluation, and how an improved topology for future DC-DC converters is necessary for the improvement of the power electronics industry. A concise comparison of the key features found in both converters and how they differ is found in Table 2.1.

Table 2.1. Performance comparison between traditional SCVRs and Buck converters

| Criterion              | Switched Capacitor<br>Converters | <b>Buck Converters</b> |  |  |

|------------------------|----------------------------------|------------------------|--|--|

| Maximum Efficiency     | Limited                          | High                   |  |  |

| Area Requirements      | Low                              | High                   |  |  |

| Integrability          | Simple                           | Complex                |  |  |

| Control Overhead       | High                             | Low                    |  |  |

| Output Voltage Ripples | Low                              | High                   |  |  |

# 2.5 Hybrid Converters

Both the SCVR and buck converters suffer from limitations in their loss models that force designers to seek a more advanced hybrid design that avoids their limitations and combines the advantages of each converter.

The main advantage of the SCVR is its ability to be integrated easily on-chip, with very small area. It also provides flexibility in conversion ratio by switching between topologies, making it a dynamic voltage regulator. However, it suffers from limited efficiency and significant parasitics. The Buck converter, however, is very efficient with very minimal overhead circuitry. However, it requires large area for the high Q inductor and suffers from large voltage ripples caused by the high current ripples. The high integrability, combined with high efficiency, is possible by combining both topologies into a hybrid.

# 2.5.1 Hybrid Converter Topologies

Despite the fact that a hybrid combining the integrability and small voltage ripples of SCVRs, and the high efficiency of Buck Converters seems like a far-fetched possibility, it is possible to combine two converter stages to obtain relatively important advantages from both converters while eliminating most disadvantages.

A hybrid converter composed of a switched-capacitor in the first stage coupled with a low pass filter in the second stage has been proposed in [24] that aims to eliminate the SSL output impedance described by Seeman, as well as allow several other benefits. A 3-Level Buck converter was also introduced in [25] that combines a capacitor with a buck converter to optimize the efficiency by decreasing the voltage ripples at the inductive stage. The result is a reduced inductor size, which minimizes the total area consumed by the converter compared to a traditional buck converter, as well as the high efficiency associated with buck converters.

If the inductor current ripples are very small, the multi-level converter has up to multiple times higher switch conduction losses. However, if inductor current ripples are more significant (in low voltage applications) the switch conduction loss in the multi-level converter can be similar to or less than that of a standard buck converter.

The 3-Level Buck, shown in Figure 2.8, also allows decreased voltage swing, which increases efficiency at the expense of control circuit complexity and very few additional components. The first stage output voltage is shown in Figure 2.9 to highlight the decreased voltage ripples, which are averaged by the inductor to provide a smoother, more efficient output. The efficiency of the ideal VR is inversely related to the output voltage ripple [17]. Therefore, decreasing the output ripples allows higher efficiency.

Figure 2.8. 3-Level Buck Converter.

The first stage operates by utilizing the switches and the capacitor to output a voltage that is a fraction of the Buck output voltage, while combining it with the full voltage output, in order to reduce the ripples. The second stage eliminates the noise, providing a suitable output voltage, while maintaining high efficiency. Results have indicated significant improvements in output voltage ripples, as is shown in the comparison in performance in Figure 2.9 [25].

Figure 2.9. 3-Level Buck Converter Output ripples vs. Conventional Buck output ripples [25].

An extended concept that would be implemented in hybrid converters is that of the multi-level multi-state hybrid converter, where the output of the switched-capacitor stage alternates between two levels. This requires a switched-capacitor circuit with the ability to output several voltage outputs by changing the configuration, and in return, the conversion ratio [26]. Introducing a series inductor to the SC converter provides adiabatic charging of the energy

transfer capacitors, which eliminates SSL loss. We use small inductors to obtain high conversion efficiency. Overall, this enhances SCVR efficiency by simply adding a low Q inductor [27].

The requirements for such a converter to operate efficiently are that the minimum Q (Quality Factor) for the inductor is 0.5 for optimal operation, and the frequency to exceed a certain damping frequency. Equations (2.10), (2.11), and (2.12) demonstrate the minimum frequency requirements for proper functionality of the hybrid converter [24].

$$W_0 = \frac{1}{\sqrt{LC}} \tag{2.10}$$

$$W_D = W_O \sqrt{1 - \frac{1}{4Q^2}} \tag{2.11}$$

$$f_{SW} > f_D \tag{2.12}$$

Operating at a frequency near or below the damping frequency  $f_D$  creates a difficulty for the operation of the converter due to the LC time constant being smaller than the period, when proper operation requires that multiple switching periods occur within one LC period to prevent the LC circuit from damping. Therefore, operating properly eliminates the SSL loss for frequencies higher than the damped frequency. This allows functionality in the FSL region at a lower frequency, which results in higher efficiency. Adding the inductor has a similar effect as increasing the flying capacitor size (capacitance), however merely a small inductor is needed for that effect.

The implementation of a control signal could be simply by alternating between two voltages with each voltage level comprising of two or more phases, yet an interesting technique is used in [26] where the 4 phases of each voltage level are interleaved, which provides many benefits including increased frequency at the inductor and reduced current ripples at the output.

# 2.5.2 Ultradynamic Voltage Regulation

Obtaining a wide range of output voltages for a DC-DC converter is important for a converter that is implemented targeting dynamic voltage scaling applications. This is simply implemented by an LDR or a Buck converter, but the conversion efficiency drops significantly

as the conversion ratio increases. Accordingly, it is important to find a converter that tackles this challenge. A hybrid converter presents a topology that allows a wide range of conversion ratios

along with high efficiency throughout that range.

Several techniques can be also used to obtain different conversion ratios based on a reference voltage. It is also possible to track changes in the load current, which cause small changes in the load voltage. For instance, a load-dependent technique is used in [23] to maintain high efficiency over diverse load ranges using mode-hopping. The technique also makes use of hysteretic control, in order to regulate the output voltage while adapting to changes in the current ripples; the result is optimized and minimized conduction and switching losses.

# 2.5.2.1 Hysteretic Control Limitations

Some limitations apply to the control circuit, such as hysteresis, which significantly affects most of the regulation techniques. Inaccurate hysteresis calculation for frequency or topology modulation could have very detrimental effects on the overall converter efficiency. This could occur due to increased instability, resulting from oscillations between two topologies, or two frequencies. The efficiency would not only decrease, but the voltage ripples at the output would also increase significantly.

Therefore, the solution becomes increasing the hysteretic value enough to prevent oscillations, while at the same time avoiding slow response time. The responsiveness of a converter to slight changes in the reference voltage is an important factor to consider. Hence, it is required for an ultradynamic converter to have minimal response time to changes in the reference voltage, and to changes in the output voltage resulting from different load currents.

# 2.6 Chapter Summary

Seeing as the conversion efficiency is one of the main metrics of a DC-DC converter, the sources of power loss are of interest to maximize performance. The buck converter and switched-capacitor converter both have very different sources of losses, and are therefore modeled differently. Power losses result from several factors, including device parasitics, control signals, and inherent topology limitations. The comparison presented shows the different advantages each converter has over the other. Yet, a method to achieve all the advantages is

necessary to meet the industry requirements for an efficient, small converter, to keep up with the trend. The hybrid converter has been presented and discussed, with emphasis on its voltage ripple reduction. The 3-Level hybrid buck converter topology is explored, and its advantages are demonstrated. It is proposed that exploration of other hybrid topologies will lead to further optimization of DC-DC converters, and would allow a design that combines the advantages of the traditional converter types.

# Chapter 3

# DESIGN OF A HIGH POWER 5-LEVEL 8-STATE HYBRID VOLTAGE REGULATOR

#### 3.1 Introduction