### MODELING AND DESIGN FOR ENERGY-EFFICIENT SPINTRONIC LOGIC DEVICES AND CIRCUITS

A Dissertation Presented to The Academic Faculty

by

Rouhollah Mousavi Iraei

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Electrical and Computer Engineering

> Georgia Institute of Technology August 2018

### COPYRIGHT © 2018 BY ROUHOLLAH MOUSAVI IRAEI

# MODELING AND DESIGN FOR ENERGY-EFFICIENT SPINTRONIC LOGIC DEVICES AND CIRCUITS

Approved by:

Dr. Azad Naeemi, Advisor School of Electrical and Computer Engineering *Georgia Institute of Technology*  Dr. Phillip First School of Physics *Georgia Institute of Technology*

Dr. James Kenney School of Electrical and Computer Engineering *Georgia Institute of Technology*  Dr. Zhigang Jiang School of Physics *Georgia Institute of Technology*

Dr. Jeffrey Davis School of Electrical and Computer Engineering *Georgia Institute of Technology*

Date Approved: May 3, 2018

For my family and friends

#### ACKNOWLEDGEMENTS

I would like to thank Dr. A. Naeemi, my advisor, for giving me the opportunity to join his group and pursue research in the field of nanoelectronics and spintronics. His guidance helped to develop me into the researcher and the engineer I am today. Moreover, I enjoyed exploring new science under the supervision of two knowledgeable and intelligent physicists Dr. Z. Jiang and Dr. P. First who taught me how to be a scientist and a researcher. Also, I would like to express my gratitude to Dr. J. Kenney and Dr. B. Ferri for their support and mentoring, which helped me to develop my teaching skills. Moreover, I would like to thank Dr. R. Poproski, Dr. K. Williams, and Dr. D. Lawrence at the Center for Teaching and Learning (CTL) at Georgia Tech who taught me how to be a good mentor and instructor.

My special thanks go to Dr. I. Young, Dr. D. Nikonov, and S. Manipatruni at Intel Components Research for their insightful guidance and discussions. In addition, I would like to express my gratitude to Dr. E. Afshari. Dr. H. Aghasi, and J. Heron from the University of Michigan for their collaboration and support. Moreover, I enjoyed mentoring five brilliant undergraduate students (W. Scott, J. Geoffrey, B. Heard, V. Tanguturi, Y. Zheng) at the school of Electrical and Computer Engineering of Georgia Tech, and I would like to thank them for their hard work and accomplishments. Furthermore, I would like to thank my previous and current group members at the Nanoelectronic Research Lab of Georgia Tech for their support.

Finally, I would like to thank my family and friends for their understanding, patience, and all the love they have given me during all these years.

### **TABLE OF CONTENTS**

| ACKNOWLEDGEMENTS                                                            | iv          |

|-----------------------------------------------------------------------------|-------------|

| LIST OF TABLES                                                              | viii        |

| LIST OF FIGURES                                                             | ix          |

| I. Spintronic Devices: Applications and Challenges                          | 1           |

| 1.1 Motivations                                                             | 1           |

| 1.1.1 Boolean Logic Applications                                            | 1           |

| 1.1.2 CMOS-Spintronic Transducers, Spintronic Interconnects, and Me         | •           |

| Applications                                                                | 4           |

| 1.1.3 Non-Boolean Logic Applications                                        | 5<br>5      |

| <b>1.2</b> The Operation of Spintronic Devices                              | 5           |

| 1.2.1 Spin Current: Generation and Transport                                | 5           |

| 1.2.2 Magnetization Switching                                               | 8           |

| <b>1.3</b> Thesis Overview                                                  | 11          |

| II. The All-Spin Logic Device, Its Performance Analysis and Adder and       | nd Coupled  |

| Oscillator Implementation                                                   | 17          |

| 2.1 All-Spin Logic Device: Applications and Challenges                      | 17          |

| 2.2 Modeling and Benchmarking of All-Spin Logic                             | 20          |

| 2.2.1 The Operation of All-Spin Logic                                       | 20          |

| 2.2.2 The Modelling of the Thermal Noise of Magnets                         | 22          |

| 2.2.3 Size Effects                                                          | 24          |

| 2.3 Applications                                                            | 29          |

| 2.3.1 ASL Adders                                                            | 29          |

| 2.3.2 ASL Oscillators and Coupled-Oscillators                               | 31          |

| 2.4 Conclusions                                                             | 37          |

| III. Image Recognition Circuit Using All-Spin Logic Devices                 | 39          |

| 3.1 Non-Boolean Applications of All-Spin Logic Device                       | 39          |

| 3.2 All-Spin Logic Majority Gate                                            | 41          |

| 3.3 Pattern Recognition Scheme                                              | 44          |

| 3.3.1 Mainly Similar Images                                                 | 44          |

| 3.3.2 Majority Training and Decision Making                                 | 46          |

| <b>3.4</b> Proposed Structure and Design Considerations                     | 46          |

| 3.4.1 Memory+Logic Comparator                                               | 47          |

| 3.4.2 Construction of the mean pixel                                        | 49          |

| 3.4.3 Single Pixel Comparator                                               | 50          |

| 3.4.4 Non-Boolean Row Decision-Maker                                        | 55          |

| 3.5 Simulation Results                                                      | 57          |

| 3.5.1 Non-Boolean Hamming Distance Identifier of $3 \times 3$ Pixel Pattern | 1 and Input |

| Image 57                                                                    |             |

| 3.5.2 Non-Boolean Similarity Comparison of a $9 \times 9$ Pixel Image and a Set | of Three |

|---------------------------------------------------------------------------------|----------|

| Pattern Images                                                                  | 59       |

| 3.6 Conclusions                                                                 | 64       |

| IV. Electrical-Spin Transduction and Long-Range Spintronic Interconnects        | s 66     |

| 4.1. Signal Transduction and Transfer for Spintronic and Magnetic Circu         | uits 66  |

| 4.2. CMOS- to Spintronic-Signal Transduction                                    | 67       |

| 4.3. Spintronic- to CMOS-Signal Transduction                                    | 70       |

| 4.4. ASL Transducer for Long-Spintronic Interconnects                           | 74       |

| 4.4.1 Performance Analysis of ASL Repeaters                                     | 74       |

| 4.4.2 Proposed Long-Range Spintronic Interconnect                               | 82       |

| 4.5. Conclusions                                                                | 88       |

| V. Magnetostriction-Assisted All-Spin Logic Device                              | 90       |

| 5.1. Magnetostriction-Assisted All-Spin Logic (MA-ASL) Device Proposa           | l 90     |

| 5.2. Device Operation                                                           | 92       |

| 5.3. 32-Bit MA-ASL ALU                                                          | 98       |

| 5.4. Clocked MA-ASL                                                             | 101      |

| 5.5 Material Analysis of MA-ASL Device                                          | 105      |

| 5.5. Conclusions                                                                | 108      |

| VI. Hybrid Piezoelectric-Magnetic Neurons: A Proposal for Energy-Efficient      | nt       |

| Machine Learning                                                                | 110      |

| 6.1 Spintronic Artificial Neural Networks                                       | 110      |

| 6.2 Spin Neuron Proposal                                                        | 112      |

| 6.2.1 Neuron Functionality                                                      | 112      |

| 6.2.2 The Transient Response of the Neuron                                      | 115      |

| 6.2.3 Integration into Neural Network                                           | 116      |

| 6.3 Benchmarking Against Competing Technologies                                 | 117      |

| 6.4 Conclusions                                                                 | 119      |

| VII. Magnetostriction-Assisted Spin-Orbit Device                                | 120      |

| 7.1.1 Motivations                                                               | 120      |

| 7.1.2 Rashba Effect                                                             | 122      |

| 7.1.3 Spin-Hall Effect                                                          | 124      |

| 7.2 Magnetostriction Assisted Spin-Orbit (MASO) Logic Device Proposa            |          |

| 7.2.1 Device Proposal                                                           | 127      |

| 7.2.2 The Modelling of the MASO Device                                          | 131      |

| 7.2.3 The Transient Response of the MASO Device                                 | 133      |

| 7.3 Optimizing the Performance of the Device                                    | 135      |

| 7.4 Performance Analysis of the Device                                          | 140      |

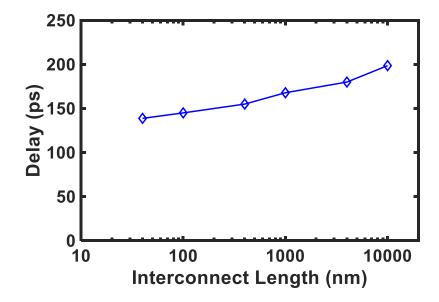

| 7.4.1 Using the Device as an Interconnect                                       | 140      |

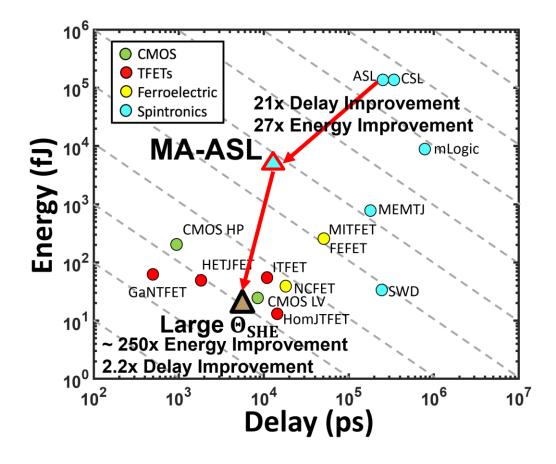

| 7.4.2 Benchmarking the Performance of the MASO Device Against CMOS a            |          |

| Spintronic Alternatives                                                         | 141      |

| 7.5 Conclusions                                                                 | 143      |

| VIII. Conclusion and Outlook                                                    | 145      |

| 8.1 ( | Conclusion                                          | 145 |

|-------|-----------------------------------------------------|-----|

| 8.2 I | Future Works                                        | 149 |

| 8.2.1 | Non-Boolean Logic Application of Spintronic Devices | 149 |

| 8.2.2 | Signal Transduction and Long-Range Interconnects    | 151 |

| 8.2.3 | The MASO Device                                     | 152 |

| REFER | ENCES                                               | 154 |

### LIST OF TABLES

| Table 1: Performance comparison of the ASL ring oscillator with CMOS oscillators 33                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 2: Performance Comparison with Existing CMOS Systems    64                                                                                 |

| Table 3: Simulation Parameters for the long-range spintronic interconnect.       81                                                              |

| Table 4: Simulation Parameter for the MA-ASL Device.    95                                                                                       |

| Table 5: Performance Comparison of MA-ASL Neuron against its CMOS and Spintronic         Counterparts.         118                               |

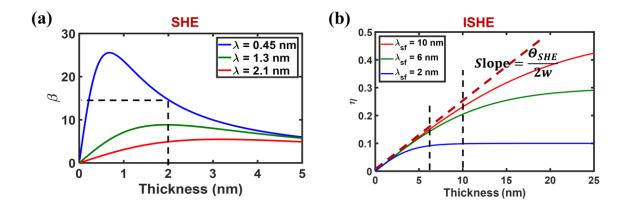

| Table 6: The spin to charge conversion efficiency of various materials are compared by comparing $\lambda_{IREE}$ and $\Theta_{SHE}\lambda_{sf}$ |

| Table 7: Comparison of the transferred strain to the magnet and spin-hall angle for Pt, Ta, and W.         137                                   |

| Table 8: Resistivity and $\Theta_{SHE}$ for various heavy metallic elements, topological insulators(TIs), magnets, and nonmagnetic metals        |

## LIST OF FIGURES

| Figure 1: To improve the performance of FET transistors, various technologies are investigated over the past five decades                                                                                                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2: Electronic spins, pseudo-spins in graphene, and excitons are some of the novel state variables studied for beyond-CMOS logic devices                                                                                                                                                                                                          |

| Figure 3: Several spintronic devices are proposed, such as the all spin logic (ASL) device, the composite-input magnetoelectric-based logic technology (COMET), the domain wall magnetic logic (mLogic), and the magnetoelectric spin-orbit device                                                                                                      |

| Figure 4: Illustration of spin-dependent Hall effects used in spin current generation and detection. In the SHE, an unpolarized charge current generates a transverse spin current, while in the ISHE, a spin current generates a transverse charge current. In the anomalous Hall effect (AHE), a charge current generates a transverse charge current |

| Figure 5: Binary information is stored as the magnetization orientation along the two stable directions along the easy axis of the magnet                                                                                                                                                                                                               |

| Figure 6: Spin-transfer torque explained in a spin valve                                                                                                                                                                                                                                                                                                |

| Figure 7: (a) 90° magnetostrictive switching is experimentally demonstrated. (b)<br>Compared to 180° magnetization reversal via applying STT, 90° switching of a magnet<br>via STT from the saddle-point of energy profile is demonstrated to be two orders of<br>magnitude more delay and energy efficient                                             |

| Figure 8: To model the physics of the all-spin logic device, magnetization dynamics, spin mixing conductance, and spin-drift diffusion in the channel are taken into account [81].18                                                                                                                                                                    |

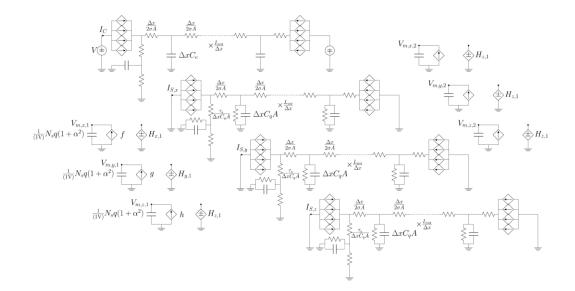

| Figure 9: ASL circuit model 19                                                                                                                                                                                                                                                                                                                          |

| Figure 10: ASL consists of two magnets connected by a non-magnetic channel. Injected spin current from Input magnet to the channel diffuses along the channel and applies a torque to the output magnet, which if strong enough, switches the output magnet                                                                                             |

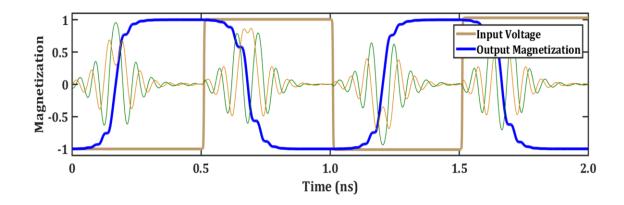

| Figure 11: Transient Response of an all-spin logic device. In this simulation, the input magnet is assumed to be oriented in the $+X$ direction. By applying a negative voltage, the device acts as a buffer, while by applying a positive voltage, the device acts as an inverter. 22                                                                  |

| Figure 12: LLG equation describes the magnetization dynamics. The corresponding vectors to the terms of LLG equation are represented in this figure                                                                                                                                                                                                     |

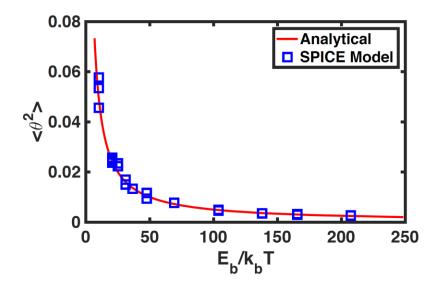

| Figure 13: To validate the SPICE model of the thermal noise, the derived average value of the thermal noise over time of the SPICE model, is compared to that of the analytical solution. SPICE results match with analytical results                                                                                                                                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

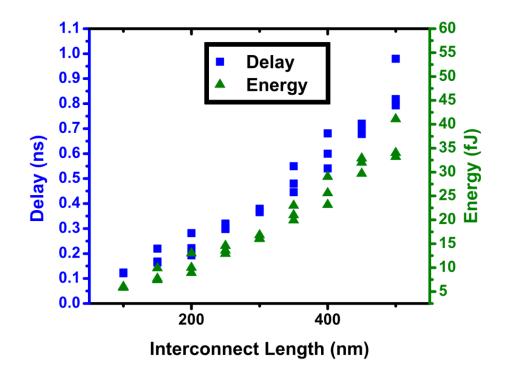

| Figure 14: Delay and energy dissipation vs channel length of an ASL gate                                                                                                                                                                                                                                                                                                                                                              |

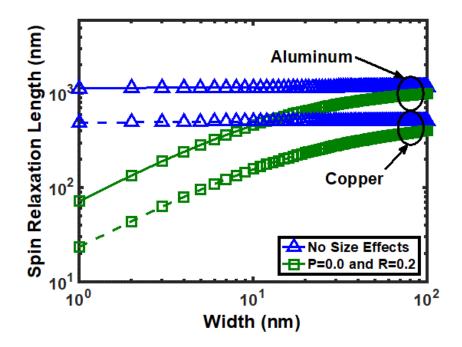

| Figure 15: Spin Relaxation versus channel Width. Size effects cause the spin relaxation length to decrease with decreasing channel width. For the no size effect case, spin relaxation length is independent of channel width                                                                                                                                                                                                         |

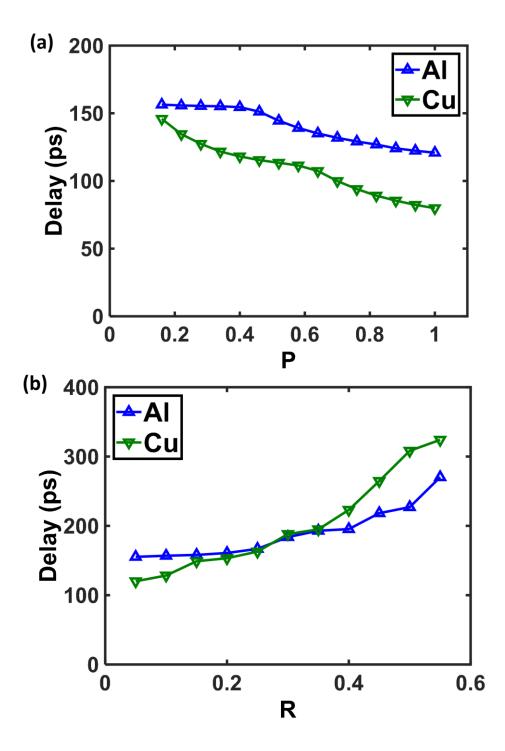

| Figure 16 : (a) Delay versus specularity parameter, P, for an 80 nm long channel. Grain boundary scattering parameter, R, is assumed to be 0.2 (b) Delay versus grain boundary reflection probability for an 80nm long channel. The specularity parameter, P, is assumed to be 0                                                                                                                                                      |

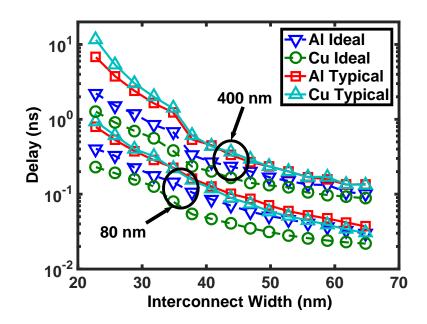

| Figure 17: Delay versus channel width for 80 nm and 400 nm long channel                                                                                                                                                                                                                                                                                                                                                               |

| Figure 18: Implementation of a full adder using two majority-not gates                                                                                                                                                                                                                                                                                                                                                                |

| Figure 19: (a) Schematics and (b) layout of the ASL full adder. (c) The transient response of an ASL full-adder. The blue color represents the magnetization orientation in the x-direction and the green and red colors are representing magnetization in the y and z directions                                                                                                                                                     |

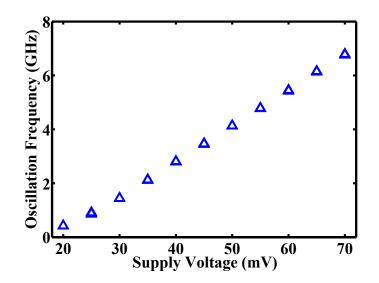

| Figure 20: Oscillation frequency versus supply voltage. The oscillation frequency increases linearly with increasing the supply voltage                                                                                                                                                                                                                                                                                               |

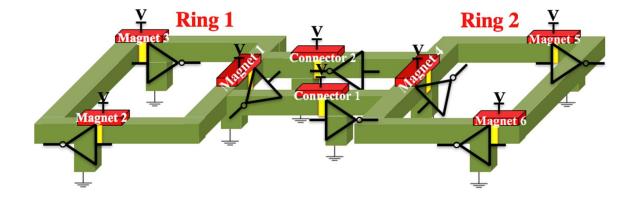

| Figure 21: (a) Two metallic channels are connecting two ASL ring oscillators to form the ASL coupled oscillator. The oscillation of the two rings will be coupled to each other if the oscillation frequencies of two oscillation loops are close to each other                                                                                                                                                                       |

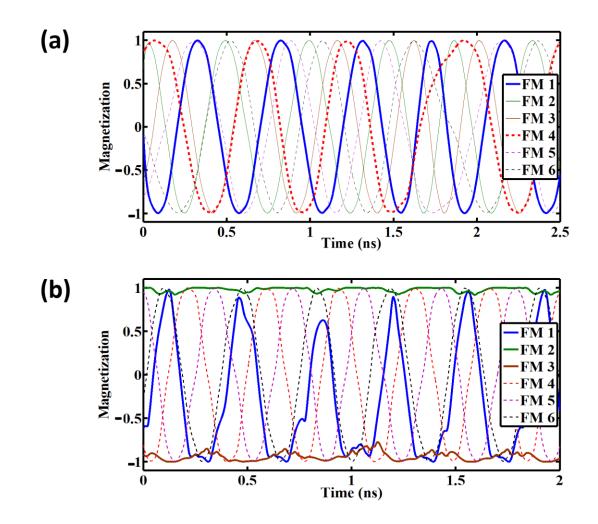

| Figure 22: The voltage applied to the magnets of the ring 1 is 35 mV. In (a), the voltage applied to the magnets of the ring 2 is 10 mV higher than the voltage applied to the ring 1, while in (b), the voltage applied to the ring 2 is 20 mV higher than the voltage applied to the ring 1                                                                                                                                         |

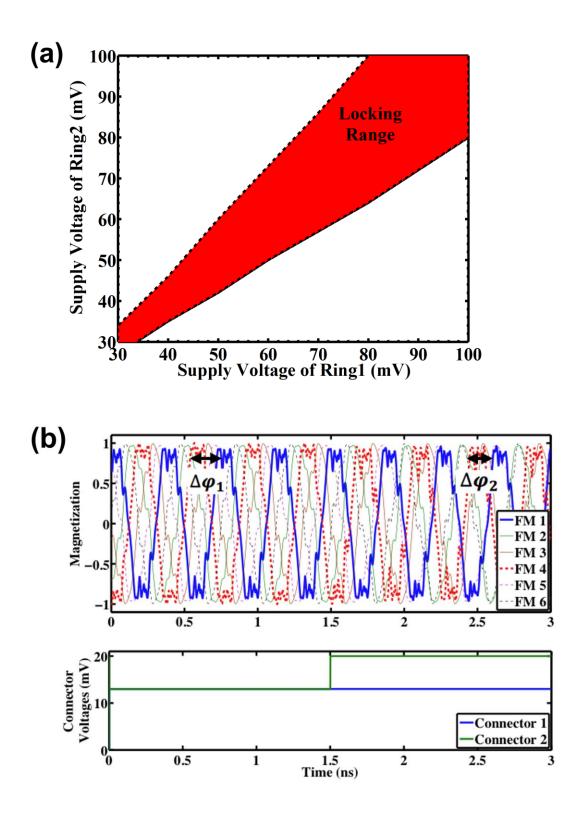

| Figure 23: (a) The supply voltage applied to the ASL connector 2 is changed from 12.5 mV to 20 mV. As a result, the phase shift of the two rings is changed from $\Delta\phi_1$ to $\Delta\phi_2$ in which $\Delta\phi_1 > \Delta\phi_2$ . (b) Locking range of the ASL coupled oscillator. The shaded region shows the region where the supply voltages of rings are different, but the two rings will show a locked oscillation. 36 |

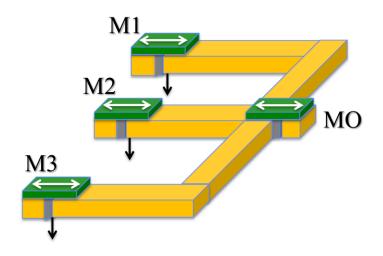

| Figure 24: An ASL Majority gate with three inputs. The three input magnets, M1, M2 and M3 are connected to the output magnet, MO, using three metallic channels                                                                                                                                                                                                                                                                       |

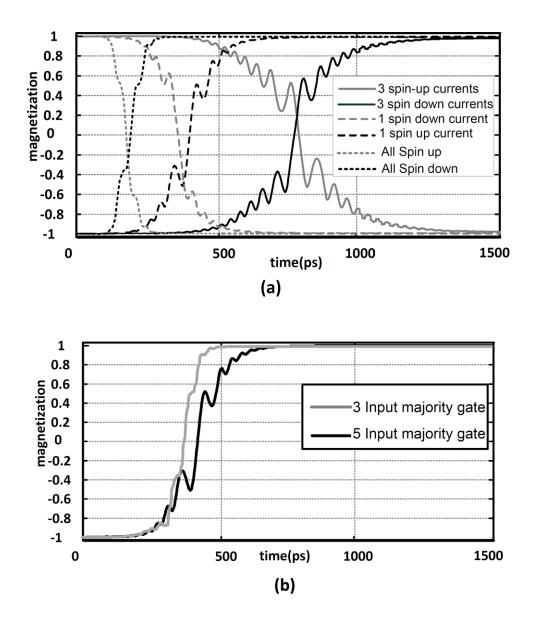

| Figure 25: (a) Switching transient response for different scenarios of input magnetization in a majority gate with 5 inputs. (b) Switching transition comparison of majority gates with three and five inputs. In this comparison, the input magnetization of magnets of                                                                                                                                                              |

| three input gates are the same. For the gate with five inputs, four inputs have similar magnetization and the net spin current is equal to the other gate. The applied voltage on magnets in these simulations is $-5$ mV.                                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

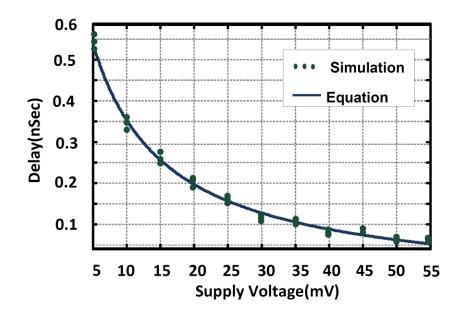

| Figure 26: Switching delay variation versus the supply voltage. Each voltage is simulated three times to verify the results                                                                                                                                                                                                                                                                |

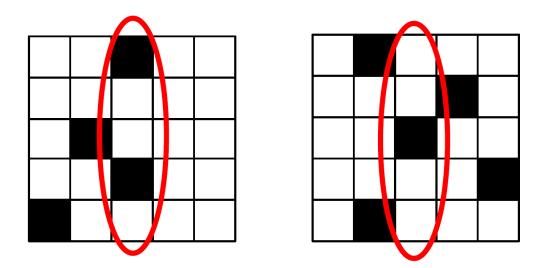

| Figure 27: The two images are mainly similar (along the rows), however, the Hamming distance between the third columns is 3 which does not imply a similarity along the columns                                                                                                                                                                                                            |

| Figure 28: 1-bit full adder used as XNOR. In the 2D implementation of this work, X and Y wires are in-plane metal wires and connections along the Z axis are vias                                                                                                                                                                                                                          |

| Figure 29: Simulated output waveforms of XNOR gate 49                                                                                                                                                                                                                                                                                                                                      |

| Figure 30: (a) Standard single pixel detector schematic. (b) The truth table with the detailed operation of the circuit                                                                                                                                                                                                                                                                    |

| Figure 31: (a) Comparator-first pixel detector schematic. (b) The truth table with the detailed operation of the circuit                                                                                                                                                                                                                                                                   |

| Figure 32: Structure of the unit smart detector cell                                                                                                                                                                                                                                                                                                                                       |

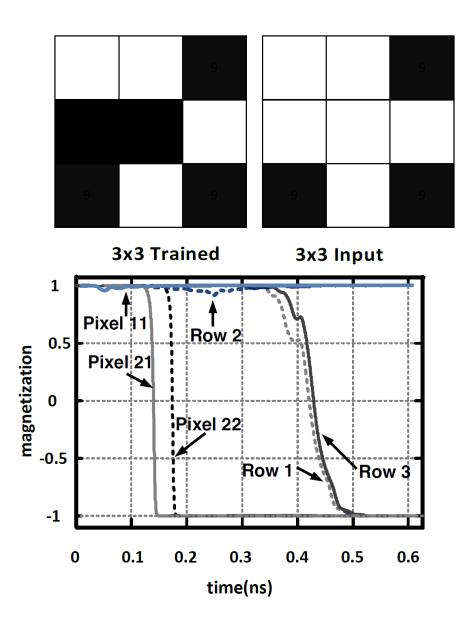

| Figure 33: Using a single smart detector cell, we can compare these $3 \times 3$ pixel images.<br>The waveforms of the comparators and majority gates (bottom)                                                                                                                                                                                                                             |

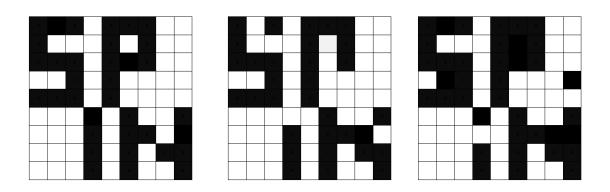

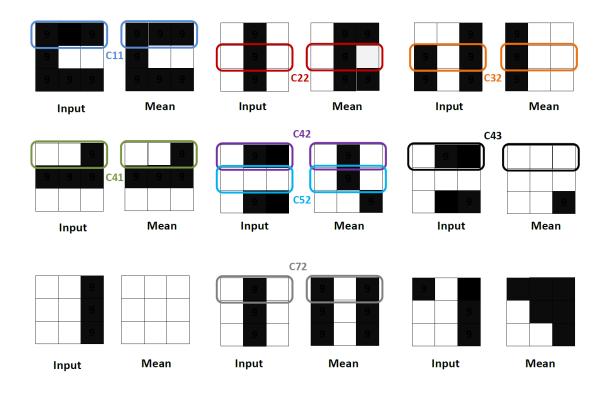

| Figure 34: Training set for the $9 \times 9$ pixel images                                                                                                                                                                                                                                                                                                                                  |

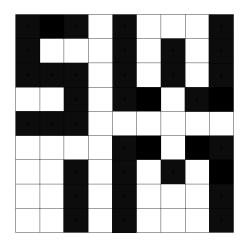

| Figure 35: The input image (left) and the representation of the mean image (right). The mean image is not a direct output of the circuit                                                                                                                                                                                                                                                   |

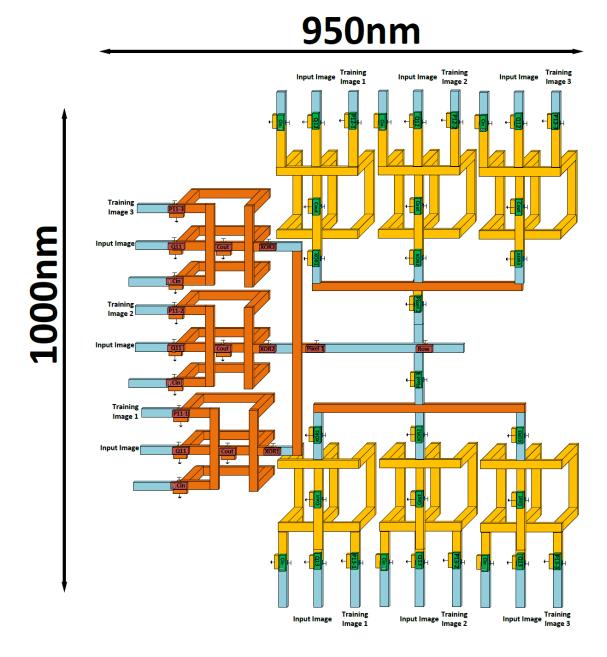

| Figure 36: Due to fan-in considerations, the circuit is consisted of 9 smart detector cells. The corresponding breakdowns of the mean image and the input image are shown here.62                                                                                                                                                                                                          |

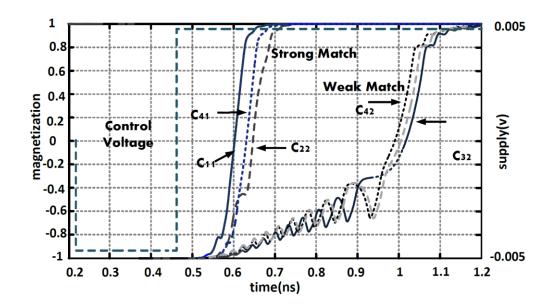

| Figure 37: The switching delay of output magnetization in last stage represents the similarity of input data and pattern data                                                                                                                                                                                                                                                              |

| Figure 38: For the cases of mismatch in clusters, magnets will not switch and the initial magnetization does not change. The y-axis shows a range from -1.002 to -0.998 in contrast with Figure 37 in which the range is from -1 to 1                                                                                                                                                      |

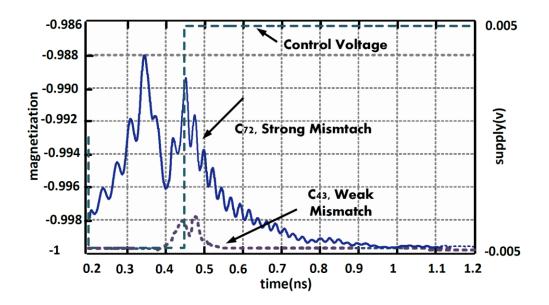

| Figure 39: Electrical signal to spin signal transducer: (a) schematics of the transducer. (b) Input signal ( $V_{DATA}$ ), which switches the polarity of the voltage applied to the fixed magnet, which switches the output magnet accordingly. The orientation of the output magnet follows the input signal with a delay of 1.6 ns and 2.0 ns for high-to-low and low-to-high switching |

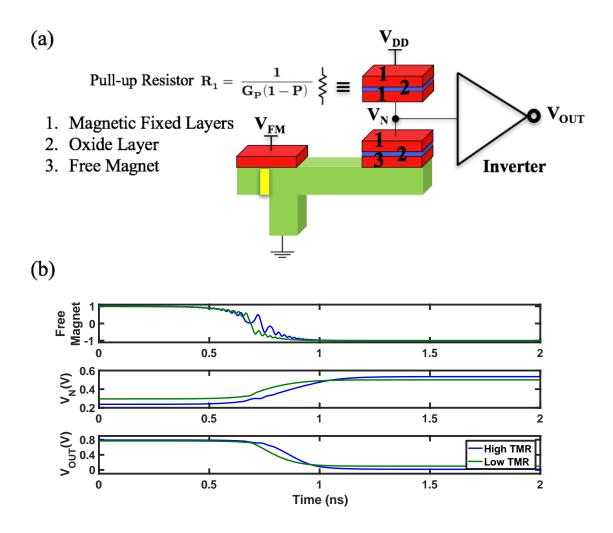

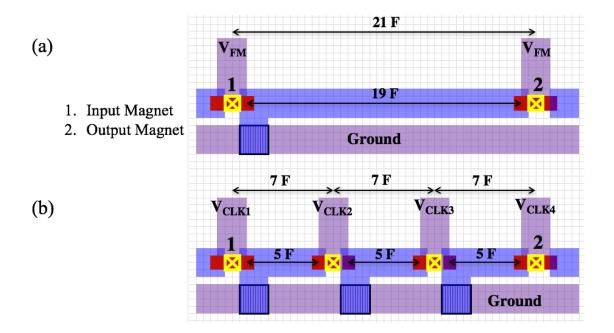

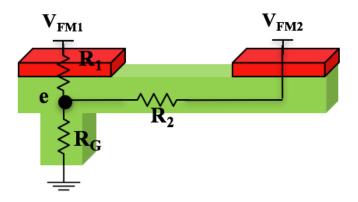

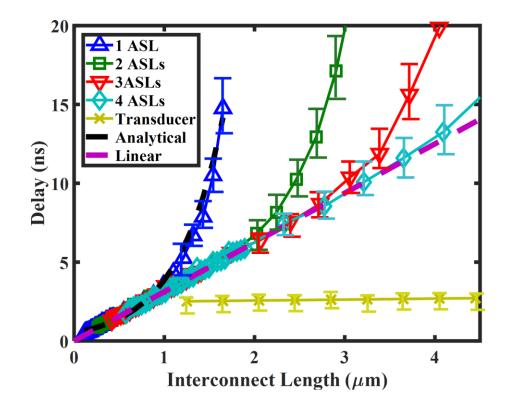

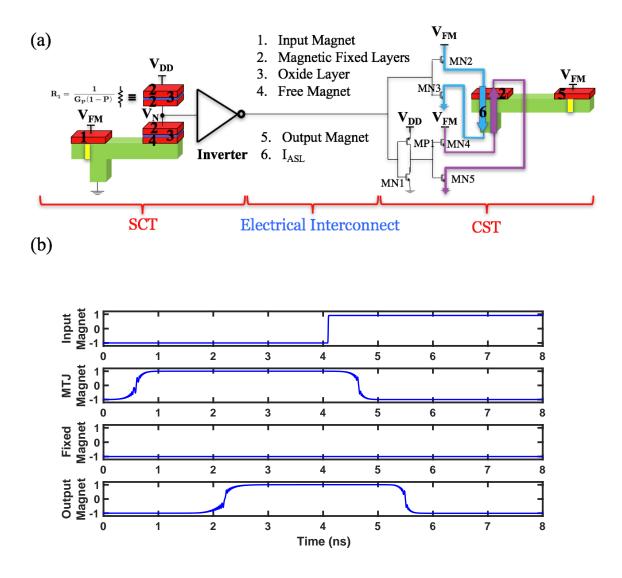

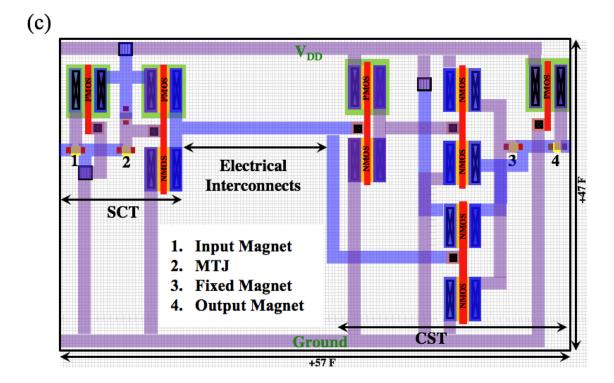

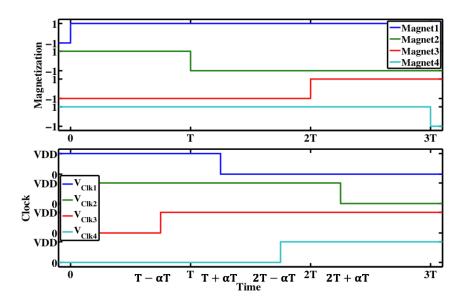

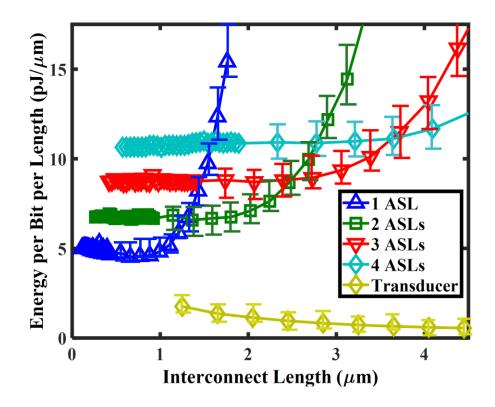

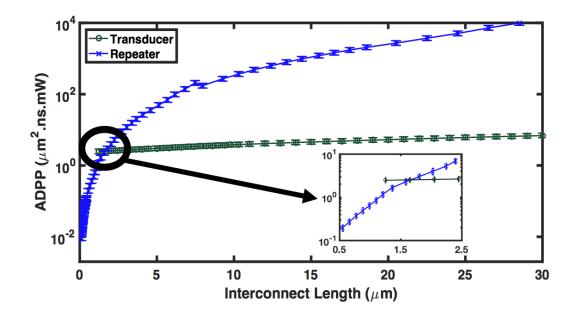

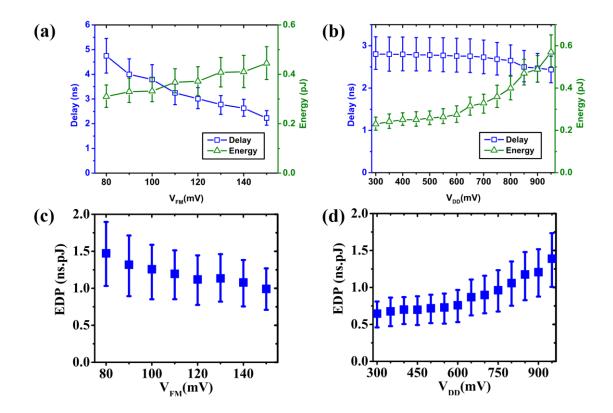

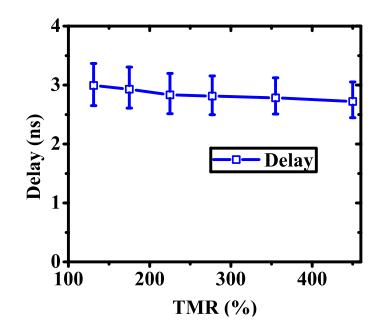

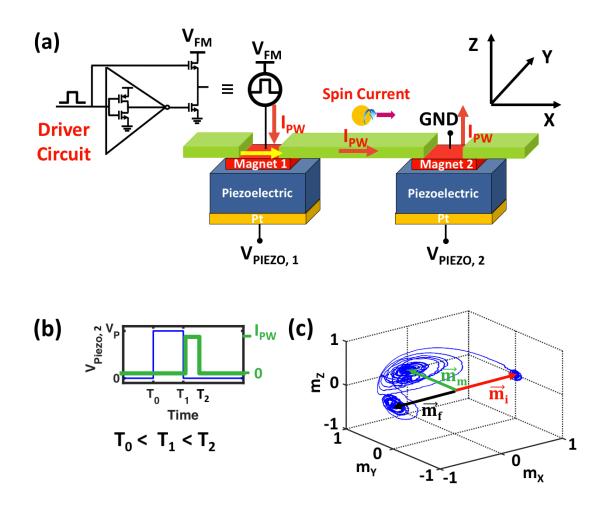

Figure 40: Spin signal to electrical signal transducer: (a) schematics of the transducer. (b) the changes in the orientation of the free magnet are translated into changes in electrical voltage on the node V<sub>N</sub>. The inverter provides a full swing between the ground and supply voltages at accordingly. Simulations are done for two TMR values of 131% (low TMR) and 355 % (high TMR)......71 Figure 41: (a) Layout of an ASL gate that transfers spin signals through a metallic interconnect, (b) layout of ASL gates in a cascaded structure, which is a solution to transfer spin signals in long interconnects. The meaning of colors is defined in [33]. .... 73 Figure 42: ASL gate modeled by a star network of resistors for calculating the electrical current passing through the input magnet......74 Figure 43: Delay of ASL repeaters is compared to that of electrical communication of spin information through transduction. For long lengths, the delay of ASL gates increases exponentially with length as predicted by the analytical equation. Meanwhile, for short lengths, the delay increases linearly because the linear terms of the Taylor expansion of delay are dominant. Similarly, the delay of ASL repeaters increases linearly with LInt for short lengths and exponentially for long lengths. Although with multiple ASLs, the linear region is extended, the delay of the electrical interconnect is still shorter than that Figure 44: Proposed long spintronic interconnect. (a) First, the spin signals are converted to electrical signals using a spin to CMOS signal transducer (SCT); then, the electrical signal is transmitted through a long electrical interconnect and converted back to spin signals using a CMOS to the spin signal transducer (CST). (b) The magnetization orientation of the output magnet is the inverse of the magnetization orientation of the input magnet with a delay of 1.6 ns. (c) The layout consists of two transducers with Figure 45: Clocking schemes used to minimize the energy dissipation of the ASL repeaters. Clocks are on  $\alpha T$  before and after the mean switching time to cancel the Figure 46: Energy dissipation per unit length of the ASL repeaters is compared to that of the proposed spintronic interconnect. The dissipated energy of the proposed interconnect is lower than that of repeaters even for  $L_{Int}$  as small as 1.25 µm. Although the energy dissipation of repeaters increases as the number of cascaded ASLs for short interconnects increases, but the repeaters with more cascaded ASLs dissipate lower power for long Figure 47: Area-delay-power product (ADPP) is a measure that takes delay, power dissipation, and area into account. Although the proposed interconnect has larger area overhead, its advantage in terms of energy enables it to outperform ASL repeaters for

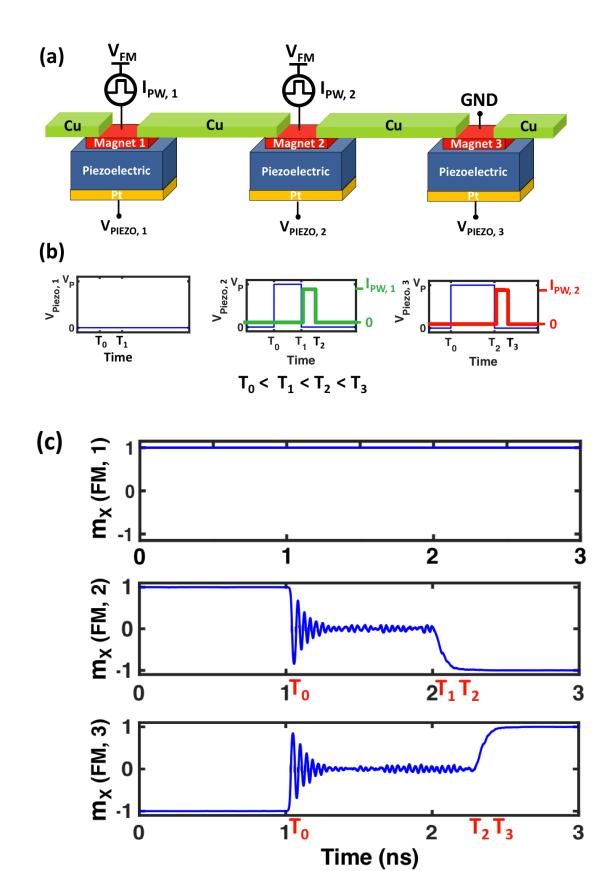

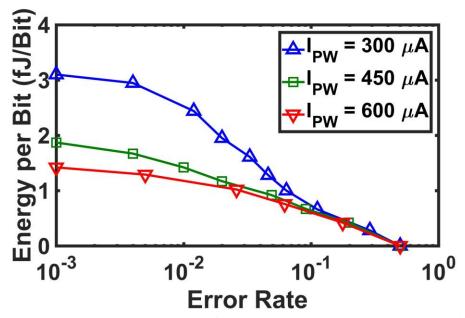

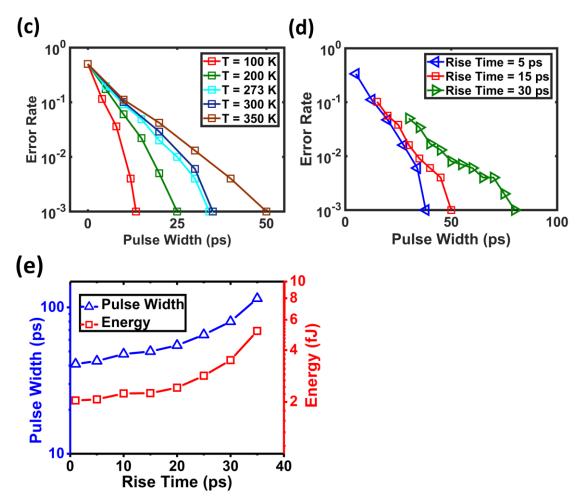

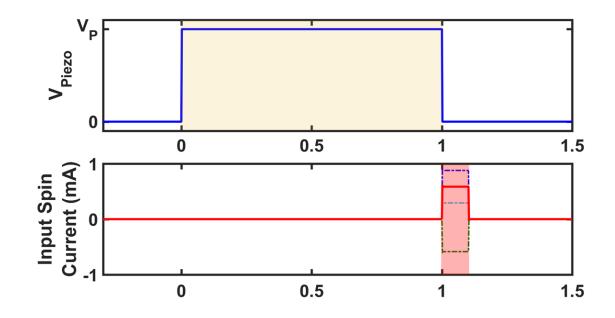

| Figure 56: (a) Definition of pulse skew. (b) The required pulse width to reach to an error rate of $10^{-3}$ for various pulse skews in an MA-ASL inverter. Positive compared to negative pulse skew, has more impact on increasing pulse width. Error rate vs pulse width for various (c) temperatures and (d) rise times. (e) The pulse width and energy to reach to an error rate of $10^{-3}$ for various rise times. The pulse skew is assumed to be -5 ps in Figures (c), (d), and (e)                                                                                              |

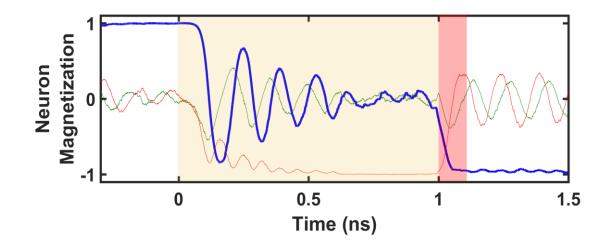

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

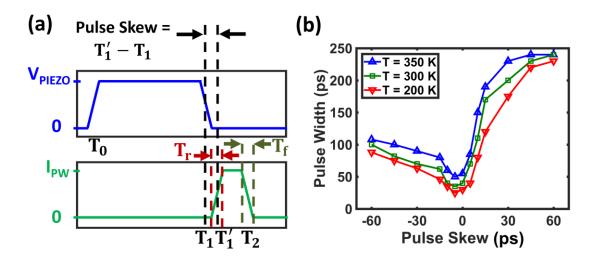

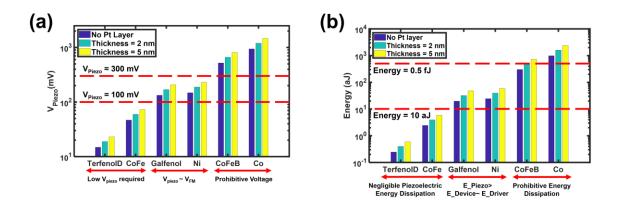

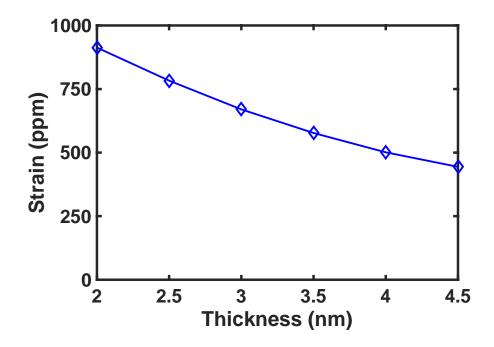

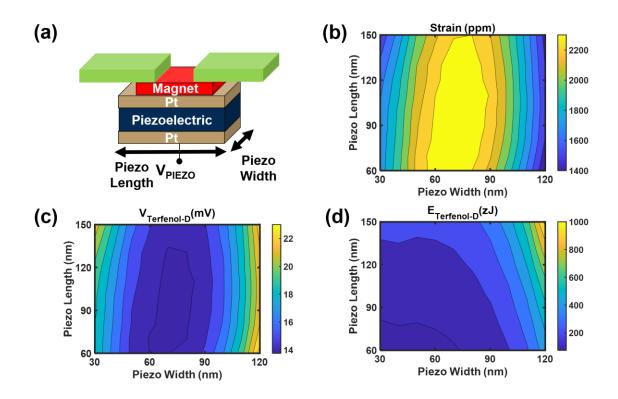

| Figure 57: (a) voltage and (b) energy required to transfer a net strain of 1200 ppm to the magnetic layer. Simulations are done for various magnetic materials, in which Terfenol-D demonstrated lowest required voltage and energy dissipation for transferring strain. Moreover, the figure compares the transferred strain for various piezoelectric thickness values. 106                                                                                                                                                                                                             |

| Figure 58: Transferred strain to the magnet vs the thickness of the Pt layer between the piezoelectric and magnetic layers                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Figure 59: Analysis on the transferred strain vs geometrical dimensions of the piezoelectric layer. (a) definition of piezoelectric dimensions. (b) Transferred strain at a constant $V_{PIEZO}$ voltage of 100 mV. The required (c) voltage and (d) energy to transfer a net strain of 1200 ppm                                                                                                                                                                                                                                                                                          |

| Figure 60: One of the most popular applications of machine learning algorithms is image classification and facial recognition                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

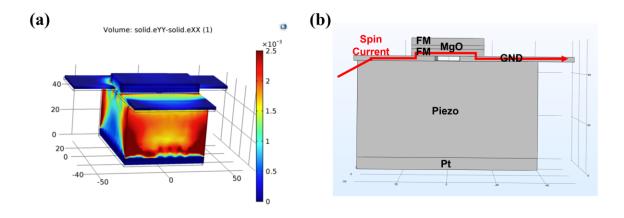

| Figure 61: (a) Transferred strain to the magnet is 800 ppm, lower than that to an MA-ASL magnet; however, the transferred strain is enough to rotate the magnetization. (b) shows the path of applied spin current through the output magnet to ground                                                                                                                                                                                                                                                                                                                                    |

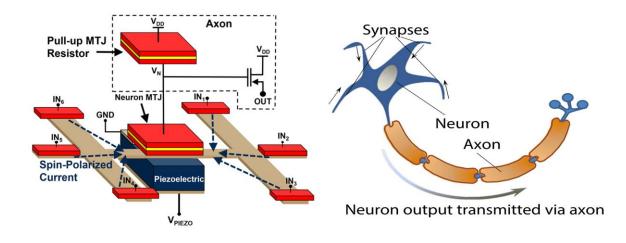

| Figure 62: (a) Proposed MA-ASL neuron, shown with six inputs. The net spin current in the interconnect applies STT to the free layer of the neuron MTJ in timing with the piezoelectric clock, switching the orientation of the neuron output. (b) Biological neural network [164]                                                                                                                                                                                                                                                                                                        |

| Figure 63: Transient response of the MA-ASL device. In the first phase of operation, $V_{PIEZO}$ turns on for 1 ns as shown in the first graph. The second graph illustrates the second phase of operation, in which STT is applied to the output magnet through the injected net spin current (in blue) from three input magnets (shown with dotted lines), applied after $V_{PIEZO}$ turns off. The third graph shows the magnetization of the output magnet (x, y, and z axes shown in blue, red, and green, respectively) and how it is affected by $V_{PIEZO}$ and the spin currents |

| Figure 64: Memristive cross-bar network. The cross-bar array sums together the input currents, abbreviating the number of magnets needed for the output neurons                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 65: Spin-orbit interactions are very strong in heavy metallic elements 121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

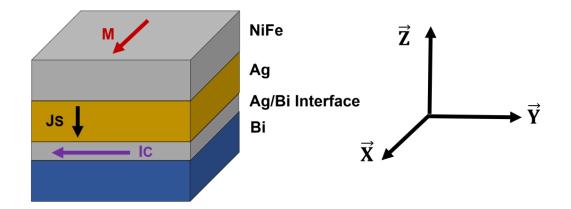

| Figure 66: A Rashba interface comprised of a hybrid NiFe/Ag/Bi structure 122                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Figure 72: First, the orientation of Magnet 2, rotates by 90 <sup>0</sup> from $m_i$ to $m_m$ using |

|-----------------------------------------------------------------------------------------------------|

| magnetostrictive switching; then, it reorients by 90 <sup>0</sup> from $m_m$ to $m_f$ using SHE 134 |

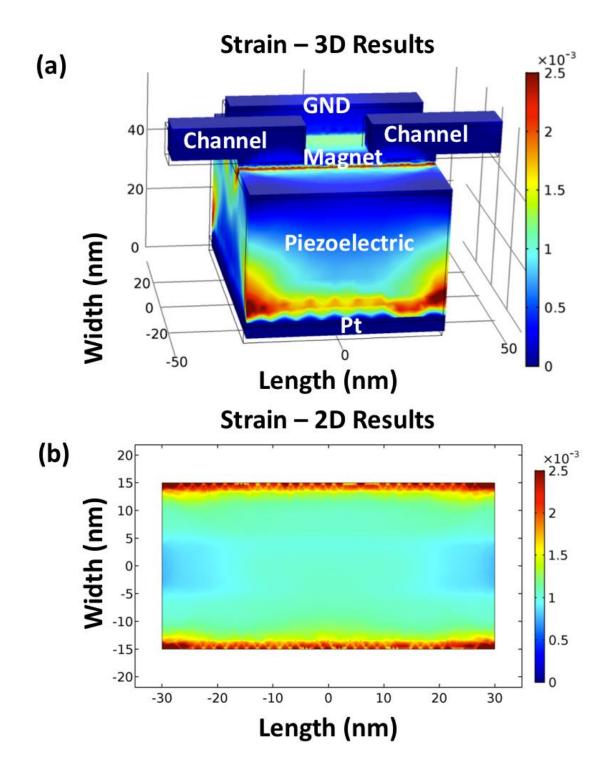

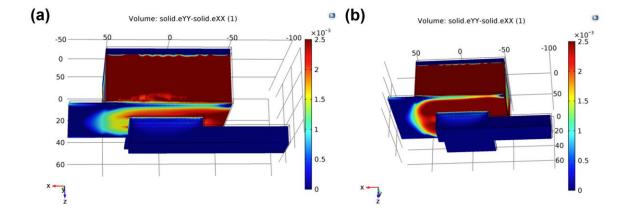

| Figure 73: Transferred strain to the magnet is simulated using COMSOL, and the resu | ılts |

|-------------------------------------------------------------------------------------|------|

| are shown for the cross-section of the magnet                                       | 136  |

|                                                                                     |      |

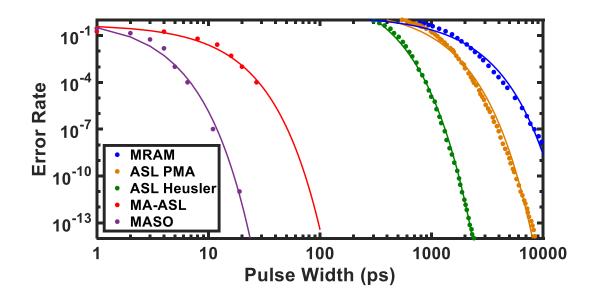

| Figure 76: Write error statistics of the MASO device vs. the ASL device, the MA-AS | SL  |

|------------------------------------------------------------------------------------|-----|

| device, and the STT-MRAM.                                                          | 142 |

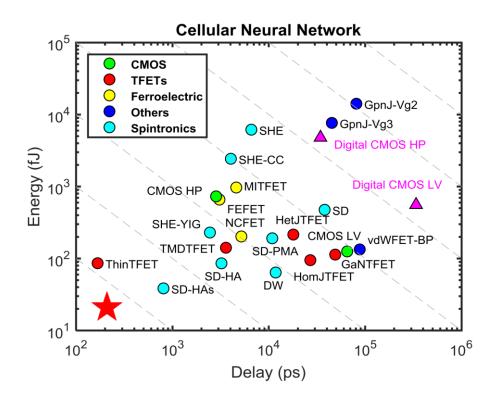

| Figure 78: Energy versus delay per memory association operation using CNN for a       |     |

|---------------------------------------------------------------------------------------|-----|

| variety of charge- and spin-based devices, where the red star indicates the preferred |     |

| corner                                                                                | 150 |

|                                                                                       |     |

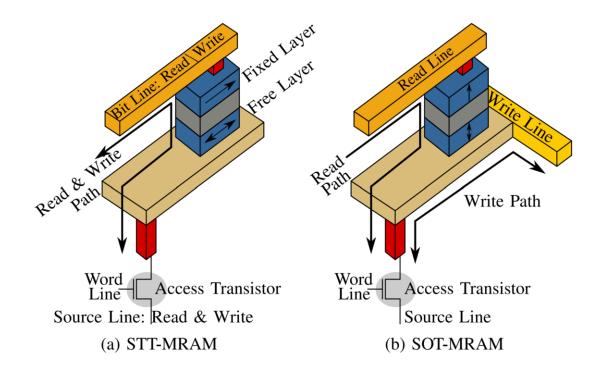

| Figure 79: Bit-cell for STT-MRAM and SOT-MRAM.                                        | 151 |

## I. SPINTRONIC DEVICES: APPLICATIONS AND CHALLENGES

#### 1.1 Motivations

#### 1.1.1 Boolean Logic Applications

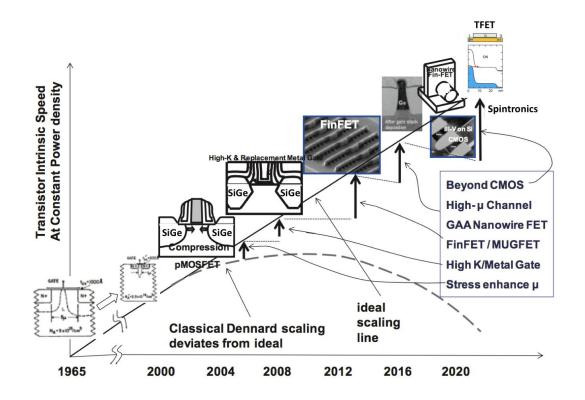

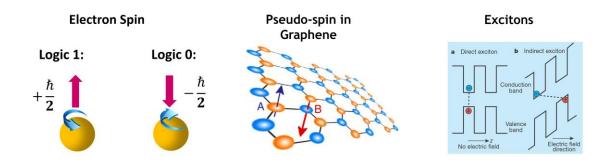

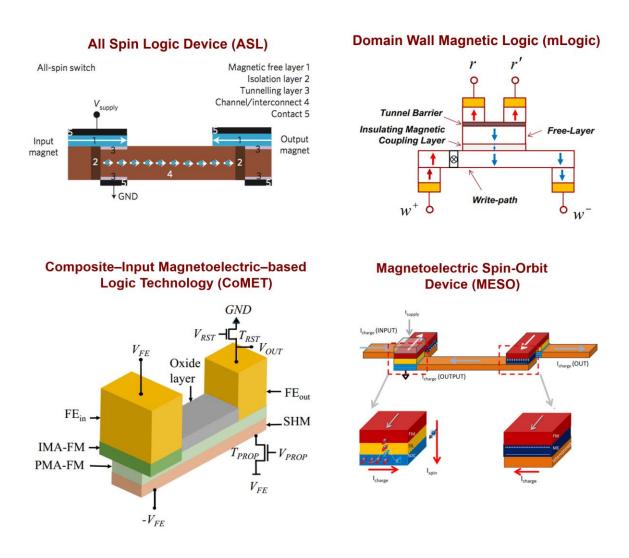

Over the past half-century, the computational throughput and the memory storage of integrated electronic circuits have improved exponentially mainly through the downscaling of the geometrical dimensions of field-effect transistors (FETs) [1]. Sustaining this trend is becoming more and more challenging as CMOS devices approach their scaling limits [2], [3]. To address this challenge, researchers have investigated various materials including high-k dielectrics such as hafnium silicate ( $HfO_4Si$ ), hafnium dioxide ( $HfO_2$ ), zirconium silicate ( $ZrO_4Si$ ), and zirconium dioxide ( $ZrO_2$ ) [4]–[17] and developed various FET technologies such as Fin field-effect transistor (FinFET) [18]-[20], (Figure 1). Moreover, researchers are investigating beyond-CMOS devices that use state variables other than the electric charge of electrons such as the spin of electrons, pseudo-spins, and excitons [1], [3], [21]–[23], (Figure 2). By employing electronic spin as the binary logic, spintronic devices gained special attention thanks to their potential advantages in terms of non-volatility and low operating voltage [24]-[26]. Several spin-based logic devices are proposed including the all spin logic (ASL) device [27], the composite-input magnetoelectric-based logic technology (COMET) [28], the domain wall magnetic logic (mLogic) [29], the magnetoelectric spin-orbit device [30], and the magnetoelectric magnetic tunnel junction (MEMTJ) [31]. Moreover, the energy efficiency, computational

speed, and chip area of these logic devices are studied [32]–[39]. Spintronic logic devices excel in implementation of logic functionalities using fewer devices because of their efficient implementation of majority gates. However, these devices compared to their CMOS counterparts, are slower and less energy efficient, due to the inefficiencies in magnetization switching and spin current generation and detection. Thus, more research must be done in developing novel spintronics devices to enhance the energy efficiency and the operational speed to realize efficient, novel devices that take advantage of non-volatility and offer new and enhanced applications.

Figure 1: To improve the performance of FET transistors, various technologies are investigated over the past five decades.

Figure 2: Electronic spins, pseudo-spins in graphene, and excitons are some of the novel state variables studied for beyond-CMOS logic devices [40], [41].

Figure 3: Several spintronic devices are proposed, such as the all spin logic (ASL) device [27], the composite-input magnetoelectric-based logic technology (COMET)

[28], the domain wall magnetic logic (mLogic) [29], and the magnetoelectric spin-orbit device [30].

## 1.1.2 CMOS-Spintronic Transducers, Spintronic Interconnects, and Memory Applications

Like CMOS logic devices, CMOS-based dynamic random access memories (DRAMs) face similar limitations in maintaining a significant growth rate [42]. These devices experience an increase in power consumption by scaling down their size because of the increase in charge leakage. To lower energy consumption, non-volatile memories that would not consume static power are studied. By offering non-volatile data storage, magnetic random-access memories (MRAMs) are widely studied to replace the purely semiconductor-based memory technologies. Moreover, spin transfer torque MRAMs [43]-[46] (STT-MRAMs) are used in embedded memories. Thus, enhancing the performance of hybrid systems of CMOS devices and magnetic memories requires energy-efficient and fast CMOS-spintronic interface circuits that can write binary CMOS data into magnets and read the binary data, stored as the magnetization orientation. Moreover, energy-efficient interface circuits are required to improve the performance of hybrid CMOS-spintronic logic circuits as well. Furthermore, interface circuits might improve the performance of large spintronic logic circuits by providing a more energy-efficient long-range interconnect scheme that works based on the conversion of spin signals into electrical signals, transferring signals in electrical interconnects, and converting signals back into spin signals. The interconnects will benefit from the conservation of electrical charge, unlike spintronic interconnect [47], [48], which will suffer from losing data due to spin relaxation

mechanism. Researchers have examined CMOS-spintronic interface circuits and proposed some read and write circuits for STT-MRAMs as wells as sense amplifiers to read MRAMs, but these circuits are mostly suitable when a large, complicated circuit reads many magnetic tunnel junctions (MTJs). Thus, more studies must be done in the cases of signal transductions that using sense amplifiers causes prohibitive energy and area overhead.

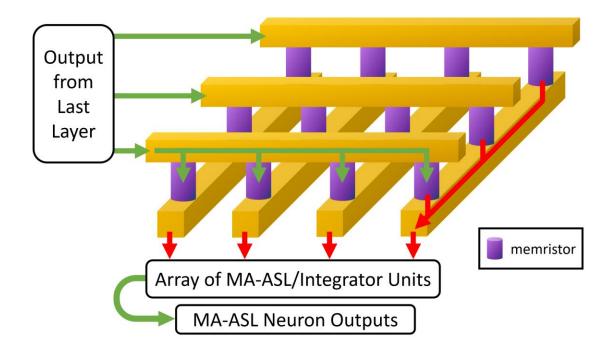

#### 1.1.3 Non-Boolean Logic Applications

In addition to Boolean logic, memory, and interconnection applications [49]–[52], spintronic device are studied for applications such as non-Boolean computing, machine learning circuits, image recognition [53], [54], and cellular neural network (CNN) [55] and shown lower energy consumption and simpler implementations compared to their CMOS counterparts. Furthermore, because of non-volatile memory, spintronic devices do not require additional memory circuits to store patterns in pattern recognition systems or synaptic weights for communicating neurons. Various spintronic neuron implementations are proposed that use tunnel magnetoresistance (TMR) in MTJs coupled with other spintronic phenomenon such as domain-wall (DW) motion, STT, and spin-Hall effect (SHE). However, advances in magnetic materials and spintronic devices in non-Boolean logic computations, which must be studied by researchers. In the next section, physical phenomena and formalisms governing the operation of spintronic devices is investigated.

#### **1.2** The Operation of Spintronic Devices

#### *1.2.1* Spin Current: Generation and Transport

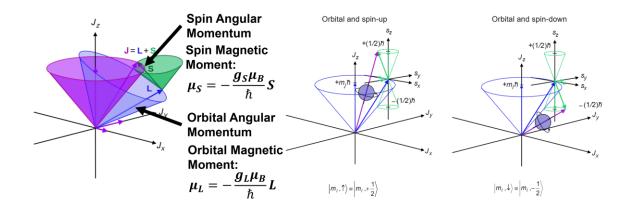

As discussed in the previous sections, spintronic devices rely on the spin of electrons to represent binary information. In these devices, the current due to spin-polarized electrons is used to transfer information among magnets that store the binary information. Spin generation in magnetic metals is due to the different mobilities and the density of states at the Fermi level for spin-up and spin-down electrons. The degree of spin polarization (DSP) varies among magnetic materials. The polarization, P, can be defined as

$$P = \frac{N_{\uparrow} - N_{\downarrow}}{N_{\uparrow} + N_{\downarrow}},\tag{1}$$

in which  $N_{\uparrow(\downarrow)}$  is the density of states (DOS) of electrons at the Fermi level [56],

$$N_i = \frac{1}{(2\pi)^3} \Sigma_{\alpha} \int \delta(E_{k\alpha i}) d^3 k = \frac{1}{(2\pi)^3} \Sigma_{\alpha} \int \frac{dS_F}{\mathbf{v}_{k\alpha i}},\tag{2}$$

in which  $E_{k\alpha i}$  is the energy of an electron with spin  $i(\uparrow \text{ or } \downarrow)$  and wave vector k in the band  $\alpha$  [56]. The current of spin-polarized electrons can be injected into non-magnetic metals as well. Spin current in paramagnetic-magnetic interfaces can be measured using schemes employing Johnson-Silsbee [57] experiment. In nonmagnetic metals, spin accumulation decays exponentially with the characteristic length, called the spin relaxation length  $\lambda_{sf}$ . The generation of spin-polarized current is not limited to magnetic materials. Because of spin-orbit interaction, scattering of unpolarized electrons by an unpolarized target yields in a spatial separation of spin-up and spin-down electrons [58]. Thus, a net spin current is generated due to spin Hall effect (SHE). Spin-orbit interactions are strong in heavy metallic elements, topological insulators, and 2D materials such as graphene.

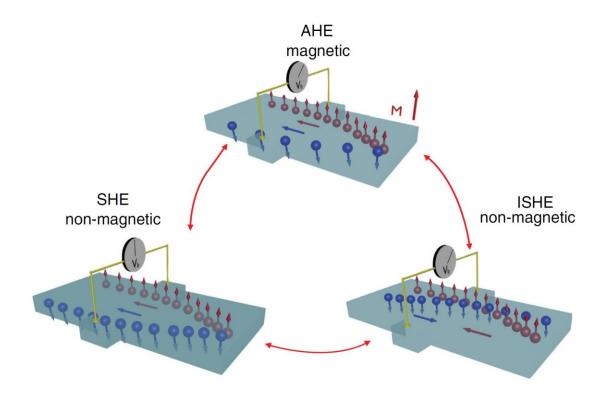

Figure 4: Illustration of spin-dependent Hall effects used in spin current generation and detection. In the SHE, an unpolarized charge current generates a transverse spin current, while in the ISHE, a spin current generates a transverse charge current. In the anomalous Hall effect (AHE), a charge current generates a transverse charge current [58].

Various spintronic devices use spin current to transfer signals in Al, Cu interconnects. Like charge current transport in CMOS devices, spin current transport is impacted by scattering and dimensional scaling in nanowires. In large CMOS circuits such as microprocessors, even more than half of the dynamic power dissipation might happen in interconnects [59]. Thus, studying spin current transport in metallic interconnects is expected to be crucially important. To provide effective design tools and insights for

electronics engineers, circuit and SPICE models must be developed that precisely account for the spin current transport in metallic nanowires.

#### 1.2.2 Magnetization Switching

#### 1.2.2.1 Spin-Transfer Torque and Spin-Orbit Torque Switching

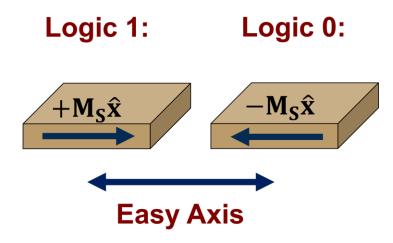

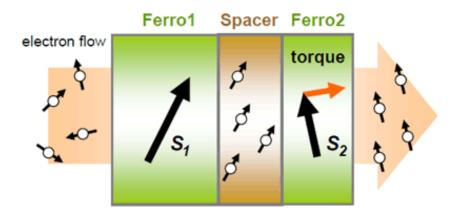

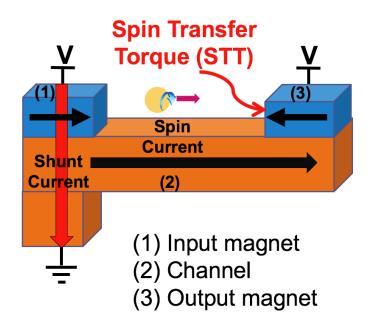

In spintronic devices, magnets are widely used to store binary information. Magnets possess an easy axis, in which the energy of a magnet is minimized when the magnet orients along this axis, (Figure 5). Thus, free magnetic layers reorient themselves along the either of the two opposing directions along the easy axis to minimize their energy. These two directions are the stable states of the magnet and can represent the binary logics 0 and 1. To switch magnets from one stable direction to another, spin torque must be applied. STT-MRAMs use STT for magnetization reversal. The STT generated in a spin valve is explained in Figure 6. Electrons pass through Ferromagnet 1, in which the spin of electrons precesses in the exchange field of the magnet and aligns with the orientation of the magnet. The spin-polarized current will be injected to a non-magnetic spacer layer. Considering the relatively narrow width of the spacer layer, the spin of electrons does not change in this region. By passing electrons through Ferromagnet 2, the spin of electrons tend to align with the orientation of the magnet. Thus, a spin transfer torque is applied to the magnet due to the conservation of angular momentum. Therefore, the spin torque can be explained as the net flux of non-equilibrium spin current passing through the magnet. If the STT is strong enough, it can fully switch a magnet by  $180^{\circ}$ .

Figure 5: Binary information is stored as the magnetization orientation along the two stable directions along the easy axis of the magnet.

Figure 6: Spin-transfer torque explained in a spin valve [60].

As explained in Subsection 1.2.1, spin current is generated in non-magnetic materials due to spin-orbit interactions. Like the spin current generated due to the interaction of electrons with the exchange field in a magnetic material, the spin current generated due to the spin orbit interaction applies torque to a magnetic layer, described as

the spin-orbit torque (SOT). Recently, researchers are widely studying the applications of SOT in the design of SOT-MRAMs [61]–[63] because a large write current does not have to pass through a tunnel junction; hence, the tunneling layer can last longer. Moreover, read and write lines can be separated and the spin transfer can be applied more efficiently. Thus, the area of STT and SOT are active fields of research and promising for novel spintronic logic and memory applications.

#### 1.2.2.2 Strain-Mediated Magnetization Switching

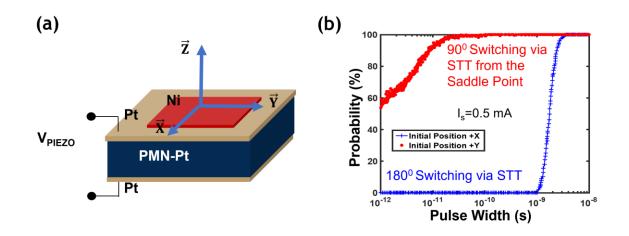

Magnetostrictive switching is an energy efficient and experimentally demonstrated magnetization reorientation mechanism [64]. In this mechanism, by changing the magnetoelastic energy, the easy axis of the magnet rotates; thus, the magnetization orientation rotates accordingly. Figure 7a shows an experimental setup for a magnetostrictive switching. In this experiment, a hybrid structure of magnetic and piezoelectric layers is fabricated. By applying a voltage along the thickness of the piezoelectric layer, an anisotropic strain is generated along the y axis, which transfers to the Ni layer on top. The strain changes the energy profile of the magnetic layer, as Ni is a material with strong magnetostrictive properties. By increasing the strain, the energy profile is changed such that the **v** axis becomes the easy axis of the magnet. Thus, the magnet reorients by  $90^{\circ}$  to align itself with the easy axis. Furthermore, researchers have combined this mechanism with STT to fully switch a magnet. In such scenario, first, the magnetization reorients by  $90^{\circ}$  using magnetostrictive switching. Second, the applied voltage to the piezoelectric is turned off; thus, the easy axis will rotate back to the  $\mathbf{x}$ direction. Therefore, the magnet will be placed at the saddle-point of its energy profile and will be equally probable to rotate to either of the two stable directions, the +x and the -x directions. Hence, by applying an STT, the magnet can be deterministically switch to one of the stable directions. Switching a magnet from the saddle-point of energy profile compared to  $180^{\circ}$  switching of a magnet using STT, is not only shown to be more robust to thermal noise, but also two orders of magnitude more energy efficient [65]. Considering the efficiency and the robustness to thermal noise, modeling the magnetostrictive switching is a promising area of research.

Figure 7: (a) 90° magnetostrictive switching is experimentally demonstrated [64]. (b) Compared to 180° magnetization reversal via applying STT, 90° switching of a magnet via STT from the saddle-point of energy profile is demonstrated to be two orders of magnitude more delay and energy efficient [65].

#### **1.3** Thesis Overview

The objective of this research is modeling the physical formalisms of common materials and phenomenon in spintronic and magnetic devices and circuits and designing novel spintronic devices for various applications such as interconnection, Boolean logic computation, non-Boolean computation, image/pattern recognition, neural networks, and interface circuits for reading and writing magnets. Various novel spintronic devices and circuits are proposed in the past decade that employ STT and SOT as well as strain for magnetization switching, Al, Cu metallic interconnects for transferring spin current, MTJs for storing data, SHE, ISHE, and IREE for converting charge currents to spin currents and vice versa. Therefore, there is a growing demand to investigate these physical phenomenon and design novel spintronic devices and circuits with enhanced functionalities and performance. Thus, the following tasks are undertaken in this research:

- 1. Designing circuit models for magnetization dynamics, thermal noise, and metallic interconnects widely used in the design of spintronic devices

- 2. Analyzing the operation and performance of the all-spin logic device as a building block for Boolean logic and coupled-oscillator applications.

- Designing spintronic pattern/image recognition circuits with non-volatile memory for storing patterns.

- Studying and designing read and write CMOS-magnetic interface circuits using MTJs and the ASL device as well as their applications in long-range interconnection schemes

- 5. Investigating strain-mediated magnetization switching and designing novel spintronic device and circuits that work based on both magnetostrictive and STT switching for logic and neural network applications

- 6. Investigating spin-orbit interactions and designing novel spintronic devices that work based on both magnetostrictive and SOT switching for logic applications

A brief description of the above tasks is given below.

*Task I and Task II*: In Chapter II, based on physical formalisms governing common magnetic and non-magnetic materials used in spintronic devices, models are developed that capture the magnetization dynamics and the impact of thermal noise on the switching of magnets as well as spin/current transport in Al, Cu nanowires. Using these models, the operation of the ASL device is explained and simulated. Moreover, the impact of size effects on the operation the ASL device is studied. Furthermore, the operation of the ASL full-adders, as a building block for more complicated Boolean logic gates, is studied. Finally, an ASL coupled oscillator is proposed, and its tuning range is studied.

*Task III*: In Chapter III, a novel circuit for non-Boolean recognition of binary images is proposed. Employing all-spin logic (ASL) devices, logic comparators and non-Boolean decision blocks for compact and efficient computation are proposed. Furthermore, the extension of the work for larger training sets or larger images thorough the manipulation of fan in number in different stages of the circuit is studied. Finally, the proposed circuit is compared with existing CMOS pattern recognition circuits in terms of footprint, power consumption, decision time, and operational voltage.

*Task IV*: In Chapter IV, first, an electrical- to spin-signal transducer is proposed. The proposed circuit can be used to write binary information into magnetic memories using STT. Then, a simple yet efficient circuit for converting the orientation of a magnet to CMOS binary voltage is proposed, which provides an energy-efficient and fast interface circuit to read magnetic memories. Using the proposed transducers, a long-range spintronic interconnect is proposed that works based on converting spin signals into electrical signals, transferring signals in electrical interconnects, and finally converting the signals back into spin signals. Moreover, an analytical study of the delay, area-delay-power product (ADPP), and the per-unit length value of energy per bit of spintronic interconnects with ASL repeaters is presented. Finally, the performance of the two methods, using spintronic repeaters and the electrical transmission of spin signals using the proposed interconnect, are benchmarked in terms of delay, energy dissipation, and area-delay-power product.

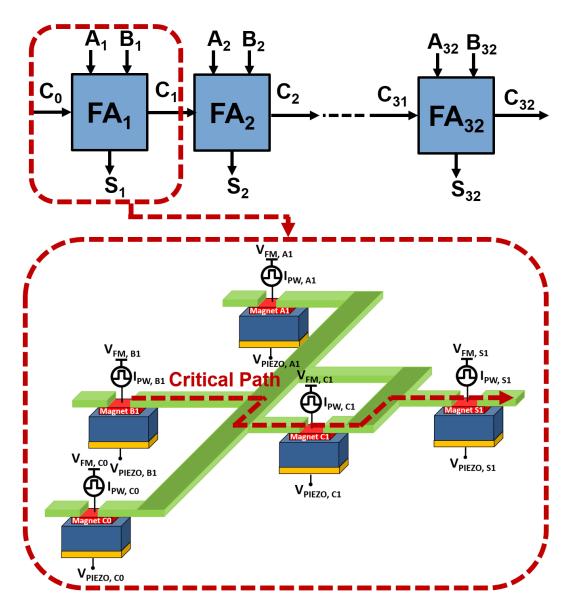

Task V: Magnetostrictive switching combined with STT has resulted in faster operational speed, higher energy-efficiency, and more robustness to thermal noise in magnetization reversal. In Chapter V, the physical formalism of magnetostrictive switching is investigated and modelled. Moreover, by combining this switching mechanism with STT, a novel spintronic device is proposed, named the magnetostriction-assisted all-spin logic (MA-ASL) device. The device is consisted of a heterostructure of magnetostrictive and piezoelectric layers. The operation of the device is modeled and simulated using developed SPICE models. Moreover, the transferred strain to the structure is simulated to ensure the correct functionality of the device. Furthermore, the impact of the pulse skew and the rise time on the operation of the device is studied, and design recommendations to counter these impacts are provided. Using the developed models and simulations, the energy, the error rate, and the delay performance of the device is studied. Moreover, to enhance the performance of the device, material analysis is done to investigate the best candidate materials to implement the MA-ASL device. The magnetic materials must exhibit strong magnetostrictive properties and low resistivity.

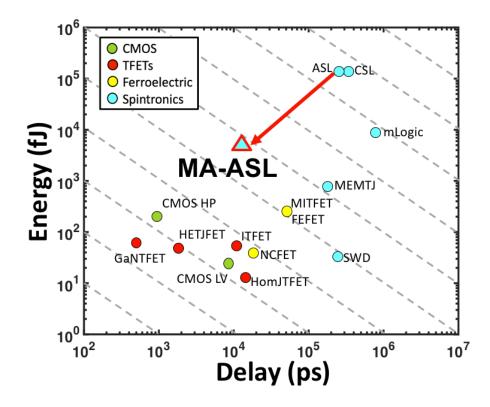

In this task, the applications of the MA-ASL device is further investigated for implementation of Boolean logic and neural network circuits. In Chapter V, the performance of a 32-bit MA-ASL arithmetic-logic unit (ALU), as a large Boolean logic circuit is studied. The proposed ALU is compared to both spintronic and CMOS ALUs. Moreover, in Chapter VI, the applications of the MA-ASL device for the neural network circuits is investigated. An MA-ASL neuron is proposed, which consists of an MA-ASL majority gate and an MTJ. The performance of the proposed neuron is studied and benchmarked against its CMOS and spintronic counterparts in terms of energy dissipation, operational speed, and thermal noise.

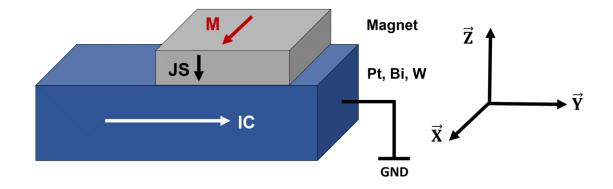

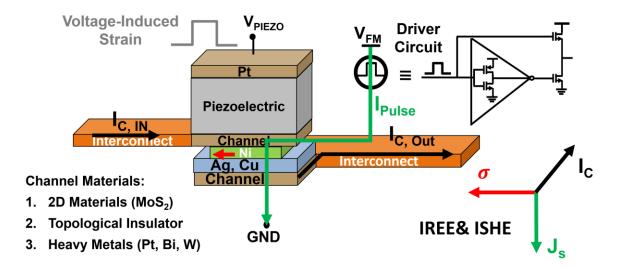

Task VI: In Chapter VII, spin-orbit interactions, SHE, and ISHE are investigated. Moreover, Rashba effect and inverse Rashba-Edelstein effect (IREE) in 2D materials and topological insulators are studied. Furthermore, these mechanisms are modeled using circuit models. In addition, by combining SHE, ISHE, IREE, and magnetostrictive switching a novel device is proposed, named the magnetostriction-assisted spin orbit (MASO) device. Unlike the ASL and the MA-ASL devices, the MASO device uses the charge current instead of the spin current to transfer data from the input magnet to the output magnet. The operation of the device is modeled and simulated using SPICE models. To optimize the performance of the device, the energy dissipation, the switching speed, and the robustness to thermal noise are studied. Moreover, materials analysis is performed to find the promising magnetic and heavy metallic materials as well as topological insulators for the implementation of the device. Using the findings of this analysis, the performance of the device in the implementation of the ALUs is studied and benchmarked against its spintronic and CMOS counterparts. Findings of this benchmarking helps to understand the potential applications of the MASO device in the implementation of large Boolean logic circuits.

The circuit models developed for the magnetization dynamics, tunnel junctions, and spin-orbit interactions as well as the novel proposed spintronic devices, neurons, image/pattern recognition circuits, spintronic interconnection schemes, and CMOSspintronic interface circuits will serve to guide future research in the field of novel beyond-CMOS devices, memories, and circuits by examining the potentials and the challenges of spintronic and magnetic devices and circuits.

# II. THE ALL-SPIN LOGIC DEVICE, ITS PERFORMANCE ANALYSIS AND ADDER AND COUPLED OSCILLATOR IMPLEMENTATION

#### 2.1 All-Spin Logic Device: Applications and Challenges

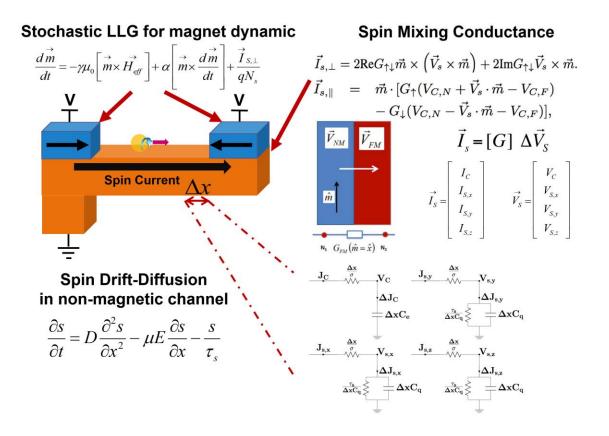

The ASL device was proposed as a building block for various spintronic devices and circuits [27]. Thus, the energy and the delay of the ASL device and ASL-based circuits are widely studied [26], [27], [49]–[51], [66]–[76]. The ASL device consists of two magnets via a channel in a non-local spin valve structure. Improving the performance of the device relies on efficient spin current transport throughout the device, spin current injection at the magnetic-non-magnetic interface, and magnetization switching, shown in Figure 8. Thus, to optimize the performance of the ASL device, the delay and the energy of the device is studied for various geometrical dimensions, supply voltage values, and channel materials. To account for the spin current transport in the metallic channel, size effects, i.e. surface and grain boundary scattering, and dimensional scaling, e.g. variations of the length and the width of the channel, must be studied [75]. Excess scattering at the grain boundaries and surfaces of metallic channels is dominated by the Elliott-Yafet (EY) mechanism [77]; when electrons scatter to a new state in the conduction band, there is a probability that they couple to a different spin state as electron states are not pure spin states. Therefore, spin relaxation mechanism becomes proportional to the scattering rate [77]. Moreover, the loss of spin information depends on the spin relaxation length of the channel. Spin signals decay exponentially for channels longer than the spin relaxation length imposing geometrical constraints on the design of ASL devices, such as limiting the maximum allowable length of channels to a few hundred nanometers [75].

Figure 8: To model the physics of the all-spin logic device, magnetization dynamics, spin mixing conductance, and spin-drift diffusion in the channel are taken into account [78].

Modeling channels with various geometrical dimensions is done using circuit models presented in [50], shown in Figure 9. In this model, the spin current transport is modeled using a distributed T-model, which accounts for the conductance of the channel as well as the spin relaxation mechanism. Moreover, these models capture the dynamics of magnetization reversal as well. Furthermore, in [50], a circuit model is developed that precisely captures the impact of thermal noise, is validated by analytical derivations presented in [52]. Based on the findings, the switching of magnets at room temperature is significantly impacted by thermal noise; as an example, the switching delay of magnets may alter by 30% at the room temperature. Because of the efficient implantation of majority gate and lower device count, ASL devices are studied for various applications [39], [70], [79]–[81]. As an example, a majority gate with a fan-out of four implemented by ASL requires four magnets [82], while that of CMOS requires 14 transistors. Similarly, a majority-based full adder implemented by ASL requires five magnets [83], while that of CMOS requires 28 transistors. Lower device count and fabrication area are two advantages of ASL devices in implementing more complicated Boolean logic applications such as 32-bit adders and arithmetic logic units (ALUs) [33]. In this chapter, an ASL full adder as the building block for ASL ALUs is analyzed, and its performance is studied.

Figure 9: ASL circuit model [78].

In addition to lower device count, the ASL device offers advantages such as a tunable delay in a large range by changing the supply voltage; a change of input voltage from 10 mV to 35 mV results in a change of delay from 350 ps to 100 ps. Hence, by

implementing ring oscillators using ASL devices [84], we expect the oscillation frequency to be tunable in a large range. Oscillators are one of the essential blocks in analog and digital electronics and communication systems. CMOS oscillators are widely studied and designed, and their phase noise, frequency tuning, and power consumption have improved over the last two decades [85]–[90]. However, ring oscillators normally suffer from a poor phase noise performance, due to the asymmetric nature of the time domain signal [91], compared to more symmetric topologies such as LC and Collpits oscillators. The tuning of CMOS ring oscillators usually requires extra tuning components such as varactors, which adds to the current path loss. As a result, lower output power and higher phase noise are inevitable in a tunable ring oscillator. Therefore, generating wideband, low phase-noise oscillators, coupled oscillators are introduced to achieve lower phase noise, wider tuning range and higher output power. Moreover, the networks of coupled oscillators can implement certain applications such as non-Boolean logic computation circuits [92]. In this chapter, an ASL coupled-oscillator scheme is proposed and investigated.

#### 2.2 Modeling and Benchmarking of All-Spin Logic

#### 2.2.1 The Operation of All-Spin Logic

In an ASL device shown in Figure 10, electrical current flows from the supply voltage to ground through the input magnet and the nonmagnetic metal underneath it. The current passing through a magnet becomes spin polarized with majority electrons' magnetic moment aligned with its magnetization. The spin polarized electrons injected (or extracted) by the input magnet increase (or decrease) the density of the electrons with the spin orientation aligned with the input magnet inside the channel. The concentration gradients for electrons with parallel and anti-parallel spin orientations inside the channel

creates a spin current towards the output magnet based on the diffusion process. This spin current applies a torque to the output magnet that, if strong enough, can flip it to align it with the spin orientation of the majority electrons. Thus, the device is capable of operating both as an inverter and as a buffer depending on the polarity of the supply voltage, which determines the injection or extraction mechanism for the spin current.

Figure 10: ASL consists of two magnets connected by a non-magnetic channel. Injected spin current from Input magnet to the channel diffuses along the channel and applies a torque to the output magnet, which if strong enough, switches the output magnet.

Major parameters that determine the performance and the energy dissipation of this device include channel and interface resistances, spin diffusion length, and the thermal noise of magnets. In the next subsections, these parameters are investigated.

Figure 11: Transient Response of an all-spin logic device. In this simulation, the input magnet is assumed to be oriented in the +X direction. By applying a negative voltage, the device acts as a buffer, while by applying a positive voltage, the device acts as an inverter.

# 2.2.2 The Modelling of the Thermal Noise of Magnets

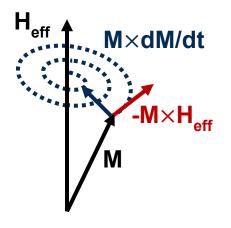

The magnetization dynamics of magnets is described by Landau-Lifshitz-Gilbert (LLG) equation,

$$\frac{d\vec{m}}{dt} = -\gamma \mu_0 \left[ \vec{m} \times \vec{H}_{eff} \right] + \alpha \left[ \vec{m} \times \frac{d\vec{m}}{dt} \right] + \frac{\vec{l}_{s,\perp}}{qN_s},\tag{3}$$

in which  $\vec{m}$ ,  $\vec{I}_{s,\perp}$ ,  $N_s$ ,  $\mu_0$ ,  $\alpha$ ,  $\gamma$  represent the magnetic orientation, the perpendicular spin current, the number of spins in the magnet, the free space permeability, the Gilbert damping coefficient, and the gyromagnetic ratio [50], [93], Figure 12. The net magnetic field,  $\vec{H}_{eff}$ , is comprised of the uniaxial anisotropy field,  $\vec{H}_U = -\frac{1}{\mu_0 M_S} \frac{\partial E}{\partial \vec{m}}$ , and the demagnetization field,  $\vec{H}_{demag} = M_S \bar{N}_d \vec{m}$ . The net magnetic field can be modified to include thermal noise. Thermal noise is caused by the thermal random motion of electrons in the magnet [33] and can be modeled by the thermal field,  $\vec{H}_{Thermal}$ , which models the statistical thermal motion of the electrons [50],

$$\vec{H}_{eff} = \vec{H}_U + \vec{H}_{demag} + \vec{H}_{Thermal}.$$

(4)

The model is implemented in SPICE and the results are validated using the analytical solution for the steady-state precession angle,  $\theta_0$ , [50] as a function of temperature

$$\langle \theta_0^2 \rangle = \frac{k_b T}{E_b},\tag{5}$$

in which  $E_b$  represents the energy barrier of the magnet. As Figure 13 shows, the SPICE results match within 5% of the analytical results.

Figure 12: LLG equation describes the magnetization dynamics. The corresponding vectors to the terms of LLG equation are represented in this figure.

Figure 13: To validate the SPICE model of the thermal noise, the derived average value of the thermal noise over time of the SPICE model, is compared to that of the analytical solution. SPICE results match with analytical results.

#### 2.2.3 Size Effects

Size effects caused by extra scattering at surface and grain boundaries affect several important parameters for ASL channels including resistivity, diffusion coefficient, and spin relaxation length. Among these factors, spin relaxation length is the most important factor since signal attenuates exponentially as channel becomes longer than spin relaxation length, Figure 14. In metals, the dominant spin relaxation mechanism is the Elliott-Yafet (EY) mechanism, in which every time an electron is scattered, there is a certain probability that it may lose its spin information [17]. Hence, spin relaxation time is proportional to momentum relaxation time, which gets shorter as channel cross-sectional dimensions become smaller, due to size effects. The models for spin relaxation time and spin diffusion length are presented in [94]. Figure 15 shows how spin relaxation length decreases as channel dimensions scale. The three important parameters of concern are the sidewall

specularity, P, the grain boundary reflectivity, R, and the average grain size. As a rule of thumb, the average grain size in channel fabricated by Dual Damascene process is equal to the width or thickness, whichever is smaller [95].

Figure 14: Delay and energy dissipation vs channel (channel) length of an ASL gate.

Figure 15: Spin Relaxation versus channel Width [2]. Size effects cause the spin relaxation length to decrease with decreasing channel width. For the no size effect case, spin relaxation length is independent of channel width.

The delay and energy per bit have been plotted versus length in Figure 16, respectively, assuming a channel width of 37.8 nm equal to the width of the magnets, and a width to thickness aspect ratio of 2. To observe the impact of size effects, a hypothetical case, in which size effects are absent is also considered (labeled ideal Cu). Size effect parameters are assumed to be R = 0.2, P = 0.0 for the typical case, and R = 0, P = 1.0 are assumed for the ideal case. Physical parameters of Cu channel are calculated as  $\sigma = 41.549$  ( $\mu\Omega$ m)<sup>-1</sup>, D = 0.014 m/s for the typical case. To demonstrate the effect of thermal noise in magnets, each simulation is repeated three times considering room temperature.

Figure 16 : (a) Delay versus specularity parameter, P, for an 80 nm long channel. Grain boundary scattering parameter, R, is assumed to be 0.2 (b) Delay versus grain boundary reflection probability for an 80nm long channel. The specularity parameter, P, is assumed to be 0 [96]–[99].

To see how improving channel process can improve channel performance and energy dissipation, Figure 17 plots delay versus surface specularity parameter, P, and grain boundary scattering, R. Both Cu and Al have been considered here. Also, to avoid busy plots, thermal noise has been turned off and its effect has been considered only in setting the initial angles of the magnets. Here, both Cu and Al have been considered as they offer different tradeoffs. As Figure 15 shows, spin relaxation in Al is higher than that of Cu. Furthermore, since the mean free path in Al is shorter than that of Cu, size effects are less severe in Al as compared to Cu. However, Cu offers a lower resistivity unless crosssectional dimensions become too small such that size effects become too prominent. The spin injection coefficients for Co/Cu and Co/Al interfaces are assumed to be the same [73].

Figure 17: Delay versus channel width for 80 nm and 400 nm long channel.

To quantify the impact of dimensional scaling, channel width analysis is presented in Figure 17. The magnet width is assumed to be 37.8 nm in all cases to ensure adequate magnet stability and non-volatility. Size effects become more pronounced at smaller dimensions. The aspect ratio of channel is assumed to be constant in these simulations. For the channel widths smaller than the magnet width, the interface area decreases which further increases delay and energy. For channel width analysis, two channel lengths of 80 nm and 400 nm have been considered. For the ideal cases (no size effects), both lengths are shorter than spin relaxation lengths in Cu and Al, and Cu is a better choice since it offers a lower resistivity. However, size effects make the spin relaxation length shorter and Al channels become faster and dissipate less energy compared to Cu channels especially at small widths. Also, one can see the delay and energy penalty associated with size effects increase drastically as wire dimensions scale down.

#### **2.3 Applications**

#### 2.3.1 ASL Adders

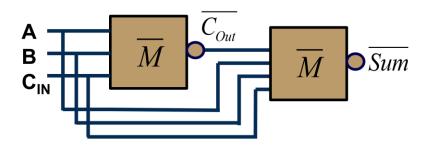

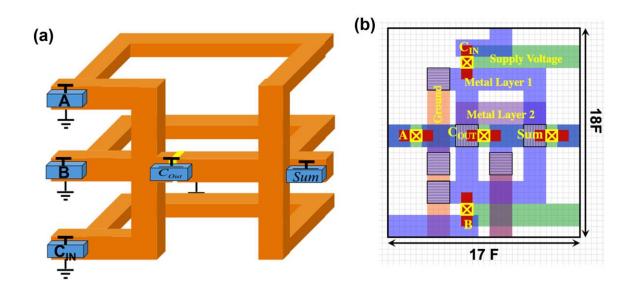

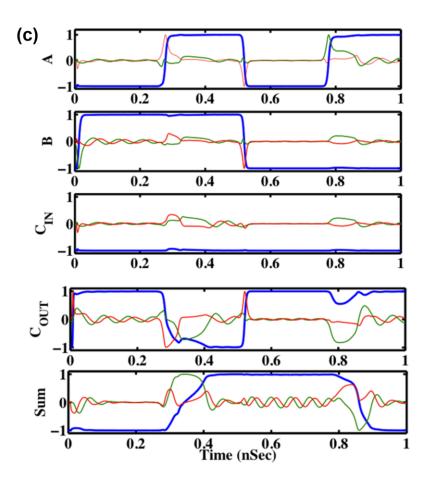

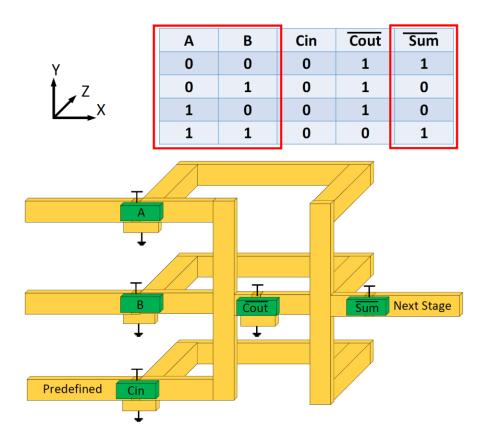

Majority gates can be used to implement full adders with lower device count, as shown in Figure 18. An ASL full-adder implementation by cascading two ASL majoritynot gates is shown in Figure 19a, and the layout is shown in Figure 19b. The carry-out bit,  $\overline{C_{OUT}}$ , is the majority-not of *A*, *B*, and the Carry in (*C*<sub>IN</sub>) bit; hence,  $\overline{Sum}$  bit can be produced as the majority-not of *A*, *B*, *C*<sub>IN</sub>,  $\overline{C_{OUT}}$ ,  $\overline{C_{OUT}}$  bits, implemented using a 5-input majority gate. The proposed structure is simulated, and the results are shown in Figure 19c. By cascading the proposed full adder, a 32-bit ASL ripple-carry adder is formed. Although the proposed 32-bit ASL adder will benefit from lower device count, the CMOS 32-bit adder will be two orders of magnitude more energy and time efficient, even without considering driver circuits for ASL adders [36]. The significant difference in energy efficiency is due to the higher energy efficiency of CMOS transistors. Hence, ASL devices cannot compete against CMOS devices in terms of delay and energy for implementation of Boolean applications. However, due to the efficient control of delay and magnetization waveform, ASL devices are studied for other applications; one example of an ASL-coupled oscillator is demonstrated in the following subsection, and another example of an ASL image-recognition circuit is demonstrated in Chapter III.

Figure 18: Implementation of a full adder using two majority-not gates.

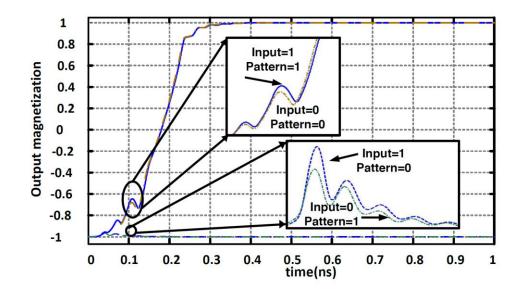

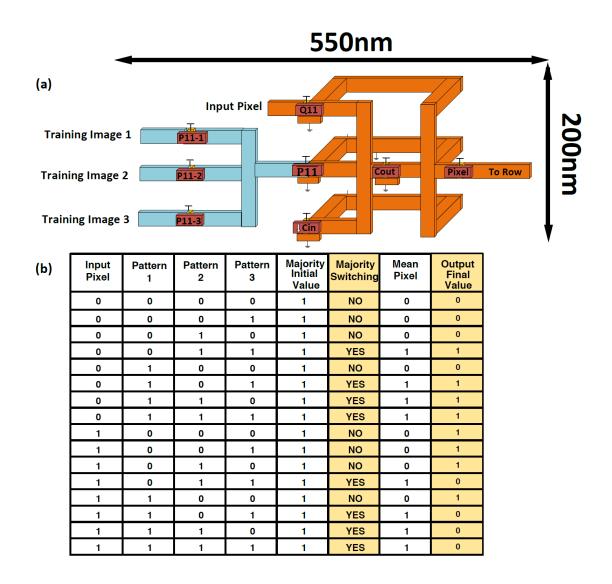

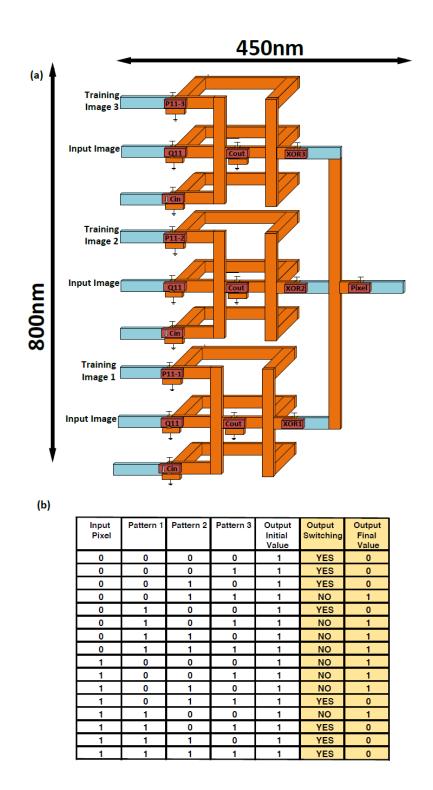

Figure 19: (a) Schematics and (b) layout of the ASL full adder. (c) The transient response of an ASL full-adder. The blue color represents the magnetization orientation in the x-direction and the green and red colors are representing magnetization in the y and z directions.

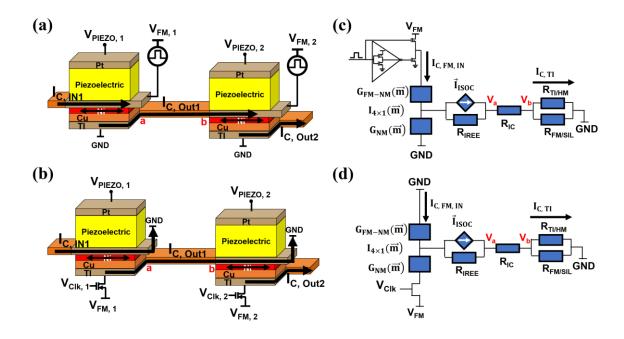

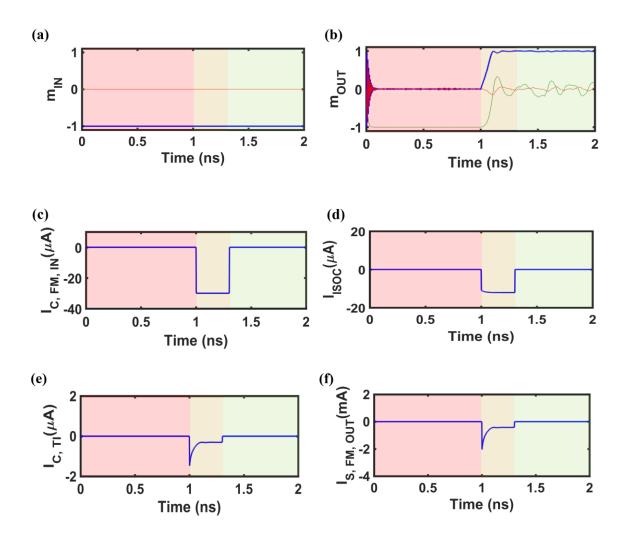

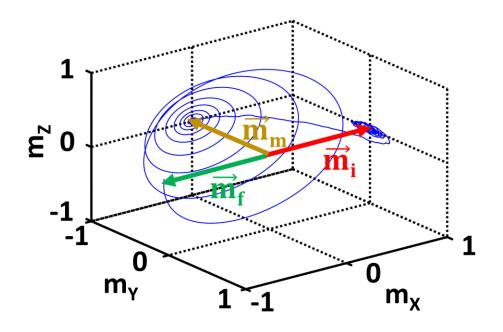

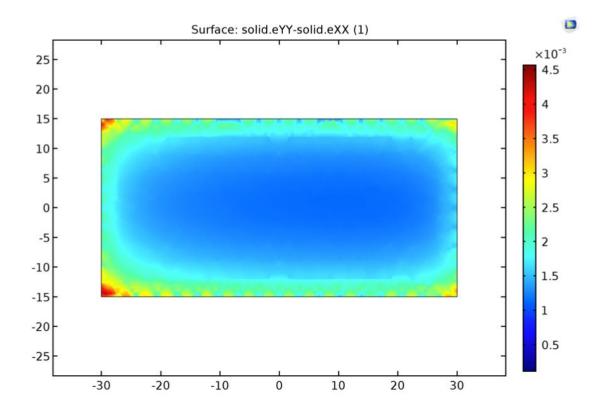

## 2.3.2 ASL Oscillators and Coupled-Oscillators