# AN INTEGRATED SIMULATION FOR VLSI DESIGN ENVIRONMENT

BY

# HOM-MING CHANG

B.S., Chinese Culture University, 1982 M.S., Pittsburg State University, 1987

### A REPORT

submitted in partial fulfillment of the requirements for the degree

MASTER OF SCIENCE

Electrical Engineering and Computer Engineering

College of Engineering

KANSAS STATE UNIVERSITY Manhattan, Kansas

1989

Approved by: Andry Rys

# ACKNOWLEDGMENTS

I would like to express my sincere gratitude to Dr. Andrzej Rys for his patience, encouragement, and valuable advice throughout my studies. Without Dr. Rys's guidance, this report would not have had clear direction.

I would also like to thank Dr. Eddie R. Fowler and Dr. Medhat M. Morcos for serving on my advisory committee.

I dedicate this work to my parents Mr. and Mrs. Chao-Chih Chang, who have encouraged me to pursue higher education and have supported me throughout the time I have been at Kansas State University.

# TABLE OF CONTENTS

| 1.0 Introduction                               | 1  |

|------------------------------------------------|----|

| 2.0 Process Simulation                         | 5  |

| 2.1 SUPREM: 1-D Process Simulator              | 5  |

| 2.2 Process Model                              | 7  |

| 2.2.1 Ion Implantation                         | 7  |

| 2.2.2 Thermal Oxidation                        | 10 |

| 2.2.3 Impurity Redistribution                  | 13 |

| 3.0 Device Simulation                          | 17 |

| 3.1 PICSES: 2-D Two Carriers Poisson Solver    | 17 |

| 3.1.2 Basic Physical description and           |    |

| Numerical Algorithm                            | 18 |

| 3.2 Classification Device Model                | 23 |

| 3.3 Model development for Diode                | 26 |

| 3.4 An Example of the MOSFET Device in PISCES- | 47 |

| 4.0 Circuit Simulation                         | 52 |

| 4.1 SPICE: Circuit Simulator                   | 52 |

| 4.2 Semiconductor devices in SPICE             | 53 |

| 4.3 MOSFET Model                               | 55 |

| 4.3.1 The MOS Capacitor                        | 55 |

| 4.3.2 MOS Transistor Model                     | 59 |

| 4.3.3 Surface Behavior of MOSFET               | 59 |

| 4 3 4 Level 1 Model in SPICE                   | 65 |

|           | 4.3.5 Equations for Level 2 Model          | 68  |

|-----------|--------------------------------------------|-----|

|           | 4.3.6 Level 2 Model in SPICE               | 69  |

|           | 4.3.7 Gate Capacitance                     | 78  |

|           | 4.3.8 Junction Capacitance                 | 80  |

|           | 4.3.9 Level 3 Model in SPICE               | 82  |

|           | 4.3.10 Level 4 Model in SPICE              | 84  |

|           | 4.3.11 Table Lookup Model                  | 85  |

| 4.4       | Charge-control Model of Dynamic Operation  |     |

|           | for SPICE in Transient Analysis            | 87  |

|           | 4.4.1 Quasi-Static Operation               | 87  |

|           | 4.4.2 Non-Quasi-Static Operation           | 90  |

| 5.0 An Ir | nterface Program between PISCES and SPICE- | 91  |

| 5.1       | Parameter Generation                       | 91  |

| 5.2       | Calculation and Measurement for MOSFET     |     |

|           | Parameters                                 | 97  |

|           | 5.2.1 The parameters for Level 1 Model     | 97  |

|           | 5.2.2 The parameters for Level 2 Model     | 101 |

|           | 5.2.3 The parameters for Level 3 Model     | 103 |

| 6.0 Cone  | lusion                                     | 106 |

| Reference | es                                         | 108 |

| Bibliogra | aphy                                       | 110 |

| Appendix  | A                                          | 111 |

| Appendix  | B                                          | 129 |

# LIST OF FIGURES

| Fig. | 1.  | Architeture of integration.                    | 3  |

|------|-----|------------------------------------------------|----|

| Fig. | 2.  | Flow for the SUPREM                            | 6  |

| Fig. | 3.  | Profiles of B, As and P with same energy and   |    |

|      |     | dose,                                          | 9  |

| Fig. | 4.  | (a)Linear rate coefficient B/A (b)Parabolic    |    |

|      |     | rate coefficient B                             | 12 |

| Fig. | 5.  | Redistributed profiles of As, P, and B         | 16 |

| Fig. | 6.  | Flow of PISCES                                 | 22 |

| Fig. | 7.  | Input file of first stage for diode device     | 29 |

| Fig. | 8.  | Potential distribution expressed in the mesh   | 30 |

| Fig. | 9.  | Doping profile in the diode device             | 31 |

| Fig. | 10. | Input file of second stage for diode           | 32 |

| Fig. | 11. | Input file of second stage for diode w/o       |    |

|      |     | contact resistor                               | 33 |

| Fig. | 12. | Input file of third stage for plotting         | 34 |

| Fig. | 13. | I-V characteristics with two different contact |    |

|      |     | resistor                                       | 35 |

| Fig. | 14. | The relation between VA1 and V1                | 36 |

| Fig. | 15  | Input file for transient analysis              | 37 |

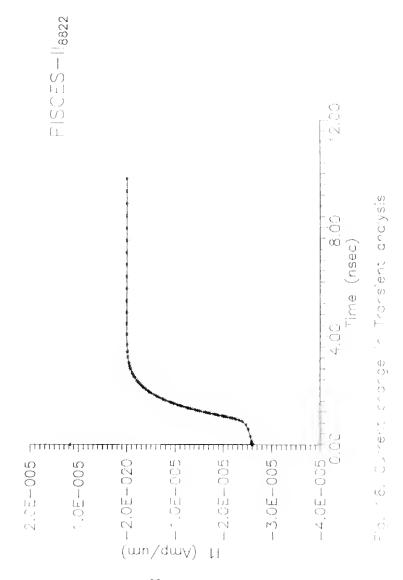

| Fig. | 16. | Current change in Transient analysis           | 38 |

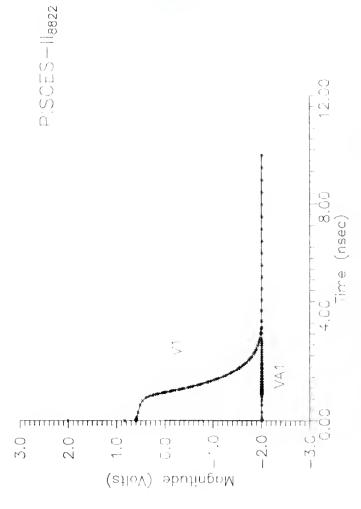

| Fig. | 17. | Transient analysis with step function voltage  | 39 |

| Fig. | 18. | Transient analysis with step function voltage  |    |

|      |     | for current                                     | 40 |

|------|-----|-------------------------------------------------|----|

| Fig. | 19. | Input file for transient analysis with ramp     |    |

|      |     | function voltage                                | 41 |

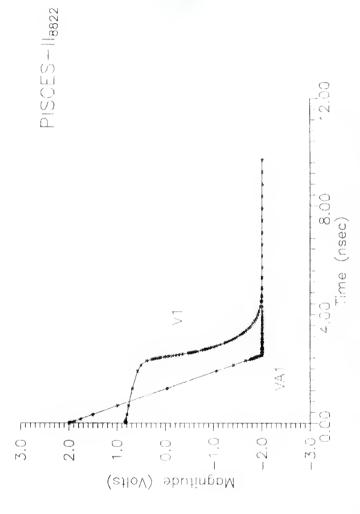

| Fig. | 20. | Transient analysis with ramp function voltage   | 42 |

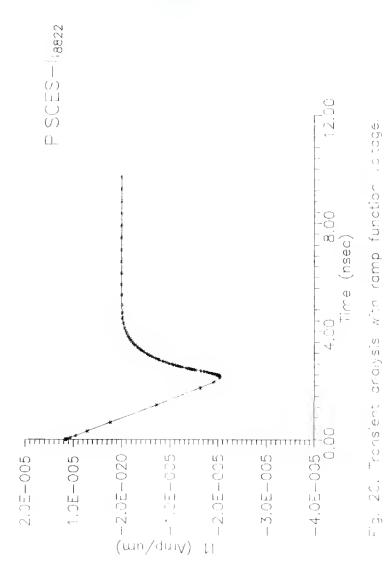

| Fig. | 21. | Transient analysis with ramp function voltage   |    |

|      |     | for current                                     | 43 |

| Fig. | 22. | Input file in AC analysis                       | 44 |

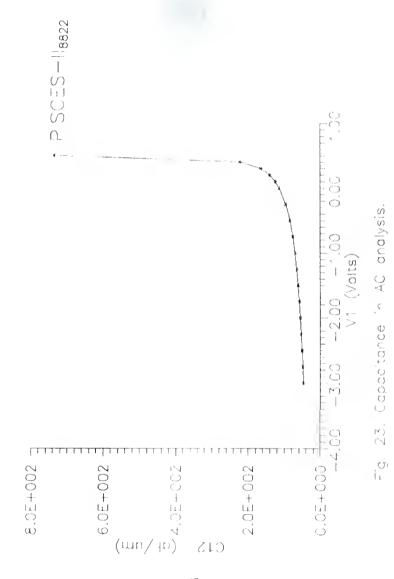

| Fig. | 23. | Capacitance in AC analysis                      | 45 |

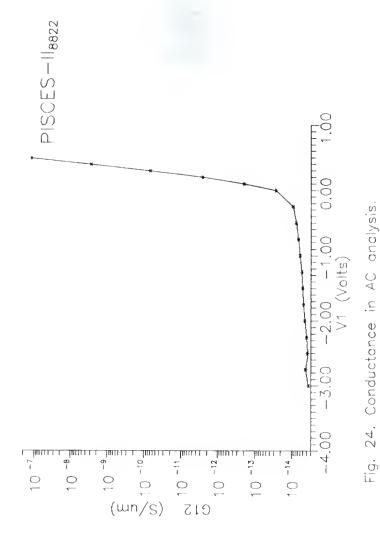

| Fig. | 24. | Conductance in AC analysis                      | 46 |

| Fig. | 25. | A input file of MSOFET for PISCES               | 50 |

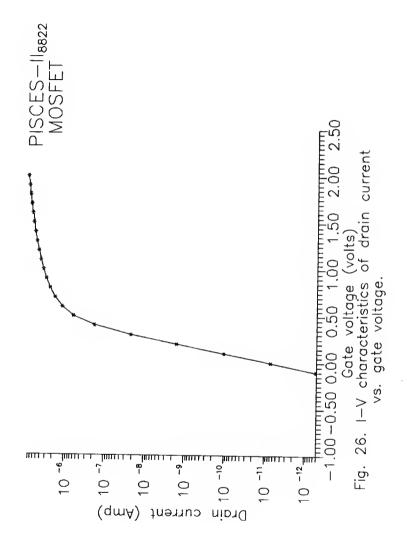

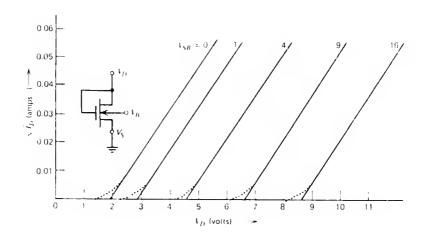

| Fig. | 26. | I-V characteristics of drain current vs.        |    |

|      |     | gate voltage                                    | 51 |

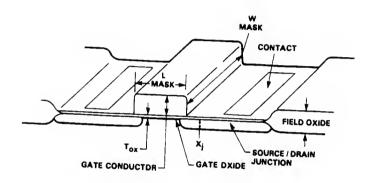

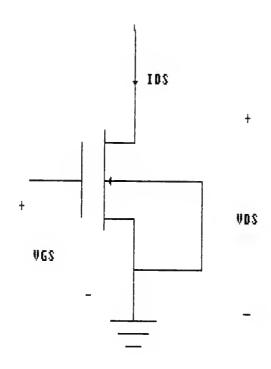

| Fig. | 27. | Structure of MOSFET                             | 56 |

| Fig. | 28. | (a)Small-signal capacitance of an MOS system    |    |

|      |     | with p-type silicon. (b) The equivalent circuit |    |

|      |     | for the overall capacitance                     | 60 |

| Fig. | 29. | Cross section of MOSFET                         | 63 |

| Fig. | 30. | Space charge as a funtion of the surface        |    |

|      |     | potential                                       | 66 |

| Fig. | 31. | (a) Output of level 1 model in SPICE with       |    |

|      |     | different KP to simulate the measured data.     |    |

|      |     | (b) Output of level 2 model in SPICE            | 71 |

| Fig. | 32. | The definition of VON                           | 73 |

| Fig. | 33. | The widths of the depleted regions of source    |    |

|      |     |                                                 |    |

|         | and drain                                        | 76  |

|---------|--------------------------------------------------|-----|

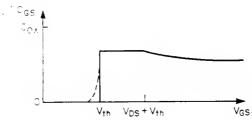

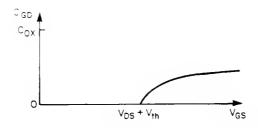

| Fig. 34 | . Meyer's model of the capacitance               | 79  |

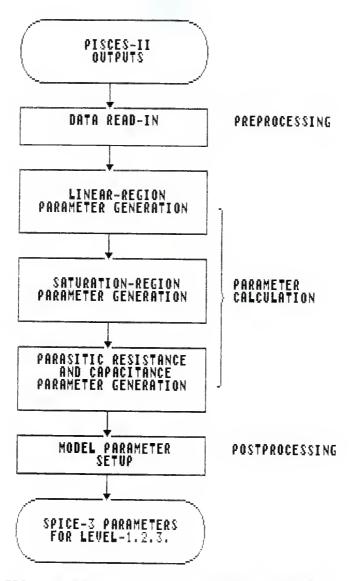

| Fig. 35 | . Architecture of interface program              | 92  |

| Fig. 36 | . Biasing condition for PISCES to generate data  |     |

|         | for interface program                            | 94  |

| Fig. 37 | . The determination of channel-length modulation |     |

|         | coefficient                                      | 96  |

| Fig. 38 | . Setup for measurement in the linear region     | 98  |

| Fig. 39 | . The effects of bias VSB between the source and |     |

|         | back,                                            | 100 |

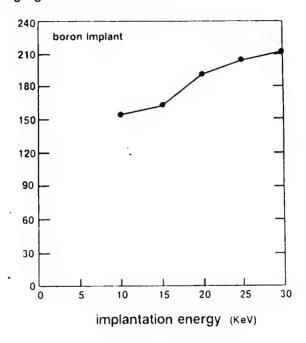

| Fig. 40 | Plot of the voltage gain vs. the boron           |     |

|         | implantation energy                              | 107 |

|         |                                                  |     |

# 1.0 INTRODUCTION

As MOSFET devices have been shrunk to the submicron range and a chip contains 100,000 transistors in the very large scale integration (VLSI) technology, trial-and-error methodology to optimize such a complex processes is impractical. Hence computer simulation is a cost effective and time efficient alternative, not only providing an appropriate approximation before fabrication, but also serving as a powerful tool in the development of advanced VLSI technology.

In the design of VLSI processes, a series of sophisticated computer simulation programs from the initial process level to the device level and finally the circuit performance are required [3]. In the last decade, various process, device, and circuit simulators have been developed independently.

The reasons for integration are based on two facts; firstly, Application Specific Integrated Circuits (ASIC) have emerged as a very important IC product in the market[4]. Secondly, process and device tools have been utilized to the extent of circuit simulation since the device features are developed to cope with the demand for more highly integrated circuit like the 4-Mbit dynamic RAM. Although the benefits of simulation can be obtained, the

realization of using simulation programs is not easy in practice. Three major attributes have been identified to use the simulation tools effectively. Firstly. understanding of the process, device, and circuit characteristics and models being simulated is very important. Secondly, in order to deal with these sophisticated and large computer program, one must be familiar with the computing environment which includes operation system, file management, programming language in C or FORTRAN so that the simulation programs can be utilized efficiently. Finally, understanding of the numerical method is needed. either to code the mathematical equations for the modified models which improve the chance of obtaining accurate results or to interpret the results when convergence problems arise. On the basis of the understanding of the above, all problems and pitfalls encountered while working with numerical simulation programs can be traced back and solved.

In this report, an integrated simulation for VLSI design environment is proposed. The idea is to link process simulator, device simulator, and circuit simulator into a comprehensive simulation tool that will improve the design and simulation efficiency by automatic generation of simulation file and automatic determination of device and circuit characteristics.

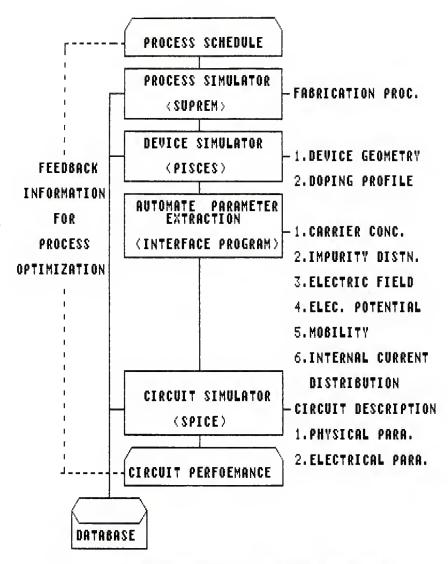

The architecture of this integration is shown in Fig 1.

FIG. 1. ARCHITETURE OF INTEGRATED SIMULATORS

In the first stage, fabrication process is converted to an input file of SUPREM. The next stage is the device simulator. Device geometry with the doping profile generated by SUPREM is used to simulate the two dimensional device characteristics. The output of PISCES is distribution, impurity distribution, internal electric field, electrostatic potential, mobility, and internal current distribution. Then, the interface program is used to generate parameters for SPICE. Finally, based on the parameters generated from interface program and specified by user, circuit performance is simulated. Results of the SPICE. PISCES, and SUPREM are stored in the common data base where they are employed by post processor to print and plot the data.

In this report, most of the capitalized variables are the parameters of SPICE which are listed in appendix B.

## 2.0 PROCESS SIMULATION

The primary purpose of process simulation is to obtain impurity profiles in silicon which can be used in device simulation program to theoretically predict the current-voltage characteristics of the fabricated devices.

Both one- and two-dimensional process simulation programs have been developed. While the one-dimensional programs are well developed, two-dimensional effects are becoming increasingly important as device structures are scaled down and lateral interaction between device regions becomes more critical.

### 2.1 SUPREM: 1-D Process Simulator

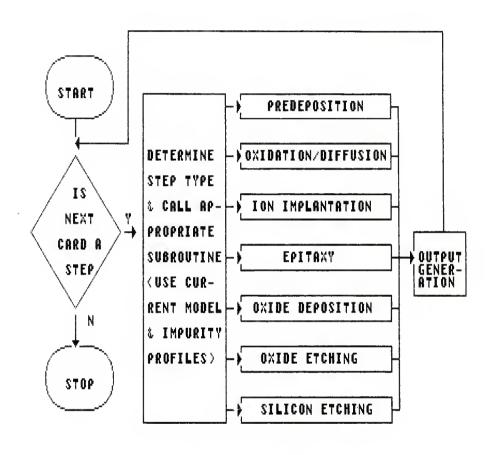

SUPREM stands for Stanford University PRocess Engineering Modeling program. The program input for SUPREM is a description of the processing schedule, specifying a sequence of times, temperatures, ambient and other parameters for diffusion, oxidation, ion implantation, deposition, and etching. The output is a one-dimensional impurity concentration profile in the vertical direction for the regions of the silicon and some other layers, such as silicon dioxide and polysilicon. The block flow diagram for the SUPREM program, shown in Fig. 2, indicates that the process steps can be simulated either individually or sequentially,

FIG. 2. FLOW FOR THE SUPREM

with the dopant profile predicted after one operation and used as the input for the next operation. The input file resembles an actual process runsheet and consists of free format statements. TITLE, GRID, and SUBSTRATE cards are always the first three cards that must appear at the beginning for array and parameter initialization. After impurities are introduced, ion implantation, oxidation, etching, deposition, impurity predeposition, and epitaxial growth are treated. The output of the program consists of the one-dimensional profiles of all the dopants present in the silicon and silicon dioxide material.

#### 2.2 Process Models

Although the fabrication step simulation is based on several process models in SUPREM, only three models for technology steps which have been used most often and bring out accurate results are presented in this section.

# 2.2.1 Ion Implantation

Ion implantation provides a highly controlled technology for introduction of the dopants into semiconductor. The simplest description of an ion implantation in silicon dioxide is a symmetric Gaussian curve with the two variables, the projected range Rp and standard deviation RHO. However, the actual distributions of many ions, such as boron,

arsenic, and phosphorus, are found to be asymmetrical. Higher order moments, therefore, must be used to construct range distributions which are better fitted by two half-Gaussian profiles, each with different deviation, RHO1 and RHO2, joined together at a modal range Rm. For the joint half-Gaussian distribution, the two sides are given by

(2.1)

$$C_1(y) = C_p * exp[-(y-Rm)^2/(2*RHO1^2)]$$

(2.2)

$$C_2(y) = C_p * exp[-(y-Rm)^2/(2*RHO2^2)]$$

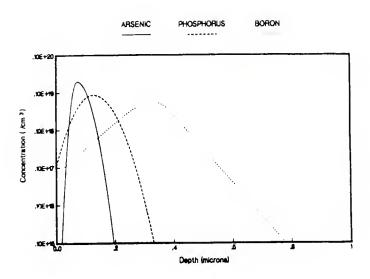

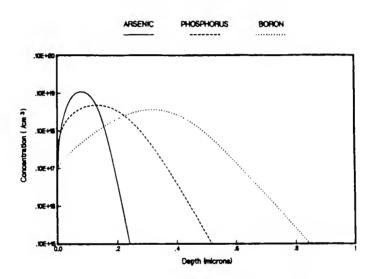

where Cp is the peak concentration. SUPREM can obtain three parameters from table lookup and interpolation. implanted boron profiles in amorphous silicon annealing has been shown by W. K. Hofker experimentally determined the fourth moment to Pearson-type IV distribution. Therefore, an exponentially long tail due to channeling can be modeled. The implantation model is valid only for pre-anneal data, enhanced diffusion of implanted species occurs during any, including a rapid, thermal annealing. The details of how to model thermally annealed boron profiles in silicon are described in Reference [5]. Fig. 3 shows different characteristics of arsenic, phosphorus and boron impurities implanted with the same energy and dose. Since boron is the lightest atom among them, the implantation peak is located at the deepest position.

Fig. 3. Profiles of B, As and P with same energy and dose[11].

### 2.2.2 Thermal Oxidation

The thermal oxidation process by which silicon dioxide is formed on silicon constitutes a major step in the fabrication of silicon devices. It is a direct reaction between atoms of silicon near the surface of the wafer and oxygen supplied in a high-temperature furnace. The high quality of the interface between silicon and thermally grown silicon dioxide is fundamental to the successful production of MOSFET technology. Three oxidant fluxes involved in the oxidation process are

- (2.3) F1=h\*(C1-C0)

- (2.4) F2=Deff\*(CO-C2)/XO)

- (2.5) F3=k\*C2

where F1 is the transport flux from gas ambient to the gasoxide surface; h is gas transport coefficient. The transport

flux F1 is proportional to the difference between equilibrium

concentration of oxygen in the oxide, C0, and concentration

at the oxide surface, C1. F2 is a diffusion flux inside the

oxide layer; Deff is the effective diffusion coefficient; C2

is the concentration at the interface between silicon and

oxide; X0 is the thickness of the oxide layer already

present. F3 is a reaction flux at the silicon/oxide

interface, and k is the surface reaction coefficient for

oxidation.

The linear-parabolic oxide-growth model in SUPREM assumes steady-state oxidant diffusion which implies that the three fluxes are equal.

$$(2.6)$$

F1 = F2 = F3 = F

The oxide growth rate is directly proportional to the flux as

$$(2.7)$$

$dXO/dt=f/N1=(k*C2/N1)/(1+k/h+k*XO/Deff)$

where N1 is the number of oxidant molecules incorporated in a unit volume per unit time of the oxide layer. When integrated, Eq(2.7) lead to the well-known linear-parabolic growth relationship but only if an initial oxide thickness X1 is specified prior to the oxidation step under consideration

$$(2.8)$$

$(X0^2-X1^2)/B+(X0-X1)/(B/A)=t$

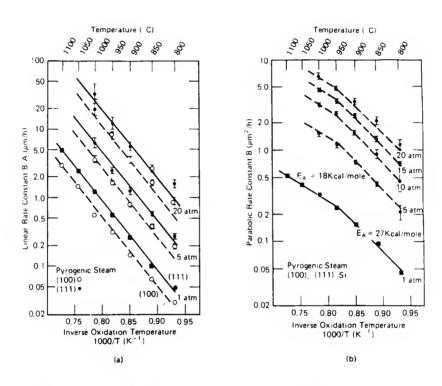

where B is called the parabolic rate constant and B/A the linear rate constant. Under relatively low dopant concentration conditions, B and B/A depend only on silicon crystal orientation, oxiding ambient and temperature. Behaviors of the two rate are stored in SUPREM as constants with default values and are shown in Fig 4.

Using high surface impurity concentration, more silicon vacancies are created, and the rate constants are,

Fig. 4. (a)Linear rate coefficient B/A (b)Parabolic rate coefficient B[12].

consequently, enhanced. Since the impurity concentration at the silicon-oxide interface changes due to diffusion and segregation during oxidation, enhanced values are calculated at each time step in SUPREM. It is known that the growth rate is enhanced as much as a factor of 10 for oxide thinner than 20 nm in a dry oxygen condition. This fast oxidation phenomenon has attracted great deal of attention recently because the gate oxide in the present VLSI process is grown within the thin oxide regime. SUPREM III has an empirical factor incorporated in the linear-parabolic model

# $(2.9) \quad dXO/dt=B/(XO+A)+K*EXP(-XO/L)$

where the decay length L is approximately independent of temperature and K is a singly activated function of temperature with an activation energy of 2.35 eV for  $\langle 111 \rangle$  orientation and 1.8 eV for  $\langle 100 \rangle$  silicon.

### 2.2.3 Impurity Redistribution

Impurity diffusion in silicon during high-temperature processing steps can be described by the complete continuity equation

### (2.10) dC/dt=d/dx(D\*dC/dx)+(-q)/(kT)\*d/dx(D\*Ci\*dPB/dx)

where D is the diffusivity, and C and Ci are the total and electrically charged impurity concentrations, respectively;

PB is the bulk junction potential which is expressed as below:

$$(2.11) PB=(k*T/q)*ln(n/ni)$$

where n and ni are the extrinsic and intrinsic carrier concentrations, respectively. The first term in the continuity equation represents classical concentration gradient-driven diffusion, including non-constant diffusivity. The second term incorporates the electrostatic field-driven flux.

SUPREM utilizes models based on vacancy diffusion mechanisms under non-oxidizing conditions. The intrinsic diffusivity of an ionized impurity species is the sum of the diffusivities resulting from neutral vacancies with an opposite charge. There are four charge states for vacancies: double negative(=), single negative(-), neutral (x), and positive (+). Thus, the effective diffusivity under non-oxidizing conditions is

(2.12)

$$DN=Di^{x}+Di^{-}[V^{-}]+Di^{-}[V^{-}]+Di^{+}[V^{+}]$$

where  $[V^-]$ ,  $[V^+]$  refer to the atom fractions of these species under extrinsic conditions divide those under intrinsic condition. A boron atom as an acceptor is negatively charged in the silicon lattice and it diffuses primarily with  $V^+$  and  $V^X$  vacancies. Thus the boron

diffusivity is

(2.13)

$$DN(B) = Di^{x} + Di^{+}(p/ni)$$

The diffusion coefficients for boron and other impurities are given as default values in SUPREM. Arsenic as a donor appears to diffuse with  $V^{\mathbf{X}}$  and  $V^{-}$  vacancies and its diffusivity is

$$(2.14) DN(As) = Di^{X} + Di^{-}(n/ni)$$

The bandgap narrowing effect due to lattice-misfit strain is also introduced in SUPREM, which causes the diffusivity to decrease in the heavily doped region that density is greater than  $5*10^{20}$  cm<sup>-3</sup>. Fig. 5 shows redistribution profiles of three implanted dopants, given in Fig. 3, where the impurities were diffused separately at the same temperature and time ( $100^{\circ}$ C and 30 min).

Fig. 5. Redistributed profiles of As, P, and B[11].

### 3.0 DEVICE SIMULATION

## 3.1 PISCES-II: 2-D 2-carrier Poisson Solver

The increased complexity of the device structure is necessary for optimization of the device performance, such as minimizing the drain-induced barrier-lowering effects, enhancing the device reliability, or reducing the electric field at the drain of the MOSFET. Therefore, in the development of VLSI MOS technology, it is essential to be able to simulate the electrical characteristics of devices which have complicated structures. The PISCES program provides this capability.

PISCES-II is a two-dimensional, two-carrier semiconductor device modeling program which simulates the electrical behavior of devices under either steady-state or transient conditions. It accepts data from the SUPREM, which provides high accuracy in the impurity definition, essential for submicron device simulations.

The PISCES program can simulate device structures such as MOSFET, JFET, MESFET, and other non-planar insulator-semiconductor structures such as the trench isolation structure. The program can extract device parameters such as the threshold voltage, subthreshold slope, punchthrough voltage, body effects, and electrode capacitance. The program

supports non-uniform triangular grids which can be specified through input card or by using an interactive grid generation pre-processor (IGGI). Further, PISCES itself can refine the specified grid during the solution process. A menu-driven post-processor is available as well for plotting solution data.

## 3.1.2 Basic Physical Description and Numerical Algorithm

To cover the whole range of the field-effect transistor operation, PISCES solves the Poisson equation and carriers continuity equations for the electric potential and carriers concentrations. The Poisson equation is

- (3.1)  $\nabla PSI = -(q/EPSILON)(p-n+ND^+-NA^-)-RHOF/EPSILON$  and the continuity equations for electrons and holes

- (3.2)  $\partial n/\partial t = (\nabla J)/q + Gn Rn$

- (3.3)  $\partial p/\partial t = (\nabla J)/q + Gn Rn$

where PSI is the electrostatic potential and EPSILON is the semiconductor dielectric permittivity; ND<sup>+</sup> and NA<sup>-</sup> are ionized donor and acceptor concentrations, respectively; RHOF is a fixed space charge density which may be present in insulating material; n and p are electron and hole concentrations, respectively. Though the Fermi-Dirac statistics should be used in the semiconductor, the Maxwell-

Boltzmann statistics is employed instead, because it is simple and still a good approximation. Then, electron and hole density can be expressed by

- (3.4) n=NC\*EXP[(Efn-Ec)/K]=ni\*EXP[q\*(PSI-PHIn)/(k\*T)]

- (3.5) p=NV\*EXP[(Ev-Efp)/K]=ni\*EXP[q\*(PHIp-PSI)/(k\*T)]

where ni is the intrinsic carrier density; T is the absolute temperature, and k is the Boltzmann constant; PHIn and PHIp are the quasi-Fermi potentials of electrons and holes, respectively.

From Boltzmann transport theory, Jn and Jp can be written as function of electrostatic potential and the quasi-Fermi levels for electrons and holes

- (3.6)  $J_{n=-q*U_n*n*} \nabla PHI_n$

- (3.7)  $J_{p=-q*Up*P*}\nabla_{PHIp}$

Alternatively, Jn and Jp can be written as function of PSI, n, and p, consisting of drift and diffusion components:

- (3.8)  $Jn=q*Un*En*n+q*Dn*\nabla n$

- (3.9) Jp=q\*Up\*Ep\*p+q\*Dp\*♡p

Where Un and Up are the electron and hole mobilities; Dn and Dp are electron and hole diffusivities; En = Ep = E =  $-\sqrt{PSI}$

by neglecting the effects of band-gap narrowing and assuming Boltzmann carrier statistics.

Basically, the Poisson equation is solved numerically using a five point finite-difference approximation. The grid structure used by PISCES-II is rectangular in first stage and has nonuniform spacing both in the horizontal and vertical directions. The grid spacings can be defined to small in regions where the potential changes rapidly, such as the regions near the source, the drain, and also near surface. A maximum of 120 grids are allowed for the horizontal as well as the vertical coordinates. A user can specify total number of grids, the minimum spacing and geometrical ratio for both x and y directions. PISCES-II two basic numerical solution techniques: the Gummel method and the full Newton method (sparse direct LU decomposition). The Gummel method is preferred for zero/reverse bias and lowlevel injection simulation, while the full Newton method is good for high-level injection as well as MOSFET saturation conditions.

In Newton's method, all the variables PSI, n, and p are solved for the roots of each single equation by Newton-Raphson method which is an iterative scheme to approximate the root by using successive tangents. An initial guess will be given for the unknowns at each node (PSIo, no, po), and

then the new update value will be calculated by solving the linear system which is formed by the derivative of the matrix called Jacobian matrix. This matrix can be solved by Gaussian elimination that is by far the most stable method. But Newton's method takes time and memory for two carriers simulations, for low current solutions the gummel method offers an attractive alternative to inverting the full Jacobian.

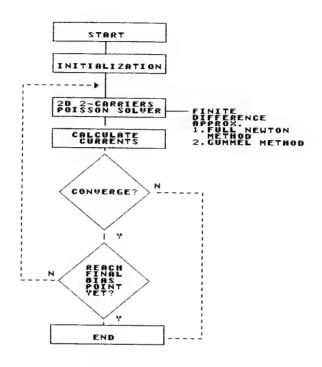

The flow of PISCES-II is shown in Fig.6. The example of pn diode and MOSFET for PISCES will be presented in Sections 3.3 and 3.4.

FIG. 6. FLOW OF THE PISCES

# 3.2 Classification of Device Modeling

A model describes the behavior of a device in a circuit simulation program. Ideally, it would be convenient to have only one model which can fit all the needs. However. different applications call for different requirements of device models. Basically, there are two classes of device models to serve different applications: first, compact models, which use the method of Gummel-Poon or Ebers-Moll. are based on closed form solution to approximate device equation for representing device in circuit simulation. corresponding requirements for these models are accuracy. simplicity to save computing time, understandability, minimal number of model parameters having direct visual effect on device characteristics. Second class is theoretical models which use a numerical method, either finite difference or finite element, to solve nonlinear semiconductor equations including Poisson's equation, current density equations for holes and elections, and continuity equations for holes and electrons. This class of models is based on the fundamentals of solid-state physics predicting electrical behavior of new devices. The corresponding requirements for these models are completely theoretical basis and understanding for the interpretation of device physics.

Process technology of integrated circuits has been improved to fabricate submicron device which encounter a variety of physical effects. Since a theoretical model becomes difficult to manipulate and a compact model results in a loss of predictive capabilities. A compromise is made in developing model, which is a combination of physics based and empirical equations, for circuit simulation.

The device model for circuit simulation computes the terminal currents and charges of the device as a function of the terminal voltages. The terminal currents and charges should be continuous functions of terminal voltages for Newton-Raphson iterations to converge. The Newton-Raphson technique requires the computation of the first derivatives which are usually difficult to obtain analytically. Hence, numerical derivative using either finite difference or finite element method is employed, but this increases the model computation time.

Comparing to device equations, terminal capacitance equations are easy to manage, but it is necessary to formulate the charge equations if the charge conservation is desired.

During model development, it is important to keep in mind the modeling paradox. Although more complex models can potentially represent the device characteristics more accurately, it is more difficult to extract all the parameters for such complex models. Therefore, if the model parameters are not specified properly, the device characteristics will not be reproduced accurately.

# 3.3 Diode Model Development

The analysis and design of integrated circuits depends heavily on the use of suitable models for integrated circuit components. In order to use models properly, the knowledge of how the models have been developed becomes important and desirable. In this section, a pn diode will be discussed by using PISCES.

In this example, a basic simulation procedure is illustrated. There are usually three separate activities in a PISCES simulation. First, a grid is created for equilibrium potential distributions which are based on the geometry of the device structure and the doping. Second, solutions are obtained for various bias points using the grid which is generated by first step, with optional grid refinement dependent on the solution. Finally, solutions are analyzed and plotted. The three phases are usually maintained in separate input decks. An interactive grid generation preprocessor (IGGI) can be involved at the first stage, and the plotting post-processor is of use for solution analysis.

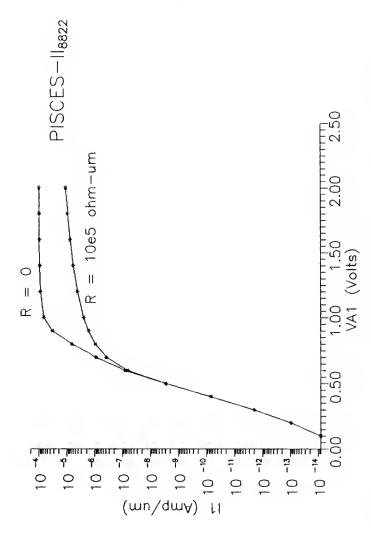

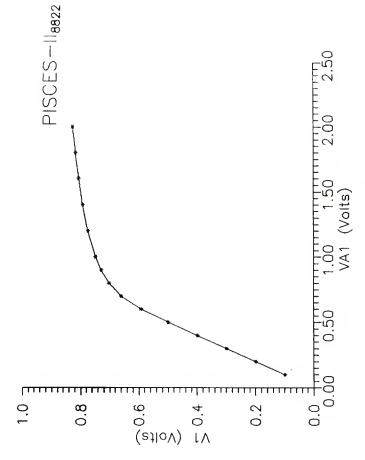

Figure 7 is an input file for PISCES to generate and plot the mesh for the diode example. Fig. 8 shows a potential distribution for a cross section of the diode. The doping profile is plotted versus distance into the device shown in Fig. 9. In Fig. 10 the input file of the second stage is

shown, in which a new file will be opened to save the calculated data into I-V or AC file. Fig. 11 shows a value of contact resistor in CONTACT card and that value is the only difference from the previous input file. In Figs. 10 and 11 the MODEL card specifies Shockley-Read-Hall and Auger recombination. It also specifies the concentration dependent mobility from table look-up and a lateral field-dependent model which has implemented for Si and GaAs. Fig. 12 is input file for stage 3. LOAD card is used to load information from the log files generated in the second stage. The output files have been written in ASCII code rather than the default (binary) by using ascii parameter in the PLOT.1D card. Fig. 13 shows I-V curves with the different resistors. Owing to the lumped resistance, actual contact bias may differ from the applied bias which can be seen Fig. 14. In Fig. 15 the input file for transient analysis with step function voltage is given. Plots are shown in Fig. 16, 17, and 18. Transient analysis with ramp function voltage are shown in Fig. 19 to Fig. 21. The input file for analysis is represented in Fig. 22. The capacitance conductance of the pn diode are analyzed in Figs. 23 and respectively. Fig. 23 shows the diode capacitive effects the reverse- and forward-biased pn junction. There exists a region depleted of carriers in the reverse bias pn junction in which a parallel plate capacitor is formed. When the reverse voltage increases, the depleted region enlarges and the capacitance reduces. When the junction is forward-biased, the large number of minority carriers injected causes a much greater charge storage effect, which is known as diffusion capacitance. But when the forward-biased voltage is greater than the built-in potential barrier, the current will flow through the diode and then the capacitance is too small to be measured.

```

Title pn diode

Generate and plot the mesh for the diode example

There are two kinds of plot device available in this

version: tek4107 and hp2600 series plotter.

option plotdev=tek4107

The mesh card either initiates the mesh generation phase

$

or reads a previously generated mesh.

rect nx=60 ny=3 outf=pn.msh

mesh

The x.m and y.m cards specify the location of lines (1)

of nodes (n) in a rectangular mesh. The location is interpreted in microns. Since the junction is at

$

$

micron specified by the DOPING card, the ratio 0.8 is

$

selected to set the space grid lines closely around

$

the junction.

n=1 l=0 r=1

x.m

n=20 1=1 r=0.8

x.m

n=60 l=5 r=1.07

x.m

n=1 l=0 r=1

v.m

y.m

n=3 l=1 r=1

The region card defines the location of materials in a

$ rectangular mesh.

region num=1 ix.l=1 ix.h=60 iy.l=1 iy.h=3 silicon

The electrode card specifies the location of electrodes in

in a rectangular mesh.

elec

num=1 ix.l=1 ix.h=1 iy.l=1 iy.h=3

elec

num=2 ix. l=60 ix. h=60 iy. l=1 iy. h=3

The doping card dopes selected regions of the device.

doping reg=1 n.type conc=1e15 uniform

$ JUNC is the location of the junction (um).

doping

reg=1

p. type conc=1e19 x.r=0 y.top=0

junc=1.0

ratio=1 gauss

Plot. 2d does not work for us so far.

plot.2 bound no.tic no.fill grid outf=pn1.grid

The plot. 1d card plots a specific quantity along a line

segment through the device (mode A), or plots an I-V curve

of data (mode B).

log dop abs a.x=0 b.x=5 b.y=0.5 a.y=0.5 points ascii

plot.1

outf=dop1.asc

$

End card.

end

```

Fig. 7. Input file of first stage for diode device.

8. Potential distribution expressed in the mesh.

Doping profile in the diode device. Fig. 9.

```

title pn diode

$ Steady-state forward bias analysis (w/ contact resistor)

option plotdev=tek4107

$ Load the potential distribution generated in the first

stage.

mesh

in=pn.msh

It has a lumped resistance 10e+5 ohm/um.

contac num=1 resis=1e5

SYMB card performs a symbolic factorization in preperation

for LU decomposition using Newton method in this case.

symb

newton carr=2

METHOD

provide parameters used to

datermine the

convergence of solution method using automated

Newton-Richardson in this case.

method

rhsnorm xnorm autonr

models temp=300 srh auger conmob fldmob print

SOLVE card instructs PISCES to perform a solution for one

$ or more specified bias points.

init ascii outf=pn2a0-r.asc

$ Any I-V and AC data subsequent to the card will be saved.

outf=IV-r.log

log

solve

vstep=0.1 nsteps=10 elect=1

solve vstep=0.2 nsteps=4 elect=1

solve v1=2 ascii outf=pn2a2-r.asc

$

end

```

Fig. 10. Input file of second stage for diode device.

```

$ Steady-state forward bias (w/o resistor)

mesh

in=pn.msh

$ If the CONTACT card is not specified, the lumped

$ resistance is zero.

symb

newton carr=2

method rhsnorm xnorm autonr

models temp=300 srh auger conmob fldmob print

solve

init ascii outf=pn2a0-nr.asc

log

outf=IV-nr.log

solve vstep=0.1 nsteps=10 elect=1

solve vstep=0.2 nsteps=4 elect=1

solve v1=2 ascii outf=pn2a2-nr.asc

$

end

```

title pn diode

Fig. 11. Input file of second stage for diode without contact resistor.

```

Title Plot file

$ Plot figures 13 and 14.

mesh inf=pn.msh

$ FIGURE 13

$option asave=fig3b.sav

$ Load the I-V data generated in second stage.

plot.1d inf=IV-nr.log x.ax=val y.ax=il log abs points

ascii

outf=pn4.asc

plot.1d inf=IV-r.log x.ax=va1 y.ax=i1 log abs points

ascii

outf=pn4r.asc

$ FIGURE 14

plot.1d inf=IV-r.log x.ax=va1 y.ax=v1 points min=0 ascii

outf=pn4v.asc

end

```

Fig. 12. Input file of third stage for plot.

Fig. 13. I—V characteristics with two different contact resistance.

Fig. 14. The relation between VA1 and V1.

```

title pn diode

$ Transient analysis - voltage step

in=pn.msh

mesh

contac num=1 resis=1e5

symb

newton carr=2

method rhsnorm xnorm autonr

models temp=300 srh auger conmob fldmob print

$ Load the file generated in the second stage.

inf=pn2a2-r.slv

load

log

outf=IV-step.log

solve

solve v1=-2 tstep=10e-12 tstop=100e-9

$ FIGURE 16

plot.1d

x.ax=time

y.ax=i1 x.max=10e-9

points ascii

outf=fig6a.asc

$ FIGURE 17

plot.1d x.ax=time

y.ax=va1 x.max=10e-9

points

ascii

outf=fig6b1.asc

plot.1d

x.ax=time

y.ax=v1 x.max=10e-9 points

ascii

outf=fig6b2.asc

$ FIGURE 18

$ Integration can be performed in the PLOT.1D card.

plot.1d x.ax=time y.ax=i1 x.max=10e-9 points integral ascii

outf=fig6c.asc

$

end

```

Fig. 15. Input file for transient analysis.

with step function voltage. (y) 17. Transient and i. Ö

o tage

```

title pn diode

$ Transient analysis - voltage ramp

mesh in=pn.msh

contac num=1 resis=1e5

newton carr=2

method rhsnorm xnorm autonr

models temp=300 srh auger conmob fldmob print

load

inf=pn2a2-r.slv

log

outf=IV-ramp.log

solve

$ Endramp specifies the exact end of the ramp in the running

$ time. It starts at t=t0 and ends at t=endramp.

solve v1=-2 tstep=10e-12 tstop=10e-8 endramp=2.5e-9

option plotdev=tek4107

$ FIGURE 20

x.ax=time y.ax=i1 x.max=10e-9 points

plot. 1d

ascii

outf=fig8b.asc

$ FUGURE 21

plot.1d

x.ax=time y.ax=val x.max=10e-9

points

ascii

outf=fig8c1.asc

plot.1d x.ax=time y.ax=v1 x.max=10e-9 points ascii

outf=fig8c2.asc

$

end

```

Fig. 19. Input file for transient analysis with ramp function voltage.

Fig. 21. Transient analysis with ramp function lorage

```

$ AC analysis

mesh

in=pn.msh

symb

newton carr=2

method rhsnorm xnorm autonr

models temp=300 srh auger conmob fldmob print

$ Load the file generated in the second stagte.

load

inf=pn2a0-r.slv

log

acfile=AC.log

solve

local v1=-3 ac freq=1e3

solve

vstep=0.25 nsteps=12 elect=1 ac freq=1e3

solve

vstep=0.1 nsteps= 5 elect=1 ac freq=1e3

option plotdev=tek4107

$ FIGURE 23

plot.1d x.ax=v1 y.ax=c12 points ascii outf=fig9b.asc

$ FUGURE 24

plot.1d x.ax=v1 y.ax=g12 log abs points ascii outf=fig9c.asc

end

```

title pn diode

Fig. 22. Input file for AC analysis

## 3.4 An Example of the MOSFET Device in PISCES

A brief introduction of the MOSFET input file is presented. Fig. 25 shows input deck of PISCES which is automatically generated by MOSMESH program. The structure and doping information of the MOSFET for the MOSMESH are listed as follows:

lateral diffusion constant = 0.8

poly gate width = 2 um

spacer thickness = 2 um

poly metal spacing = 2 um

substrate doping = 1e15

gate oxide thickness = 250 ang

channel threshold adjust

type doping = P

peak doping concentration = 1e16

peak doping location = 0.1

dose = 2e12

lightly doped drain

type doping = N

peak doping concentration = 1e18

peak doping location = 0

junction depth = 0.25 um

drain doping

type doping = N

peak doping concentration = 1e20

peak doping location = 0

junction depth = 0.1 um

maximum drain substrate reverse bias = 0.1

maximum source substrate reverse bias = 0

drain voltage = 0.1

starting gate voltage = -1.0

sweep gate voltage = 2.0

gate bias increment = 0.1

After the above values are entered for the MOSMESH, an output file which can be the input file for PISCES is produced. Fig. 26 shows the IV characteristics of this MOSFET.

# title MOSMESH automatic mesh - Version 8822

\$starting mesh card

mesh nx=45 ny=22 rect outf=nmesh

\$x mesh locations

x.mesh node=1 location=-3.1 rat=1

x.mesh node=2 location=-3 rat=1

x.mesh node=8 location=-1.59265 rat=1.25

x.mesh node=9 location=-1.37133 rat=1.25

x.mesh node=10 location=-1.15 rat=0.8

x.mesh node=11 location=-1 rat=0.8

x.mesh node=11 location=-0.72 rat=0.64

x.mesh node=31 location=0.72 rat=1

x.mesh node=33 location=0.72 rat=1

x.mesh node=35 location=1 rat=1.33

x.mesh node=36 location=1.15 rat=2.51

x.mesh node=37 location=1.59265 rat=0.8

x.mesh node=38 location=1.59265 rat=0.8

x.mesh node=44 location=3 rat=0.8

x.mesh node=45 location=3.1 rat=1

#### \$y mesh locations

y.mesh node=1 location=-0.025 rat=1 y.mesh node=3 location=0 rat=0.8

y.mesh node=4 location=0.01 rat=1

y.mesh node=14 location=0.35 rat=1.24

y.mesh node=19 location=1.05896 rat=1.25

y.mesh node=22 location=2 rat=1,25

\$eliminate some nodes that aren't needed

elim y.dir ix.l=11 ix.h=35 iy.l=5 iy.h=22

elim y.dir ix.l=1 ix.h=45 iy.l=14 iy.h=22

\$region definitions

region num=1 ix.l=1 ix.h=45 iy.l=1 iy.h=3 oxide region num=2 ix.l=1 ix.h=45 iy.l=3 iy.h=22 silicon

\$Gate = 1 Source = 2 Drain = 3 Bulk = 4 electrode num=1 ix.l=11 ix.h=35 iy.l=1 iy.h=1 electrode num=2 ix.l=1 ix.h=2 iy.l=3 iy.h=3 electrode num=3 ix.l=44 ix.h=45 iy.l=3 iy.h=3 electrode num=4 ix.l=1 ix.h=45 iy.l=22 iy.h=22

\$Doping Information

\$ junction depth is 0.35um

doping reg=2 uniform x.lef=-3.1 x.rig=3.1

```

y.top=0.0 y.bot=2 conc=1.000000e+15 p.type

$ Channel Doping Region

doping reg=2 gauss char=0.564191 peak=0.1 conc=2.000000e+16

p.type x.lef=-3.1 x.rig=3.1 ratio.la=0.8

$ Lightly Doped Source

doping reg=2 gauss char=0.133168 peak=0 conc=1.000000e+18

n.type x.lef=-3.1 x.rig=-1 ratio.la=0.8

$ Lightly Doped Drain

doping reg=2 gauss char=0.133168 peak=0 conc=1.000000e+18

n.type x.lef=1 x.rig=3.1 ratio,la=0.8

$ Heavily Doped Source

doping reg=2 gauss char=0.0736796 peak=0 conc=1.000000e+20

n.type x.lef=-3.1 x.rig=-1.15 ratio.la=0.8

$ Heavily Doped Drain

doping reg=2 gauss char=0.0736796 peak=0 conc=1.000000e+20

n.type x.lef=1.15 x.rig=3.1 ratio.la=0.8

gate characteristics. Vd is 0.100000, minVg is -0.100000

maxVg is 2,000000

symb gummel carriers=1 electrons

method iccg damped

models srfmob

$ change the below line if another gate material is used

contac num=1 n.poly

$ solve for the initial step. save in file initial

solve initial v1=-0.100000 outfile=initial

$ save I-V information in gateIV.log

log ivfile=gateIV.log

regrid potential step=0.2

symb gummel carriers=1 electrons

method iccg damped

solve

v1=-0.100000 v3=0.100000 vstep=0.100000 nsteps=21

electrode=1

$ plot statement in ascii format in file iv.ascii

plot.1d x.axis=v1 y.axis=i3 ascii outfile=iv.ascii

end

```

Fig. 25. A input file of MOSFET for PISCES.

#### 4.0 CIRCUIT SIMULATION

# 4.1 SPICE: Circuit Simulator

SPICE, which stands for simulation program with integrated circuit emphasis, is a general-purpose circuit simulation program developed at the University of California at Berkeley for nonlinear dc, nonlinear transient, and linear ac analysis. Circuits can contain resistors, capacitors, inductors, mutual inductors, independent voltage and current sources, four types of dependent sources, transmission lines, and the four most common semiconductor devices: diodes, BJTs, JFETs, MESFET, and MOSFET.

SPICE has built-in models for the semiconductor devices, and the user need specify only the pertinent model parameter values. The model for the BJT is based on the integral charge model of Gummel-Poon; however, if the Gummel-Poon parameters are not specified, the model reduces to the simpler Ebers-Moll model. In either case, charge-storage effects, ohmic resistances, and a current-dependent output conductance can be included. The diode model can be used for either junction diodes or Schottky barrier diodes. The JFET model is based on the FET model of Shichman-Hodges. Four MOSFET models are implemented: MOS1 is described by a square-law I-V characteristic, MOS2 is an analytical model, and MOS3 is a

semiempirical model. MOS4 is the Berkeley Short-channel IGFET Model (BISM). MOS2, MOS3, and MOS4 include second-order effects such as channel-length modulation, subthreshold conduction, scattering limited velocity saturation, small-size effects, and charge-controlled capacitances[1].

SPICE is node voltage-oriented, so any node voltage can be requested. Element currents flowing through independent voltage sources can also be requested. Tabular lists and printer plots are available.

#### 4.2 Semiconductor devices in SPICE

The models for the five semiconductor devices included in SPICE require many parameter values. Moreover, many devices in a circuit often are defined by the same set of device model parameters. For these reasons, a set of device model parameters is defined on a separate .MODEL card and assigned a unique model name. The device element cards in SPICE then reference the model name. This scheme alleviates the need to specify the same model parameters on each device element card.

Each device element card contains the device name, the nodes to which the device is connected, and the device model name. In addition, other optional parameters can be specified for each device: geometric factors and an initial condition.

The value of input parameters for the five semiconductor

device models will be calculated to determine the accuracy of the models. These input parameters should be related to the particular process used at each manufacturing site. In the next section, MOSFET models will be emphasized and discussed.

#### 4.3 MOSFET Model

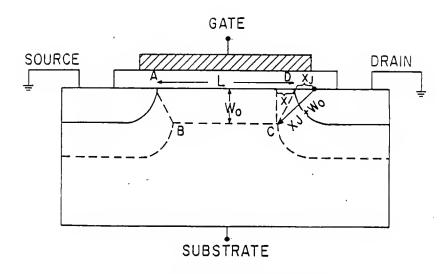

The metal-oxide-semiconductor field effect transistor (MOSFET) is the most important device for for VLSI circuits. Figure 27 shows the structure of a MOSFET in which the region covered by the gate and thin oxide is the channel, and its length is L. This length is indicated in the SPICE input deck of the MOS transistor. Leff is the effective channel length which is defined as the distance between two diffused regions. The width of the channel, W, is the width of area covered by the thin oxide between the thick field oxide.

# 4.3.1 The MOS Capacitor

The MOS capacitor is not only the basis of the MOS transistor, but is a useful nonlinear device whose nonlinearity is fundamental to a number of circuit techniques. The MOS capacitor combines the characteristics of the parallel plate capacitor. Cox, and the pn junction diode. Since the charges on a plate will be mirrored by charges on another plate, Cox is independent of the applied voltage. The pn junction capacitor, Csi, which has been discussed previously is voltage dependent. The silicon surface represents an equipotential plane that acts virtually as a common plate for both capacitors in series. In order to describe the latter capacitance by an equivalent parallel

Fig. 27. Structure of MOSFET[3].

plate capacitor, we must determine the effective depth below the silicon surface at which an imaginary bulk plate should be placed. This effective depth is referred to as the Debye Length.

Since we do not contact the silicon surface, we induce a voltage variation between the silicon interface and the silicon bulk by varying the voltage between the gate and the silicon bulk. When a voltage variation is positive with respect to p-type substrate, a positive charge is induced at the metal-oxide interface. The positive charge at the metaloxide repels holes from silicon surface, leaving behind negatively charged, unneutralized and immobile acceptor ions. Note that the charge of acceptor ions balances the positive charge induced at the metal-oxide interface and the majority carriers, holes, follow the signal changing at the terminal. The difference in the depth of distribution of free carriers between the metal and silicon lies in the concentration of the free carriers. The concentration of electrons in metal is in the order of  $10^{23}~{\rm cm}^{-3}$  and in silicon is roughly in the order of  $10^{16}$  cm<sup>-3</sup>. Consequently, the depth of distribution of free carriers that follow the signal is considerably smaller in metal than in silicon. The number of free carriers that follow the voltage decreases exponentially with increasing depth. Therefore, deep in the silicon bulk the free carriers which are shielded by the free carriers lying

above them do not "feel" the voltage variation. The depth below the surface at which the number of free carriers that follow the voltage signal has decreased to 37% of the free carrier concentration is the Debye Length. This results in a capacitance per unit area that is less than Cox, and is the series connection of these two capacitors. Therefore,

### (4.1) 1 / Cmos = 1 / Cox + 1 / Csi

The capacitance of a MOS capacitor in inversion region is more complicated than it was in depletion accumulation. Because the electrons which are observed equilibrium at the inversion layer come from the thermal generation of electrons at the oxide-silicon interface. process is slow which is in the order of millisecond. Thus if we measure the capacitance of the MOS structure in inversion very slowly, only the capacitance value of Cox is observed. This is because the thermal generation of carriers will short out the depletion layer capacitance. But when the applied ac signal is changed rapidly while the dc bias voltage is varied slowly, the inversion layer cannot respond to the ac applied signal. The number of charges in the silicon space-charge layer is modulated instead of the movement of the holes at the far edge of the depletion region. The capacitance then corresponds to the series combination of the oxide

capacitance and the depletion region capacitance.

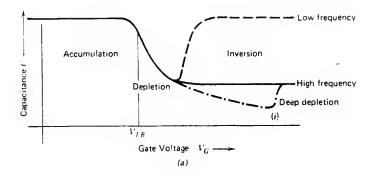

Since the depletion region reaches a maximum width when the device goes to strong inversion, the depletion region capacitance remains constant as the bias voltage is increased further. This high frequency C-V curve is shown by the solid line in Fig 28.

#### 4.3.2 MOS Transistor Model

In SPICE3A7 there are four different MOS models available to the users. The Level 1 model is the simple Shichman-Hodge model which has been found necessary checking out the correctness of hand calculations and for understanding or developing new circuit. The Level 2 model is an analytical one-dimensional model which incorporates most second order effects of small size devices. The Level 3 model is a semi-empirical model described by a set parameters which are defined by curve-fitting rather than physical background. The Level 4 model is the Berkeley Shortchannel IGFET Model (BSIM) which is used in the design with a process characterization system that provides all the parameters. There are no default values for the parameters and leaving one parameter out is considered an error. Thus, it is necessary for the circuit designer to know what are the equations governing the behavior of the MOSFET.

(b)

Fig. 28. (a)Small-signal capacitance of a MOS system with p-type silicon. (b)The equivalent circuit for the overall capacitance[14].

#### 4.3.3 Surface Behavior of MOSFETS

The first step in studying the theory of the MOSFET is a behavior of the surface of a semiconductor under the influence of an electric field. This electric field, which is produced by the voltage applied between the gate and the substrate, is perpendicular to the oxide-semiconductor interface.

The reference condition of the surface is when the semiconductor has the same carrier concentrations at the surface as at the substrate. In other words, the concentrations of electrons and holes are not disturbed at the silicon surface when no bias voltage is applied to structure. This state is called the flat-band condition and is achieved by the application of a voltage equal to flat-band voltage between the metal and the silicon.

#### (4.2) VFB = PHIms - Q0 / Cox

where QO is positive charge at the oxide-silicon interface, and therefore it requires a negative charge to neutralize its effect and Cox is the capacitance per unit area of the thin oxide layer. When VGB = VFB, the carrier concentration is constant in the semiconductor; in other words, it is equal to  $N_A$ . The condition VGB < VFB increases the negative charge on the gate and increases the concentration of the holes near the surface in order to balance the gate charge. Thus the

concentration of the p-type carriers at the surface is greater than at the substrate, and this state is called an accumulation. When VGB > VFB, the holes are pushed away from the surface so that the negative charge of the fixed ions restores the balance with the gate charge. The carriers concentration near the surface is less than that in the bulk, and this state is called a depletion. The thickness WO of the depleted region is shown in Fig. 29 and the equation is listed below:

# (4.3) W0 = $SQRT(2*EPSILONsi*PB/q*N_A)$

where PB is the potential across the depleted region. It is interesting to know how the carriers vary in the accumulation, depletion, and inversion regions when a voltage is applied. A solution for this electrostatic potential as a function of y direction, which is perpendicular to the surface and goes into the semiconductor, allows a complete description of the carrier concentration. The electrostatic potential is defined as

## (4.4) PSI=[Ei(y)-Ei(bulk)]/q

The electrostatic potential evaluated at the surface, y=0, will be called the surface potential, PHI. For a grounded bulk, the potential and the electric field are related by

Fig. 29. Cross section of MOSFET[10].

#### (4.5) E = - V PSI

To obtain a solution for PHI, Poisson's equation must be solved. In one dimension, Poisson's equation is

$$(4.6)$$

d PSI/d y = - RHO/EPSILONs

where RHO, the total space-charge density, is defined as

(4.7) RHO =

$$q*(Pp - Np + ND^{+} - NA^{+})$$

The majority carrier concentration, Pp, and the minority carrier concentration, Np, can be expressed as

$$(4.8)$$

Pp=ni\*exp(q\*PSI/kT)

$$(4.9)$$

Np=ni\*exp(-q\*PSI/kT)

where ni is the intrinsic carrier concentration carrier concentration. In the bulk, phi =0 and RHO = 0, hence

$$(4.10)$$

$ND^+ - NA^- = Npo - Ppo$

where Npo and Ppo are the equilibrium densities of electrons and holes, respectively, in the bulk of the semiconductor. The densities of the surface are

(4.11) Ns = Npo \*

$$\exp(q*PHI/(k*T))$$

$$(4.12) Ps = Ppo * exp(q*PHI/(k*T))$$

Therefore, Poisson's equation may be expressed as

(4.13)

$$PS1=-q/RHO*[Ppo*((exp(-z)-1)-Npo*((exp(z)-1))]$$

where z is equal to q\*PS1/(k\*T). Integrating Eq. (4.13) from the bulk toward the surface, transforming it into a form relating potential PS1 to the electric field, and using Gauss's law, the space charge per unit area in the semiconductor can be expressed as

where LD is the extrinsic Debye length for holes, and m is equal to q/(k\*T).

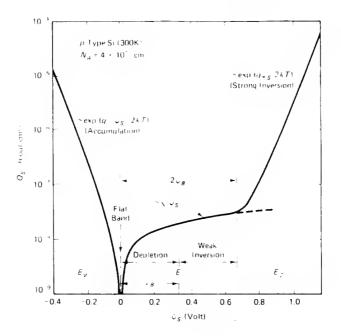

Figure 30 shows the variation in the space charge as a function of the surface potential. Notice the sharp increase in charge as surface increases past 2\*PB. Hence, the onset of strong inversion is defined as occurring when

$$(4.15)$$

PH1=2\*PB=2\*(k\*T/q)\*ln(NA/ni)

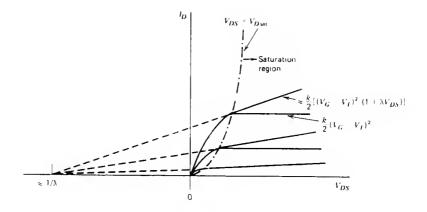

#### 4.3.4 Level 1 Model in SPICE

The level 1 MOSFET model used in SPICE is developed by Shichman and Hodges[7]. In this model, the equations used for linear and saturation regions are listed below:

#### linear region

For VGS > VTH and VDS < VGS - VTH:

Fig. 30. Space charge as a funtion of the surface potential[13].

$$(4.16)$$

IDS=KP\*[W/(L-LD)]\*(VGS-VTH-VDS/2)\*VDS\*(1+LAMBDA\*VDS)

$$(4.17)$$

VTH=VTO+GAMMA(SQRT(2\*PB-VBS)-SQRT(2\*PB)

#### saturation region

For VGS > VTH AND VDS > VGS - VTH:

$$(4.18)$$

IDS= $(KP/2)[W/(L-2*LD)]*(VGS-VTH)^2*(1+LAMBDA*VDS)$

where W and L are the values of the length and width of the channel specified in the SPICE input card. The amount by which the gate electrode overlaps the source and drain regions must be subtracted from the nominal channel length. Thus,

$$(4.19)$$

Leff = L - 2 \* LD

The term 1 + LAMBDA \* VDS introduced in the model is an empirical correction of the conductance in the saturation region. There are five parameters which refer to the electrical behavior of the MOSFET in the this model: KP, VTO, GAMMA, PHI, and LAMBDA.

They can be specified directly in the .MODEL card, or they can be calculated from physical parameters, using the following equations:

(4.20) KP = u \* Cox

(4.21) GAMMA = SQRT(2\*EPSILONs\*q\*NA)/Cox

(4.22) 2 \* PB = 2\*(kT/q)\*ln(NA/ni)

Where Cox = EPSILONs / Tox. In case of conflict, the value of the electrical parameter is read from the input , but they will not be computed from the above equations.

#### 4.3.5 Equations for the Level 2 Model

To obtain a better model for IDS, it is necessary to consider QB which will be affected by the voltage in the channel. According to Meyer model, we have

(4.23) dQB=W\*dx\*GAMMA\*Cox\*SQRT(2\*PB-VBS+VC(x))

Therefore, a new equation for the current can be obtained as

(4.24) IDS=BETA{(VGS-VFB-2\*PB-VDS/2)\*VDS-2/3\*GAMMA[(VDS-VBS+2\*PB)^1.5]}

Where BETA is u\*Cox\*(W/Leff).

This model has validity limits that can be easily reached with the present technology. The method chosen to cope with

this problem is to adapt the model by applying semi-empirical corrections to the basic equations to develop new and more accurate model rather than start again form the basis of the theory.

#### 4.3.6 Level 2 Model in SPICE

This section summarizes the basic equations of Meyer's model as they have been introduced in SPICE. The corrections which are made to simulate effects not provided for in the theory of the basic model in the previous section will be described.

The threshold voltage can be calculated from physical parameters as follows

## (4.26) VTO=PHIms-q\*NSS/Cox+2\*PB+GAMMA\*SQRT(2\*PB)

Where PHIms is the potential difference between gate and substrate. The current in the linear region is calculated through Eq.(4.24), where the corrective term of the channel length is also present. Therefore,

Where BETA is [KP/(1-GAMMA\*VDS)]\*[W/(L-2\*LD). The current in the saturation region is

## (4.28) IDS=ID(sat)\*[1/(1-GAMMA\*VDS)

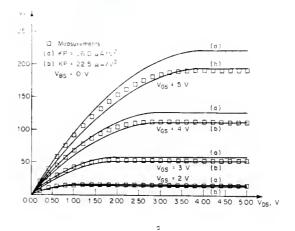

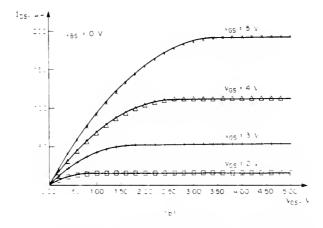

Where ID(sat) is calculated from last equation at VDS = VD(sat), and VD(sat) is from Eq. (4.25). These equations give better result than level 1 model, but they are still not sufficient for a good agreement with experimental data, even for long channel simulation. Therefore, the following will show the modification of the above equations to improve precision for long- and wide-channel MOSFET of level 2 model. Fig. 31 shows how well the level 1 model and level 2 model simulate the measured data.

## Effect of the gate electric field on mobility

The constant mobility has been assumed with the applied voltage so far. A reduction in mobility with an increase in the gate voltage has been observed. In order to simulate this effect, a variation of the parameter KP is introduced in SPICE:

## (4.29) KP'=KP\*{(EPSILONs/EPSILONox)\*[UCRIT\*Tox/(VGS-VTH-UTRA\*VDS)]^UEXP

Where UCRIT is the gate-to-channel critical field parameter for mobility degradation to determine when the mobility begins to decrease and UTRA is the transverse field coefficient chosen between 0 and 0.5 (dimensionless) due to

Fig. 31. (a) Output of level 1 model in SPICE with different KP to simulate the measured data.

(b) Output of level 2 model in SPICE[15].

drain voltage. The use of this formula has been proven a good agreement between SPICE and experimental data.

#### Subthreshold conduction

In the basic model implemented in SPICE, the drift current is calculated only when the surface potential is equal to or greater than 2\*PB. In reality, a concentration of electrons near the surface exists even for VGS < VTH, and therefore there is a current when the surface is not in strong inversion. This current is due to a diffusion of charge carriers between the source and the channel.

## (4.30) IDS=ION\*exp[(VDS-VON)\*q/(n\*k\*T)]

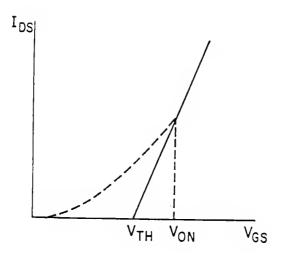

where ION is the current in the weak inversion for VGS=VON, and VON, shown in Fig. 32, is defined as

#### (4.31) VON=VTH+z\*k\*T/q

where z=1+(q\*NFS+Cd)/Cox. NFS is defined as the number of fast surface states which also determines the slope of IDS vs. VGS characteristics in the weak inversion, and Cd is the capacitance associated with the depleted region and is given by:

## (4.32) Cd=dQB/dVDS=GAMMA/[2\*SQRT(2\*PB-VBS)]

It is clear that the model introduces a discontinuity in

Fig. 32. The definition of VON[10].

the derivative and therefore the simulation of the transition region between strong and weak inversion is not very accurate.

## Variation of channel length in the saturation region

An empirical equation using the parameter LAMBDA has been used to calculate the conductance in the saturation region. The level 2 model also offers a physical model to compute the channel length in saturation:

If the parameter LAMBDA is not specified in the .MODEL card, it will be calculated using the following equation:

Where,

$$(4.35) \ Leff-L'=XD*\{(VDS-VD(sat))/4+sqrt[1+(VDS-VD(sat))/4]\}$$

and

(4.36) XD=SQRT[2\*EPSILONs/(q\*NA)]

This model shows a correct dependence of the conductance in the saturation region on Leff. Thus, if the model with constant LAMBDA is used, the transconductance KP does not vary with Leff when VDS > VD(sat).

## Effect of channel length on threshold voltage

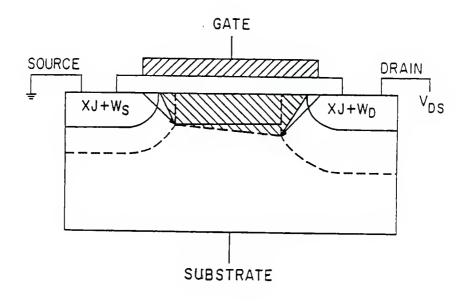

Experimental data has shown that when the channel length is small enough to compare with the thickness of the depleted region, the channel dimensions W and L will have an effect on the threshold voltage. This phenomenon can be explained in two ways from the following equation

#### (4.37) VTH=VFB+2\*PB-QB/Cox

A reduction in the charge QB due to the source and drain depleted region below threshold, or an increase in the channel surface potential due to the effect of the voltage VDS. This effect can be introduced by modifying the value of GAMMA as

where WS and WD, shown in Fig. 33, are the widths of the depleted regions of source and drain, respectively, and are defined as

- (4.39) WS=XD\*SQRT(2\*PHI-VBS)

- (4.40) WD=XD\*SQRT(2\*PHI-VBS+VDS)

Where XD=SQRT[2\*EPSILONs/(q\*NA)]. In practice, a correct analytical model of two-dimensional effects on VTH is very tedious, but it is possible to approximate a good model for

# DASHED ZONE-BULK CHARGE DEPLETED BY GATE FIELD

Fig. 33. The widths of the depleted regions of source and drain[10].

threshold voltage of a short-channel MOSFET with two dimensional numerical model. This type of analysis is time-consuming for a circuit simulation program, but it can be used in the study of physical behavior of short-channel MOSFET.

## Effect of speed limit of the carrier

The calculation of the saturation voltage using Eq. (4.25) is based on the hypothesis that the charge in the channel is zero after pinch off point or near the drain, but it actually has to maintain a minimum concentration of the carriers to sustain the saturation current. This concentration depends on the speed at which the carriers are moving.

The electric field between the drain and the pinch off point can be sufficiently high to drift the carriers at the speed limit, which is the maximum speed allowed for the scattering effect within the crystal lattice. The VMAX can be obtained by

## (4.41) VMAX=ID(sat)/(W\*QI)

where QI is the mobile charge in the channel for VDS=VD(sat).

The model discussed so far provides good results in the simulation of MOSFET with a minimal channel length of about 4 to 5 um, but this model has a discontinuity in the derivative

at the boundary between the saturation region and linear region, and also between subthreshold and linear region. This phenomenon results in a less precise calculation of the conductance and also the cause of difficulties in the convergence of the Newton-Raphson algorithm.

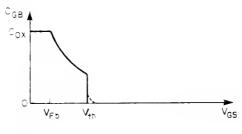

## 4.3.7 Gate Capacitance

SPICE uses a gate capacitance model similar to that proposed by J. E. Meyer[16]. In this simple model, the charge-storage effect is represented by three nonlinear two-terminal capacitors: CGB, CGS and CGD. The equations of this model are listed below and shown in Fig. 34.

## Accumulation region

For VGS < VON - 2\*PB:

$$(4.42) CGB = Cox + CGBO * Leff$$

$$(4.43) CGS = CGSO * W$$

$$(4.44) CGD = CGDO * W$$

#### Depleted region

For VON - 2 \* PB < VGS < VON:

$$(4.45) CGB = Cox* (VON-VGS)/(2*PB)+CGBO*Leff$$

(4.46)

$$CGS = 2/3*Cox*[(VON-VGS)/(2*PB)+1]+CGSO*W$$

$$(4.47) CGD = CGDO * W$$

Fig. 34. Meyer's model of the capacitance[15].

## Saturation region

For Von < VGS < VON + VDS:

$$(4.48) CGB = CGBO * Leff$$

(4.49)

$$CGS = 2/3*Cox + CGSO* W$$

$$(4.50) CGD = CGDO * W$$

#### Linear region

For VGS > VON + VDS:

$$(4.51) CGB = CGBO * Leff$$

$$(4.52) \quad CGB = Cox\{1-[(VGS-VDS-VON)/(2VGS-2VON-VDS)]^2\}+CGSO*W$$

$$(4.53) \quad CGD = Cox\{1-[(VGS-VDS-VON)/(2VGS-2VON-VDS)]^2\}+CGDO*W$$

The voltage VON is calculated from Eq. (4.31). If the parameter NFS is specified in the MODEL card, then VON is equal to VTH.

CGBO, CGSO, and CGDO are the overlap capacitances among the gate electrode and the other terminals outside the channel region. The model introduced in SPICE differs from that developed by Meyer because of the discontinuity between the capacitance with the accumulation surface and the depleted surfaces causes nonconvergence in the Newton-Raphson algorithm.

## 4.3.8 Junction Capacitance

The capacitance of the diffused regions of the source and

drain is simulated with the pn junction model. The total capacitance of a diffused region is calculated from the sum of an area and a perimeter capacitance:

$$(4.54)$$

CBS= $(CJ*AS)/(1-VBS/PB)^MJ+(CJSW*PS)/(1-VBS/PB)^MJSW$

$$(4.55)$$

CBD= $(CJ*AD)/(1-VBS/PB)^MJ+(CJSW*PD)/(1-VBS/PB)^MJSW$

where CJ is the bulk capacitance at zero-bias voltage per square meter and CJSW is zero-bias perimeter capacitance per meter, and PB is the junction potential that can be put in the .MODEL card or calculated from the physical parameters as

## (4.53) PB=Eg/2+(kT/q)\*ln(NB/ni)

The exponential factors have the following default values: MJ = 0.5, for the step-junction approximation, and MJSW = 0.33, for the linearly graded approximation. The junction capacitances are very important not only for the correct description of the circuit to be simulated but also because the convergence of the algorithm is easier if all the nodes are connected to ground with a capacitance. For this reason, it is useful to define the areas of the source and drain diffusions even if the layout has not been done when the designer is writing down the input for SPICE. The use of the default values DEFAD and DEFAS in the OPTIONS card to avoid dangerous floating nodes is recommended.

#### 4.3.9 Equations for the Level 3 Model

This model is developed to simulate short-channel MOSFET which has a channel length up to 2um.

## The basic model of level 3

Many of the equations which have been used in this model are empirical. The purpose is to improve the precision and to limit the complexity of the calculations. This approximation results in the development of more manageable basic equations than used in the level 2 model. The current equation in the linear region is

#### (4.53) IDS=IDS[VGS-VTH-(1+FB)/2\*VDS]\*VDS

where FB=(GAMMA\*FS)/[2\*SQRT(PHI-VBS)]+FN. The FS is a correction factor of short channel effect and FN is a correction factor of narrow channel effect. The details of correction factors and empirical data can be found in Reference[10].

The dependence of mobility on the gate electric field is simulated with a simpler equation than that used for the level 2 model. Thus,

## (4.54) Us=U0/[1+THETA\*(VGS-VTH)]

where THETA is the SPICE parameter for mobility modulation.

## Effect of channel length and width on threshold voltage

Based on the hypotheses mentioned in the level 2 model, the effect of the different thickness of the depleted regions in the cylindrical junction region and under the channel has been considered in the calculation of the fixed charge QB in this model. Then, The equation for the threshold voltage is

where the parameter SIGMA expresses empirically the effect of the threshold voltage on VDS. It is known that the shorter channel length is, the lower the threshold voltage. This effect has a linear relationship between the variation of VTH and VDS, and allow us to introduce the term SIGMA\*VDS. The relationship between SIGMA and Leff is also empirical:

where ETA is a static feedback on the threshold, and its typical value is 1.

## Channel length modulation in the saturation region

The equation of the level 3 model simulates the channel length modulation in saturation as

where EP=ID(sat)/[GD(sat)\*Leff] which is the lateral field at channel pinch-off point; ID(sat) and GD(sat) are the drain current and the drain conductance at saturation respectively; K is an empirical fitting parameter, which is used to prevent a negative channel length, with a typical value of 1.

# Effect of channel length on velocity saturation of hot electrons

The saturation of hot electron velocity lowers the conduction current in the linear region. This model includes a decrease in the effective mobility with the average electrical field between the source and the drain[10],

## (4.60) Ueff=Us/[1+(Us\*VDS)/(VMAX\*Leff)

where Us is the surface mobility. If the parameter VMAX is not input by the user, Ueff is set to Us and then this hot electron effect is not modeled.

## 4.3.10 The Level 4 Model in SPICE

It is also called Berkeley Short-channel IGFET Model (BSIM) which is built upon the Compact Short-channel IGFET Model (CSIM). Since a fully physics-oriented modeling approach usually makes parameter extraction particularly difficult, a semi-empirical approach is used to cope with the rapid advances in technology and to extract parameters

automatically. Proc2Mod is the program which converts a process runsheet file into a sequence of .MODEL cards suitable for a SPICE input deck. This model has a large number of empirical parameters, the extra care has to be taken to define the values of parameters.

#### 4.3.11 Table Lookup Model

This is not a SPICE model, but it has been used extensively. It represents the device characteristics in terms of tables of data points instead of using analytical equations. These data points can be obtained from measurements on the test devices or from device analysis programs if the fabricated device is not available. With the use of table models, the model evaluation time can be reduced considerably while a good accuracy is still maintained. Also, as the technology progresses, the present models may not be adequate to characterize new devices.

For example, the drain current is a function of five variables: VGS, VDS, VBS, Leff, and Weff. Modeling the drain current as a function of all these variables will lead to the use of a five-dimensional table, which is impractical. Therefore, knowledge of the device behavior is used to reduce this five-dimensional table. The threshold voltage is principally a function of VBS. The second order effects which affect the threshold voltage are the short channel effect,

the narrow channel effect, and the drain induced barrier lowering. Thus, the threshold voltage is modeled by three tables:

(4.61) VTH=VT1(VBS)+VT2(VDS, Weff)+VT3(VDS, Leff)

Then, a new variable VA = VTH - VGS can be made. The drain current can then be modeled by one three-dimensional table:

(4.62) ID=ID3(VA, VDS, VBS)

Therefore, the measured or simulated data can be easily transformed into the needed tables and table dimensions can be chosen based on sensitivities of device characteristics.

# 4.4 Charge-Control Model of Dynamic Operation for SPICE in Transient Analysis

In the previous section, the MOSFET has been treated as if all terminal voltage were constant. However, the device is usually used with varying terminal voltages in a circuit. The varying terminal voltages cause the transistor to vary the charges which must be supplied from outside other than transistor itself. The charges are supplied through the device terminal by the extra current which is not predicted by dc theory. In this section the charges and terminal currents will be evaluated.

## 4.4.1 Quasi-static operation

With the charge-control model to analyze the dynamic operation, it is assumed that the variation of the terminal voltages is sufficiently slow, so that the device operates quasi-statically. Therefore, the charges per unit area at any time are assumed identical to those that would be found if dc voltage were used. The total charges of each region can be given by

(4.63)

$$q_G(t) = f_G(v_D(t), v_G(t), v_B(t), v_S(t))$$

$$(4.64)$$

$q_B(t)=f_B(v_D(t), v_G(t), v_B(t), v_S(t))$

(4.65)

$$q_I(t) = f_I(v_D(t), v_G(t), v_B(t), v_S(t))$$

Where  $\mathbf{q}_{G}$  and  $\mathbf{q}_{B}$  are the transient charges stored in the gate and bulk region, respectively.  $\mathbf{q}_{I}$  is due to electrons in the inversion (channel) layer. These electrons, which continuously enter through the source and eventually leave the drain, are not really stored in the device. Hence,  $\mathbf{q}_{I}$  is simply the total charge of the electrons that happen to be in the inversion layer at any given instant.

Assuming there is no leakage in the gate, all the gate current attributed to the displacement current is associated with a changing gate charge:

$$(4.66)$$

$i_G(t)=dq_G/dt$

Similarly, all bulk current ascribed to depleting or recovering acceptor atoms is associated with carriers changing the charge in the bulk:

$$(4.67)$$

$i_B(t)=dq_B/dt$

Finally, the sum of the drain current and source currents represents the total charge changing in the inversion layer:

$$(4.68)$$

$i_D(t)+i_S(t)=dq_T/dt$

Where  $i_D(t)$  is a measure of the number of electrons leaving the device through the drain per unit time and  $-i_S(t)$  is a measure of the number of electrons entering the device

through the source per unit time. When  $v_{\rm G}$  is increasing, the number of electrons in the channel must increase. Therefore, the rate of entering electrons from the source must be temporarily greater than the rate of removing electrons from the drain. Thus,

$$(4.69)$$

$i_D(t)=i_T(t)+i_{DD}(t)$

$$(4.70)$$

$i_{S}(t) = -i_{T}(t) + i_{SD}(t)$

Where  $i_T(t)$  is the "dc-like" current, and  $i_{DD}(t)$  as well as  $i_{SD}(t)$  are responsible for a changing charge  $q_T$  in the channel. From the last three equations,

$$(4.71)$$

$i_{SD}(t)+i_{DD}(t)=dq_{I}/dt$

It also can be expressed as

## (4.72) dq<sub>S</sub>/dt+dq<sub>D</sub>/dt=dq<sub>I</sub>/dt

where a changing charges  $\mathrm{dq}_S$  in time dt cause  $\mathrm{i}_{SD}(t)$  and  $\mathrm{dq}_D$  in time dt cause  $\mathrm{i}_{DD}(t)$ . To simplify the discussion in quasistatic operation, the charge changing which causes current is considered here. The components of these currents will hold for Kirchhoff's law as well. Therefore, the quasi-static approximation is built to evaluate the strong, moderate, and weak inversions, separately, in stead of a general charge sheet model.

#### 4.4.2 Non-Quasi-Static Operation

It is intuitively clear that the assumption of quasistatic operation will be no longer valid if the terminal voltages vary too fast.

The non-quasi-static model is based on an approximate solution to the nonlinear current-continuity equation in the channel[8]. The non-quasi-static operation of the MOSFET is a very difficult mathematical analysis. In SPICE3A7 the analytic non-quasi-static long channel MOSFET for the transient analysis has been implemented. The results of this model is suggested to check accuracy with the PISCES 2-D device simulation.

#### 5.0 AN INTERFACE PROGRAM BETWEEN PISCES AND SPICE