# LEVERAGING PERFORMANCE OF 3D FINITE DIFFERENCE SCHEMES IN LARGE SCIENTIFIC COMPUTING SIMULATIONS

by

Raúl de la Cruz Martínez

Advisors: José María Cela Mauricio Araya Polo

## DISSERTATION

Submitted in partial fulfillment of the requirements for the PhD Degree issued by the Department of Computer Architecture

> Universitat Politècnica de Catalunya Barcelona, Spain

> > October 2015

## Abstract

Gone are the days when engineers and scientists conducted most of their experiments empirically. During these decades, actual tests were carried out in order to assess the robustness and reliability of forthcoming product designs and prove theoretical models. With the advent of the computational era, scientific computing has definetely become a feasible solution compared with empiricial methods, in terms of effort, cost and reliability. The deployment of powerful supercomputers, with thousands of computing nodes, have additionally promoted the extent and use of scientific computing. Large and massively parallel computational resources have reduced the simulation execution times and have improved their numerical results due to the refinement of the sampled domain.

Several numerical methods coexist for solving the Partial Differential Equations (PDEs) governing the physical phenomena to simulate. Methods such as the Finite Element (FE) and the Finite Volume (FV) schemes are specially well suited for dealing with problems where unstructured meshes are frequent owing to the complex domain to simulate. Unfortunately, this flexibility and versatility are not bestowed for free. These schemes entail higher memory latencies due to the handling of sparse matrices which involve irregular data accesses, therefore increasing the execution time. Conversely, the Finite Difference (FD) scheme has shown to be an efficient solution for specific problems where the structured meshes suit the problem domain requirements. Many scientific areas use this scheme for solving their PDEs due to its higher performance compared to the former schemes.

This thesis focuses on improving FD schemes to leverage the performance of large scientific computing simulations. Different techniques are proposed such as the Semi-stencil, a novel algorithm that increases the FLOP/Byte ratio for medium- and high-order stencils operators by reducing the accesses and endorsing data reuse. The algorithm is orthogonal and can be combined with techniques such as spatial- or time-blocking, adding further improvement to the final results.

New trends on Symmetric Multi-Processing (SMP) systems —where tens of cores are replicated on the same die— pose new challenges due to the exacerbation of the memory wall problem. The computational capability increases exponentially whereas the system bandwidth only grows linearly. In order to alleviate this issue, our research is focused on different strategies to reduce pressure on the cache hierarchy, particularly when different threads are sharing resources due to Simultaneous Multi-Threading (SMT) capabilities. Architectures with high level of parallelism also require efficient work-load balance to map computational blocks to the spawned threads. Several domain decomposition schedulers for work-load balance are introduced ensuring quasi-optimal results without jeopardizing the overall performance. We combine these schedulers with spatial-blocking and auto-tuning techniques conducted at run-time, exploring the parametric space and reducing misses in last level cache.

As alternative to brute-force methods used in auto-tuning, where a huge parametric space must be traversed to find a suboptimal candidate, performance models are a feasible solution. Performance models can predict the performance on different architectures, selecting suboptimal parameters almost instantly. In this thesis, we devise a flexible and extensible performance model for stencils. The proposed model is capable of supporting multi- and many-core architectures including complex features such as hardware prefetchers, SMT context and algorithmic optimizations (spatial-blocking and Semi-stencil). Our model can be used not only to forecast the execution time, but also to make decisions about the best algorithmic parameters. Moreover, it can be included in run-time optimizers to decide the best SMT configuration based on the execution environment.

Some industries rely heavily on FD-based techniques for their codes, which strongly motivates the ongoing research of leveraging the performance. Nevertheless, many cumbersome aspects arising in industry are still scarcely considered in academia research. In this regard, we have collaborated in the implementation of a FD framework which covers the most important features that an HPC industrial application must include. Some of the node-level optimization techniques devised in this thesis have been included into the framework in order to contribute in the overall application performance. We show results for a couple of strategic applications in industry: an atmospheric transport model that simulates the dispersal of volcanic ash and a seismic imaging model used in Oil & Gas industry to identify hydrocarbon-rich reservoirs.

To my little Inés, my resilient wife Mónica and my dear family

# Contents

| 1 | Pref  | ace                                        | 1  |

|---|-------|--------------------------------------------|----|

|   | 1.1   | Motivation of this Thesis                  | 1  |

|   | 1.2   | Thesis Contributions                       | 2  |

|   |       | 1.2.1 Thesis Limitations                   | 3  |

|   | 1.3   | Thesis Outline                             | 3  |

|   | 1.4   | List of Publications                       | 4  |

|   | 1.5   | Acknowledgements                           | 6  |

| 2 | Intro | oduction                                   | 9  |

|   | 2.1   | Numerical Methods                          | 9  |

|   | 2.2   | Finite Difference Method                   | 11 |

|   | 2.3   | Implicit and Explicit Methods              | 14 |

|   | 2.4   | Summary                                    | 18 |

| 3 | Ехр   | erimental Setup                            | 19 |

|   | 3.1   | Architecture Overview                      | 19 |

|   |       | 3.1.1 Intel Xeon X5570 (Nehalem-EP)        | 19 |

|   |       | 3.1.2 IBM POWER6                           | 20 |

|   |       | 3.1.3 IBM Blue Gene/P                      | 21 |

|   |       | 3.1.4 AMD Opteron (Barcelona)              | 22 |

|   |       | 3.1.5 IBM Cell/B.E                         | 22 |

|   |       | 3.1.6 IBM POWER7                           | 23 |

|   |       | 3.1.7 Intel Xeon E5-2670 (Sandy Bridge-EP) | 23 |

|   |       | 3.1.8 Intel Xeon Phi (MIC)                 | 24 |

|   | 3.2   | Parallel Programming Models                | 26 |

|   | 3.3   | Programming Languages and Compilers        | 27 |

|   | 3.4   | Performance Measurement                    | 28 |

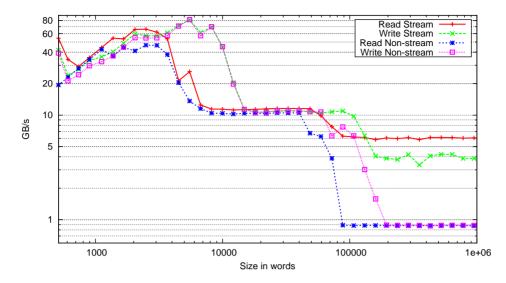

|   | 3.5   | STREAM2                                    | 29 |

|   | 3.6   | Prefetchers                                | 31 |

|   | 3.7   | The Roofline Model                         | 33 |

|   | 3.8   | The StencilProbe Micro-benchmark           | 35 |

|   | 3.9   | Summary                                    | 36 |

| 4 | Opt  | imizing Stencil Computations                                 | 37  |

|---|------|--------------------------------------------------------------|-----|

|   | 4.1  | The Stencil Problem                                          | 38  |

|   | 4.2  | State of the Art                                             | 40  |

|   |      | 4.2.1 Space Blocking                                         | 41  |

|   |      | 4.2.2 Time Blocking                                          | 42  |

|   |      | 4.2.3 Pipeline Optimizations                                 | 43  |

|   | 4.3  | The Semi-stencil Algorithm                                   | 45  |

|   |      | 4.3.1 Forward and Backward Updates                           | 46  |

|   |      | 4.3.2 Floating-Point Operations to Data Cache Access Ratio   | 47  |

|   |      | 4.3.3 <i>Head</i> , <i>Body</i> and <i>Tail</i> computations | 48  |

|   |      | 4.3.4 Orthogonal Algorithm                                   | 48  |

|   | 4.4  | Experiments                                                  | 55  |

|   |      | 4.4.1 Data Cache Accesses                                    | 55  |

|   |      | 4.4.2 Operational Intensity                                  | 57  |

|   |      | 4.4.3 Performance Evaluation and Analysis                    | 60  |

|   |      | 4.4.4 SMP Performance                                        | 70  |

|   | 4.5  | Summary                                                      | 73  |

| 5 | SMI  | Γ, Multi-core and Auto-tuning Optimizations                  | 75  |

|   | 5.1  | State of the Art                                             | 76  |

|   | 5.2  | Simultaneous Multithreading Awareness                        | 78  |

|   | 5.3  | Multi-core and Many-core Improvements                        | 81  |

|   | 5.4  | Auto-tuning Improvements                                     | 87  |

|   | 5.5  | Experimental Results                                         | 88  |

|   | 5.6  | Summary                                                      | 94  |

| 6 | Peri | formance Modeling of Stencil Computations                    | 97  |

|   | 6.1  | Performance Modeling Overview                                | 98  |

|   | 6.2  | State of the Art                                             | 99  |

|   | 6.3  | Multi-Level Cache Performance Model                          | 101 |

|   |      | 6.3.1 Base Model                                             | 102 |

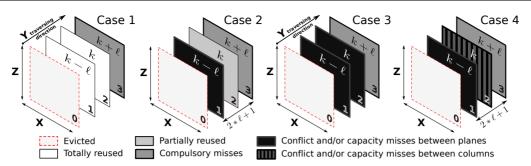

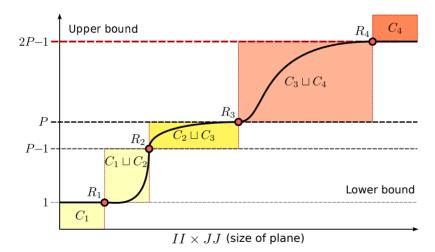

|   |      | 6.3.2 Cache Miss Cases and Rules                             | 104 |

|   |      | 6.3.3 Cache Interference Phenomena: II×JJ Effect             | 106 |

|   |      | 6.3.4 Additional Time Overheads                              | 107 |

|   | 6.4  | From Single-core to Multi-core and Many-core                 | 108 |

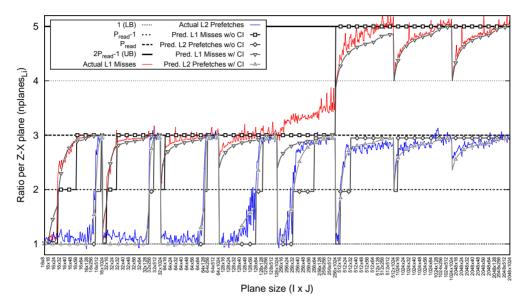

|   | 6.5  | Modeling the Prefetching Effect                              | 109 |

|   |      | 6.5.1 Hardware Prefetching                                   | 109 |

|   |      | 6.5.2 Software Prefetching                                   | 111 |

|   | 6.6  | Optimizations                                                | 112 |

|   |      | 6.6.1 Spatial Blocking                                       | 112 |

|   |     | 6.6.2 Semi-stencil Algorithm                        |

|---|-----|-----------------------------------------------------|

|   | 6.7 | Experimental Results                                |

|   |     | 6.7.1 Preliminary Model Results                     |

|   |     | 6.7.2 Advanced Model Results                        |

|   | 6.8 | Summary                                             |

| 7 | Cas | e Studies 127                                       |

|   | 7.1 | Oil & Gas Industry                                  |

|   |     | 7.1.1 RTM Overview                                  |

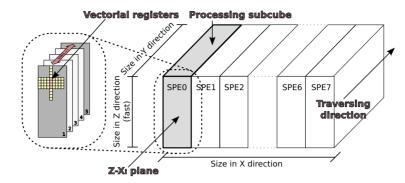

|   |     | 7.1.2 Semi-stencil Implementation in Cell/B.E       |

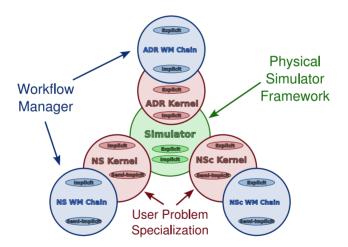

|   | 7.2 | WARIS Framework                                     |

|   |     | 7.2.1 System Architecture                           |

|   |     | 7.2.2 Optimization Module                           |

|   | 7.3 | Atmospheric Transport Modeling - Ash Dispersal      |

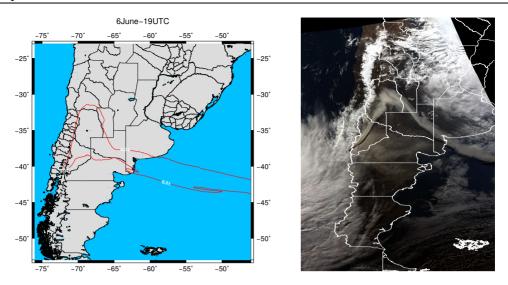

|   |     | 7.3.1 WARIS-Transport Specialization                |

|   |     | 7.3.2 Volcanic Ash Dispersal Results                |

|   | 7.4 | Summary                                             |

| 8 | Con | clusions and Future Work 155                        |

|   | 8.1 | Optimizing Stencil Computations                     |

|   | 8.2 | SMT, Multi-core and Auto-tuning                     |

|   | 8.3 | Performance Modeling of Stencil Computations        |

|   | 8.4 | Case Studies                                        |

| Δ | Nun | nerical Equations 161                               |

|   | A.1 | Heat Equation                                       |

|   | A.2 | Wave Equation         161           161         161 |

|   | A.3 | Advection–Diffusion–Reaction Equation               |

|   |     | FALL3D Governing Equation                           |

|   | 1   |                                                     |

# **List of Figures**

| 2.1  | Translation from the continuous to the discrete problem              | 10 |

|------|----------------------------------------------------------------------|----|

| 2.2  | Discretization of $u(x)$ the domain.                                 | 11 |

| 2.3  | FD example of 1D problem with a 5 points grid domain                 | 15 |

| 2.4  | 7-point stencil layout                                               | 17 |

| 3.1  | Diagram of a dual-socket configuration with Intel Nehalem-EP.        | 20 |

| 3.2  | Diagram of the IBM Cell/B.E. processor.                              | 23 |

| 3.3  | Diagram of the Intel Xeon Phi processor.                             | 25 |

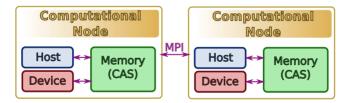

| 3.4  | Shared and distributed memory layout using OpenMP and MPI APIs       | 27 |

| 3.5  | STREAM2 example results                                              | 32 |

| 3.6  | Streaming concurrency effect                                         | 33 |

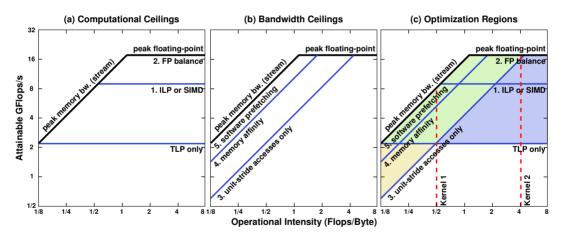

| 3.7  | Roofline model example                                               | 34 |

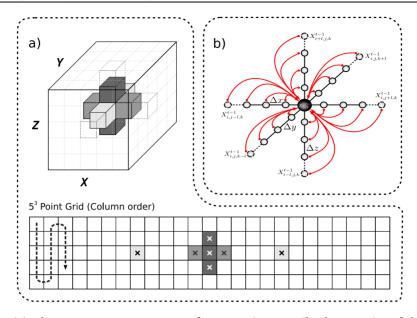

| 4.1  | The memory access pattern for a 7-point stencil                      | 39 |

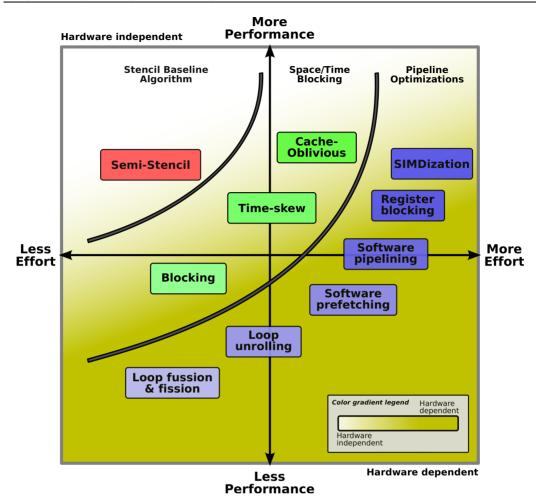

| 4.2  | Characterization of different optimization schemes                   | 41 |

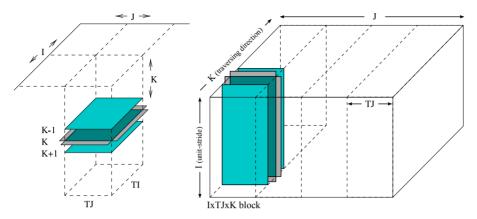

| 4.3  | 3D spatial-blocking                                                  | 42 |

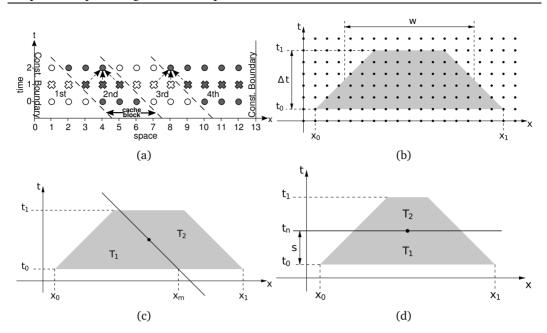

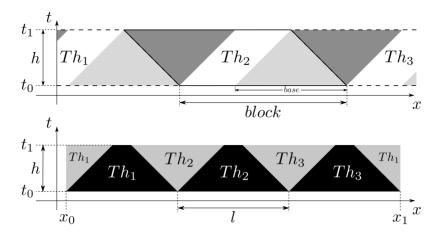

| 4.4  | Execution sequence of time blocking algorithms on 2D problems        | 44 |

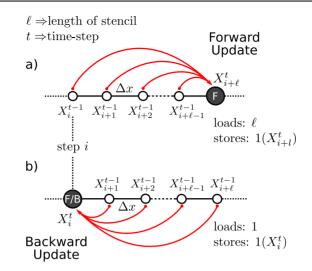

| 4.5  | Forward and backward updates of Semi-stencil                         | 47 |

| 4.6  | Execution example of Semi-stencil algorithm for a 1D problem         | 49 |

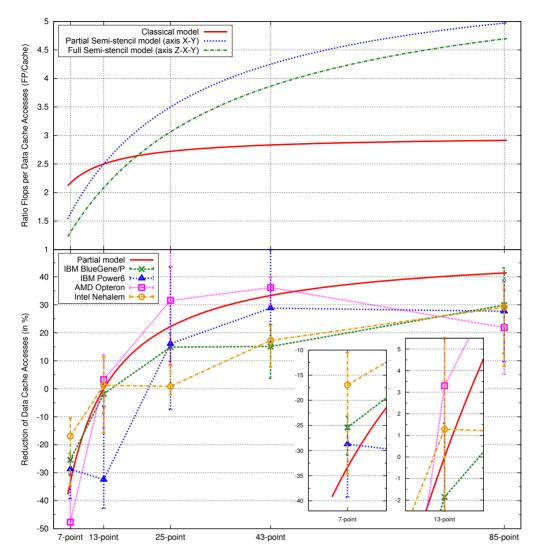

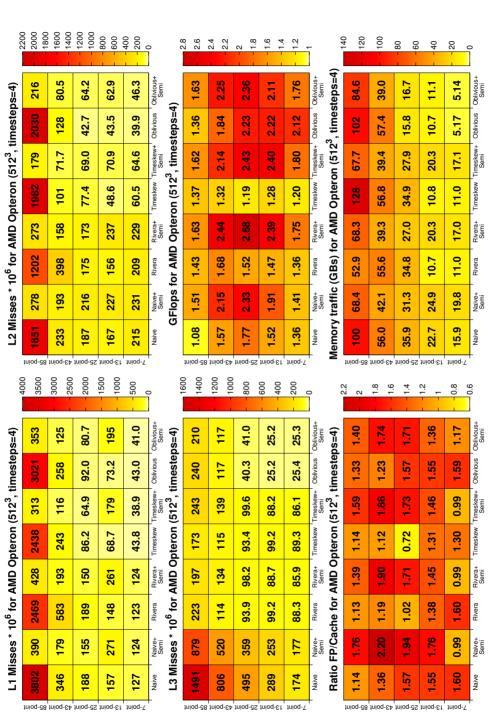

| 4.7  | Ratio of floating-point operations to data cache accesses            | 56 |

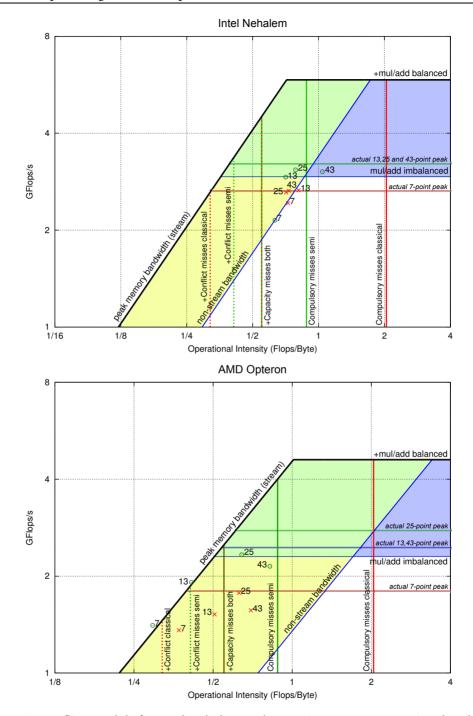

| 4.8  | Roofline models for Intel Nehalem and AMD Opteron                    | 59 |

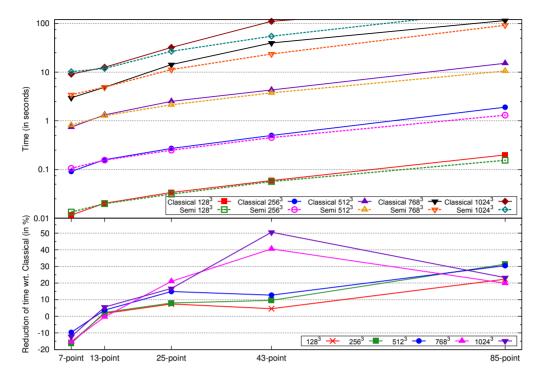

| 4.9  | Comparison between classical and Semi-stencil                        | 61 |

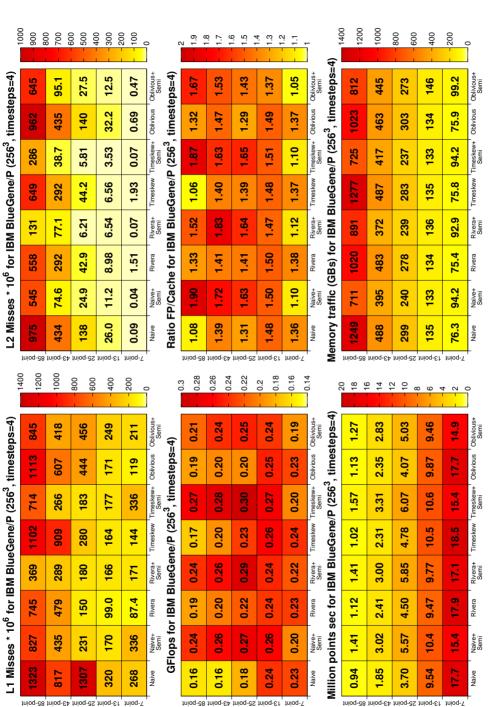

| 4.10 | Matrix of metric results for IBM Blue Gene/P                         | 63 |

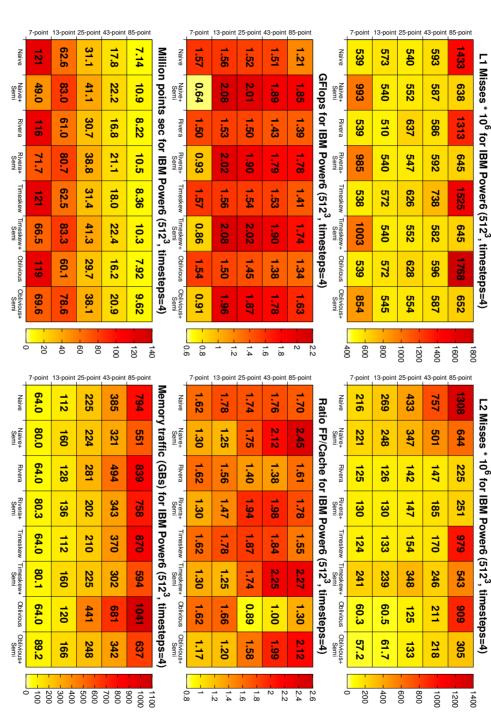

| 4.11 | Matrix of metric results for POWER6                                  | 64 |

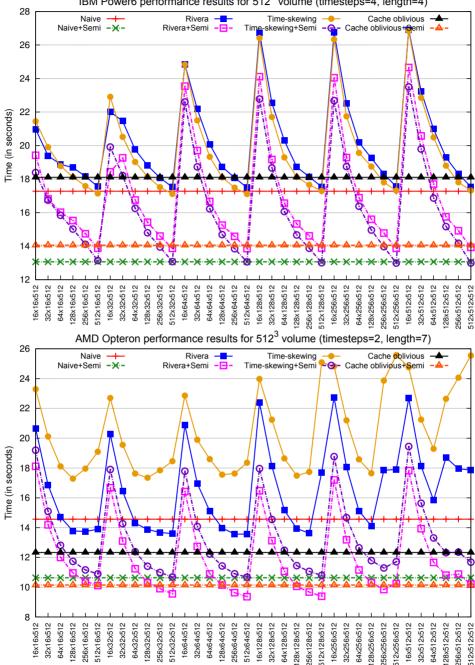

| 4.12 | Matrix of metric results for AMD Opteron                             | 65 |

| 4.13 | Matrix of metric results for Intel Nehalem                           | 66 |

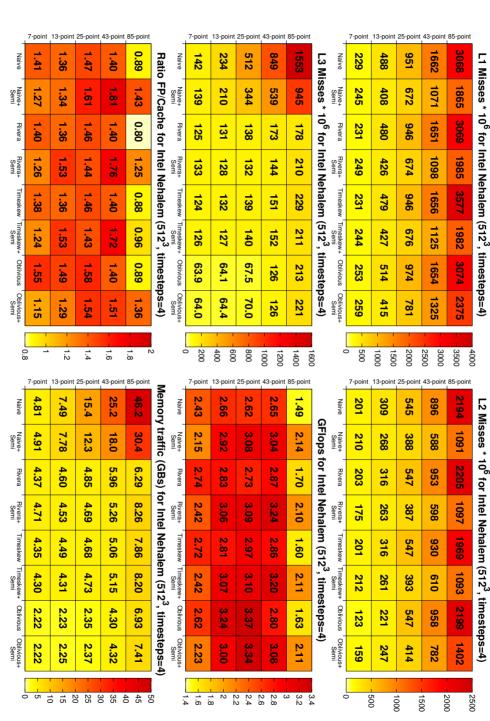

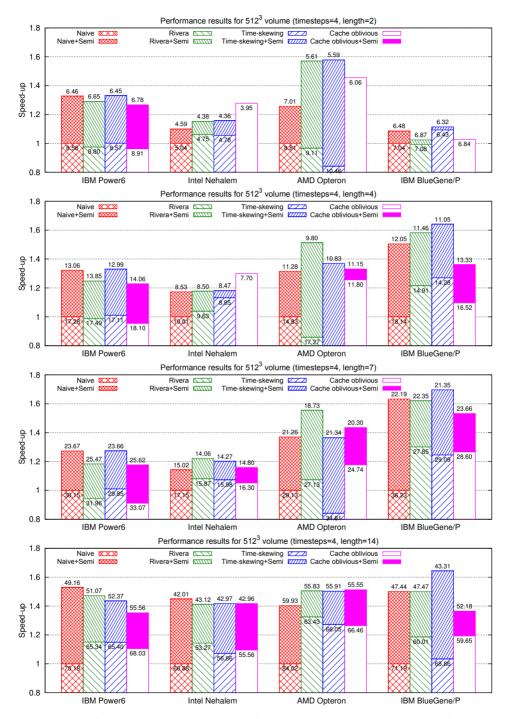

| 4.14 | Speed-up results with respect to the baseline algorithm              | 67 |

| 4.15 | IBM POWER6 and AMD Opteron execution times for all algorithms        | 68 |

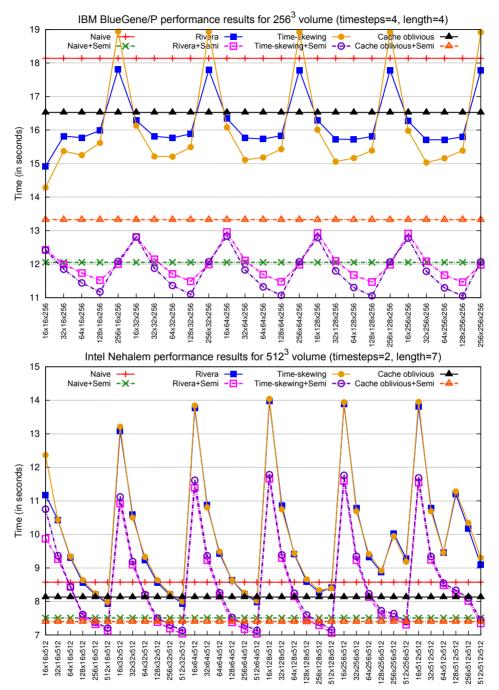

| 4.16 | IBM BlueGene/P and Intel Nehalem execution times for all algorithms  | 69 |

| 4.17 | Thread decomposition strategies for time blocking algorithms         | 71 |

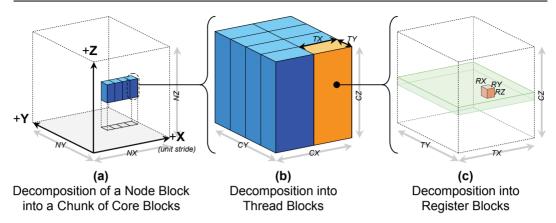

| 5.1  | Four-level problem decomposition proposed by Datta and <i>et al.</i> | 77 |

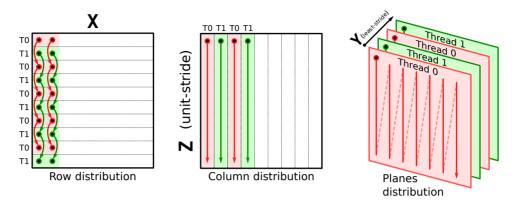

| 5.2  | Data distributions for SMT threads                                   | 79 |

| 5.3  | Thread affinity strategy proposed for MIC architecture               | 80 |

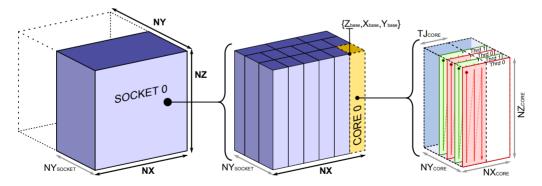

| 5.4  | Intra-node domain decomposition                                                                    | 81  |

|------|----------------------------------------------------------------------------------------------------|-----|

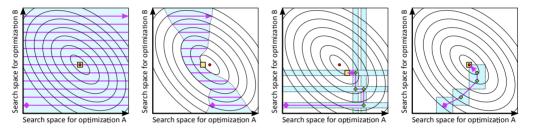

| 5.5  | Auto-tuning strategies for exploring the optimization space                                        | 87  |

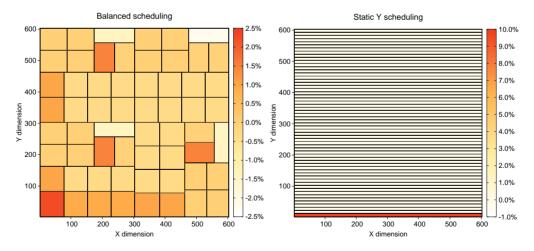

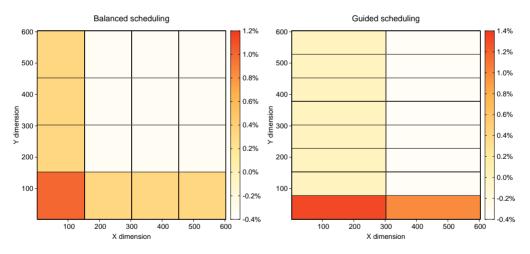

| 5.6  | Imbalance of decomposition strategies for Intel Xeon Phi with a $64 \times 601 \times 75$          |     |

|      | problem size                                                                                       | 91  |

| 5.7  | Imbalance of <i>balanced</i> and <i>static</i> Y schedulings for Intel Xeon Phi with a $64 \times$ |     |

|      | $601 \times 601$ problem size                                                                      | 91  |

| 5.8  | Imbalance of <i>balanced</i> and <i>guided</i> schedulings for Intel Sandy Bridge-EP plat-         |     |

|      | form with a $64 \times 601 \times 601$ problem size                                                | 92  |

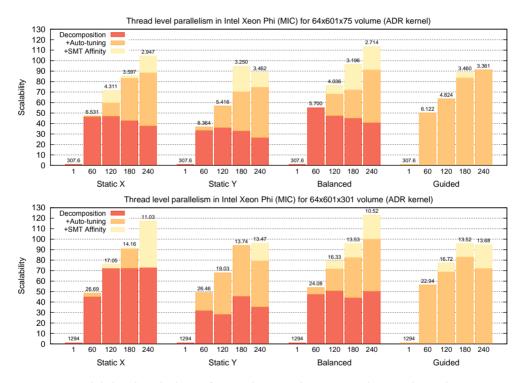

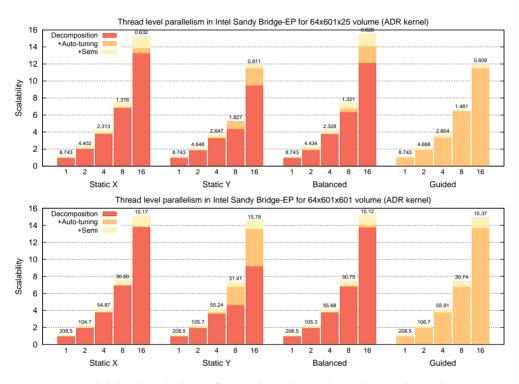

| 5.9  | Scalability break-down for Intel Xeon Phi (MIC)                                                    | 93  |

| 5.10 | Scalability break-down for Intel Sandy Bridge                                                      | 94  |

|      |                                                                                                    |     |

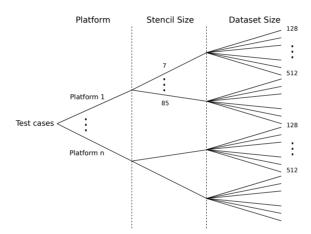

| 6.1  | Test cases tree                                                                                    |     |

| 6.2  | Cases considered for cache misses during the stencil computation                                   |     |

| 6.3  | The different rules $R_1$ , $R_2$ , $R_3$ and $R_4$                                                |     |

| 6.4  | Cache interference effect as a function of problem size                                            |     |

| 6.5  | STREAM2 results for Intel Xeon Phi architecture                                                    | 109 |

| 6.6  | L2 prefetching efficiency for Intel Xeon Phi architecture                                          | 111 |

| 6.7  | Modeling of spatial blocking optimization                                                          | 113 |

| 6.8  | Work-flow of the model methodology with feedback mechanism.                                        | 115 |

| 6.9  | AMD Opteron results for the preliminary model with a 85-point stencil $\ldots$                     | 117 |

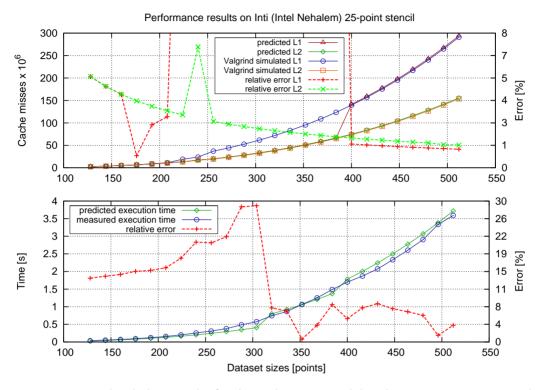

| 6.10 | Intel Nehalem results for the preliminary model with a 25-point stencil $\ldots$                   | 118 |

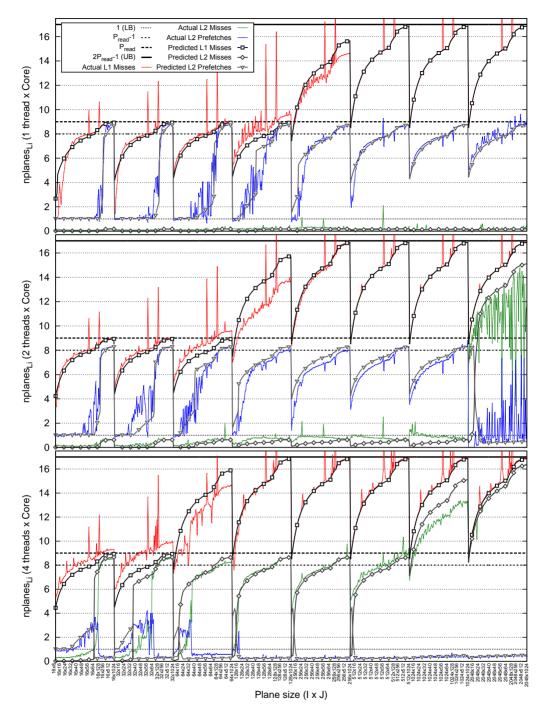

| 6.11 | Actual and predicted for prefetched and non-prefetched cache-lines                                 | 121 |

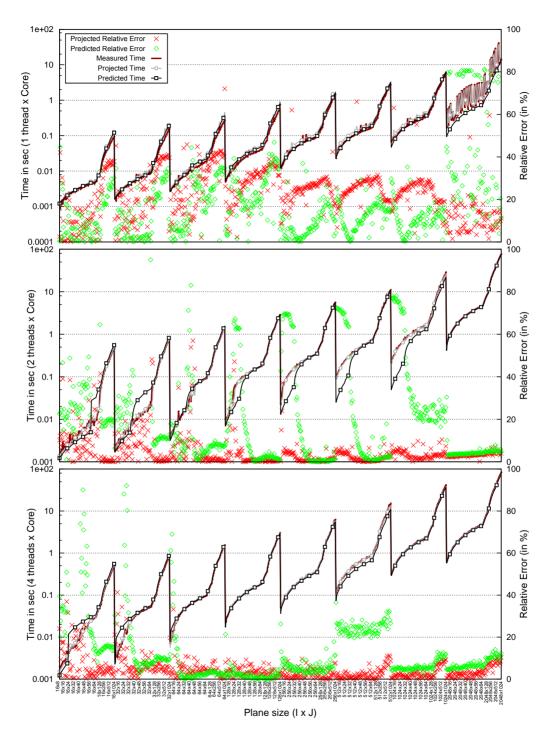

| 6.12 | Actual, projected and predicted execution times                                                    | 123 |

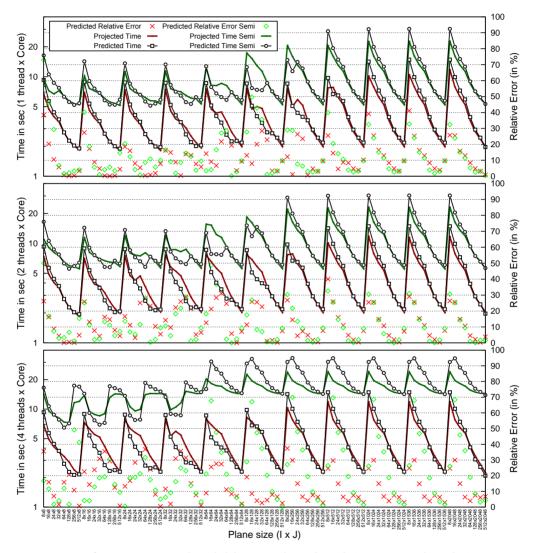

| 6.13 | Projected and predicted execution times for spatial blocking results                               | 124 |

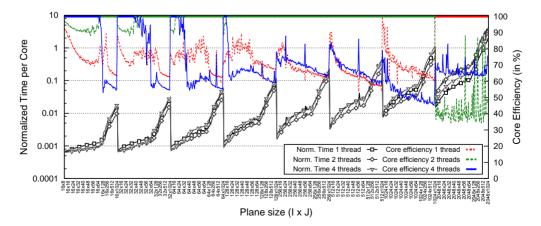

| 6.14 | Core efficiency for all three SMT combinations using a naive stencil                               | 125 |

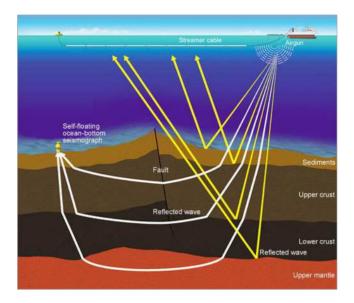

| 7.1  | Off-shore oil and gas prospection                                                                  | 128 |

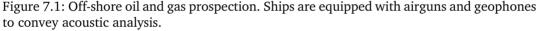

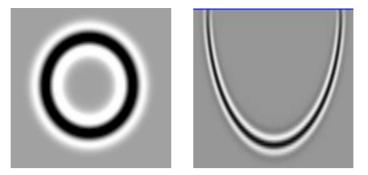

| 7.2  | Comparison between WEM and RTM results                                                             |     |

| 7.3  | Decomposition strategy on Cell/B.E. of 3D domain along the X axis                                  |     |

| 7.4  | The forward wave propagation of single-SPE implementation                                          |     |

| 7.5  | RTM output of the SEG/EAGE salt synthetic model                                                    |     |

|      | WARIS System                                                                                       |     |

| 7.7  | Architecture model supported by the PSK.                                                           |     |

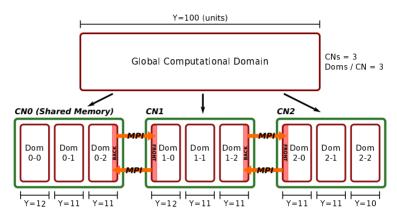

| 7.8  | Domain decomposition conducted by the PSK infraestructure                                          |     |

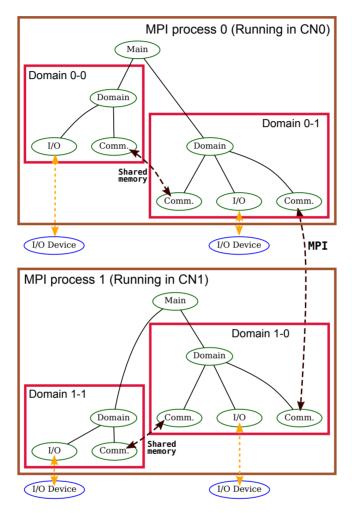

| 7.9  | Threads spawned by the PSK framework                                                               |     |

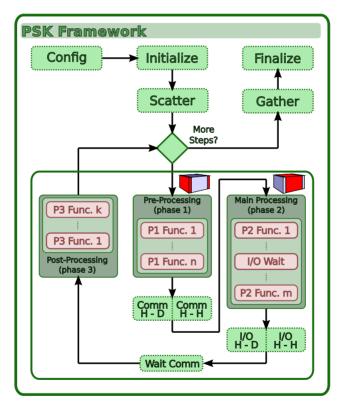

| 7.10 | Execution flow of the PSK framework.                                                               |     |

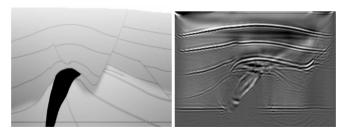

|      | Output example of the volcanic ash dispersion model.                                               |     |

|      | Comparison of simulated ash column mass and TERRA satellite images                                 |     |

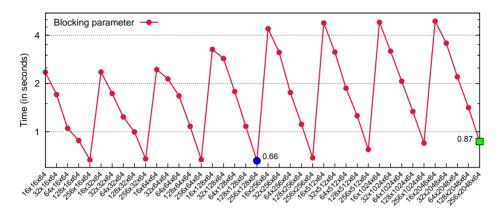

|      | Spatial-blocking impact on the ADS kernel execution time                                           |     |

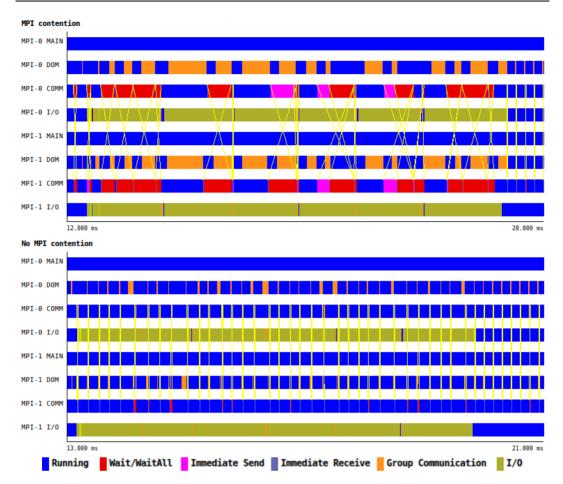

|      | EXTRAE traces of WARIS-Transport with Caulle-0.05 case                                             |     |

# **List of Tables**

| 2.1 | Comparison of FD, FE and FV numerical schemes.                         | 11  |

|-----|------------------------------------------------------------------------|-----|

| 2.2 | Different order Finite Difference formulas for BD, FD and CD           | 13  |

| 3.1 | Architecture description                                               | 21  |

| 3.2 | Architecture description continuation                                  | 24  |

| 3.3 | The four computational kernels in STREAM2 micro-benchmark              | 30  |

| 3.4 | The different STREAM2 execution modes supported.                       | 30  |

| 3.5 | Prefetchers micro-benchmark kernels                                    | 33  |

| 3.6 | Extended version features of the StencilProbe                          | 36  |

| 4.1 | Operation and instruction cost of two representations of stencil codes | 45  |

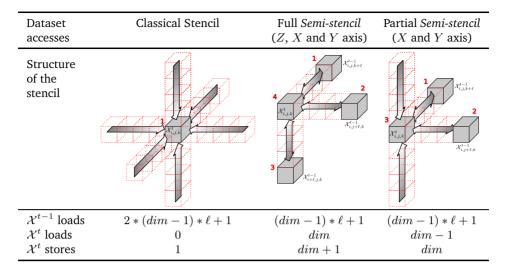

| 4.2 | Dataset accesses per stencil implementation                            | 50  |

| 4.3 | List of parameters used for the extended version of StencilProbe       | 55  |

| 4.4 | Computational and bandwidth ceilings for Roofline model                | 58  |

| 4.5 | Theoretical OI for stencils depending on their 3C's misses             | 58  |

| 4.6 | Summary of execution times and speed-ups for Semi-stencil              | 62  |

| 4.7 | POWER7 SMP results among the different algorithms                      | 71  |

| 4.8 | Sandy Bridge (1 socket) SMP results for the different algorithms       | 72  |

| 4.9 | Knight Corner beta 0 SMP (balanced scheduling) results                 | 73  |

| 5.1 | SMT tests results of the Ash Dispersion Model                          | 81  |

| 5.2 | List of parameters used for testing the decomposition strategies       | 90  |

| 5.3 | Domain decomposition results for Intel Xeon Phi (MIC) architecture     | 90  |

| 5.4 | Domain decomposition results for Intel Sandy Bridge platform           | 92  |

| 6.1 | Features used for preliminary and advanced model results               |     |

| 6.2 | Parameters used in the preliminary model                               |     |

| 6.3 | Summary of preliminary model results                                   |     |

| 6.4 | List of parameters used for the model and the StencilProbe benchmark   | 119 |

| 6.5 | Hardware counters and the formulas used to compute the projected time  | 120 |

| 7.1 | Execution time breakdown of the RTM workload                           |     |

| 7.2 | Performance results of the single-SPE implementation                   |     |

| 7.3 | Pipeline statistics of the single-SPE implementations                  |     |

| 7.4 | Performance results of the RTM implementation                          | 136 |

| 7.5 | Domain resolutions for Cordón Caulle reference simulations                  | 146 |

|-----|-----------------------------------------------------------------------------|-----|

| 7.6 | Time comparison between FALL3D and WARIS-Transport (naive)                  | 149 |

| 7.7 | WARIS-Transport simulation times on Intel Sandy Bridge and Intel Xeon Phi . | 150 |

| 7.8 | Break-down of the optimized WARIS-Transport times on Intel Sandy Bridge .   | 151 |

| 7.9 | Time break-down of EXTRAE traces with Caulle-0.05 case                      | 153 |

| A.1 | Scaling factors for a spherical terrain-following coordinate system         | 165 |

| 1  | General control flow structure of a generic Finite Difference code             | 13  |

|----|--------------------------------------------------------------------------------|-----|

| 2  | Heattut kernel of Chombo toolkit                                               | 35  |

| 3  | The classical stencil algorithm pseudo-code for a 3D problem                   | 40  |

| 4  | The Semi-stencil algorithm pseudo-code (Part 1)                                | 51  |

| 5  | Continuation of the Semi-stencil algorithm pseudo-code (Part 2)                | 52  |

| 6  | Pseudo-code for the space tiling implementation of the Semi-stencil algorithm  | 52  |

| 7  | Pseudo-code for the time-skewing implementation of the Semi-stencil algorithm  | 53  |

| 8  | Pseudo-code for the cache-oblivious implementation of the Semi-stencil algo-   |     |

|    | rithm                                                                          | 54  |

| 9  | Snippet of C code that implements a plane distribution among SMT threads       |     |

|    | using OpenMP                                                                   | 80  |

| 10 | Pseudo-code of the static domain decomposition scheduler                       | 84  |

| 11 | Pseudo-code of the balanced domain decomposition scheduler                     | 85  |

| 12 | Pseudo-code of the guided domain decomposition scheduler                       | 86  |

| 13 | Pseudo-code of the auto-tuner used for finding a pseudo-optimal $TJ$ parameter | 89  |

| 14 | The classical stencil algorithm pseudo-code                                    | 102 |

| 15 | The RTM pseudo-code                                                            | 30  |

| 16 | Pseudo-code of the PDE solver for the 3D wave equation in the RTM 1            | 131 |

| 17 | Volcanic ash dispersion pseudo-code in WARIS-Transport                         | 45  |

## **Chapter 1**

## Preface

### 1.1 Motivation of this Thesis

Nowadays, most of the scientific codes are run in supercomputers. To achieve full resource utilization, these codes must be able to scale from a single node up to a cluster. This scalable migration involves at least four main tasks to succeed: kernel computation, load balancing, input/output (I/O) and inter/intra-node communications. Therefore, the optimization efforts must be driven to these tasks in order to leverage the scientific computing performance.

The computational kernels in scientific applications usually consist of nested loops. In Von Neumann architectures most of the loop optimization techniques are based on improving the floating point to memory access ratio (FLOPS/Byte). This ratio measures the bytes required from memory with respect to the floating point operations performed. The higher this metric is, the better performance is expected. However, there are no general rules, and the optimization techniques may vary depending on the underlying platform due to the memory system intricacy, e.g. complex multi-level cache hierarchies or scratchpad memories.

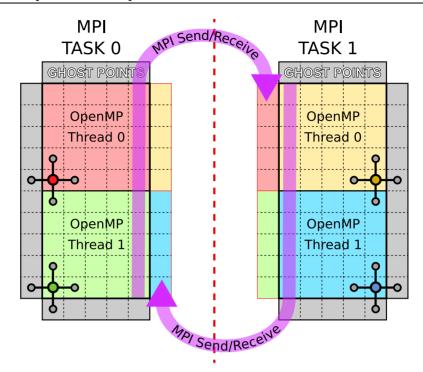

The parallelization of scientific codes is conducted at two different levels: inter-node and intra-node, which are usually performed with message passing libraries (e.g. MPI) and shared memory multiprocessing APIs (e.g. OpenMP) respectively. At intra-node level, two parallelism approaches can be distinguished: Thread Level Parallelism (TLP) —that exploits the multiple cores within a node—, and Instruction Level Parallelism (ILP) —that takes advantage of the multiple execution units within a core. In TLP, load-balancing is critical in order to maximize the overall throughput and reduce the execution time. However, thread imbalance may be exacerbated as the trend to many-core integration in the same die is strengthened within Symmetric Multi-Processing architectures (SMP). This issue will require the deployment of efficient load-balancing and auto-tuning techniques to leverage the intranode performance.

Another concern is the inter-node communication, which is essential in parallel computing to keep the synchronization and coherence of the global results during the time-steps of the simulation. Minimizing the impact of communication between domains is crucial to prevent node stagnation. As a solution, the boundary regions can be reduced and the communication of contiguous allocated data promoted. In this way, the message sizes are minimized and the temporal copies of scattered data across the parallel stack avoided. In this regard, task overlapping can also help allowing the simultaneous execution of kernel computation, I/O and communications, thus hiding the shortest latencies.

The main goal of this thesis is to improve the performance of FD-based codes at every above-mentioned level. Within the scientific computing, the FD scheme is typically employed to solve problems dealing with structured meshes that arise in science and industry. However, some application-based implementations of the FD scheme can only reach up to 30-40% of the peak performance [5]. This inefficient usage of resources has motivated this research, exploring new strategies to improve the critical sections of these codes, either serial or parallel. Since the *stencil* can represent up to 80% of the execution time in some FD-based simulations [9, 42], this kernel is our first target for optimization. To achieve it, we focus on enhancing the memory access pattern and increasing the data re-utilization at core-level, devising also new load-balancing strategies as node-level optimizations.

### **1.2 Thesis Contributions**

This thesis contributes to the performance improvement of FD-based codes focusing on the following main areas:

- A novel algorithm called *Semi-stencil* has been developed for computing stencil operators. This new algorithm establishes an innovative way of computing the spatial operator for medium- and high-order stencils. Its use permits data reuse and reduces the required dataset per point.

- We have unveiled new ways of improving the stencil computations on architectures with Symmetric Multi-Processing (SMP) and Simultaneous Multi-Threading (SMT) capabilities. These strategies are based on a group of schedulers for arranging and traversing the computational domain promoting cache effectiveness and scalability on many-core architectures.

- As improvement to the multi-core and SMT environment, we have developed a straightforward auto-tuner that selects pseudo-optimal tiling parameters (TJ) for computational domains. The auto-tuner, when is combined with domain schedulers, improves even further the expected performance by reducing misses in last level caches.

- A sophisticated performance model for stencil computations has been elaborated to mimic the behavior on a broad variety of computer architectures. This model is a big step forward compared with any previous stencil performance model that can be found in the literature. It includes modern capabilities such as hardware prefetching, multi-level cache hierarchy and many-core support. It has been designed to be modular, incorporating spatial-blocking and Semi-stencil optimizations.

- Our stencil model not only predicts the best parameters for a given optimization algorithm, but also conveys hints of outperforming SMT configurations that can be conducted for a specific architecture.

- Finally, we have collaborated in the development of WARIS, a FD-based framework for High Performance Computing, that deploys efficient performance when is tailored to the industry. This framework is intended to be modular and considers all the requirements for production, including overlapping of computation and communication as well as asynchronous I/O. We demonstrate the effectiveness of our core- and nodel-level optimizations on two real applications used in the industry.

Other minor contributions of this thesis are the following:

- We have extended the StencilProbe micro-benchmark [43] to obtain and assess the experimental results. In order to conduct the experiments, we have incorporated the proposed core- and node-level optimizations using OpenMP to exploit the Thread Level Parallelism.

- The STREAM2 benchmark [55] has been enhanced to fully characterize the memory hierarchy of modern architectures. This benchmark is now able to gather nonstreaming bandwidth in multi-threaded environments considering aligned, SIMD and non-temporal accesses.

- We have developed from scratch a new micro-benchmark called *Prefetchers* that aims to characterize the prefetching engines of an architecture. By means of this tool, we can gather insightful metrics such as the prefetching efficiency, the triggering of the prefetcher and the look-ahead parameters.

#### 1.2.1 Thesis Limitations

The current research is targeted at stencil computations on structured cartesian grids (constant coefficients). However, although not explicitly covered in this thesis, our research may be easily extended to suit other structured meshes such as rectilinear and curvilinear grids (variable coefficients). On the other hand, non-structured grids are out of scope due to the incompatibility of their irregular connectivity with our algorithms.

In addition, despite the recent emergence of massively-parallel accelerators such as the Graphics Processing Units (GPUs), this thesis is specially devoted to scratchpad and cachebased architectures with a high emphasis on multi- and many-core processors. Even though, the latest GPUs with some levels of cache may take partial advantage of this work.

## 1.3 Thesis Outline

This thesis is organized as follows:

In Chapter 2, a brief background of the most representative numerical methods for solving scientific problems is given. Then, we focus on FD schemes, on which this thesis is specially devoted. The FD scheme is introduced, explaining the explicit and implicit approaches for obtaining the numerical solutions.

Chapter 3 presents the different architectures used for the elaboration of this thesis. We also detail the whole set of tools, characterization benchmarks, libraries and parallel paradigms employed.

In Chapter 4, we unveil the stencil-specific optimizations developed at core-level such as the novel Semi-stencil algorithm and its performance when combined with other common strategies.

Chapter 5 proposes specific domain decomposition schedulers that aim to improve the stencil performance when is scaled at node-level. We also propose the combination of these schedulers with auto-tuning methods in order to allow last level cache optimizations.

Chapter 6 introduces the performance models for stencil computations and details the multi-level cache model developed in this research and its insightful results.

In Chapter 7, we present the implementation of some optimization techniques from Chapters 4 and 5 for two strategic applications for the society: a seismic imaging model used by Oil & Gas industry and a volcanic ash dispersal model used by civil aviation authorities.

Finally, Chapter 8 concludes this thesis with a summary of the contributions of each topic, and proposing ideas for possible future work.

## 1.4 List of Publications

The work presented in this thesis has been presented and published in journals and proceedings of international conferences. The papers and talks categorized by topic are the following:

#### Semi-stencil:

- Raúl de la Cruz and Mauricio Araya-Polo. Algorithm 942: Semi-stencil. ACM Transactions on Mathematical Software (TOMS), 40(3):23:1–23:39, April 2014

- Raúl de la Cruz, Mauricio Araya-Polo, and José María Cela. Introducing the Semi-stencil algorithm. In Parallel Processing and Applied Mathematics, 8th International Conference, PPAM 2009, Wroclaw, Poland, September 13-16, 2009. Revised Selected Papers, Part I, pages 496–506, 2009

- Mauricio Araya-Polo and Raúl de la Cruz. Semi-stencil algorithm: Improving data locality and reuse in stencil computation. 14th SIAM Conference on Parallel Processing for Scientific Computing, Seattle, Washington, February 2010. Part of CP4 PDEs (Talk)

#### **Performance Modeling:**

- Raúl de la Cruz and Mauricio Araya-Polo. Modeling stencil computations on modern HPC architectures. In *High Performance Computing Systems. Performance Modeling, Benchmarking, and Simulation,* volume 8966 of *Lecture Notes in Computer Science*, pages 149–171. Springer International Publishing, 2015

- Raúl de la Cruz and Mauricio Araya-Polo. Towards a multi-level cache performance model for 3D stencil computation. In *Proceedings of the International Conference on Computational Science, ICCS 2011, Nanyang Technological University, Singapore, 1-3 June, 2011*, pages 2146–2155, 2011

- Raúl de la Cruz and Mauricio Araya-Polo. Using modeling to develop stencil codes. 2015 Rice Oil & Gas HPC Workshop, Rice University, Houston, March 2015. Coarse-grained Seismic Algorithms (Talk)

- Raúl de la Cruz and Mauricio Araya-Polo. Modeling stencil code optimizations. 16th SIAM Conference on Parallel Processing for Scientific Computing, Portland, Oregon, February 2014. CP8: Performance Optimization for Stencils and Meshes (Talk)

- Mauricio Araya-Polo and Raúl de la Cruz. Performance model for 3D stencil computation. 2012 Rice Oil & Gas HPC Workshop, Rice University, Houston, March 2012. Parallel session A: Benchmarking, Optimization & Performance (Talk)

#### **Case Studies:**

- Raúl de la Cruz, Arnau Folch, Pau Farré, Javier Cabezas, Nacho Navarro, and José María Cela. Optimization of atmospheric transport models on HPC platforms. *Computational Geosciences*, 2015. (Submitted)

- Raúl de la Cruz, Mauricio Hanzich, Arnau Folch, Guillaume Houzeaux, and José María Cela. Unveiling WARIS code, a parallel and multi-purpose FDM framework. In *Numerical Mathematics and Advanced Applications - ENUMATH 2013 - Proceedings of ENUMATH 2013, the 10th European Conference on Numerical Mathematics and Advanced Applications, Lausanne, Switzerland, August 2013*, pages 591–599, 2013

- Mauricio Araya-Polo, Félix Rubio, Mauricio Hanzich, Raúl de la Cruz, José María Cela, and Daniele P. Scarpazza. 3D seismic imaging through reverse-time migration on homogeneous and heterogeneous multi-core processors. *Scientific Programming, Special Issue on the Cell Processor*, 17, 2009

- Mauricio Araya-Polo, Félix Rubio, Raúl de la Cruz, Mauricio Hanzich, José María Cela, and Daniele Paolo Scarpazza. High-performance seismic acoustic imaging by reverse-time migration on the Cell/B.E. architecture. *ISCA2008 WCSA2008*, 2008

• Raúl de la Cruz, Mauricio Hanzich, and José María Cela. Stencil computations: from academia to industry. 16th SIAM Conference on Parallel Processing for Scientific Computing, Portland, Oregon, February 2014. Part of MS66 Optimizing Stencil-based Algorithms - Part II of II (Talk)

#### **Other Publications:**

- Muhammad Shafiq, M. Pericas, Raúl de la Cruz, Mauricio Araya-Polo, Nacho Navarro, and E. Ayguade. Exploiting memory customization in FPGA for 3D stencil computations. In *IEEE International Conference on Field-Programmable Technology*, 2009

- Francisco Ortigosa, Mauricio Araya-Polo, Raúl de la Cruz, and José M. Cela. Seismic imaging and the road to peta-scale capacity. *17th SPE 70th EAGE Conference*, 2008

- Francisco Ortigosa, Mauricio Araya-Polo, Félix Rubio, Mauricio Hanzich, Raúl de la Cruz, and José Maria Cela. Evaluation of 3D RTM on HPC platforms. *SEG 2008, Las Vegas, USA*, 2008

- Francisco Ortigosa, Hongbo Zhou, Santiago Fernandez, Mauricio Hanzich, Mauricio Araya-Polo, Felix Rubio, Raúl de la Cruz, and José M. Cela. Benchmarking 3D RTM on HPC platforms. Instituto Argentino del Petroleo y del Gas, November 2008

### 1.5 Acknowledgements

This work could not have been done without the support, in knowledge and inspiration, of many people.

First, I want to thank the support of my family, but specially the one given by my wife. Her resilience and patience to the large process of getting my PhD has endorsed me to success in this endeavour.

I would also want to thank my thesis advisor Mauricio Araya-Polo, for his support and willingness to motivate me in the worst moments to finish my doctoral degree.

I am grateful to Arnau Folch and José María Cela for giving me the opportunity of developing the WARIS-Transport module and the liberty of exposing and implementing some new ideas. It has not been a smooth journey, but it has inspired me in insightful research that has allowed me to fulfill the requirements of this thesis.

I am also indebted to the Barcelona Supercomputing Center and my colleagues at the Computer Applications in Science & Engineering (CASE) department for the nice working atmosphere that motivated to give the best of me. All the years working at the BSC have been enriching and fruitful in intellectual terms.

I would also like to express my gratitude to the Partnership for Advanced Computing in Europe (PRACE) for the grant of computing time on their supercomputing facilities. The PRACE project receives funding from the EU's Seventh Framework Programme (FP7/2007-2015) under grant agreements RI-211528, 261557, 283493 and 312763. This thesis has been partially supported by the Spanish Ministry of Science and Innovation (CICYT) under grants TIN2007-60625 and 2009501052. Finally, I would like to acknowledge Intel for providing early access to a MIC based system.

## **Chapter 2**

## Introduction

## 2.1 Numerical Methods

Before the transistor revolution, many engineering fields needed costly and time consuming experiments to improve the product design [19, 63]. However, in the last decades, the cost reduction of microprocessors and memory has allowed the advent of a new supercomputers generation [77]. The availability of supercomputers has enabled scientists to conduct large and complex simulations that usually consume days of computational time. Since then, scientific simulations have become a cutting-edge factor for industry. They have permitted to shorten the development cycle of engineering products by assisting in design and optimization stages, thus eliminating lengthy and costly prototype manufacturing. As an example, scientific computing may help to reduce friction coefficients of high speed trains by slightly changing the product geometry.

Today, large scientific computing simulations are widely used to solve numerical problems arising in Aerospace [44], Meteorology [76], Astrophysics [12], Geophysics [58, 65], Quantum Chemistry [4, 15] and Oceanography [38, 45]. Most of these scientific simulations have something in common, the physical and mathematical models are approximated using Partial Differential Equations (PDEs), which can be solved using various numerical analysis schemes.

In general terms, we could enumerate the following main reasons to perform scientific simulations:

- Analysis: in some engineering fields (e.g. Aerospace) it is far too expensive and difficult to build specific experimental models. In addition, simulations can provide data that empirically is impossible or very hard to obtain.

- Prediction: it provide answers to different design implementations in a short time of period, improving the quality of the final product.

- Efficiency: as a consequence of the shortening of the design and development stages, the final product can reach faster to the market.

The most representative fields within scientific computing are Computational Mechanics (CM) and Computational Physics (CP). They are devoted to study phenomena governed by

the principles of mechanics and physics by means of computational methods. Both are interdisciplinary fields that are based on three disciplines: physics, mathematics and computer science. The development of computational simulations codes in these fields involves the following steps, which are also represented in Figure 2.1:

- 1. Mathematical modeling: a physical phenomenon or engineering system is represented by PDEs in the continuous domain.

- 2. Discretization of the mathematical model: PDEs are turned into forms which are suitable to be solved by computers. In this step, the numerical scheme (e.g. Finite Difference or Finite Elements) discretizes the original continuous PDEs. Commonly, the PDEs involved are translated into a system of algebraic equations.

- 3. Computational implementation: once the discretized equations are built, the scientific code is written to represent the equations as computer programs. The discretized equations are solved using direct or iterative methods.

- 4. Validation: the software application, the numerical method and the mathematical model are verified either empirically or using simplified models with exact analytical solutions.

| Continuous<br>PDE for<br>$\phi(x,t)$ | $\stackrel{\text{Numerical}}{}$ | Discrete<br>Difference<br>Equation<br>$\phi(x_i, t_n)$ | $\xrightarrow{\text{Solution}}$ | $\phi_i^n$ approximation to $\phi(x,t)$ |

|--------------------------------------|---------------------------------|--------------------------------------------------------|---------------------------------|-----------------------------------------|

|                                      |                                 | $\varphi(x_i, t_n)$                                    |                                 |                                         |

Figure 2.1: Translation from the continuous to the discrete problem.  $\phi(x,t)$ : continuous solution (exact solution).  $\phi(x_i, t_n)$ : continuous solution evaluated at the mesh points.  $\phi_i^n$ : approximated solution by solving the numerical scheme.

High Performance Computational Simulations (HPCS) is a sub-discipline of scientific computing, where the implementation of the scientific simulation runs on large supercomputers. Due to the cluster nature of the supercomputers, HPCS is intrinsically related to highly parallel demanding computations. This large computations involve two main aspects. First the kernel computation, which solves numerically the PDEs and consumes large amount of resources, both computational and memory. Second the parallelization step, that permits to scale the performance up to thousands of nodes. This parallelization may be performed in two levels: intra-node, which takes advantage of the multi-core nature of modern architectures, and inter-node that enables the cluster-level parallelism.

The most popular numerical schemes used nowadays are the Finite Difference (FD), the Finite Element (FE) and the Finite Volume (FV) methods. Table 2.1 shows a summary of the advantages and disadvantages of these methods. FD method is commonly used in thermodynamics, electromagnetism and geophysics, whereas FE and FV are widely used in solid and fluid mechanics problems. There are also other methods to numerically solve PDEs (e.g. Discrete Element, Spectral or Particle-In-Cell), but they are out of scope of this introduction. In

| Num. Scheme | Finite Difference | Finite Element       | Finite Volume        |

|-------------|-------------------|----------------------|----------------------|

| Appeared in | 20s               | 70s                  | 80s                  |

| Robustness  | Medium            | High                 | High                 |

| Meshes      | Structured        | Non-structured       | Non-structured       |

| Coverage    | Specific problems | All kind of problems | All kind of problems |

| Peak Perf.  | Up to 40%         | Between 8-12%        | Between 8-12%        |

Table 2.1: Comparison of FD, FE and FV numerical schemes.

the following sections, we will review in detail the FD method, and the ways of numerically solve PDEs using this scheme (implicitly or explicitly).

### 2.2 Finite Difference Method

The Finite Difference method (FD) is the simplest and straightforward way of numerically solve PDEs [80]. The FD consists in approximating the solutions to the PDEs by replacing derivative expressions with approximately equivalent difference quotients. Therefore, the PDE is converted into a set of finite difference algebraic equations. As a result, the continuous domain of the problem is transformed into a structured mesh of discrete points. In this structured mesh, by using different forms of the finite different equations, a wide variety of physical phenomena can be conformed.

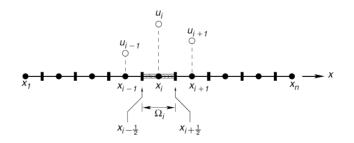

Consider the case of a function with one variable u(x). Given a set of points  $x_i$ ; i = 1, ..., Nin the domain of u(x), as shown in Figure 2.2, the numerical solution is represented by a discrete set of function values  $\{u_1, ..., u_N\}$  that approximate u at these points, i.e.,  $u_i \approx u(x_i)$ ; i = 1, ..., N.

Figure 2.2: Discretization of u(x) the domain.

Generally, and for simplicity, the points are equally spaced along the domain with a  $\Delta x$  constant distance ( $\Delta x = x_{i+1} - x_i$ ), so we write  $u_{i+1} \approx u(x_{i+1}) = u(x_i + \Delta x)$ . This discretized domain is referred to as structured mesh or grid.

PDEs involve unknown functions of several independent variables (in time and space) and their partial derivatives. The derivative of a unknown u(x) with respect to x can be approximated by linear combinations of function values at the grid points,

$$\frac{\partial u}{\partial x}(x_i) = \lim_{\Delta x \to 0} \frac{u(x_i + \Delta x) - u(x_i)}{\Delta x} \approx \frac{u(x_{i+1}) - u(x_i)}{\Delta x} \quad \text{(FD)}$$

$$= \lim_{\Delta x \to 0} \frac{u(x_i) - u(x_i - \Delta x)}{\Delta x} \approx \frac{u(x_i) - u(x_{i-1})}{\Delta x} \quad \text{(BD)}$$

$$= \lim_{\Delta x \to 0} \frac{u(x_i + \Delta x) - u(x_i - \Delta x)}{2\Delta x} \approx \frac{u(x_{i+1}) - u(x_{i-1})}{2\Delta x} \quad \text{(CD)}.$$

All these expressions are equivalent and they converge to the derivative of u(x) when  $\Delta x \rightarrow 0$ . However, when  $\Delta x$  is finite but small enough, the Equations 2.1 can be used to obtain approximations of the derivative of u(x). In that case, we may use  $u_i$ ,  $u_{i-1}$  and  $u_{i+1}$  to obtain the derivative.

Such approximations (Equations 2.1), depending on the points used for the derivative, are referred to as forward (FD:  $x_i, x_{i+1}$ ), backward (BD:  $x_{i-1}, x_i$ ) and centered (CD:  $x_{i-1}, x_i, x_{i+1}$ ) finite difference approximations of  $u(x_i)$ . The precision of such approximations may differ from each other, where the accuracy depends on the number of neighbors used (order of accuracy) and the discretization of the mesh.

A way to compute a better accuracy of first and high order derivatives approximations is using Taylor series expansions around the point  $x_i$ ,

$$u(x) = \sum_{n=0}^{\infty} \frac{(x-x_i)^n}{n!} \frac{\partial^n u}{\partial x^n}(x_i)$$

$$u_{i+1} = u_i + \Delta x \left(\frac{\partial u}{\partial x}\right)_i + \frac{(\Delta x)^2}{2} \left(\frac{\partial^2 u}{\partial x^2}\right)_i + \frac{(\Delta x)^3}{6} \left(\frac{\partial^3 u}{\partial x^3}\right)_i + R_n(x)$$

(2.2)

$$u_{i-1} = u_i - \Delta x \left(\frac{\partial u}{\partial x}\right)_i + \frac{(\Delta x)^2}{2} \left(\frac{\partial^2 u}{\partial x^2}\right)_i - \frac{(\Delta x)^3}{6} \left(\frac{\partial^3 u}{\partial x^3}\right)_i + R_n(x) .$$

Taylor expansions permit to elaborate high-order accuracy derivatives using more neighbors of the grid. Depending on the truncation point of the Taylor serie, we may have a bigger or smaller residual term  $(R_n(x))$ . This truncation error is proportional to the mesh discretization and the number of expanded series  $(\mathcal{O}(\Delta x^n)/n$ -th order accuracy). Table 2.2 summarizes the coefficient terms of various order finite difference formulas up to fourth-order derivatives.

Two different approaches can be used in scientific computing in order to obtain the numerical solutions of time-dependent PDEs: explicit and implicit methods. These two methods are discussed in detail in Section 2.3, but generally, when FD methods are implemented in scientific simulations, explicit time integration schemes are mostly used as direct solvers. Explicit methods can solve time-dependent PDEs directly, involving both the current state of the system and some previous ones, advancing the solution through small intervals of time ( $\Delta t$ ).

| Tormara                       |              |       |           |           |           |           |  |  |

|-------------------------------|--------------|-------|-----------|-----------|-----------|-----------|--|--|

| Order                         | Disc. coeff  | $u_i$ | $u_{i+1}$ | $u_{i+2}$ | $u_{i+3}$ | $u_{i+4}$ |  |  |

| $\partial u/\partial x$       | $\Delta x$   | -1    | 1         |           |           |           |  |  |

| $\partial^2 u / \partial x^2$ | $\Delta x^2$ | 1     | -2        | 1         |           |           |  |  |

| $\partial^3 u/\partial x^3$   | $\Delta x^3$ | -1    | 3         | -3        | 1         |           |  |  |

| $\partial^4 u / \partial x^4$ | $\Delta x^4$ | 1     | -4        | 6         | -4        | 1         |  |  |

Forward Difference -  $\mathcal{O}(\Delta x)$

Backward Difference -  $\mathcal{O}(\Delta x)$

| Order                         | Disc. coeff  | $u_{i-4}$ | $u_{i-3}$ | $u_{i-2}$ | $u_{i-1}$ | $u_i$ |

|-------------------------------|--------------|-----------|-----------|-----------|-----------|-------|

| $\partial u / \partial x$     | $\Delta x$   |           |           |           | -1        | 1     |

| $\partial^2 u / \partial x^2$ | $\Delta x^2$ |           |           | 1         | -2        | 1     |

| $\partial^3 u / \partial x^3$ | $\Delta x^3$ |           | -1        | 3         | -3        | 1     |

| $\partial^4 u / \partial x^4$ | $\Delta x^4$ | 1         | -4        | 6         | -4        | 1     |

Central Difference -  $\mathcal{O}(\Delta x^2)$

| Order                               | Disc. coeff   | $u_{i-2}$ | $u_{i-1}$ | $u_i$ | $u_{i+1}$ | $u_{i+2}$ |

|-------------------------------------|---------------|-----------|-----------|-------|-----------|-----------|

| $\partial u/\partial x$             | $2\Delta x$   |           | 1         | 0     | 1         |           |

| $\partial^2 \dot{u} / \partial x^2$ | $\Delta x^2$  |           | 1         | -2    | 1         |           |

| $\partial^3 u / \partial x^3$       | $2\Delta x^3$ | 1         | 2         | 0     | 2         | 1         |

| $\partial^4 u / \partial x^4$       | $\Delta x^4$  | 1         | -4        | 6     | -4        | 1         |

Table 2.2: Different order Finite Difference formulas for BD, FD and CD.

Algorithm 1 General control flow structure of a generic Finite Difference code. The tasks to be performed can be categorized in four different types: Kernel Computation (KC), Data Communication (DC), Input/Output (IO) and Load Balancing (LB).

| 1:  | Domain decomposition of the structured mesh                      | (LB) |  |  |  |

|-----|------------------------------------------------------------------|------|--|--|--|

|     | 2: for $t = time_{start}$ to $time_{end}$ in $\Delta t$ steps do |      |  |  |  |

| 3:  | Read input for t                                                 | (IO) |  |  |  |

| 4:  | Pre-process input                                                | (KC) |  |  |  |

| 5:  | Inject source                                                    | (KC) |  |  |  |

| 6:  | Apply boundary conditions                                        | (KC) |  |  |  |

| 7:  | for all discretized points in my domain do                       |      |  |  |  |

| 8:  | Stencil computation (update $u^t$ )                              | (KC) |  |  |  |

| 9:  | end for                                                          |      |  |  |  |

| 10: | Exchange overlap points between neighbor domains                 | (DC) |  |  |  |

| 11: | Post-process output                                              | (KC) |  |  |  |

| 12: | Write output for <i>t</i>                                        | (IO) |  |  |  |

| 13: | 13: end for                                                      |      |  |  |  |

A parallel implementation of the explicit FD solver involves, amongst many others steps, the so-called *stencil computation* (see Algorithm 1 line 8), which solves the spatial and temporal differential operators of the governing equations. The stencil computation consists in accumulating the contribution of the neighbors points  $(u^{t-1})$  in the discretized domain

(i = 1, ..., N) along the cartesian axis, updating in this way the unknown for the next time step  $(u_i^t)$ . This operation is usually the main computational bottleneck of FD codes and it may require up to 80% of the total execution time for some simulations [8, 9, 67]. Nevertheless, the stencil is conducted through an outer loop advancing the simulation over time (t) and composed of other tasks that concern minor kernel computations (KC), data communication (DC) and Input/Output (IO). Likewise, prior to the loop time iteration, a load balancing process must be carried out to ensure appropriate decomposition of the global domain among the computational resources in charge of the parallel simulation.

At any time step, the simulation may require acquiring and pre-processing input data (lines 3 and 4) as new solver parameters and post-processing and writting the current system state as the output solution (lines 11 and 12). The simulation also involves applying the boundary conditions (line 6), which are numerical tricks to confine the problem in a finite domain. This is done by prescribing the boundary elements ( $u_1$  and  $u_N$ ) of the domain to specific values that replicate the environment outbounds. Last but not least important, the data communication process (line 10) is conducted after the computation of the stencil. In this step, each computational resource exchanges its boundary areas with their neighbors in order to proceed with the local update of the system state.

### 2.3 Implicit and Explicit Methods

In spatial approximations, PDEs can be solved through two different methods: implicit and explicit.

In order to illustrate how we can find numerical solutions using both methods, let us consider a heat equation problem (see Appendix A.1). The heat equation is a PDE that describes the evolution of the heat distribution in a medium over time. This kind of equations can be used to describe the heat conduction in a metal rod. In one-dimensional problems and in the continuum case, this equation is written as

$$\frac{\partial u}{\partial t} = \alpha \frac{\partial^2 u}{\partial x^2} \tag{2.3}$$

where  $\alpha$  is the thermal diffusivity of the material being described, and u is the unknown temperature.

This first-order in time and second-order in space PDE can be discretized by using Finite Differences in a equally spaced grid ( $\Delta x$ ). Then, we can formalize the heat problem as

$$u_i^t = u(t, i) = u(t\Delta t, i\Delta x) ; i = 1, \dots, N ; t \ge 0.$$

(2.4)

At this point, we continue the discretization by replacing the continuous derivatives in space and time with discrete approximations of FD. In the interest of simplicity, we use a central difference (CD) in space with respect to x ( $u_{i-1}^t - 2u_i^t + u_{i+1}^t$ ). However, we use a

backward difference (BD) for the derivative with respect to t. Using this numerical scheme, the heat equation is discretized as

$$\frac{1}{\Delta t}(u^t - u^{t-1}) = \frac{\alpha}{\Delta x^2}(u^t_{i-1} - 2u^t_i + u^t_{i+1})$$

(2.5)

obtaining an implicit scheme where the unknown  $(u^t)$  function value includes terms involving as well unknown derivative values. In other words, we obtain a system where linear combinations of unknown derivative values  $(u^t)$  are given in terms of known function values  $(u^{t-1})$ . Then, rearranging the terms, we can obtain the following algebraic equation for each discrete point to solve in the grid,

$$\underbrace{-ru_{i-1}^t + (1+2r)u_i^t - ru_{i+1}^t}_{A \text{ coefficients}} = \underbrace{u_i^{t-1}}_{RHS}, \quad r = \frac{\alpha \Delta t}{\Delta x^2}.$$

(2.6)

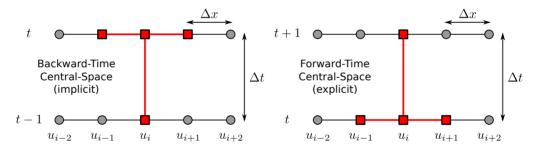

Figure 2.3.Left shows an example with 5 points where the Backward-Time-Central-Space (BTCS) scheme has been used.

Figure 2.3: FD example of 1D problem with a 5 points grid domain. Left: Backward in Time and Central in Space scheme (implicit). Right: Forward in Time and Central in Space scheme (explicit). Red squares depict the data dependencies for each scheme.

To obtain a well-defined problem, some initial conditions must be applied on the boundary nodes of the domain ( $u_0$  and  $u_4$  of the 5 point example). These two end points depend on values that are outside of the computational domain ( $u_{-1}$  and  $u_5$ ), and therefore we must enforce boundary conditions to confine the problem in the discrete domain. There are different boundary conditions that can be applied, one of them is the Dirichlet boundary condition that imposes the boundary to a fixed value,

$$u_0^t = \beta, \quad u_4^t = \gamma, \quad \forall t \tag{2.7}$$

Once the problem has been well-defined enforcing the boundary condition to the end nodes of the grid, we can proceed to build the linear system. For the 5 point grid example, the final system of equations would be

$$\begin{bmatrix} 1 & 0 & 0 & 0 & 0 \\ -r & 1+2r & -r & 0 & 0 \\ 0 & -r & 1+2r & -r & 0 \\ 0 & 0 & -r & 1+2r & -r \\ 0 & 0 & 0 & 0 & 1 \end{bmatrix} \begin{bmatrix} u_0^t \\ u_1^t \\ u_2^t \\ u_3^t \\ u_4^t \end{bmatrix} = \begin{bmatrix} \beta \\ u_1^{t-1} \\ u_2^{t-1} \\ u_3^{t-1} \\ \eta \end{bmatrix}$$

(2.8)

where the boundary nodes  $(u_0^t \text{ and } u_4^t)$  have already been imposed as Dirichlet boundary conditions ( $\beta$  and  $\gamma$ ). Structured meshes produce banded matrices in the linear system which hold large sparsity. This banded sparsity is deterministic and can be optimally stored using specific matrix storage formats as DIAG. Solving the Ax = b linear system requires any of the different solver algorithms available, either the classical iterative (CG or GMRES) or direct (Gaussian or LU factorization). By solving this system, we finally propagate the solution one time-step ( $\Delta t$ ).

So far, we have seen how to formulate the heat equation as an implicit problem, where linear algebra problems arise. Actually, it is the backward difference discretization in time which leads to implicit schemes. Then, by discretizing the Equations 2.3 and 2.4 using a first-order forward differences in time (FTCS) instead of backward differences, we obtain the following discretization of the heat equation:

$$\frac{1}{\Delta t}(u^{t+1} - u^t) = \frac{\alpha}{\Delta x^2}(u^t_{i-1} - 2u^t_i + u^t_{i+1})$$

(2.9)

where the only changed terms are the time superscripts of the left unknowns  $(u^{t+1} - u^t)$ . This other way of discretizing in time produces the following explicit scheme for the heat equation,

$$u_i^{t+1} = ru_{i-1}^t - (1+2r)u_i^t + ru_{i+1}^t, \ r = \frac{\alpha\Delta t}{\Delta x^2}$$

(2.10)

which can be solved explicitly due to the knowledge of all its dependences. While the implicit scheme leads to a set of algebraic equations, the explicit scheme results in a formula that gives us the solution without the requirement of an iterative or direct solver. This explicit formula that performs nearest neighbor computations is called *stencil*, and gives us the solution of the PDE for the next time-step.

In a stencil computation, each point of the structured grid is traversed and updated with the weighted contributions from a subset of neighbors points over each direction of the cartesian axis in space  $(u_{i\pm1}^t)$  and time  $(u^{t-1})$ . Figure 2.3.right shows the 5 point grid example with an explicit scheme where all dependencies are known  $(u^t)$ . The structured grid points represent the unknowns  $(u_i^t)$  in space for the PDE problem to be solved in time-step t. The number of neighbors, their coefficients (-(1+2r) and r in Equation 2.10) and the discretization  $(\Delta x)$  set the order accuracy of the spatial differential operator. These coefficients may be the same for each point of the grid or may not be. This is often related to uniformly spaced meshes (constant coefficients) and rectilinear and curvilinear meshes (variable coefficients), where discretization over the cartesian axis vary for each point of the grid.

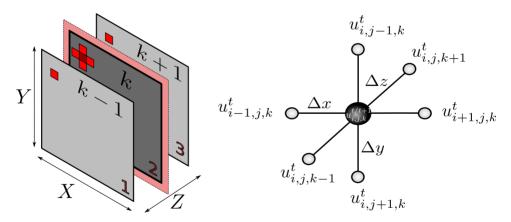

As in the implicit scheme, specific boundary conditions must be applied to boundary nodes  $(u_0 \text{ and } u_4 \text{ in 5 point grid example})$  so as to confine the problem to the discretized grid. To do this, explicit schemes incorporate to the computational domain the so-called *ghost points* (see pink outer area in Figure 2.4.Left). This technique is two-fold, first it intends to impose those boundary nodes to an specific boundary condition (e.g. Dirichlet), and second it allows to use the same stencil operator throughout the whole computational domain.

In order to ensure numerical stability, explicit methods must conform the Courant-Friedrichs-Levy (CFL) condition. This condition ensures no numerical instabilities during the timemarching of the explicit solver by setting the time-step ( $\Delta t$ ) to a sufficient small value. The timestep must assure that the numerical domain dependence of any point in space and time must include the analytical domain of dependence. In particular, the CFL condition for the 1D heat equation using FTCS (2nd order in space and 1st in time) is

$$r = \frac{\alpha \Delta t}{\Delta x^2} < \frac{1}{2}, \quad \Delta t < \frac{\Delta x^2}{2\alpha}.$$

(2.11)

Once the critical time-step has been computed, we have a well-defined problem that can be solved numerically. The FTCS scheme is easy to implement in parallel because  $u_i^{t+1}$  values can be updated independently from each other and only depend on older steps  $(u_i^t)$ . The entire solution of the PDE is conducted in two nested loops, an outer loop over all time-steps, and an inner loop that traverses all grid points.

Figure 2.4: 7-point stencil layout. Left: Data involved in the computation of a 7-point stencil. The layout structure is totally different to 1D or 2D stencil computations. The pink halo in plane k depicts the *ghost points* required to perform the boundary conditions. Right: structure of the 7-point stencil. Data is accessed in the three axes.

Unlike the 1D example exposed here on account of simplicity, stencil computations are usually performed on 3D domains, on which this thesis is specially focused. In 3D stencils, the working dataset required is much bigger than in 1D or 2D problems (see Figure 2.4.Right). For example, the formulation of the 7-point 3D stencil operator (FTCS scheme: 2nd order in space and 1st in time) for the heat equation problem is the following,

$$u_{i,j,k}^{t+1} = (1 - 2r_i - 2r_j - 2r_k)u_i^t + r_i(u_{i-1,j,k}^t + u_{i+1,j,k}^t) + r_j(u_{i,j-1,k}^t + u_{i,j+1,k}^t) + r_k(u_{i,j,k-1}^t + u_{i,j,k+1}^t),$$

$$r_i = \frac{\alpha \Delta t}{\Delta x^2}, r_j = \frac{\alpha \Delta t}{\Delta y^2}, r_k = \frac{\alpha \Delta t}{\Delta z^2}.$$

(2.12)

Two main problems can be inferred from 3D computations. The first one is the memory access pattern. Accesses across the j and k indexes may be significantly more expensive in a hierarchy cache architecture. The spatial order of the stencil has direct impact on this problem. The more neighbors are accessed, the more expensive is in latency-wise, in particular for the k index which accesses over the least-stride dimension. The second stencil problem is the low ratio of floating point operations to memory accesses, which is related to the poor data reuse. This ratio is the result of dividing the floating-points instructions per load and stores accesses of  $u^t$  and  $u^{t-1}$  data grids. These two problems provoke that 3D stencil computations are often memory-bound, requiring special algorithmic treatments to sort out these issues.

## 2.4 Summary

This chapter has introduced a big picture of the most important numerical methods that can be found today. We have paid special attention to Finite Difference scheme, to which this thesis is devoted. As shown, this scheme is specially well suited to solve problems that can be represented in structured meshes in a reasonable execution time. We have also dedicated a section to explain the difference between implicit and explicit methods to solve numerically PDEs. Through a simple PDE problem as the heat equation, we have shown step by step how to deduce the linear system equations for implicit methods but also the nearest neighbor formula (*stencil*) for explicit methods. In order to obtain well-defined problems, we have dealt with the boundary conditions, and how to apply them to the boundary nodes of the difference of solving 1D or 2D against 3D stencil computations in terms of memory access complexity, unveiling the main computational problems that scientists and developers must face.

## **Chapter 3**

## **Experimental Setup**

In this chapter, the testbeds for the experiments are presented and detailed at each hardware and software implementation level. From the point of view of the hardware, all the peculiarities of the architectures and their memory hierarchy systems used in this thesis are discussed. Likewise, the software stack chosen for each platform to sort out aspects such as the parallel programming model, programming language and compiler versions are also addressed. Finally, we explain the details about the methodology considered to collect the performance results for the experiments and the instrumentation support used to measure the metrics.

### 3.1 Architecture Overview

The architecture variety used for the elaboration of this thesis is rather extent (see Tables 3.1 and 3.2 for further details about their specifications). Many types of architectures have been covered to assess the effectiveness of the optimizations proposed in most of the platforms available nowadays. The architectures analysed range from heterogeneous architectures with low latency scratchpad memories to homogeneous architectures with tenths of cores, which are able to run multiple threads simultaneously, and complex multi-level cache hierarchies that sport software and hardware prefetching capabilities.

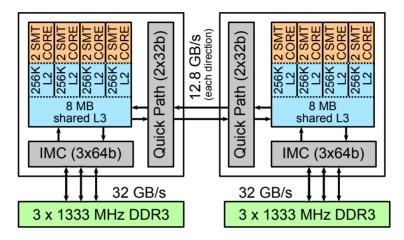

#### 3.1.1 Intel Xeon X5570 (Nehalem-EP)

The Intel Nehalem chip is the next multi-core processor generation of the Intel Core family, which includes technologies that bestow better performance compared to its predecessors. The main difference is the replacement of the front side bus architecture, and the integration of a memory controller (IMC) in the same die. Due to this new on-chip integration, an inter-chip network connection, called Quick Path Interconnect (QPI), is required for the multi-socket implementation. The QPI is also in charge of conducting the coherence protocol and the access to the I/O devices. This technology revamps the memory performance shortening the processor and memory performance gap.

As multi-socket architecture, memory can be attached to different processors, and therefore the cost of accessing data from one processor to the neighbor processor's memory has a higher penalty. This memory organization is called *non-uniform memory access* (NUMA), and requires careful consideration for the programmer in order to minimize remote memory accesses. However, the memory performance improvement overcomes the cost of the additional specific code.

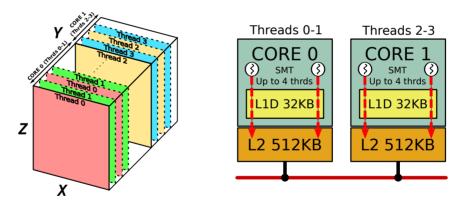

The Intel Xeon 5500 series includes a quad-core processor with Simultaneous Multi-Threading (SMT) capabilities (see Figure 3.1). Each core has 2 independent FP units (FPADD and FPMUL) and is able to compute 8 floating points in SIMD mode (SSE) for single-precision and 4 floating points in double-precision. This gives a peak performance of 46.88 GFlops and 23.44 GFlops respectively for balanced codes (parity of adds and multiplications).

Figure 3.1: Diagram of a dual-socket configuration with Intel Nehalem-EP.

#### 3.1.2 IBM POWER6

IBM introduced the POWER6 architecture in 2007. This was a higher improvement over the POWER5 version which was based on the two-way Simultaneous Multi-Threading (SMT) and dual-core technologies that were proven in its predecessor. In this version, IBM coupled high-frequency cores with a massive cache hierarchy and a complex memory subsystem specifically tuned for high-end computing.

The POWER6 processor incorporates two high-frequency (up to 5.0 GHz) two-way SMT cores, which are able to operate in 32- and 64-bit modes. Each core includes a 64 KB L1-D and L1-I caches, and a private on-chip 4 MB L2 cache. Finally a 32 MB L3 victim cache located off-chip is shared among the two cores. Each core also contains a sophisticated prefetching engine that reduces the effective latency by detecting 16 independent streams on L1 and L2 caches for reading and writing operations.

Likewise, two integrated memory controllers and an integrated SMP coherence and data interconnect switch are included in the same die. Both memory controllers can operate at 3.2 GHz, reading up to 16 bytes of data and simultaneously writing up to 8 bytes per cycle (peaks of 51.2 GB/s and 25.6 GB/s in read/write operations) when using 800 MHz DDR2

| System<br>name                  | Bull<br>NovaScale   | IBM<br>Server | IBM<br>System           | Cray<br>XT5    |

|---------------------------------|---------------------|---------------|-------------------------|----------------|

| Architecture                    | Intel<br>Nehalem-EP | IBM<br>POWER6 | IBM<br>PowerPC 450      | AMD<br>Opteron |

| Model                           | X5570               | p-575         | BlueGene/P              | 2356           |

| Execution                       | out-of-order        | in-order      | in-order                | out-of-order   |

| SMT                             | 2                   | 2             | 1                       | 1              |

| SIMD                            | SSE4.2              | VMX           | HUMMER                  | SSE4.2         |

|                                 | 128-bit             | 128-bit       | 128-bit                 | 128-bit        |

| ISA                             | amd64               | POWER         | PowerPC                 | amd64          |

| Chips×Cores                     | $2 \times 4$        | 16 	imes 2    | $1 \times 4$            | $2 \times 4$   |

| Clock (GHz)                     | 2.93                | 4.7           | 0.850                   | 2.3            |

| SP GFlops <sup>†</sup>          | 93.76               | 75.2          | 13.6                    | 73.6           |

| DP GFlops <sup>†</sup>          | 46.88               | 37.6          | 13.6                    | 36.8           |

| L1 D-Cache                      | 32 KB               | 64 KB         | 32 KB                   | 64 KB          |

| L2 Cache                        | 256 KB              | 4096 KB       | 1920 B                  | 512 KB         |

| L3 Cache                        | 8 MB                | 32 MB         | $2 \times 4 \text{ MB}$ | 2 MB           |

|                                 | (inclusive)         | (victim)      |                         | (victim)       |

| Main memory                     | 24 GB               | 128 GB        | 2 GB                    | 8 GB           |

| Bandwidth                       | 32 GB/s             | 51.2 GB/s     | 13.6 GB/s               | 21.3 GB/s      |

| Watts $	imes$ hour <sup>†</sup> | 95                  | 100           | 39                      | 75             |

| Compiler                        | Intel v11.1         | IBM XL        | IBM XL                  | Portland v10.2 |

|                                 | GCC v4.1.2          | v12.1/v10.01  | v9.0/v11.01             | GCC v4.1.2     |

DRAM. Besides, the SMP switch enables scalable connectivity for up to 32 POWER6 chips through chip-to-chip and node-to-node links.

Table 3.1: Architectural configuration of the platforms used. <sup>†</sup>Only one chip is considered.

### 3.1.3 IBM Blue Gene/P

The IBM BG/P architecture, the successor of BG/L, was conceived to emphasize the highpower efficiency in platforms while keeping the race to the future petascale energy-efficient supercomputers. The BG/P version maintains the application-specific integrated circuit (ASIC) and the 3D torus interconnection topology of the BG/L, but incorporating significant important enhancements that boost the throughput of this architecture.

The BG/P die includes four IBM PowerPC 450 32-bit cores running at 850 MHz. Each core contains a dual-pipeline FPU, that supports two simultaneous floating-point operations in SIMD mode (either single or double precision). These units are able to conduct fused multiple-add operations (2 FLOPs), conferring a peak throughput of 13.6 GFlops per chip. In addition, each PPC450 core sports a 32 KB L1-I and L1-D caches, a private L2 stream buffer on-chip able to keep 7 streams simultaneously (2 cache-lines per stream), and a 8 MB L3 cache shared among the cores. All four cores are interconnected with the DDR2 main memory through a 16 byte wide dual-channel able to keep a sustainable bandwidth of 13.6

GBytes/s. In order to fully utilize the compute node resources, this platform supports three execution modes: SMP mode (one MPI task with up to four threads per process), dual mode (two MPI tasks with up to two threads per process) and quad mode (four MPI tasks with one single thread per process).

#### 3.1.4 AMD Opteron (Barcelona)

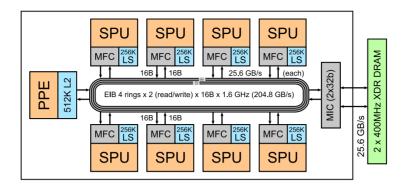

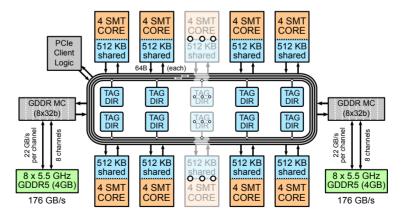

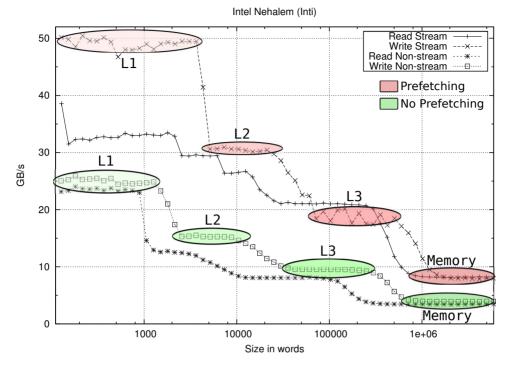

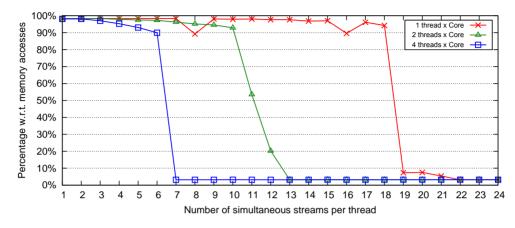

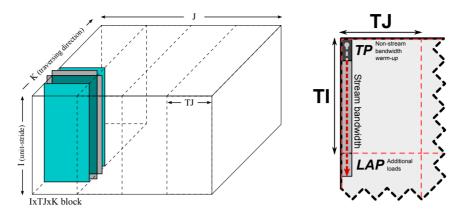

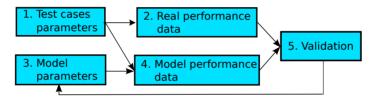

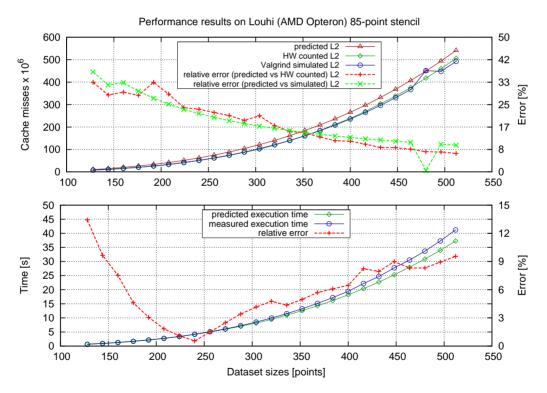

The AMD Opteron codename Barcelona was the first AMD chip to combine in the same die a quad-core processor. In this NUMA architecture, each die include an integrated memory controller that uses the AMD HyperTransport (HT) technology for point-to-point communications between chips. Although the AMD Opteron is similar to Intel Nehalem in number of cores, clock rate and cache sizes, performance results can differ significantly. The lack of SMT parallelism and the number of channels of the memory controllers and their frequency are the main reasons of its lower performance.