# Run-time support for multi-level disjoint memory address spaces

Javier Bueno Hedo

Advisor: Xavier Martorell Bofill

Departament d'Arquitectura de Computadors

Universitat Politècnica de Catalunya

Thesis submitted in fulfillment of the requirements of the degree: Doctor per la Universitat Politècnica de Catalunya

July 2015

### **Abstract**

High Performance Computing (HPC) systems have become widely used tools in many industry areas and research fields. Research to produce more powerful and efficient systems has grown in par with their popularity. As a consequence, the complexity of modern HPC architectures has increased in order to provide systems with the highest levels of performance. This increased complexity has also affected the way HPC systems are programmed. HPC users have to deal with new devices, languages and tools, and this is can be a significant access barrier to people that do not have a deep knowledge in computer science.

On par with the evolution of HPC systems, programming models have also evolved to ease the task of developing applications for these machines. Two well-known examples are OpenMP and MPI. The former can be used in shared memory systems and is praised for offering an easy methodology of software development. The latter is more popular because it targets distributed environments but it is considered burdensome to use. Besides these two, many programming models have emerged to propose new methodologies or to handle new hardware devices. One of these models is OmpSs.

OmpSs is a programming model for modern HPC systems that is based on OpenMP and StarSs. Developed by the Programming Models group at the Barcelona Supercomputing Center, it targets the latest generation of HPC systems while benefiting from the ease of use of OpenMP. OmpSs offers asynchronous parallelism with the concept of *tasks* with data dependencies. These tasks allow the specification of sections of code that can be executed in parallel while the dependencies specify the restrictions about the order in which the tasks can be executed. With this, OmpSs programs can adapt to a many different system configurations while fundamentally still being sequential programs with annotations.

This thesis explores the benefits of providing OmpSs the capability to target architectures

with complex memory hierarchies. An example of such systems can be the new generation of clusters that use accelerators to power their computing capabilities. The memory hierarchy of these machines is composed of a first level of distributed memory formed by the memory of each individual node, and a second level formed by the private memory of each accelerator devices. We propose a reference implementation that enables OmpSs programs to run on a cluster with or without accelerators while also providing a competitive performance when compared with other programming models.

We also discuss the enhancement of the OmpSs programming model with the support of non-contiguous regions of data. Offering this feature allows applications with complex data accesses to be easily annotated with OmpSs. This is important to widen the spectrum of applications that can be handled by the programming model. We present an implementation and evaluation of the performance and programmability impact of supporting non-contiguous memory regions.

### **Acknowledgments**

I would like to thank Dr. Xavier Martorell for giving me the chance of pursue a doctorate at the Departament d'Arquitectura de Computadors at UPC, and tutoring this work. Also special thanks to Dr. Alejandro Duran who also provided invaluable guidance to develop this thesis, undoubtedly this work would not have possible without his support. This work was supported by the European Commission through the HiPEAC-2 Network of Excellence (FP7/ICT 217068), the HiPEAC-3 Network of Excellence (ICT FP7 NoE 287759) the ENCORE project (FP7-248647), the TERAFLUX project (FP7-249013) and the TEXT project (IST-2007-261580), the Spanish Ministry of Education (TIN2007-60625, TIN2012-34557, and CSD2007-00050) and the Generalitat de Catalunya (2009-SGR-980).

I consider an important part of this thesis the people I have had the pleasure to meet while working at the Barcelona Supercomputing Center. Big thanks to Roger Ferrer, Xavier Teruel, Jordi Vaquero, Alberto Miranda, Jairo Balart, David Ródenas, Juanjo Costa, Marta García, Judit Planas, Guillermo Miranda, Sergi Mateo, Victor López, Sara Royuela, Claudia Rosas, Jan Ciesko, Diego Caballero, Jorge Bellón, Marçal Solà, Diego Nieto, Marcos Maroñas and many others who I have crossed paths with. Thanks for sharing many moments that made this thesis such a way easier and enjoyable experience. Definitely meeting you is one of the most valuable things I have got from doing this work.

I also want to thank my family for all the support they have given to me. My parents have worked hard during their lives to ensure that I received a good education. Their effort is also part of this thesis.

Finally, special thanks go to my wife, Sonia, who has been patient and supportive during these years. She excels in making me happy every day which compensates some of the feelings that were caused by this thesis. Thank you.

## **Contents**

| 1 | Intr | oductio | on                                                | 13 |

|---|------|---------|---------------------------------------------------|----|

|   | 1.1  | Motiva  | ation                                             | 13 |

|   |      | 1.1.1   | Programming models for High Performance Computing | 15 |

|   | 1.2  | Object  | ive of the thesis                                 | 17 |

|   | 1.3  | Thesis  | contributions                                     | 18 |

|   | 1.4  | Thesis  | organization                                      | 20 |

| 2 | The  | OmpSs   | s programming model                               | 23 |

|   | 2.1  | Introd  | uction                                            | 23 |

|   | 2.2  | Expres  | ssing parallelism                                 | 25 |

|   |      | 2.2.1   | Tasks                                             | 25 |

|   |      | 2.2.2   | Loops                                             | 27 |

|   |      | 2.2.3   | Multi-level parallelism                           | 27 |

|   | 2.3  | Synch   | ronizing parallelism                              | 28 |

|   |      | 2.3.1   | Dependencies                                      | 28 |

|   |      | 2.3.2   | Explicit synchronization                          | 31 |

|   | 2.4  | Refere  | ncing memory                                      | 32 |

|   | 2.5  | Disjoir | nt address spaces                                 | 33 |

|   |      | 2.5.1   | Single address space view                         | 33 |

|   |      | 2.5.2   | Specifying task data                              | 33 |

|   |      | 2.5.3   | Accessing children task data from the parent task | 35 |

|   |      | 2.5.4   | Limitations                                       | 37 |

|   | 2.6  | Hetero  | geneity                                           | 38 |

|   | 2.7 | Additi | onal features               | 39 |

|---|-----|--------|-----------------------------|----|

|   |     | 2.7.1  | Priority clause             | 39 |

|   |     | 2.7.2  | Task versioning             | 39 |

|   | 2.8 | Influe | nce in OpenMP               | 40 |

| 3 | The | OmpSs  | s run-time environment      | 43 |

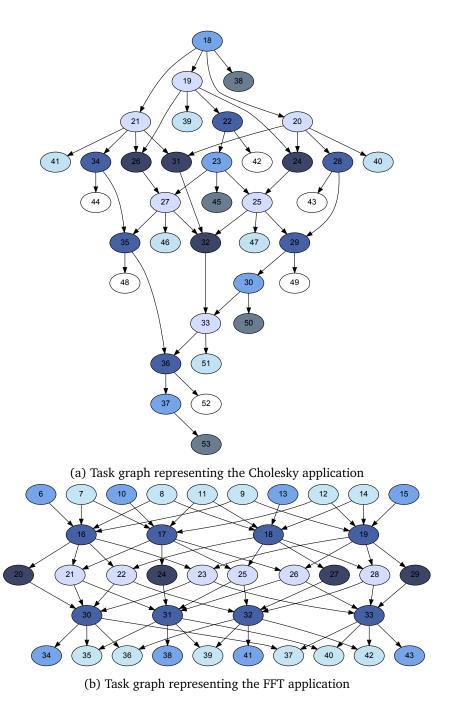

|   | 3.1 | Mercu  | rium compiler               | 43 |

|   | 3.2 | Nanos  | ++ run-time library         | 45 |

|   |     | 3.2.1  | Work Descriptors            | 45 |

|   |     | 3.2.2  | Architecture support        | 46 |

|   |     | 3.2.3  | Behavior subsystems         | 48 |

|   |     | 3.2.4  | Execution flow              | 52 |

|   | 3.3 | Conclu | asions                      | 53 |

| 4 | Omp | Ss for | clusters of multi-cores     | 55 |

|   | 4.1 | Cluste | r architectures             | 56 |

|   | 4.2 | Nanos  | ++ for clusters             | 56 |

|   |     | 4.2.1  | New components              | 57 |

|   |     | 4.2.2  | Network                     | 59 |

|   |     | 4.2.3  | Master-slave design         | 59 |

|   |     | 4.2.4  | Task execution              | 60 |

|   |     | 4.2.5  | Memory management           | 61 |

|   |     | 4.2.6  | Optimizations               | 63 |

|   | 4.3 | Impac  | t in OmpSs                  | 65 |

|   |     | 4.3.1  | Cluster memory              | 65 |

|   | 4.4 | Perfor | mance evaluation            | 65 |

|   |     | 4.4.1  | Methodology and environment | 66 |

|   |     | 4.4.2  | Benchmarks                  | 66 |

|   |     | 4.4.3  | Experiments                 | 69 |

|   |     | 4.4.4  | Results: MareNostrum2       | 69 |

|   |     | 4.4.5  | Results: MareNostrum3       | 70 |

|   | 4.5 | Conclu | asions                      | 74 |

| 5 | Omp | Ss for | clusters of GPUs            | 77 |

|   | 5.1 | Cluste | rs with GPUs                | 78 |

|   | 5.2 | Nanos  | ++ support for GPUs         | 78 |

CONTENTS 9

|   | 5.3  | Nanos   | ++ for clusters of GPUs                        | 79  |

|---|------|---------|------------------------------------------------|-----|

|   |      | 5.3.1   | Cluster thread                                 | 80  |

|   |      | 5.3.2   | Hierarchical address space organization        | 80  |

|   |      | 5.3.3   | Optimizations                                  | 82  |

|   | 5.4  | Impac   | t in OmpSs                                     | 83  |

|   | 5.5  | Perform | mance evaluation                               | 83  |

|   |      | 5.5.1   | Methodology and environment                    | 83  |

|   |      | 5.5.2   | Benchmarks                                     | 84  |

|   |      | 5.5.3   | Experiments                                    | 85  |

|   |      | 5.5.4   | Results                                        | 86  |

|   | 5.6  | Produ   | ctivity evaluation                             | 88  |

|   | 5.7  | Conclu  | isions                                         | 90  |

| 6 | Regi | ons of  | data in OmpSs                                  | 93  |

|   | 6.1  | Limita  | tions of Nanos++                               | 94  |

|   |      | 6.1.1   | Dependencies                                   | 94  |

|   |      | 6.1.2   | Data directory and cache                       | 95  |

|   | 6.2  | Impac   | t of data regions in OmpSs                     | 95  |

|   | 6.3  | Precise | e regions of data in Nanos++                   | 98  |

|   |      | 6.3.1   | Representing regions                           | 98  |

|   |      | 6.3.2   | Region based memory management                 | 103 |

|   | 6.4  | Optim   | izing for clusters                             | 104 |

|   |      | 6.4.1   | Data packing for non-contiguous data transfers | 104 |

|   |      | 6.4.2   | Affinity scheduler improvements                | 105 |

|   | 6.5  | Perfor  | mance evaluation                               | 106 |

|   |      | 6.5.1   | Methodology and environment                    | 106 |

|   |      | 6.5.2   | Benchmarks                                     | 107 |

|   |      | 6.5.3   | Experiments                                    | 109 |

|   |      | 6.5.4   | Results: Minotauro                             | 109 |

|   |      | 6.5.5   | Results: MareNostrum3                          | 113 |

|   | 6.6  | Conclu  | ısions                                         | 116 |

| 7 | Rela | ted wo  | rk                                             | 119 |

|   | 7.1  | Progra  | imming models for distributed systems          | 119 |

|   |      | 7.1.1   | Translation to MPI                             | 120 |

| 8 | Con | clusion | s and Future Work                          | 127 |

|---|-----|---------|--------------------------------------------|-----|

|   |     | 7.2.2   | Annotation-based programming models        | 124 |

|   |     | 7.2.1   | Translation to CUDA/OpenCL                 | 123 |

|   | 7.2 | Progra  | amming models for heterogeneous systems    | 122 |

|   |     | 7.1.3   | Partitioned global address space           | 121 |

|   |     | 7.1.2   | Software distributed shared memory systems | 120 |

# **List of Figures**

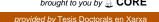

| 1.1  | Top 500 Supercomputers types over the time as of June 2014         | 14 |

|------|--------------------------------------------------------------------|----|

| 1.2  | Top 5 supercomputers as of June 2014                               | 16 |

| 2.1  | Inline task example with OmpSs                                     | 26 |

| 2.2  | Task function example with OmpSs                                   | 26 |

| 2.3  | Parallelizing a loop with OmpSs                                    | 27 |

| 2.4  | Invalid data dependency on a nested task                           | 29 |

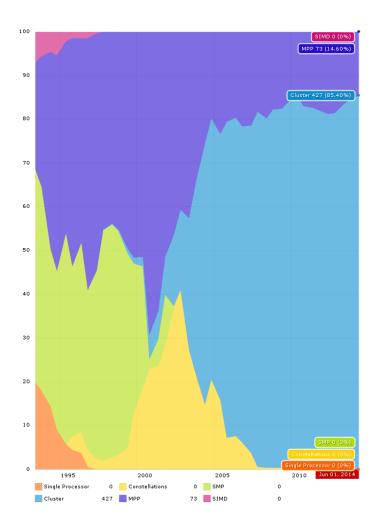

| 2.5  | Example task graphs                                                | 30 |

| 2.6  | Example of usage of firstprivate                                   | 31 |

| 2.7  | An OmpSs program with a SMP task and a GPU task                    | 35 |

| 2.8  | Illegal and legal accesses from the parent task                    | 35 |

| 2.9  | Difference between using noflush or not on a taskwait              | 36 |

| 2.10 | Example usage of taskwait on to selectively synchronize data       | 37 |

| 2.11 | Using a complex data structure within a copy clause                | 38 |

| 2.12 | Usage of the task versioning mechanism                             | 40 |

| 3.1  | Mercurium C/C++/FORTRAN compiler internal organization             | 44 |

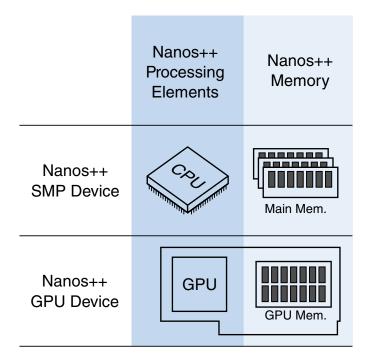

| 3.2  | Nanos hardware resources                                           | 47 |

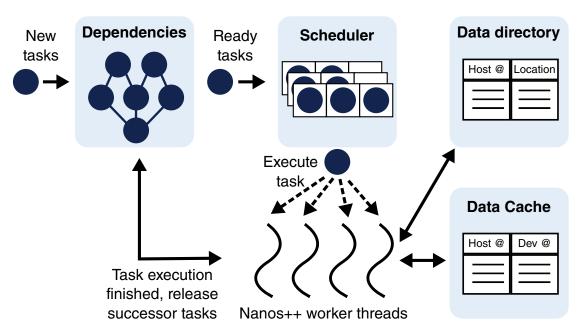

| 3.3  | Nanos++ internal subsystems                                        | 48 |

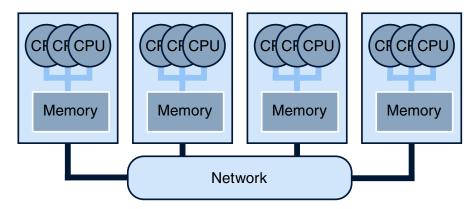

| 4.1  | Cluster architecture                                               | 56 |

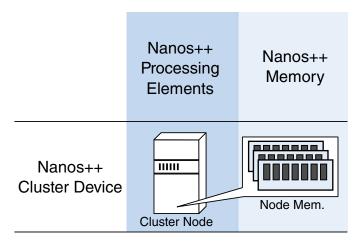

| 4.2  | Nanos++ new hardware resources                                     | 57 |

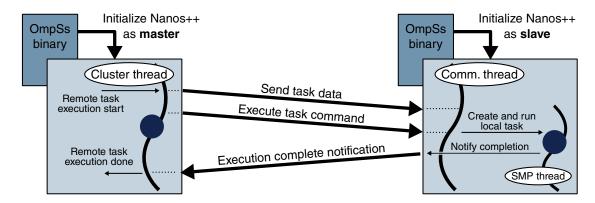

| 4.3  | Master-slave pattern used to implement the Nanos++ cluster support | 60 |

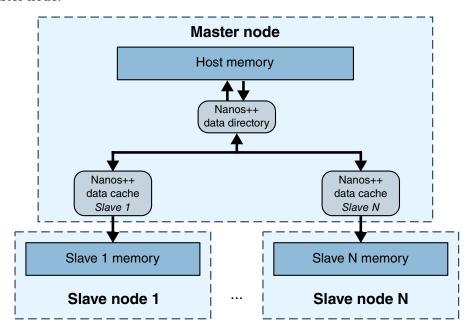

| 44   | Nanos++ distributed memory management organization                 | 62 |

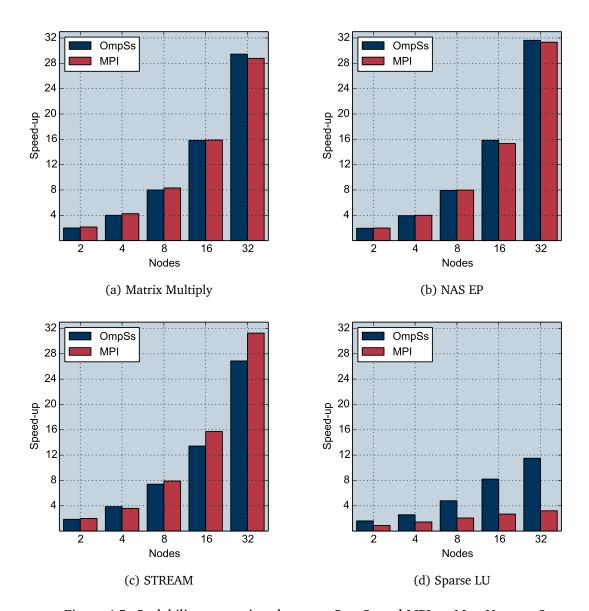

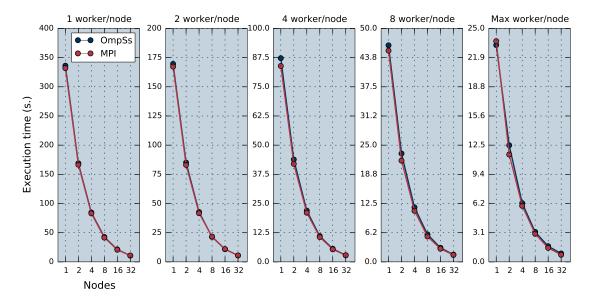

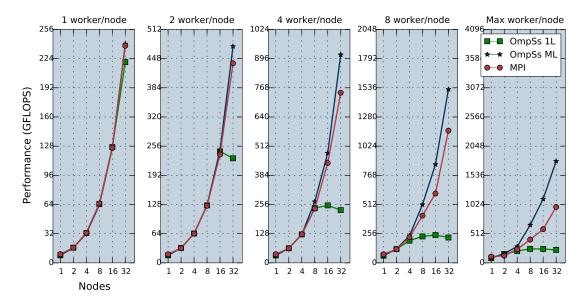

| 4.5  | Scalability comparison between OmpSs and MPI on MareNostrum2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 71  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

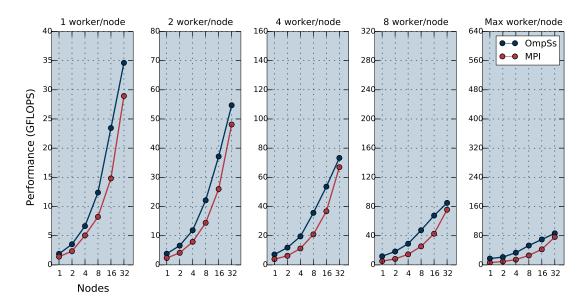

| 4.6  | Matmul performance comparison between OmpSs and MPI on MareNostrum3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 72  |

| 4.7  | NAS EP performance comparison between OmpSs and MPI on MareNostrum3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 73  |

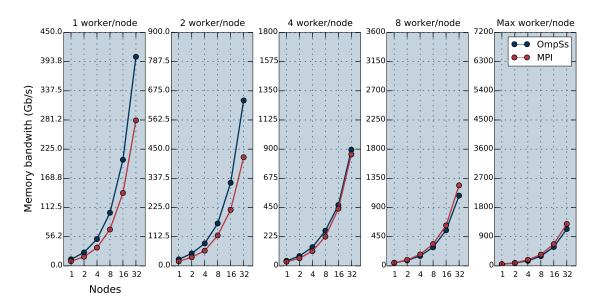

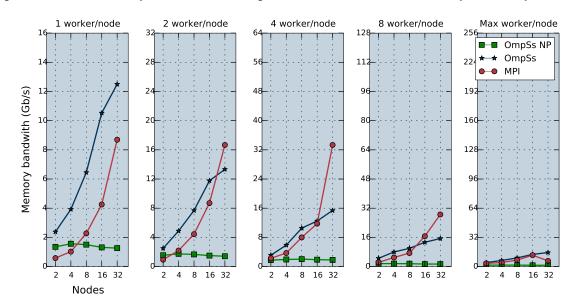

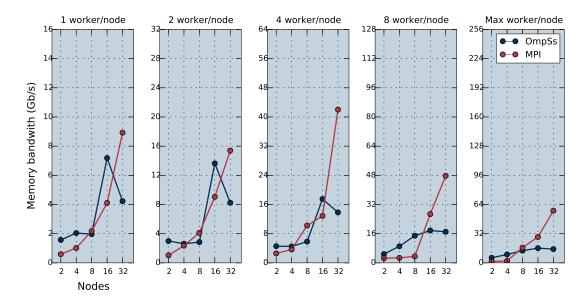

| 4.8  | STREAM performance comparison between OmpSs and MPI on MareNostrum3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 74  |

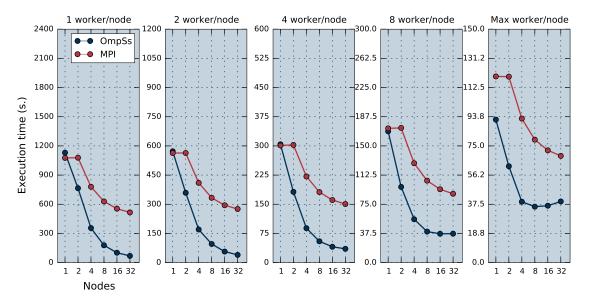

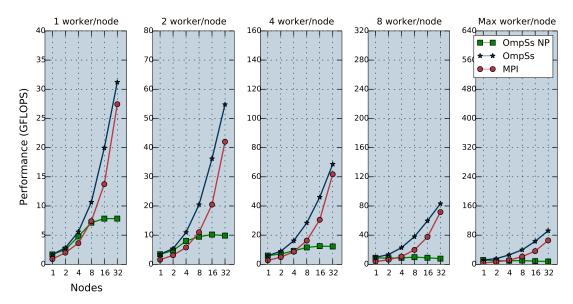

| 4.9  | SparseLU performance comparison between OmpSs and MPI on MareNostrum3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 74  |

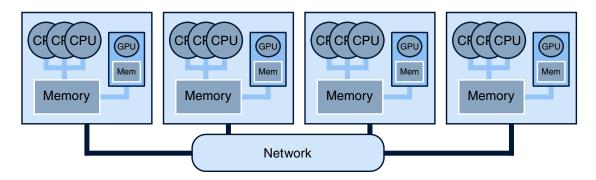

| 5.1  | Cluster GPU architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 79  |

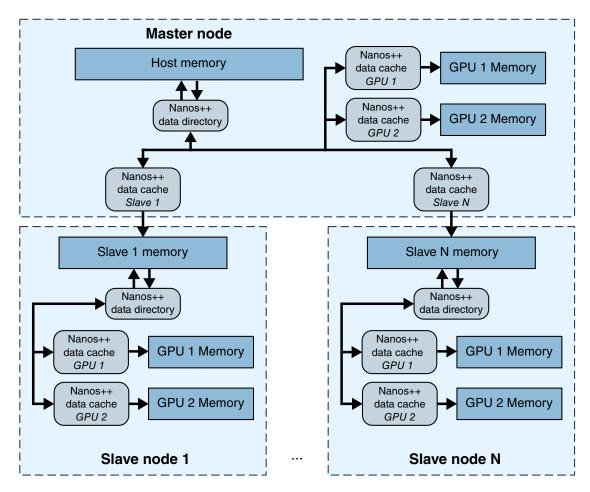

| 5.2  | Hierarchical memory management structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 81  |

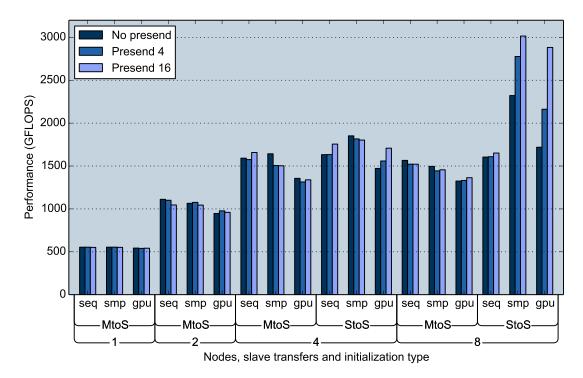

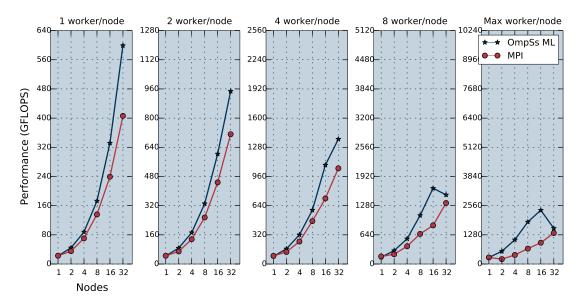

| 5.3  | Matmul performance results on the GPU cluster environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 87  |

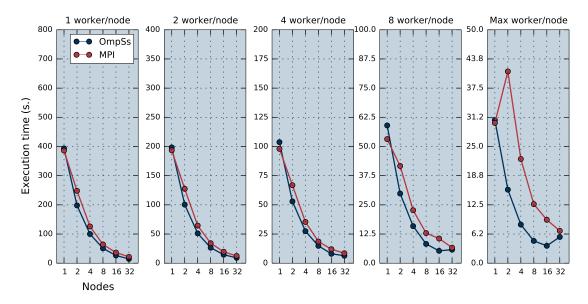

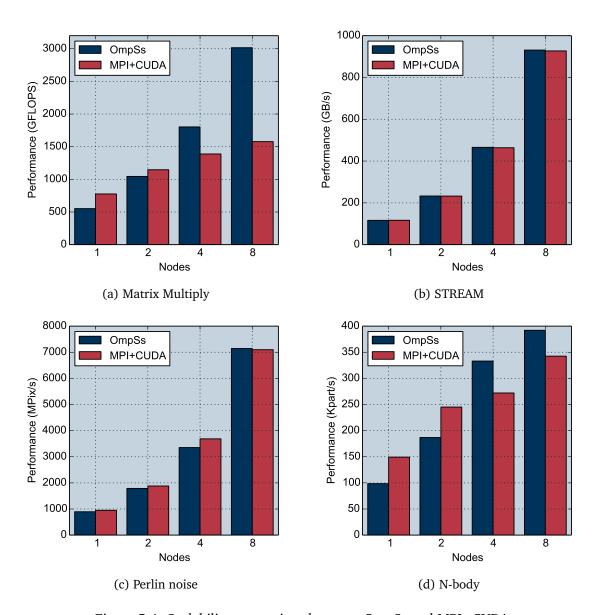

| 5.4  | Scalability comparison between OmpSs and MPI+CUDA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 89  |

| 5.5  | $Comparison\ of\ total\ number\ of\ lines\ in\ Serial,\ CUDA,\ MPI+CUDA\ and\ OmpSs+CUDA\ $ | JDA |

|      | versions of the benchmarks (in parenthesis, the percentage of increment, with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

|      | respect to the Serial version)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 90  |

| 6.1  | DGEMM OmpSs implementation without regions support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 96  |

| 6.2  | $\operatorname{DGEMM}$ OmpSs implementation, with regions and multi-level parallelism                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 96  |

| 6.3  | FFT1D OmpSs implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 97  |

| 6.4  | A task defining a region                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 99  |

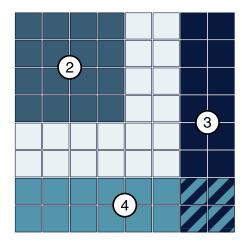

| 6.5  | Internal organization of regions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 100 |

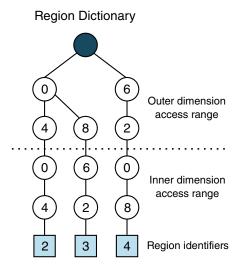

| 6.6  | Region Dictionary example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 101 |

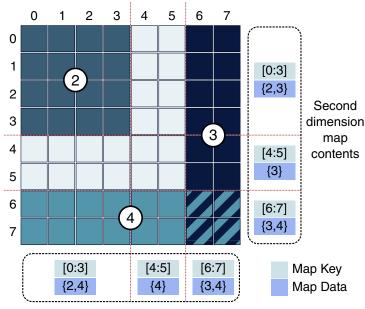

| 6.7  | Intersection maps of the corresponding program object and regions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 102 |

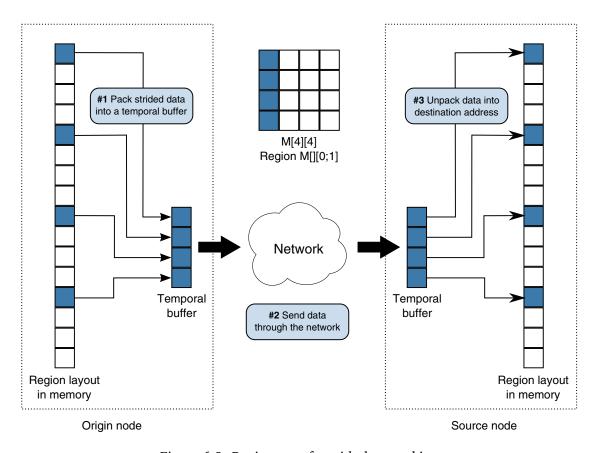

| 6.8  | Region transfer with data packing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 105 |

| 6.9  | DGEMM performance comparison, OmpSs against MPI running on Minotauro.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 111 |

| 6.10 | PTRANS performance comparison, OmpSs against MPI running on Minotauro.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 112 |

| 6.11 | FFT1D performance comparison, OmpSs against MPI running on Minotauro.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 113 |

| 6.12 | DGEMM performance comparison, OmpSs against MPI running on MareNos-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|      | trum3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 114 |

| 6.13 | PTRANS performance comparison, OmpSs against MPI running on MareNos-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

|      | trum3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 115 |

| 6.14 | FFT1D performance comparison, OmpSs against MPI running on MareNos-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|      | trum3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 116 |

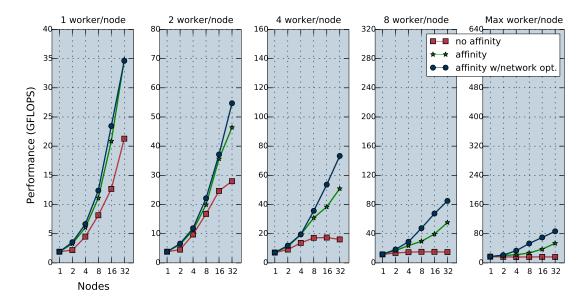

| 6.15 | OmpSs FFT1D performance with different execution options running on MareNos                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3-  |

|      | trum3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 117 |

# 1 Introduction

#### 1.1 Motivation

General purpose CPUs have reached a performance level where it is difficult to obtain more performance from a single unit. This has affected the way high-performance computers are organized, shifting to designs with a higher number of CPUs, since relying on future, more powerful, designs is no longer a viable option. This trend has brought new challenges in how processors are interconnected in order to allow systems to achieve a good performance at a reasonable cost.