# ENERGY-EFFICIENT MOBILE GPU SYSTEMS

Jose Maria Arnau

Doctor of Philosophy

Department of Computer Architecture

Universitat Politecnica de Catalunya

2014

# Abstract

The design of mobile GPUs is all about saving energy. Smartphones and tablets are battery-operated and thus any type of rendering needs to use as little energy as possible. Furthermore, smartphones do not include sophisticated cooling systems due to their small size, making heat dissipation a primary concern. Improving the energy-efficiency of mobile GPUs will be absolutely necessary to achieve the performance required to satisfy consumer expectations, while maintaining operating time per battery charge and keeping the GPU in its thermal limits.

The first step in optimizing energy consumption is to identify the sources of energy drain. Previous studies have demonstrated that the register file is one of the main sources of energy consumption in a GPU. As graphics workloads are highly data- and memory-parallel, GPUs rely on massive multithreading to hide the memory latency and keep the functional units busy. However, aggressive multithreading requires a huge register file to keep the registers of thousands of simultaneous threads. Such a big register file exceeds the power budget typically available for an embedded graphics processors and, hence, more energy-efficient memory latency tolerance techniques are necessary.

On the other hand, prior research showed that the off-chip accesses to system memory are one of the most expensive operations in terms of energy in a mobile GPU. Therefore, optimizing memory bandwidth usage is a primary concern in mobile GPU design. Many bandwidth saving techniques, such as texture compression or ARM's transaction elimination, have been proposed in both industry and academia.

The purpose of this thesis is to study the characteristics of mobile graphics processors and mobile workloads in order to propose different energy saving techniques specifically tailored for the low-power segment. Firstly, we focus on energy-efficient memory latency tolerance. We analyze several techniques such as multithreading and prefetching and conclude that they are effective but not energy-efficient. Next, we propose an architecture for the fragment processors of a mobile GPU that is based on the decoupled access/execute paradigm. The results obtained by using a cycle-accurate mobile GPU simulator and several commercial Android games show that the decoupled architecture combined with a small degree of multithreading provides the most energy efficient solution for hiding memory latency. More specifically, the decoupled access/execute-like design with just 4 SIMD threads/processor is able to achieve 97% of the performance

of a larger GPU with 16 SIMD threads/processor, while providing 20.5% energy savings on average.

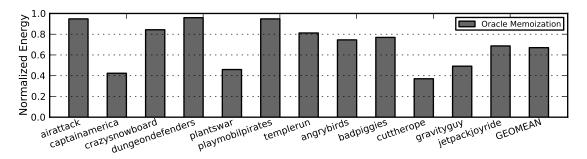

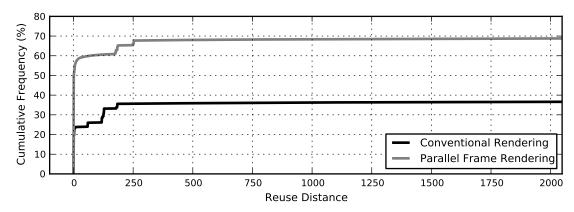

Secondly, we focus on optimizing memory bandwidth in a mobile GPU. We analyze the bandwidth usage in a set of commercial Android games and find that most of the bandwidth is employed for fetching textures, and also that consecutive frames share most of the texture dataset as they tend to be very similar. However, the GPU cannot capture inter-frame texture re-use due to the big size of the texture dataset for one frame. Based on this analysis, we propose Parallel Frame Rendering (PFR), a technique that overlaps the processing of multiple frames in order to exploit inter-frame texture re-use and save bandwidth. By processing multiple frames in parallel textures are fetched once every two frames instead of being fetched in a frame basis as in conventional GPUs. PFR provides 23.8% memory bandwidth savings on average in our set of Android games, that result in 12% speedup and 20.1% energy savings.

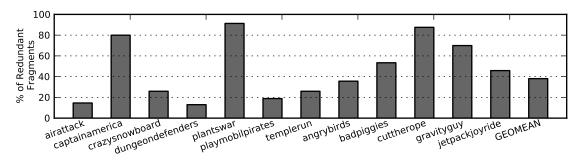

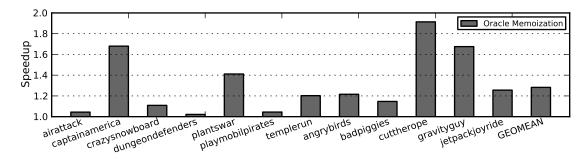

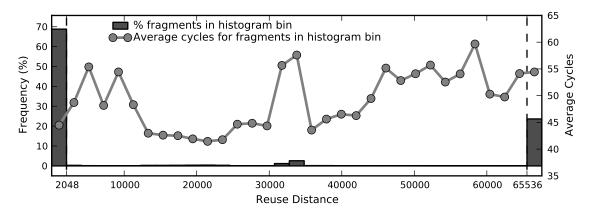

Finally, we improve PFR by introducing a hardware memoization system on top. As consecutive frames tend to be very similar, not only most of the texture fetches are the same from frame to frame but also a significant percentage of the computations performed on the fragments. We analyze the redundancy in mobile games and find that more than 38% of the Fragment Program executions are redundant on average. We thus propose a task-level hardware-based memoization system that, when architected on top of PFR, provides 15% speedup and 12% energy savings on average.

# Acknowledgements

First and foremost, I would like to thank my advisers Joan-Manuel Parcerisa and Polychronis Xekalakis, for teaching me everything I know about Computer Architecture. I feel very lucky to have had the opportunity to work with them over the past years. I am very grateful for their invaluable guidance and support.

I would like to make a special mention to Antonio Gonzalez, who offered me the opportunity to start a research career in the ARCO group. Thanks for your wise advice and support.

I wish to thank all the members of ARCO. I was lucky enough to be part of a large and enriching research group. I was fortunate to share an office with Marc Lupon and Enric Herrero, thanks for teaching me what being a PhD student means. Thanks to Aleksandar Brankovic for showing me what attending to a conference is about. Thanks to Enrique De Lucas for his feedback, I am very glad you decided to work in the exciting field of mobile graphics processors!

I would like to thank Christophe Dubach for having me as an intern in the University of Edinburgh. It was a great experience and a pleasure to work with him. Thanks to all the members of the CArD research group. Thanks to Chris Fensch for his feedback and his valuable help in finding opportunities to develop my career after my PhD.

On a more personal note, I would like to thank my family for their unconditional support, their fondness and their infinite patience. My parents Jose-Medin and Gloria, my brother Ignacio and my sister Maria Lidon have always encouraged me to carry on with my research work. I am grateful for their love, care and affection.

# Declaration

I declare that this thesis was composed by myself, that the work contained therein is my own except where explicitly stated otherwise in the text, and that this work has not been submitted for any other degree or professional qualification except as specified. Some of the material used in this thesis has been published in the following papers:

- "Boosting Mobile GPU Performance with a Decoupled Access/Execute Fragment Processor".

Jose-Maria Arnau, Joan-Manuel Parcerisa and Polychronis Xekalakis.

International Symposium on Computer Architecture, 2012.

- "TEAPOT: A Toolset for Evaluating Performance, Power and Image Quality on Mobile Graphics Systems".

Jose-Maria Arnau, Joan-Manuel Parcerisa and Polychronis Xekalakis.

International Conference on Supercomputing, 2013.

- "Parallel Frame Rendering: Trading Responsiveness for Energy on a Mobile GPU".

Jose-Maria Arnau, Joan-Manuel Parcerisa and Polychronis Xekalakis.

International Conference on Parallel Architectures and Compilation Techniques, 2013.

- "Eliminating Redundant Fragment Shader Executions on a Mobile GPU via Hardware Memoization".

Jose-Maria Arnau, Joan-Manuel Parcerisa and Polychronis Xekalakis.

International Symposium on Computer Architecture, 2014.

(Jose Maria Arnau)

# Contents

| Abstract |              |                                   |                                                  |          |  |  |

|----------|--------------|-----------------------------------|--------------------------------------------------|----------|--|--|

| 1        | Introduction |                                   |                                                  |          |  |  |

|          | 1.1          | Current Trends in Mobile Graphics |                                                  |          |  |  |

|          |              | 1.1.1                             | Mobile Graphics Hardware                         | 12       |  |  |

|          |              | 1.1.2                             | Mobile Graphics Software                         | 13       |  |  |

|          | 1.2          | Proble                            | em Statement                                     | 15       |  |  |

|          | 1.3          | State-                            | of-the-art in GPU Energy Efficiency              | 18       |  |  |

|          |              | 1.3.1                             | Memory Latency Tolerance Techniques              | 18       |  |  |

|          |              | 1.3.2                             | Bandwidth Saving Techniques                      | 21       |  |  |

|          |              | 1.3.3                             | Other Related Works                              | 24       |  |  |

|          | 1.4          | Thesis                            | S Overview and Contributions                     | 25       |  |  |

|          |              | 1.4.1                             | Mobile GPU Simulation Infrastructure             | 25       |  |  |

|          |              | 1.4.2                             | The Decoupled Access/Execute Fragment Processor  | 26       |  |  |

|          |              | 1.4.3                             | Parallel Frame Rendering                         | 29       |  |  |

|          |              | 1.4.4                             | Eliminating Redundant Fragment Shader Executions | 31       |  |  |

|          | 1.5          | Thesis                            | s Structure                                      | 32       |  |  |

| <b>2</b> | Evr          | verime                            | ntal Environment                                 | 35       |  |  |

| 4        | 2.1          | Simulation Infrastructure         |                                                  |          |  |  |

|          | 2.1          | 2.1.1                             |                                                  | 35<br>36 |  |  |

|          |              |                                   | Application Level                                |          |  |  |

|          |              | 2.1.2                             | Driver Level                                     | 37       |  |  |

|          |              | 2.1.3                             | Hardware Level                                   | 38       |  |  |

|          |              | 2.1.4                             | Automatic Image Quality Assessment               | 45       |  |  |

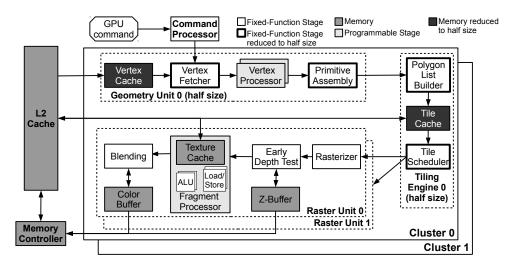

|   |                            | 2.1.5                                       | Assumed Graphics Pipeline                           | 45  |  |  |  |

|---|----------------------------|---------------------------------------------|-----------------------------------------------------|-----|--|--|--|

|   | 2.2                        | 2 Workloads                                 |                                                     |     |  |  |  |

|   |                            | 2.2.1                                       | Workload Selection                                  | 47  |  |  |  |

|   |                            | 2.2.2                                       | Workload Characterization                           | 51  |  |  |  |

|   | 2.3                        | Summ                                        | nary of Methodology                                 | 55  |  |  |  |

| 3 | Dec                        | coupled                                     | d Access/Execute Fragment Processor                 | 57  |  |  |  |

|   | 3.1                        | .1 Memory Latency Tolerance in a Mobile GPU |                                                     |     |  |  |  |

|   |                            | 3.1.1                                       | Aggressive Multithreading                           | 59  |  |  |  |

|   |                            | 3.1.2                                       | Hardware Prefetching                                | 61  |  |  |  |

|   | 3.2                        | Decou                                       | apled Architecture for Fragment Processors          | 67  |  |  |  |

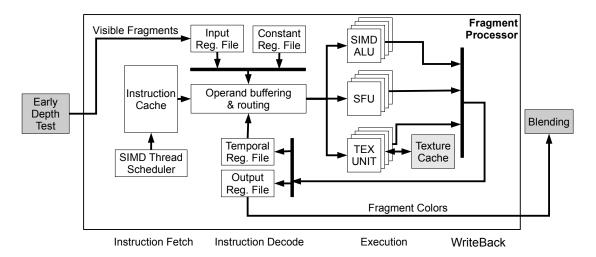

|   |                            | 3.2.1                                       | Base Architecture                                   | 67  |  |  |  |

|   |                            | 3.2.2                                       | Remote Texture Cache Accesses                       | 69  |  |  |  |

|   | 3.3                        | Multit                                      | threading, Prefetching and Decoupled Access/Execute | 72  |  |  |  |

|   | 3.4                        | Concl                                       | usions                                              | 76  |  |  |  |

| 4 | Parallel Frame Rendering 7 |                                             |                                                     |     |  |  |  |

|   | 4.1                        | Memo                                        | bry Bandwidth Usage on a Mobile GPU                 | 79  |  |  |  |

|   | 4.2                        | Trading Responsiveness for Energy           |                                                     |     |  |  |  |

|   |                            | 4.2.1                                       | Parallel Frame Rendering                            | 81  |  |  |  |

|   |                            | 4.2.2                                       | Reactive Parallel Frame Rendering                   | 83  |  |  |  |

|   |                            | 4.2.3                                       | N-Frames Reactive Parallel Frame Rendering          | 86  |  |  |  |

|   |                            | 4.2.4                                       | Delay Randomly Parallel Frame Rendering             | 87  |  |  |  |

|   | 4.3                        | Exper                                       | imental Results                                     | 88  |  |  |  |

|   | 4.4                        | Concl                                       | usions                                              | 93  |  |  |  |

| 5 | Har                        | ardware Memoization in Mobile GPUs 95       |                                                     |     |  |  |  |

|   | 5.1                        | Redundancy in Mobile GPUs                   |                                                     |     |  |  |  |

|   | 5.2                        | Redundancy and Memoization                  |                                                     |     |  |  |  |

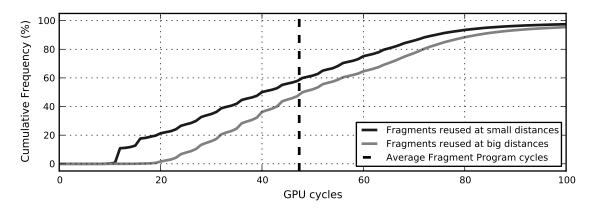

|   |                            | 5.2.1                                       | Reuse Distance and Parallel Frame Rendering         | 98  |  |  |  |

|   |                            | 5.2.2                                       | Task-level Complexity                               | 99  |  |  |  |

|   |                            | 5.2.3                                       | Referential Transparency                            | 100 |  |  |  |

|              | 5.3                                          | Task Level Hardware-Based Memoization on a Mobile GPU | 101 |  |  |

|--------------|----------------------------------------------|-------------------------------------------------------|-----|--|--|

|              |                                              | 5.3.1 Memoization System                              | 101 |  |  |

|              |                                              | 5.3.2 Screen Coordinates Independent Memoization      | 106 |  |  |

|              | 5.4                                          | Experimental Results                                  | 107 |  |  |

|              | 5.5                                          | Conclusions                                           | 114 |  |  |

| 6            | Con                                          | nclusions                                             | 115 |  |  |

|              | 6.1                                          | Conclusions                                           | 115 |  |  |

|              | 6.2                                          | Contributions                                         | 117 |  |  |

|              | 6.3                                          | Open-Research Areas                                   | 118 |  |  |

| A            | A Decoupled Fragment Processor on top of TBR |                                                       |     |  |  |

| В            | callel Frame Rendering on top of IMR         | 125                                                   |     |  |  |

| $\mathbf{C}$ | Har                                          | rdware Memoization on top of IMR                      | 129 |  |  |

# Chapter 1

# Introduction

This chapter presents the background and motivation behind this work, a brief description of related work, and an overview of the main proposals and contributions of this thesis.

# 1.1 Current Trends in Mobile Graphics

Mobile phones have been adopted faster than any technology in history [137]. Smartphones and tablets are becoming primary devices of choice for a variety of activities such as reading email, playing games, taking pictures, interacting with social networks or browsing the web. In recent years, stationary desktop computers have been replaced in many scenarios by mobile devices as they begin to deliver a truly mobile computing experience. Powered by advances in mobile technology and System-on-a-Chip (SoC) design, current smartphones support a plethora of capabilities that cope with consumer expectations.

Undoubtedly, the capability to provide a real computing experience explains to a large extent the success of these mobile devices. Mobile graphics hardware/software improvements play an important role in this respect, as visually compelling graphics and high responsiveness are key to deliver a satisfactory user experience. Current mobile SoCs are able to decode 1080p videos at real time [163], capture and process pictures at resolutions bigger than 12 MegaPixels or render complex 3D graphics at high frame rates, achieving fill rates bigger than 4 GigaPixels/second [150, 161, 162]. On the other hand, smartphones support a plethora of mobile applications, for instance, more than 1.2 million Android applications are available in Google Play by May 2014 [24]. This combination of mobile hardware able to deal with multimedia content at real time frame rates and plentiful mobile software that exploits hardware capabilities makes smartphones/tablets very powerful and versatile devices.

In following sections we will discuss the mobile graphics hardware/software improvements that contributed to the expansion of the smartphones and tablets market. Later in this chapter we will discuss how supporting all these capabilities

affects the energy aspect of an embedded graphics processor, and we will introduce the main problems that have to be dealt with when designing a mobile GPU.

### 1.1.1 Mobile Graphics Hardware

In this section we will briefly review the improvements in mobile graphics hardware, focusing on the main components of the graphics system: the screen and the Graphics Processing Unit (GPU). In first place, mobile screens have evolved from small text-based displays to high resolution multi-touch displays. High-end smartphones begin to support Full-HD (1080x1920) resolution in 5-inches displays, whereas HD resolution (720x1280) is common in the mid and low-end. Hence, current screens deliver high quality visually compelling graphics, making the smartphone amenable for a broad range of applications. Furthermore, the touch screen is the main input device in a smartphone, being its response time critical for user experience.

On the other hand, mobile GPUs have experienced a significant evolution in recent years, becoming a key component of a SoC. Early mobile phones featured pure software rendering, performing all the graphics on the CPU since no specific graphics hardware was included. Furthermore, fixed-point arithmetic was employed in many cases due to the lack of floating-point units in embedded processors [157]. However, due to the aforementioned evolution in screen resolution the graphics system was required to provide huge fill rates, and the use of hardware acceleration became a hard requirement. The first mobile GPUs were fixed-function pipelines (non-programmable) that implemented the OpenGL ES 1.1 API [53], offering fill rates in the order of 100 MegaPixels/second [161]. Based on these primitive designs, mobile GPUs evolved towards more programmability and parallelism, in a similar way than desktop GPUs did, improving both flexibility and performance. Modern smartphones include programmable multicore GPUs that support the OpenGL ES 2.0/3.0 APIs [54], achieving fill rates in the order of GigaPixels/second and supporting scenes with millions of triangles [150, 161, 162].

It is worth mentioning at this point the main actors in the mobile GPU market. NVIDIA develops the Tegra SoC [26] that includes the Ultra Low-Power GeForce GPU [117], a version of the desktop GeForce optimized for low-power consumption. The ULP GeForce implements a classical Immediate-Mode Rendering architecture [113], and it is included in high-end smartphones and tablets such as the NVIDIA SHIELD [25], the Sony XPeria Tablet S [34] or the HTC One X [17].

Mali [9] is a series of GPUs produced by ARM. Unlike desktop GPUs, Mali implements a Tile-Based Rendering architecture [165], i. e. the screen is divided into small tiles and the scene is rendered tile by tile to maximize locality and minimize bandwidth usage [51]. A more detailed comparison between Immediate-Mode and Tile-Based architectures is provided in Chapter 2. Mali GPUs are employed in

popular SoCs such as the Samsung Exynos [164], included in smartphones like the Samsung Galaxy S3 [31].

Imagination Technologies produces the PowerVR [161] family of mobile GPUs. The PowerVR also implements a Tile-Based Rendering architecture, with special emphasis on addressing the overdraw [56] problem, i. e. unnecessarily computing and writing multiple colors for the same screen pixel due to multiple graphical objects drawn over the top of one another. PowerVR GPUs are included in popular mobile devices such as the Apple iPhone 5S [6], the iPad Air [5] or the Playstation Vita [27].

Adreno [162] is the solution developed by Qualcomm for embedded devices, included in the Snapdragon SoC [163]. Adreno GPUs implement a hybrid architecture able to switch at run-time between Immediate-Mode and Tile-Based by leveraging the FlexRender technology [11]. Google Nexus 5 [22], Samsung Galaxy S5 [32] or Sony XPeria Z2 [35] are examples of popular smartphones powered by Adreno GPUs.

Beyond the products developed by big companies, there exist two other families of mobile GPUs that are not so widespread, but they achieve comparable performance and power consumption. On one hand, Vivante Corporation introduced the Vega 3D architecture [42], implemented in the Vivante GC Series of mobile GPUs. Vivante also proposed the use of a dedicated accelerator for image composition [127], the Composition Processing Cores [41], offloading all the GUI related tasks from the GPU and achieving significant energy savings. Vivante GPUs are included in mobile devices such as the Samsung Galaxy Tab 3 [33] or the Huawei Ascend G615 [18]. On the other hand, Digital Media Professionals created the PICA-200 [160] mobile GPU, the graphics processor of the Nintendo 3DS [156].

# 1.1.2 Mobile Graphics Software

In this section we will briefly review the graphics software stack of mobile devices including the applications, Operating Systems and graphics APIs. Mobile phones are no longer restricted to making phone calls and sending text messages, but they support a plethora of applications such as web browsing, maps, gaming, social networks or picture and video editing. Mobile SDKs [3, 19] deliver plenty of functionality from networking to graphics including, for instance, libraries for multimedia content processing. Furthermore, they provide access to a great diversity of hardware available in mobile devices like the GPS, the GPU, the camera or the accelerometers. On the graphics side, developers have access to numerous widgets that allow the creation of very rich user interfaces. Furthermore, graphics hardware acceleration is available via OpenGL ES [94], allowing the creation of immersive 3D environments.

OpenGL for Embedded Systems (OpenGL ES) is a subset of the OpenGL API for rendering 2D and 3D computer graphics in low-power systems, developed and

maintained by the Khronos Group [20]. OpenGL ES is the dominant graphics API for accessing the GPU in handheld and embedded devices, as it is widely supported by all the manufacturers mentioned in section 1.1.1. Khronos has released five OpenGL ES specifications so far. The OpenGL ES 1.0 and 1.1 specifications implement a fixed-function pipeline. The OpenGL ES 2.0 specification implements a programmable pipeline, providing full support for vertex/fragment shaders. The OpenGL ES 3.0 specification includes new features to enable acceleration of advanced visual effects, such as occlusion queries [15], transform feedback [36] or multiple render targets [155]. Furthermore, bandwidth saving features like texture compression [140] and framebuffer invalidation [80] are included in the API. Finally, the OpenGL ES 3.1 specification adds the compute shaders [13] to support general purpose computation on the GPU (GPGPU). OpenGL ES specifications are derived from desktop OpenGL revisions, removing complex features and redundant function calls in order to keep the GPU drivers and the graphics hardware as simple as possible.

Regarding the Operating Systems, Android and iOS clearly dominate the smartphone market [92]. On the graphics department both systems provide extensive support for developing graphical user interfaces, in the form of a rich set of widgets and support for 2D/3D rendering via OpenGL ES. Furthermore, the GUI compositor is an essential component in both Operating Systems. Composition [127] is the process of combining multiple surfaces, usually generated by multiple graphical applications running simultaneously, together into a single surface that can be displayed on the screen. In order to achieve high responsiveness, composition is usually hardware accelerated in the GPU [127] or in a dedicated accelerator [41]. Android's GUI compositor, SurfaceFlinger [2], employs the OpenGL ES 1.1 API to boost composition. Therefore, the graphics hardware is used in any mobile application that displays content in the screen, since OpenGL ES is either explicitly called by the programmer or implicitly called when using widgets that are later rendered by the OS GUI compositor.

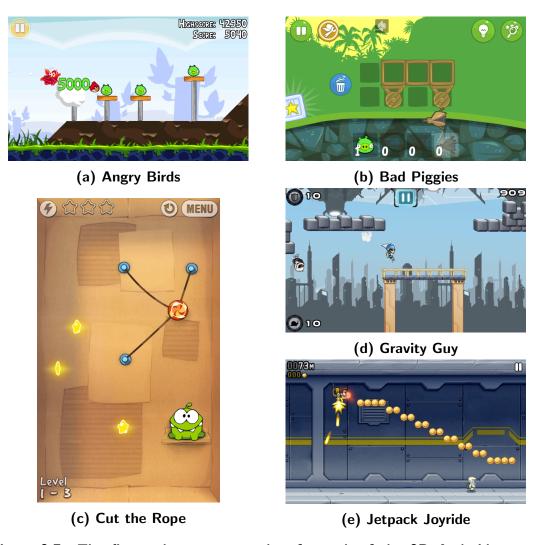

Many popular applications take benefit of hardware accelerated graphics, such as Google Maps, Google Street View or Facebook. The Web Browser also has to deal with tons of multimedia content, and WebGL [99] provides access to the GPU from JavaScript applications. Nevertheless, the applications that especially benefit from hardware acceleration are undoubtedly the numerous games available in Android and iOS. Casual 2D games like Angry Birds, with more than 1 billion downloads and 200 million active monthly users [4], or Candy Crush, with more than 500 million downloads and 124 million active daily users [16], are among the most popular applications for smartphones. Their game style, based in simple mechanics and short game levels, together with the effective use of the smartphone hardware (touch screen, accelerometers...) are some of the sources of their great acceptance.

On the other hand, smartphones and tables also support multiple desktoplike 3D games that exploit the capabilities of the graphics hardware. Popular franchises such as *Minecraft*, *Call of Duty* or *Need for Speed* are available for mobile devices. This type of games exhibit dynamic shadows [166], reflections [67], particle systems [130] and many other advanced graphical effects achieved by leveraging programmable shaders.

#### 1.2 Problem Statement

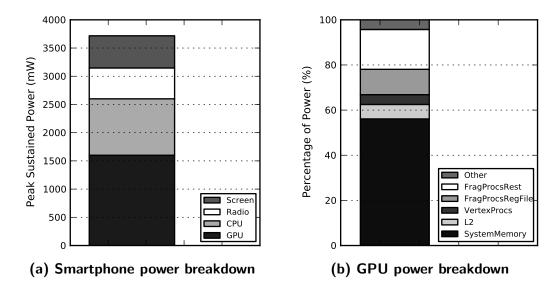

All the mobile hardware/software improvements described in the previous sections are key to satisfy consumer expectations and deliver compelling user experience. However, supporting all these capabilities comes at the cost of a significant increase in energy consumption. Figure 1.1a shows the power breakdown in a Samsung Galaxy S3 when running the Egypt benchmark of the GLBenchmark suite. The GPU is the main battery consumer, requiring more than 1500 mW. Despite technology improvements, achieving the fill rates required to support high image resolutions in mobile devices with a tiny power budget is not an easy task. Mobile GPU design is all about reducing energy consumption because architects are concerned about battery life, but also because they are concerned about heat dissipation.

As smartphones and tablets are powered by batteries, any type of graphics rendering needs to use as little energy as possible. Operating time per battery charge is an important parameter of any mobile device, since users do not want to recharge their devices every few hours. The GPU energy demand increases significantly on each generation of smartphones to achieve the performance requirements, and it increases at a much faster pace than battery improvements [126]. The trend observed in recent years shows an increasing disparity between the energy required and the energy available in a smartphone [111], producing an energy gap that widens on each new generation of mobile devices, resulting in fairly short operating times per battery charge. As an example, Figure 1.1a shows that the Samsung Galaxy S3 requires 3.17 Watts to power the screen, the CPU and the GPU —we assume the radio is disabled while running graphical benchmarks. The Galaxy S3 features a 2100 mAh battery [31] at 3.7 V, so the energy available is:  $\frac{2100mAh\times3.7V}{1000} = 7.77Wh$ . Converting the Wh to Joules we have:  $7.77Wh \times 3600\frac{s}{h} = 27972J$ . As the battery is drained at a ratio of 3.17 Joules/sec, the total operating time is 2 hours and 27 minutes. Hence, operating time per battery charge is a big concern since the energy available is consumed in just a few hours when running graphical workloads. Nevertheless, even if some breakthrough in battery technology would provide massive amounts of energy —something that is not likely to happen in the near future—mobile GPU energy consumption would still be a primary concern since architects would have to deal with a huge issue: heat dissipation.

Current smartphones and tablets feature big screens, but they are extremely thin since weight is an important parameter on mobile devices. Hence, smartphones cannot include sophisticated cooling systems such as fans or water cooling radiators. Even if batteries would suddenly become much more powerful, energy consumption could not be increased arbitrarily since the small size of the smartphone means it would need to dissipate large amounts of heat from a small area,

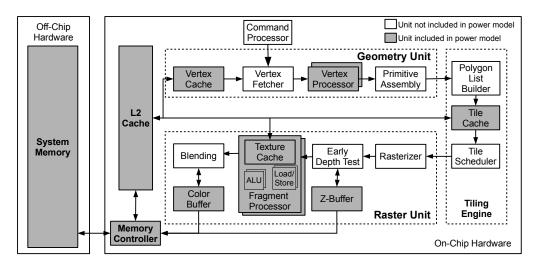

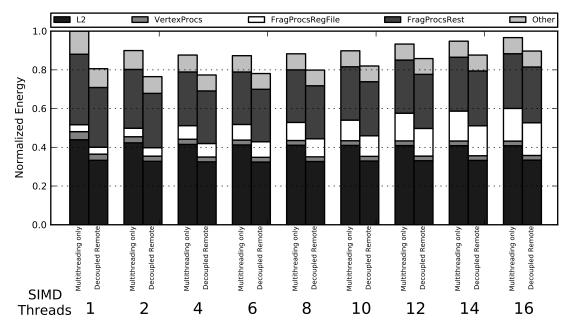

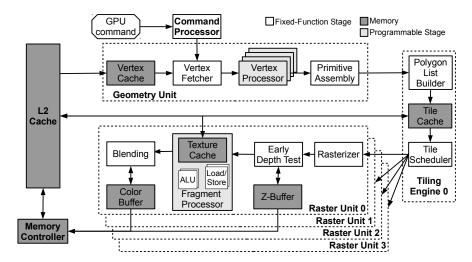

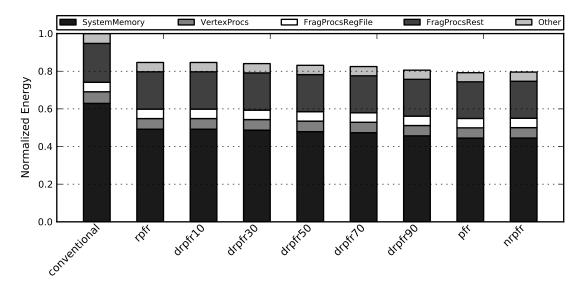

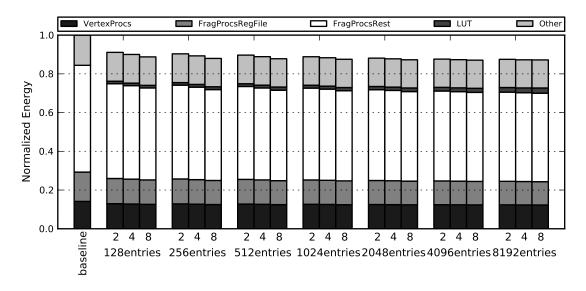

Figure 1.1: The left graph shows the power breakdown measured in a Samsung Galaxy S3. The graph includes the four main battery consumers: screen, radio, CPU and GPU. The peak power of the screen, a 4.8 inches AMOLED display at HD resolution, and the peak power of the radio are provided in [129]. The peak power of the CPU, an ARM-based dual-core Krait at 1.5 GHz, and the GPU, a Qualcomm Adreno 225, are provided in [30]. The peak power was measured while running the Egypt benchmark of the GLBenchmark suite. On the other hand, the right graph shows the power breakdown in a mobile GPU with a Tile-Based Rendering architecture similar to the ARM Mali 400MP4. The graph shows the average power estimated by our power model based on McPAT, described in section 2.1.3, when running the twelve Android games presented in section 2.2.1. The power consumed by the Fragment Processors is split in two categories: the power of the main Register File, "FragProcsRegFile", and the power consumed by the rest of the pipeline, "FragProcsRest".

and thus become too hot to handle [44]. Mobile GPUs are thermally limited [120], since they could easily overheat their packages if the appropriate mechanisms to force them to slow down when they get too hot were not included. Therefore, saving energy is also an effective way of increasing performance on a mobile GPU. As an illustrative example of the importance of energy in mobile GPU design, the ARM Mali GPU requires 35% additional energy efficiency improvements every year to fit new performance requirements within SoC thermal limits [72].

Performance metrics employed for decades such as pixels per second (fill rate [152]) or the controversial triangles per second [121] have been displaced by other metrics that take into account energy. The most important metrics to optimize now are performance per watt [159] and/or nanojoules per pixel [45]. Energy-efficiency is also usually measured as the ratio between the speedup and the normalized energy [70].

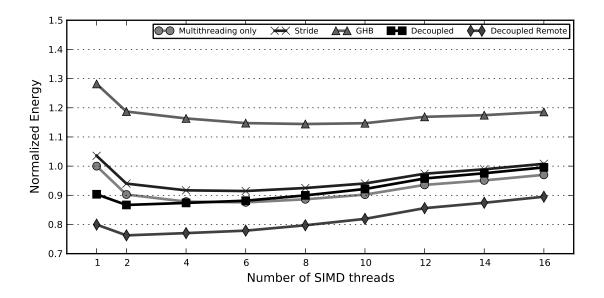

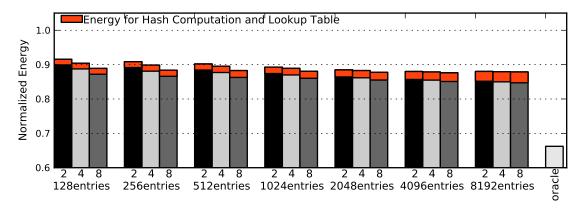

The first step in optimizing the energy-efficiency is identifying the main sources of energy consumption in a mobile GPU. Previous studies have found two major sources: the big Register File (RF) required to sustain a huge number of simultaneous threads and the external accesses to off-chip system memory. The numbers

obtained in our mobile GPU simulation infrastructure, described in Chapter 2, support the results of previous studies as illustrated in Figure 1.1b. The RF of the Fragment Processors consumes 25% of GPU power and 11.2% of overall power consumption. On the other hand, the external accesses to off-chip system memory consume 56% of the power of the graphics subsystem.

Regarding the big size of the RF, GPUs are massively parallel programmable processors designed to exploit the concurrency inherent in graphics workloads. Unlike CPUs that generally target single-threaded performance, GPUs aim for high throughput by employing extreme multithreading [73]. Memory latency is hidden by maintaining a huge number of parallel threads, so in case of a cache miss the scheduler switches to another hardware thread to avoid pipeline stalls. Modern desktop GPUs can have thousands of hardware threads. For example, the NVIDIA Fermi architecture supports over 20000 thread contexts [68]. Just holding the registers of these threads requires substantial on-chip storage: a RF of around 2 MBytes that consumes more than 9 Watts [79]. Such a big RF is absolutely prohibitive for a mobile GPU, that usually has at its disposal a small power budget of around 1 Watt [120]. Indeed, mobile GPUs reduce the degree of parallelism to tenths or a few hundreds of threads [23]. The memory latency cannot be completely tolerated as the number of parallel threads is scaled down, introducing pipeline stalls that degrade performance. In short, although multithreading is a very effective technique for hiding the memory latency, we believe that more energy-efficient mechanisms are necessary to meet the energy requirements of mobile GPUs.

Besides the aforementioned issues with the RF, the general agreement in both industry and academia is that the main sources of energy drain in a mobile GPU are the expensive off-chip accesses to system memory [44, 47, 119, 120]. External memory accesses are often the operation that uses the most energy in a computer system [76]. An off-chip memory access consumes more than an order of magnitude more energy than an access to on-chip SRAM in lowpower processes. This means that memory bandwidth have to be used with great care in a mobile GPU. Furthermore, this also means that optimizing memory bandwidth usage is an effective way of reducing energy consumption. Multiple bandwidth saving techniques have been proposed in recent years such as texture compression [119, 140] or framebuffer compression [8, 128], Section 1.3.2 provides a review of the state-of-the-art in memory bandwidth usage optimization for lowpower GPUs. Most of these schemes are adaptations of techniques previously proposed for desktop GPUs, we believe that bigger bandwidth savings can be achieved by taking into account the specific characteristics of mobile graphics workloads.

In short, the demand for high quality rendering and the requirement of low energy consumption are contradictory. Developing more energy-efficient memory latency tolerance schemes and optimizing memory bandwidth usage are among the most promising ways to ameliorate this conflict. In following sections we will review the solutions proposed in recent years, and later in this chapter we will introduce our proposals to close the energy gap in embedded graphics processors.

# 1.3 State-of-the-art in GPU Energy Efficiency

Improving the energy-efficiency of mobile GPUs has attracted a lot of attention from the architecture community in recent years. As stated in prior section, reducing the energy consumption of the RF is one of the primary concerns regarding mobile GPU design, previous studies have focused on saving RF energy as described in Section 1.3.1. On the other hand, saving memory bandwidth has been proven to be an effective way of reducing energy consumption and, hence, multiple techniques targeting memory bandwidth usage optimization have been proposed as depicted in Section 1.3.2.

### 1.3.1 Memory Latency Tolerance Techniques

Graphics workloads have a large amount of inherent parallelism that can be easily exploited by a parallel machine. Texture memory accesses are common operations in graphics workloads and tend to be fine-grained and difficult to prefetch [79]. Graphics workloads have large, long-term (inter-frame) working sets that are not amenable to caching. Therefore, texture cache units focus on conserving bandwidth rather than reducing latency [73]. Because texture accesses are macroscopically unpredictable, and frequent, GPUs rely on massive multithreading to keep arithmetic units utilized. As a result, a huge RF is required to maintain the registers of all the simultaneous threads.

In this section we will first review previous work focused on optimizing the energy consumption of the GPU RF. Second, we will discuss other research work based on the use of prefetching to hide the memory latency, with the objective of reducing the multithreading degree requirements and, hence, the size and the energy consumption of the RF. Finally, we will review related work on Decoupled Access/Execute architectures.

#### Register File Optimizations

Gebhart et al. [79] propose the use of a Register File Cache to replace accesses to the large main RF with accesses to a smaller structure containing the immediate register working set of active threads. As extreme multithreading requires a complicated thread scheduler, the authors also propose a two-level thread scheduler that maintains a small set of active threads to hide ALU and local memory accesses, and a larger set of pending threads to hide main memory latency. Combined with the RF Cache, this two-level thread scheduler provides a further reduction in energy by limiting the allocation of temporary register cache resources to only the currently active subset of threads. The authors report significant energy savings in both graphics and GPGPU workloads. Note that this approach saves dynamic energy by replacing accesses to a bigger hardware structure by accesses to a smaller structure, but it does not save static energy as the original big RF is kept as in conventional GPUs.

Yu et al. [169] introduce a hybrid memory design that tightly integrates embedded DRAM into SRAM cells to reduce area and energy consumption of a multi-threaded RF. In this memory, each SRAM cell is augmented with multiple DRAM cells so that multiple bits can be stored in each cell. This approach saves both dynamic energy and leakage by keeping data for active threads in SRAM while placing data for pending threads in DRAM. However, such a RF requires explicit data movements between SRAM and DRAM in order to access the registers of pending threads. The thread scheduler has to be modified in order to minimize context switching impact.

Regarding proposals that specifically target mobile GPUs, Sohn et al. [167] propose a mechanism for clock gating an entire RF bank when it is not being accessed. Chu et al. [63] introduce the possibility of further reducing dynamic energy by dividing the register bank into multiple regions and controlling clock gating individually. In a later study, Chu et al [89] extended their work proposing an Adaptive Thread Scheduling mechanism combined with a low-power RF with hybrid power gating [103]. Besides dynamic energy savings, this RF exploits both  $gated-V_{dd}$  and drowsy techniques [75] to achieve long and short term leakage energy savings. Finally, a compiler-assisted demand-driven RF for mobile GPUs is presented in [90]. In this scheme the RF is shared on demand between concurrent threads, and multiple power gating modes are employed to avoid wasting static energy for unused registers.

#### Prefetching

Besides multithreading, prefetching data into the caches can also help tolerate memory latency. The largest concerns with any prefetching scheme are accuracy and timeliness. Regarding accuracy, if an application's memory stream is irregular or unpredictable cache pollution can occur and increase the number of cache accesses and, hence, energy consumption. Regarding timeliness, prefetch requests have to be issued at the appropriate time in order to be effective. Otherwise data could be prefetched too early and evicted before accessed from the application, or prefetched too late so the memory latency cannot be completely tolerated. Note that prefetching can only provide memory latency tolerance, whereas multithreading can hide both memory and functional units latency.

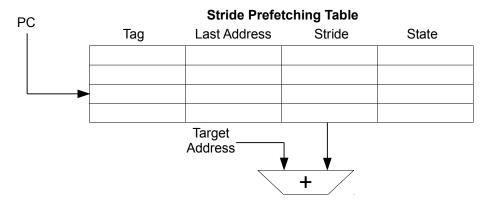

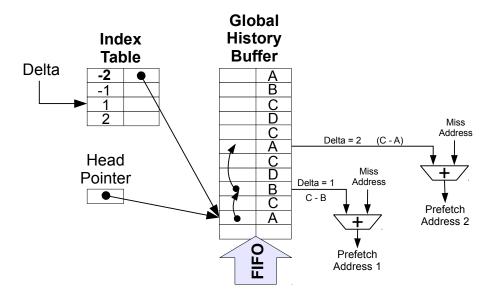

Several hardware-based data prefetching schemes for CPUs have been proposed in past decades. The next-line [58] and the stride [77] prefetchers are commonly implemented in desktop CPUs as they perform well for typical CPU work-loads and they require simple hardware. More sophisticated prefetching schemes try to correlate recent miss addresses, such as the Markov prefetcher [100], whereas other prefetchers try to correlate recent strides, like the distance prefetcher [102]. On the other hand, Nesbit et al. [114] show that the history information employed by the previous prefetchers, that is typically stored in a table, can be kept more efficiently in a new hardware structure called the Global History Buffer.

Classical CPU prefetching results in higher performance, but worse energy in some cases due to unnecessary data being fetched on chip. With the advent of General Purpose computing on GPUs (GPGPU), several authors have proposed to use prefetching in GPUs with the main objective of saving energy. Sethia et al. [135] proposed APOGEE, a prefetching mechanism able to dynamically detect and adapt to the memory access patterns found in scientific codes that are run on modern GPUs. APOGEE employs multi-thread miss address stream analysis, instead of considering threads in isolation, to improve accuracy and timeliness in highly threaded processors. The net effect is that fewer threads are required to tolerate memory latency and thus sustain performance. Hence, APOGEE saves energy by removing part of the thread contexts in the big and complex RF of a GPU, and including instead the smaller and simpler prefetch tables.

Lee et al. [106] also proposed the use of hardware prefetching for GPGPU applications. They show that conventional CPU prefetchers cannot be straightforwardly applied to GPGPU systems. Instead, they propose a stride based prefetcher tailored to many-core architectures. This prefetcher is based on interthread prefetching mechanisms and an adaptive throttling scheme to disable prefetching when it is useless, significantly improving accuracy and reducing energy waste.

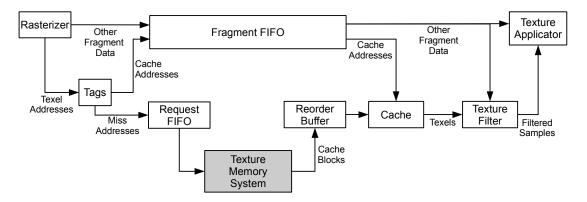

The prefetchers previously mentioned target general purpose applications running on CPUs or GPGPU systems. That is why they do not take into account the specific issues with graphics workloads and the ubiquitous and unpredictable texture fetches. Igehy et al. [93] proposed a prefetching architecture for texture caches that is designed to accelerate the process of applying textures on triangles. This texture prefetcher is thoroughly discussed in Chapter 3.

#### Decoupled Access/Execute

A Decoupled Access/Execute architecture [138] divides the program into two independent instruction streams, one doing memory accesses and the other performing computations. By decoupling memory accesses from computations, access/execute architectures effectively prefetch data from memory much in advance from the time it is required, thus allowing cache miss latency to overlap with useful computations without causing stalls. While this can be viewed as a form of data prefetching, it has a substantial advantage over other prefetching schemes, because it relies on computed rather than predicted addresses, which translates into a higher accuracy and a lower energy waste.

Despite the high potential of access/execute architectures to tolerate a long memory latency at a moderate hardware cost, they have not been widely adopted by current commercial CPUs because their effectiveness is greatly degraded when the computation of an address has a data or control dependence on the execution stream (this occurs, for instance, in pointer chasing codes). In such circumstances, termed loss of decoupling events (LOD), the access stream is forced to stall in order to synchronize with the execution stream. LODs force the access stream to lose its timeliness (i.e. the prefetch distance), so that subsequent cache misses will cause the execution stream to stall as well. Unfortunately, for general purpose

CPUs the frequency of LODs is quite significant in many cases, resulting in fairly restricted performance gains.

Crago et al. [71, 70] propose the use of Decoupled Access/Execute architectures to hide the memory latency in highly threaded workloads. Their scheme is different from classical access/execute architectures as they run the multiple instruction streams in just one core by using multiple thread contexts, instead of having two separate processors for memory accesses and computations. Furthermore, they propose several strategies to mitigate the effect of LODs in multithreaded applications. Overall, they show that decoupled access/execute is an effective energy saving technique in many-core architectures as it requires simple hardware and, in addition, the number of thread contexts required to keep the functional units busy can be significantly reduced. It is worth noting that similar conclusions about the synergy of decoupling and multithreading were already suggested in [122].

Talla et al. [141, 142] describe the benefits of Decoupled Access/Execute for multimedia applications. They introduce the *MediaBreeze* architecture, a system that decouples the useful/true computations from the overhead/supporting instructions that are necessary to feed the SIMD execution units. The *Media-Brezze* architecture includes hardware for efficient address generation, looping and data reorganization. The proposal was evaluated on top of an out-of-order CPU with SIMD extensions and the authors reported significant performance improvements in media applications.

### 1.3.2 Bandwidth Saving Techniques

The rendering of 3D computer graphics requires the GPU to fetch big datasets from main memory on a frame basis. Retrieving these massive amounts of data is one of the main sources of energy consumption on a mobile GPU and thus optimizing memory bandwidth usage is a primary concern in embedded graphics processors. In this section we will review previous techniques to reduce the number of external memory accesses to the texture datasets and to the framebuffers.

#### Tile-Based Rendering

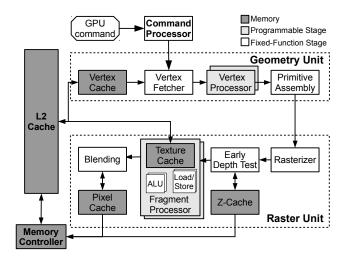

Desktop GPUs implement an Immediate-Mode Rendering (IMR) architecture [113]. In IMR, the geometry that describes an object is transformed in the vertex processors and immediately sent down the graphics pipeline for further pixel processing, updating the framebuffer before processing the next object. If a subsequent object is rendered on top of a previous one, the colors of the pixels are computed again and overwritten in the framebuffer. This issue is commonly known as the overdraw problem [56]: the colors of some pixels are computed and written multiple times into main memory due to multiple graphical objects being drawn over the top of one another, resulting in a waste of bandwidth. The average number of times a pixel is written in a single frame is often referred as the depth complexity [69].

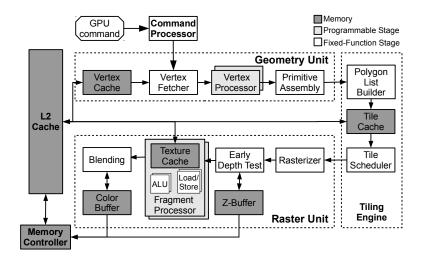

Tile-Based Rendering (TBR) architectures [44] are designed to address the overdraw. In TBR the screen is split into rectangular blocks of pixels called tiles, and the frames are generated tile by tile. Tiles are small enough so the portion of the framebuffer corresponding to a tile can be stored in local on-chip memory, avoiding off-chip accesses to a large extent. Unlike IMR architectures, transformed 2D triangles are not immediately rendered in the framebuffer, instead they are stored into main memory in the Scene buffer [51]. Furthermore, 2D triangles are sorted into tiles, so for each tile a triangle overlaps a pointer to that triangle is stored. Once all the geometry for a given frame has been transformed and sorted, the rendering starts tile by tile. Note that pixels are written just once in main memory, as the tiles are generated first in the local on-chip memory and copied to the corresponding region of the framebuffer only when they are ready, i. e. when all the triangles for the given tile have been rendered. TBR provides significant bandwidth savings for generating the framebuffer, however, it requires the 2D triangles to be stored in memory and fetched back for rendering, so it trades geometry bandwidth for pixel bandwidth. Antochi et al [52] report significant bandwidth savings in low-power systems by using TBR. Although IMR dominates the desktop GPU segment, TBR is more popular in the mobile segment [9, 161, 162] as the geometry datasets of mobile workloads are smaller and, hence, the extra cost of storing/fetching 2D geometry is usually less than the bandwidth savings in the framebuffers.

#### Compression

Compression techniques can reduce both the memory footprint and the bandwidth requirements of graphical workloads. In first place, hardware texture compression was introduced by Knittel et al. [105] and Beers et al. [60]. The core idea is to use lossy compression on the textures, and store the compressed version in system memory. When accessing the texture during rendering, the compressed texture is transferred over the bus, and decompressed on-the-fly as needed, thus saving bandwidth.

Ström et al [140] propose *iPackman*, a texture compression scheme that targets mobile devices. *iPackman* has low-complexity, being amenable for hardware implementation on embedded graphics processors. Furthermore, it achieves high image fidelity and compression ratios of 4 bits per pixel (bpp). The OpenGL ES 3.0 API introduces support for texture compression by using the Ericsson Texture Compression [151] (ETC2/EAC version) algorithm, which is based on *iPackman*.

On the other hand, the major mobile GPU manufacturers provide their vendor-specific texture compression methods. ARM Mali supports the Adaptive Scalable Texture Compression (ASTC) [119], a lossy compression algorithm that provides a high degree of flexibility to trade image quality for bandwidth savings. ASTC achieves bit rates ranging from 8 bpp to less than 1 bpp in very fine steps. Qual-comm Adreno also supports texture compression by using the ATC [1] algorithm, whereas Imagination PowerVR leverages PVRTC [74] and NVIDIA Tegra provides support for DXT compression [109, 123].

Besides texture compression, framebuffer compression can also provide significant bandwidth savings. The framebuffer consists of a set of 2D buffers required for rendering such as the color buffer, that stores a RGBA color for each pixel in the screen, or the depth buffer, that keeps a depth value for each pixel in order to solve visibility. Framebuffer compression works in a similar way than texture compression does, storing the buffers compressed in main memory, transferring the data compressed over the bus, decompressing on-the-fly when reading and compressing on-the-fly when writing to the framebuffer. Note that the color buffer has to be uncompressed in order to be displayed on the screen, in case of using framebuffer compression the display controller has to include the corresponding color buffer decompression hardware.

Regarding IMR GPU architectures, Rasmusson et al. [128] propose both loss-less and lossy compression algorithms for the color buffer. Hasselgren et al. [86] introduce a depth buffer compression algorithm to save bandwidth in the depth test. Regarding TBR architectures, ARM Frame Buffer Compression (AFBC) introduces the compression of the tiles before being transferred from local on-chip memory to system memory, achieving compression ratios of 50% with a lossless algorithm. As for the depth buffer, Tile-Based architectures do not usually require to save and restore the depth values of the tiles. In OpenGL ES 2.0 the driver can infer in some cases that the contents of the depth buffer does not need to be preserved from frame to frame, whereas OpenGL ES 3.0 introduces the glInvalidateFramebuffer [80] function call to explicitly indicate to the driver that the depth buffer is not required to be saved/restored. Hence, TBR architectures can completely avoid all the transfers to the external depth buffer in main memory.

#### Transaction Elimination

Transaction Elimination [57, 120] (TE) is a bandwidth saving technique for Tile-Based GPU architectures introduced by ARM and implemented in the Mali GPUs. With TE, the graphics hardware compares the current framebuffer with the previously rendered frame and performs a partial update only to the particular parts of it that have been modified, thus significantly reducing the amount of data transferred per frame to external memory. The comparison is done on a per tile basis, using a Cyclic Redundancy Check signature to determine if the tile has been modified. Tiles with the same signature are identical and eliminating them has no impact in the resulting image quality. TE is highly effective for popular graphical applications such as User Interfaces or casual games, since they usually feature static 2D backgrounds and there are not many changes from frame to frame. However, it is also effective for other graphical applications like 3D games or video.

#### Multi-View and Multi-Frame Rendering

Stereoscopic and 3D displays require the generation of multiple views or images for every single frame. Hasselgren et al. [87] propose a novel rasterization architecture

that renders each triangle to multiple views simultaneously, with the objective of maximizing the hit rate in the texture caches and thus saving memory bandwidth. When determining which view to rasterize next, the architecture employs an efficiency metric that estimates which view is expected to get the most hits in the texture cache. As the different views of the same frame are very similar, a better utilization of the texture caches is achieved by generating the multiple images in parallel instead of rendering the views sequentially. Instead of processing all the triangles for a given view and then proceed to the next one, the proposed architecture iterates all the views for each triangle to maximize texture locality.

NVIDIA Scalable Link Interface (SLI) [118] is a multi-GPU configuration that offers increased rendering performance by dividing the workload across multiple GPUs. The most common SLI configuration is known as Alternate Frame Rendering (AFR). Under AFR the driver divides the workload by alternating GPUs every frame. For example, on a system with two SLI-enabled GPUs, odd frames would be rendered by GPU 1 whereas even frames would be rendered by GPU 2. The main target of AFR is to increase graphics performance by duplicating hardware resources and increasing memory bandwidth, so power consumption is also significantly increased. However, it is possible to save bandwidth and energy in a multi-GPU system if the multiple graphics processors share a single memory address space as suggested in [112], in that case part of the dataset employed for rendering can be shared by the different GPUs.

#### 1.3.3 Other Related Works

Mochocki et al [111] propose the use of Dynamic Voltage and Frequency Scaling (DVFS) in mobile 3D graphics pipelines. Want et al. [147, 148] describe different power gating strategies for graphics processors. Chu et al [61, 62, 88] propose dynamic precision selection in the GPU shader cores, switching at runtime between fixed-point arithmetic —faster and more energy-efficient— and floating-point arithmetic —better graphics quality.

As described in previous sections, the overdraw [56] is one of the main issues in graphics processors as it results in a waste of bandwidth and energy. Hence, different hardware-based techniques that try to address the overdraw in mobile GPUs have been proposed. The ULP GeForce GPU in the NVIDIA Tegra SoC features Early-Z rejection [115] to preemptly discard fragments that are known to be occluded. When using Early-Z rejection, the depth test is performed before the execution of the fragment shader to avoid computing the colors of non-visible fragments. This scheme achieves maximum efficiency when the triangles are sent to the GPU ordered from front to back. On the contrary, worst case happens when triangles are sent ordered from back to front, as younger fragments always overlap older fragments and, hence, they always pass the depth test and proceed to the fragment shader.

Tile-Based architectures are designed to minimize the impact of the overdraw since pixels are written just once into off-chip system memory due to the use of local on-chip color buffers. However, the colors of some pixels are still computed and written multiple times in the local on-chip memory. Ideally, the fragment shader should be executed just once for each screen pixel on every frame to completely remove the overdraw <sup>1</sup>. Some mobile GPUs include techniques to remove re-executions of the fragment shader for the same screen pixel, in order to avoid spending time and energy in shading fragments that are not going to contribute to the final image. For example, ARM Mali GPUs implement Forward Pixel Kill (FPK) [21]. In an FPK-enabled GPU, the threads that shade fragments are not irrevocably committed to complete once they are launched. On the contrary, inflight threads can be terminated at any time if the hardware detects that a later thread will write opaque data to the same pixel location. On the other hand, Imagination Technologies PowerVR GPUs include hardware for Hidden Surface Removal (HSR) [28]. With HSR all the geometry for a tile is processed and the visibility is completely solved before shading any fragment. Once the closestto-the-observer fragment for each pixel in the tile has been found the fragment shader computations take place and, hence, each pixel is shaded just once.

#### 1.4 Thesis Overview and Contributions

The goal of this thesis is to propose novel and effective techniques that address the issues in mobile GPU design, with the objective of improving the energy-efficiency of embedded graphics processors while keeping complexity low. Our main contributions are a decoupled access/execute-like architecture for the Fragment Processors, a bandwidth saving technique called Parallel Frame Rendering and a hardware-based memoization scheme that avoids redundant computations and memory accesses. All these proposals apply to a conventional mobile GPU architecture, and can be implemented on top of both Immediate-Mode and Tile-Based GPUs. The following sections outline the problems we are trying to solve, describe the approach we take to solve the problem and provide a comparison with related work, highlighting the novel contributions of this thesis.

#### 1.4.1 Mobile GPU Simulation Infrastructure

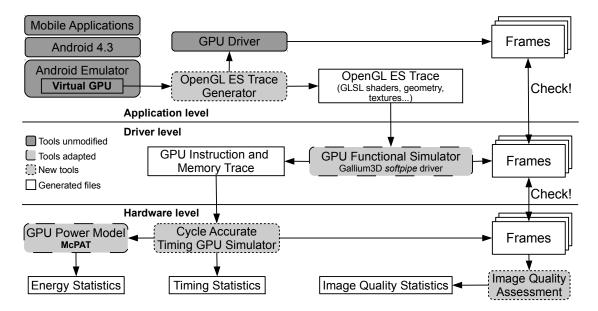

We have developed our custom mobile GPU simulation infrastructure, that we call TEAPOT. To the best of our knowledge, TEAPOT is the first simulator tailored towards the mobile segment, as none of the previous GPU simulators provide support for running Android graphical applications that employ the OpenGL ES API. TEAPOT consists on a set of tools for evaluating the performance, energy consumption and image quality of mobile graphics processors. Its main target is to drive the evaluation of energy saving techniques for mobile GPUs.

Regarding its features, TEAPOT provides full-system simulation of Android applications. Furthermore, it includes a GPU timing simulator able to model

<sup>&</sup>lt;sup>1</sup>In case transparent or translucent objects are included in the scene the optimum number of executions of the fragment shader can be greater than one per pixel

both Tile-Based and Immediate-Mode rendering architectures, a power model for mobile GPUs, and automatic image quality assessment by using several metrics. TEAPOT is extensively described in Chapter 2. This infrastructure was presented in a paper published in the proceedings of the 27th International Conference on Supercomputing:

• "TEAPOT: A Toolset for Evaluating Performance, Power and Image Quality on Mobile Graphics Systems".

Jose-Maria Arnau, Joan-Manuel Parcerisa and Polychronis Xekalakis.

International Conference on Supercomputing, 2013.

The development of tools for evaluating the GPU has attracted the attention of the architectural community the last few years. Recent simulators, such as GPGPUSim [59] or Barra [65], model General Purpose GPU (GPGPU) architectures. These tools support CUDA [116] or OpenCL [172], but they do not support graphics APIs such as OpenGL [97]. GPGPUSim includes a power model, GPUWattch [170], which is also based on McPAT as in TEAPOT. Both power models are similar, but GPUWattch focuses on GPGPU specific features whereas TEAPOT models more specialized graphics hardware. For instance, GPGPUSim models FP units that can be combined to execute 1 double-precision (DP) or 2 single-precision (SP) operations, but TEAPOT relies on SP units since DP is common in scientific workloads but not in games. On the contrary, TEAPOT models specialized Texture Sampling units since texture fetching instructions are frequent in graphical workloads.

ATTILA [113] provides an OpenGL framework for collecting traces of desktop games and a cycle-accurate GPU simulator. A Direct3D [171] driver is also included in the last versions. Although ATTILA provides full support for desktop games, it cannot run applications for smartphones. Furthermore, its GPU simulator models a desktop-like Immediate-Mode Renderer, whereas Tile-Based Rendering is much more popular in smartphones. Finally, ATTILA does not include a power model. Qsilver [136] can also collect traces from desktop OpenGL games and it models a desktop-like NVIDIA GPU, including a power model. GRAAL [101] also provides OpenGL support and a power model for GPUs. Furthermore, it models a low-power Tile-Based Rendering architecture. However, OpenGL ES support is not available in any of these simulators so they cannot run mobile applications for smartphones and tablets. Unlike the aforementioned tools, TEAPOT provides image quality metrics for automatic image quality assessment. In addition, TEAPOT supports full-system GPU simulation, being able to profile multiple applications accessing the GPU concurrently.

# 1.4.2 The Decoupled Access/Execute Fragment Processor

Extreme multithreading is the solution employed by desktop GPUs to hide the memory latency, as both graphical and GPGPU workloads exhibit a high degree of parallelism. However, aggressive multithreading requires a huge Register

File (RF) to keep the registers of all the parallel threads. Bound by severe energy constraints, mobile GPUs cannot accommodate such a big RF in their tiny power budgets. Hence, memory latency cannot be completely tolerated just by using multithreading due to the smaller number of parallel threads employed in embedded graphics processors.

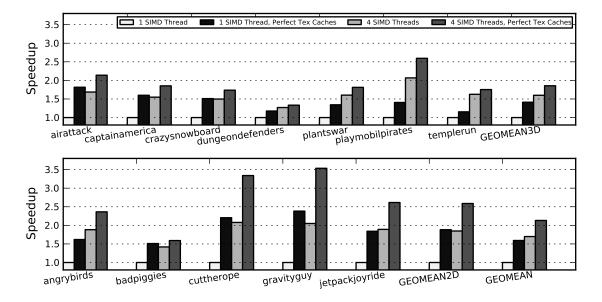

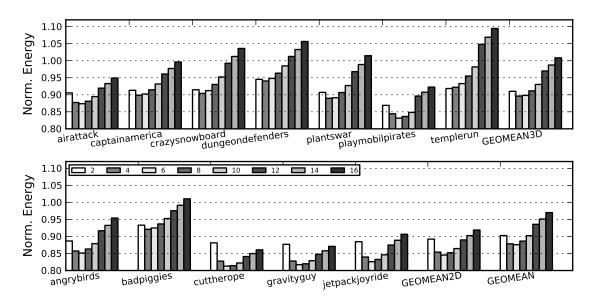

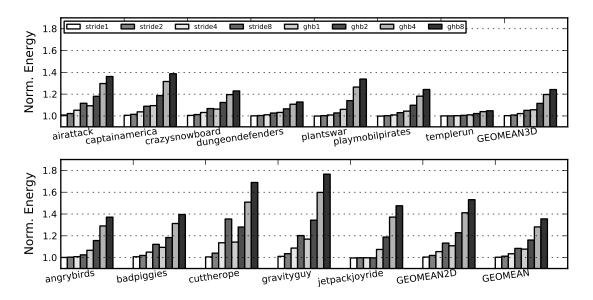

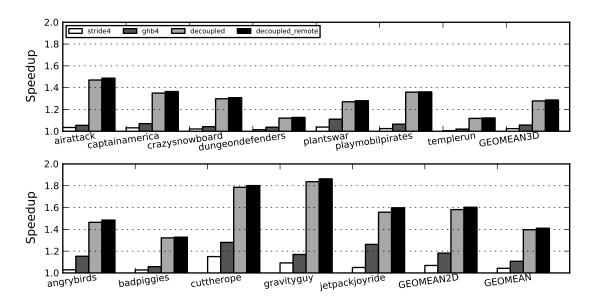

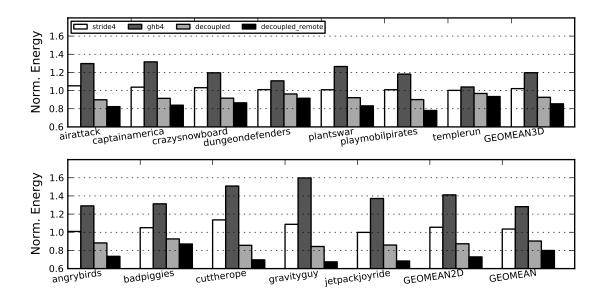

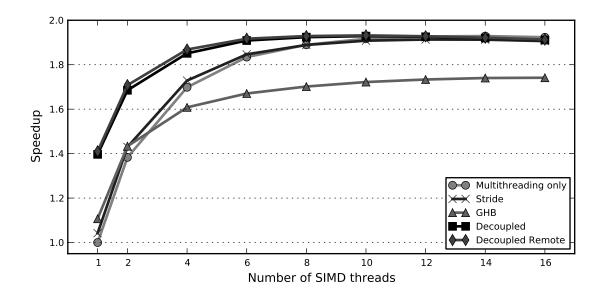

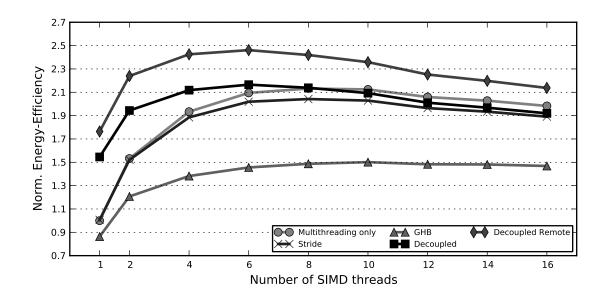

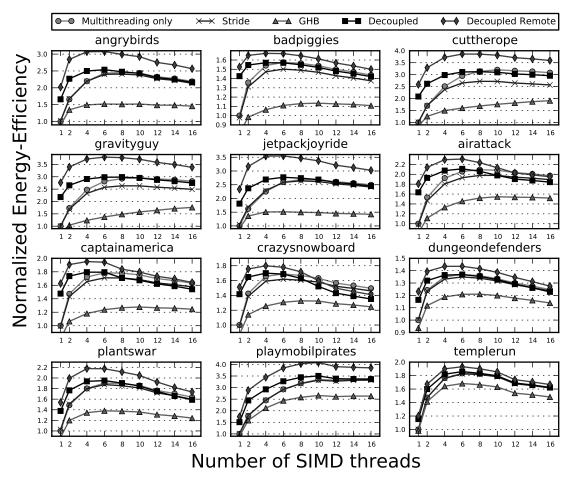

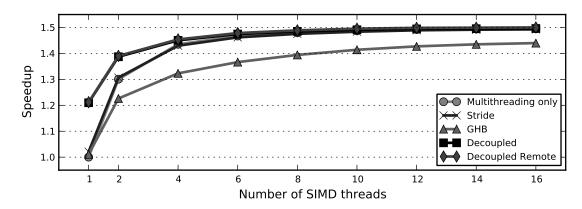

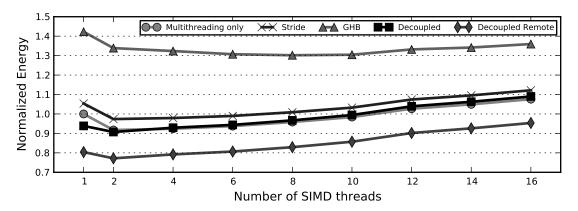

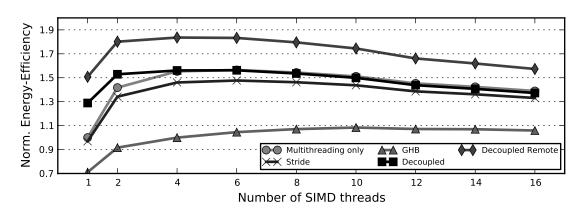

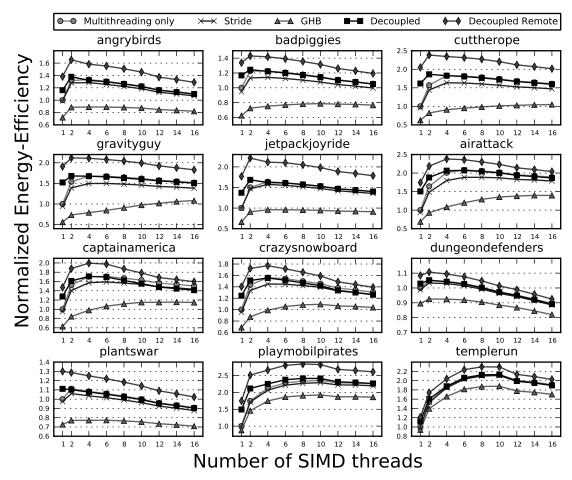

In first place we evaluate the effects of aggressive multithreading in a mobile GPU, analyzing its impact on performance and energy consumption. As the results show that multithreading is effective but not energy-efficient, due to the big size of the RF, we try to reduce the number of hardware threads by combining multithreading with other memory latency tolerance techniques such as prefetching. We evaluate several state-of-the-art CPU, GPU and GPGPU hardware prefetchers on a mobile GPU running graphics workloads. The results obtained in our cycle-accurate timing simulator indicate that these prefetchers obtain non-negligible performance improvements, but they perform far from ideal as texture accesses are highly unpredictable.

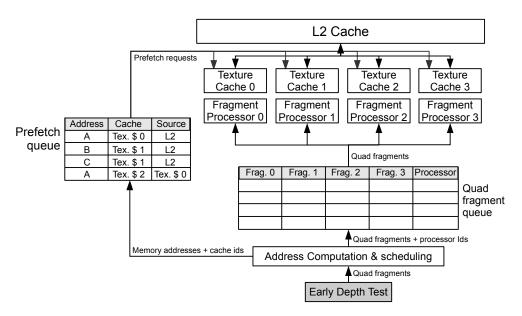

In second place, we propose a decoupled access/execute-like architecture for the fragment processors of a mobile GPU. For GPU fragment programs the memory access patterns are typically free of the dependences that cause Loss of Decoupling (LOD) events. This makes the access/execute paradigm a perfect fit for the requirements of a low-power high-performance GPU: with few extra hardware requirements it can reduce drastically the number of cache miss stalls. In our scheme, all the necessary data for processing the fragments is prefetched into the caches while the fragments are waiting to be dispatched to the GPU cores. By the time a fragment is issued all the data required to process the fragment is hopefully available in the caches, significantly improving the hit rates in the shader cores.

In third place, we improve our base system by introducing remote L1 cache accesses to exploit the high degree of data sharing among fragment processors. When the system detects that a cache line that is going to be prefetched in the L1 cache of a fragment processor has been recently prefetched in another L1 cache, the memory request is redirected to this cache instead of accessing the bigger L2 cache. This optimization saves bandwidth to the L2 cache and saves additional energy by replacing accesses to the bigger L2 cache by accesses to the smaller L1 caches. The end design is able to achieve similar performance to a heavily-threaded GPU by consuming only a fraction of its energy. More specifically, we evaluate our scheme on top of a state-of-the-art mobile GPU by using several commercial Android games, and show that the end design is able to achieve 97% of the performance of a massively multithreaded GPU, while providing 20.5% energy savings. This work has been published in the proceedings of the 39th International Symposium on Computer Architecture (ISCA):

• "Boosting Mobile GPU Performance with a Decoupled Access/Execute Fragment Processor".

Lose Mario Armay, Lose Manuel Perception and Polyschronic Veltalekie.

Jose-Maria Arnau, Joan-Manuel Parcerisa and Polychronis Xekalakis. International Symposium on Computer Architecture, 2012.

Unlike most of the prefetching schemes described in section 1.3.1, our work is focused on graphics workloads instead of general purpose applications. Furthermore, our scheme employs computed addresses rather than predicted addresses to significantly improve accuracy, as in graphics workloads the memory access patterns are typically free of dependences. The work that is closest to ours is the prefetching architecture for texture caches proposed by Igehy et al. [93]. However, our work is different in several ways. First, our system is built on top of a modern mobile GPU pipeline instead of a fixed-function pipeline, so our scheme supports multicore GPUs, programmable shaders and multiple texture fetches per fragment. Second, we take advantage of the Early-Z Test to only prefetch data for visible fragments, increasing the energy efficiency. Third, our proposal allows for remote L1 requests to exploit the high degree of data sharing among fragment processors, providing significant energy benefits.

The efforts to reduce register file power on a GPU include the register file cache and the two-level warp scheduler proposed by Gebhart et al. [79], and the hybrid SRAM-DRAM memory design presented by Yu et al. [169]. We show that there is no real necessity for high degree of multithreading and as such for large register files, as multithreading can be combined with other techniques to hide the memory latency in a more energy-efficient way. On the other hand, the abovementioned research is focused on GPGPU workloads, whereas our study targets graphical applications. General purpose codes employ complex addressing modes that can cause loss of decoupling events, reducing the effectiveness of decoupled access/execute architectures. However we believe that mobile phones are not the ideal platform for scientific applications, so our research is focused on more typical workloads for smartphones, such as games.

Recently, research in the field of mobile GPUs has emerged. Akenine-Moller and Strom [47] propose a rasterization architecture for mobile devices that employs a novel texture compression system to reduce memory bandwidth usage by 53%. Our work is also focused on reducing bandwidth, but we achieve bandwidth savings by exploiting inter-core data sharing.

Tarjan et al. [143] propose the sharing tracker, a simplified directory employed to capture inter-core reusage among the private non-coherent caches of a GPU. Our decoupled system is also able to exploit data sharing, but at a smaller energy cost by using a much smaller hardware structure, the prefetch queue. On the other hand, several tiled-cache approaches have been proposed. Reactive NUCA [85] introduces fixed-center clusters and rotational interleaving on a distributed shared L2 cache, these novel mechanisms provide high aggregate capacity while exploiting fast nearest-neighbour communication. NoC-aware cache design [43] introduces a first-touch data placement policy, a migration policy that moves each block to its most frequent sharer and a replacement policy that is biased towards retaining shared blocks and replacing private ones. DAPSCO [78] consists on a distance-aware cache organization that minimizes the average distance travelled by cache requests. In our system the L2 cache is centralized instead of distributed, since the number of cores in a mobile GPU is much smaller than what is assumed in a many-core system due to power constraints. Furthermore, the tiled-cached

systems use the hardware coherence mechanisms (directory) to detect data sharing among the first level caches, whereas we employ the prefetch queue to detect data reusage among non-coherent L1 caches at a much smaller energy budget (hardware coherent caches are considered too expensive for GPUs [143]).

Crago et al. [71] present OUTRIDER, a decoupled system for throughputoriented processors. OUTRIDER is similar to our proposal since it also employs a decoupled access/execute architecture to hide the memory latency with fewer threads. However, our system reduces hardware complexity, does not require compiler assistance to generate the instruction streams and it is able to detect inter-core data sharing. On the other hand, OUTRIDER offers better tolerance to LODs by using multiple memory access streams, so it is best suited for scientific applications whereas our system is best suited for graphical workloads.

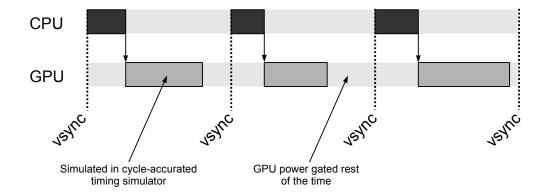

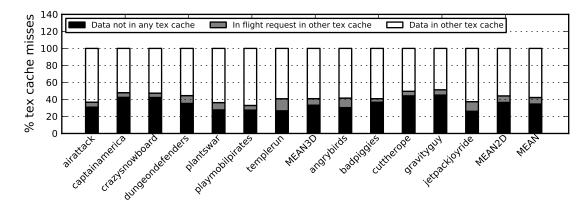

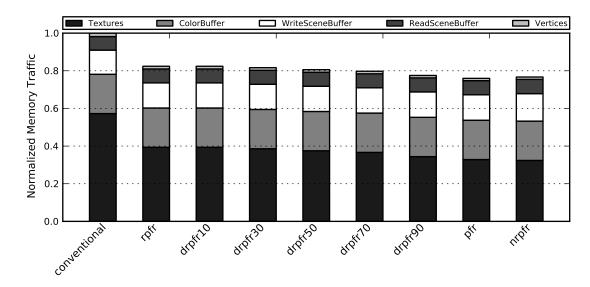

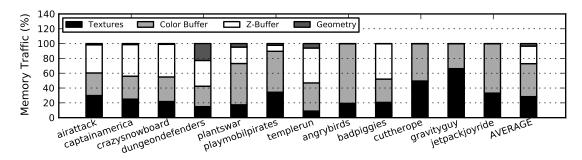

### 1.4.3 Parallel Frame Rendering

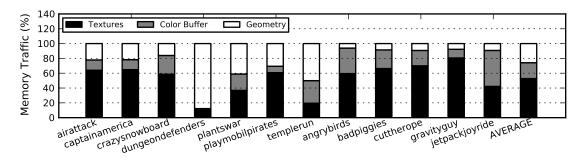

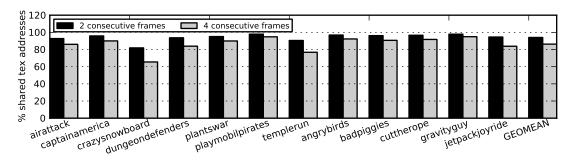

A large fraction of a mobile GPU energy consumption can be attributed to the external off-chip memory accesses to system RAM. As noted by [87, 119], most of these accesses fetch textures. Our numbers support this claim, as we found that 62% of the memory accesses can be directly attributed to texture data on average in our set of commercial Android workloads. Focusing on the texture dataset of consecutive frames, we realized that there exists a large degree of reuse across frames. Hence, the same textures are fetched frame after frame, but the GPU cannot exploit these frame-to-frame reuses due to the huge size of the texture dataset.

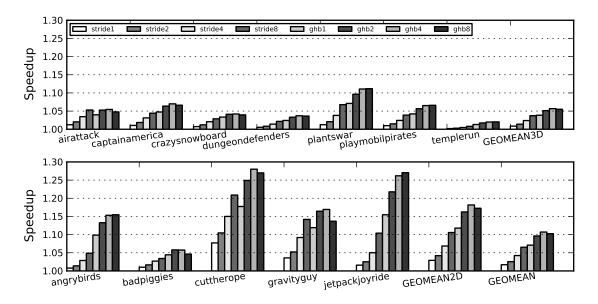

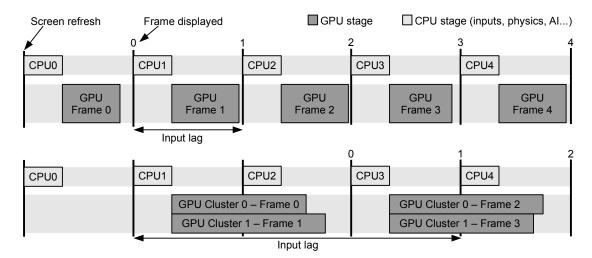

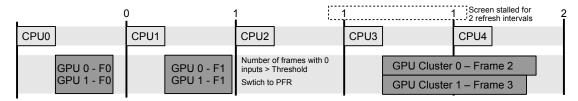

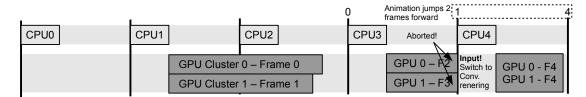

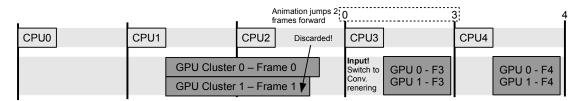

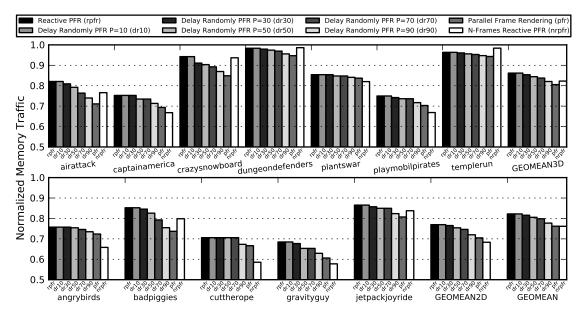

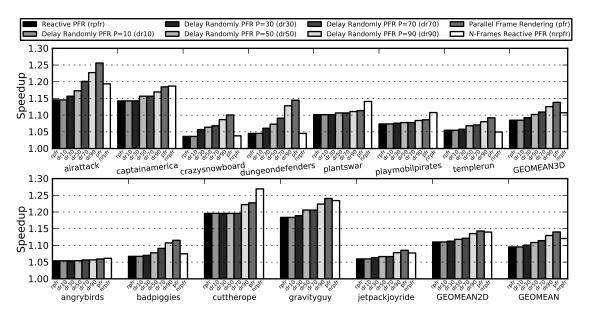

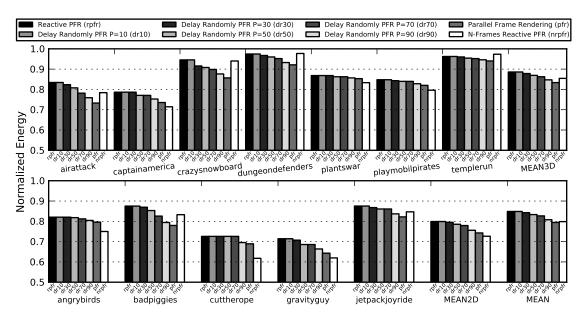

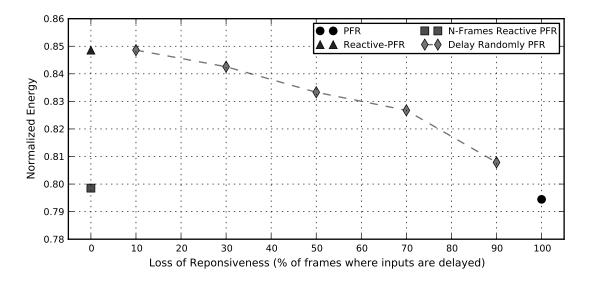

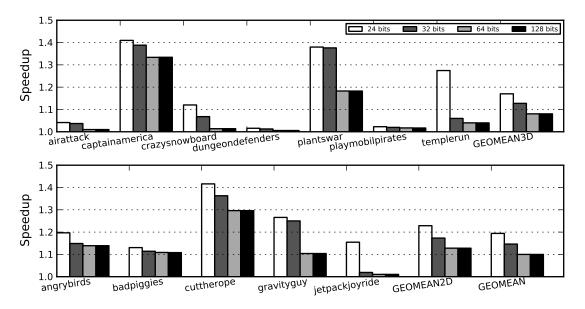

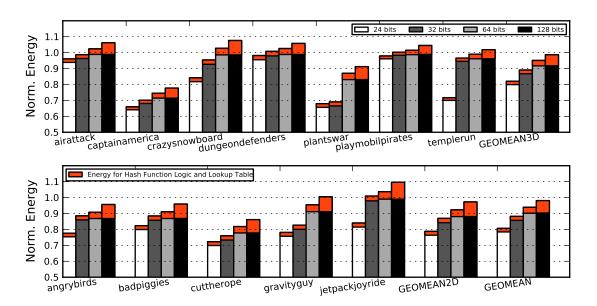

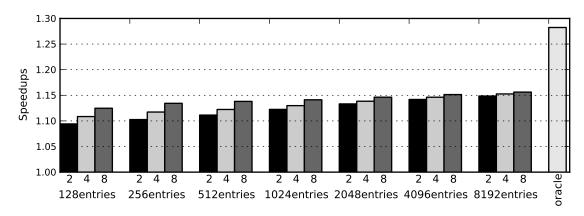

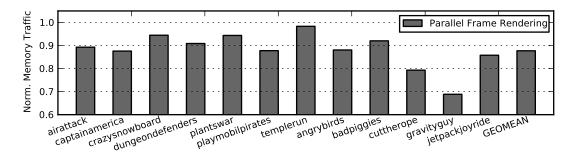

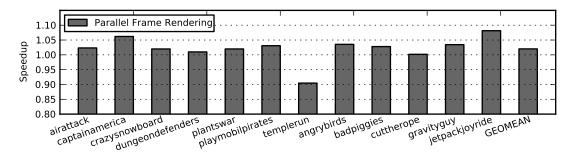

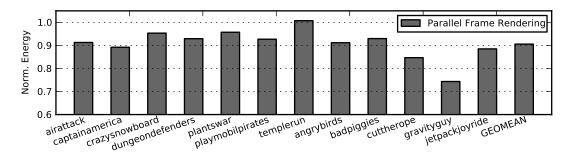

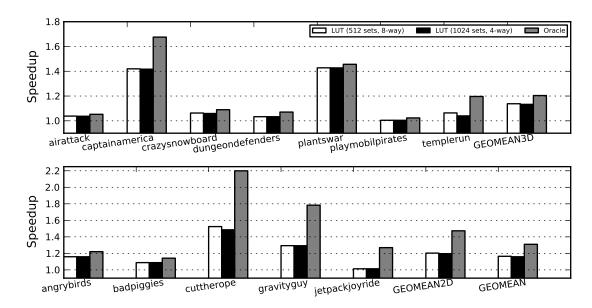

Firstly, we present Parallel Frame Rendering (PFR), a technique to improve texture locality on a mobile GPU. Under PFR, two consecutive frames are processed in parallel by devoting half of the graphics hardware resources to render each frame. By using this organization, each texture is read from memory once and used for rendering two successive frames. Therefore, textures are fetched from memory just once every two frames instead of being fetched on a frame basis as in conventional GPUs. The results show that PFR achieves 23.8% bandwidth savings on average for a set of Android games, providing 14% speedup and 20.5% energy savings.

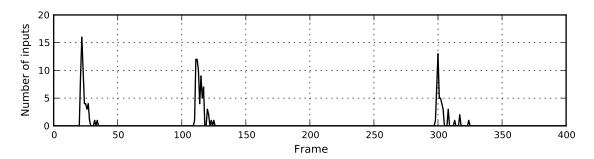

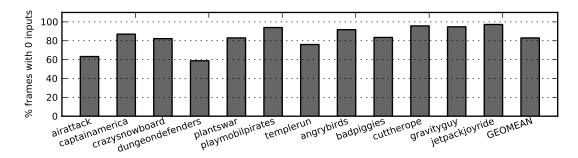

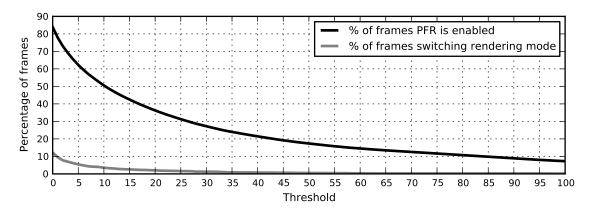

Secondly, we evaluate the effects of PFR in responsiveness. A valid concern for PFR is that since it devotes half of the resources to render each frame, the time required to render a frame is longer. This is an unfortunate side-effect as it ultimately leads to a less responsive system from the end-user's perspective. Nevertheless, we show that the increase in input lag is acceptable for many mobile applications. Furthermore, we propose a new version of PFR reactive to user inputs that is able to maintain the same levels of responsiveness than conventional mobile GPUs. The reactive versions of PFR monitor user inputs so two frames are processed in parallel just when the user is not interacting with the device, which accounts for most of the time, according to our user interaction analysis. As soon as the user provides inputs the system reverts to conventional rendering,

employing all the GPU resources to render just one frame in order to achieve high responsiveness. In addition, we also explore the possibility of rendering more than 2 frames in parallel. The reactive version of PFR achieves high responsiveness while it provides 23.8% bandwidth savings, achieving 12% speedup and 20.1% energy savings on average. This work has been published in the proceedings of the 22nd international conference on Parallel Architectures and Compilation Techniques (PACT):

• "Parallel Frame Rendering: Trading Responsiveness for Energy on a Mobile GPU".

Jose-Maria Arnau, Joan-Manuel Parcerisa and Polychronis Xekalakis. International Conference on Parallel Architectures and Compilation Techniques, 2013.

Although it might appear that PFR is similar in concept to the NVIDIA AFR paradigm [118] mentioned in Section 1.3.2, our approach clearly differs from the AFR, both in its goals and its methods: while AFR aims at increasing performance and frame rate by coordinating multiple independent GPUs with separate address spaces to maximize bandwidth, PFR pursues reducing energy by exploiting inter-frame temporal locality through splitting the computation resources of a single GPU with a shared last level cache and synchronizing memory accesses of consecutive frames. To the best of our knowledge, PFR is the first multi-frame rendering technique that targets energy savings instead of performance improvements.

On the other hand, Hasselgren et al. [87] propose a bandwidth saving technique for systems with stereoscopic displays. Since multiple views of the same frame have to be generated for a 3D display, the authors propose to compute the different views concurrently to improve texture cache hit ratio by using a novel rasterization architecture. Although the objective is the same than in our technique, i. e. saving memory bandwidth, the implementation is significantly different since PFR splits the graphics hardware in multiple clusters, but each cluster is still a conventional mobile GPU that implements a Tile-Based Rendering architecture. Furthermore, PFR is not limited to 3D displays and it achieves bandwidth savings on smartphones with 2D screens. Note that both techniques can be combined in stereoscopic systems: PFR can exploit inter-frame texture similarity by processing consecutive frames in parallel, whereas each GPU cluster can employ the technique described in [87] to maximize intra-frame texture locality.

Our approach is orthogonal to a wide range of memory bandwidth saving techniques for mobile GPUs, such as texture compression [140], texture caching [83], color buffer compression [128], Tile-Based Rendering [52] or depth buffer compression [86].

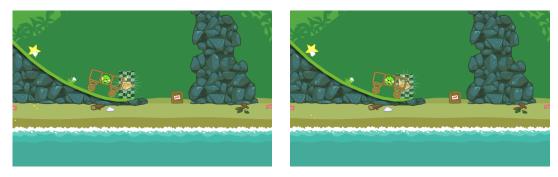

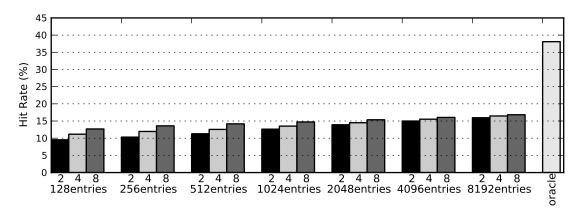

### 1.4.4 Eliminating Redundant Fragment Shader Executions

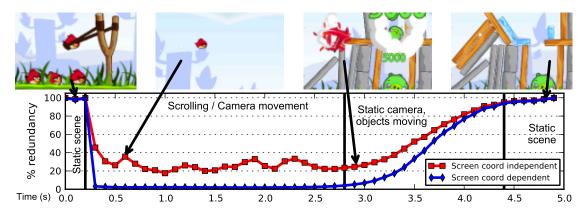

Graphical applications for mobile devices tend to exhibit a large degree of scene replication across frames. Our numbers show that, on average, more than 40% of the fragments computed in a given frame were previously computed in the frame before it. Recent work attempts to exploit this inter-frame locality in order to save memory bandwidth and improve overall energy efficiency, such as the ARM's Transaction Elimination [57]. Removing all these redundant computations and memory accesses would provide significant performance and energy improvements.

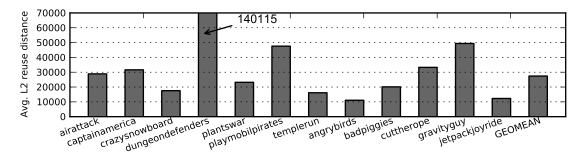

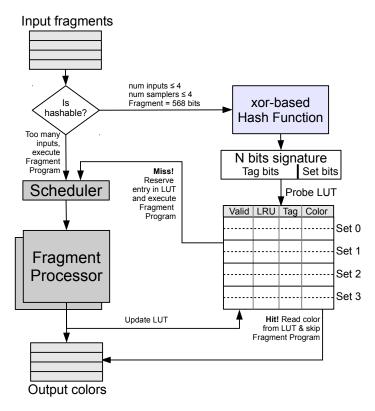

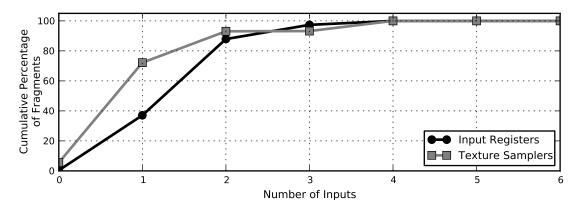

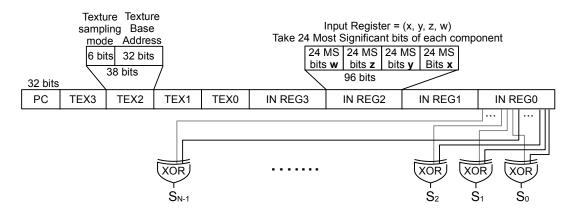

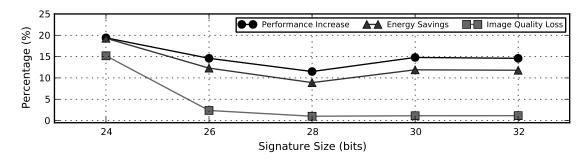

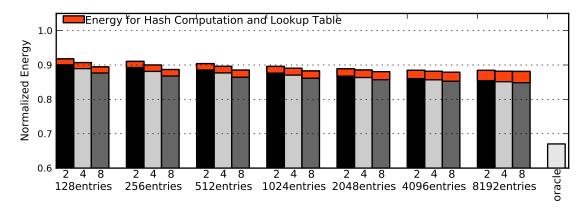

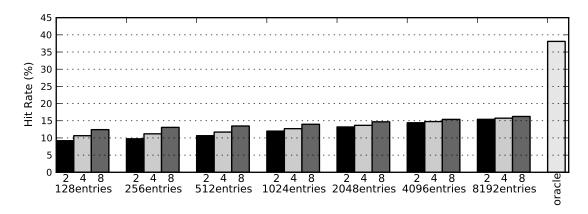

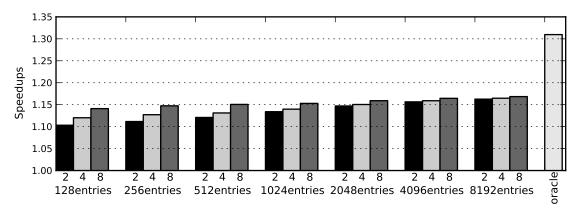

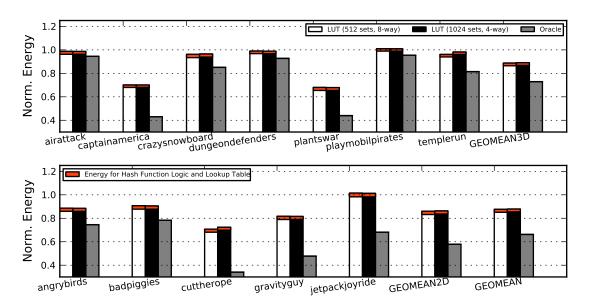

In first place, we provide a detailed analysis on the fragment redundancy that exists across frames. We analyze the locality and the complexity of redundant fragments, and conclude that a significant percentage of the redundant fragment shader executions could be avoided by using a simple memoization scheme.

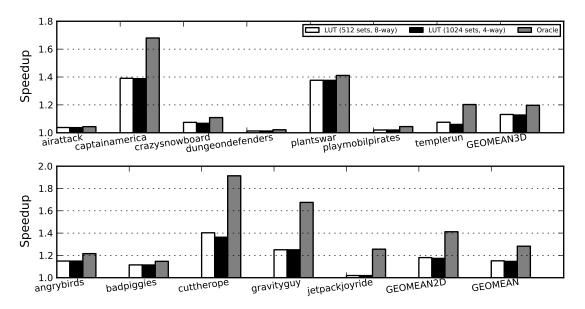

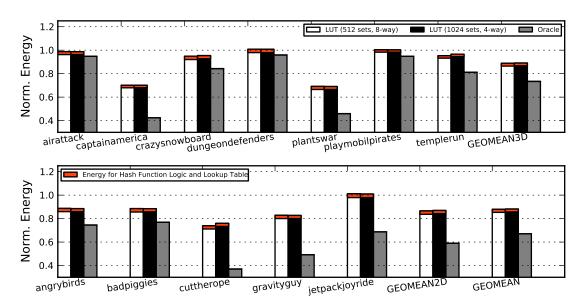

In second place, we propose a task-level hardware-based memoization scheme that, when architected on top of Parallel Frame Rendering, is able to improve energy-efficiency by 12%, while providing 15% speedup on average. Our memoization scheme keeps a hardware structure that computes the signature of all the inputs to a task and caches the value of the corresponding fragments. Subsequent computations form the signature and check against the signatures of the memoized fragments. Hits in the hardware structure result in the removal of all the relevant fragment computations and the corresponding memory accesses.