# Efficient multiprocessing architectures for Spiking Neural Network emulation based on configurable devices

Tesi doctoral presentada per a l'obtenció del títol de Doctor per la Universitat Politècnica de Catalunya, dins el Programa de Doctorat en Enginyeria Electrònica

Giovanny Sánchez Rivera

Director: Jordi Madrenas Boadas

## **Abstract**

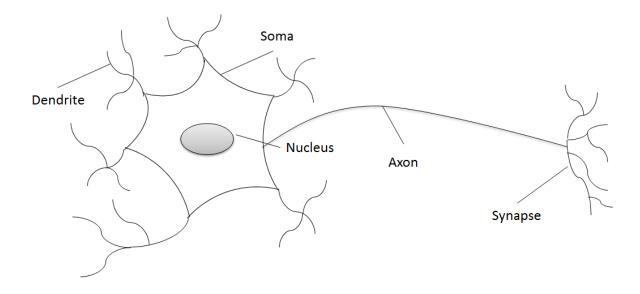

The exploration of the dynamics of bio-inspired neural networks has allowed neuroscientists to understand some clues and structures of the brain. Electronic neural network implementations are useful tools for this exploration. However, appropriate architectures are necessary due to the extremely high complexity of those networks. There has been an extraordinary development in reconfigurable computing devices within a short period of time especially in their resource availability, speed, and reconfigurability (FPGAs), which makes these devices suitable to emulate those networks.

Reconfigurable parallel hardware architecture is proposed in this thesis in order to emulate in real time complex and biologically realistic spiking neural networks (SNNs). Some relevant SNN models and their hardware approaches have been studied, and analyzed in order to create an architecture that supports the implementation of these SNN models efficiently. The key factors, which involve flexibility in algorithm programmability, high performance processing, low area and power consumption, have been taken into account. In order to boost the performance of the proposed architecture, several techniques have been developed: time to space mapping, neural virtualization, flexible synapse-neuron mapping, and specific learning and execution modes, among others.

Besides this, an interface unit has been developed in order to build a bio-inspired system, which can process sensory information from the environment. The spiking-neuron-based system combines analog and digital multi-processor implementations. Several applications have been developed as a proof-of-concept in order to show the capabilities of the proposed architecture for processing this type of information.

## Resumen

El estudio de la dinámica de las redes neuronales bio-inspiradas ha permitido a los neurocientíficos entender algunos procesos y estructuras del cerebro. Las implementaciones electrónicas de estas redes neuronales son herramientas útiles para llevar a cabo este tipo de estudio. Sin embargo, ls alta complejidad de las redes neuronales requiere de una arquitectura apropiada que pueda simular este tipo de redes. Emular este tipo de redes en dispositivos configurables es adecuado debido a su extraordinario desarrollo en cuanto a recursos, velocidad y capacidad de reconfiguración (FPGAs).

En esta tesis se propone una arquitectura hardware paralela y configurable para emular las complejas y realistas redes neuronales tipo spiking en tiempo real. Se han estudiado y analizado algunos modelos de neuronas tipo spiking relevantes y sus implementaciones en hardware, con el fin de crear una arquitectura que soporte la implementación de estos modelos de manera eficiente.

Se han tenido en cuenta varios factores clave, incluyendo flexibilidad en la programación de algoritmos, procesamiento de alto rendimiento, bajo consumo de energía y área. Se han aplicado varias técnicas en la arquitectura desarrollada con el propósito de aumentar su desempeño. Estas técnicas son: mapeado de tiempo a espacio, virtualización de las neuronas, mapeo flexible de neuronas y sinapsis, modos de ejecución, y aprendizaje específico, entre otras.

Además, se ha desarrollado una unidad de interfaz de datos con el fin de construir un sistema bio-inspirado, que puede procesar información sensorial del medio ambiente. Este sistema basado en neuronas tipo spiking combina implementaciones analógicas y digitales. Varias aplicaciones se han desarrollado usando este sistema como prueba de concepto, con el fin de mostrar las capacidades de la arquitectura propuesta para el procesamiento de este tipo de información.

## Acknowledgments

First of all, I would like to thank all people who have been participated with me in the development of this project. It is very difficult to write it in few lines how they were important in this project.

I would like to thank Dr. Jordi Madrenas Boadas, who is the director of this thesis, for his supporting, and guiding me in the development of this thesis. I am very grateful with him for allowing me to do this thesis, also for his friendship. His valuable help has allowed me to develop this thesis and improve several professional aspects.

I would like to thank Dr. Alister Hamilton, and Dr. Thomas Jacob Koickal for their support, guidance during my research stage at *Institute for Micro and Nano Systems, School of Engineering and Joint Research Institute for Integrated Systems*, University of Edinburgh, Edinburgh, UK. The contribution with new ideas and observations given by Dr. Alister and Dr. Thomas has allowed improving this work.

I would like to thank to Adam Sokolnicki, Karthikeyan k., Salvo cambria, Vito pirrone for participating in the development of this thesis.

I would like to thank to Athul sripad for his important contributions in the development of this thesis. I am so grateful for his valuable help in the development and for his friendship.

I would like to thank to Sanjana Sekar for checking my spelling mistakes to improve my thesis and for her valuable friendship.

I would like to thank to Piotr Michalik, besides being my collage, he is my friend. I am so grateful with his help in several issues and friendship.

Quiero dar las gracias a mi amiga Rosario Zarate Maldonado, por su apoyo emocional que me ha brindado durante mi estancia en España.

I would like to thank to the Catalan Department of Innovation, Universities and Companies, and the European Social Fund for sponsoring this work.

Agradezco al Consejo de Ciencia y Tecnologia CONACyT por patrocinio para la realización de este proyecto de tesis.

# Contents

| Abstra  | ct       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | iii    |

|---------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Acknow  | wledgmei | nts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | v      |

|         | Figures  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | XV     |

| List of | Tables   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | xix    |

|         |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |

| Chapte  | er 1 In  | atroduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |

| 4.4     | D 11     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1      |

| 1.1     |          | m statement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1      |

| 1.2     |          | methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11     |

| 1.3     |          | e of the thesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 13     |

|         | Refere   | nces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 14     |

| Part 1  | I – Ubi  | ichip benchmarks and applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

| _ 00_0  |          | Total processing the state of t |        |

| Chapte  | er 2 Do  | escription and performance study of SNN implemen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | tation |

| 2.1     | Introdu  | action                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 19     |

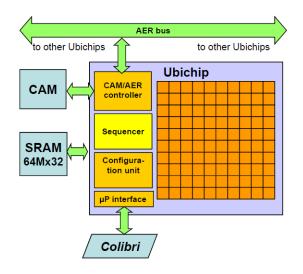

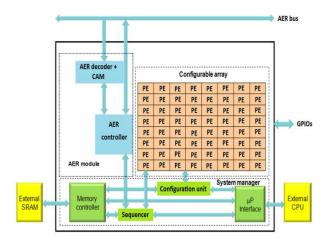

| 2.2     | Ubichi   | p architecture description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 20     |

|         | 2.2.1    | Architectural functional details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 22     |

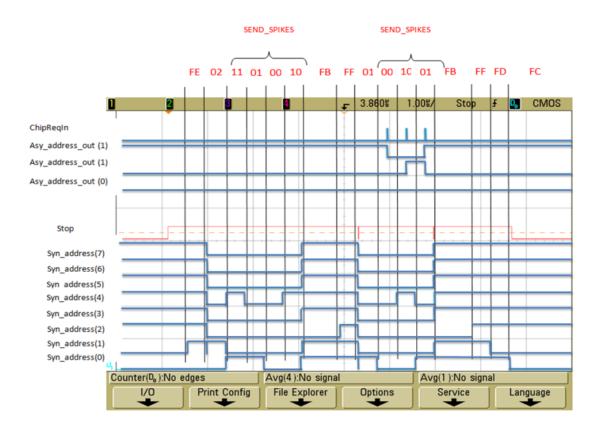

|         |          | 2.2.1.1 AER system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 24     |

| 2.3     | Perform  | mance evaluation – Iglesias and Villa model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 25     |

|         | 2.3.1    | Iglesias and Villa model description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 25     |

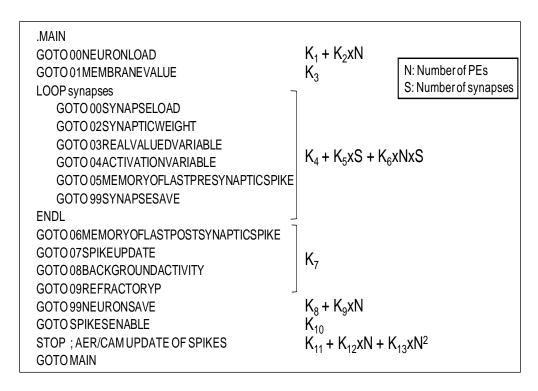

|         | 2.3.2    | Iglesias and Villa model implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 28     |

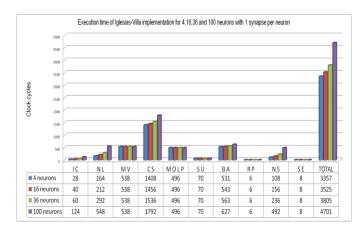

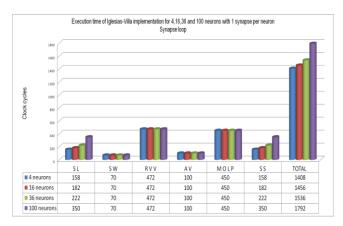

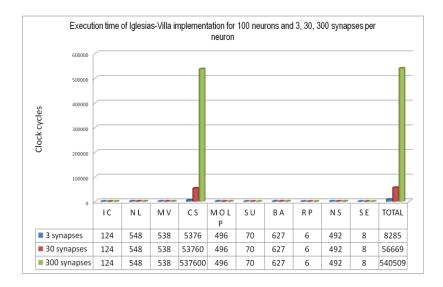

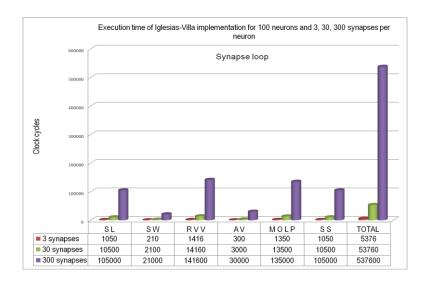

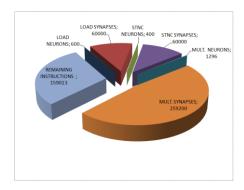

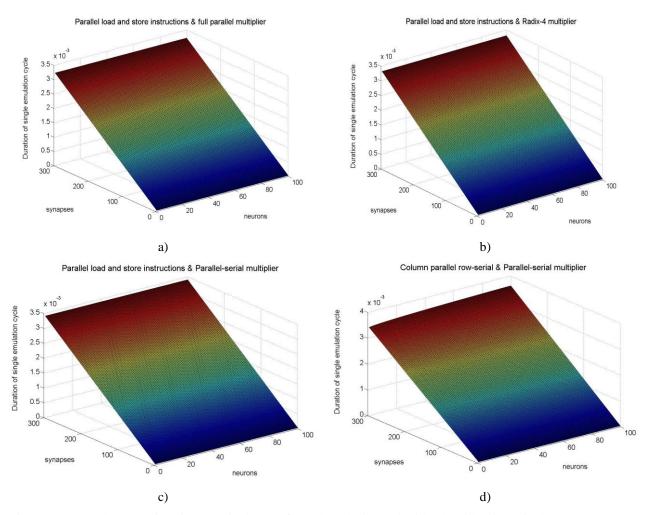

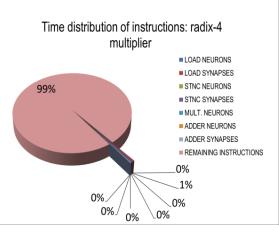

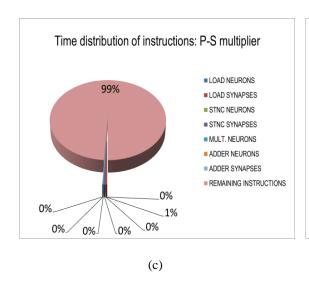

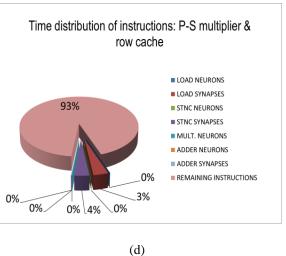

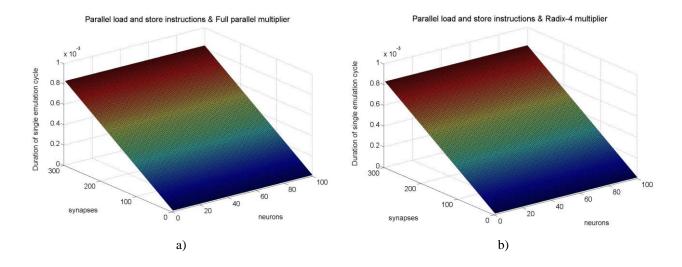

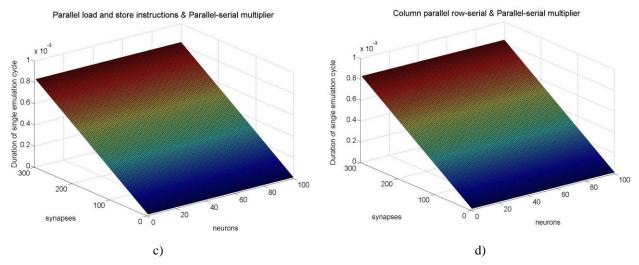

|         | 2.3.3    | Figures of performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 30     |

|         | 2.3.4    | Architecture limitations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 34     |

| 2.4     | Perform  | nance evaluation – Izhikevich model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 40     |

|         | 2.4.1    | Izhikevich model description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 40     |

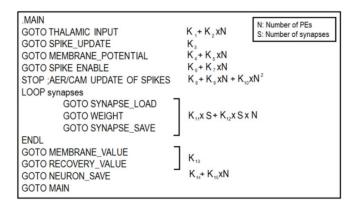

|         | 2.4.2    | Izhikevich model implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 41     |

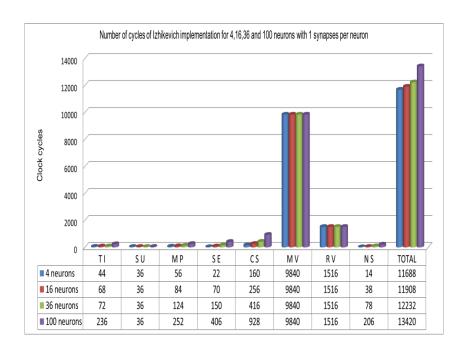

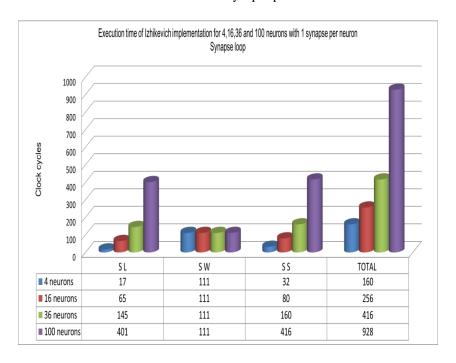

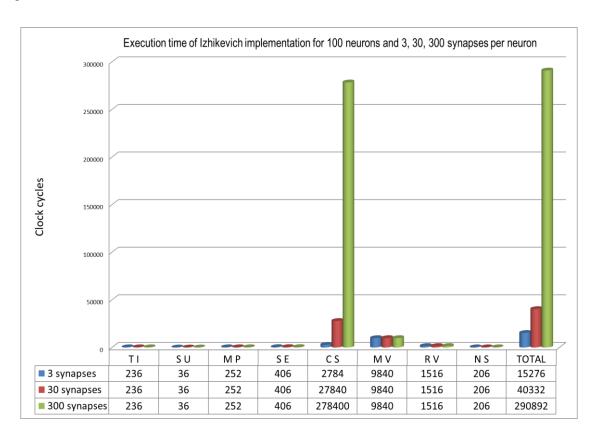

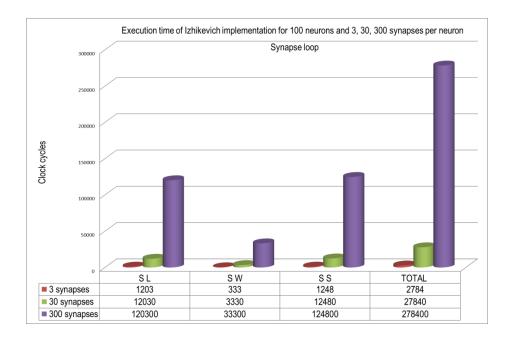

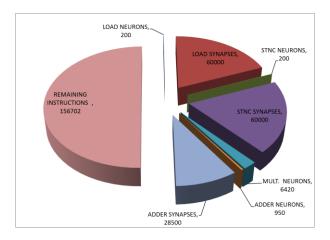

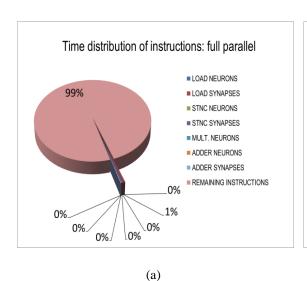

|         | 2.4.3    | Figures of performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 42     |

|         | 2.4.4    | Architecture limitations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 46     |

| 2.5     | Conclu   | sions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 51     |

|         | Referei  | nces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 53     |

|         |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |

| Chapter             | 3 Deve     | elopment of a data interface between Analog and  | l Digital |

|---------------------|------------|--------------------------------------------------|-----------|

| Neuromo             | orphic sys | tems                                             |           |

|                     |            |                                                  |           |

| 3.1                 | Introducti |                                                  | 55        |

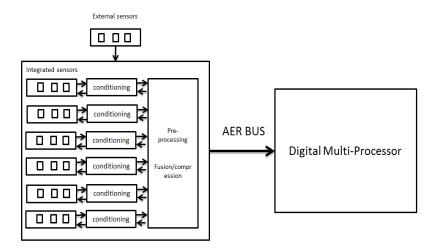

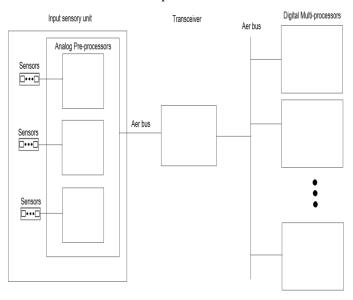

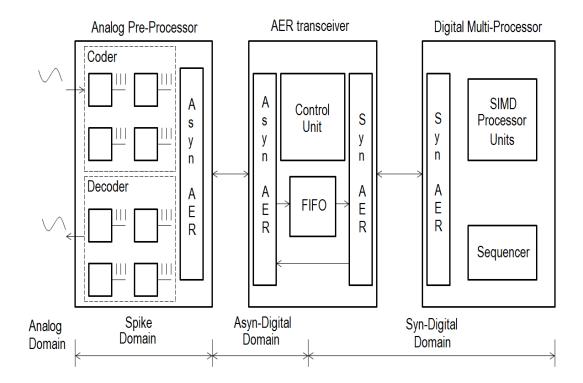

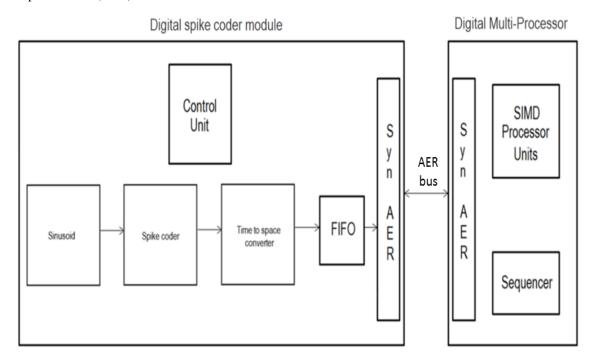

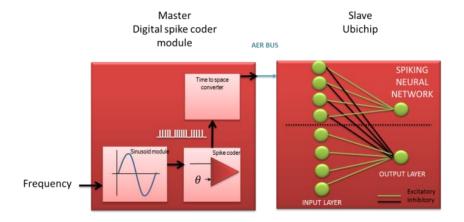

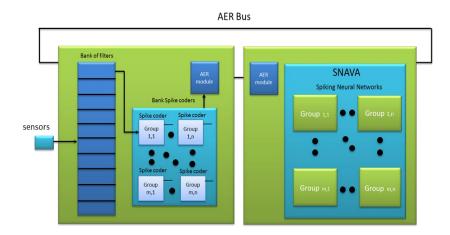

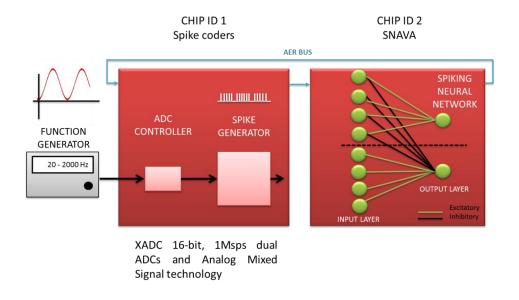

| 3.2                 |            | ogue-Digital neuromorphic system                 | 57        |

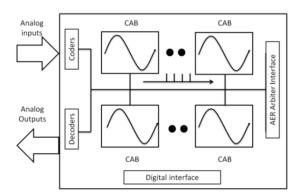

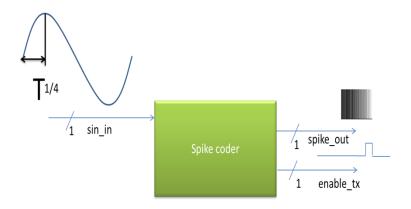

| 3.3                 |            | ogue Pre-Processor (APP)                         | 58        |

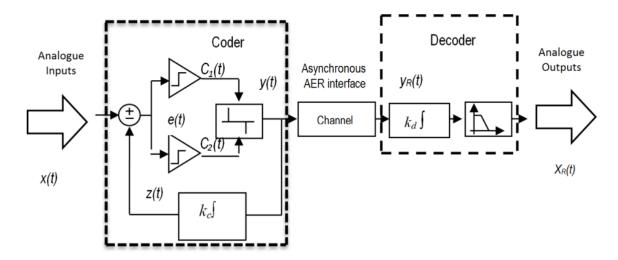

|                     | 3.3.1      | AER channel                                      | 59        |

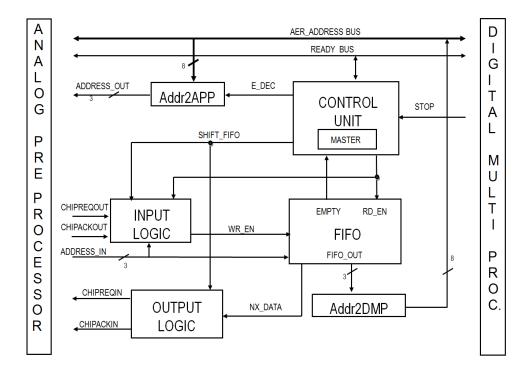

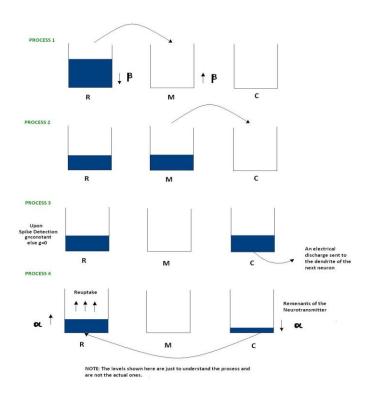

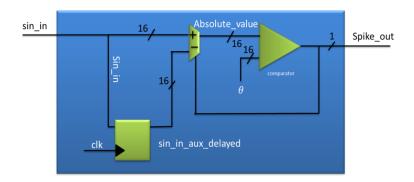

| 3.4                 |            | rer functional description                       | 59        |

| 3.5                 | Metric co  | nsiderations in the design of the data interface | 62        |

| 3.6                 | Results    |                                                  | 64        |

| 3.7                 | Conclusio  | ons                                              | 65        |

|                     | Reference  | ?S                                               | 66        |

| Chapter             | 4 App      | lication on Ubichip                              |           |

| 4.1                 | Introducti | ion                                              | 67        |

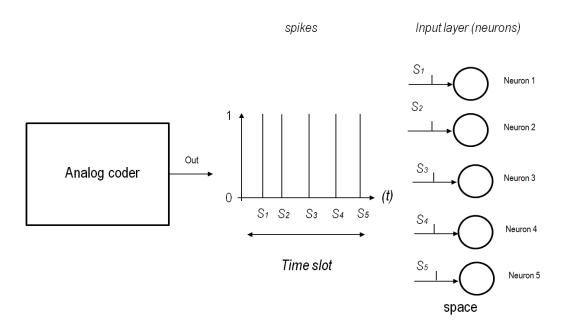

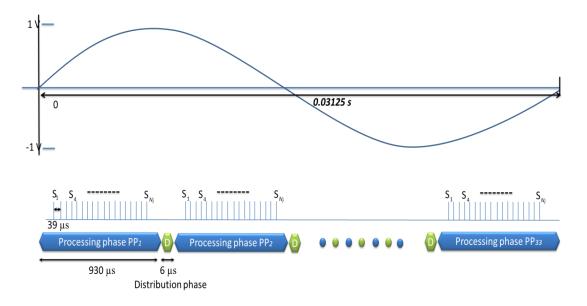

| 4.2                 | Frequency  | y level detection system                         | 68        |

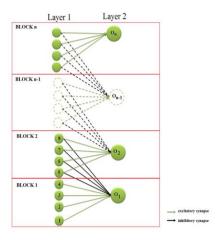

|                     | 4.2.1      | SNN model                                        | 69        |

|                     |            | 4.2.1.1 Parameters values                        | 70        |

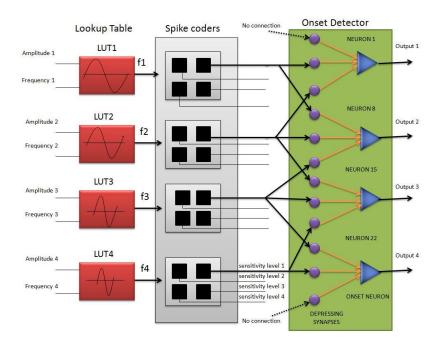

|                     | 4.2.2      | Frequency classifier                             | 71        |

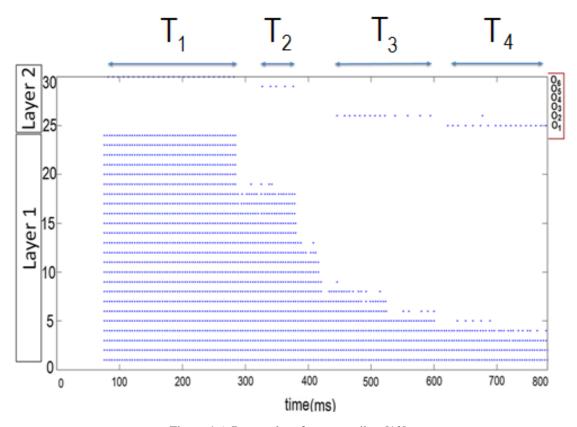

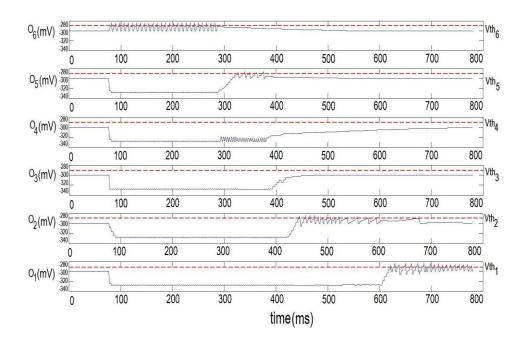

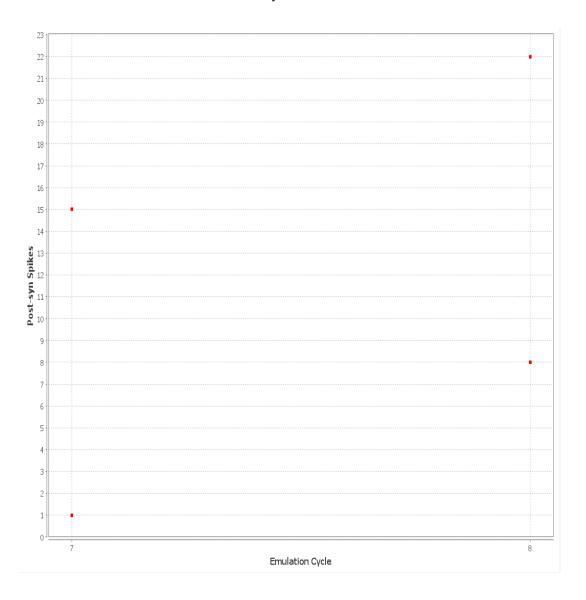

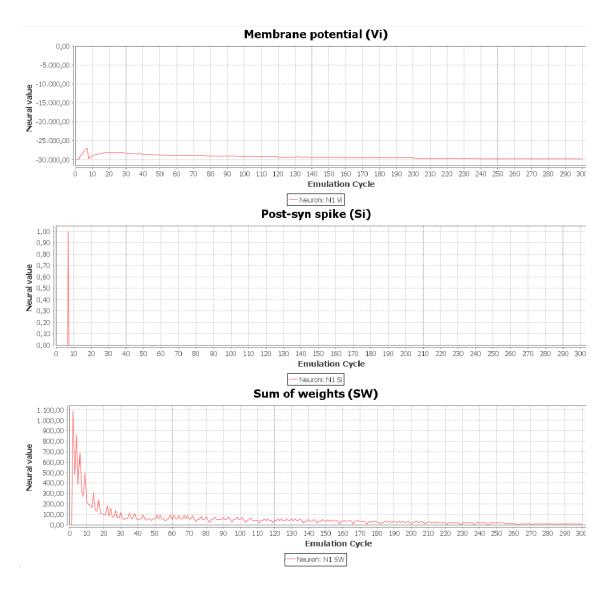

|                     | 4.2.3      | Experimental result                              | 72        |

| 4.3                 | Conclusio  | •                                                | 78        |

|                     | Reference  | es                                               | 78        |

|                     |            |                                                  |           |

| Part II             | - SNA      | VA architecture and applications                 |           |

|                     |            |                                                  |           |

| Chapter<br>Applicat |            | NAVA: Spiking Neural-network Architecture for    | Versatile |

| 5.1                 | Introducti | ion                                              | 82        |

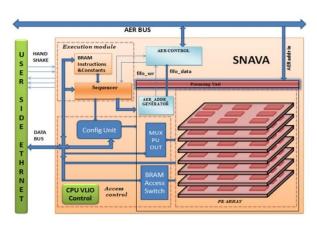

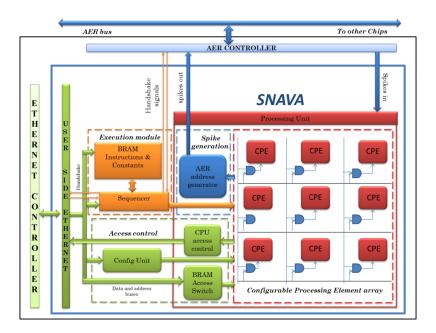

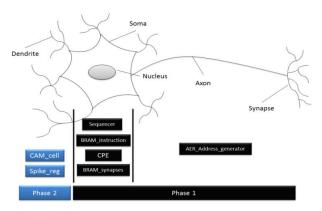

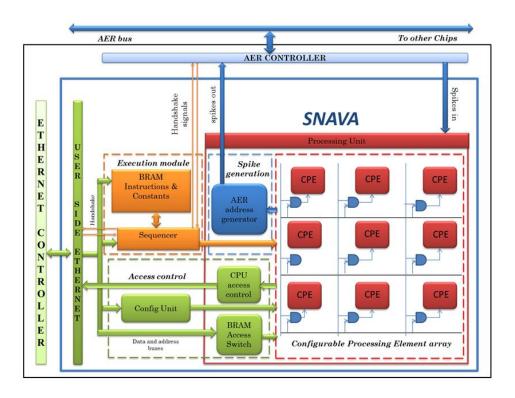

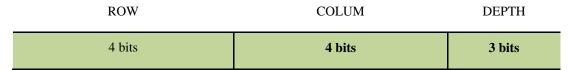

| 5.2                 | SNAVA o    | description                                      | 84        |

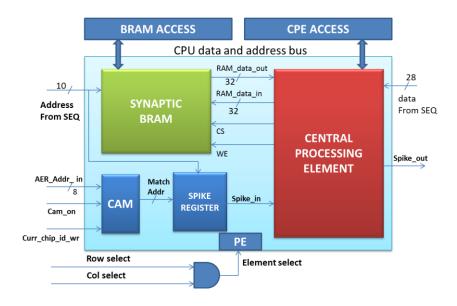

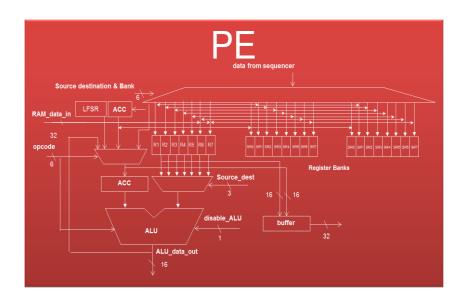

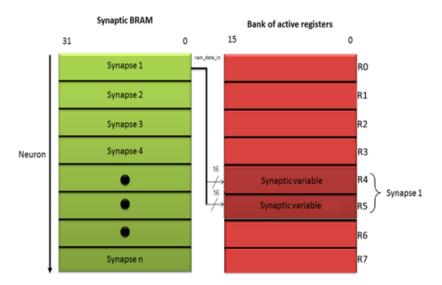

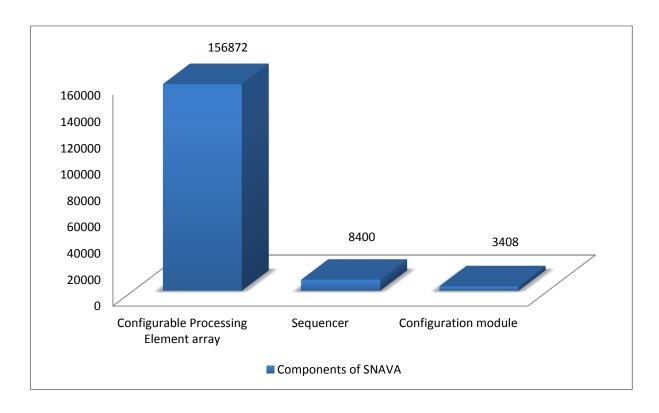

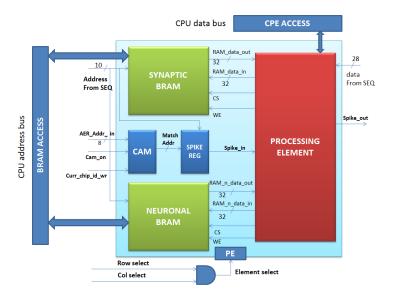

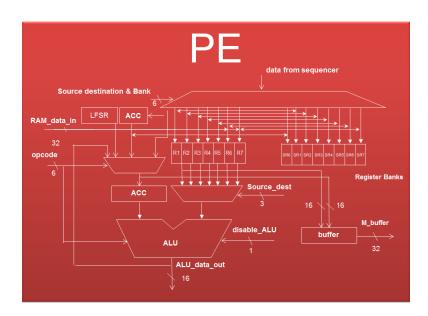

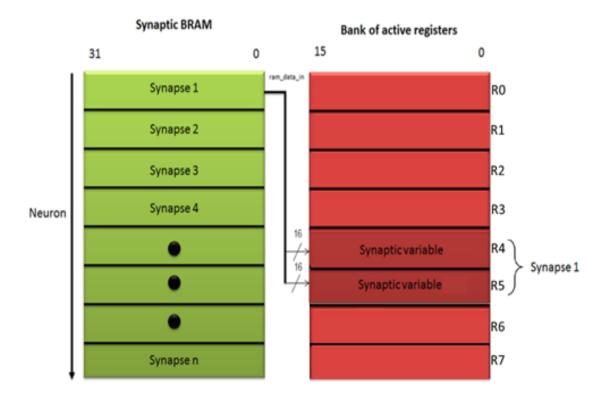

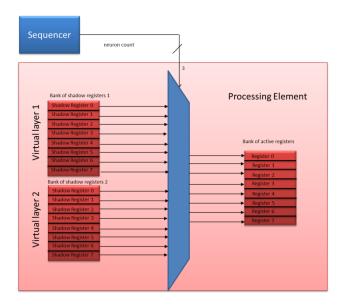

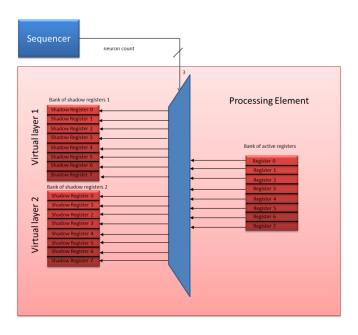

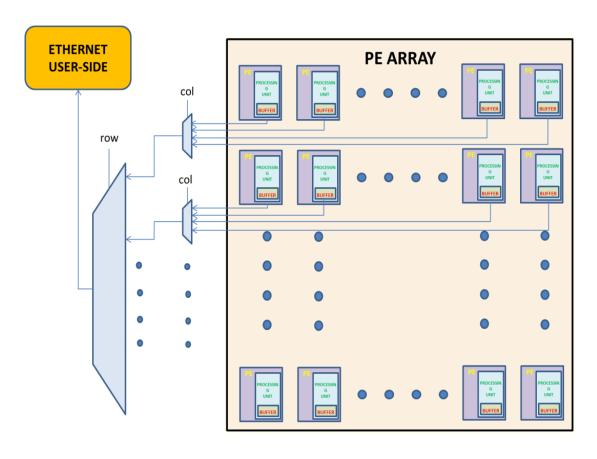

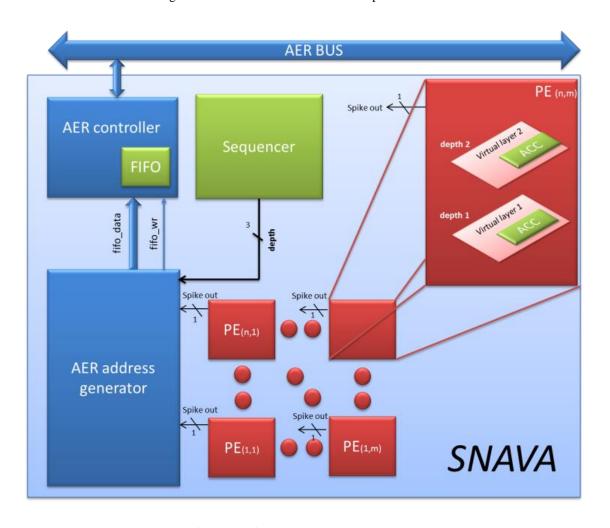

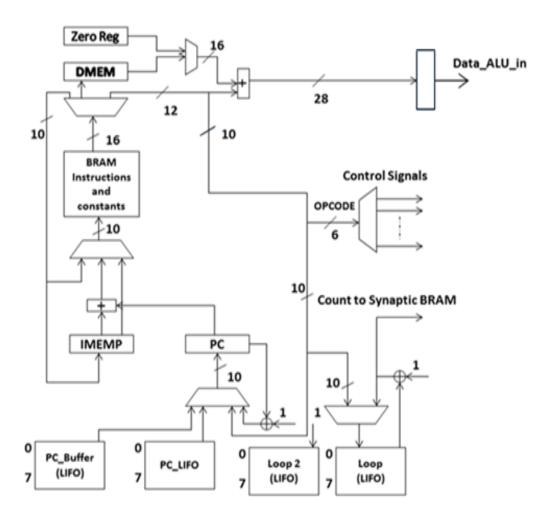

|                     | 5.2.1      | The Configurable Processing Element array        | 84        |

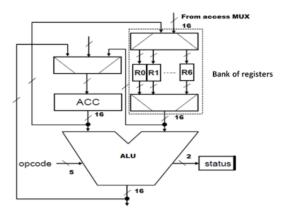

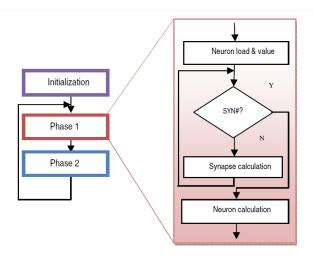

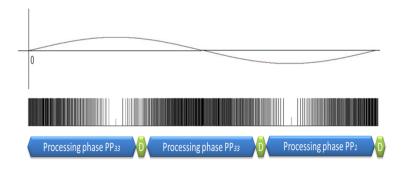

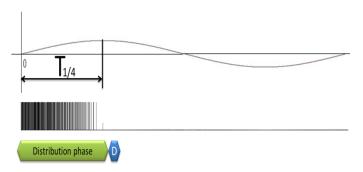

|                     | 5.2.2      | The execution module                             | 88        |

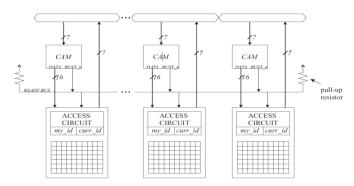

|                     | 5.2.3      | Access control module                            | 88        |

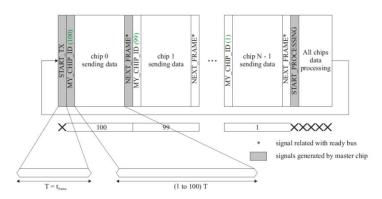

|                     | 5.2.4      | AER address generator                            | 90        |

|                     | 5.2.5      | Ethernet user side                               | 90        |

|                     | 5.2.6      | Phases of operation                              | 91        |

| 5.3                 | Implemen   | ntation and performance                          | 92        |

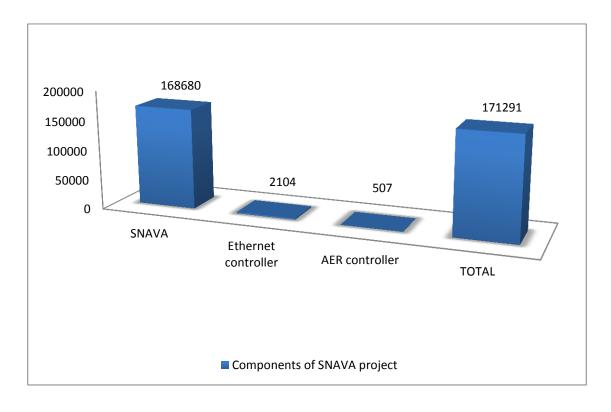

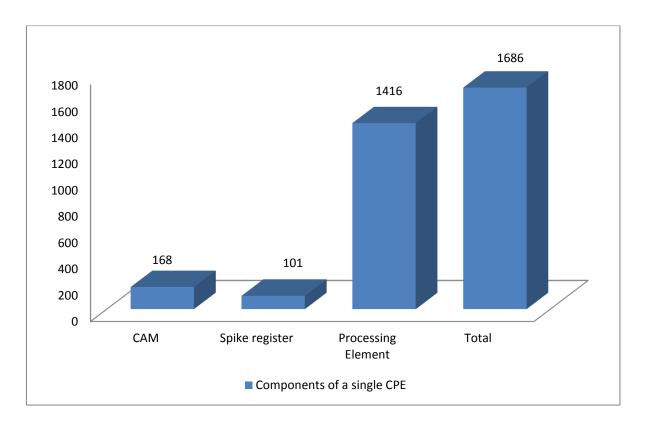

|                     | 5.3.1      | Area consumption                                 | 93        |

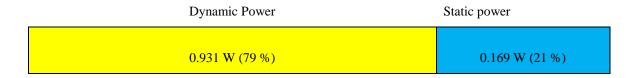

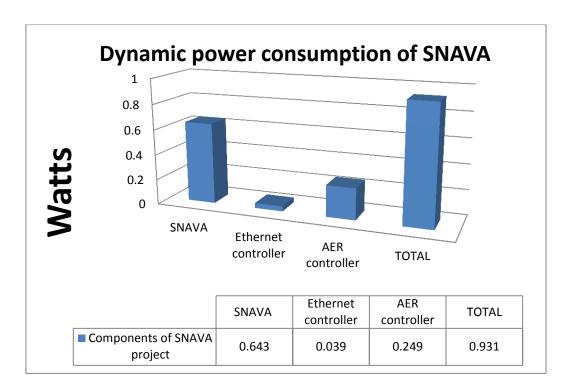

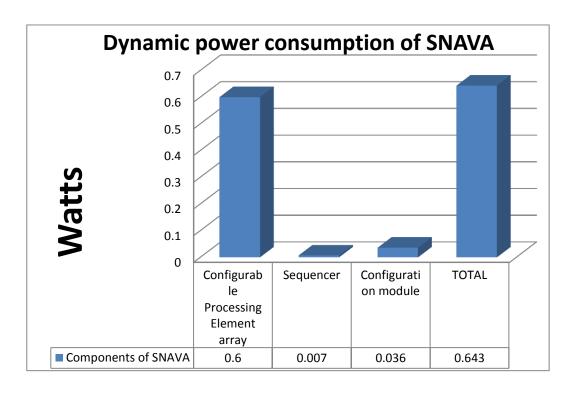

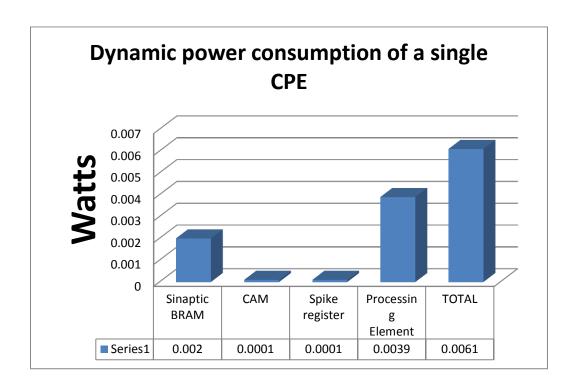

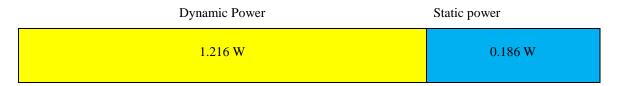

|                     | 5.3.2      | Power consumption                                | 96        |

| 5.4                 | Performa   | nce evaluation                                   | 98        |

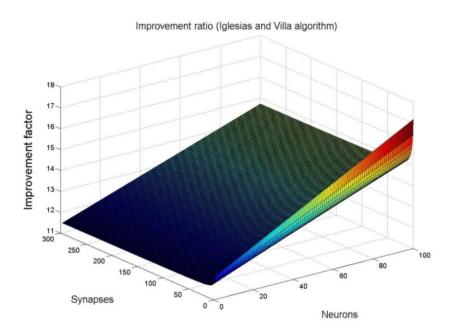

|                     | 5.4.1      | Iglesias and Villa model execution analysis      | 99        |

|            | 5.4.2          | Inhibayish model avacution analysis                     | 103        |

|------------|----------------|---------------------------------------------------------|------------|

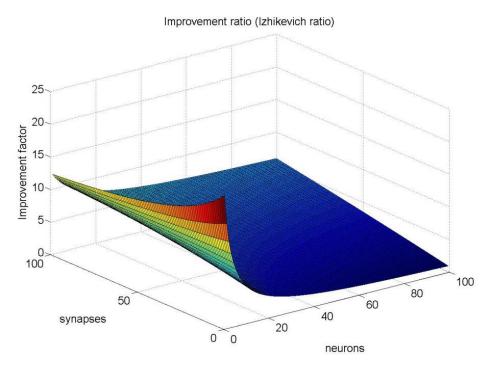

|            | 5.4.2<br>5.4.3 | Izhikevich model execution analysis                     |            |

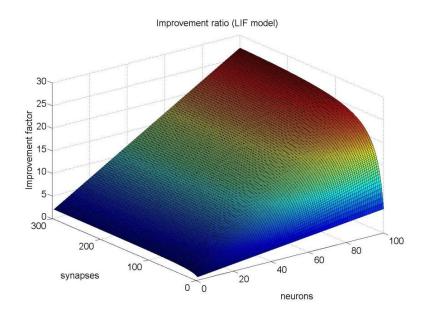

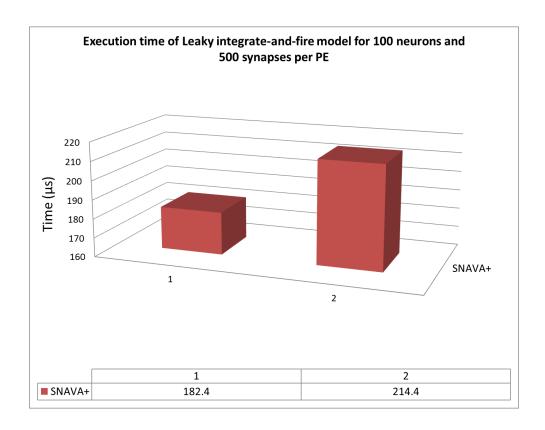

|            | 5.4.3<br>5.4.4 | Leaky Integrate-and-Fire model execution analysis       | 106<br>109 |

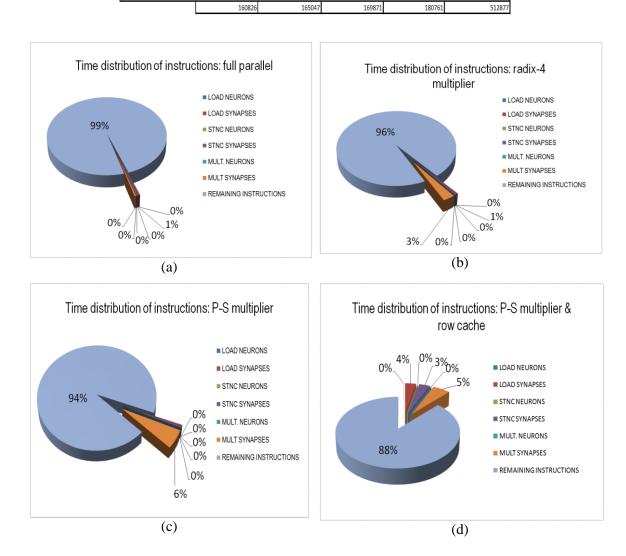

| 5.5        |                | Processing time and distribution time for any SNN model | 1109       |

| 3.3        | 5.5.1          | son with other approaches                               | 110        |

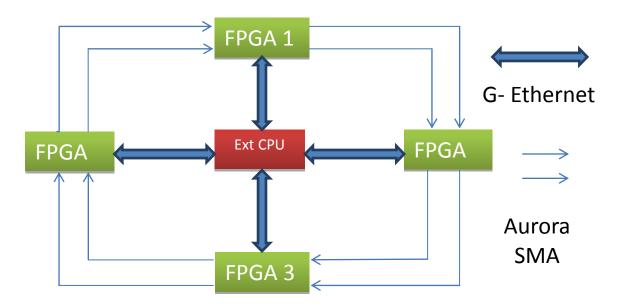

|            |                | Implementation on multi-processor                       | 111        |

|            | 5.5.2<br>5.5.3 | Implementations on GPU                                  | 112        |

|            | 5.5.4          | Implementations on FPGA General discussion              | 115        |

| 5 6        |                |                                                         | 113        |

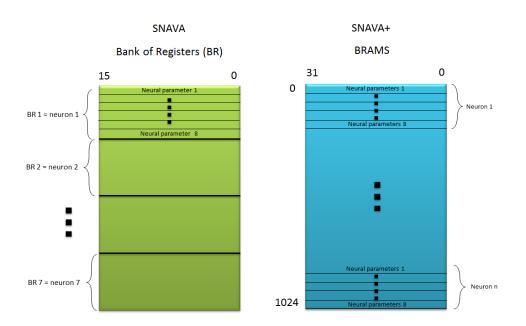

| 5.6        | 5.6.1          | ments in SNAVA: SNAVA+                                  | 118        |

|            |                | Brief description of SNAVA+ architecture                |            |

|            | 5.6.2          | Implementation and performance                          | 121<br>121 |

|            |                | 5.6.2.1 Area consumption                                |            |

|            | 5 6 2          | 5.6.2.2 Power consumption                               | 122        |

|            | 5.6.3          | Performance evaluation                                  | 124        |

| <i>5</i> 7 | 5.6.4          | Comparison with other approaches                        | 128        |

| 5.7        | Conclusion     |                                                         | 130        |

|            | Referenc       | es                                                      | 130        |

| Chapter    | 6 Pro          | oof-of-concept application on SNAVA                     |            |

| 6.1        | Introduct      | ion                                                     | 133        |

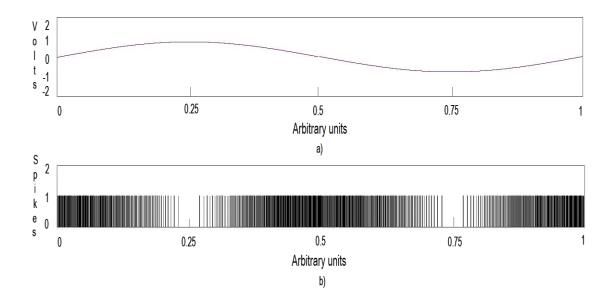

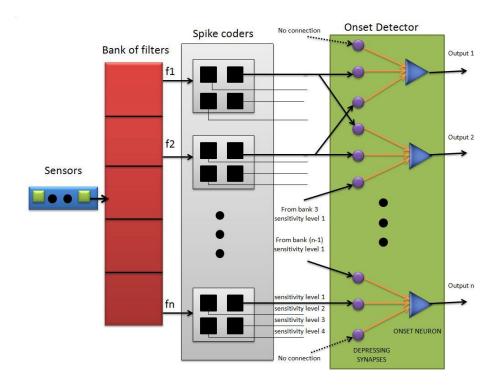

| 6.2        |                | ired system description                                 | 134        |

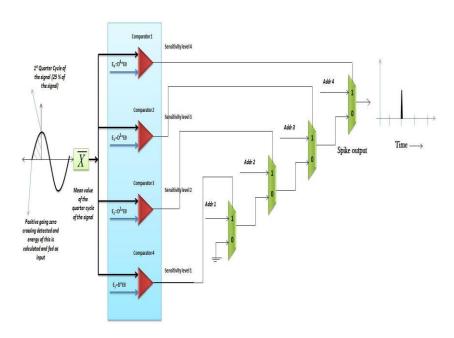

| 6.3        | -              | le detection                                            | 136        |

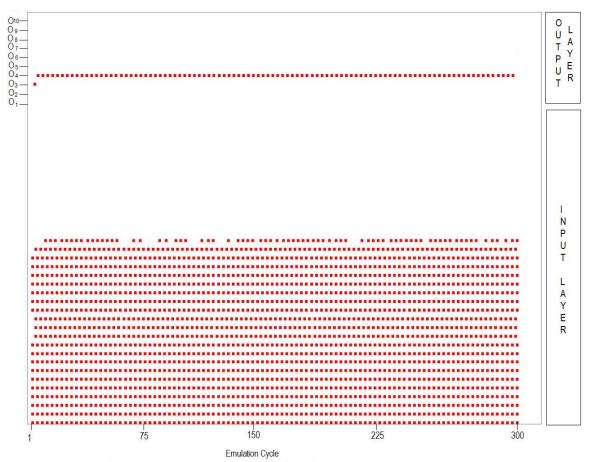

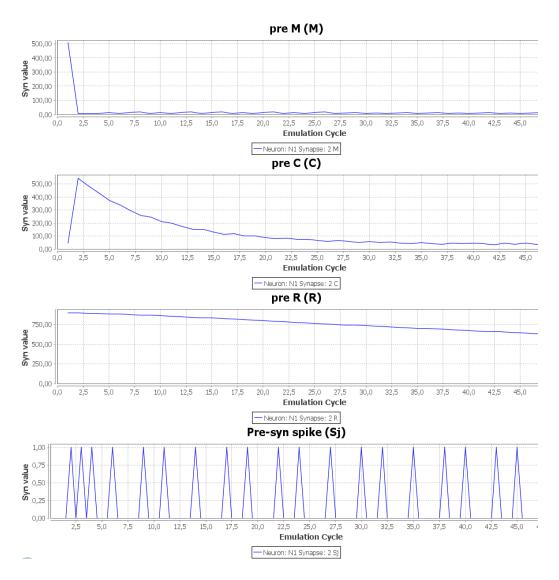

|            | 6.3.1          | SNN model description                                   | 137        |

|            | 6.3.2          | Amplitude classifier                                    | 139        |

| 6.4        | Experime       | ental results                                           | 140        |

| 6.5        | Conclusi       |                                                         | 145        |

|            | Referenc       | es                                                      | 146        |

| Chapter    | 7 Ger          | neral Conclusion and ongoing work                       |            |

| ozup.vz    |                |                                                         |            |

| 7.1        | General (      | Conclusion                                              | 147        |

| 7.2        | Ongoing        | work                                                    | 148        |

|            | Referenc       | es                                                      | 149        |

|            |                |                                                         |            |

| Annexui    | re A Set       | of instructions of SNAVA                                |            |

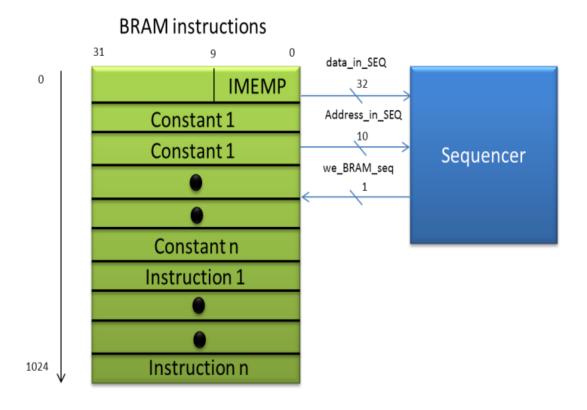

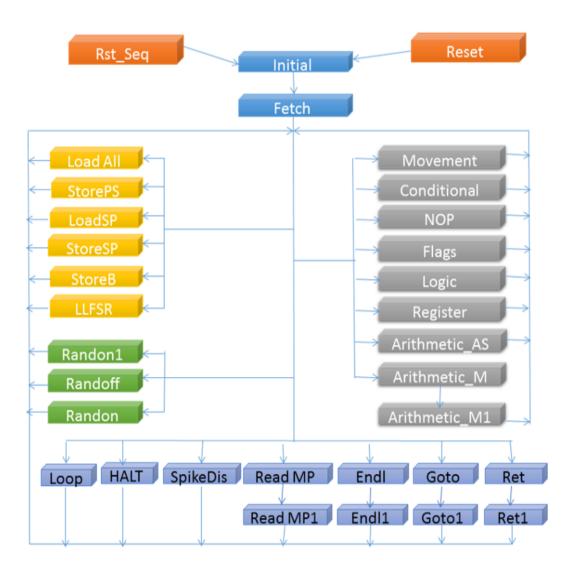

| A.1        | Introduct      | ion                                                     | 151        |

| A.2        | Operation      | n of the sequencer                                      | 152        |

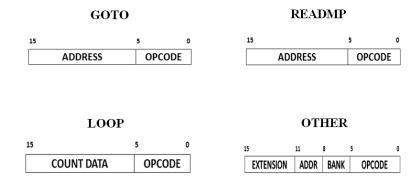

| A.3        | •              | ons classification and formats                          | 153        |

| A.4        | Algorith       | n structure                                             | 160        |

| A.5        | •              | ture functional details                                 | 164        |

| A.6        |                | er register mapping                                     | 167        |

|            | _              |                                                         |            |

## Annexure B Register mapping in SNAVA for CPU access

| B.1     | Register   | mapping                                                  | 171 |

|---------|------------|----------------------------------------------------------|-----|

| Annexu  | re C As    | sembly codes                                             |     |

| C.1     | Assemb     | ler code of Iglesias and villa algorithm – Ubichip       | 177 |