### Scalable System Software for High Performance Large-scale Applications

Alessandro Morari Department of Computer Architecture Universitat Politècnica de Catalunya

A thesis submitted for the degree of Doctor of Philosophy

$27~\mathrm{May}~2014$

Ai miei genitori Fabrizio ed Elena, a mia sorella Elisa ed ai miei nonni Stefano e Vera.

#### Acknowledgements

I would like to thank my Thesis Director Prof. Mateo Valero, for his continuous support and prompt attention, even when we were separated by a whole continent. I would also like to acknowledge my mentor Dr. Roberto Gioiosa, for believing in me from the beginning, and for challenging me with his thoughtful remarks. I would like to thank my friends and colleagues at Pacific Northwest National Laboratories, Dr. Oreste Villa and Dr. Antonino Tumeo. Their friendship and teachings made me change radically, transforming this time in the laboratory to an amazing experience. I would like to thank the director of the Center for Adaptive Supercomputer Software Dr. John Feo, for his incredible heart and honesty, and for supporting me from the first day we met. I would also like to thank my group leader at the Barcelona Supercomputing Center, Dr. Francisco Cazorla, for continuously supporting my research activity and for patiently dealing with my laziness with bureaucratic procedures. I would like to acknowledge my colleagues in the CAOS group at Barcelona Supercomputing Center Marco Paolieri, Roberta Piscitelli, Carlos Luque, Carlos Boneti, Bojan Maric, Kamil Kedzierski, Victor Jimenez, Petar Radojkovic, Vladimir Kacarevic, Dr. Eduardo Quiñones, Dr. Jaume Abella and Dr. Miquel Moreto for the interesting discussions and the beautiful moments shared when I was working in Barcelona. Also, I would like to thank my colleagues at IBM T. J. Watson Dr. Robert Wisniewski, Dr. Bryan Rosenburg, Dr. Jose Brunheroto, Dr. Chen-Yong Cher and Dr. Alper Buyuktosunoglu for sharing with me their knowledge and giving me the opportunity of working on extremely interesting problems. Finally, I am deeply grateful to my family for their incredible support, for their love and for giving me the gift of curiosity that has taken me where I stand today.

#### Abstract

In the last decades, high-performance large-scale systems have been a fundamental tool for scientific discovery and engineering advances. The next generation of supercomputers will be able to deliver a performance in the order of  $10^{18}$  floating point operations per seconds (ExaFlop). The design of a new generation of supercomputers, called *Exascale* generation, is the object of a large part of current research in HPC. The availability of largescale models and simulation and the availability of large instruments like telescopes, colliders and light sources has generated a growing volume of scientific data. Computing resources to move, analyze and manage this exponentially growing volume of data is becoming the next big challenge, commonly referred as *big data*. The steps toward the design of an Exascale Supercomputer are increasingly pointing to the necessity of integrating Exascale with big data.

Over the years, the difficulty of efficiently manage large-scale system resources has repeatedly shown the importance of providing scalable system software. System software has evolved to keep pace with technology and applications evolution. Research on scalable system software for large-scale system has historically been driven by two fundamental aspects: on one side, performance, efficiency and reliability, on the other side the goal of providing a productive developing environment.

Considered the challenges posed by the next-generation large-scale highperformance systems and applications, it is clear that system software needs to be significantly updated if not redesigned. In this Thesis, we propose approaches to measure, design and implement scalable system software.

Overall, this Thesis proposes three orthogonal approaches that should be integrated into a new system-software layer for next-generation large-scale high performance computing systems:

• To obtain scalable applications a detailed measurement and under-

standing of system software performance and overhead are necessary. We design and implement a methodology to provide detailed measurement of system software interruptions and their effect on applications performance.

- The runtime system is the right candidate to provide highly scalable system services and to exploits low-level hardware optimizations. Some system services could be moved from the operating system to the runtime system. A specialized runtime system for a class of application can leverage a deeper knowledge of the application behaviour and exploit low-level hardware features to improve scalability. We design and implement a runtime system for the class of irregular applications and show a performance improvement of several orders of magnitude with respect to more traditional approaches.

- Exploiting low-level hardware features at user-level (i.e., in the application) can lead to considerable performance improvement. We show two instances of optimizations leveraging architecture-specific hardware features and obtaining significant performance improvement.

To enhance the performance of an entire class of applications, those approaches should be integrated into a specialized runtime system.

# Contents

| Co            | onter | $\mathbf{nts}$ |                                                               | v         |

|---------------|-------|----------------|---------------------------------------------------------------|-----------|

| $\mathbf{Li}$ | st of | Figur          | es                                                            | xi        |

| Ι             | Int   | roduc          | tion and Backround                                            | 1         |

| 1             | Intr  | roducti        | ion                                                           | 3         |

|               | 1.1   | Challe         | enges of Next-generation High-performance Large-scale systems | 3         |

|               | 1.2   | Propo          | sed approach and methodologies                                | 5         |

|               | 1.3   | Thesis         | s contributions                                               | 6         |

|               | 1.4   | Thesis         | s structure                                                   | 8         |

| <b>2</b>      | Bac   | kgrou          | nd: current trends in High Performance Computing              | 9         |

|               | 2.1   | Techn          | ology trends                                                  | 9         |

|               | 2.2   | Scient         | ific and large-scale applications                             | 12        |

|               |       | 2.2.1          | Big data and exascale computing                               | 14        |

|               |       | 2.2.2          | Data-intensive and Irregular Applications                     | 16        |

|               | 2.3   | Syster         | n software for large-scale systems                            | 17        |

|               |       | 2.3.1          | Operating Systems                                             | 18        |

|               |       | 2.3.2          | Runtime Systems and Parallel Programming Models               | 20        |

|               |       | 2.3.3          | Trends in System Software                                     | 26        |

| II            | O     | perati         | ng System Scalability                                         | 29        |

| 3             | Ger   | neral P        | Purpose Operating Systems                                     | <b>31</b> |

|               | 3.1   |                | nary                                                          | 31        |

|               | 3.2   | Exper          | imental environment                                           | 34        |

|          | 3.3          | Related Work                                           | 34       |

|----------|--------------|--------------------------------------------------------|----------|

|          | 3.4          | Measuring OS noise                                     | 36       |

|          |              | 3.4.1 LTTNG-NOISE                                      | 39       |

|          |              | 3.4.2 Tracing scalability                              | 40       |

|          |              | 3.4.3 Analyzing FTQ with LTTNG-NOISE                   | 40       |

|          | 3.5          | Experimental Results                                   | 43       |

|          |              | 3.5.1 Noise breakdown                                  | 44       |

|          |              | 3.5.2 Page faults                                      | 46       |

|          |              | 3.5.3 Scheduling                                       | 48       |

|          |              | 3.5.4 Process preemption and $I/O$                     | 49       |

|          |              | 3.5.5 Periodic activities                              | 52       |

|          | 3.6          | Noise disambiguation                                   | 53       |

|          |              | 3.6.1 Disambiguation of qualitative similar activities | 55       |

|          |              | 3.6.2 OS noise composition                             | 56       |

|          |              | 3.6.3 Conclusions                                      | 56       |

| 4        | т:1          | t militate On another Southanna                        | -0       |

| 4        |              |                                                        | 59<br>50 |

|          | 4.1          | U U                                                    | 59<br>69 |

|          | 4.2          | 1                                                      | 62<br>62 |

|          | $4.3 \\ 4.4$ |                                                        | 62<br>63 |

|          | 4.4          |                                                        | 03<br>65 |

|          | 4.0          |                                                        | 66       |

|          |              |                                                        | 68       |

|          |              | 5                                                      |          |

|          | 1 C          |                                                        | 69<br>71 |

|          | 4.6          | 1                                                      | 71       |

|          |              |                                                        | 72       |

|          |              | 0                                                      | 73       |

|          | 4 7          | 0                                                      | 77<br>00 |

|          | 4.7          | Conclusions                                            | 82       |

|          |              |                                                        |          |

| II       | I R          | Cuntime System Scalability 8                           | 83       |

| <b>5</b> | Scal         | able Runtimes for Distributed Memory Systems           | 85       |

|          | 5.1          |                                                        | 85       |

|          | 5.2          |                                                        | 89       |

#### CONTENTS

|   | 5.3  | Relate                  | ed Work                                                                                                                |

|---|------|-------------------------|------------------------------------------------------------------------------------------------------------------------|

|   | 5.4  | Progra                  | amming model and API                                                                                                   |

|   |      | 5.4.1                   | PGAS communication model                                                                                               |

|   |      | 5.4.2                   | Loop parallelism program structure model                                                                               |

|   |      | 5.4.3                   | Explicit data and code locality management                                                                             |

|   |      | 5.4.4                   | Blocking and Non-blocking semantics                                                                                    |

|   |      | 5.4.5                   | Explicit synchronization                                                                                               |

|   |      | 5.4.6                   | Example                                                                                                                |

|   | 5.5  | Runti                   | me architecture                                                                                                        |

|   |      | 5.5.1                   | Overview                                                                                                               |

|   |      | 5.5.2                   | $Communication \ldots 101$                       |

|   |      | 5.5.3                   | Aggregation                                                                                                            |

|   |      | 5.5.4                   | Multithreading $\ldots \ldots 105$ |

|   | 5.6  | Exper                   | imental Evaluation                                                                                                     |

|   |      | 5.6.1                   | ${\rm Micro-benchmarks}  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  109$                          |

|   |      | 5.6.2                   | BFS                                                                                                                    |

|   |      | 5.6.3                   | Graph Random Walk                                                                                                      |

|   |      | 5.6.4                   | Concurrent Hash Map Access                                                                                             |

|   | 5.7  | Concl                   | usions $\ldots$ $\ldots$ $\ldots$ $\ldots$ $117$                                                                       |

|   |      |                         |                                                                                                                        |

| I | V U  | Jser-le                 | vel Scalability Exploiting Hardware Features 119                                                                       |

|   |      |                         |                                                                                                                        |

| 6 | -    | -                       | g Hardware Thread Priorities on Multi-threaded Architec-                                                               |

|   | ture |                         | 121                                                                                                                    |

|   | 6.1  |                         | nary                                                                                                                   |

|   | 6.2  | -                       | imental environment                                                                                                    |

|   | 6.3  |                         | ed Work                                                                                                                |

|   | 6.4  |                         | ER5 and POWER6 Microarchitecture                                                                                       |

|   |      | 6.4.1                   | POWER5 and POWER6 Core Microarchitecture                                                                               |

|   |      | 6.4.2                   | Simultaneous Multi-Threading 125                                                                                       |

|   |      |                         |                                                                                                                        |

|   |      | 6.4.3                   | Software-controlled Hardware Thread Priorities                                                                         |

|   | 6.5  | Exper                   | imental Setup                                                                                                          |

|   | 6.5  | Exper<br>6.5.1          | imental Setup128Experimental environment129                                                                            |

|   | 6.5  | Exper<br>6.5.1<br>6.5.2 | imental Setup128Experimental environment129The Linux kernel modification130                                            |

|   | 6.5  | Exper<br>6.5.1          | imental Setup128Experimental environment129                                                                            |

|   |     |        | 6.5.4.1      | Integer micro-benchmarks                                                              |    | • • |     | 132 |

|---|-----|--------|--------------|---------------------------------------------------------------------------------------|----|-----|-----|-----|

|   |     |        | 6.5.4.2      | Floating point micro-benchmarks                                                       |    | •   |     | 132 |

|   |     |        | 6.5.4.3      | Memory micro-benchmarks                                                               |    | •   |     | 133 |

|   | 6.6 | Analys | sis of resul | ts $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$   |    | •   |     | 133 |

|   |     | 6.6.1  | Default F    | Priorities                                                                            |    | •   |     | 133 |

|   |     | 6.6.2  | Malleabil    | ity                                                                                   |    | •   |     | 134 |

|   |     | 6.6.3  | Higher P     | riority                                                                               |    | •   |     | 135 |

|   |     | 6.6.4  | Lower Pr     | iority                                                                                |    | •   |     | 141 |

|   |     | 6.6.5  | Maximun      | a priority difference                                                                 |    | •   |     | 141 |

|   |     | 6.6.6  | Malleabil    | ity of SPEC CPU2006                                                                   |    | •   |     | 142 |

|   | 6.7 | Use ca | ses          |                                                                                       |    | •   |     | 144 |

|   |     | 6.7.1  | Use case     | A - Load Balancing                                                                    |    | •   |     | 144 |

|   |     | 6.7.2  | Use case     | B - Transparent threads                                                               |    | •   |     | 146 |

|   | 6.8 | Conclu | usions       |                                                                                       |    | •   |     | 148 |

| _ | Б   |        |              |                                                                                       |    |     |     |     |

| 7 | -   |        |              | cality and network-on-chip to optimize so                                             | rt | ing | g ( |     |

|   |     | v      | ore archit   |                                                                                       |    |     |     | 151 |

|   | 7.1 |        | U U          |                                                                                       |    |     |     |     |

|   | 7.2 | -      |              | vironment                                                                             |    |     |     |     |

|   | 7.3 |        |              | e processor                                                                           |    |     |     |     |

|   |     | 7.3.1  |              | architecture                                                                          |    |     |     |     |

|   |     | 7.3.2  |              | ural characterization                                                                 |    |     |     |     |

|   | 7.4 | 0      |              |                                                                                       |    |     |     |     |

|   |     | 7.4.1  |              | .t                                                                                    |    |     |     |     |

|   |     | 7.4.2  |              | vork                                                                                  |    |     |     |     |

|   | 7.5 |        |              | ort                                                                                   |    |     |     |     |

|   |     | 7.5.1  |              | togram                                                                                |    |     |     |     |

|   |     | 7.5.2  |              | mputation                                                                             |    |     |     |     |

|   |     | 7.5.3  | 0            | ribution                                                                              |    |     |     | 161 |

|   | 7.6 | -      |              |                                                                                       |    |     |     |     |

|   |     | 7.6.1  |              | $togram \ldots \ldots$ |    |     |     | 162 |

|   |     | 7.6.2  |              | mputation                                                                             |    |     |     | 163 |

|   |     | 7.6.3  | 0            | tribution                                                                             |    |     |     | 164 |

|   | 7.7 | Exper  |              | aluation                                                                              |    |     |     |     |

|   |     | 7.7.1  | -            | ental setup                                                                           |    |     |     |     |

|   |     | 7.7.2  | Optimiza     | tion effects $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$  |    | •   |     | 167 |

#### CONTENTS

|                 |            | 7.7.3  | Scaling  |     |  |  |  |  |  | •   |       | <br>• |       |   |  |  |  | 167 |

|-----------------|------------|--------|----------|-----|--|--|--|--|--|-----|-------|-------|-------|---|--|--|--|-----|

|                 |            | 7.7.4  | Comparia | son |  |  |  |  |  | •   |       | <br>• | <br>• |   |  |  |  | 169 |

|                 | 7.8        | Conclu | usions   |     |  |  |  |  |  |     | <br>• | <br>• | <br>• | • |  |  |  | 171 |

| 8               | Con        | clusio | ns       |     |  |  |  |  |  |     |       |       |       |   |  |  |  | 173 |

| Pubblications 1 |            |        |          |     |  |  |  |  |  | 175 |       |       |       |   |  |  |  |     |

| R               | References |        |          |     |  |  |  |  |  | 177 |       |       |       |   |  |  |  |     |

CONTENTS

# List of Figures

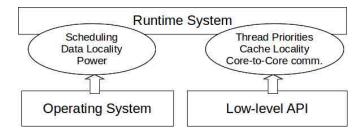

| 1.1 | Next-generation runtime systems will include additional system services<br>and exploit low-level hardware features to optimize an entire class of<br>applications                                   | 6  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

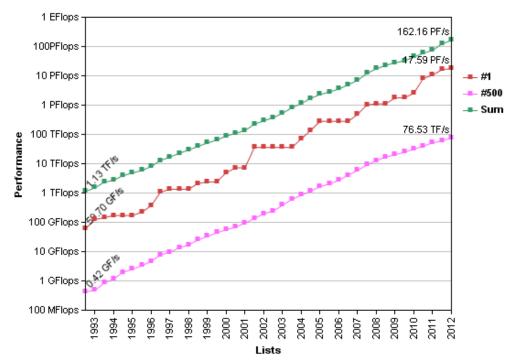

| 2.1 | Exponential growth of supercomputing power as recorded by the TOP500 $[10]$ - #1 refers to the first in the list, #500 refers to the 500th and Sum is the sum of all supercomputers in the list.    | 10 |

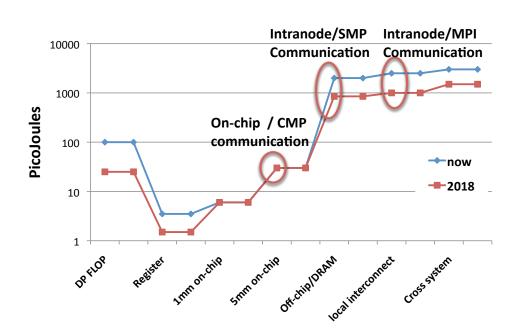

| 2.2 | Energy consumption for data communication, difference between today and in 2018 [24]                                                                                                                | 13 |

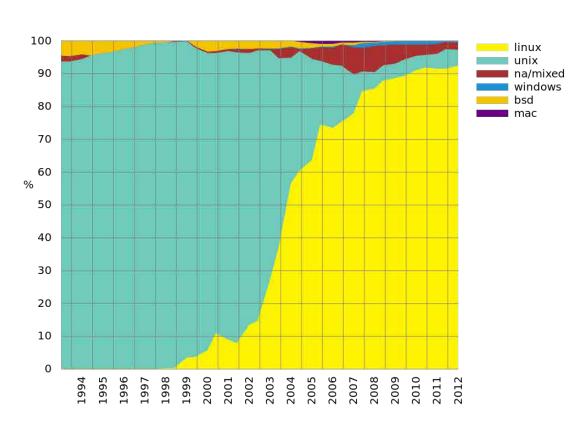

| 2.3 | Percentage of the TOP500 using a given Operating System $[10]$                                                                                                                                      | 19 |

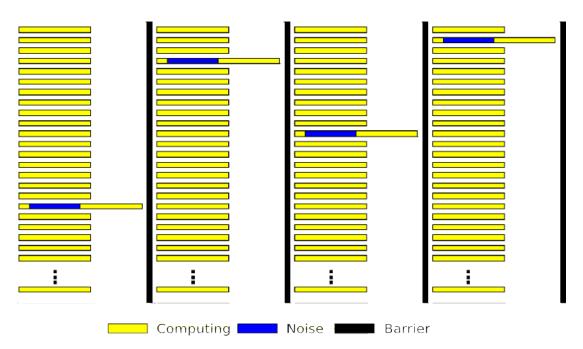

| 2.4 | Effect of an OS interruption on a parallel application.                                                                                                                                             | 20 |

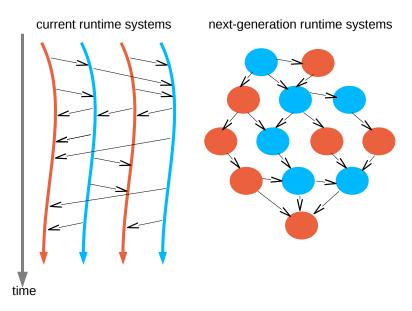

| 2.5 | Programming model schema for current and next-generation runtime systems                                                                                                                            | 27 |

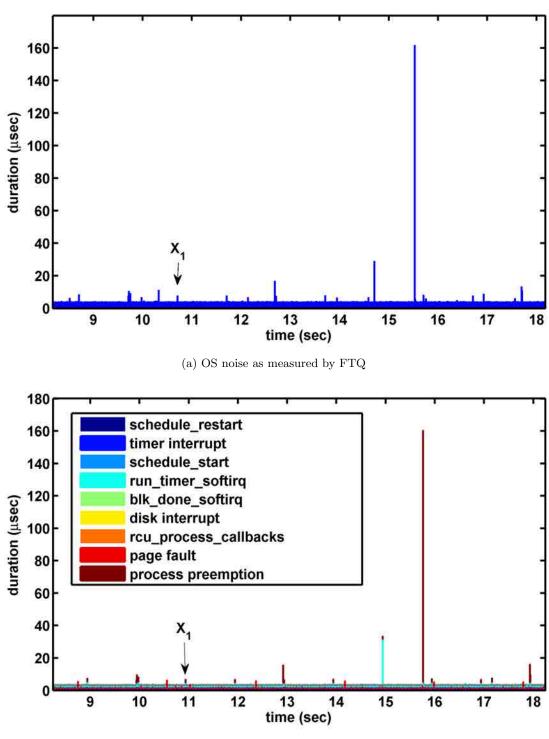

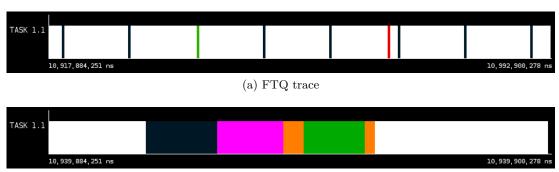

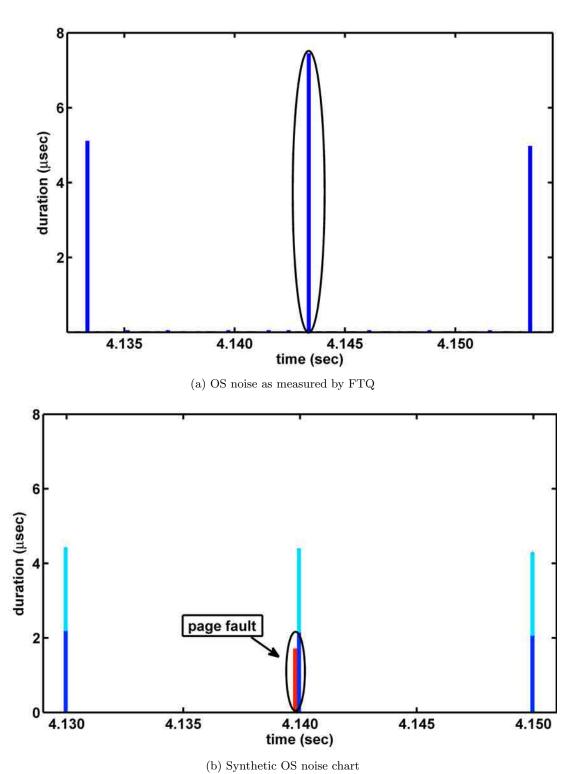

| 3.1 | Measuring OS noise using FTQ and LTTNG-NOISE. Figures 3.1a and 3.2a report the direct OS overhead obtained multiplying the execution time of a basic operation by the number of missing operations. | 37 |

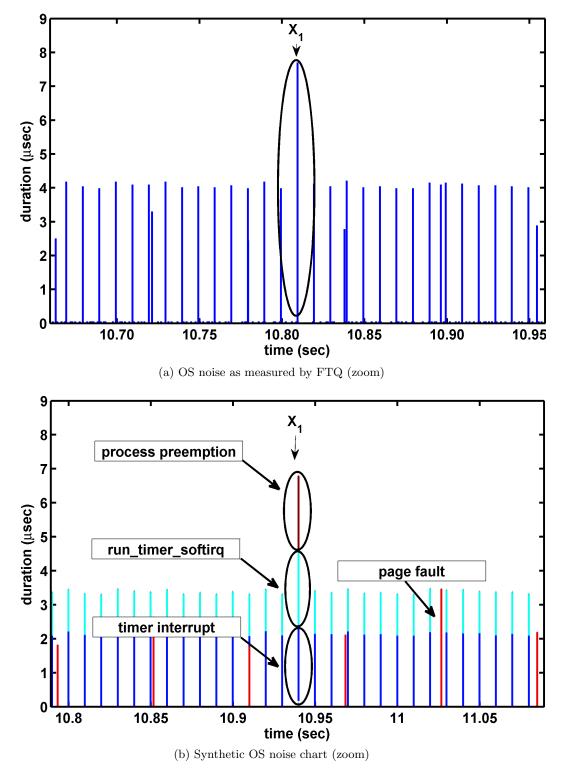

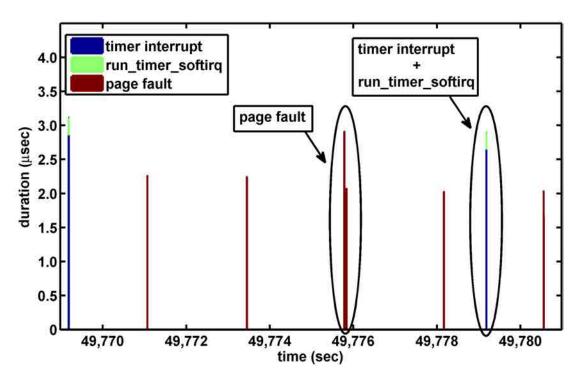

| 3.2 | Zoom on noise peak using FTQ and LTTNG-NOISE. Figures 3.1b and 3.2b report time as measured by LTTNG-NOISE.                                                                                         | 42 |

| 3.3  | FTQ Execution Trace. Figure 3.3a shows a part (75 $ms$ ) of the FTQ trace that highlights the periodic timer interrupts (black lines), the page faults (red line), and a process preemption (green line). Figure 3.3b zooms in and shows that the interruption consists of several kernel events. At this level of detail we can distinguish the timer interrupt (2.178 $\mu sec$ , |          |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|      | black) followed by the run_timer_softirq softirq (1.842 $\mu sec$ , pink), the                                                                                                                                                                                                                                                                                                      |          |

|      | first part of the schedule $(0.382 \mu sec, \text{ orange})$ , the process preemption                                                                                                                                                                                                                                                                                               |          |

|      | $(2.215 \ \mu sec, \text{ green})$ , and the second part of the schedule $(0.179 \ \mu sec,$                                                                                                                                                                                                                                                                                        |          |

|      | orange)                                                                                                                                                                                                                                                                                                                                                                             | 43       |

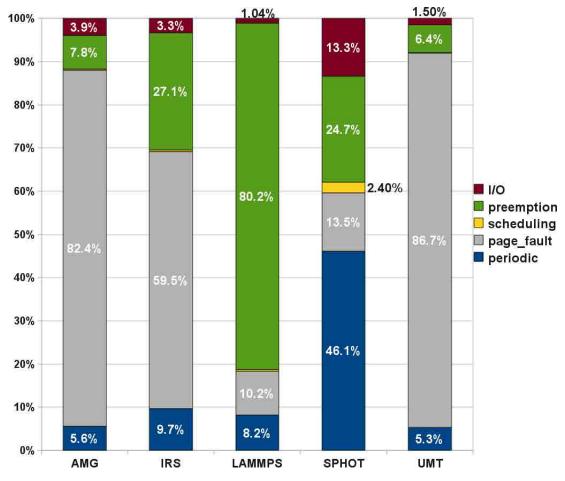

| 3.4  | OS noise breakdown for Sequoia benchmarks                                                                                                                                                                                                                                                                                                                                           | 45       |

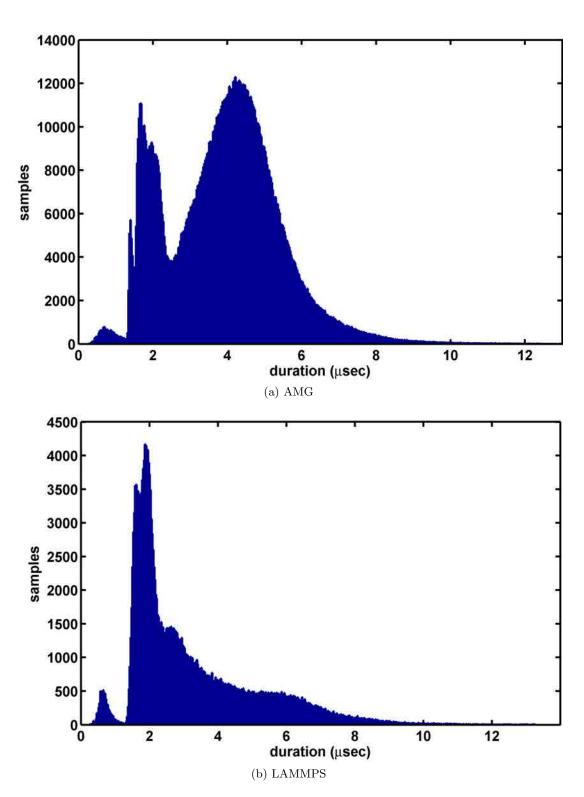

| 3.5  | Page fault time series                                                                                                                                                                                                                                                                                                                                                              | 47       |

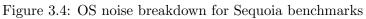

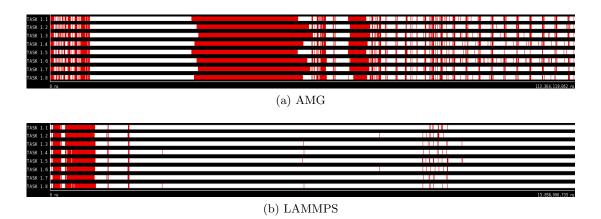

| 3.6  | Page Fault Trace. Figures 3.6a and 3.6b show the execution trace of                                                                                                                                                                                                                                                                                                                 |          |

|      | AMG and LAMMPS, respectively. We filtered out all the events but the                                                                                                                                                                                                                                                                                                                |          |

|      | page faults (red). The traces highlight the different distributions of page                                                                                                                                                                                                                                                                                                         |          |

|      | fault for AMG (throughout all the execution) adn LAMMPS (mainly                                                                                                                                                                                                                                                                                                                     |          |

|      | located at the beginning and the end). Notice that in some regions page                                                                                                                                                                                                                                                                                                             |          |

|      | faults are very dense and appear as one large page fault when, in fact,                                                                                                                                                                                                                                                                                                             |          |

|      | there are thousands very close to each other but the pixel resolution does                                                                                                                                                                                                                                                                                                          | 10       |

|      | not allow distinguishing them                                                                                                                                                                                                                                                                                                                                                       | 48       |

| 3.7  | Domain rebalance softirq time series                                                                                                                                                                                                                                                                                                                                                | 50       |

| 3.8  | Process preemption experienced by LAMMPS. This picture shows the                                                                                                                                                                                                                                                                                                                    |          |

|      | complete execution trace of LAMMPS. We filtered out all events but                                                                                                                                                                                                                                                                                                                  |          |

|      | process preemptions (green). Though the pixel resolution does not al-<br>low distinguishing all the process preemption, it is clear that LAMMPS                                                                                                                                                                                                                                     |          |

|      | suffers many frequent preemptions                                                                                                                                                                                                                                                                                                                                                   | 51       |

| 3.9  | run_timer_softirq time series                                                                                                                                                                                                                                                                                                                                                       | 54       |

|      | AMG - Synthetic OS noise graph                                                                                                                                                                                                                                                                                                                                                      | 55       |

|      | Noise disambiguation                                                                                                                                                                                                                                                                                                                                                                | 57       |

| 0.11 |                                                                                                                                                                                                                                                                                                                                                                                     | <b>.</b> |

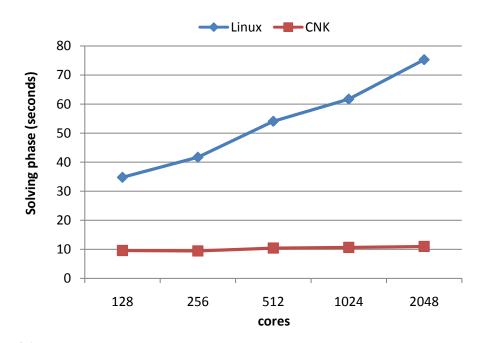

| 4.1  | Performance of AMG in weak scaling mode with a non-optimized version of Linux                                                                                                                                                                                                                                                                                                       |          |

|      | and with CNK on BG/P. This figure shows the effects of Linux system noise on AMG                                                                                                                                                                                                                                                                                                    |          |

|      | at scale: compared to CNK, Linux shows lower performance (3.62x with 128 cores)                                                                                                                                                                                                                                                                                                     |          |

|      | and limited scalability                                                                                                                                                                                                                                                                                                                                                             | 66       |

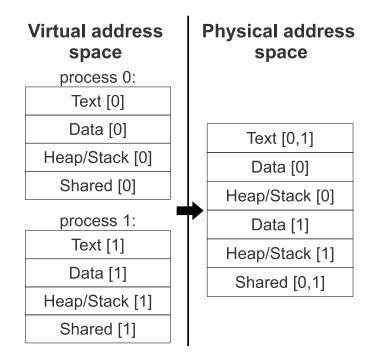

| 4.2  | Example of virtual-to-physical memory mapping for two MPI processes                                                                                                                                                                                                                                                                                                                 | <u> </u> |

|      | (SMP mode) in CNK.                                                                                                                                                                                                                                                                                                                                                                  | 67       |

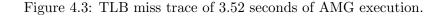

| 4.3  | TLB miss trace of 3.52 seconds of AMG execution                                                                                                                                                                                                                                                                                                                                     | 69       |

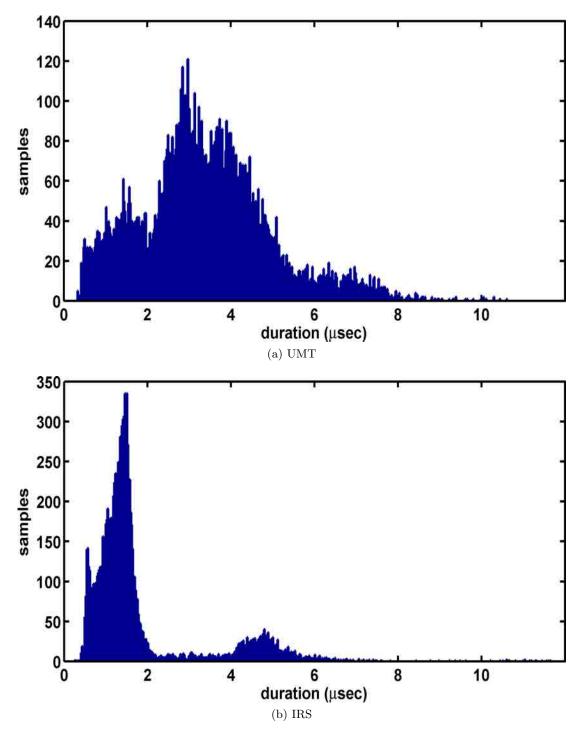

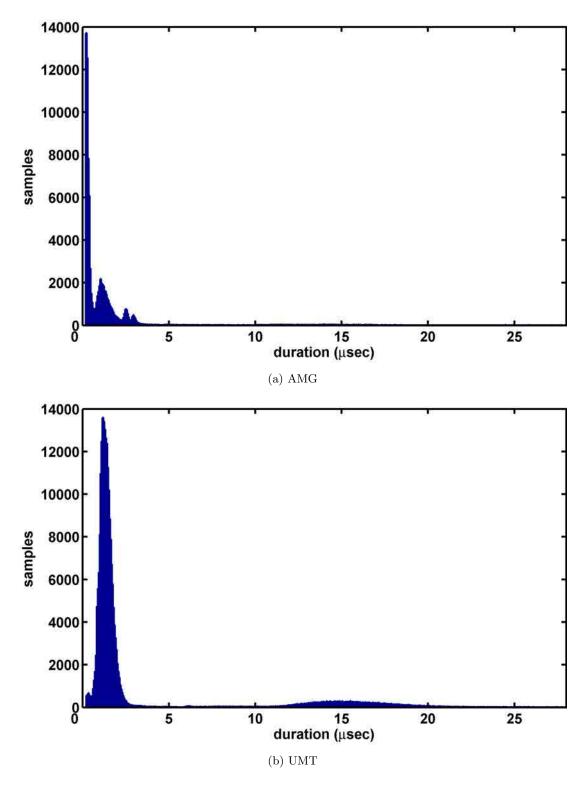

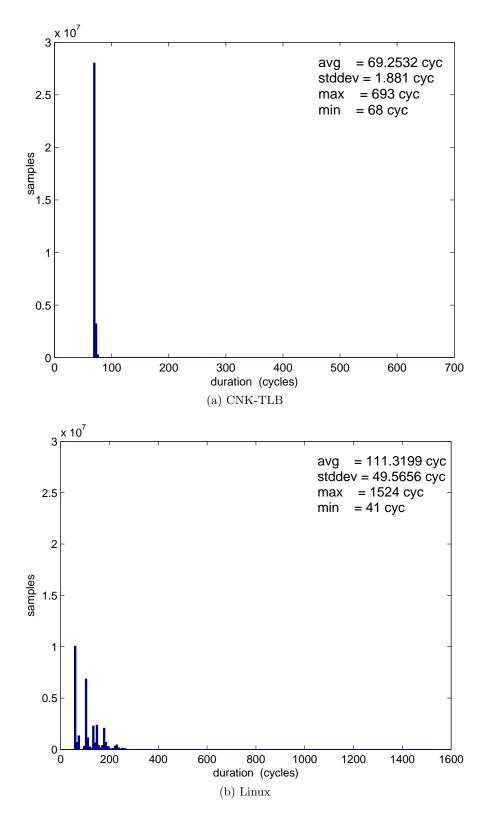

| 4.4 | TLB miss handler execution time distribution for CNK-TLB and Linux.                                                                         | 70  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------|-----|

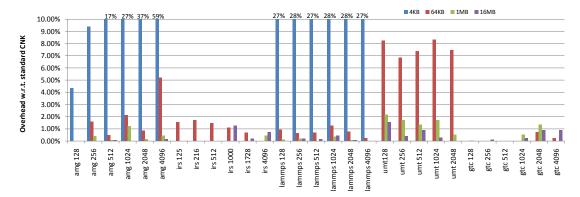

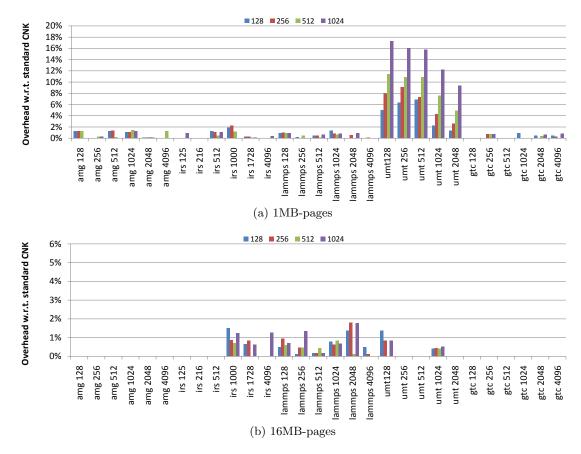

| 4.5 | TLB misses overhead with varying page sizes and concurrent cores. This graph shows that the overall overhead is below 2% for 16MB-pages for |     |

|     | all the applications while 1MB-pages only guarantee overhead below 2%                                                                       |     |

|     | for some application.                                                                                                                       | 74  |

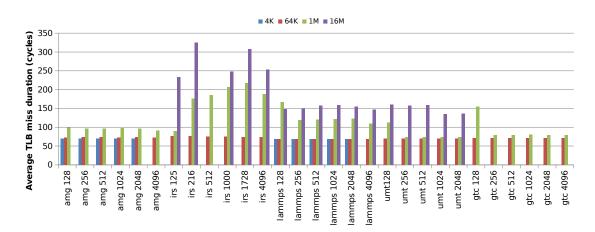

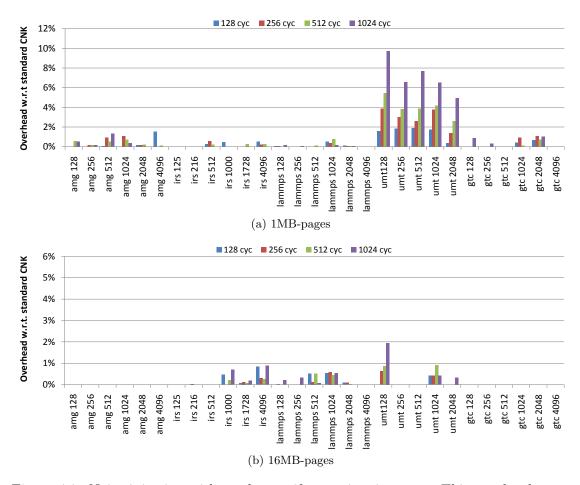

| 4.6 | TLB miss handler execution time with varying page sizes and concurrent                                                                      |     |

|     | cores. The graph shows that the time required to perform a virtual-to-                                                                      |     |

|     | physical translation in CNK-TLB changes depending on the page size                                                                          |     |

|     | (the larger the page, the longer the execution time), especially with pages                                                                 |     |

|     | larger than 64KB. The TLB miss handler execution time influences the                                                                        |     |

|     | applications' overall overhead. Missing 4K page bars refer to experiments                                                                   |     |

|     | that could not complete due to the high overhead with small pages (see                                                                      |     |

|     | Table 4.3). Also, the 1M page experiment with IRS is missing due to                                                                         |     |

|     | the very low number of TLB misses to sample (less than 1 TLB miss on                                                                        |     |

|     | average)                                                                                                                                    | 76  |

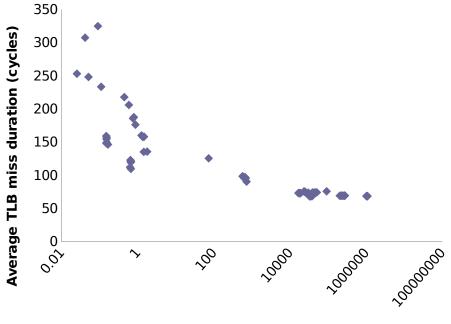

| 4.7 | Empirical relationship between TLB misses/second and TLB handler                                                                            |     |

|     | execution time: when the TLB pressure is low (less than 1 TLB mis-                                                                          |     |

|     | s/second) the probability of cache misses increases with the result that                                                                    |     |

|     | the TLB handler takes longer to complete                                                                                                    | 76  |

| 4.8 | Noise injection with constant noise signature. This graphs shows that                                                                       |     |

|     | the overall overhead of injecting TLB miss with a constant signature is                                                                     |     |

|     | below $2\%$ with 16MB-pages for all the applications. With 1MB-pages,                                                                       |     |

|     | instead, UMT shows considerable overhead                                                                                                    | 78  |

| 4.9 | Noise injection with random uniform noise signature. This graphs shows                                                                      |     |

|     | that the overall overhead of injecting TLB miss with a random uniform                                                                       |     |

|     | signature is below 2% with 16MB-pages for all the applications. With                                                                        |     |

|     | 1MB-pages, instead, UMT shows considerable overhead                                                                                         | 81  |

| 5.1 | Sequential queue-based BFS implementation                                                                                                   | 97  |

| 5.2 | Parallel BFS implementation with GMT                                                                                                        | 98  |

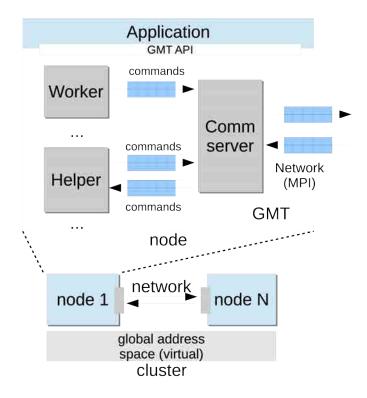

| 5.3 | Architecture overview of GMT                                                                                                                | 100 |

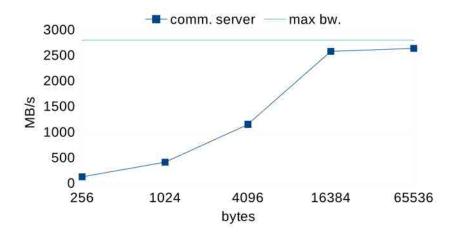

| 5.4 | Bandwidth between two nodes using a single Communication Server and                                                                         |     |

|     | a single worker with varying message size                                                                                                   | 103 |

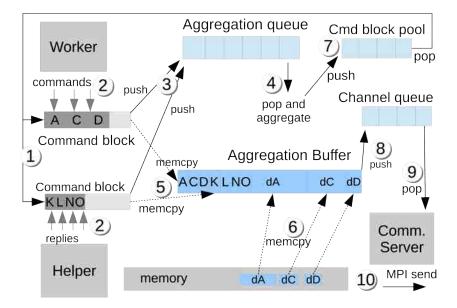

| 5.5 | Aggregation mechanism                                                                                                                       | 104 |

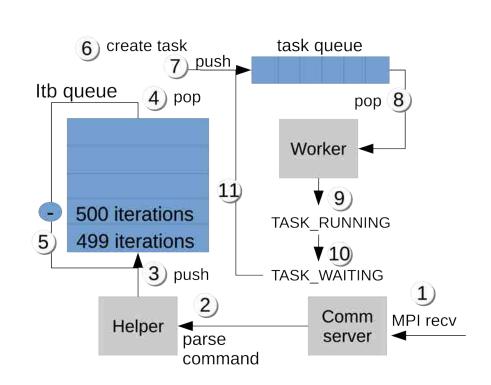

| 5.6 | Fine grain multithreading in GMT                                                                                                            | 107 |

#### LIST OF FIGURES

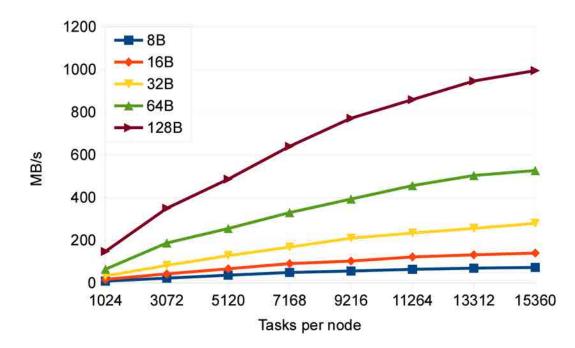

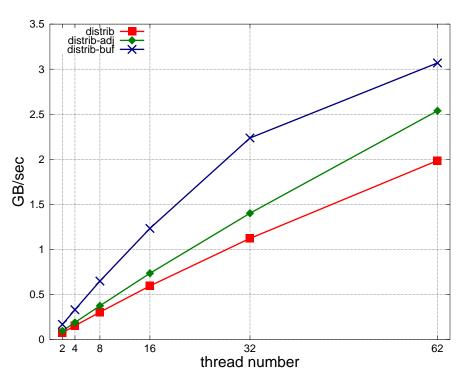

| 5.7  | Transfer rates of put operations between 2 nodes while increasing con-                                                                                                  |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | currency. Multiple lines show the transfer rate with message sizes from                                                                                                 |    |

|      | 8 bytes to 128 bytes                                                                                                                                                    | 09 |

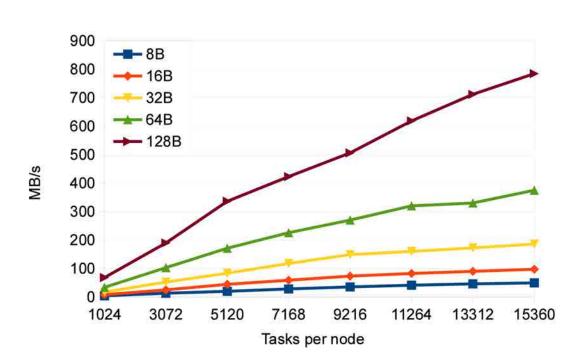

| 5.8  | Transfer rates of put operations among 128 nodes (one to all) while                                                                                                     |    |

|      | increasing concurrency. This is the transfer rate of the outgoing messages                                                                                              |    |

|      | from the source node. Multiple lines show the transfer rate with message                                                                                                |    |

|      | sizes from 8 bytes to 128 bytes                                                                                                                                         | 11 |

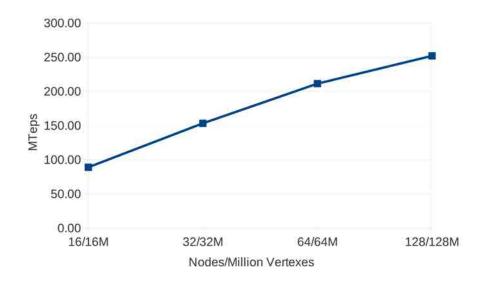

| 5.9  | Million traversed edges per second for the GMT implementation of the                                                                                                    |    |

|      | BFS (weak scaling)                                                                                                                                                      | 12 |

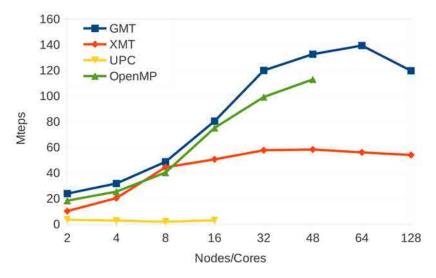

| 5.10 | Million traversed edges per second for the BFS implementation on GMT,                                                                                                   |    |

|      | UPC, Cray XMT, OpenMP (strong scaling). The horizontal scale for                                                                                                        |    |

|      | GMT, XMT and UPC represents cluster-nodes while for OpenMP rep-                                                                                                         |    |

|      | resents cores                                                                                                                                                           | 13 |

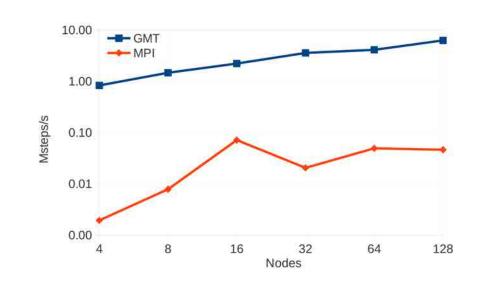

| 5.11 | Millions of steps per second for the random walk implementation on                                                                                                      |    |

|      | GMT and MPI (weak scaling)                                                                                                                                              | 15 |

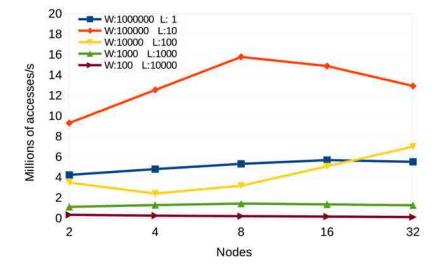

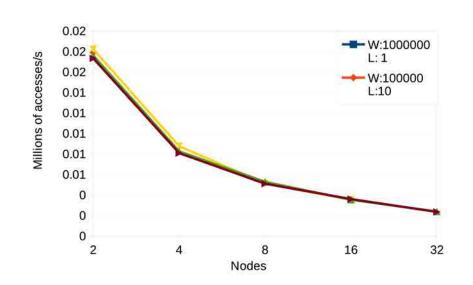

| 5.12 | Number of strings hashed and inserted per second (Millions of access-                                                                                                   |    |

|      | es/s) for the GMT implementation of the Concurrent Hash Map Access                                                                                                      |    |

|      | benchmark. In the legend, $W$ refers to the number of tasks and $L$ to the                                                                                              |    |

|      | number of accesses performed by each task                                                                                                                               | 16 |

| 5.13 | Number of strings hashed and inserted per second (Millions of access-                                                                                                   |    |

|      | es/s) for the MPI implementation of the Concurrent Hash Map Access                                                                                                      |    |

|      | benchmark. In the legend, $W$ refers to the number of processes and ${\cal L}$                                                                                          |    |

|      | to the number of accesses performed by each process                                                                                                                     | 17 |

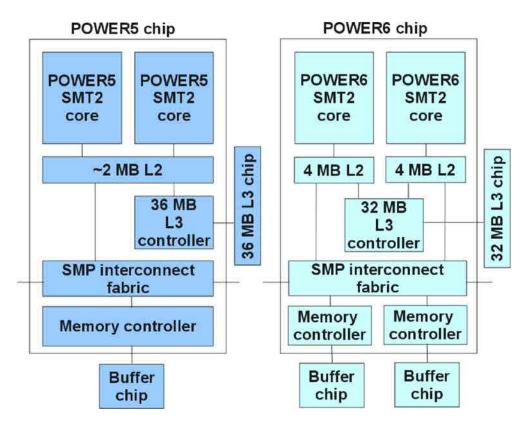

| 6.1  | POWER5 and POWER6 architecture                                                                                                                                          | 26 |

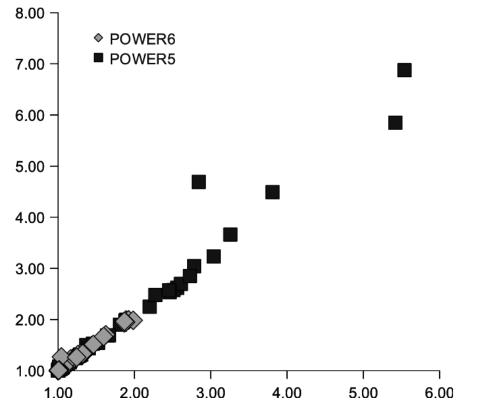

| 6.2  | Correlation between the IPC in ST mode normalized to the IPC in SMT mode                                                                                                |    |

|      | on y-axis $\left(\frac{IPC_{ST}}{IPC_{SMT}^{4/4}}\right)$ , and the malleability with priorities 6/2 on x-axis $\left(\frac{IPC_{SMT}^{6/2}}{IPC_{SMT}^{4/4}}\right)$ . | 36 |

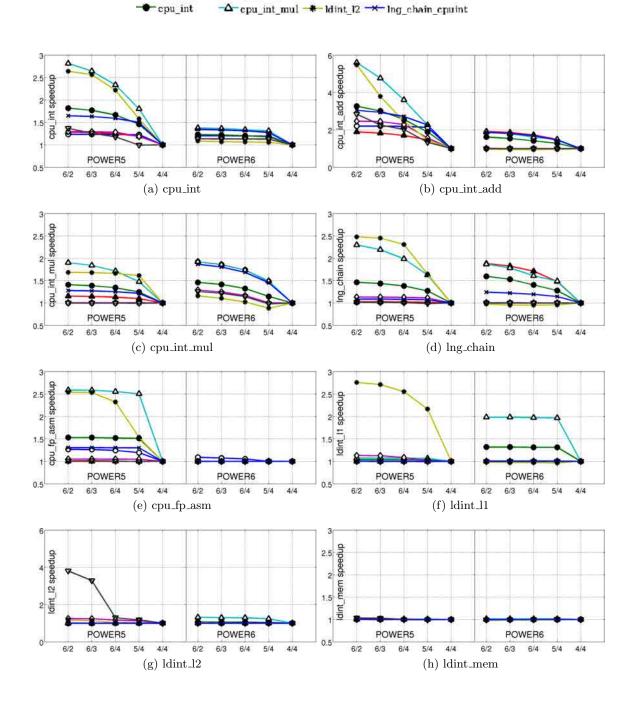

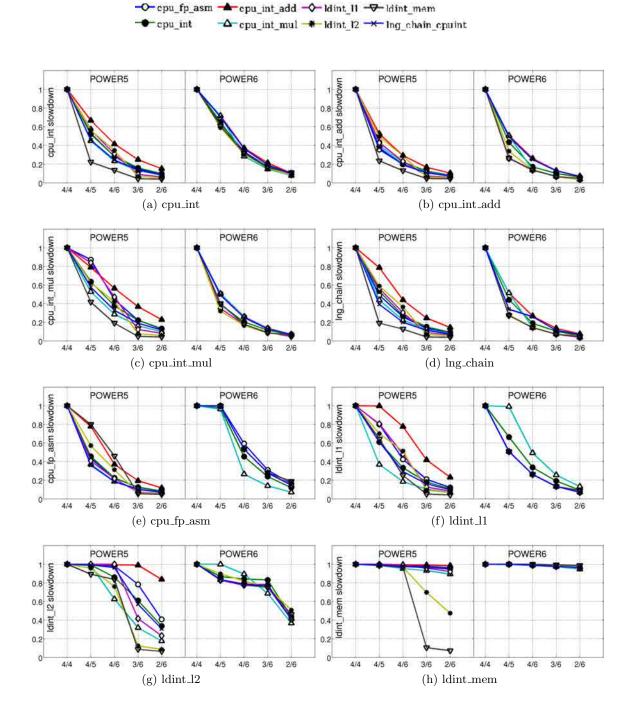

| 6.3  | Malleability of the primary thread when its priority is higher than the                                                                                                 |    |

|      | priority of the secondary thread. Y-axis reports $\frac{IPC_{SMT}^{P/Q}}{IPC_{SMT}^{4/4}}$ and X-axis is                                                                |    |

|      | the hardware priority for the primary and secondary threads ( <i>primary</i> -                                                                                          |    |

|      | $priority/secondary-priority$ ). Please note the different scale for $cpu_int_add$                                                                                      |    |

|      | and $ldint_l2$                                                                                                                                                          | 37 |

| 6.4  | Malleability of the primary thread when its priority is lower than the                                                                                                  |    |

|      | priority of the secondary thread. Y-axis reports $\frac{IPC_{SMT}^{P/Q}}{IPC_{SMT}^{4/4}}$ and X-axis is                                                                |    |

|      | the hardware priority for the primary and secondary threads ( <i>primary</i> -                                                                                          |    |

|      | priority/secondary-priority)                                                                                                                                            | 38 |

#### LIST OF FIGURES

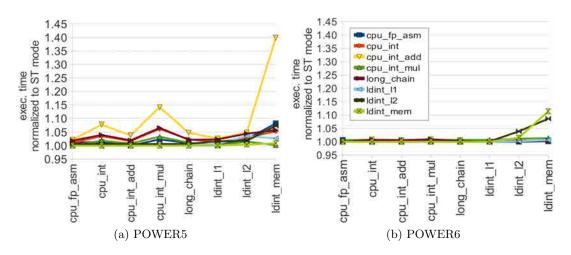

| 6.5  | Execution time of the primary thread running with priority 6 against                                     |

|------|----------------------------------------------------------------------------------------------------------|

|      | a secondary thread with priority 1, normalized to the execution time                                     |

|      | in single-thread mode. X-axis is the actual secondary thread micro-                                      |

|      | benchmark                                                                                                |

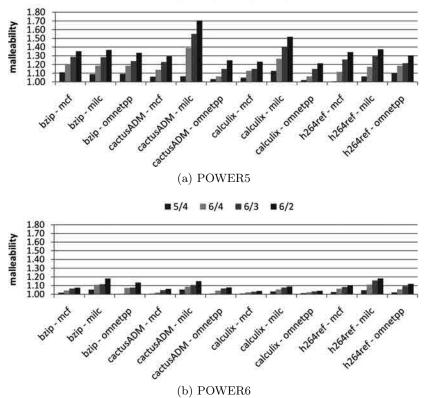

| 6.6  | Malleability of selected SPEC CPU2006 using higher priorities for the                                    |

|      | primary thread.Y-axis reports $\frac{IPC_{SMT}^{P/Q}}{IPC_{SMT}^{4/4}}$ and x-axis is the actual pair of |

|      | benchmarks running in SMT mode                                                                           |

| 6.7  | Transparent execution: percentage of the performance in single-thread                                    |

|      | mode for the foreground and the background threads. Y-axis reports                                       |

|      | $\frac{IPC_{SMT}^{P/Q}}{IPC_{ST}}$ × 100 and x-axis is the actual pair of benchmarks running in          |

|      | SMT mode with priorities 6 and 1                                                                         |

|      |                                                                                                          |

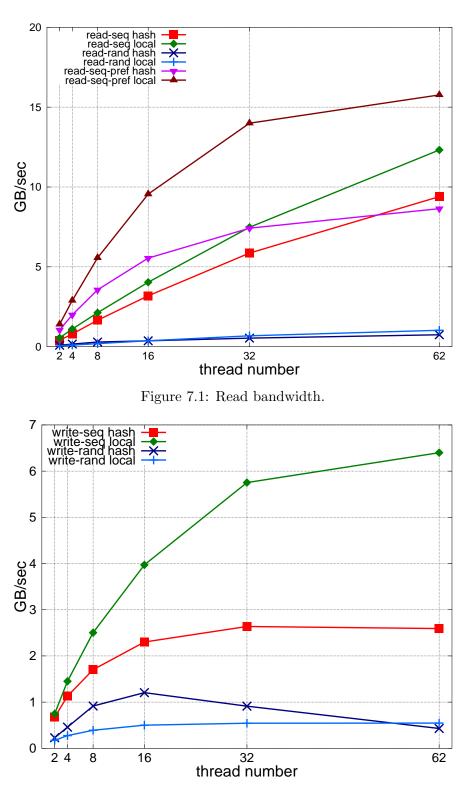

| 7.1  | Read bandwidth                                                                                           |

| 7.2  | Write bandwidth. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $155$                    |

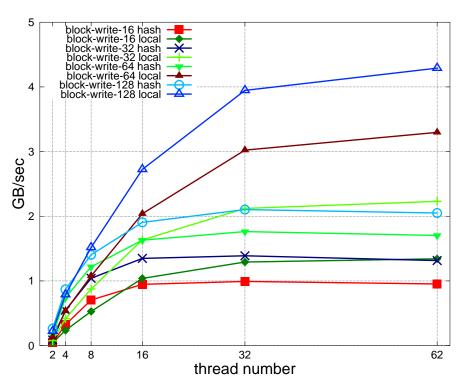

| 7.3  | Write bandwidth for larger chunks of data                                                                |

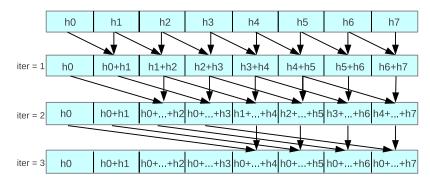

| 7.4  | Parallel prefix-sum with 8 threads                                                                       |

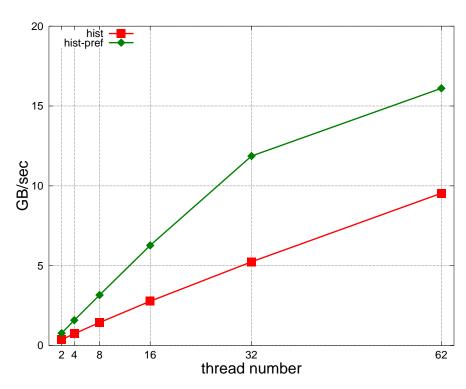

| 7.5  | Histogram computation bandwidth                                                                          |

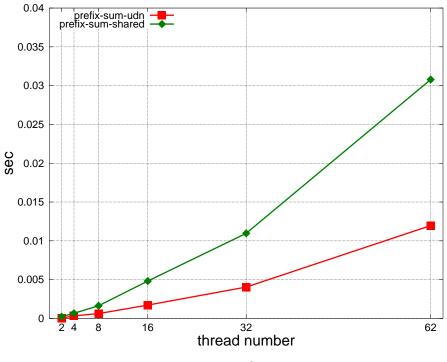

| 7.6  | Prefix sum                                                                                               |

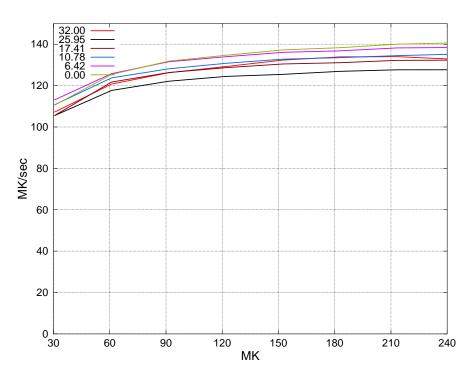

| 7.7  | Key distribution bandwidth                                                                               |

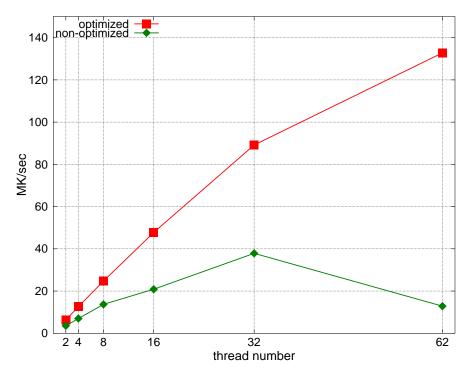

| 7.8  | Throughput with and without optimizations for the TILEPro64 processor. $168$                             |

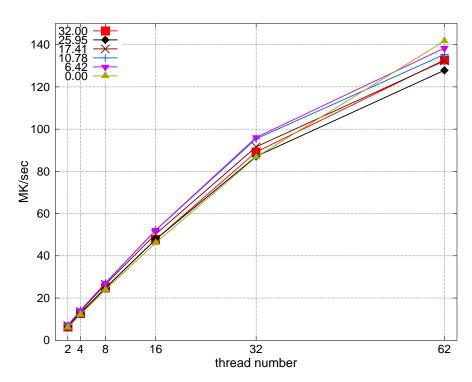

| 7.9  | Throughput with varying number of threads, 240 MK and striped allo-                                      |

|      | cations                                                                                                  |

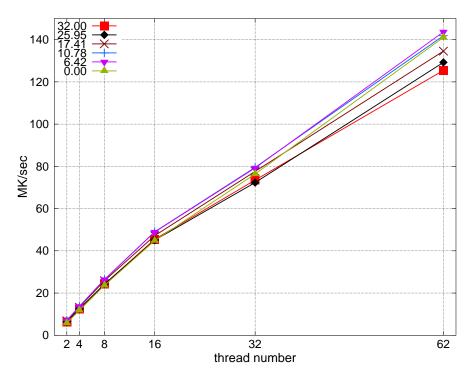

| 7.10 | Throughput with varying number of threads, 240 MK and allocations                                        |

|      | on specific memory controllers                                                                           |

| 7.11 | Throughput with varying dataset sizes and 62 threads                                                     |

Part I

# Introduction and Backround

### Chapter 1

### Introduction

In the last decades, high-performance large-scale systems have been a fundamental tool for scientific discovery and engineering advances. The sustained growth of supercomputing performance and the concurrent reduction in cost have made this technology available for a large number of scientists and engineers working on many different problems.

### 1.1 Challenges of Next-generation High-performance Largescale systems

Supercomputing performance has been growing at a faster pace than Moore's law, thanks to the ability to leverage systems scalability [10]. High Performance Computing (HPC) employs large clusters of multicore nodes, interconnected with a high-speed network. Today, scientific research and high-end technological firms leverage HPC computational resources to perform extremely complex computations in order to solve a large variety of problems. HPC is a necessary tool to face important scientific and technological challenges that might have a huge impact on human life. Some of the traditional HPC applications include: molecular dynamic, quantum chemistry, fluid dynamic, nuclear simulations. Besides traditional ones new applications are emerging, such as: improving therapy efficiency, extreme weather forecast, energy efficient aircraft design and material science analysis [25].

Furthermore, an entirely new paradigm of scientific discovery is emerging. The availability of large-scale models and simulations and the availability of very large instruments like colliders and light sources has generated a growing volume of scientific data [48]. This very large volume of data has the potential of further improving scientific

research and our understanding of many problems. Nonetheless, large-scale computing systems were not designed to handle such a high data volume and are currently not efficient in this task. The design of next-generation supercomputers will include traditional HPC requirements as well as the new requirements to handle data-intensive computations.

Data intensive applications will hence play an important role in a variety of fields, and are the current focus of several research trends in HPC. A particular class of dataintensive applications is the class of irregular applications [67]. Applications of this class are called irregular because they may have irregular memory access pattern, irregular network communication and irregular instruction control logic. The unpredictable network and data access pattern has a significant impact on performance. In fact, modern large-scale HPC machine are not optimized for this type of applications and their performance results sub-optimal [159]. A large number of relevant applications fall in this class: bioinformatics, big science applications, complex network analysis, community detection, data analytics, natural language processing, pattern recognition, semantic databases and, in general, knowledge discovery applications. The challenges to support this class of applications is affecting the design of next-generation HPC hardware and software. Large projects [153] have been following this approach. Current largescale systems focus around regular computations and data access patterns and exploit complex cache-based architectures to reduce data access latencies.

The solution to this kind of problems includes a complete redesign of the whole software stack. Being at the bottom of the software stack, the system software is expected to change drastically to support the upcoming hardware and to meet new application requirements [102].

Regarding the operating system (OS), two different approaches have been taken: on one side adapting a general purpose operating system (e.g. Linux), on the other side developing a specialized OS for HPC. The former solution leverages the large software ecosystem and experience available for general purpose OS (GPOS), while the latter solution guarantees better performance.

One of the drawbacks of using a GPOS is the difficulty of obtaining predictable performance [140]. Linux, for instance, is not designed to provide a constant predictable execution time to the applications. It features a variety of system services that can interrupt the application at any moment. This phenomena, called OS noise [137], has been frequently identified as an issue for large-scale systems. OS noise can, indeed, significantly reduce applications scalability. With a GPOS a detailed understanding of OS noise and its effects on applications performance is necessary. Once measured, OS noise can be reduced by re-configuring or modifying the OS.

Operating systems that are specialized for HPC do not show significant OS noise, because they are designed to be lightweight (so called lightweight kernels). Lightweight kernels (e.g. IBM CNK) guarantee predictable performance and optimal scalability [148]. The drawback of lightweight kernels is the lack of many features offered by a GPOS (e.g. full featured dynamic memory allocation).

Because of the need for a low-overhead and low-noise OS, many features traditionally provided by the OS are being moved into the runtime system. The runtime system, because of the higher knowledge of the running application, is the best candidate to provide services that depend on the application specific characteristics.

#### **1.2** Proposed approach and methodologies

Considered the challenges posed by the next-generation large-scale high-performance systems and applications, it is clear that system software needs to be significantly updated, if not redesigned. In this Thesis, we propose an approach to measure, design and implement scalable system software. The ideas behind this work are the following:

- Detailed measurement of system software overhead and its effect on scalability is necessary: obtaining scalable system software can be achieved only throughout a detailed measurement and understanding of system software performance, overhead, and their effect on real applications. Without a deep understanding of the sources of OS noise scalable system software is difficult to design [89].

- Adaptive system software: system software has to adapt to the changing hardware architecture and applications. The use of a standard, full-featured OS it is not a viable solution anymore. Similarly, the exclusive use of a minimal lightweight kernel is not the optimal solution to support the wide range of next-generation applications [135]. These two approaches have to be merged in a modular adaptive solution that can provide the benefits of both.

- The runtime system is the right candidate to provide highly scalable system services and to exploit low-level hardware optimizations: some of the system services traditionally provided by the OS have to be moved into the runtime system. As shown in Figure 1.1 next-generation runtime systems will include more system services and will exploit low level hardware features to optimize performance and power [13].

Services like scheduling, power management and data locality management can be effectively provided by the runtime system, with the advantage of specializing them for a particular class of applications (e.g. irregular applications). Moreover, the runtime system is the software layer that can better exploit hardware features provided by modern microprocessors such as on-chip communications and hardware thread priorities. This approach allows the implementation of highly adaptive system software to face the scalability and power efficiency challenges of the next-generation large-scale machines [58]. Exploiting low-level hardware features such as fine-grain cache locality management, core-to-core communications and hardware thread priorities can significantly improve application performance. Nonetheless, optimizing a single application can require considerable effort. The runtime system, on the other hand, has detailed knowledge of the application behavior and requirements. For this reason, the runtime system is one of the best options to implement the optimization logic that exploit low-level hardware features to optimize an entire class of applications.

Figure 1.1: Next-generation runtime systems will include additional system services and exploit low-level hardware features to optimize an entire class of applications.

#### **1.3** Thesis contributions

This Thesis address the problem of evaluating and designing scalable system software for large-scale system. This work starts by addressing the scalability issues of the OS, first regarding GPOS and then regarding lightweight kernels. Subsequently, we focus on the runtime system. For shared memory systems we show how a runtime system can be effectively used to improve data locality on emerging many-core architecture. Finally, we implement a runtime system for distributed memory systems that includes many of the system services required by next-generation applications. The contribution of this thesis are as follows:

#### 1. Operating System Scalability

We provide an accurate study of the scalability problems of modern Operating Systems for HPC.

**OS noise measurement and tracing:** We design and implement a methodology whereby detailed quantitative information may be obtained for each OS noise event. We validate our approach by comparing it to other well-known standard techniques to analyze OS noise, such FTQ (Fixed Time Quantum [154]). We provide a case study in which we use our methodology to analyze the OS noise when running benchmarks from the Lawrence Livermore National Lab (LLNL) Sequoia applications.

**Evaluation of the address translation management:** we provide an applesto-apples comparison of different TLB management approaches — dynamic memory mapping, static memory mapping with replaceable TLB entries, and static memory mapping with fixed TLB entries (no TLB misses) — on a real BG/P system with up to 1024 nodes (4096 cores).

#### 2. Runtime System Scalability

We show that a runtime system can efficiently incorporate system services and improve scalability for a specific class of applications.

Design and implementation of a runtime library to efficiently execute irregular applications on a commodity cluster: we design and implement a full-featured runtime system and programming model to execute irregular applications on a commodity cluster. The runtime library is called Global Memory and Threading library (GMT) and integrates a locality-aware Partitioned Global Address Space communication model with a fork/join program structure. It supports massive lightweight multithreading, overlapping of communication and computation and small messages aggregation to tolerate network latencies. We compare GMT to other PGAS models, hand-optimized MPI code and custom architectures (Cray XMT) on a set of large scale irregular applications: breadth first search, random walk and concurrent hash map access. Our runtime system shows performance orders of magnitude higher than other solutions on commodity clusters and competitive with custom architectures.

#### 3. User-level Scalability Exploiting Hardware Features

We show the high complexity of low-level hardware optimizations for single applications, as a motivation to incorporate this logic into an adaptive runtime

#### system.

**Exploiting hardware multi-thread priorities in multithreaded architectures:** we evaluate the effects of controllable hardware-thread prioritization mechanism that controls the rate at which each hardware-thread decodes instruction on IBM POWER5 and POWER6 processors.

Exploting cache-locality and network-on-chip to optimize sorting in many-core architectures: we show how to effectively exploit cache locality and network-on-chip on the Tilera many-core architecture to improve intra-core scalability.

#### 1.4 Thesis structure

The thesis is divided into four parts:

**Part I** includes the Introduction and Chapter 2 that provides the background for this work.

**Part II** addresses the scalability problems of modern Operating Systems for HPC. Chapter 3 describes the methodology to perform the detailed measurement of OS noise for a GPOS, Chapter 4 describes the evaluation of the address translation management for lightweight kernels.

**Part III** describes the issues of designing a specialized runtime system to improve a specific class of applications. Chapter 5 describes a runtime system and a programming model to efficiently execute irregular application on a commodity cluster.

**Part IV** shows that implementing optimization at user-level can require considerable programming effort, suggesting that the runtime should be used to implement this logic. Chapter 6 shows the potential hardware thread priorities to improve several target metrics for various applications on POWER5 and POWER6 processors. Chapter 7 how a radix sort kernel implemented for an emerging many-core architecture can be optimized using hardware features like data locality management and network-on-chip. The final Chapter concludes summarizing the work presented in this thesis and proposing some possible future work.

### Chapter 2

# Background: current trends in High Performance Computing

This chapter introduces concepts that will be further expanded in the following chapters. In particular, this chapter describes the current technology trends, the characteristics of future exascale and big-data applications and the system software enabling those application to scale on future systems.

#### 2.1 Technology trends

The last two decades witnessed an exponential growth of extreme scale systems performance. As Moore's law states, transistor densities double every 18 months. Industry has been following Moore's law to deliver more powerful processors every year. Leveraging the Moore's law and employing large-scale parallelism, supercomputer performance managed to grow even faster than processor performance.

Figure 2.1 shows the exponential growth of supercomputing power as recorded by the TOP500 [10]. From the early nineties GFlop systems to current PFlop systems, the sustained growth rate of supercomputers performance has been two times the growth rate of Moore's law.

This impressive performance growth as been possible because of several concurrent factors, including: sustained increase of processor performance, reduction of network latency, increment of network and memory bandwidth. If this growth rate continues, the next generation of supercomputers should be able to deliver a performance in the order of  $10^{18}$  floating point operations per seconds (ExaFlop). The design of a new generation of supercomputers, called *Exascale* generation, is the object of large

## 2. BACKGROUND: CURRENT TRENDS IN HIGH PERFORMANCE COMPUTING

#### Performance Development

Figure 2.1: Exponential growth of supercomputing power as recorded by the TOP500 [10] - #1 refers to the first in the list, #500 refers to the 500th and Sum is the sum of all supercomputers in the list.

part of current research in HPC. The joint efforts of several institutions to design an Exascale supercomputer are the driving force behind many new development in computer architecture, operating systems, runtime systems, programming models, and large scale applications. Exascale systems will be the results of current technology trends meeting with application requirements, and leveraging the lessons learned from more than two decades of supercomputing. For this reason, observing the direction technology trends is a consistent and necessary approach to do sensible research in HPC. In the context of this research efforts, the Defense Advanced Research Projects Agency (DARPA) produced the first comprehensive study on the challenges in achieving HPC systems with ExaFlop performance [24]. The study concluded that there are four challenges to build exascale supercomputers:

- 1. The Energy and Power Challenge: Today it does not exist a technology able to deliver sufficiently powerful systems at connected wattages well below 100 MW. From a political-economic perspective has been suggested a power threshold of 20 MW, even though an exact power consumption constraint is not yet defined.

- 2. The Memory and Storage Challenge: There is a lack of mature memory and storage technologies that will be able to fulfil the I/O bandwidth requirements of future exascale systems within an acceptable power envelope.

- 3. The Concurrency and Locality Challenge: The end of increasing single thread processing performance and the trend towards many-core processing elements pose challenges to achieve the expected level of parallelism. Projections for exascale systems indicate that future applications may have to support more than a billion of separate threads in order to efficiently use the hardware.

- 4. The Resilience Challenge: This challenge is related to the explosive growth in the number of components in a supercomputer as well as the need to use advanced technology at extreme voltage and temperature operating points. Individual devices and circuits will become more and more sensitive to operating environments and hence resiliency and reliability will be of utmost importance.

The expected technology trends toward exascale computing is summarized in Table 2.1. As shown in Table 2.1, performance of various components of today extremescale systems are expected to grow at different rate. This is a major game changer for the design and implementation of extreme-scale systems, compared to today's systems. Dennard scaling states that while transistor size decreases (Moore's law) power density remains constant, so the transistor power usage decreases too. In the last decade

| Metric               | 2012          | 2015                                | exascale              | $\operatorname{growth}$ |

|----------------------|---------------|-------------------------------------|-----------------------|-------------------------|

| System Peak [PF]     | 25            | 200                                 | 1000                  | 100                     |

| Power [MW]           | 6-20          | 15-50                               | 20-80                 | 10                      |

| System Memory [PB]   | 0.3 - 0.5     | 5                                   | 32-64                 | 100                     |

| Memory per Core [GB] | 0.5 - 2       | 0.2-1                               | 0.1 - 0.5             | 1/10                    |

| Node Perf. [GF]      | $160 - 10^3$  | $500-7 \times 10^4$                 | $10^3 - 10^4$         | $10 - 10^3$             |

| Cores/Node           | 16-32         | 100-1,000                           | $10^3 - 10^4$         | $100 - 10^3$            |

| Node Mem. BW [GB/s]  | 70            | $100-10^3$                          | $400-4 \times 10^{3}$ | 100                     |

| Number of nodes      | $10^4 - 10^5$ | $5 \times 10^{3} - 5 \times 10^{4}$ | $10^4 - 10^5$         | 10-100                  |

| Total Concurrency    | $O(10^6)$     | $O(10^7)$                           | $O(10^9)$             | $10^{4}$                |

2. BACKGROUND: CURRENT TRENDS IN HIGH PERFORMANCE COMPUTING

Table 2.1: Technology trends from current systems to ExaFlops systems [25]. Column growth refers to the expected growth from 2012 to exascale.

days

O(1 day)

O(1 day)

1/10

MTTI

Dennard scaling ended and was evident that power density could not be maintained constant as transistor sizes were decreasing [64]. This implied a paradigm shift, because performance could not anymore be obtained with higher clock frequencies. Processor design started to change, from single core to multi and many core architectures. Because of this paradigm shift, modern applications need to exploit thread-level parallelism to compensate for the lack of single-core performance. New processors are expected to have hundreds to thousands cores and to leverage hardware multi-threading. As a consequence, the available memory per core is decreasing. While performance in older system was dependent mostly on computational power (i.e., FLOPS) this is not the case for exascale. Data-movement across the system, through the memory hierarchy and even for register-to-register operations is expected to be the main contributor to energy consumption.

Figure 2.2 shows the energy cost of data communication between several parts of the system. The cost of register access is lower than the cost of a double precision floating point operation. Nonetheless off-chip communications produce an increase in energy consumption of two orders of magnitude.

#### 2.2 Scientific and large-scale applications

Scientific applications are becoming more and more vital to do research in a wide variety of scientific fields. Besides experimentation, simulation is today one of the fundamental methodologies of modern scientific research. Through simulation of physical systems scientists can validate hypothesis and make prediction with an increasing level of ac-

Figure 2.2: Energy consumption for data communication, difference between today and in 2018 [24]

curacy. Simulations are an opportunity not only for scientific research but also for a large number of industrial and service sectors such as Energy, Aeronautic, Mechanic, Finance and Health. Scientific applications are commonly developed by domain experts with a basic knowledge of the languages and programming models available on their systems. Most of the scientific applications end to be very complex codes, because of the necessity to solve complex scientific problems in the shortest possible time.

The European Exascale Software Initiative (ESSI) enumerates several grand challenges for exascale computing [25]. These challenges could improve the state of the art of many scientific medical and engineering problems. Some of the grand challenges identified by the ESSI are:

- Therapy efficiency: genetic sequencing is quickly becoming a primary tool to identify and prevent health risks for a growing number of diseases. The improvement of sequencing instruments by a factor of 10<sup>3</sup> to 10<sup>6</sup> it will make possible to integrate genomic data into clinical trials. This will have a huge impact on drug development and therapies. This will be possible only if exascale systems will enable the management of ExaBytes of sequencing data.

- Extreme Weather Forecast: Computational modeling is a necessary tool to

integrate with physical earth observations to better understand the weather processes. The accuracy of computational models has a direct impact on the ability of predicting natural hazard and foster policy-making for risk-mitigation. Uncertainty quantification also plays a central role in evaluating the potential outcomes of extreme natural events. The economic, social and environmental impacts of this challenge are enormous.

- Greening the Aircraft: as energy is becoming a huge issue for every aspect of the social and economic life, future air transportation systems will have to reduce their energy consumption and their impact on the environment. These reductions include a reduction of emission by 50% and a decrease of external noise level by 10-20 dB (known as the vision-2020 plan).

- Materials: exascale is expected to bring major changes also in the Material science. Focus of simulations is expected to shift from a qualitative description of basic phenomena to the numerical optimization and quantitative analysis of soft material properties, micro-structural evolution and chemistry-driven problems.

#### 2.2.1 Big data and exascale computing

In the 20th century, simulation has been referred as the *third paradigm* of scientific discovery, theory and experimentation being the first two. Large-scale scientific simulations have in fact enabled deep understanding of physical systems where experimentation is difficult, hazardous, or very expensive. Enabling this new paradigm of scientific discovery has fostered the design of state of the art HPC systems and software, driving research in computer science and engineering. The availability of large-scale models and simulation and the availability of large instruments like telescopes, colliders and light sources has generated a growing volume of scientific data. Computing resources to move, analyze and manage this exponentially growing volume of data is becoming the next big challenge [48], commonly referred as *big data*. The efforts to extract knowledge from large scientific dataset is considered today the *fourth paradigm* of scientific discovery. Because of the increasing velocity, heterogeneity, and volume of the data generated, extracting knowledge from large datasets is becoming a key aspect of science.