# IMPROVING THE EFFECTIVE USE OF MULTITHREADED ARCHITECTURES: IMPLICATIONS ON COMPILATION, THREAD ASSIGNMENT, AND TIMING ANALYSIS

Petar Radojković

Barcelona, 2013

A thesis submitted in fulfillment of the requirements for the degree of DOCTOR OF PHILOSOPHY / DOCTOR PER LA UPC

> Department of Computer Architecture Technical University of Catalonia

# IMPROVING THE EFFECTIVE USE OF MULTITHREADED ARCHITECTURES: IMPLICATIONS ON COMPILATION, THREAD ASSIGNMENT, AND TIMING ANALYSIS

## Petar Radojković

Barcelona, 2013

Thesis director: Francisco J. Cazorla Almeida

Barcelona Supercomputing Center and Spanish National Research Council (IIIA-CSIC)

Thesis co-directors: Javier Verdú

Universitat Politècnica de Catalunya

Alex Pajuelo

Universitat Politècnica de Catalunya

Mario Nemirovsky

ICREA Research Professor

at Barcelona Supercomputing Center

A thesis submitted in fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY / DOCTOR PER LA UPC

Department of Computer Architecture Technical University of Catalonia

# **Abstract**

Currently, multithreaded architectures are the mainstream in the processor design. They are widely used in servers, desktop computers, lap-tops, and mobile devices. Multithreaded processors are a very good solution for exploiting processor performance beyond the limitations imposed by limited instruction-level parallelism and power wall. They deliver superior performance and higher performance-per-watt ratio than single-threaded architectures for a given target throughput.

On the other hand, multithreaded architectures introduce several challenges at the software level. In order to utilize the hardware potential optimally and to deliver maximum performance, state-of-the-art multithreaded architectures have to execute numerous software threads simultaneously. At the operating system level, one of the main challenges becomes how to schedule simultaneously-running software threads. Also, the need for numerous software threads motivates the development of multithreaded applications and algorithms. Development of efficient, portable, and correct multithreaded software requires novel programming models and paradigms, and increases the complexity of compilers. In time-critical environments (real-time systems), the timing analysis has to estimate the impact of the collision in shared hardware resources between simultaneously-running threads on the execution time of each thread.

In this thesis, we present cross-domain approaches that improve the effective use of multithreaded architectures. First, we demonstrate the importance of scheduling of network applications running in state-of-the-art multithreaded servers, and propose several methods that improve it. We further analyze optimizations that improve the compilation of multithreaded applications. In particular, we analyze the problem of graph partitioning that is a part of the compilation process of multithreaded streaming applications. Finally, we analyze the impact of shared resources in multithreaded processors in time-critical environments. Our study provides a systematic method for measurement-based timing analysis of applications running on multithreaded architectures.

# Acknowledgments

The work presented in this thesis was done mostly at Barcelona Supercomputing Center (BSC), Barcelona, Spain. BSC provided financial support and access to resources that were indispensable for our research. Our work was also supported by the Ministry of Science and Innovation of Spain (contract number TIN-2007-60625), HiPEAC European Network of Excellence on High Performance and Embedded Architecture and Compilation, Sun Microsystems Inc. (now Oracle), and Thales Research and Technology.

Petar Radojković holds the FPU grant AP2008-02370 (Programa Nacional de Formación de Profesorado Universitario) of the Ministry of Education of Spain. During his secondary education and undergraduate studies, Petar Radojković received several grants from Ministry of Education of Republic of Serbia.

The work related to evaluation of multithreaded Commercial-Off-The-Shelf processors in time-critical environments was done mostly during the author's internship at Embedded Systems Lab, Thales Research and Technology, Palaiseau, Paris area, France (December 2010 - March 2011). The internship was funded by HiPEAC. In 2008, Petar Radojković spent three months at Netra DPS group, Sun Microsystems Inc., Menlo Park, California, US. The internship was funded by HiPEAC and "Real-time Chip Multithreading systems" project between BSC and Sun Microsystems Inc.

Professional development of the author was monitored and consulted by Grupo Psicoac S.L., Barcelona.

I would like to thank my advisers for their time and patience. This dissertation could not have been written without their help and guidelines.

Personal gratitude to my advisers, and gratitude to colleagues, friends, and family will be expressed in person. This is the only way for me to do it sincerely and without censorship. The ones who helped me to become who I am deserve no less.

# **Contents**

| Al | ostrac |                                                              | i   |

|----|--------|--------------------------------------------------------------|-----|

| A  | cknov  | edgments                                                     | iii |

| In | dex    |                                                              | ix  |

| 1  | Intr   | duction                                                      | 1   |

|    | 1.1    | Challenges for the effective use of multithreaded            |     |

|    |        | processors                                                   | 2   |

|    |        | 1.1.1 Process scheduling                                     | 3   |

|    |        | 1.1.1.1 Thread assignment of network applications            | 4   |

|    |        | 1.1.1.2 Importance of the thread assignment                  | 5   |

|    |        | 1.1.1.3 Intractability of the thread assignment problem      | 6   |

|    |        | 1.1.2 Compilation of multithreaded streaming applications    | 8   |

|    |        | 1.1.3 Multithreaded processors in time-critical environments | 10  |

|    | 1.2    | Thesis contributions                                         | 12  |

|    |        | 1.2.1 Thread assignment on multithreaded processors          | 12  |

|    |        | 1.2.2 Kernel partitioning of streaming applications          | 13  |

|    |        | 1.2.3 Multithreaded processors in time-critical environments | 14  |

|    | 1.3    | Thesis structure                                             | 14  |

| 2  | Exp    | rimental setup                                               | 17  |

|    | 2.1    | UltraSPARC T2 processor                                      | 18  |

|    | 2.2    | Netra DPS                                                    | 19  |

|    | 2.3    | Benchmarks                                                   | 20  |

|    |        | 2.3.1 Overview                                               | 20  |

|    |        | 2.3.2 Implementation                                         | 23  |

|   | 2.4   | Methodology                                                                  | 24 |  |

|---|-------|------------------------------------------------------------------------------|----|--|

| 3 | Thre  | read assignment of multithreaded network applications on multicore/multithro |    |  |

|   | proc  | cessors                                                                      | 25 |  |

|   | 3.1   | Introduction                                                                 | 25 |  |

|   | 3.2   | Background                                                                   | 26 |  |

|   | 3.3   | Thread assignment methods                                                    | 27 |  |

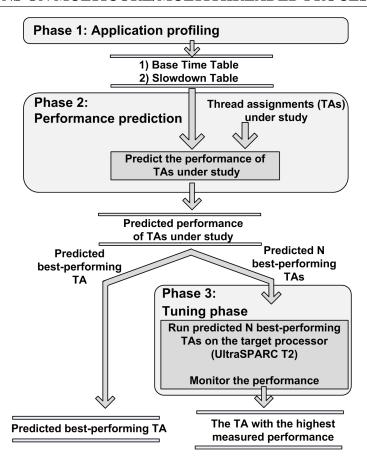

|   |       | 3.3.1 TSBSched                                                               | 30 |  |

|   |       | 3.3.1.1 Phase 1: Application profiling                                       | 30 |  |

|   |       | 3.3.1.2 Phase 2: Performance prediction                                      | 33 |  |

|   |       | 3.3.1.3 Phase 3: Selection phase                                             | 36 |  |

|   |       | 3.3.1.4 TSBSched limitations                                                 | 37 |  |

|   |       | 3.3.2 BlackBox scheduler                                                     | 38 |  |

|   |       | 3.3.2.1 Phase 1: Application profiling                                       | 39 |  |

|   |       | 3.3.2.2 Phase 2: Performance prediction                                      | 40 |  |

|   |       | 3.3.2.3 Phase 3: Selection phase                                             | 42 |  |

|   |       | 3.3.3 Scalability of the thread assignment methods                           | 42 |  |

|   | 3.4   | Evaluation                                                                   | 44 |  |

|   |       | 3.4.1 Exploration space                                                      | 45 |  |

|   |       | 3.4.2 Six software threads                                                   | 47 |  |

|   |       | 3.4.3 Nine software threads                                                  | 49 |  |

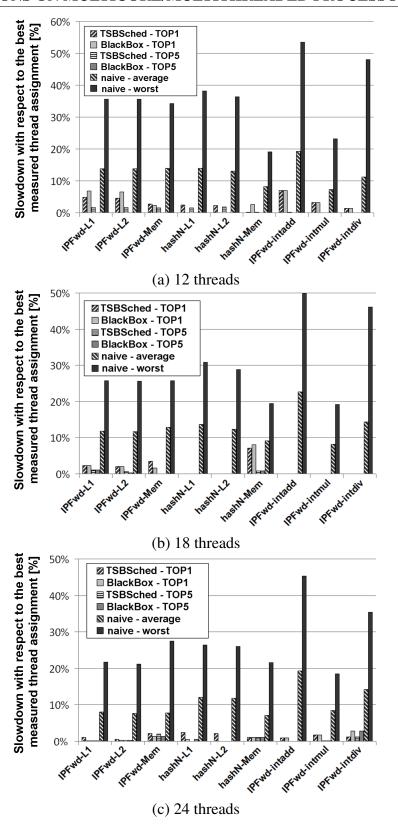

|   |       | 3.4.4 12, 18, and 24 software threads                                        | 51 |  |

|   | 3.5   | Related Work                                                                 | 54 |  |

|   | 3.6   | Summary                                                                      | 56 |  |

| 4 | A sta | atistical approach to thread assignment problem                              | 59 |  |

|   | 4.1   | Introduction                                                                 | 60 |  |

|   | 4.2   | Motivation and background                                                    | 61 |  |

|   | 4.3   | A statistical approach to the thread assignment                              |    |  |

|   |       | problem                                                                      | 63 |  |

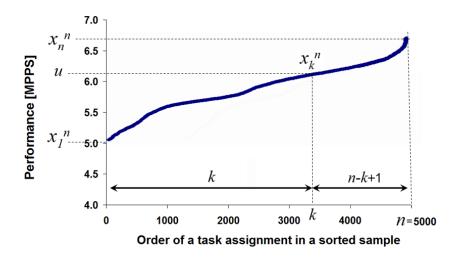

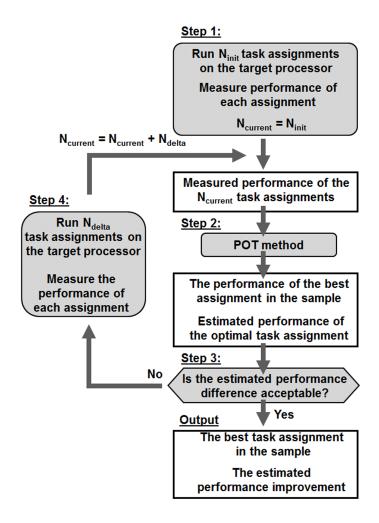

|   |       | 4.3.1 Finding thread assignments with a good performance                     | 64 |  |

|   |       | 4.3.2 Cumulative Distribution Function                                       | 65 |  |

|   |       | 4.3.3 Estimation of the optimal performance                                  | 66 |  |

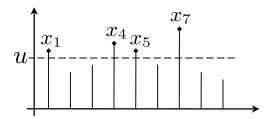

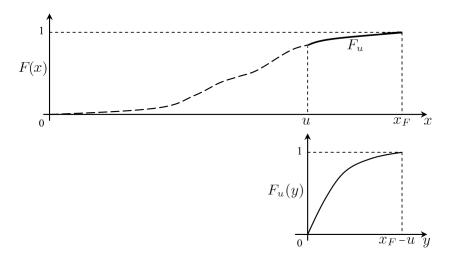

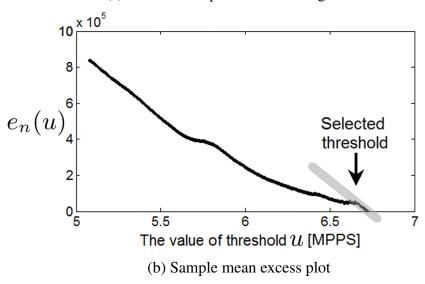

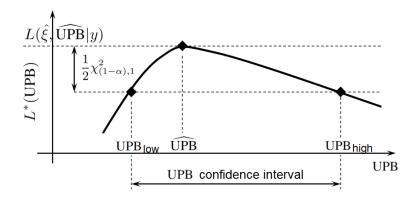

|   |       | 4.3.3.1 Extreme value theory                                                 | 67 |  |

|   |       | 4.3.3.2 Application of Peak Over Threshold method                            | 69 |  |

# **CONTENTS**

|   |      | 4.3.4     | Summary of the statistical analysis                                | . 74  |

|---|------|-----------|--------------------------------------------------------------------|-------|

|   | 4.4  |           | 8                                                                  |       |

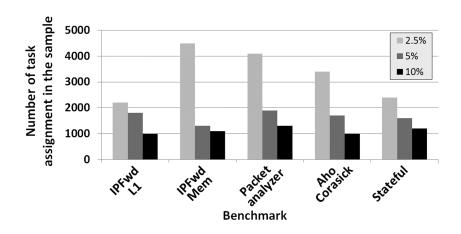

|   | 1. 1 | 4.4.1     | Finding thread assignments with good performance                   |       |

|   |      | 4.4.2     | Estimation of the optimal performance                              |       |

|   |      | 4.4.3     | Case study                                                         |       |

|   |      | 4.4.4     | Other Considerations                                               |       |

|   | 4.5  | Relate    | d work                                                             |       |

|   | 4.6  | Summ      | ary                                                                | . 83  |

| 5 | A st | atistical | l approach to kernel partitioning of streaming applications        | 85    |

|   | 5.1  | Introd    | uction                                                             | . 86  |

|   | 5.2  | Backg     | round                                                              | . 88  |

|   |      | 5.2.1     | Target metric                                                      | . 88  |

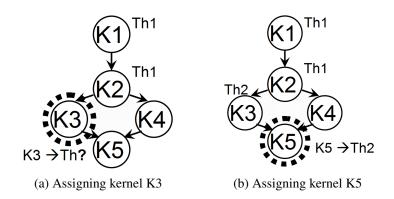

|   |      | 5.2.2     | Convexity constraint                                               | . 88  |

|   | 5.3  | Sampl     | ing methods                                                        | . 89  |

|   |      | 5.3.1     | Depth-First Search (DFS)                                           | . 90  |

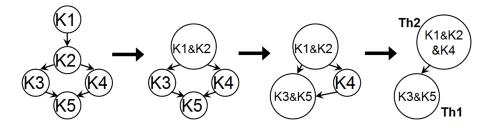

|   |      | 5.3.2     | Edge Contraction (EC)                                              | . 90  |

|   |      | 5.3.3     | Edge Contraction with Filter (EC-F)                                | . 91  |

|   |      | 5.3.4     | Uniformly Distributed (UD) sampling                                | . 92  |

|   |      | 5.3.5     | Statistical <i>i.i.d.</i> tests                                    | . 93  |

|   | 5.4  | A stati   | stical approach to kernel partitioning of streaming applications . | . 94  |

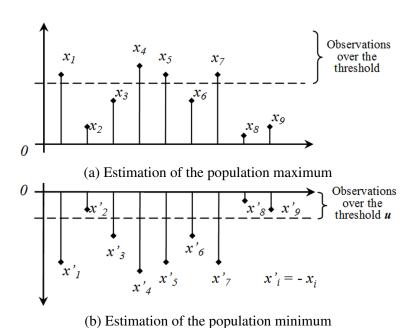

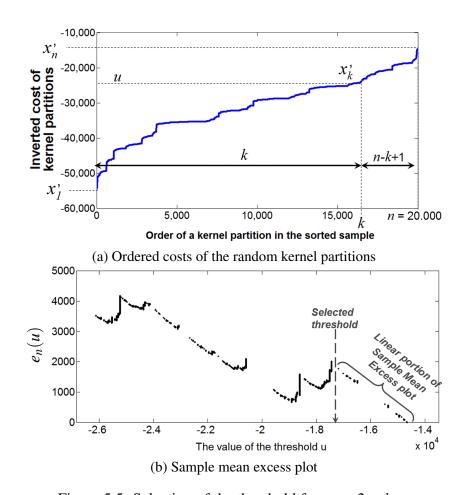

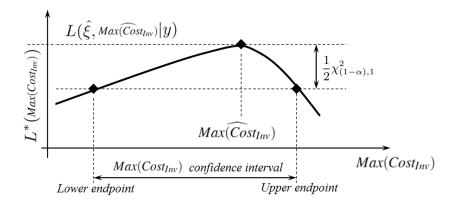

|   |      | 5.4.1     | Application of Peak Over Threshold method                          | . 96  |

|   | 5.5  | Result    | s                                                                  | . 101 |

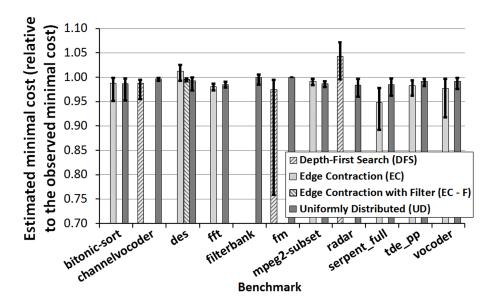

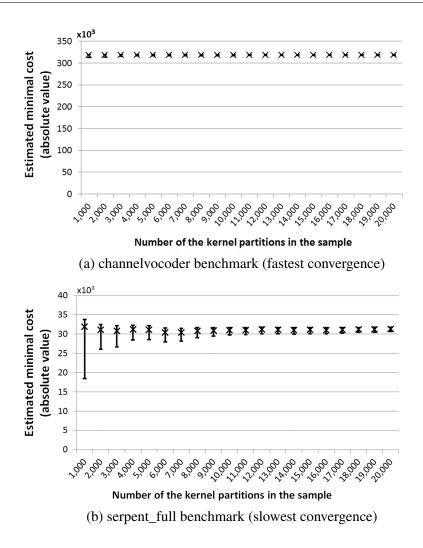

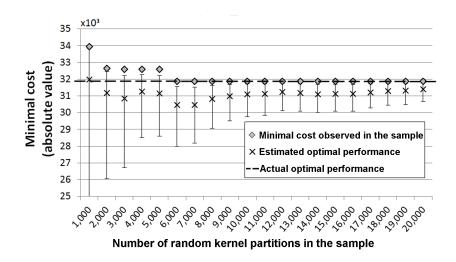

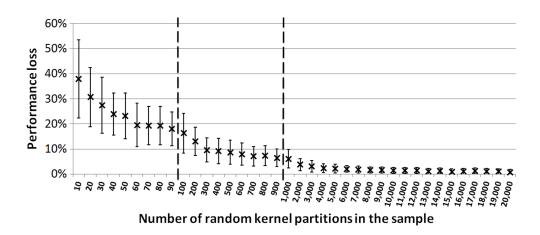

|   |      | 5.5.1     | Estimation of the minimal cost using the POT method                | . 102 |

|   |      | 5.5.2     | Precision of the estimation                                        | . 103 |

|   |      | 5.5.3     | Accuracy of the estimation                                         | . 106 |

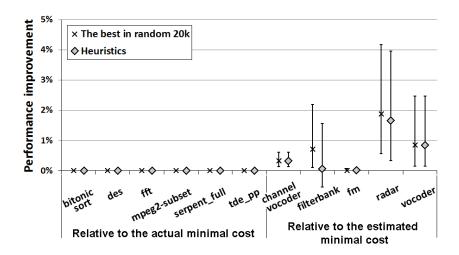

|   |      | 5.5.4     | Random sampling approach to a kernel partitioning                  | . 108 |

|   |      | 5.5.5     | Other considerations                                               | . 111 |

|   | 5.6  | Relate    | d Work                                                             | . 113 |

|   | 5.7  | Summ      | ary                                                                | . 114 |

| 6 | Eval | luation   | of the impact of shared resources in multithreaded COTS proce      | es-   |

|   | sors | in time   | e-critical environments                                            | 117   |

|   | 6.1  | Introd    | uction                                                             | . 118 |

|   | 6.2  | Δnalve    | sis of Inter-Task Interferences in current MT processors           | 122   |

|   |     | 6.2.1    | Worst-interference benchmark                                 |

|---|-----|----------|--------------------------------------------------------------|

|   |     | 6.2.2    | Resource-stressing benchmarks                                |

|   |     | 6.2.3    | Implementation                                               |

|   |     | 6.2.4    | Using the resource-stressing benchmarks                      |

|   |     |          | 6.2.4.1 Worst-case slowdown in shared processor resources 13 |

|   |     |          | 6.2.4.2 WCET estimation for real applications                |

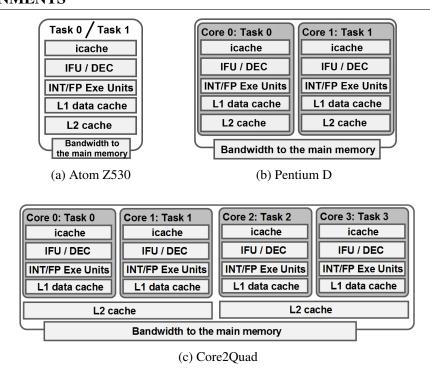

|   | 6.3 | Experi   | mental Environment                                           |

|   |     | 6.3.1    | Hardware environment                                         |

|   |     | 6.3.2    | Benchmarks                                                   |

|   |     | 6.3.3    | Experimental methodology                                     |

|   | 6.4 | Evalua   | tion                                                         |

|   |     | 6.4.1    | Potential execution time variation                           |

|   |     | 6.4.2    | Application sensitivity to resource sharing                  |

|   |     | 6.4.3    | WCET estimation                                              |

|   |     | 6.4.4    | Mixed stressing workloads                                    |

|   |     | 6.4.5    | Additional considerations                                    |

|   | 6.5 | Relate   | d Work                                                       |

|   | 6.6 | Summ     | ary                                                          |

| 7 | Con | clusions | s 14                                                         |

|   | 7.1 | Thesis   | contributions                                                |

|   |     | 7.1.1    | Thread assignment on multithreaded processors                |

|   |     | 7.1.2    | Kernel partitioning of streaming applications                |

|   |     | 7.1.3    | Multithreaded processors in time-critical environments 15    |

|   | 7.2 | Future   | work                                                         |

|   |     | 7.2.1    | Thread assignment                                            |

|   |     | 7.2.2    | Kernel (graph) partitioning                                  |

|   |     | 7.2.3    | Statistical analysis                                         |

|   |     | 7.2.4    | Timing analysis of multithreaded processors                  |

|   | 7.3 | Publica  | ations                                                       |

|   |     | 7.3.1    | Conferences                                                  |

|   |     | 7.3.2    | Journals                                                     |

|   |     | 7.3.3    | Posters                                                      |

|   |     | 7.3.4    | Other publications                                           |

# CONTENTS

| 7.4 Awards      |     |

|-----------------|-----|

| Bibliography    | 161 |

| List of Figures | 177 |

| List of Tables  | 179 |

| Glossary        | 181 |

# Chapter 1

# Introduction

In the past, at the hardware level, two essential techniques were used to improve the processor performance: increasing the operating frequency (frequency scaling) and improving the processor design (mostly at microarchitecture level). Because of improvements in the transistor implementation technology, the number of transistors on the die duplicated in each processor generation [112]. Additional transistors were used mainly to improve single-threaded processor performance. Each new generation of the processors had deeper and more complex pipelines, more complex prediction engines, and larger on-chip cache memories. Although the manufacturing technology continues to improve and to provide significantly larger number of transistors in each new generation, there are two primary obstacles for additional development of single-threaded processors:

- Power wall: The power consumption of the processor scales super-linearly with the working frequency (clock rate) [79]. High power consumption causes several problems. First, it is becoming complex to supply the die with the required electrical current (required power). Second, cooling-down of the die becomes more difficult. Power dissipation has reached the limitation of the reliable processor operation. Third, energy consumption is an important portion of the maintenance cost of IT systems.

- Limited Instruction Level Parallelism (ILP): Data and control dependencies limit ILP. It is increasingly difficult to find sufficient parallelism in the instructions stream of a single process to use hardware resources of single-threaded processors effectively [79].

# 1.1. CHALLENGES FOR THE EFFECTIVE USE OF MULTITHREADED PROCESSORS

Limited ILP and the power wall motivated the design of multithreaded<sup>1</sup> processors. In multithreaded architectures, the transistors provided by the technology improvement are used to build multiple processing engines that can simultaneously execute different software threads. The main idea behind multithreaded processors is to use simpler processing engines working on a lower frequency, to deliver moderate single-threaded, but superior overall performance. Currently, multithreaded architectures are the mainstream in the processor design. They are widely used in servers, desktop computers, lap-tops, and mobile devices.

In addition to ILP, which is still exploited for each software thread independently, multithreaded processors increase the system throughput by exploiting Thread Level Parallelism (TLP). State-of-the-art multithreaded architectures exploit different TLP paradigms. The most commonly used ones are Simultaneous Multithreading (SMT), Fine-Grain Multithreading (FGMT), and Chip-Multiprocessing (CMP). Also, most of the high-end multithreaded processors such as the Sun UltraSPARC T1 [6, 7], T2 [8, 9], and T4 [13], the IBM POWER5 [142], POWER6 [101], and POWER7 [12] and the Intel core i7 [14], combine different TLP paradigms on a singe die. This allows better utilization of the hardware resources and improves the overall system performance.

# 1.1 Challenges for the effective use of multithreaded processors

Multithreaded processors are a very good solution for exploiting processor performance beyond the limitations imposed by limited ILP and power wall. They deliver superior performance and higher performance-per-watt ratio than single-threaded architectures for a given target throughput [79]. However, on the other hand, multithreaded architectures introduce several challenges at the software level. In order to utilize the hardware potential optimally, and to deliver maximum performance, state-of-the-art multithreaded architectures have to execute numerous software threads simultaneously. At the operating system level, one of the main challenges becomes how to schedule concurrently-running

<sup>&</sup>lt;sup>1</sup> In this thesis, we will use the term "multithreaded processor" to refer to any processor that can execute more than one thread simultaneously. Chip-Multiprocessors, Simultaneous Multithreading, Coarse-grain Multithreading, Fine-Grain Multithreading processors or any combination of them are multithreaded processors.

software threads [141]. Also, the need for numerous threads<sup>2</sup> motivates the development of multithreaded applications and algorithms. Development of efficient, portable, and correct multithreaded software requires novel programming models and paradigms, and increases the complexity of compilers. In time-critical environments (real-time systems), the timing analysis has to estimate the impact of the collision in shared hardware resources between simultaneously-running tasks on the execution time of the tasks.

In this thesis, we present cross-domain approaches that improve the effective use of multithreaded architectures. First, we demonstrate the importance of scheduling of network applications running in state-of-the-art multithreaded servers, and propose several methods that improve it. We further analyze optimizations that improve the compilation of multithreaded applications. In particular, we analyze the problem of graph partitioning that is a part of the compilation process of multithreaded streaming applications. Finally, we present a method that improves the analysis of the timing behavior or real-time applications executed in multithreaded architectures. The method quantifies the slowdown that simultaneously-running tasks may experience due to collision in shared processor resources.

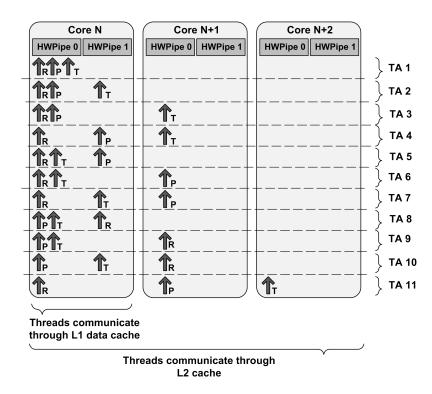

# 1.1.1 Process scheduling

In multithreaded processors, concurrently-running (co-running) threads share and compete for hardware resources. The collision of co-running threads in shared processor hardware resources affects the execution time of the threads and the overall system performance. Moreover, state-of-the-art multithreaded processors have different *levels of resource sharing* [154]. For example, in a CMP processor where each core supports the concurrent execution of several threads through SMT, all simultaneously-running threads share global resources such as the last level of cache memory or the I/O. In addition to this, threads running in the same core share resources such as the Instruction Fetch Unit, or the L1 instruction and data cache. Therefore, the way that threads are assigned to cores determines which resources they share, which, in turn, may significantly affect the system performance.

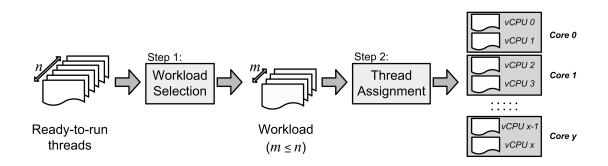

In processors with several levels of resource sharing, thread scheduling is comprised of two steps (see Figure 1.1). In the first step, usually called *workload selection*, the

<sup>&</sup>lt;sup>2</sup> In this thesis, we use the term "thread" to refer to a software i.e. application thread. Words "software thread", "application thread", "thread", and "task" are used interchangeably. When we refer to a hardware context of the processor, we also use the terms "hardware thread", "strand", "logical CPU", and "virtual CPU".

# 1.1. CHALLENGES FOR THE EFFECTIVE USE OF MULTITHREADED PROCESSORS

Figure 1.1: Process scheduling in multithreaded processors with several levels of resource sharing: *Workload selection* and *Thread assignment*

operating system (OS) selects the set of threads (workload) that will be executed in the processor in the next time slice, from a set of ready-to-run threads. In the second step, called *thread assignment*, each thread in the workload is assigned to a hardware context (virtual CPU, vCPU) of the processor.

### 1.1.1.1 Thread assignment of network applications

In this thesis, we address the problem of thread assignment of network applications running on massive multithreaded processors that can execute tens of software tasks concurrently. The importance of network applications constantly increases with the continuous growth of the Internet traffic and the number and the complexity of the services that these applications provide. In order to provide high-speed processing and high throughput, network applications have specific hardware and operating system requirements.

In networking, the traffic is composed of numerous packets from different users that can be processed at a time. Massively multithreaded processors like UltraSPARC T2 support concurrent execution of multiple threads that can process concurrently the packets with no data dependencies. This makes massively multithreaded processors particularly well suited for the networking systems.

At the operating system level, network-oriented systems require runtime environments that provide high performance, high-speed packet processing, and execution time predictability. In order to address these requirements, network-oriented systems use low-overhead runtime environments that minimize the impact of the system management tasks to the application performance [11]. In networking environments, applications continuously process different packets repeating similar processing algorithm for each packet. As applications running on network processors provide a constant set of services and pro-

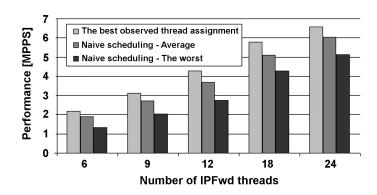

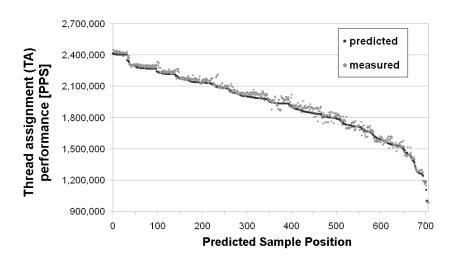

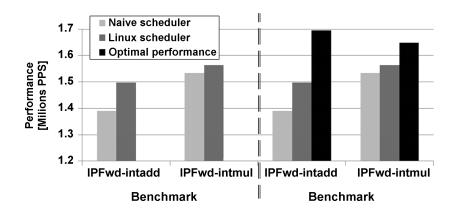

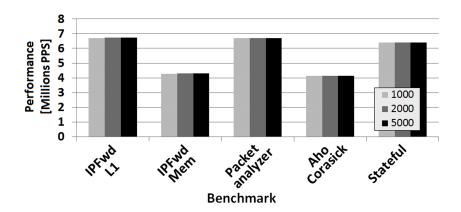

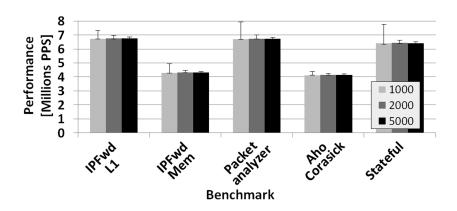

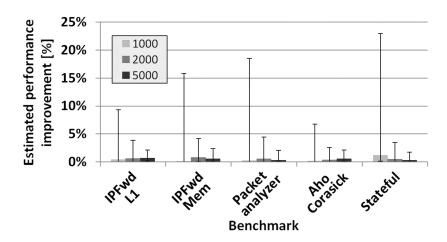

Figure 1.2: Performance of the IPFwd benchmark

cess different packets in a similar manner, a dynamic thread scheduling is not required. In addition to this, the workload running in network processor is usually known beforehand and does not change at runtime. Therefore, the most promising way to improve the performance of network applications running on massive multithreaded processors is to determine a close-to-the-optimal thread assignment, which is the focus of our study.

### 1.1.1.2 Importance of the thread assignment

In order to illustrate the importance of the thread assignment of network applications, we execute several workloads composed of multithreaded IP Forwarding (IPFwd) application [11] in different thread assignments on the UltraSPARC T2 processor. We executed experiments with 2, 3, 4, 6, and 8 IPFwd instances. Each IPFwd instance is comprised of three threads, Receiving, Processing, and Transmitting, that process the packets in a pipelined manner<sup>3</sup>. Thus, the workload was composed of 6, 9, 12, 18, and 24 IPFwd threads. We could not execute more than 24 IPFwd threads (8 IPFwd instances) simultaneously because of the limitation in the experimental environment. The on-chip Network Interface Unit (NIU) of the UltraSPARC T2 processor used in the study can split the incoming network traffic into up to eight DMA channels, and we could bind at most one receiving thread (at most one IPFwd instance) to each DMA channel.

In each set of the experiments, we executed and measured the performance of between 700 and 1500 different thread assignments (see Section 2.4). The results of the experiments are presented in Figure 1.2. The X-axis of the figure shows the number of threads in the workload, while the Y-axis shows the system performance in processed Millions of Packets Per Second (MPPS).

<sup>&</sup>lt;sup>3</sup>IPFwd application is described in detail in Section 2.3.

# 1.1. CHALLENGES FOR THE EFFECTIVE USE OF MULTITHREADED PROCESSORS

The figure presents three groups of bars. Bar 'The best observed thread assignment' shows the performance of the best observed thread assignment for each number of IPFwd threads. Bars 'Naive scheduling-Average' and 'Naive scheduling-The worst' show the average and the worst performance of the naive thread assignment, the technique that randomly distributes the running threads among the processor cores and hardware pipelines of the processor. The results presented in Figure 1.2 show that thread assignment has a significant impact on the system performance. The average performance loss of naive scheduling with respect to the performance of the detected best-performing thread assignment ranges from 290,000 PPS (six IPFwd threads) to 680,000 PPS (18 threads). The worst detected performance loss of naive tasks assignment ranges up to 1.5 million PPS (12 threads), which represent the degradation of 35%.

By choosing a given thread assignment, we implicitly decide which hardware resources are shared between concurrently-running (co-running) threads. State-of-the-art OSs, like Linux and Solaris, use load balancing mechanism [15][149] to distribute the load of the running processes among all the available logical CPUs (*i.e.* cores in a CMP architecture or hardware contexts in a SMT architecture). Also, cache and TLB affinity algorithms [15][149] try to keep threads in the same logical CPU to reduce cache misses and page faults as much as possible. Although these characteristics improve performance, they do not fully exploit the capabilities of the current multithreaded processors with several levels of resource sharing. The main drawback of the thread assignment algorithms used in current OSs is that they do not consider the hardware requirements of each thread; thus they are not able to provide thread assignments that optimally use processor hardware resources [50]. We analyze real network applications running on state-of-the-art server comprising UltraSPARC T2 processor and measure significant performance loss introduced by Linux-like process scheduler.

### 1.1.1.3 Intractability of the thread assignment problem

Analytical analysis of optimal thread assignment is an NP-complete problem [67]. Also, in current multithreaded processors comprised of several cores where each core supports several simultaneously-running threads, the total number of possible thread assignments is vast [50, 59, 87, 131]. This number will grow rapidly in future massively multithreaded processors in which the number of cores and number of different levels of resource sharing increase [116]. In order to illustrate this, we study the number of possible assignments when several threads simultaneously execute on the UltraSPARC T2 processor.

| Number of threads | Number of possible thread assignments | Time needed to execute all thread assignments |                               |

|-------------------|---------------------------------------|-----------------------------------------------|-------------------------------|

| 3                 | 11                                    | 11 seconds                                    | 11 µs                         |

| 6                 | 1,526                                 | 25 minutes                                    | 1.5 ms                        |

| 9                 | 591 x 10 <sup>3</sup>                 | 7 days                                        | 0.6 seconds                   |

| 12                | 459 x 10 <sup>6</sup>                 | 15 years                                      | 8 minutes                     |

| 15                | 600 x 10 <sup>9</sup>                 | 19 thousand years                             | 7 days                        |

| 18                | 971 x 10 <sup>12</sup>                | 30 million years                              | 31 years                      |

| 60                | 550 x 10 <sup>56</sup>                | 1.75 x 10 <sup>51</sup> years                 | 1.75 x 10 <sup>45</sup> years |

Table 1.1: Number of different thread assignments for applications running on the UltraSPARC T2 processor

The UltraSPARC T2 processor comprises eight cores, and each core contains two hardware pipelines. Each (hardware) pipeline can execute up to four threads at a time, meaning that the maximum number of simultaneously running threads is  $64^4$ . The number of possible thread assignments for different workload size is shown in Table 1.1. The first column of the table shows the number of threads in the workload. We present results for 3, 6, 9, 12, 15, 18, and 60 threads. The second column presents the number of different thread assignments for a given workload size. The third column of the table shows the time needed to execute all possible thread assignments assuming that each assignment can be executed in only one second. Finally, in the last column, we present the time needed to predict the performance of all thread assignments. We make an optimistic assumption that the performance of a single assignment can be predicted in  $1\mu s$  that is in the order of 1000 cycles of a processor running at 1GHz frequency.

Overall, we observe that the number of possible threads assignments as well as the time needed to execute them grows rapidly with the number of threads in the workload. The point where running all assignments is unfeasible is reached very fast. For 9 threads in the workload, the time needed to execute all assignments is 7 days, for 12 threads, the execution time is more than 15 years. For 60-thread workloads that use 94% of hardware contexts of the processor, the time needed to execute all possible thread assignments is  $1.75 \times 10^{51}$  years. The results presented in Table 1.1 clearly show that, in general, running all thread assignments is unfeasible, and that an exhaustive search cannot be used to find the optimal system performance for a given workload.

Several studies (see Section 3.5) propose methods that can predict the performance of different thread assignments of a given workload. However, from Table 1.1, we also see that the prediction of all possible threads assignments is unfeasible. The last column

<sup>&</sup>lt;sup>4</sup>For more information about the UltraSPARC T2 processor used in the study, refer to Section 2.1.

# 1.1. CHALLENGES FOR THE EFFECTIVE USE OF MULTITHREADED PROCESSORS

shows that, for example, for the case of 15-thread workloads, the time needed to predict all assignments is 7 days. For 18 threads, the prediction time is measured in years. Therefore, performance predictors can be used only to determine the close-to-the-optimal thread assignment in a limited sample. However, since the number of possible thread assignments in modern processors is vast, the effectiveness of performance predictors is questionable [50, 59]; even if we assumed that a performance predictor would be able to find the best assignment in the sample, it would not be clear what the performance difference between the best assignment in the sample and the actual global best assignment (the optimal system performance) would be.

Therefore, the current thread assignment approaches can not guarantee that the performance of the predicted best assignment is either the optimal one, or close to it. As the performance of the optimal thread assignment for a workload is unknown, the room for improvement of the current thread assignment techniques cannot be determined. Thus, it is difficult to determine the effort needed to invest in the thread assignment process. This may lead to overspending if a good thread assignment algorithm is constantly improved, or sub-optimal performance if a poor-performing algorithm is not enhanced.

In this thesis, we address the problem of thread assignment of multithreaded network applications running on processors with several levels of resource sharing. We present two methods, *TSBSched* and *BlackBox scheduler*, that profile the applications running on a target architecture and predict the performance of different thread assignments. We also present a statistical method based on Extreme Value Theory that predicts the performance of the optimal thread assignment. TSBSched, BlackBox scheduler, and the proposed statistical method are evaluated on a set of multithreaded network applications running on a network server that comprises UltraSPARC T2 processor.

# 1.1.2 Compilation of multithreaded streaming applications

In order to exploit the hardware potential and deliver maximum performance, state-of-the-art multithreaded architectures have to execute numerous software threads simultaneously. One way to use multithreaded architectures effectively is to execute numerous software threads concurrently. For example, Internet, network, and data-center servers can concurrently execute multiple instances of a single application that process (highly-)independent traffic from different users. However, in various domains (such as desktop and mobile applications) it is not trivial to find numerous independent software threads that can execute concurrently. Actually, one of the greatest challenges in software devel-

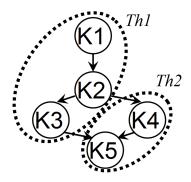

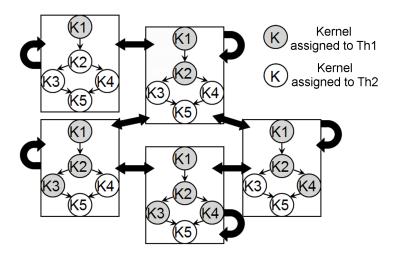

Figure 1.3: A kernel partition example

opment is how to write efficient, portable, and correct software for multithreaded processors. A promising approach to develop multithreaded applications is to expose parallelism to the compiler through the use of domain-specific languages. The compiler can then perform complex transformations that the programmer would otherwise have had to do.

One of the widely-used domain-specific languages is stream programming. Stream programming is suitable for applications that process long sequences of data, such as voice, image, multimedia content, Internet and communication traffic. Stream programming languages [2, 17, 30, 33, 148] represent the program as concurrent kernels, which communicate only via point-to-point streams. A kernel is a basic computation block with a user-defined function that processes one or more input data streams into one or more output data streams. Dependencies between different kernels are described explicitly through the communication data channels. The whole application can be represented as a *stream* graph. The nodes of the stream graph correspond to the kernels, while the directed edges represent the communication data channels. In order to take advantage of multiple processor cores, the stream program is automatically compiled into a multithreaded executable by the stream compiler. One of the most important tasks of the stream compiler is to partition the kernels in the stream graph into software threads. In Figure 1.3, we illustrate a stream graph of a simple program, which is comprised of five kernels (K1 to K5). The figure also shows one possible kernel partition of the graph: kernels K1, K2, and K3 are to be compiled to software thread Th1, while kernels K4 and K5 are to be compiled into Th2.

Kernel partitioning can affect the overall system performance significantly. For example, for the benchmarks included in the StreamIt 2.1.1 suite [3, 138], the relative performance difference between good and bad kernel partitions of the same benchmark mapped into four software threads ranges from  $2.4 \times$  to  $3.9 \times$ , and on average it is  $3.5 \times$ .

# 1.1. CHALLENGES FOR THE EFFECTIVE USE OF MULTITHREADED PROCESSORS

Several studies (see Section 5.6) propose heuristic-based algorithms to address the kernel partitioning problem. As kernel partitioning is an intractable problem [63, 67], it is impossible in general to know the performance of the optimal partition, so the room for improvement is also unknown. It is hard to decide whether to invest additional effort to try to improve a given algorithm, since it may already be close to optimal.

In this thesis, we propose a statistical approach to the kernel partitioning problem. We present a method that predicts the performance of the optimal partition based on the observed performances of a random sample of kernel partitions. We also analyze whether random sampling on its own is likely to find a kernel partition with good performance. The proposed method is evaluated on the kernel partitioning of the benchmarks included in StreamIt 2.1.1 suite.

### 1.1.3 Multithreaded processors in time-critical environments

Due to good performance-per-watt ratio and high performance opportunities, multithreaded processors are of special interest for embedded real-time systems [152]. These architectures are particularly well suited for embedded *integrated architectures* [22, 113, 158] in which several functions are integrated into the same processor. In this context, multithreaded processors can potentially schedule mixed criticality workloads, *i.e.* workloads composed of safety-critical, mission-critical, and non-critical applications inside the same processor, improving the hardware utilization and so reducing cost, size, weight, and energy consumption [110].

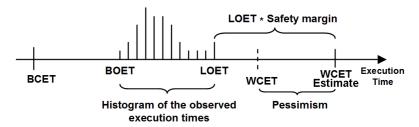

Unfortunately, despite the benefits that multithreaded processors may offer in embedded real-time systems, particularly in integrated architectures, the market has not yet embraced such a shift. In addition to the functional correctness of operations, in real-time systems, it is required to guarantee that the execution time of tasks does not exceed the corresponding *deadlines*. This requisite of real-time systems is referred to as *time correctness*. In order to guarantee time correctness of a given task, it is obligatory to estimate the maximum execution time that the task could have on a specific hardware platform, *i.e.* to determine the *Worst Case Execution Time (WCET)* of the task. In multithreaded processors, simultaneously-running tasks share and compete for processor resources, so the timing analysis has to estimate the possible impact that these inter-task interferences have on the execution time of the applications. As a result, it is much more difficult to provide the WCET estimations for applications running on multithreaded processors than running on single-threaded processors [120].

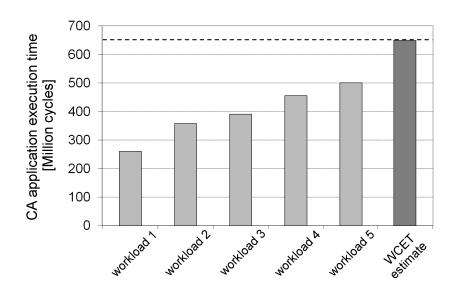

Figure 1.4: Collision Avoidance (CA) application: The execution time in different workloads and the WCET estimate

In addition to this, in order to reduce the cost of the system verification in the time domain, it is required to do an incremental timing verification of real-time tasks. Incremental timing verification means that a user does not have to verify the timing behavior of all concurrently-running applications each time a new component (application) is changed or added to the system [60]. In that sense, the system is time composable if the WCET estimate of the tasks do not change if any of the tasks in the workload change.

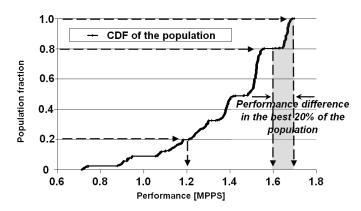

In the following example, Paolieri et al. [117] demonstrate the execution time variations of applications running in multithreaded processors, and illustrate the composable WCET estimate for the application under study. In this experiment, the Collision Avoidance (CA) application developed by Honeywell Corporation is executed with different sets of co-running applications (different workloads) on a multicore processor. The CA application is based on 3D path planning algorithm that is used in autonomous-driven airplanes.

The results of the experiment are presented in Figure 1.4. The X-axis of the figure lists different workloads (*workload 1* to *workload 5*) that are executed simultaneously with the CA application. The Y-axis shows the execution time of the CA application in each configuration. From the results presented in Figure 1.4, we see that the execution time of the CA application varies significantly (from 250 to 500 million cycles) depending on the co-running workload. A safe and time-composable WCET estimate for the CA application running on the architecture under study (dark gray bar in Figure 1.4) must be computed independently of the co-running workload, and it must exceed the execution

time of the CA application in *any* possible workload. In this way, the WCET estimate of the CA application is computed only once, and it does not have to be recomputed each time that any of the co-running tasks is replaced or updated.

In this thesis, we present a systematic method for measurement-based timing analysis of applications running on multithreaded architectures, and we demonstrate that the presented method helps with providing composable WCET estimations. We also show how the method can be used to determine whether different multithreaded architectures are suitable for time-critical environments.

### 1.2 Thesis contributions

This thesis presents cross-domain approaches that improve the effective use of multithreaded architectures. The contributions of the thesis can be classified in three groups. First, we propose several methods for thread assignment of multithreaded network applications running in multithreaded servers. Second, we analyze the problem of graph partitioning that is a part of the compilation process of multithreaded streaming applications. Finally, we present a method that improves the measurement-based timing analysis of multithreaded architectures used in time-critical environments. The following sections briefly summarize each of the contributions.

### 1.2.1 Thread assignment on multithreaded processors

The first problem that we address in the thesis is thread assignment of multithreaded network applications running on network servers that comprise state-of-the-art multithreaded processors. We propose *TSBSched* (Thread-to-Strand Binding Scheduler) [131], a systematic method for thread assignment of multithreaded network application running on processors with several levels of resource sharing. Based on minimum information about the target processor architecture, and without any data about the hardware requirements of the applications under study, the proposed method determines a set of thread assignments that can be used to model the interference between concurrently running threads (*profiling thread assignments*). The profiling assignments are executed on the processor under study, and the performance of each assignment is measured. Finally, the method uses the measured performance of the profiling thread assignments to estimate the performance of *any* assignment composed of applications under study.

TSBSched is a simple, architecture independent thread assignment approach that determines assignments with a good performance. However, TSBSched has two main limitations: (1) The programmer who profiles the application must have a profound knowledge about the application behavior. (2) Also, TSBSched requires adjustments of the application source code. If the source code is not available, TSBSched method cannot be used.

In order to overcome these limitations, we design *BlackBox* scheduler [132]. Black-Box scheduler does not require inserting any test points in the application source code nor the profound understanding of it. Therefore, BlackBox scheduler can be used when the source code is not available, which is a common limitation.

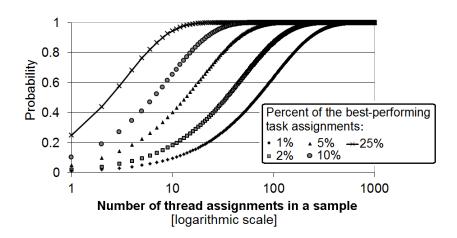

We also present a statistical approach to the thread assignment problem [130]. We present a method based on Extreme Value Theory (EVT)[26, 34] that predicts of the performance of the optimal thread assignment. Knowing the optimal system performance improves the evaluation of any thread assignment technique and it is the most important piece of information for the system designer when deciding whether any scheduling algorithm should be enhanced. We also show that, in environments in which the workload infrequently changes, the system designer can simply execute a sample of several hundred or several thousand *random* thread assignments of a given workload and measure the performance of each assignment. According to this analysis, there is a high probability that the performance of the best observed assignment will be close to the optimal system performance. This removes the need for any application profiling or an understanding of the increasingly complex multithreaded architectures. Unlike other thread assignment proposals that use performance predictors to find the best thread assignment, the method can be applied directly and without any change to any architecture running any set of applications.

# 1.2.2 Kernel partitioning of streaming applications

The second problem that is addressed in the thesis is kernel partitioning of streaming applications. We present a method based on EVT that statistically estimates the performance of the optimal kernel partition [128]. To the best of our knowledge, this is the first study that applies EVT to a graph partitioning problem. We use the estimates of the optimal performance to evaluate a state-of-the-art heuristic-based kernel partitioning algorithm. Also, we show that the sampling method used to generate random partitions, has a significant effect on the applicability of the statistical analysis. We analyze different sampling

methods, and our results strongly recommend that the samples should be uniformly distributed. Since a complex heuristic-based algorithm may not always be available, the user may pick the best from a random sample, and measure its quality using the estimates of the optimal performance. We analyze whether random sampling is likely to find a good kernel partition.

### 1.2.3 Multithreaded processors in time-critical environments

Finally, we analyze the impact of shared resources in multithreaded processors in time-critical environments. Our study provides a systematic method for measurement-based timing analysis of applications running on multithreaded architectures [129]. We define a set of specific resource-stressing benchmarks that introduce a high number of interferences on each potentially-shared hardware resource. By using these *resource-stressing* benchmarks as co-running threads, we obtain a good estimation of the worst-case slow-down that real applications may experience because of collision in shared processor resources.

We also show how the proposed method can be applied to determine the suitability of different multithreaded architectures for time-critical systems. When a workload is composed only of resource-stressing benchmarks, the detected slowdown is unlikely to be exceeded for any workload composed of real applications. Therefore, the slowdown detected when using resource-stressing benchmarks may serve as an upper estimate of the effect of inter-task interference for a given processor. This analysis is important when companies have to determine which architectures are good candidates to be used in their future time-critical systems.

### 1.3 Thesis structure

The rest of the thesis is organized as follows:

- Chapter 2 presents the experimental environment used to analyze the thread assignment problem. In this chapter, we describe the hardware platform, operating system, and benchmarks used in the study.

- In Chapter 3, we propose and evaluate two systematic methods for thread assignment of multithreaded network applications running on processors with several levels of resource sharing, *TSBSched* and *BlackBox* scheduler.

### **CHAPTER 1. INTRODUCTION**

- Chapter 4 presents a statistical method based on Extreme Value Theory that predicts the performance of the optimal thread assignment in multithreaded processors. We further show that executing a sample of several hundred or several thousand random thread assignments is enough to obtain, with very high confidence, an assignment with a performance that is close to the optimal one.

- Chapter 5 summarizes our work on the problem of kernel partitioning for streaming applications. In this chapter, we present a method that statistically estimates the performance of the optimal kernel partition. We further use the presented method to evaluate a recently-published partitioning algorithm based on a heuristic.

- In Chapter 6, we propose a method that quantifies the slowdown that simultaneouslyrunning tasks may experience due to collision in shared processor resources. This information is a base for incremental timing verification of multithreaded architectures that are used in time-critical environments.

- Chapter 7 lists the conclusions of the thesis, briefly summarizes future work, and lists the relevant publications and awards.

# Chapter 2

# **Experimental setup**

This chapter presents the experimental environment that was used to analyze the problem of thread assignment on multithreaded processors. The experimental setup in which we analyzed kernel partitioning for streaming applications is presented in Chapter 5. Chapter 6 includes the description of the environment in which we executed the experiments related to the study of timing behavior of real-time applications running in multithreaded architectures.

We evaluated the proposed thread assignment methods for a set of multithreaded network applications running in a real industrial environment. The environment comprised two Oracle T5220 servers that managed the generation and the processing of network traffic. Each T5220 server comprised one UltraSPARC T2 processor. One T5220 server executed the Network Traffic Generator (NTGen) [11]. NTGen is a software tool, developed by Oracle, that generates IPv4 TCP/UDP packets with configurable options to modify various packet header fields. In addition to this, we enhanced the NTGen to transmit network traffic read from trace files, such as anonymized Internet trace files [5]. T5220 server running NTGen transmitted network packets through a 10Gb link to the second T5220 server in which we executed the thread assignments selected by our method. In all the experiments presented in the study, NTGen generated enough traffic to saturate the network processing server. Thus, in all the experiments, the performance bottleneck was the speed at which the packets were processed, which is determined by the performance of the selected thread assignment.

In order to avoid interferences between user applications and operating system processes, we executed the experiments in Netra DPS, a low-overhead environment used in network processing systems [10, 11]. We briefly describe Netra DPS being focused on the difference between this environment and a fully-fledged operating systems, such as Linux or Solaris. At the end, we present the set of multithreaded network applications

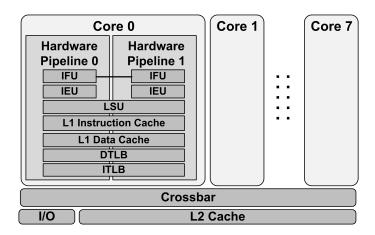

Figure 2.1: Schematic view of the three resource sharing levels of the UltraSPARC T2 processor

and the methodology we use to evaluate the proposed thread assignment approaches.

# 2.1 UltraSPARC T2 processor

The UltraSPARC T2 is a multithreaded processor [8][9] that comprises eight cores connected through the crossbar to the shared L2 cache (see Figure 2.1). Each of the cores supports eight hardware contexts (strands), thus up to 64 threads can be simultaneously executed on the processor. Strands inside each hardware core are divided into two groups of four strands, forming two hardware execution pipelines, from now on also referred as hardware pipelines or hardware pipes.

Processes simultaneously running on the UltraSPARC T2 processor share (and compete for) different resources depending on how they are assignmed to hardware contexts. As it is shown in Figure 2.1, the resources of the processor are shared on three different levels: *IntraPipe*, between threads running in the same hardware pipeline; *IntraCore*, between threads running in different hardware pipelines of the same core; and *InterCore*, between threads running on different cores [154].

**IntraPipe**: Resources shared at this level are the Instruction Fetch Unit (IFU) and the Integer Execution Units (IEU). Even if the IFU is physically shared between all processes that execute on the same hardware core, the instruction fetch policy prevents any interaction in the IFU between threads running in different hardware pipelines. That is, the IFU actually behaves as two private IFUs, one for each hardware pipeline.

**IntraCore**: Threads that execute on the same core share the IntraCore resources: the

16KB L1 instruction cache, the 8KB L1 data cache (2 cycles access time), the Load Store Unit (LSU), the Floating Point and Graphic Unit (FPU), and the Cryptographic Processing Unit.

InterCore: Finally, the main InterCore resources (globally-shared resources) of the UltraSPARC T2 processor are: the L2 cache, the on-chip interconnection network (crossbar), the memory controllers, and the interface to the off-chip resources (such as the I/O). The 4MB 16-way associative L2 cache is partitioned eight banks that operate independently from each other. The L2 cache access time is 22 cycles, and the L2 miss that accesses the main memory lasts around 185 CPU cycles. The L2 cache connects to four on-chip DRAM controllers, which directly interface to a pair of fully buffered memory channels.

In order to fully utilize the performance of a multithreaded processors like the UltraSPARC T2, it is important to understand which hardware resources are shared on each resource-sharing level. In the UltraSPARC T2, two threads running in the same hardware pipeline conflict at all resource-sharing levels: IntraPipe, IntraCore, and InterCore. Threads running in different hardware pipelines of the same core conflict at the IntraCore and InterCore levels. Finally, threads in different cores interact only at InterCore level. On the other hand, threads running in the same processor core communicate through L1 cache shared at the IntraCore level, while threads from different cores share data and instructions only at globally shared L2 cache that has significantly higher access time.

### 2.2 Netra DPS

State-of-the-art operating systems (OSs) provide features like the dynamic process scheduler or the virtual memory to enhance the execution of user applications. On the other hand, user applications experience slowdown and have variable execution time because of interference with OS processes. Many networking systems use lightweight runtime environments in order to reduce the overhead introduced by fully-fledged OSs. One of these environments is Netra DPS [10, 11] developed by Oracle. Netra DPS provides less functionality than fully-fledged OSs, but also introduces less overhead. In our previous study [133], we compared the overhead introduced by Linux, Solaris, and Netra DPS in the execution of benchmarks running on the UltraSPARC T1 processor. Presented results show that Netra DPS is the environment that clearly exhibits the best and most stable application execution time.

Netra DPS does not incorporate virtual memory nor a run-time process scheduler, and performs no context switching. The assignment of running threads to processor hardware contexts (virtual CPUs) is performed statically at the compile time. It is the responsibility of the programmer to define the hardware context in which each particular thread will be executed. Netra DPS does not provide any interrupt handler nor daemons. A given thread runs to completion on the assigned hardware context without any interruption.

### 2.3 Benchmarks

Netra DPS is a specific lightweight runtime environment that does not provide functionalities of fully-fledged OSs such as system calls, dynamic memory allocation, or file management. Therefore, benchmarks included in standard benchmark suites have to be adapted in order to execute in this environment.

### 2.3.1 Overview

The benchmarks used are described next:

- (1) IP Forwarding (IPFwd) is one of the most representative Layer2/Layer3 network applications. IPFwd application makes the decision to forward a packet to the next hop based on the destination IP address. Depending on the size of the lookup table, the IPFwd application may have significantly different memory behavior [82, 95]. In order to cover different cases of IPFwd memory behavior, we created three variants of the IPFwd application that are based on the IPFwd application included in the Netra DPS distribution [10]:

- (1) The lookup table fits in the L1 data cache (*IPFwd-L1*);

- (2) The table does not fit in the L1 data cache, but it fits in the L2 cache (*IPFwd-L2*). The routing table entries of IPFwd-L2 are configured to cause a lot of data L1 misses in IPFwd traffic processing.

- (3) The table does not fit in the L2 cache and the lookup table entries are initialized to make IPFwd continuously access the main memory (*IPFwd-Mem*).

IPFwd-L1 is representative of the best case of IPFwd memory behavior, since it shows high locality in data cache accesses. On the other hand, IPFwd-Mem represents the worst case of IPFwd memory behavior used in network processing studies, in which there is no cache locality between accesses to the lookup table [140].

(2) Complex packet processing: Based on the IP Forwarding application included

in the Netra DPS distribution, we also designed the benchmarks that emulate more complex packet processing and multiple accesses to the memory. In these benchmarks, the hash function call and the hash table lookup are repeated N times (three times in our experiments). We refer to these benchmarks as *hashN*. Again, we use three different configurations to analyze complementary scenarios that cover from the best to the worst case studies:

- (1) hashN-L1: the lookup table fits in the L1 data cache;

- (2) hashN-L2: the table does not fit in the L1 data cache, but it fits in the L2 cache;

- (3) hashN-Mem: the table does not fit in the L2 cache.

- (3) CPU intensive packet processing: The behavior of CPU-intensive network applications (such as high layer packet decoding or URL decoding) is emulated by the benchmarks that have a high rate of resource conflicts in the IntraPipe and IntraCore processor resources.

In order to stress IntraPipe processor resources, we developed *IPFwd-intadd* benchmark. Benchmark *IPFwd-intadd* is a modification of the IPFwd application included in the Netra DPS. We develop *IPFwd-intadd* by inserting a set of *integer addition* instructions at the end of the IPFwd processing stage. These instructions put significant stress to Instruction Fetch Unit and Integer Execution Unit, both shared between threads running on the same hardware pipeline.

In order to stress IntraCore processor resources, we developed benchmarks *IPFwd-intmul* and *IPFwd-intdiv*. We develop these benchmarks by inserting insert a set of *integer multiplication* and *integer division* instructions at the end of the IPFwd processing stage. In the UltraSPARC T2 processor, *integer multiplication* and *integer division* instructions are executed in the Floating Point Unit (FPU) that is shared between threads executing on the same processor core (IntraCore resource). Benchmarks *IPFwd-intmul* and *IPFwd-intdiv* stress FPU in two different ways [154]: (1) *Integer multiplication* instructions are pipelined with throughput of one instruction per cycle. This means that several *IPFwd-intmul* benchmarks may execute simultaneously in the same processor core and share the FPU with almost no overhead. (2) On the other hand, *integer division* instructions are non-pipelined. When several *integer division* instructions are ready to be executed at the same time, they are serialized – only one instruction is executed at a time, while others are delayed. This may cause significant overhead when several *IPFwd-intdiv* processing threads run on the same processor core.

(4) Packet analyzer is a program that can intercept and log traffic passing over a

network or part of a network [45]. Packet analyzers are primary tolls for network monitoring and management used to troubleshoot network problems, examine security issues, gather and report network statistics, detect suspect content, and filter it from the network traffic [4, 145, 163].

The packet analyzer that we used in the experiments captures each packet that passes through the Network Interface Unit (NIU), inspects the packet, and analyzes its content according to the appropriate RFC specifications [84]. The packet analyzer can display the information about different fields of packet headers at Layer 2, Layer 3, and Layer 4, and about the packet payload. A user can decide to log all traffic that passes through the NIU, or to define filters based on many criteria. We used the packet analyzer to log MAC source and destination address, time to live field, Layer 3 protocol, source and destination IP address, and source and destination port number of all packets passing through the NIU of the processor under study.

(5) Aho-Corasick is a string matching algorithm. String matching is the basic technique to analyze the network traffic at the application layer [76]. In networking, string matching algorithms search for a set of strings (keywords) in the payload of the network packets. Aho-Corasick is an efficient algorithm that locates all occurrences of a given set of keywords in a string of text (packet payload in case of packet processing). The algorithm constructs a finite state pattern matching machine from the keywords and then uses the pattern matching machine (finite automata) to process the string of text in a single pass [19]. The Aho-Corasick string matching algorithm has proven linear performance, and it is suitable for searching of a large set of keywords concurrently. This is why the Aho-Corasick algorithm is used in state-of-the art network intrusion detection systems such as Snort [114].

In the presented experiments, we used the Aho-Corasick algorithm to search for keywords from Snort Denial-of-Service set of intrusion detection rules (version 2.9, November 2011) in the payloads of the packets that were processed.

(6) Stateful packet processing is an important component of state-of-the art network monitoring tools [115, 156] and intrusion prevention and detection system [145]. Unlike stateless applications that process each packet independently (like the other benchmarks used in our study), stateful packet processing keeps the information of previous packet processing.

The packets that belong to the same *flow*, *i.e.* have the same *flow-5-tuple* <sup>1</sup>, share the common information called the *flow-record* [56]. The record of a given flow contains the information as to whether the flow is open (the connection is established), safe, malicious, *etc.* The information about the active flows is stored in a hash table that is indexed based on the flow-keys. The common main components of stateful packet processing are: (1) Read the flow-keys of a packet; (2) Use a hash function to determine the corresponding hash table entry based on the packet flow-keys; (3) Access the hash table. Lock, read, and update the flow-record of an already-existing flow, or create a flow-record for a new flow.

The stateful packet processing benchmark that we used in the experiments is comprised of these three components. The stateful benchmark uses the same hash function as the one that is implemented in nProbe network monitor [56, 115]. The hash table contains  $2^{16}$  entries, which is sufficient to store the records of active flows of fully-utilized 10Gb link [155], and it is the hash table size that was already used to test different network monitoring tools [56].

### 2.3.2 Implementation

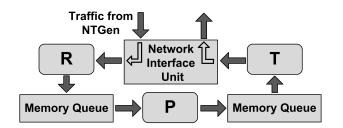

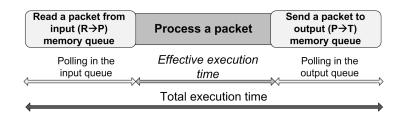

Each benchmark is divided into three threads that form a software pipeline (see Figure 2.2). This is a commonly-used approach in the development of the network applications [11, 164]:

- The receiving threads (R) of all benchmarks read the packets from the Network Interface Unit (NIU) associated with the receiver 10Gb network link, and write the pointers to the packets into the R→P memory queues.

- The processing threads (P) read the pointer to the packets from the memory queues, process the packets, and write the pointers to the P→T memory queues. The packet processing is different for each benchmark, e.g. P threads of the IPFwd-L1 and IPFwd-Mem benchmarks read the destination IP address, call the hash function, and access the lookup table; P threads of the Aho-Corasick benchmark search for the keywords in the packet payload, etc.

- Finally, the transmitting threads (T) of all benchmarks read the pointers from the

<sup>&</sup>lt;sup>1</sup>The flow-5-tuple is consisted of the source and destination IP address, the source and destination port, and the protocol used.

Figure 2.2: The schematic view of the benchmarks

P→T memory queues, and send the packets to the network through the NIU associated to the 10Gb network link.

To summarize, the presented benchmarks represent a good testbed for the analysis of threads assignment techniques because:

- (1) Each benchmark is divided in three different threads, thus the systems deal with heterogeneous threads even when several instances of the same application are executed simultaneously.

- (2) The benchmarks stress the hardware resources of the UltraSPARC T2 processor at all three sharing levels [154].

- (3) Each instance of the benchmarks comprises interconnected threads that communicate through shared memory queues. The performance of the benchmarks also depend on the distribution of interconnected threads between processor cores (L1 cache domains).

- (4) The impact of thread assignment to the performance is significant. We detect performance variation of up to 60% between different thread assignments of the same workload.

## 2.4 Methodology

In order to assure stable results, we measured the performance of thread assignments when each application instance processed from three to four million network packets. This means that each application thread was executed from three to four million times. The execution time of each experiment was at least 1.5 seconds, and the duration depended on the benchmark and on the distribution of the simultaneously running threads.

## Chapter 3

# Thread assignment of multithreaded network applications on multicore/multithreaded processors

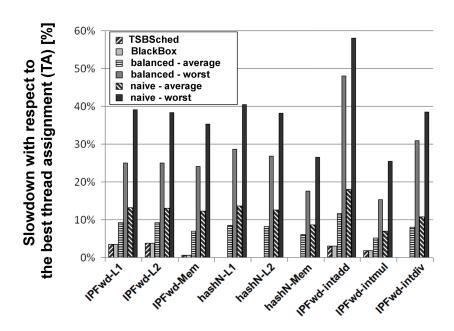

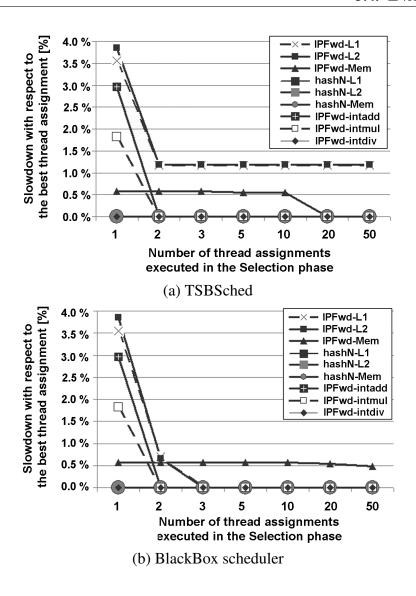

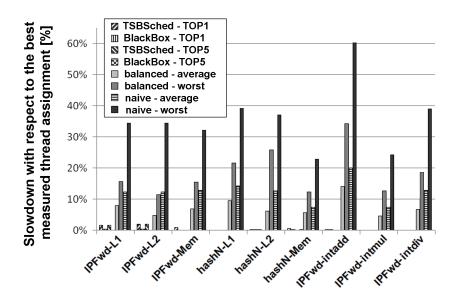

In this chapter, we propose two systematic methods for thread assignment of multithreaded network applications running on processors with several levels of resource sharing, *TSBSched* and *BlackBox* scheduler. We evaluated the proposed methods for a set of multithreaded network applications running on the UltraSPARC T2 processor. The proposed thread assignment methods improve the system performance up to 48% with respect to state-of-the-art scheduling algorithms, and up to 60% with respect to a naive scheduling.

#### 3.1 Introduction

In processors with several levels of resource sharing, thread scheduling comprises two steps: workload selection and thread assignment. We propose TSBSched and BlackBox scheduler, systematic methods for thread assignment of multithreaded network application running on processors with several levels of resource sharing. Based on minimum information about the target processor architecture, and without any data about the hardware requirements of applications under study, TSBSched and BlackBox scheduler determine a set of thread assignments that can be used to model the interference between concurrently running threads (profiling thread assignments). The profiling assignments are executed on the processor under study and the performance of each assignment is measured. Finally, the methods use the measured performance of the profiling thread assignments to estimate the performance of any assignment composed of the applications

under study.

The proposed thread assignment methods are evaluated with an industrial case study for a set of multithreaded networking applications running on the UltraSPARC T2 processor. The results show that the methods provide thread assignments with performance close to the optimal one. In most of the experiments, the proposed thread assignment methods detected the best actual (measured) thread assignment in the evaluation sample. The highest performance difference between the thread assignment provided by TSBSched and BlackBox scheduler and the actual best thread assignments in the evaluation sample is only 3%. The proposed methods also provide a significant performance improvement with respect to the state-of-the-art thread assignment techniques.

The rest of the chapter is organized as follows. Section 3.2 discusses the hardware and OS requirements of network applications, demonstrates the importance of the thread assignment for network applications, and presents the overview of the state-of-the-art thread assignment approaches. Section 3.3 describes in detail the thread assignment methods that we propose. The results of the experiments used in the evaluation of TSBSched and BlackBox scheduler are presented in Section 3.4. Section 3.5 shows the overview of the related work, while Section 3.6 summarizes the study.

## 3.2 Background

Optimal thread assignment requires a profound knowledge of the resource requirements of each running thread, and the understanding of how the threads interact in each of the shared processor resource. Therefore, it is difficult to determine the optimal thread assignment without previous analysis of a large number of experiments that exponentially increases with the number of processor hardware contexts (virtual CPUs), number of different levels of resource sharing, and number of concurrently running threads. The problem becomes even more complex for multithreaded applications. When an application is comprised of several threads, it is not sufficient to understand how sharing of hardware resources affects the execution time of each of the threads independently. The designer also has to be aware of the inter-thread communication, and to understand which application thread is the bottleneck that determines the application performance. Currently, thread assignment is done in one of three ways:

(1) **Resource-oblivious** (naive) thread assignment randomly distributes the workload among hardware contexts of the processor. Naive thread assignment provides non-optimal

performance. In our experiments, naive scheduling introduces the performance loss of up to 60% with respect to the optimal thread assignment.

- (2) **Manual assignment:** A skilled designer attempts to determine a good thread assignment based on a detailed analysis of the target architecture and an off-line application profiling. This analysis is complex and its complexity increases with the number of processor hardware contexts, number of levels of resource sharing, and number of concurrently running threads. In addition to this, any change in the application or in the hardware platform requires the repetition of the analysis. Manual thread assignment is not a systematic approach, its performance depends on the programmer skills, and, in general, does not provide the thread assignment with the optimal performance.

- (3) Load balancing and cache affinity: State-of-the-art fully-fledged OSs, like Linux and Solaris, use load balancing mechanism [15][149] to equally distribute the load of the running threads among all the available scheduling domains (e.g. cores of the CMP architecture). In addition to this, cache and TLB affinity algorithms [15][149] keep the threads assigned to the same logical CPU in order to reduce cache and TLB misses caused by the thread migration. Although these techniques improve the performance, they are not sufficient to fully exploit the capabilities of the current multithreaded processors with several levels of resource sharing. De Vuyst et al. [50] demonstrate that the load balancing used in the state-of-the-art operating systems eliminates the unbalanced schedules that allocate the proper amount of processor resources for each of the co-running threads, which is one of the important advantages of the modern multithreaded processors. We analyze real network applications running on the UltraSPARC T2 processor, and measure the performance difference of up to 48% between load-balanced and optimal thread assignments.

## 3.3 Thread assignment methods

We present *TSBSched* and *BlackBox scheduler*, two systematic methods for thread assignment of multithreaded network applications running on processors with several levels of resource sharing. The purpose of these methods is to estimate the performance of different (many) thread assignments and to determine the assignments that provide a good performance.

Without any data about the hardware requirements of the applications under study, and using the minimum information about the processor under study, the methods determine a set of thread assignments (*profiling thread assignments*) that are used to model the in-

terference between co-running threads. Based on the measured performance of profiling thread assignments, the method estimates the performance of *any* assignment composed of the applications under study.

Thread assignment methods are designed to accomplish two main objectives:

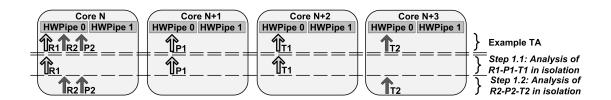

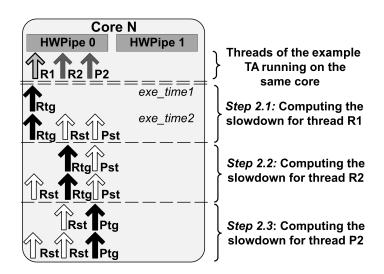

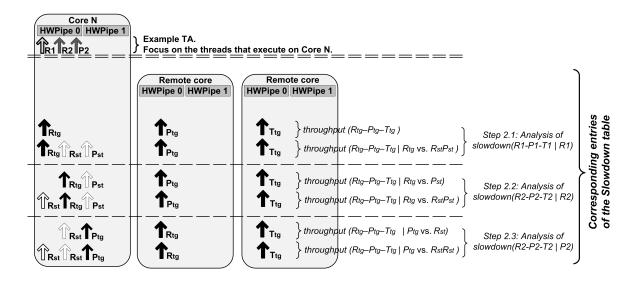

- (1) Remove the need for detailed knowledge about the hardware requirements of applications under study: In order to select a good assignment, scheduling methods have to be aware of the interaction between concurrently running threads. Modeling application interference in shared processor resources is a challenging task. Most of the studies that address this problem (see Section 3.5) profile each thread independently, and then predict the performance when several threads execute concurrently on a processor. We measure directly the interaction between concurrently running threads for a limited set of thread assignments, and use this data to model the interference in hardware resources between co-running threads in any given assignment. The main benefit of this approach is that the information about the application hardware requirements is not incorporated into the thread assignment method, but it is encapsulated into the data passed to the method (the profiling data).