# Testing conformance of a deterministic implementation against a non-deterministic stream X-machine

R. M. Hierons a M. Harman a

<sup>a</sup>Department of Information Systems and Computing, Brunel University, Uxbridge, Middlesex, UB8 3PH, UK.

**keywords:** Stream X-machines, testing, non-determinism, conformance, deterministic implementation.

### Abstract

Stream X-machines are a formalisation of extended finite state machines that have been used to specify systems. One of the great benefits of using stream X-machines, for the purpose of specification, is the associated test generation technique which produces a test that is guaranteed to determine correctness under certain design for test conditions. This test generation algorithm has recently been extended to the case where the specification is non-deterministic. However, the algorithms for testing from a non-deterministic stream X-machine currently have limitations: either they test for equivalence, rather than conformance or they restrict the source of non-determinism allowed in the specification. This paper introduces a new test generation algorithm that overcomes both of these limitations, for situations where the implementation is known to be deterministic.

# 1 Introduction

Many systems can be modelled by finite state machines. However, if the system's specification requires memory, then an extended form of finite state machine is required. The stream X machine is just such a form of extended finite state machine. A software development approach is associated with stream X-machines. Here a set of trusted components are integrated to form a larger system, where communication between the components is modelled using a shared memory. The approach allows test data to be constructed from a model of such a component—based system. The test data is then applied to the implementation.

The most striking aspect of the stream X machine approach is the, at first, implausible-sounding claim that the set of test data constructed from the model is sufficient to *guarantee* the correctness of the implementation. This sounds implausible because it seems to contradict Dijkstra's oft quoted aphorism, which appears, *inter alia*, in his book (co-authored with Dahl and Hoare [8]):

"Program testing can be used to show the presence of bugs, but never to show their absence!"

How could passing a finite set of tests ever provide a *guarantee* of a system's correctness?

The salient point here is that the approach does *not* guarantee that the implementation is correct if it should turn out that the trust placed in the 'trusted components' is a misplaced trust. That is, the approach guarantees that the *integration* of the trusted components is correct, on the *assumption* that the trusted components are, themselves, correct. In this way the stream X machine approach can be regarded as an instance of Gaudel's [12] testing framework, in which formal proof discharges one part of the correctness demonstration, while testing is used to discharge the remaining part. The combination of formal proof and testing thereby establishes the overall correctness of the system under consideration.

For stream X machines, a full correctness guarantee of the entire system would require the proof of correctness for the trusted components in addition to the results which show that the implementation passes all the tests constructed from the stream X machine model.

Since reliance on 'trusted components' is an increasing feature of software development, both by necessity and design, the stream X machine approach offers a soundly-based, yet practicable technique by which the correctness issue can be split into integration—correctness concerns and component—correctness concerns. As such, the approach allows one to guarantee correctness of the implementation concerns, in isolation, simply by passing a set of test data. This is a significant advantage of the approach, and has been the primary motivation for its study (for example see [3–6,19,21]).

The components used to construct the implementation could have been developed from smaller (trusted) components using the Stream X-machine approach. Thus a system could be built from basic components through a sequence of refinement and testing phases.

The model of testing from a stream X machine is one in which tests are generated from a state based model (the stream X machine), and are applied to an implementation which, it is hoped, respects the model. Traditionally, only

deterministic stream X-machines have been used for the purpose of describing specifications. This was largely because the stream X-machine test technique was only applicable to deterministic stream X-machines.

However, the restriction to deterministic stream X machines is clearly a significant barrier to its wider uptake. It is part of the nature of a specification to want to leave certain paths open to the designer and implementor of the system. A favourite mechanism by which this is achieved is that of making the specification non-deterministic. That is, the specifier of a system, merely indicates that one of several possibilities should be implemented. This leaves the implementor free to choose that which is the most efficient or practical according to a set of concerns and criteria, the detail of which is unknown or unimportant at the specification level. A technique that is capable of generating test data from non-deterministic stream X machines is therefore an important research goal.

Recently, the test technique has been extended to allow non-determinism [16,24]. However, each piece of published work on testing from a non-deterministic stream X-machine suffers from at least one of the following restrictions:

- (1) The test generation algorithms assume that the notion of correctness used is equivalence [24]. Thus, the test determines whether the set of traces in the *implementation under test (IUT)* is identical to that in the specification. However, when the specification is non-deterministic, often the appropriate notion of correctness is conformance: the set of traces in the IUT is contained within the set of traces of the specification. Where conformance is the appropriate form of correctness, algorithms that test for equivalence are not applicable.

- (2) The algorithms limit the source of non-determinism in the specification [16], thus restricting the set of specifications to which the approach may be applied.

This paper extends the current work by considering the problem of testing a deterministic implementation for conformance to a general non-deterministic stream X-machine. The case in which the specification is non-deterministic and the implementation is deterministic is highly relevant; while most implementations are deterministic, non-determinism aids abstraction and thus is appropriate for specifications. Here the appropriate notion of correctness is conformance rather than equivalence and thus this case is not covered by current approaches to non-determinism. A further extension to the work by Hierons and Harman [16] is provided by weakening the design for test conditions in a similar manner to the changes made by Ipate and Holcombe [24].

When testing from a stream X-machine M it is normal to assume that the IUT I behaves like some unknown stream X-machine  $M_I$ . Interestingly, in

the case considered in this paper, I may conform to M even if  $M_I$  and M have significantly different structures. This contrasts with problems previously considered. An important consequence of this observation is that the traditionally-used W-method cannot be applied. In its place a test procedure, based on the notion of state counting, is introduced. State counting has previously been used for testing from a Non-deterministic Finite State Machine (see, for example, [31,37]).

The rest of this paper is structured as follows. Section 2 briefly reviews the testing of state based systems. Section 3 provides preliminary material and gives an example. Section 4 defines the design for test conditions used in this paper. Section 5 characterises conformance in terms of a relationship between languages defined by  $M_I$  and M. Section 6 introduces the test process that allows the tester to decide whether a word is a member of the language defined by the stream X-machine  $M_I$ , that represents the implementation, through black-box testing. Section 7 considers the problem of finding sequences to reach and distinguish states of M; this problem is significantly altered by the conditions considered here. Based on this, Section 8 introduces an algorithm that produces a test that is guaranteed to determine correctness under the design for test conditions. Section 9 then discusses possible future work and finally, Section 10 draws conclusions.

# 2 Background and Motivation

# 2.1 State based systems

Many systems have a persistent internal state and such systems are often specified using state-based languages such as Statecharts [13] and SDL [26]. These languages specify a system in terms of a finite set of logical states, an internal store, and transitions between the states, each transition being labelled with an operation that may change the store. Typically, the logical state is used to indicate which sequences of operations are currently possible while the store is used to hold additional information. Thus, the logical states and transitions between them specify the control structure, while the operations that label the transitions specify the data processing.

Consider, for example, a video recorder (VCR). A model of a VCR might have logical states such as one representing the VCR being in play mode and another representing the VCR being paused. There might also be other data, such as a counter to state how long the currently-loaded cassette has been playing and information about the configuration settings of the VCR. This additional data forms part of the internal store. Such a state-based view

of the behaviour of a VCR is highly amenable to state-based modeling and reasoning.

State-based specification languages have been used for a variety of systems. SDL is used for the specification of communications protocols while State-charts are widely used for the specification of reactive systems and now form part of the Unified Modeling Language (UML). Specifications written in such languages can usually be thought of as extended finite state machines (EF-SMs).

Model-based languages such as Z and VDM have also been used for specifying systems that have an internal state. Interestingly, it has been recognised that it is useful to devise a logical state structure, and thus produce an EFSM, when testing from such a specification (see, for example, [9,10,14,33]). The presence of a logical state structure provides a number of benefits when testing. For example, it helps in the process of finding a sequence of inputs or events that set up the state in order for a test to be applied.

The wide reliance upon state-based models for specification, design and reasoning about systems has led to a significant research effort concerned with the verification of state-based systems. One of the primary concerns for this state-based verification research agenda has been the question of how best to test state-based systems.

### 2.2 Testing state based systems

Testing is a process in which the implementation under test (IUT) is provided with sequences of input values and the resultant behaviours are observed and checked against the specification. Testing is often divided into at least the following three stages:

- (1) Unit testing: the individual components of the IUT are tested against their specifications.

- (2) Integration testing: the interaction between these components is checked.

- (3) System testing: the overall functionality of the system is tested against the requirements. This phase will often involve users.

When testing from an EFSM, it is sometimes possible to apply techniques that have been developed for testing from a finite state machine (or transducer). There is a wide range of such techniques (see, for example, [1,15,17,28,34,35]). However, in order to apply such techniques, it is necessary to produce a finite state machine (FSM) from the given EFSM specification. This FSM could be produced using one of the following approaches.

- (1) Expand out the internal store.

- (2) Abstract away the internal store.

Where the internal store is infinite, it is not possible to produce an FSM by expanding out the store. Even where the store is finite, this process leads to a combinatorial explosion. Thus, for many EFSM specifications, it is not practical to expand out the internal store. If the store is abstracted away the resultant sequences need not be feasible in the original EFSM since the abstraction process removes the preconditions from the transitions (see, for example, [18,36]). Further, it is often difficult to relate the fault coverage of the resultant FSM to that of the EFSM. Thus, each of these approaches has limitations.

When testing from an FSM M, it is often possible to produce a checking experiment: a test that is guaranteed to determine correctness under certain conditions (see, for example, [7,15,17,30,34]). Typically, it is assumed that the IUT behaves like some unknown FSM M' that has the same input and output alphabets as M and no more than m states for some predefined m. Thus, where it is practical to produce an FSM model from the specification, there exist test generation techniques that provide strong guarantees regarding the fault-detecting ability of the resultant test sequence.

### 2.3 Stream X-machines

X-machines were introduced by Eilenberg [11]. Later, Holcombe [19] proposed their use as a specification formalism. The stream X-machine formalism specifies a system as an EFSM. Stream X-machines provide a convenient standard formalism within which issues such as test generation may be considered. Further, they have been used to specify a range of systems (see, for example, [4,19–21,27]). Results regarding testing from a stream X-machine can be applied when testing from specifications written in other state based languages such as Statecharts (see, for example, [6]).

Associated with stream X-machines is a development and testing philosophy [21]. Under this philosophy, it is assumed that the system is built from a set of trusted components. These components may have been tested in a previous phase, such as unit testing, or they might be imported from a library. System development could proceed through a sequence of steps, each of which involves building larger components from smaller components that have already been developed (see, for example, [21]). Thus, the testing problem reduces to checking that these components have been combined in the correct way and so it might be seen as an approach to integration testing. This philosophy leads to methods that generate tests that are guaranteed to determine correctness

under certain design for test conditions (see, for example, [4,16,19–24,27]).

When testing from a stream X-machine M, it is normal to assume that the IUT behaves like some unknown stream X-machine  $M_I$ . This makes it possible to formally reason about test effectiveness. In testing it is desirable to apply a set of input sequences that, between them, determine whether the unknown model  $M_I$  is a correct implementation of M. This paper introduces a new algorithm that produces a test that, under certain design for test conditions, determines whether a deterministic implementation conforms to a specification in the form of a non-deterministic stream X-machine.

It is worth noting that, even where it is practical to produce an FSM from an EFSM by expanding out the store, the test resulting from applying FSM based techniques will normally be much larger than that produced using the stream X-machine methods. This is because the stream X-machine test techniques utilise the belief that the individual components are correct. They avoid the state explosion associated with expanding out the store and may be applied when the store is infinite.

# 3 Preliminaries and Example

### 3.1 Finite automata

A finite automaton (FA) N is defined by a tuple  $(S, s_0, Z, \delta, \Gamma)$  in which S is a finite set of states,  $s_0 \in S$  is the initial state, Z is the finite input alphabet,  $\delta$  is the state transfer relation of type  $S \times Z \leftrightarrow S$ , and  $\Gamma \subseteq S$  is the set of final states. If N receives an input  $z \in Z$  when in state  $s \in S$  it moves to some state in the set  $\delta(s,z)$ . Note that given sets A and B,  $A \leftrightarrow B$  denotes the set of relations between A and B and so may be considered to be equivalent to  $A \times B$ . Further, if relation r has type  $A \leftrightarrow B$  and  $a \in A$  then r(a) denotes the set of elements of B related to a under  $r: r(a) = \{b \in B \mid r(a,b)\}$ . The relation  $\delta$  may be extended to take an input sequence, giving the relation  $\delta^*$  defined below.

**Definition 1** Let  $\epsilon$  denote the empty sequence and  $z \in Z$ ,  $\overline{z} \in Z^*$ . The following define  $\delta^*$ .

$$\delta^*(s,\epsilon) = \{s\}$$

$$\delta^*(s, \overline{z}z) = \{ s' \mid \exists \, s''.s'' \in \delta^*(s, \overline{z}) \land s' \in \delta(s'', z) \}$$

Throughout this paper, a variable name with a line over it will denote a sequence. The FA N defines a language L(N), of words that can take N from its initial state to some final state, in the following way.

**Definition 2** Given a FA  $N = (S, s_0, Z, \delta, \Gamma)$  the language L(N) is defined as  $\{\overline{z} \in Z^* \mid \delta^*(s_0, \overline{z}) \cap \Gamma \neq \emptyset\}$ .

Further, given a state s of N, there is a corresponding language formed from words that take N from s to a final state.

**Definition 3** Given a FA  $N = (S, s_0, Z, \delta, \Gamma)$  and state  $s \in S$  the language  $L_N(s)$  is defined as  $\{\overline{z} \in Z^* \mid \delta^*(s, \overline{z}) \cap \Gamma \neq \varnothing\}$ .

Clearly

$$L(N) = L_N(s_0)$$

.

A FA is deterministic if for all  $s \in S$  and  $z \in Z$  there is at most one possible next state:  $\forall s \in S, z \in Z. \mid \delta(s,z) \mid \leq 1$ . Two FA are equivalent if they define the same language. Given FA N, there is some equivalent deterministic FA [32]. A deterministic FA (DFA) is minimal if there is no equivalent DFA with fewer states. Any FA may be rewritten to an equivalent minimal DFA [29]. It will thus be assumed that any FA considered is deterministic and minimal.

### 3.2 Stream X-machines

A stream X-machine is a form of extended finite state machine in which there is a set of states, the transitions between states are labelled with relations, and there is an internal memory. More formally, a stream X-machine is defined by a tuple  $(In, Out, S, Mem, \Phi, F, s_0, m_0, \Gamma)$  [21] in which:

- *In* is the input alphabet.

- Out is the output alphabet.

- S is the finite set of states.

- Mem is the memory. Mem need not be finite.

- $\Phi$  is a set of processing relations, each having type  $Mem \times In \leftrightarrow Out \times Mem$ .

- F is the next state relation of type  $S \times \Phi \leftrightarrow S$ .

- $s_0 \in S$  is the initial state.

- $m_0 \in Mem$  is the initial memory value.

- $\Gamma$  is the set of final states.

Essentially, the state transition structure of stream X-machine M determines a set L of sequences of relations from  $\Phi^*$ : the sequences that label walks from the initial state of M to some final state of M. Each of these sequences defines a relationship between input sequences and output sequences. The behaviour defined by M is the union of the relationships (of type  $In^* \leftrightarrow Out^*$ ) defined

by the sequences in L. This specified behaviour will be formally defined in Section 3.4 and will be illustrated by an example in Section 3.3. Note that traditional definitions of stream X-machines limit the sets In and Out to being finite. However, it transpires that the results regarding test generation do not require these restrictions to be in place. Therefore, in this paper, In and Out are allowed to be infinite.

The set  $\Phi$  is often called the *type* of M. This set denotes the set of relations from which M is built. Typically, each element of  $\Phi$  specifies components that may be used in the construction of the implementation. Since the philosophy behind stream X-machine test techniques is that the IUT is built from components that are known (or trusted) to be correct, the set  $\Phi$  places restrictions on the IUT.

Observe that the memory Mem need not correspond to the notion of the memory of a program. Rather, Mem models the passing of values between components as a (possibly infinite) memory. Thus, Mem might be formed from tuples, where each element of the tuple corresponds to either a global variable or a parameter that may be passed between two relations in  $\Phi$ .

The next state relation F can be extended, to take sequences from  $\Phi^*$ , to form the relation  $F^*$ . It is possible to allow a set of initial states, rather than a single initial state. However, allowing a set  $S_I$  of initial states does not significantly affect the test generation problem: a test may be devised by combining those produced for each possible initial state from  $S_I$ . Thus, to simplify the explanation, the definition of a stream X-machine will include one initial state only.

### 3.3 Example

This section introduces an example specification of a stream X machine for a simple calculation system. The example will be used throughout the paper to illustrate the approach to testing from non-deterministic stream X machines. The example has been chosen to illustrate the central issues with non-deterministic stream X machines. In order to do this, the example must contain at least two states which are not deterministically reachable and two states which are not pairwise distinguishable. These terms will be formally defined later. Informally, what this entails, is a stream X machine where there are two states for which there is no sequence of inputs which is guaranteed to reach them (not deterministically reachable) and there are two states for which there is no input sequence which is guaranteed to trigger an output that distinguishes them. Each of these two properties make testing harder and complicates the example.

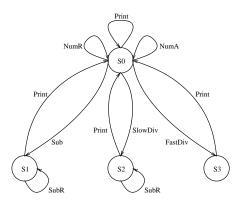

Fig. 1. A Simple Non-deterministic Division Calculator

The challenge is therefore to find a suitable example which has these properties, but which is not so complex as to lose its expository value. The example presented here is simplified in order to ensure that it adequately illustrates the definitions, concepts and testing process. The example is contrived in the sense that it is unlikely that such a simplistic calculating device would be built in practice, but is not so contrived that the design choices involved are without intuitive foundation.

The state structure of the calculator stream X-machine is pictured on Figure 1. In what follows, its input, output, memory and operations will be formally defined using the Z notation. The calculator has BUTTONS, Lights and a numeric keypad. Buttons are input devices used to select a particular behaviour. The calculator has a memory which consists of three non-negative integers: the accumulator (A), register (R) and index (I). Initially these three integers are set to zero. The relations used in the machine will now be described.

There are six buttons, in the set BUTTONS. The  $\mathcal{S}$  button, is used to request a subtraction operation, which subtracts the current value of the register from the current value of the accumulator, storing the result in the accumulator. The buttons represent inputs to the system. The  $\mathcal{R}$  button, is used to request a single repetition of the subtraction operation. The  $\mathcal{D}$  button, is used to request the division operation. The  $\mathcal{P}r$  button, is used to request the print operation. The  $\mathcal{N}A$  button, is used to indicate that a numeric input is to be stored in the Accumulator. The  $\mathcal{N}R$  button, is used to indicate that a numeric input is to be stored in the register. It is not possible to directly store a value in the index. The  $\mathcal{N}A$  and  $\mathcal{N}R$  button are used in conjunction with a numeric keypad which allows the user to enter a single non-negative number.

The calculator has four lights LSub, LSubR, LSlowDiv and LFastDiv, corresponding to the operations, Sub, SubR, SlowDiv and FastDiv. Each of these lights is illuminated when the corresponding operation is invoked. There is also an underflow light LUnderflow, which is illuminated when an attempt

is made to evaluate an expression which would lead to a negative result.

In addition to the lights, there is also a simple screen output device, which is capable of displaying up to two non-negative integers in the range storeable by the accumulator and register. This will be assumed to be the natural numbers,  $\mathbb{N}$ .

The operations NUMR and NUMA cause input to be read from the numeric keypad. The NUMR operation is triggered by  $\mathcal{N}R$ , while the NUMA operation is triggered by the  $\mathcal{N}A$  button. When the NUMR operation is executed the number previously read into the numeric keypad is stored in the register (R) and the value of the number read in is displayed on the screen. When the NUMA operation is executed, the number previously read into the numeric keypad is stored in the accumulator (A) and the value of the number read in is displayed on the screen.

Finally, at any point in the execution of the machine, the user can press the  $\mathcal{P}r$  button, causing the PRINT operation to be executed. This causes the value currently stored in the accumulator and register to be displayed on the screen.

The operations, Sub, Subr, SlowDiv and FastDiv perform simple computations on the values stored in the memory. The Sub operation, responds to the  $\mathcal{S}$  button, storing the results of subtracting the register from the accumulator (or zero if this would lead to a negative result).

The Subraction, responds to the  $\mathcal{R}$  button. It can be used in conjunction with the SLOWDIV operation to achieve division by repeated subtraction. If the value of the accumulator is greater than or equal to the value of the register, then the Subraction increases the index register by one and subtracts the register contents from the accumulator contents. This will happen if additional iterations are required to compute the integer division result by repeated subtraction. If the accumulator value is less then the register value then the operation does not affect any of the memory values but illuminates the LUnderflow light. This illumination signifies the end of a sequence of applications of the Subraction. In this way, should the user trigger repeated applications of the Subraction, by repeatedly pressing the  $\mathcal S$  button, the machine will compute integer division by repeated subtraction.

The FASTDIV operation, responds to the  $\mathcal{D}$  button. It stores the result of dividing the contents of the accumulator by the contents of the register using integer division and illuminates the LFastDiv light.

The SlowDiv operation, also responds to the  $\mathcal{D}$  button. It affects neither the accumulator nor the register, but stores zero in the index and illuminates the LSlowDiv light. The SlowDiv operation establishes a logical state in which it is possible to compute the result of dividing the contents of the accumulator

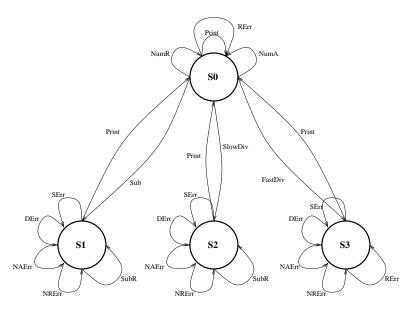

Fig. 2. The Completely Specified Non-deterministic Division Calculator

by the contents of the register.

This is achieved (albeit slowly) by repeated subtraction; the user must repeatedly invoke the Subraction until the LUnderflow light is illuminated.

In each state there is a set of operations {SERR, DERR, PERR, RERR, NAERR, NRERR} which have the 'no operation' effect (other than to light the error light, LError). Adding these operations to the state diagram, complicates the diagram (see Figure 2), but does not affect the essential core structure of the stream X machine specification depicted in Figure 1.

The specification is non-deterministic because either the FASTDIV operation or the SLOWDIV operation can be triggered by the  $\mathcal{D}$  button. A deterministic implementation must choose between these two.

The above definitions of operations are made more formal and are related back to the definition of a stream X machine in the Z specification which follows.

$$\begin{split} BUTTONS ::= \mathcal{R} \mid \mathcal{D} \mid \mathcal{S} \mid \mathcal{P}r \mid \mathcal{N}A \mid \mathcal{N}R \\ \text{Lights } ::= \mathsf{LSub} \mid \mathsf{LSubR} \mid \mathsf{LSlowDiv} \mid \mathsf{LFastDiv} \mid \mathsf{LUnderflow} \mid \mathsf{LError} \end{split}$$

The memory (the Mem component of the stream X Machine as defined in Section 3.2), consists of three components, the accumulator, A, the register, R and the index I.

The initial state of the memory ( $m_0$  in the definition in Section 3.2) is defined by the Schema below:

| InitialMemory   |

|-----------------|

| $\Delta Memory$ |

| A'=0            |

| R'=0            |

| I' = 0          |

In the following schemas, the input events (decorated with a?) correspond to the pressing of buttons, while the output events (decorated with!) correspond to the illumination of lights or the display of accumulator and register values on the screen. In terms of the definition of a stream X machine presented in Section 3.2, the input events form the set In, while the output events form the set Out.

The user functions PRINT, NUMR, NUMA, SUB, SUBR, SLOWDIV and FAST-DIV, form the set of operations (the set  $\Phi$  in the definition in Section 3.2) and are defined as follows:

| Print                              |  |  |

|------------------------------------|--|--|

| $\Xi Memory$                       |  |  |

| b?:BUTTONS                         |  |  |

| $r!: \mathbb{N} \times \mathbb{N}$ |  |  |

| $b? = \mathcal{P}r$                |  |  |

| r! = (A, R)                        |  |  |

SubR\_\_\_

$r! = \mathsf{LSub}$

b?: BUTTONS  $\Delta Memory$   $r!: \mathsf{Lights}$   $b? = \mathcal{S}$   $(A - R < 0 \ \land A' = I \ \land R' = R \ \land I' = I \ \land r! = \mathsf{LUnderflow}$   $\lor$   $A - R \ge 0 \ \land A' = A - R \ \land R' = R \ \land I' = I + 1 \ \land r! = \mathsf{LSubR})$

NUMR  $u? : BUTTONS \times \mathbb{N}$   $\Delta Memory$   $r! : \mathbb{N}$   $\exists i : \mathbb{N} \bullet u? = (\mathcal{N}R, i)$  A' = A

A' = A R' = i I' = I r! = i

NumA\_

$u?:BUTTONS\times \mathbb{N}$

$\Delta Memory$   $r! : \mathbb{N}$

$\exists i : \mathbb{N} \bullet u? = (\mathcal{N}A, i)$

A' = i

R' = R

I'=I

r! = i

FASTDIV b?: BUTTONS  $\Delta Memory$  r!: Lights  $b? = \mathcal{D}$   $(R > 0 \land A' = A/R) \lor (R = 0 \land A' = 0)$  R' = R I' = I  $r! = \mathsf{LFastDiv}$

b? : BUTTONS  $\Delta Memory$  r! : Lights b? =  $\mathcal{D}$  A' = A R' = R I' = 0 r! = LSlowDiv

In addition to the user functions above, there is a set of six 'error' functions which are triggered when the user attempts to invoke a function which has no effect. The presence of these functions makes the specification completely specified.

SERR b? : BUTTONS  $\Xi Memory$  r! : Lights b? = S r! = LError

DERR b?: BUTTONS  $\Xi Memory$  r!: Lights  $b? = \mathcal{D}$  r! = LError

```

PERR

b? : BUTTONS

\Xi Memory

r! : Lights

b? = \mathcal{P}r

r! = LError

```

```

RER

b? : BUTTONS

\Xi Memory

r! : Lights

b? = \mathcal{R}

r! = LError

```

```

NAERR

u?: BUTTONS \times \mathbb{N}

\Xi Memory

r!: Lights

\exists i: \mathbb{N} \bullet u? = (\mathcal{N}A, i)

r! = \mathsf{LError}

```

```

NRERR

u? : BUTTONS \times \mathbb{N}

\Xi Memory

r! : Lights

\exists i : \mathbb{N} \bullet u? = (\mathcal{N}R, i)

r! = \mathsf{LError}

```

# 3.4 Properties of stream X-machines

This section will describe a number of properties of stream X-machines that will be used throughout the paper. It will also define the semantics of stream X-machines.

A stream X-machine M can be represented by a finite automaton, called the associated automaton, that is defined below. Essentially, the associated automaton inherits the state and transition structure of the stream X-machine but has no internal memory. **Definition 4** Given stream X-machine  $M = (In, Out, S, Mem, \Phi, F, s_0, m_0, \Gamma)$ , the associated automaton A(M) is  $(S, s_0, \Phi, F, \Gamma)$ .

The stream X-machine M is minimal if A(M) is minimal. When looking at the problem of testing from a stream X-machine it is normal to assume that every state is a final state and thus  $\Gamma = S$  [21]. This is not usually a restriction when considering interactive systems. Since any non-deterministic finite automaton can be rewritten to form an equivalent minimal deterministic FA (DFA), it will be assumed that A(M) is a minimal DFA and thus that F is a function.

Given a sequence  $\overline{f}$  of elements from  $\Phi$ ,  $\|\overline{f}\|$  will denote the relation of type  $Mem \times In^* \leftrightarrow Out^* \times Mem$  induced by  $\overline{f}$ . Essentially,  $\|\overline{f}\|$  corresponds to the possible results of executing the sequence of relations from  $\overline{f}$  in the given order.

**Definition 5** Given a sequence  $\overline{g} \in \Phi^*$ ,  $\overline{g}$  induces the relation  $||\overline{g}||$ , of type  $Mem \times In^* \leftrightarrow Out^* \times Mem$ , defined by the following in which  $f \in \Phi$  and  $\overline{f} \in \Phi^*$ .

$$\|\epsilon\| = \{((m, \epsilon), (\epsilon, m)) \mid m \in Mem\}$$

$$\|\overline{f}f\| = \{((m, \overline{x}x), (\overline{y}y, m')) \mid \exists m'' \in Mem.((m, \overline{x}), (\overline{y}, m'')) \in \|\overline{f}\| \land ((m'', x), (y, m')) \in f\}$$

Consider, for example, the sequence < NUMR, NUMA > of operations from the calculator example. The first operation has an input consisting of an integer  $x_1$  and the pressing of the  $\mathcal{N}R$  button. It updates the register and outputs the value  $x_1$ . The second operation has an input consisting of an integer  $x_2$  and the pressing of the  $\mathcal{N}A$  button. It updates the accumulator and outputs the value  $x_2$ . Let the memory with A = a, R = r and I = i be denoted by the tuple (a, r, i). Thus, the following is the relation defined by < NUMR, NUMA >.

Since a stream X-machine starts with an initial memory  $m_0$ ,  $\overline{f}$  defines a relation  $\langle \overline{f} \rangle$  between input sequences and output sequences. This is formed by restricting the relation  $||\overline{f}||$  to the case where the initial memory is  $m_0$  and then abstracting away the final memory.

### Definition 6

$$\langle \overline{f} \rangle = \{ (\overline{x}, \overline{y}) \mid \exists m \in Mem.((m_0, \overline{x}), (\overline{y}, m)) \in ||\overline{f}|| \}$$

The calculator starts with memory (0,0,0). Thus  $\langle < \text{NumR}, \text{NumA} > \rangle$  is as follows:

$$\langle < \text{NumR}, \text{NumA} > \rangle = \{(< (\mathcal{N}R, x_1), (\mathcal{N}A, x_2) >, < x_1, x_2 >) \mid x_1 \in \mathbb{N} \land x_2 \in \mathbb{N}\}$$

The stream X-machine M can be seen as defining a relation between input sequences and output sequences. An input sequence  $\overline{x}$  is related to an output sequence  $\overline{y}$  if some sequence of consecutive arcs, from the initial state of M to a final state of M, gives a sequence of relations that allows  $\overline{y}$  to be produced in response to  $\overline{x}$  when the initial memory is  $m_0$ . The set of sequences of arcs from the initial state of M to a final state of M defines the regular language L(A(M)) and each sequence  $\overline{f} \in L(A(M))$  induces a relation  $\langle \overline{f} \rangle$  of type  $In^* \leftrightarrow Out^*$ . More formally, M defines a relation, denoted  $\lfloor M \rfloor$ , of type  $In^* \leftrightarrow Out^*$  defined in the following way.

### Definition 7

$$\lfloor M \rfloor = \bigcup_{\overline{f} \in L(A(M))} \langle \overline{f} \rangle$$

**Definition 8** Given a relation R of type  $A \leftrightarrow B$ , dom R denotes the set of values in A related to values in B under R.

$$dom R = \{ a \in A \mid \exists b.b \in B \land (a,b) \in R \}$$

The stream X-machine M has an input domain: the set of input sequences that are related to output sequences under |M|.

**Definition 9** Given a stream X-machine M, the input domain of M, denoted dom M, is defined by:

$$\operatorname{dom} M = \{\overline{x} \in \operatorname{In}^* \mid \exists \, \overline{y}. \overline{y} \in \operatorname{Out}^* \wedge (\overline{x}, \overline{y}) \in \lfloor M \rfloor \}$$

**Definition 10** Stream X-machine M is completely specified if and only if  $dom M = In^*$ .

It is straightforward to show that the stream X-machine given in Figure 2 is completely specified.

Where M is not completely specified, it is possible to complete  $\lfloor M \rfloor$ , to give  $\lfloor M \rfloor_{\perp}$ , using a symbol  $\perp \not\in In$  that represents the behaviour terminating with an error.  $\lfloor M \rfloor_{\perp}$  is defined by the following [16].

**Definition 11** Given input sequence  $\overline{x}$  and output sequence  $\overline{y}$ ,  $(\overline{x}, \overline{y}) \in \lfloor M \rfloor_{\perp}$  if and only if one of the following hold:

- (1)  $(\overline{x}, \overline{y}) \in \lfloor M \rfloor$ .

- (2)  $\overline{x} \notin dom M$ ,  $\overline{x} = \overline{x}_1 \overline{x}_2$  for some maximal length  $\overline{x}_1 \in dom M$ ,  $\overline{y} = \overline{y}_1 \perp$ , and  $(\overline{x}_1, \overline{y}_1) \in |M|$ .

The first rule deals with the case where M is defined on  $\overline{x}$  and the second rule deals with the case where M is not defined on  $\overline{x}$ . The second rule essentially says that the output sequence is found by following the sequence of outputs produced in response to the input sequence until a failure occurs. At this point the value  $\bot$  is produced and no more output is observed.

Throughout this paper I will denote the implementation under test. As is usual, it will be assumed that the input and output domains of I are the same as those of the specification. Thus, since it will be assumed that I is deterministic, I is a function from the set of input sequences to the set of output sequences. Thus I has type  $In^* \to Out^*$ .

There are certain classes of stream X-machines.

**Definition 12** Stream X-machine  $M = (In, Out, S, Mem, \Phi, F, s_0, m_0, \Gamma)$  is deterministic if and only if |M| is a (possibly partial) function.

Thus, if stream X-machine M is deterministic, for each input sequence  $\overline{x} \in In^*$  there is at most one output sequence  $\overline{y} \in Out^*$  such that  $(\overline{x}, \overline{y}) \in |M|$ .

A number of different structural properties of a stream X-machine may lead to non-determinism. It is possible to restrict the sources of non-determinism in the specification.

**Definition 13** Stream X-machine  $M = (In, Out, S, Mem, \Phi, F, s_0, m_0, \Gamma)$  is quasi-non-deterministic [16] if for all  $s \in S$  and  $f, f' \in \Phi$ , if  $(s, f), (s, f') \in dom F$  and  $f \neq f'$  then  $dom f \cap dom f' = \emptyset$ .

This means that, given the state, memory and input, at most one relation may be triggered. However, non-determinism may still occur through the relations not being functions. This restriction is applied by Hierons and Harman [16]. It will transpire that by removing this restriction we significantly alter the test generation problem.

# 3.5 Notions of correctness

The IUT I is equivalent to a stream X-machine M if and only if I and M define the same relation between input sequences and output sequences. This is the case if and only if  $I = \lfloor M \rfloor_{\perp}$ . Equivalence is the standard notion of correctness used where the specification and implementation are both deterministic.

When the specification is non-deterministic the appropriate notion of correctness is often weaker than equivalence. The specification gives a range of allowed behaviours and the behaviours in the IUT must be drawn from this. This alternative notion of correctness is often called conformance.

The IUT I conforms to stream X-machine M if and only if every input/output sequence (or trace) of I is also a trace of M. The following formally defines what it means for I to conform to M.

**Definition 14** I conforms to M if and only if  $I \subseteq \lfloor M \rfloor_{\perp}$ . I conforming to M will be denoted  $I \preceq M$ .

The following is an immediate consequence of the above definition.

**Proposition 1** Assuming I behaves like some (possibly unknown) stream X-machine  $M_I$  with the same input alphabet as M, I conforms to M if and only if  $\lfloor M_I \rfloor_{\perp} \subseteq \lfloor M \rfloor_{\perp}$ .

### 4 Testing and design for test conditions

When testing against a formal specification it is normal to assume that the implementation I is functionally equivalent to some element of a fault domain that contains a set of models described using a particular formal language (see, for example, [25]). When testing from a stream X-machine the fault domain contains stream X-machines: it is assumed that the implementation behaves like some unknown stream X-machine  $M_I$  with the same input and output alphabets, memory, and initial memory as M. Since we assume that it is known that the IUT I is deterministic,  $M_I$  must be deterministic. Further restrictions, called design for test conditions, are placed on M and the fault model.

It is worth briefly explaining why it may often be assumed that the model  $M_I$  has the same memory (Mem) as M. Recall that the memory models the values that may be passed between components from  $\Phi$ : it acts like a (possibly infinite) central store that may be accessed and updated by any element from  $\Phi$ . Since each component from  $M_I$  is known to conform to a component

from  $\Phi$  and the interfaces of these components are known, the components from  $M_I$  do not access or affect values outside of this central store. Thus, the memory/central store of  $M_I$  is contained within that of M. It is possible to assume that  $M_I$  has memory Mem since values in Mem that are not required by  $M_I$  have no influence on testing. It is also assumed that M and  $M_I$  are initialized with the same values for the memory.

The design for test conditions may be divided into two groups [16]: specify for test conditions that place restrictions on  $\Phi$ ; and test hypotheses that place restrictions on  $M_I$ . These conditions will be described in the following.

When testing, test input may be chosen from a special set [24]. This might also restrict the possible memory values met in testing. These notions, based on those described by Ipate and Holcombe [24], will now be defined.

**Definition 15** A test environment TE is some pair  $(\mathcal{M}, U)$ , where  $\mathcal{M} \subseteq Mem$  and  $U : \Phi \to \mathcal{P}(In)$ ; we write U(f) as  $U_f$ .

The design for test conditions will be defined in terms of  $\mathcal{T}E$ . Essentially  $\mathcal{T}E$  will be used to restrict the test input used: only input values from  $U_f$  will be used to try to trigger f. This weakens the overall design for test conditions by considering only some subset of values; those specified in  $\mathcal{T}E$ . Naturally, in some cases  $\mathcal{T}E$  will allow any input:  $\mathcal{M} = Mem$  and for all  $f \in \Phi$ ,  $U_f = In$ .

It will be important that, when testing using  $\mathcal{T}E$ , values outside  $\mathcal{M}$  are not met: the result of applying f with an input from  $U_f$ , when M has memory in  $\mathcal{M}$  must lead to M having a memory value from  $\mathcal{M}$ . This is guaranteed if  $\Phi$  is closed with respect to  $\mathcal{T}E$  [24].

**Definition 16**  $\Phi$  is closed with respect to  $\mathcal{T}E$  if  $m_0 \in \mathcal{M}$  and for all  $f \in \Phi$ ,  $x \in U_f$ ,  $m \in \mathcal{M}$ ,  $y \in Out$ , and  $m' \in Mem$ , if  $((m, x), (y, m')) \in f$  then  $m' \in \mathcal{M}$ .

The design for test conditions will now be described.

Informally,  $\Phi$  is output distinguishable with respect to  $\mathcal{T}E$  if when restricting testing to values allowed by  $\mathcal{T}E$ , the output determines which relation has been applied. That is, given any two different relations  $f_1, f_2 \in \Phi$ , a memory value  $m \in \mathcal{M}$ , and an input value  $x \in U_{f_1} \cup U_{f_2}$ , the two relations cannot lead to the same output value if given x when the memory is m. This property allows the tester to associate input/output behaviour with relations from  $\Phi$  [16,21].

**Definition 17**  $\Phi$  is output distinguishable with respect to  $\mathcal{T}E$  if for all  $f_1, f_2 \in \Phi$  such that  $f_1 \neq f_2$ , all  $x \in U_{f_1} \cup U_{f_2}$ , all  $y \in Out$ , and all  $m, m' \in \mathcal{M}$  such that  $((m, x), (y, m')) \in f_1$ , there does not exist  $m'' \in \mathcal{M}$  such that

$$((m, x), (y, m'')) \in f_2.$$

Informally,  $\Phi$  is observable with respect to TE if, when restricting testing to TE, the output from a relation can be used to determine the new memory value after its application. Observability allows the tester to determine the expected memory value based on the input and the output observed [16]. Without this property, it is difficult for the tester to determine an appropriate next input since this will typically depend on the current memory value.

**Definition 18**  $\Phi$  is observable with respect to  $\mathcal{T}E$  if and only if  $\forall f \in \Phi, m \in \mathcal{M}, x \in U_f$

$$(y_1, m_1), (y_2, m_2) \in f(m, x) \Rightarrow ((y_1 = y_2) \Rightarrow (m_1 = m_2)).$$

Possible ways of weakening this condition will be discussed in Section 9.

Informally  $\Phi$  is complete with respect to TE if for each  $f \in \Phi$ , the tester can always apply an input from  $U_f$ , that is capable of triggering f, as long as the current memory value is known and is from  $\mathcal{M}$ . Note that this does not require that there actually be a transition from every state labelled with f, just that if there is such a transition then it can be followed by issuing an input from  $U_f$  regardless of memory.

**Definition 19**  $\Phi$  *is* complete with respect to  $\mathcal{T}E$  *if*  $\forall$   $m \in \mathcal{M}$ ,  $f \in \Phi$ .  $\exists$   $x \in U_f.(m, x) \in dom f$ .

The following are the specify for test conditions. It is worth noting that they are weaker than those used by Hierons and Harman [16].

**Definition 20** If  $\Phi$  is the relation set of a non-deterministic stream X-machine  $M = (In, Out, S, Mem, \Phi, F, s_0, m_0, \Gamma)$ , for which A(M) is deterministic, and the test environment is TE then the specify for test conditions are:

- (1)  $\Phi$  is closed with respect to TE;

- (2)  $\Phi$  is output distinguishable with respect to TE;

- (3)  $\Phi$  is observable with respect to TE;

- (4)  $\Phi$  is complete with respect to TE.

These conditions differ from those used by Hierons and Harman [16] only in the introduction of the test environment TE. If TE allows all memory and input values, the specify for test conditions reduce to those previously given. However, as long as TE is closed with respect to  $\Phi$ , reducing the set of values allowed by TE weakens the specify for test conditions applied to M. Naturally, they introduce conditions on TE: not all choices of TE allow these specify for test conditions to be satisfied.

It has been noted that a stream X-machine which does not satisfy the specify for test conditions can always be rewritten to one that does satisfy these conditions [21]. This rewriting might involve the addition of new input and output values. Potentially these could either be removed or hidden when the system is released.

Consider the example given in Figure 2. In this paper we will use the test environment TE = (Mem, In): we will not restrict the input values that can be used in testing. The presence of the lights ensures that the operations are pairwise output distinguishable. The error operations guarantee that the specification is completely specified.

Since the test environment allows any memory value from Mem,  $\Phi$  is immediately closed with respect to  $\mathcal{T}E$ : an operation cannot lead to a memory value outside the set given in  $\mathcal{T}E$  since this set contains all the possible memory values. The print operation, Print and the six 'error' operations, SERR, DERR, PERR, RERR, NAERR and NRERR do not change the value of Mem and so these are vacuously observable. Since all the relations are actually functions, they are automatically observable.

To be complete with respect to TE, every operation must have some input which triggers it in every memory from Mem. This can easily be verified. Thus, the example in Figure 2 satisfies the specify for test conditions.

The test hypotheses will now be described. It will be assumed that I behaves like some unknown stream X-machine  $M_I = (In, Out, S', Mem, \Phi', F', s'_0, m_0, \Gamma')$ . When testing from a deterministic stream X-machine it is normal to assume that M and  $M_I$  have the same sets of functions: faults may only occur through an incorrect state structure [21]. This assumption relates to either reusing trusted components or building a system from components that have been thoroughly tested. When testing for conformance, rather than equivalence, this assumption is relaxed to the assumption that each element of the set  $\Phi'$  of relations of  $M_I$  conforms to some relation in M. A relation f' conforms to a relation f if and only if f' and f have the same preconditions and every pair in f' is also contained in f. A relation  $f' \in \Phi'$  conforming to a relation  $f \in \Phi$  will be denoted  $f' \leq f$ .

**Definition 21** Given  $f' \in \Phi'$  and  $f \in \Phi$ ,  $f' \leq f$  if and only if dom f' = dom f and  $f' \subseteq f$ . Further,  $\Phi' \leq \Phi$  if and only if  $\forall f' \in \Phi' \exists f \in \Phi. f' \leq f$ .

Informally, this means that f' conforms to f if they have the same input domain and any behaviour allowed by f' is also allowed by f. It is possible to extend  $\leq$  to take sequences of relations, giving  $\leq$ \* [16].

Suppose  $M_I$  has a relation set  $\Phi'$  with  $\Phi' \leq \Phi$ . In a slight abuse of notation, it is possible to talk about  $\Phi'$  satisfying the specify for test conditions with

$\mathcal{T}E$ : for a relation  $f' \in \Phi'$   $U_{f'} = U_f$  for the (unique<sup>1</sup>) relation  $f \in \Phi$  with  $f' \leq f$ . Interestingly, if  $M_I$  has a relation set  $\Phi'$  with  $\Phi' \leq \Phi$ , if M satisfies the specify for test conditions then  $M_I$  must also satisfy some of these. The following result is an immediate consequence of the definitions.

**Proposition 2** Suppose stream X-machine M, with relation set  $\Phi$ , satisfies the specify for test conditions. If relation set  $\Phi' \leq \Phi$  then:

- (1)  $\Phi'$  is closed with respect to TE;

- (2)  $\Phi'$  is observable with respect to TE;

- (3)  $\Phi'$  is complete with respect to TE.

It is now possible to formally state the two test hypotheses.

**Definition 22** If  $M = (In, Out, S, Mem, \Phi, F, s_0, m_0, \Gamma)$  is a non-deterministic stream X-machine and I is the deterministic implementation to be tested against M then the test hypotheses are:

- (1) I behaves like some (unknown) minimal deterministic stream X-machine  $M_I = (In, Out, S', Mem, \Phi', F', s'_0, m_0, \Gamma')$ , for which  $A(M_I)$  is deterministic, such that  $\Phi' < \Phi$ .

- (2) There is some known n' such that  $M_I$  has at most n' states.

The design for test conditions given by Hierons and Harman [16] are a generalisation of those traditionally used when testing against deterministic stream X-machines. Thus these two test hypotheses together with the specify for test conditions are a generalisation of those traditionally used with deterministic stream X-machines.

It is often assumed that M is completely specified [24] and throughout the rest of the paper this assumption will be made. Where M is not completely specified, it may be converted into a completely specified stream X-machine by adding an error state and error messages. In order to maintain output distinguishability it may be necessary to use more than one error message. It will also be assumed that, for each input sequence, I has some corresponding behaviour and thus that  $M_I$  is completely specified. Section 9 will consider how these restrictions might be relaxed.

# 5 Characterising conformance

This section will characterise what it means for I to conform to M in terms of a relationship between the associated automata  $A(M_I)$ , the abstraction of the

$<sup>^{1}</sup>$  The uniqueness of f will be proved in Lemma 6.

implementation automaton, and A(M), the abstraction of the specification. An algorithm that generates a test, that determines whether this relationship holds, will be given in Section 8.

Before developing the characterisation, those already considered in the literature will be described. For deterministic stream X-machines the characterisation is simple: I conforms to M if and only if A(M) and  $A(M_I)$  are equivalent [21]. Recent work has, however, considered the problem of testing against a non-deterministic stream X-machine.

It has been proved that testing to determine whether an implementation is equivalent to a non-deterministic stream X-machine may again be seen as a process of determining whether A(M) and  $A(M_I)$  are equivalent [24]. However, this is not the case when testing to determine whether an implementation I conforms to a quasi-non-deterministic stream X-machine M [16] since A(M) and  $A(M_I)$  could have different alphabets. To be precise, the relation set  $\Phi'$  of  $M_I$  forms the alphabet of the automaton  $A(M_I)$  and this need not be the same as the relation set  $\Phi$  of M which forms the alphabet of the automaton A(M).

A consequence of the design for test conditions (Lemma 6 below) is that for every  $f' \in \Phi'$  there is exactly one  $f \in \Phi$  such that  $f' \leq f$ . This relation f will be denoted  $abs_{\Phi}(f')$ . When comparing sequences of labels from A(M) and  $A(M_I)$ , it is useful to introduce the abstraction,  $Abs(M_I)$ , of  $A(M_I)$  formed by replacing each relation  $f' \in \Phi'$  of  $M_I$  by the unique relation  $abs_{\Phi}(f) \in \Phi$ . Then, when M is quasi-non-deterministic, I conforms to M if and only if  $Abs(M_I)$  is equivalent to A(M) [16].  $Abs(M_I)$  may be formally defined in the following way.

**Definition 23** Given stream X-machine  $M_I = (In, Out, S', Mem, \Phi', F', s'_0, m_0, \Gamma')$  and relation set  $\Phi$  such that  $\Phi' \leq \Phi$ ,  $Abs(M_I)$  is the automaton  $(S', s'_0, \Phi, F'', \Gamma')$  in which the function F'' is defined by the following.

$$F'' = \{((s_i', abs_\Phi(f')), s_j') \mid ((s_i', f'), s_j') \in F'\}$$

Note that while Abs is parameterised by  $\Phi$ , this parameter will remain implicit.

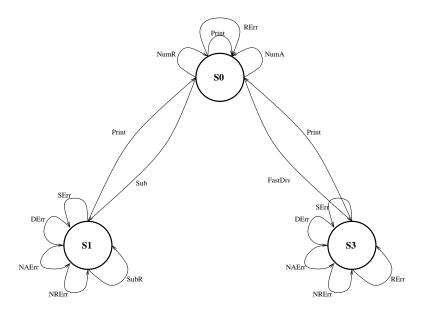

The situation considered in this paper is quite different from that considered previously. This is because I may conform to M even if A(M) and  $Abs(M_I)$  have very different structures. For example, if relations  $f_1$  and  $f_2$  leave a state s of M and dom  $f_1 = \text{dom } f_2$ , then it is possible that I conforms to M and yet  $M_I$  has only one relation f' leaving a corresponding state ( $f' \leq f_1$  or  $f' \leq f_2$ ). This is illustrated by the deterministic stream X-machine in Figure 3 that conforms to the stream X-machine given in Figure 2 but has a different structure; the slow division operation is removed, so that the division operation selected by

Fig. 3. A Correct Implementation

the  $\mathcal{D}$  button is always the fast division operation. This situation cannot occur either when M is quasi-non-deterministic or when correctness is considered to be equivalence rather than conformance.

To further demonstrate how M and  $M_I$  may have different structures even if  $M_I$  conforms to M, consider the following class of examples. Given a set  $\Phi$  of processing relations  $M_{\Phi}$  is the chaos machine with one state  $s_0$  and in which, for all  $f \in \Phi$ , there is a transition from  $s_0$  to  $s_0$  with label f. Assuming  $M_{\Phi}$  is completely specified, any completely specified stream X-machine with relation set  $\Phi'$ , with  $\Phi' \leq \Phi$ , conforms to  $M_{\Phi}$ . The restrictions applied in previous work did not allow such situations to occur.

Given that  $M_I$  may conform to M and yet have a radically different structure, the first challenge is to determine how  $M_I$  and M must relate in order for I to conform to M. Before stating this relationship, the notion of triggering a sequence  $\overline{f} \in \Phi^*$  in a manner that is consistent with the test environment  $\mathcal{T}E$ , will be defined and some results will be proved. Essentially, an input/output sequence  $\overline{x}/\overline{y}$  triggers  $\overline{f} \in \Phi^*$  in a manner that is consistent with  $\mathcal{T}E$  if each input is contained within the appropriate  $U_{f_i}$  and  $\overline{x}/\overline{y}$  is contained in the relation of type  $In^* \leftrightarrow Out^*$  defined by  $\overline{f}$ .

**Definition 24** Input/output sequence  $\overline{x}/\overline{y} = x_1, \ldots, x_k/y_1, \ldots, y_k$  is consistent with TE for  $\overline{f} = f_1, \ldots, f_k \in \Phi^*$  if there exists  $m_1, \ldots, m_k \in \mathcal{M}$  such that, for all  $1 \leq i \leq k$ , the following hold

(1)

$$x_i \in U_{f_i}$$

(2)  $((m_{i-1}, x_i), (y_i, m_i)) \in f_i$

Note that this means that if  $\overline{x}/\overline{y}$  is consistent with the test environment TE for  $\overline{f}$  then  $(\overline{x}, \overline{y}) \in \langle \overline{f} \rangle$ .

We will now give some preliminary results which will be used, in Theorem 7, to define how  $Abs(M_I)$  and A(M) must relate in order for I to conform to M.

The following shows that every sequence from  $\Phi^*$  has some input/output sequence that is consistent with TE. This property allows testing to be restricted to using values from TE.

**Lemma 3** Suppose the design for test conditions hold. Then given  $\overline{f} \in \Phi^*$  there is some input/output sequence  $\overline{x}/\overline{y}$  that is consistent with TE for  $\overline{f}$ .

### Proof

This follows using proof by induction on the length of  $\overline{f}$  and from  $\Phi$  being closed and complete with respect to TE.

The following shows that given a sequence of relations, that conforms to  $\overline{f}$ , it is possible to execute this sequence using values from  $\mathcal{T}E$ .

**Lemma 4** Suppose the design for test conditions hold. Then given  $\overline{f} \in \Phi^*$  and  $\overline{f}' \in \Phi'^*$ , with  $\overline{f}' \leq^* \overline{f}$ , there is some input/output sequence  $\overline{x}/\overline{y}$  that is consistent with the test environment TE for  $\overline{f}$  such that  $(\overline{x}, \overline{y}) \in \langle \overline{f}' \rangle$ .

### Proof

Proof by induction on the length of  $\overline{f}$ . Clearly the result holds for the base case, the empty sequence.

Suppose the results hold for all sequences from  $\Phi^*$  with length less than k  $(k \geq 1)$  and suppose  $\overline{f}$  has length k. Then  $\overline{f} = \overline{f}_1 f_2$  and  $\overline{f}' = \overline{f}'_1 f'_2$ , where  $\overline{f}'_1 \leq^* \overline{f}_1$  and  $f'_2 \leq f_2$ . By the inductive hypothesis, there exist some input/output sequence  $\overline{x}_1/\overline{y}_1$  that is consistent with TE for  $\overline{f}_1$  such that  $(\overline{x}_1, \overline{y}_1) \in \langle \overline{f}'_1 \rangle$ . Let m denote the memory after  $\overline{f}'_1$  is triggered with input  $\overline{x}_1$  to produce output  $\overline{y}_1$ . By Proposition 2,  $\Phi'$  is observable with respect to TE and so m is uniquely defined. By the definition of  $\leq$  and the observability of  $\Phi$ , m is also the memory after  $\overline{f}_1$  is triggered with input  $\overline{x}_1$  to produce output  $\overline{y}_1$ .

Since  $\Phi$  is closed with respect to  $\mathcal{T}E$ ,  $m \in \mathcal{M}$ . Observe that since  $\Phi$  is complete with respect to  $\mathcal{T}E$ , there exists  $x_2 \in U_{f_2}$  such that  $(m, x_2) \in \text{dom } f_2$ . Suppose  $f'_2$  responds to  $x_2$  with output  $y_2$  when in memory m. Then  $\overline{x}_1 x_2 / \overline{y}_1 y_2$  is consistent with  $\mathcal{T}E$  for  $\overline{f}$  and  $(\overline{x}_1 x_2, \overline{y}_1 y_2) \in \langle \overline{f}' \rangle$ . The result thus follows.  $\square$

**Lemma 5** Suppose the design for test conditions hold. Suppose also that  $\overline{f}, \overline{g}$  are non-empty sequences from  $\Phi^*$  such that there exists  $(\overline{x}, \overline{y}) \in \langle \overline{f} \rangle \cap \langle \overline{g} \rangle$  that

is consistent with the test environment TE for  $\overline{f}$ . Then  $\overline{f} = \overline{g}$ .

Proof

Proof by induction on the length of  $\overline{f}$ . Clearly the result holds for the base case, the empty sequence.

Suppose the results hold for all sequences from  $\Phi^*$  with length less than k  $(k \geq 1)$  and suppose  $\overline{f}$  has length k. Then  $\overline{f} = \overline{f}_1 f$  and  $\overline{g} = \overline{g}_1 g$ , for some  $\overline{f}_1, \overline{g}_1 \in \Phi^*$  and  $f, g \in \Phi$ . Further,  $\overline{x} = \overline{x}_1 x$  and  $\overline{y} = \overline{y}_1 y$  for some  $\overline{x}_1 \in X^*$ ,  $x \in X$ ,  $\overline{y}_1 \in Y^*$ , and  $y \in Y$ . Clearly  $(\overline{x}_1, \overline{y}_1)$  is consistent with TE for  $\overline{f}_1$ . Thus, by the inductive hypothesis,  $\overline{f}_1 = \overline{g}_1$ .

Let m denote the unique memory value such that  $((m_0, \overline{x}_1), (\overline{y}_1, m)) \in ||\overline{f}_1||$ . Then  $((m, x), (y, m')) \in f$  and  $((m, x), (y, m'')) \in g$  for some  $m', m'' \in Mem$ . Since  $(\overline{x}, \overline{y})$  is consistent with  $\mathcal{T}E$  for  $\overline{f}$ , and  $\Phi$  is closed with respect to  $\mathcal{T}E$ ,  $m \in \mathcal{M}$ . Further, since  $(\overline{x}, \overline{y})$  is consistent with  $\mathcal{T}E$  for  $\overline{f}$ ,  $x \in U_f$ . The result now follows by observing that, since  $\Phi$  is output distinguishable with respect to  $\mathcal{T}E$ , f = g.

The following shows that  $abs_{\Phi}$  and thus  $Abs(M_I)$  is uniquely defined.

**Lemma 6** Suppose the design for test conditions hold. If  $\overline{f}' \in \Phi'^*$ , then there is exactly one sequence  $\overline{f}$  in  $\Phi^*$  with  $\overline{f}' \leq^* \overline{f}$ .

Proof

This follows from Lemmas 4 and 5.

The following states how M and  $M_I$  must relate for I to conform to M.

**Theorem 7** Suppose M is a stream X-machine that satisfies the specify for test conditions and I behaves like some deterministic stream X-machine  $M_I$  that satisfies the test hypotheses. I conforms to M if and only if the following conditions hold:

- (1)  $L(Abs(M_I)) \subseteq L(A(M))$

- (2)  $dom M = dom M_I$

Proof

Case 1:  $\Rightarrow$

Suppose I conforms to M. By definition, dom  $M = \text{dom } M_I$ . Thus it is sufficient to prove that  $L(Abs(M_I)) \subseteq L(A(M))$ . Proof by contradiction will be used: suppose there exists  $\overline{f} \in L(Abs(M_I)) \setminus L(A(M))$ . Thus there is some  $\overline{f}' \in L(A(M_I))$  such that  $\overline{f}' \leq^* \overline{f}$ .

By Lemma 4 there is some  $(\overline{x}, \overline{y}) \in \langle \overline{f}' \rangle$  that is consistent with TE for  $\overline{f}$ . Since  $(\overline{x}, \overline{y}) \in \lfloor M_I \rfloor$  and I conforms to M,  $(\overline{x}, \overline{y}) \in \lfloor M \rfloor$ . Thus, there exists  $\overline{f}_0 \in L(A(M))$  with  $(\overline{x}, \overline{y}) \in \langle \overline{f}_0 \rangle$ . Thus  $(\overline{x}, \overline{y}) \in \langle \overline{f}_0 \rangle$  and  $(\overline{x}, \overline{y}) \in \langle \overline{f} \rangle$  and so, by Lemma 5,  $\overline{f}_0 = \overline{f}$ . Thus  $\overline{f} \in L(A(M))$ , providing a contradiction as required.

Case 2:  $\Leftarrow$

Proof by contradiction: suppose conditions 1 and 2 hold but I does not conform to M. Then there exists minimal length  $\overline{x} \in In^*$  and some sequence  $\overline{y}$ , of outputs possibly followed by  $\bot$ , such that  $(\overline{x}, \overline{y}) \in \lfloor M_I \rfloor_\bot$  and  $(\overline{x}, \overline{y}) \notin \lfloor M \rfloor_\bot$ . Since dom  $M = \text{dom } M_I$  and  $\overline{x}$  is minimal,  $(\overline{x}, \overline{y}) \in \lfloor M_I \rfloor \setminus \lfloor M \rfloor$ . Now consider sequence  $\overline{f}' \in L(A(M_I))$  such that  $(\overline{x}, \overline{y}) \in \langle \overline{f}' \rangle$ . By condition 1 there is some  $\overline{f} \in L(A(M))$  such that  $\overline{f}' \leq^* \overline{f}$ . Thus, since  $(\overline{x}, \overline{y}) \in \langle \overline{f}' \rangle$  and  $\overline{f}' \leq^* \overline{f}$ ,  $(\overline{x}, \overline{y}) \in \langle \overline{f} \rangle$ . From this it follows that  $(\overline{x}, \overline{y}) \in \lfloor M \rfloor$ , providing a contradiction as required.

Since M and  $M_I$  are completely specified, the second condition is automatic.

**Corollary 8** If M is a completely specified stream X-machine that satisfies the specify for test conditions, and I behaves like some completely specified deterministic stream X-machine  $M_I$  that satisfies the test hypotheses, I conforms to M if and only if  $L(Abs(M_I)) \subseteq L(A(M))$ .

Proof

Since  $M_I$  is completely specified dom  $M_I = In^*$ . The result thus follows from Theorem 7.

The verification problem is now expressed as that of deciding whether  $L(Abs(M_I)) \subseteq L(A(M))$ . In Section 8 we will show how a finite test may be used to decide this.

# 6 The test process

This section will define the test process, that takes some  $\overline{f} \in \Phi^*$  and tests the black-box implementation to determine whether  $\overline{f} \in L(Abs(M_I))$ . The test process will thus be used to determine whether some set of sequences from  $\Phi^*$  is contained in  $L(Abs(M_I))$ . Section 8.2 will consider the problem of deriving some set  $\mathcal{T}$  such that  $L(Abs(M_I)) \subseteq L(A(M))$  if and only if  $\mathcal{T} \subseteq L(Abs(M_I))$ . Once such a set  $\mathcal{T}$  has been found, we may determine whether the IUT conforms to M by applying the test process to the IUT with each sequence from  $\mathcal{T}$ . This leads to the IUT being executed with a set of test

sequences, each test sequence corresponding to some element of  $\mathcal{T}$ .

As with the quasi-non-deterministic case [16] the test process is adaptive: the next input depends upon the previous output observed. It thus produces a pair containing an input sequence and the corresponding output sequence observed in testing. Essentially, given  $\overline{f}$ , a test process tries to find some  $(\overline{x}, \overline{y})$ that is consistent with the test environment TE for  $\overline{f}$ . If such a  $(\overline{x}, \overline{y})$  can be found,  $\overline{f}$  must be contained in  $L(Abs(M_I))$ . Since there may be more than one acceptable input at some point, there can be more than one possible test process.

**Definition 25** A test process for a non-deterministic stream X-machine M. with test environment TE, is a function t of type  $\Phi^* \to In^* \times Out^*$  that satisfies the following conditions:

- (1)  $t(\epsilon) = (\epsilon, \epsilon)$ .

- (2) Suppose  $\overline{f} \in L(A(M)), \ t(\overline{f}) = (\overline{x}_1, \overline{y}_1), \ and \ ((m_0, \overline{x}_1), (\overline{y}_1, m')) \in \|\overline{f}\|.$ Then there is some  $x \in U_f$  such that  $(m', x) \in dom f$ , and if I produces output y in response to the input of x after  $\overline{x}_1/\overline{y}_1$ , then  $t(\overline{f}f) =$

- (3) Suppose  $\overline{f} \in L(A(M))$  and  $t(\overline{f}) = (\overline{x}_1, \overline{y}_1)$ . If  $\neg \exists m \in Mem.((m_0, \overline{x}_1), (\overline{y}_1, m')) \in$  $\|\overline{f}\|, \ t(\overline{f}f) = (\overline{x}_1, \overline{y}_1).$ (4) If  $\overline{f} \notin L(A(M)), \ t(\overline{f}f) = t(\overline{f}).$

Throughout this paper we assume the existence of a test process t.

The first rule is the base case, stating that testing based on the empty sequence requires no input and produces no output. The second and third rules are recursive cases, explaining how the test for sequence  $\overline{f}f$  ( $\overline{f} \in \Phi^*$ ,  $f \in \Phi$ ) may be defined in terms of  $t(\overline{f})$ . The second rule gives the case where some  $\overline{f}' \leq^* \overline{f}$  has been triggered by  $t(\overline{f})$ : here the sequence is extended by some value from  $U_f$  that should trigger f. The third rule covers the case where  $t(\overline{f})$ has triggered some other sequence  $\overline{f}' \not\leq^* \overline{f}$ . In this paper the test process will be used to decide membership of  $L(Abs(M_I))$ , the language defined by the abstraction of the implementation machine, and thus, since at this point it has been determined that  $\overline{f}$  is not contained in  $L(Abs(M_I))$  the test need not be extended. The final rule states how a sequence  $\overline{q} \in \Phi^*$  may be pruned, based on the observation that if there is some initial subsequence  $\overline{f}$  of  $\overline{g}$  such that  $\overline{f} \notin L(A(M))$  then it is not necessary for the test process to test beyond  $\overline{f}$ : it is sufficient to decide whether  $\overline{f} \in L(Abs(M_I))$ . Note that I is an implicit parameter of the test process t.

Suppose the test process is applied to a sequence  $\overline{f} = f_1, \dots, f_k$  from the language L(A(M)) defined by the specification. The test process follows a sequence of steps. At the ith step, the test process produces an input  $x_i$  from

$U_{f_i}$  that can trigger  $f_i$ , given the current memory. The input  $x_i$  is sent to the IUT I and the output is observed. From this, the memory after the transition may be determined.

The test process is not a function from  $\Phi^*$  to input sequences: the next input used depends upon the output received in response to previous input. This is due to non-determinism in M and the fact that the next input will typically depend upon the memory value that has resulted from the previous behaviour. This memory value may be determined from the input/output behaviour since  $\Phi$  is observable with respect to TE.

The following results explain how the test process may be used to explore the relationship between  $L(Abs(M_I))$ , the language defined by the abstraction of the implementation, and L(A(M)), the language defined by the specification.

**Lemma 9** Suppose M and  $M_I$  satisfy the design for test conditions, t is a test process,  $\overline{f} \in \Phi^*$  and  $(\overline{x}, \overline{y}) = t(\overline{f})$ . If  $(\overline{x}, \overline{y}) \in \langle \overline{f} \rangle$  then the sequence  $\overline{f}' \in L(A(M_I))$  with  $(\overline{x}, \overline{y}) \in \langle \overline{f}' \rangle$  satisfies  $\overline{f}' \leq^* \overline{f}$ .

# Proof

By the definition of a test process,  $\overline{x}/\overline{y}$  is consistent with  $\mathcal{T}E$  for  $\overline{f}$ . Consider the unique sequence  $\overline{f}_1 \in \Phi^*$  with  $\overline{f}' \leq^* \overline{f}_1$ . Then  $(\overline{x}, \overline{y}) \in \langle \overline{f}_1 \rangle \cap \langle \overline{f} \rangle$ . The result now follows from Lemma 5.

Note that a consequence of this result is that, under the conditions specified, we know that  $\overline{f} \in L(Abs(M_I))$ . The following shows the converse.

**Lemma 10** Suppose M and  $M_I$  satisfy the design for test conditions, t is a test process,  $\overline{f} \in \Phi^*$  and  $(\overline{x}, \overline{y}) = t(\overline{f})$ . If  $(\overline{x}, \overline{y}) \notin \langle \overline{f} \rangle$  then  $\overline{f} \notin L(Abs(M_I))$ .

### Proof

It is sufficient to prove that  $\overline{f} \in L(Abs(M_I)) \Rightarrow t(\overline{f}) \in \langle \overline{f} \rangle$ . This will be proved by induction on the length of  $\overline{f}$ . The result clearly holds for the base case,  $\epsilon$ .

Suppose the result holds for every sequence of length less than  $k, k > 0, \overline{f}$  has length k, and  $\overline{f} \in L(Abs(M_I))$ . Then  $\overline{f} = \overline{f}_1 f$  for some  $f \in \Phi$ ,  $\overline{f}_1 \in \Phi^*$ . Let  $\overline{x} = \overline{x}_1 x$  and  $\overline{y} = \overline{y}_1 y$  for some  $x \in In, y \in Out$ .

Since  $\overline{f} \in L(Abs(M_I))$ ,  $\overline{f}_1 \in L(Abs(M_I))$ . By the inductive hypothesis,  $(\overline{x}_1, \overline{y}_1) \in \langle \overline{f}_1 \rangle$ . Suppose that  $\overline{f}_1$  leads to memory m when triggered from the initial memory  $m_0$  with input  $\overline{x}_1$  and producing output  $\overline{y}_1$ . Since  $\Phi$  is output distinguishable with respect to TE, the behaviour  $\overline{x}/\overline{y}$  in  $M_I$  can only occur through some  $\overline{f}'_1 \in L(A(M_I))$  with  $\overline{f}'_1 \leq^* \overline{f}_1$ . Since  $\Phi$  is observable with respect to TE the memory of  $M_I$  is m after  $\overline{f}'_1$  and thus is m after  $\overline{x}_1/\overline{y}_1$ . Since  $\Phi$  is closed

with respect to TE,  $m \in \mathcal{M}$ .

Now consider the input of x in  $M_I$  after  $\overline{x}_1/\overline{y}_1$ . By the definition of t,  $x \in U_f$  and  $(m, x) \in \text{dom } f$ . Since  $M_I$  is deterministic,  $\overline{f}_1 f \in L(Abs(M_I))$ , and  $\Phi$  is observable with respect to TE, the input of x in  $M_I$  after  $\overline{x}_1/\overline{y}_1$  must trigger some  $f' \leq f$ ,  $f' \in \Phi'$ , and so there exists  $m' \in Mem$  such that  $((m, x), (y, m')) \in f'$ . Thus,  $(\overline{x}, \overline{y}) \in \langle \overline{f}'_1 f' \rangle$ . The result thus follows from observing that  $\overline{f}'_1 f' \leq^* \overline{f}$ .

# 7 Reaching and Distinguishing States

This section will initially consider the problem of finding a sequence from  $\Phi^*$  that reaches a state s of the specification M and that must be implemented in the model  $M_I$  of the IUT if  $M_I$  conforms to M. The situation considered in this paper makes these issues significantly different from those considered in previous work. It will then consider the problem of finding sequences from  $\Phi^*$  that distinguish the states of A(M). Both of these types of sequences will be useful in test generation.

Before considering the problems of reaching and distinguishing states of A(M), the notion of a sequence  $\overline{f}$  being implemented in  $M_I$  will be defined.

**Definition 26** A sequence  $\overline{f} \in \Phi^*$  is implemented from state  $s_i'$  of  $M_I$  if  $\overline{f} \in L_{Abs(M_I)}(s_i')$ . A sequence  $\overline{f} \in \Phi^*$  is implemented in  $M_I$  if it is implemented from the initial state of  $M_I$ .

## 7.1 Reaching states of M

Due to non-determinism, in some cases a sequence  $\overline{f}$  from M need not be implemented in  $M_I$  even if I conforms to M. This may happen where the input domain of  $\overline{f}$  intersects the input domain of other sequences from L(A(M)). However, given a state s of M, it may be possible to identify sequences that must be implemented from any state of  $M_I$  that corresponds to s if I conforms to M. These are the sequences in the set  $LD_M(s)$  defined below.

**Definition 27** A sequence  $\overline{f} = f_1, \ldots, f_k \in L_{A(M)}(s)$  is contained in  $LD_M(s)$  if and only if for all  $m \in \mathcal{M}$  and  $\overline{x} = x_1, \ldots, x_k, x_i \in U_{f_i}$  for all  $i, 1 \leq i \leq k$ , such that  $(m, \overline{x}) \in dom\overline{f}$  the following holds

$$(m, \overline{x}) \not\in \bigcup_{\overline{g} \in (L_{A(M)}(s) \setminus \{\overline{f}\})} dom \overline{g}$$

A consequence of this definition is that for each memory,  $m \in \mathcal{M}$ , and input sequence  $\overline{x}$  that could be used by a test process to try to trigger  $\overline{f}$ ,  $(m, \overline{x})$  is in the input domain of  $\overline{f}$  only. Thus, if  $M_I$  conforms to M then the behaviour of  $M_I$  in response to  $\overline{x}$ , when it is in a state s' corresponding to s and has memory m, must be consistent with  $\overline{f}$ . Since the input sequence  $\overline{x}$  uses values from the appropriate  $U_{f_i}$ , if the corresponding behaviour is seen in  $M_I$  then, due to output distinguishability with respect to  $\mathcal{T}E$ , it can only have arisen through the execution of some  $\overline{f}'$  with  $\overline{f}' \leq^* \overline{f}$ . From this it is possible to deduce that  $\overline{f} \in L_{Abs(M_I)}(s')$ .

Interestingly, the above condition may be weakened: it is sufficient that for each  $m \in \mathcal{M}$  there is some such input sequence  $\overline{x}$ . Such a definition might state that a sequence  $\overline{f} = f_1, \ldots, f_k \in L_{A(M)}(s)$  is contained in  $LD'_M(s)$  if and only if for all  $m \in \mathcal{M}$  there exists  $\overline{x} = x_1, \ldots, x_k, x_i \in U_{f_i}$  such that  $(m, \overline{x}) \in \text{dom } \overline{f}$  and the following holds.