3471

# **International Journal of Electrical and Computer Engineering (IJECE)**

Vol. 8, No. 5, October 2018, pp. 3471~3483

ISSN: 2088-8708, DOI: 10.11591/ijece.v8i5.pp3471-3483

# Performance Comparison of Multi Input Capacitor Converter Circuits

# Sreejith S<sup>1</sup>, Karthik Balasubramanian<sup>2</sup>

<sup>1</sup>School of Electrical Engineering, Vellore Institute of Technology, Vellore, India <sup>2</sup>School of Electrical and Electronic Engineering, Nanyang Technological University, Singapore

## **Article Info**

#### Article history:

Received Jun 18, 2018 Revised Sep 2, 2018 Accepted Sep 9, 2018

#### Keyword:

Inverting circuit

Multi Input Converters

Summing circuit

Switched capacitor circuits

## **ABSTRACT**

This paper analyze the operation of a multi input switched capacitor (MIC) converters using a couple of switches, diodes and capacitors for several levels. With two input sources it is possible to obtain 8 output voltage levels. Here, 5 topologies of switched capacitor circuits namely summation, subtraction, inverting, double and half circuits are simulated and their performances are analyzed. Multi Input Converters have a high regard for multiple renewable energy sources used in smart grid systems, especially for distributed generators. The effects on output voltage with variation in load for different frequencies are also analyzed. Hardware implementation of summation and subtraction circuit is carried out and the results are compared with the simulated results

Copyright © 2018 Institute of Advanced Engineering and Science.

All rights reserved.

## Corresponding Author:

Sreejith S,

Department of Energy and Power Electronics, School of Electrical Engineering, Vellore Institute of Technology,

Vellore, Tamil Nadu, India. Email: sreejith.s@vit.ac.in

## 1. INTRODUCTION

Inductors and capacitors are the main energy storage for the switched-mode power supplies (SMPS). The sizes are usually dominated by the inductor and transformer [1]. DC-DC converters play a vital role in renewable energy based applications [2], [3]. Resonant converters based on this SMPS can operate at high switching frequencies to decrease the size of the converters, however, their switching frequencies are not constant and hence the electromagnetic interference (EMI) filter cannot be optimized. Extended period quasiresonant converters have been introduced in [4], [5]. These converters are able to operate at constant switching frequencies and all the switching devices are switched at zero-current or zero-voltage. The requirement of magnetic components restricts the application and increases the difficulty in designing the converters. These difficulties were replaced with switched capacitor circuits. Switched-capacitor (SC) DC-DC power converters [6] are a subset of DC-DC power converters, using only switches and capacitors that can efficiently convert one voltage to another. Since SC converters does not have any inductors, they are ideal for integrated implementations, as common integrated inductors are not suitable for power electronic applications. The main advantage of this kind of converter is that no magnetic component is required for storing energy, making it possible to fabricate a smaller size and lighter weight converter in an integrated circuit [7]. There are very mature theories and techniques to design variety of DC-DC converters with singleinput. Buck converter can for lower voltage than input [8], boost converter output higher voltage [9], boostbuck converter and Cuk converter can obtain the output voltage with step up or down ratio [10] In addition, Half-mode, Double-mode [11], step-up and step-down converter based on switched-capacitor can output half, twice and multiple and fractional voltage ratios [12], [13]. In recent years, with the continuous development

of new energy technologies and the production of complex electrical equipment, multi-input DC–DC converter has aroused significant attention. A few topologies of multi input converters (MICs) have been presented in [14]-[21]. Due to the advantages of multiport converter, recently there have been extensive researches that resulted in a wide variety of topologies. One simple approach is to interface several converter stages to a common dc bus with independent control for each converter stage. A multi input boost-type converter [22] was designed for hybrid electric vehicles using such loose structure.

## 2. MULTILEVEL CONVERSION CIRCUITS

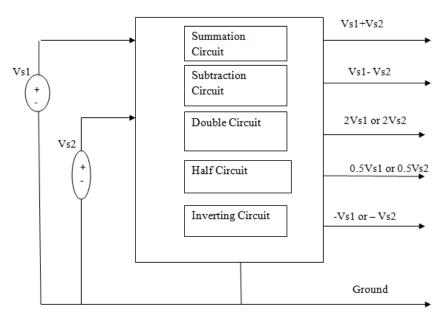

Figure 1 shows the diagram of a multilevel dc conversion from two different voltage levels. Two voltage levels as input, it is anticipated that the two voltage levels can be converted to other voltage levels in order to suit different voltage needs for other electronic appliances. With these five conversion circuits namely summation circuit, subtraction circuit, double circuit, half circuit, inverting circuit it is possible to convert two input voltages into eight levels of voltage. With only one input source Vs , the family of switched-capacitor converter can transform it into 0.5VS , –Vs, or 2Vs . With two input supplies Vs1 and Vs2, it can transform them into Vs1 + Vs2 or Vs1–Vs2. So, using the switched-capacitor converter and three distribution lines, two voltage levels can be converted into eight voltage levels. It includes Vs1+Vs2 (Summation) , Vs1-Vs2 (Subtraction), 2Vs1 (Double) , 2Vs2 (Double) , 0.5Vs1 (Half), 0.5Vs2 (Half), -Vs1 (Inverting) and –Vs2 (Inverting). Each of the circuits uses only two switches, two diodes and two capacitors. Therefore, the size of the circuits is very small and simple enough to handle. A pair of complementary pulses is given to two switches with fixed duty ratio of 0.5 for all the five circuits.

Figure 1. Multilevel converter

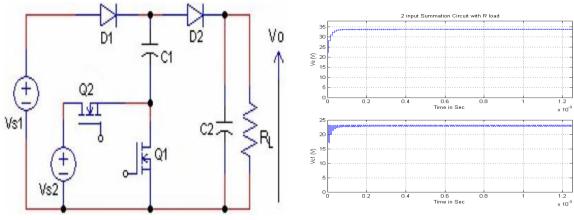

#### 2.1. Summation circuit

The basic circuit diagram of a summation circuit is shown in Figure 2. Here, when Q1 is turned ON and Q2 is turned OFF, diode D1 is forward biased and D2 is reverse biased. Vs1, C1, Q1, and D1 forms a closed loop. Vs1 charges C1 and the voltage across C1 is the same voltage as Vs1, i.e., Vc1 = Vs1. When, Q1 is turned OFF and Q2 is turned ON, D2 is forward biased and D1 is reverse biased, Vs2, C1, Q2, D2, and C2 form a closed loop. C1 is connected in series with Vs2 and delivers the total voltage to C2, so the voltage across C2 is Vs2 + Vc1. As Vc1 = Vs1, the output voltage Vo2 = Vs1 + Vs2. Figure 3 shows the output voltage of summation circuit. Here Vs1 and Vs2 are Vs2 + Vs2 + Vs3 + Vs3

Figure 2. Summation Circuit

Figure 3. Output voltage and capacitor voltage of Summation Circuit

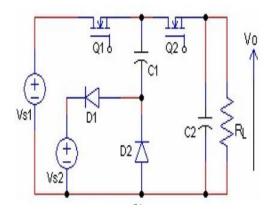

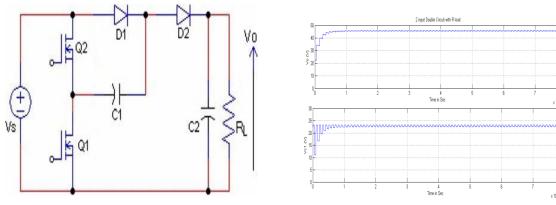

## 2.2. Subtraction circuit

The circuit diagram of a subtraction circuit is shown in Figure 4. When Q1 is turned ON and Q2 is turned OFF, D1 is forward biased and D2 is reverse biased. Vs1, Vs2, C1, Q1, and D1 form a closed loop, and Vs1 is connected in series with –Vs2 and charges C1, so the voltage across C1 is Vs1-Vs2. Next, when Q1 is turned OFF and Q2 is turned ON, D2 is forward biased and D1 is reverse biased, C1, Q2, D2, and C2 form a closed loop. C1 is connected in series with C2, so the voltage across C2 is equal to Vc1. The output voltage Vo = Vs-Vs. Figure 5 shows the output of a subtraction circuit. Here Vs1 and Vs2 are 24V and 12 V respectively, Vo = 12.27V.

Figure 5. Output voltage and capacitor voltage of Subtraction circuit

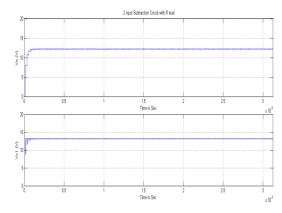

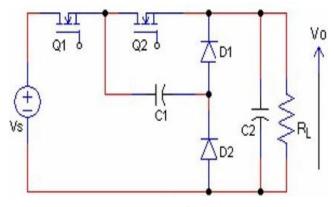

## 2.3. Double circuit

The circuit diagram of double circuit is shown in Figure 6. During mode 1, when Q1 is ON, Q2 is OFF, D1 is forward biased and D2 is reverse biased, Vs1, D1,C1,Q1 forms a closed loop and capacitor C1 charges to voltage Vs. This is known as charging state. In mode 2 Q2 is ON, Q1 is OFF, D2 is forward biased and D1 is reverse biased, Vs, Q2, C1, D2, RL forms a closed loop. Capacitor C1 discharges now and capacitor C2 is now charging to voltage Vc1+Vs. This is known as discharging state. The output of double circuit becomes Vo = 2Vs. Figure 7 shows the output of double circuit. Here Vs1 and Vs2 are 24V and 12V respectively, the output voltage Vo = 45.67V.

Figure 6. Double circuit

Figure 7. Output voltage and capacitor voltage of double circuit

## 2.4. Half circuit

The diagram of half circuit is shown in Figure 8. In mode 1 Q1 is ON, Q2 is OFF, D1 is forward biased and D2 is reverse biased, Vs, Q1, C1, D1, C2 forms a closed loop. Capacitor C1and capacitor C2 equally charges to voltage 0.5Vs. In mode 2 Q2 is ON, Q1 is OFF, D2 is forward biased and D1 is reverse biased. The voltage across capacitor C2 remains constant. The output of half circuit is Vo = 0.5Vs2. Figure 9 shows the output of half circuit. Here Vs2 is 24V, the output voltage Vo = 11.14V.

Figure 8. Half circuit

Figure 9. Output voltage and capacitor voltage of half circuit

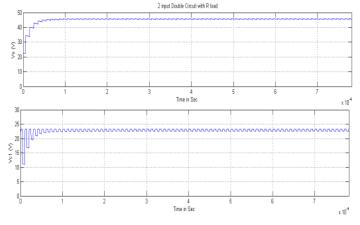

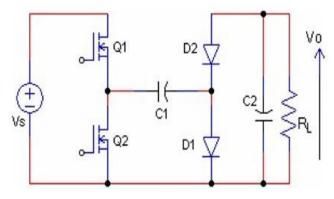

## 2.5. Inverting circuit

The inverting circuit is shown in Figure 10. In mode 1 Q1 is ON, Q2 is OFF, D1 is forward biased and D2 is reverse biased, Vs,Q1,C1,D1 forms a closed loop and capacitor C1 charges to voltage Vs . This is known as charging state. In mode 2 Q2 is ON, Q1 is OFF, D2 is forward biased and D1 is reverse biased, Q2, C1, D2, C2 forms a closed loop and capacitor C1 starts discharging. Capacitor C2 is now charging to voltage Vs with reverse polarity. This is known as discharging state. The output of inverting circuit Vo = -Vs. The output voltage of an inverter circuit is shown in Figure 11. The input voltage is 12V and output voltage is -12V.

Figure 10. Inverting circuit

Figure 11. Output voltage and capacitor voltage of inverting circuit

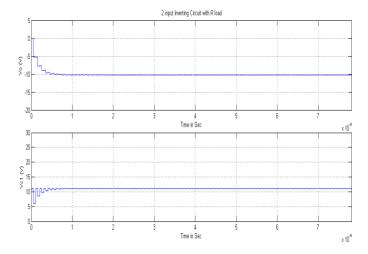

# 3. VARIATION OF LOAD AND FREQUENCY ON CONVERSION CIRCUITS

The performance of the above said circuits are analyzed under different loads and frequencies. The results obtained are shown in Figure 11 (a) to Figure 11(e). The input voltages considered are 24V and 12V. The frequency chosen are 50 kHz and 100 kHz. The load is varied from 1 to  $500\Omega$ . It is clear that, the performance of the circuit is independent of the switching frequency. The initial voltage shoot increases with frequency, finally settle down to a constant value.

Figure 12. (a) Summing circuit under variable load and frequency, (b) subtracting circuit under variable load and frequency, (c) double Circuit under variable load and frequency, (d) half circuit under variable load and frequency, (e) inverting circuit under variable load and frequency

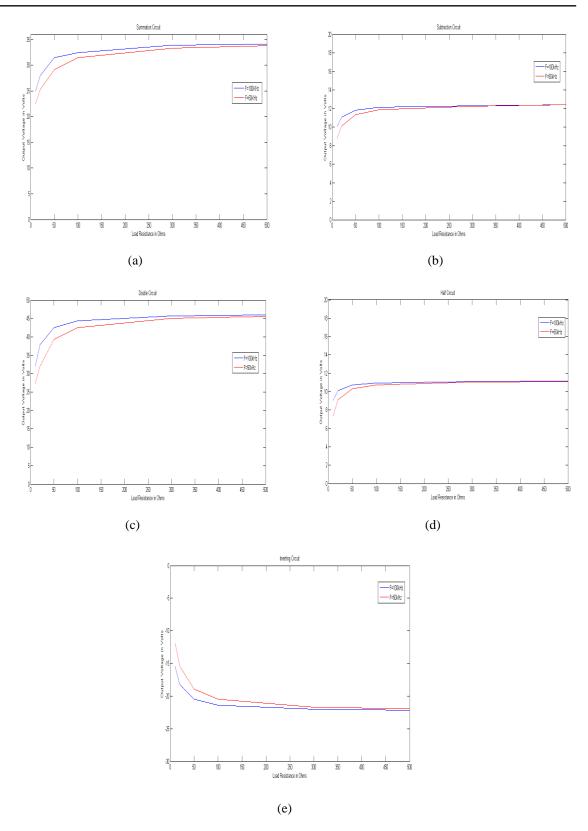

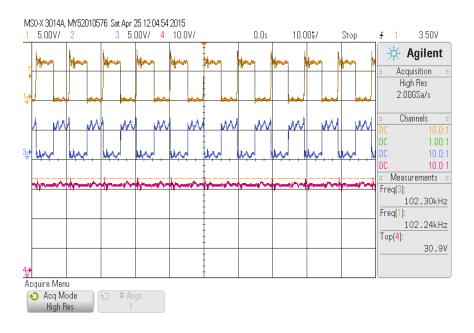

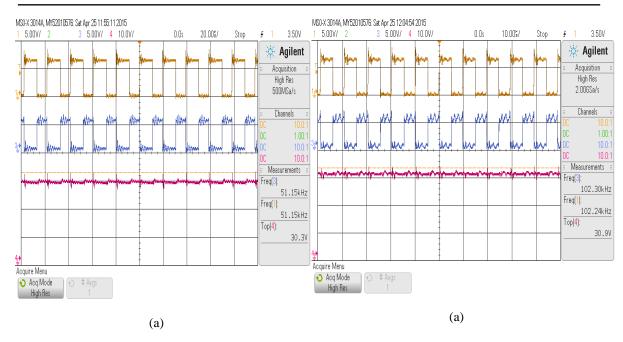

#### 4. HARDWARE REULTS AND DISCUSSION

To validate the simulation findings a hardware prototype for summation and subtraction circuit are fabricated. The circuit is tested for the frequencies of 50 kHz, 100 kHz and  $100\Omega$  and  $330 \Omega$ .

Figure 13. Hardware set up for summation circuit

Figure 13 shows the experimental setup for summation circuit. For a load of  $330\Omega$  and switching frequency of 100 kHz, the input voltages given to the summation converter are 24V and 12 V respectively. The output voltage obtained is 32.1V and is shown in Figure 14. This is similar to the values obtained in simulation.

Table 1. Summation Circuit Results for 100 kHz

| Load<br>(Ω) | Calculated output voltage (V) | Simulated output voltage (V) | Experimental output voltage(V) |

|-------------|-------------------------------|------------------------------|--------------------------------|

| 100         | 33.09                         | 31.52                        | 30.3                           |

| 330         | 34.1                          | 33.46                        | 32.1                           |

| 430         | 34.23                         | 33.67                        | 32.4                           |

Figure 14. Output voltage for summation circuit

## 4.1. Variable load with fixed frequency of 100 kHz

When C1 and f are fixed, the variation in frequency is shown in Figure 15(a) and Figure 15(b). indicates the influence of a varying load on Vo. The output voltages for resistances of  $100\Omega$  and  $330~\Omega$  are shown. It is clear that, the output voltage changes with variation in load resistance. The comparison between

simulated and hardware results are furnished in Table 2.

(a)

(b)

Figure 15. (a) Output voltage for  $100\Omega$ , (b) Output voltage for  $330\Omega$

Table 2. Summation Circuit Results for Variable Load

| Load $(\Omega)$ | Calculated output voltage (V) | Simulated output voltage(V) | Experimental output voltage(V) |

|-----------------|-------------------------------|-----------------------------|--------------------------------|

| 100             | 33.83                         | 32.88                       | 30.9                           |

| 330             | 34.36                         | 33.91                       | 32.1                           |

| 430             | 34.4                          | 34.02                       | 32.6                           |

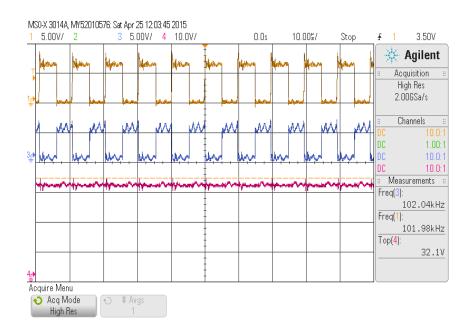

## 4.2. Variable load with fixed frequency of 50 kHz

The hardware output for 50 kHz for variable resistance is shown in Figure 16(a) and Figure 16(b). The output varies with the change in load resistance.

MSO-X 3014A, MY52010576: Sat Apr 25 11:54:29 2015 5.00V/ 3 5.00V/ 4 10.0V/ 0.0s 20.00%/ Stop 3.50V 🔆 Agilent Acquisition High Res 500MSa/s Channels 1.00:1 10.0:1 Measurements :: Freq(3): 51.25kHz Freq(1) 51.25kHz Top(4): ¥1 Acquire Menu Acq Mode € # Avgs

Figure 16. (a.) Output voltage for  $100\Omega$ , (b) output voltage for  $330\Omega$

(b)

# 4.3. Variable frequency with fixed of load 100 $\Omega$

For a fixed load of  $100~\Omega$ , the switching frequency is varied for 50~kHz and 100~kHz and the results obtained are shown in fig 17.a and 17.b. The simulated and hardware results are furnished in Table 3. It is clear that, the output depends on both load resistance and frequency.

Figure 17. (a) Output voltage for 50 kHz, (b) output voltage for 100 kHz

Table 3. Summation Circuit Results for Variable Frequencies

| Frequency (kHz) | Calculated output voltage (V) | Simulated output voltage (V) | Experimental output voltage (V) |

|-----------------|-------------------------------|------------------------------|---------------------------------|

| 50              | 33.09                         | 31.52                        | 30.3                            |

| 100             | 33.83                         | 32.88                        | 30.9                            |

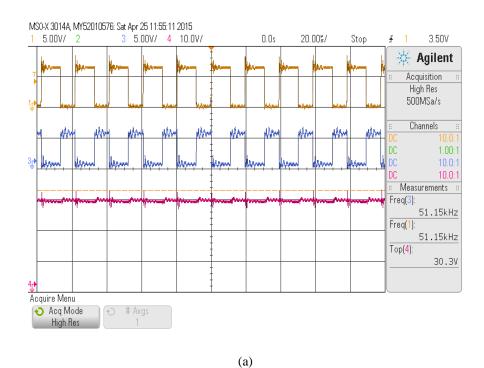

## 4.4. Subtraction circuit

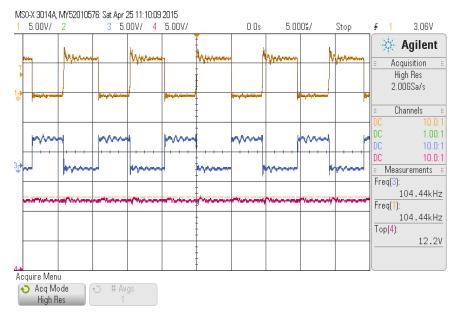

For a load of  $330\Omega$  and switching frequency of 100 kHz, the input voltages given to the subtraction converter are 24V and 10 V respectively. The output voltage obtained is 12.2V and is shown in Figure 18.

Figure 18. Output voltage for subtraction circuit

**3**4

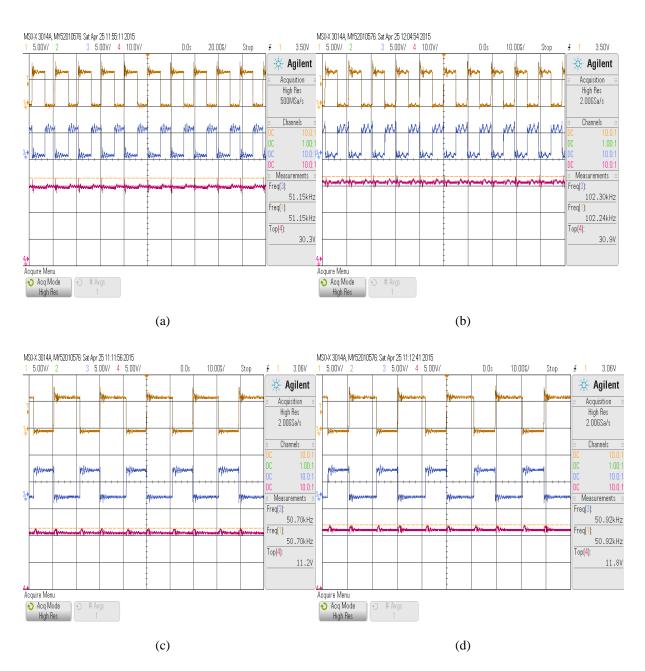

Figure 19(a) to Figure 19(b) shows the output voltage at 100 kHz and 100 $\Omega$ , output voltage at 100 kHz and 330 $\Omega$ , output voltage at 50 kHz and 100 $\Omega$ , and the output voltage at 50 kHz and 330 $\Omega$ . Table 4 shows the subtraction circuit results for variable frequencies.

Figure 19. (a) Output voltage at 100 kHz and  $100\Omega$ , (b) Output voltage at 100 kHz and  $330\Omega$ , (c) Output voltage at 50 kHz and  $100\Omega$ , (d) Output voltage at 50 kHz and  $330\Omega$

Table 4. Subtraction Circuit Results for Variable Frequencies

|                 | Frequency = 100 kHz                 |                              | Frequency = 50 kHz              |                               |                              |                                 |

|-----------------|-------------------------------------|------------------------------|---------------------------------|-------------------------------|------------------------------|---------------------------------|

| Load $(\Omega)$ | Calculated<br>output voltage<br>(V) | Simulated output voltage (V) | Experimental output voltage (V) | Calculated output voltage (V) | Simulated output voltage (V) | Experimental output voltage (V) |

| 100             | 12.32                               | 12.11                        | 11.6                            | 12.02                         | 11.85                        | 11.2                            |

| 330             | 12.5                                | 12.32                        | 12.2                            | 12.42                         | 12.26                        | 11.8                            |

| 430             | 12.53                               | 12.36                        | 12.2                            | 12.46                         | 12.33                        | 12.2                            |

#### 5. CONCLUSION

The performance of various multi input switched capacitor converters are analyzed in this paper. Various topologies namely summation, subtraction, inverting, double and half circuits are simulated under variable load and variable frequencies. The variation in outputs with variable load and frequencies are illustrated. With different switched capacitors topologies mentioned here a multi converter can convert two input voltages can be used to obtain 7 different voltage levels. The results have been experimentally verified for summation and subtraction converters for different loads under different frequencies. These results have been compared with the theoretical and simulated value. This can be extended to three input converters also.

## REFERENCES

- [1] Ganesh S, et al., "DC UPS for Critical Loads", Internatioal Journal of Electrical and Computer Engineering, 2105, vol. 2, no. 5, pp. 231-241.

- [2] Khandker Tawfique Ahmed, Mithun Datta and Nur Mohammad, "A Novel Two Switch Non-inverting Buck-Boost Converter based Maximum Power Point Tracking System", *Internatioal Journal of Electrical and Computer Engineering*, 2017, vol. 7, no. 2, pp. 720-727.

- [3] Khandker Tawfique Ahmed, et al., "A Novel Two Switch Non-inverting Buck-Boost Converter based Maximum Power Point Tracking System", Internatioal Journal of Electrical and Computer Engineering, 2013, vol. 3, no. 4, pp. 467-777.

- [4] Cheng, K.W.E., and Evans, P.D., "Parallel-mode Extended-period Quasiresonant Converter", *IEE Proceedings B* (*Electric Power Applications*), vol. 138, no. 5, pp. 243-251, 1991.

- [5] Cheng, K.W.E. and Evans, P.D., "Unified Theory of Extended Period Quasiresonant Converters", *IEE Proc. Electr. Power Appl.*, vol. 147, no. 2, pp. 119-130, 2000.

- [6] Bengtsson, H.A., Switch in Methods, New Electron, pp. 40-41, 1997.

- [7] Tse, C.K., et al., "On Lossless Switched-capacitor Power Converter", IEEE Trans. Power Electron, vol. 10, no. 3, pp. 286-291, 1995.

- [8] Kazimierczuk, M.K., "Steady-state Analysis and design of a Buck Zerocurrent-switching Resonant DC/DC Converter", *IEEE Trans. Power Electron*, vol. 3, no. 3, pp. 286-296, 1988.

- [9] Hwu, K.I., and Yau, Y.T., "Two Types of KY Buck-boost Converters", *IEEE Trans. Ind. Electron*, vol. 56, no. 8, pp. 2970-2980, 2009.

- [10] Sahu, B., and Rincon-Mora, G.A., "A Low Voltage, Dynamic, Noninverting, Synchronous Buck-boost Converter for Portable Applications", *IEEE Trans. Power Electron.*, vol. 19, no. 2, pp. 443-452, 2004.

- [11] Cheng, K.W.E., "Zero-current-switching Switched-capacitor Convertors", IEE Proc. Electr. Power Appl., vol. 148, no. 5, pp. 403-409, 2001.

- [12] Law, K.K., et al., "Design and Analysis of Switched-capacitor-based Step-up Resonant Converters", IEEE Trans. Circuits Syst., vol. 52, no. 5, pp. 943-948, 2005.

- [13] Yeung, Y.P.B., et al., "Generalised Analysis of Switched-capacitor Step-down Quasi-resonant Converter", IEE Proc. Electr. Power Appl., pp. 149, no. 2, pp. 111-121, 2002.

- [14] Dobbs, B.G., and Chapman, P.L., "A Multiple-input DC–DC Converter Topology", *IEEE Power Electron.*, vol. 1, no. 1, pp. 6-9, 2003.

- [15] Liu, Y.-C., and Chen, Y.-M., "A Systematic Approach to Synthesizing Multiinput DC–DC Convertors", *IEEE Trans. Power Electron.*, vol. 24, no. 1, pp. 116-127, 2009.

- [16] Qian, Z., et al., "Modeling and Control of three-port DC/DC Converter Interface for Satellite Applications", *IEEE Trans. Power Electron.*, 2010, vol. 25, no. 3, pp. 637-649.

- [17] Stumberger, G., et al., "Prevention of Iron Core Saturation in Multi-winding Transformers for DC–DC Converters", *IEEE Trans. Magn.*, 2010, vol. 46, no. 2, pp. 582-585.

- [18] Kwasinski, A., "Identification of Feasible Topologies for Multiple-input DC–DC Converters", *IEEE Trans. Power Electron.*, vol. 24, pp. 856-861, 2009.

- [19] Ou, T.-C., et al., "A Multi-input Power Converter for Hybrid Renewable Energy Generation System", IEEE PES/IAS SAE Conf. 2009, pp. 1-7.

- [20] Liu, D., and Li, H., "A Novel Multiple-input ZVS Bidirectional DC-DC Converter", *Industrial Electronics Society Conf.*, pp. 579-584, 2005.

- [21] Jun, X., et al., "Design of Multiple-input DC–DC Converter Control System for Fuel Cell Electrical Vehicle", *Int. Conf. Energy and Environment Technology*, pp. 123-126, 2009.

- [22] A. Di Napoli, *et al.*, "Multiple-input DC–DC Power Converter for Power-flow Management Inhybrid Vehicles", In *Proc. IEEE Ind. Appl. Conf.*, pp. 1578-1585, 2002.

Int J Elec & Comp Eng ISSN: 2088-8708

3483

## **BIOGRAPHIES OF AUTHORS**

**Sreejith S** received his Bachelor's degree in Electrical and Electronics Engineering from M.S University. He completed his Master's in Power Electronics and Drives from Anna University Chennai. He completed his Doctoral research in Electrical Engineering at National Institute of Technology, Trichy, India. Presently he is working as an Associate Professor at VIT university, Vellore. His areas of interest include FACTS, Power Electronics & Drives and Power Electronics Applications to Power Systems.

**Karthik Balasubramanian**. Completed B. Tech in Electrical and Electronics Engineering with Minor in Industrial Automation from VIT University, Vellore, India, in 2014. He is currently working as an Electrical Engineer in Saipem India Projects Pvt. Ltd. He has published many research papers in various national and international journals. His area of research interest are Power engineering, Fuel cell system design, PV system design and applications of Power electronics in Renewable Energy systems