International Journal of Electrical and Computer Engineering (IJECE) Vol. 6, No. 2, April 2016, pp. 484~494 ISSN: 2088-8708, DOI: 10.11591/ijece.v6i2.9442

**D** 484

# High Performance Control of Grid Connected Cascaded H-Bridge Active Rectifier Based on Type II-Fuzzy Logic Controller with Low Frequency Modulation Technique

### M. Dabbaghjamanesh<sup>1</sup>, A. Moeini<sup>2</sup>, M. Ashkaboosi<sup>3</sup>, P. Khazaei<sup>4</sup> K. Mirzapalangi<sup>3</sup>

<sup>1</sup> Department of Electrical Engineering, Northern Illinois University, DeKalb, IL, USA

<sup>2</sup> Department of Electrical and Computer Engineering, University of Tehran, Tehran, Iran

<sup>3</sup> Islamic Azad University Central Tehran Branch, Tehran, Iran

<sup>4</sup>Department of Electrical and Computer Engineering, Shiraz university technology, Shiraz, Iran

## **Article Info**

Article history:

# ABSTRACT

Received Nov 17, 2015 Revised Dec 16, 2015 Accepted Jan 5, 2016

### Keyword:

Active rectifier Cascaded H-Bridge Fuzzy Logic Controller type II Multilevel converter Optimal Modulation Technique Particle Swarm Optimization This paper tries to employ a fuzzy logic (FL) controller type II to control the Cascaded H-Bridge (CHB) active rectifier. This controller has strong performance, specially, when a low switching frequency Selective Harmonic Elimination (SHE) method is used. In order to regulate all of the DC link voltages, the optimum voltage balancing strategy in the low frequency modulation technique is used in the proposed method. Finally, the performance and effectiveness of the proposed method is validated in MATLAB environment. All the simulation and result has been simulated by MATLAB software.

Copyright © 2016 Institute of Advanced Engineering and Science. All rights reserved.

#### **Corresponding Author:**

A. Moeini,

Department of Electrical and Computer Engineering, University of Tehran, Tehran, Iran

#### 1. INTRODUCTION

In the recent years, the multilevel converters are considered more in power electronics applications. Compare to traditional power electronics converters, multilevel converters have significant benefits such as lower THD, higher efficiency and lower common mode noises (CM) [1, 2]. Moreover, these converters can be used in modular structures. So, in this converter, the voltage level can easily be increased to have a better performance in high voltage and high power applications. As the result, the application of multilevel converters in grid applications has rapidly been increased [3-7].

Multilevel converters can be organized in three categories: Neutral Point Clamped (NPC), Cascaded H-Bridge (CHB), and Flying Capacitor (FC) [2]. In this paper, the CHB converter due to its modular structure, more redundancy states in generating the output voltage and lower electronic components has been considered [2].

A lot of paper discussed about using the CHB converter in both inverting (DC/AC) and rectifying (AC/DC) modes [8-12]. Optimal modulation technique also has been employed in order to increase the efficiency and meet the power quality requirements. One of the challenges in the optimal modulation techniques is having high performance control in the CHB active rectifier [5]. In paper [6], a control technique based on PI controller has been proposed to improve the performance of the converter. However, the CHB active rectifier is a nonlinear system. Thus, nonlinear controller can have a better performance than the linear controller such as PI [5, 6].

In this paper type II Fuzzy logic controller which is nonlinear one has been used on the CHB active rectifier in order to improve the performance of the converter. Moreover, the optimal Selective Harmonic

Elimination technique has been employed on the CHB converter when the harmonics of the converter up to 25<sup>th</sup> are eliminated in the output voltage and current of the converter. The number of switching transitions in the proposed technique is reduced to 9 in each quarter of the period to improve the efficiency of the converter [12-15].

### 2. CASCADED H-BRIDGE CONVERTER STRUCTURE

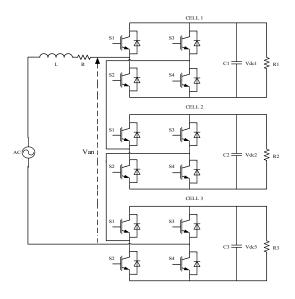

The single phase diagram of the CHB converter is showed in Figure 1. As it can see in this figure, the converter is connected to the AC grid voltage, by using an inductor to program the injected current of the CHB. Also, in order to filter ripples in the voltage of the DC link of the converter, a capacitor has been paralleled to each load in the cell. It should be mentioned that, in order to transfer AC power of the grid to the desired DC voltages, the 4 solid state switches with anti-parallel diodes has been employed in each cell of the converter. The AC voltage of the CHB converter can synthesis a seven level voltage in AC side, when there are some redundancy states for producing each level.

Figure 1. Configuration of the CHB multilevel active rectifier

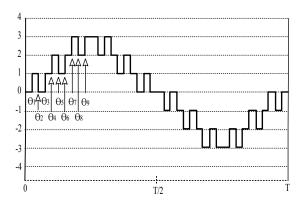

Figure 2. Predefined waveform of 7-level SHE-PWM, when frequency of each cell is equal to 150Hz

#### 3. SELECTIVE HARMONIC ELIMINATION-PWM TECHNIQUE

One of the optimal modulation techniques which can be used in order to eliminate low order harmonics of the output voltage of the converter is Selective Harmonic Elimination (SHE-PWM). This technique is very useful when the converter has been employed on the high power converter that is connected

to the grid voltage. This method tries to use the Fourier equations of the predefined waveform (Figure 2) to extract the harmonic equations of the waveform [6].

In this method, in each quarter of the period of output voltage of the converter, a nine-switching transition waveform has been employed [7-12]. So, this modulation technique can suppress the low order harmonics of the output voltage up to 29<sup>th</sup> harmonic. The equations of the harmonics of the converter has been presented below,

$$Cos\theta_{1} - Cos\theta_{2} + Cos\theta_{3} + Cos\theta_{4} - Cos\theta_{5}$$

$$+Cos\theta_{6} + Cos\theta_{7} - Cos\theta_{8} + Cos\theta_{9} = M$$

$$Cosm\theta_{1} - Cosm\theta_{2} + Cosm\theta_{3} + Cosm\theta_{4} - Cosm\theta_{5}$$

$$+Cosm\theta_{6} + Cosm\theta_{7} - Cosm\theta_{8} + Cosm\theta_{9} = 0$$

(2)

For m= 5, 7, 11, 13, 17, 19, 23, 25

$$M = \frac{\pi V_{peak}}{4V_{dc}} \tag{3}$$

here,

$\theta_1$  to  $\theta_9$ : Switching angles;

M : Modulation index;

V<sub>dc</sub>: Desired value of DC link voltage;

V<sub>peak</sub>: Peak value of AC terminal voltage;

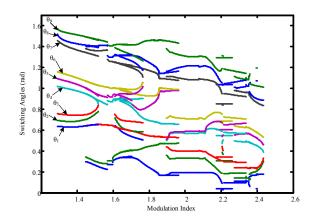

To reach goals in the equations (1-3), Particle Swarm Optimization (PSO) approach has been used to optimize the nonlinear transcendental equations of the SHE-PWM method. Figure 3 shows that the obtained solutions by the PSO optimization techniques are so complete and cover wide range for the control purposes.

Figure 3. Switching transitions in radian versus modulation indices to meet the required limits in equation (1-3)

#### 4. PROPOSED CONTROL STRATEGY

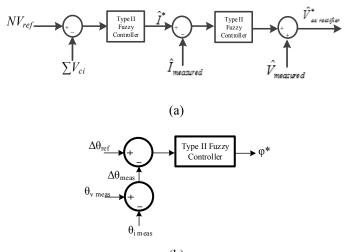

The controller which has been used in this paper is Type II Fuzzy Logic Controller. The main purpose of this controller is to balance the DC link voltages according to the reference value, and keep in phase and sinusoidal the input current and voltage of the CHB converter. Figure 4 presents the bock diagram of the Fuzzy controller which is used in the proposed controller. The controller which is employed in the Figure 4 is similar to the controller that has been introduced in [5] and [16-18]. The main difference is using

High Performance Control of Grid Connected Cascaded H-Bridge Active Rectifier Based on ... (A. Moeini)

the Type II fuzzy logic controller instead of PI controllers to improve the performance of the Optimal SHE-PWM technique.

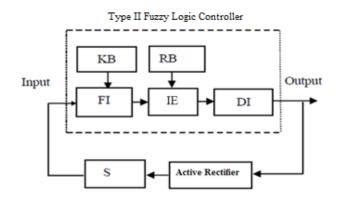

The complete block diagram of Type II Fuzzy Logic Control (Type II-FLC) system is shown in Figure 5. Based on the Figure 5, four sections have been defined as the main components of the Type II Fuzzy Logic Controller [18-20];

- First, the Knowledge Base (KB) which is encompassing knowledge regards of all the input and output fuzzy parts. Also, it contains the term set and the membership functions of the controller about the input variables to the fuzzy 'Rule-Base' (RB) system and the output or decision variables to the plant.

- Second, the Fuzzification Interface (FI).

- Third, the inference engine (IE).

- Fourth, the Defuzzification Interface (DI).

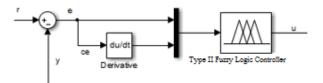

The inputs of the Type II Fuzzy Logic Controller (Type II-FLC) are error (e), which is the difference between the phase of the current and phase of the grid voltage of the CHB active rectifier and error change (*ce*) which is derivatives of the error (e). Each input and output of the Type II-FLC has seven membership functions which can be defined as NB (Negative Big), NS (Negative Small), NM (Negative Medium), ZE (Zero), PS (Positive Small), PM (Positive Medium), and PB (Positive Big) based on the range of changes. The next step in designing a Type II-FLC is rule definition.

Three Fuzzy Logic Controllers (Type II-FLC) are required in the proposed control method. The first Type II-FLC tries to reduce the error among phases of the current and phase of the grid voltage of the active rectifier to produce an acceptable terminal voltage in CHB active rectifier (Figure 4(b)). The inputs of the controller are the error changes which are within (-200, 200) and the derivative of error changes which are within (-10, 10). Furthermore, the output of the controller varies between (-16, 16) to provide the desired performance.

The second Type II-FLC is used to decide the modulation index of the converter (Figure 4 (a)). As it can see, two Type II-FLCs are needed to keep the modulation index in the desired value. The first Type II-FLC tries to minimize the difference between all of the DC link voltages and keep equal to specific value. In this case, the error is in interval (-30, 30), and the derivative of error is in interval (-6000, 6000). The output of the Type II-FLC is the reference of the current amplitude of the rectifier that varies in range of (-5, 5).

The second Type II-FLC compensates fundamental current of the rectifier and reference current of the rectifier to have the least error. As the result, the inductor and parasite resistor voltages are the output of this controller. All of the Type II FLCs in the Figure 4 (a) and Figure 4 (b) are exactly same with each other and use seven triangular membership functions for each input and output.

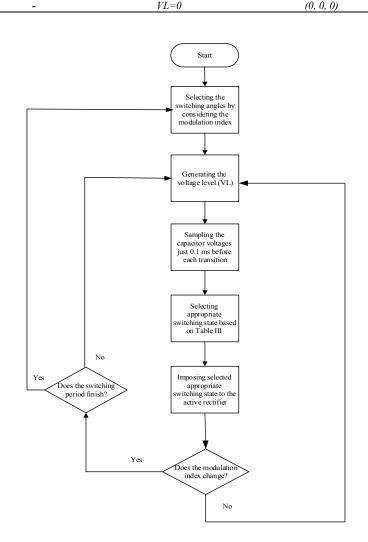

The voltage balancing strategy of the proposed SHE-PWM technique is the same as the approach which is explained in [6]. Moreover, the flowchart of the voltage balancing strategy has been presented in the Figure 9.

It should be mentioned that the switching transitions of the active rectifier applied by using optocoupler or isolation transformer. Theses components are required, because signal of the controller should be isolated from the voltage that is imposed to the gate driver of the Power MOSFET or IGBT switches [15-17].

## 5. COMPRASION OF THE TYPE I AND TYPE II FUZZY LOGIC CONTROLLERS

In the recent years, the Fuzzy Logic Controller has been employed in various applications. One of the most important reasons which convinced the scientist to employ Fuzzy logic systems is the high capability of decision making in Fuzzy Controller [13-17].

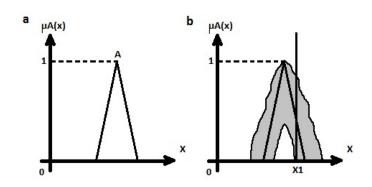

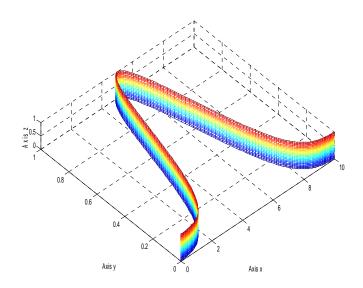

There are two types of Fuzzy Controller which are used in applications: Type I Fuzzy Logic Controller (Type I-FLC) and Type II Fuzzy Logic Controller (Type II-FLC) [18-22]. The big difference between them is in dealing with uncertainty issues. In other words, the Type I-FLC cannot perfectly cover the measurements and parameters of uncertainty problems. Therefore, in order to improve the ability of fuzzy systems to control the uncertainties, Type I-FLC has been used. Moreover, in Type I-FLC, the membership functions grades are determined by a crisp value. However, in Type II-FLC, the membership functions grades for every element is not a specific crisp value. Figure 7 and 8, show difference between type I and II. Indeed, Type II-FLC is a powerful tool when exact value for the membership function must be tuned. In this study, FLC type II has been employed, due to the uncertainty in the DC link voltage balancing and also provide a better performance in dynamic conditions.

(b)

Figure 4. Schematic diagram of the proposed controller

Figure 5. The fuzzy logic controller configuration

Figure 6. The FLC structure which is used on the CHB

Figure 7. A type-I membership function, (b) Blurred type-II membership function [18]

Figure 8. 3D illustration of type-II fuzzy Gaussian membership function [19]

| Table II. The rule base for the Type II FLC |    |    |    |  |

|---------------------------------------------|----|----|----|--|

| Rule No.                                    | e  | ce | U  |  |

| 1                                           | PB | ZE | PB |  |

| 2                                           | PM | ZE | PM |  |

| 3                                           | PS | ZE | PS |  |

| 4                                           | ZE | NB | NB |  |

| 5                                           | ZE | NM | NM |  |

| 6                                           | ZE | NS | NS |  |

| 7                                           | NB | ZE | NB |  |

| 8                                           | NM | ZE | NM |  |

| 9                                           | NS | ZE | NS |  |

| 10                                          | ZE | PB | PB |  |

| 11                                          | ZE | PM | PM |  |

| 12                                          | ZE | PS | PS |  |

| 13                                          | ZE | ZE | ZE |  |

| 14                                          | PB | NS | PM |  |

| 15                                          | PS | NB | NM |  |

| 16                                          | NB | PS | NM |  |

| 17                                          | NS | PB | PM |  |

| 18                                          | PS | NS | ZE |  |

| 19                                          | NS | PS | ZE |  |

| Table II. The rule base for the Type II FLC | 2 |

|---------------------------------------------|---|

|---------------------------------------------|---|

| Table III. The sort of the DC link voltages in different available redundant states conditions |                                |                                  |  |  |  |

|------------------------------------------------------------------------------------------------|--------------------------------|----------------------------------|--|--|--|

| Sort of DC link voltages                                                                       | Voltage level after transition | Optimal selected switching state |  |  |  |

| $(Vdc1 \ge Vdc2 \ge Vdc)$                                                                      | VL=1                           | (0, 0, 1)                        |  |  |  |

| (Vdc1≥Vdc3≥Vdc)                                                                                | VL=1                           | (0, 1, 0)                        |  |  |  |

| $(Vdc2 \ge Vdc3 \ge Vdc)$                                                                      | VL=1                           | (1, 0, 0)                        |  |  |  |

| (Vdc2≥Vdc1≥Vdc)                                                                                | VL=1                           | (0, 0, 1)                        |  |  |  |

| (Vdc3≥Vdc1≥Vdc)                                                                                | VL=1                           | (0, 1, 0)                        |  |  |  |

| $(Vdc3 \ge Vdc2 \ge Vdc)$                                                                      | VL=1                           | (1, 0, 0)                        |  |  |  |

| (Vdc1≥Vdc2≥Vdc)                                                                                | VL=2                           | (0, 1, 1)                        |  |  |  |

| (Vdc1≥Vdc3≥Vdc)                                                                                | VL=2                           | (0, 1, 1)                        |  |  |  |

| $(Vdc2 \ge Vdc3 \ge Vdc)$                                                                      | VL=2                           | (1, 0, 1)                        |  |  |  |

| $(Vdc2 \ge Vdc1 \ge Vdc)$                                                                      | VL=2                           | (1, 0, 1)                        |  |  |  |

| (Vdc3≥Vdc1≥Vdc)                                                                                | VL=2                           | (1, 1, 0)                        |  |  |  |

| $(Vdc3 \ge Vdc2 \ge Vdc)$                                                                      | VL=2                           | (1, 1, 0)                        |  |  |  |

| -                                                                                              | VL=3                           | (1, 1, 1)                        |  |  |  |

| $(Vdc1 \ge Vdc2 \ge Vdc)$                                                                      | VL=-1                          | (0, 0, -1)                       |  |  |  |

| (Vdc1≥Vdc3≥Vdc)                                                                                | VL=-1                          | (0, -1, 0)                       |  |  |  |

| $(Vdc2 \ge Vdc3 \ge Vdc)$                                                                      | VL=-1                          | (-1, 0, 0)                       |  |  |  |

| $(Vdc2 \ge Vdc1 \ge Vdc)$                                                                      | VL=-1                          | (0, 0, -1)                       |  |  |  |

| $(Vdc3 \ge Vdc1 \ge Vdc)$                                                                      | VL=-1                          | (0, -1, 0)                       |  |  |  |

| $(Vdc3 \ge Vdc2 \ge Vdc)$                                                                      | VL=-1                          | (-1, 0, 0)                       |  |  |  |

| $(Vdc1 \ge Vdc2 \ge Vdc)$                                                                      | VL=-2                          | (0, -1, -1)                      |  |  |  |

| (Vdc1≥Vdc3≥Vdc)                                                                                | VL=-2                          | (0, -1, -1)                      |  |  |  |

| $(Vdc2 \ge Vdc3 \ge Vdc)$                                                                      | VL=-2                          | (-1, 0, -1)                      |  |  |  |

| $(Vdc2 \ge Vdc1 \ge Vdc)$                                                                      | VL=-2                          | (-1, 0, -1)                      |  |  |  |

| $(Vdc3 \ge Vdc1 \ge Vdc)$                                                                      | VL=-2                          | (-1, -1, 0)                      |  |  |  |

| $(Vdc3 \ge Vdc2 \ge Vdc)$                                                                      | VL=-2                          | (-1, -1, 0)                      |  |  |  |

| -                                                                                              | VL=-3                          | (-1, -1, -1)                     |  |  |  |

| -                                                                                              | VL=0                           | (0, 0, 0)                        |  |  |  |

Figure 9. The flowchart of the DC link voltage balancing approach

## 6. SIMULATION RESULTS

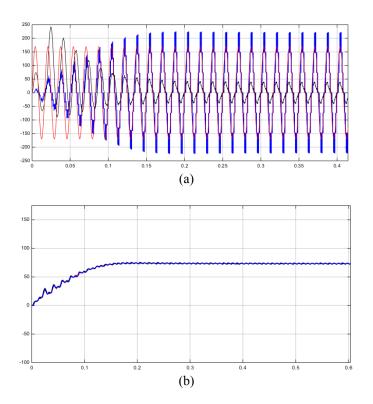

In order to show superiority and effectiveness of the proposed control strategy approach, the converter is simulated in MATLAB Simulink environment. Table IV illustrates the parameters of the CHB Active Rectifier. The start-up and steady state behavior of the rectifier has been presented in the first simulation. As far as it can see in Figure 8, the behavior of the converter is very good especially, in start-up and steady state points. The second simulation shows the DC link ripples of the converter in different switching frequency of the control strategy.

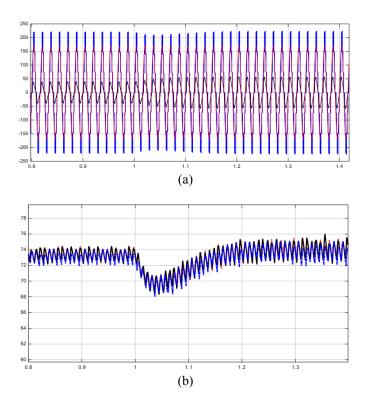

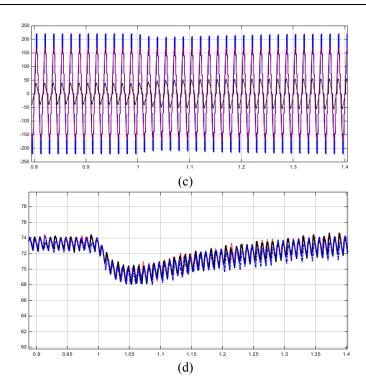

The dynamic behavior of the controller, when the loads of the converter have suddenly increased 50% in each cell has been illustrated in the last simulation. Based on the Figure 10, the controller has a high performance in dynamic conditions.

| Tuble IV: Chedit parameters used for simulation |                    |       |  |  |

|-------------------------------------------------|--------------------|-------|--|--|

| Parameter                                       | Symbol             | Value |  |  |

| Number of H-bridges                             | Ν                  | 3     |  |  |

| Cell nominal load                               | Р                  | 150W  |  |  |

| Grid Voltage                                    | V <sub>ac</sub>    | 120V  |  |  |

| DC bus voltage                                  | $V_{dc}$           | 73V   |  |  |

| Input inductance                                | L                  | 6mH   |  |  |

| Line resistance                                 | R                  | 0.2Ω  |  |  |

| DC bus capacitor                                | С                  | 3mF   |  |  |

| Line frequency                                  | F                  | 60Hz  |  |  |

| Converter total power                           | P <sub>total</sub> | 450W  |  |  |

Table IV. Circuit parameters used for simulation

Figure 9. The start-up and steady state condition of the converter. (a) AC voltage and current of the grid and CHB AC terminal voltage (b) DC link voltages, (c) DC link voltage ripples of the proposed SHE-PWM (d) harmonic spectra of the current

High Performance Control of Grid Connected Cascaded H-Bridge Active Rectifier Based on ... (A. Moeini)

Figure 11. The DC link voltages of each cell in 50% load variations in the proposed Type II-FLC and Type I-FLC controllers, (a) The AC grid voltage and CHB voltage and AC current in proposed Type-II FLC (b) DC link voltages in Type II-FLC (c) The AC grid voltage and CHB voltage and AC current in Type-I FLC (d) DC link voltages in Type I-FLC

## 7. CONCLUSION

In this paper, in order to control the seven-level CHB active rectifier, a Type II Fuzzy Logic Controller (Type II-FLC) has been used. This method is very useful when the converter employs DC link balancing approach in the [6]. Also, the Selective Harmonic Elimination PWM which has the lowest switching frequency between the modulation techniques is used to decrease the switching losses and increase the efficiency of the converter. The proposed SHE-PWM technique can eliminate the harmonics of the voltage and injected current up to 29<sup>th</sup> harmonic. As it is illustrated in the simulation section, the simulation results of the Type II Fuzzy Logic Controller has better dynamic performance than the PI controller due to better decision making than PI controller to reduce the phase difference between grid voltage and current.

#### REFERENCES

- [1] S. Khomfoi, L.M. Tolbert, "Multilevel Power Converters", Power Electronics Handbook, The University of Tennessee, Department of Electrical and Computer Engineering,

- [2] J. Rodriguez, L. Jih-Sheng, P.F. Zheng, "Multilevel inverters: a survey of topologies, controls, and applications," IEEE Transactions on Industrial Electronics, vol. 49, no. 4, pp. 724-738, Aug 2002

- [3] A. Marzoughi, H. Imaneini, A. Moeini, "An optimal selective harmonic mitigation technique for high power converters", International Journal of Electrical Power & Energy Systems, Volume 49, July 2013, Pages 34-39

- [4] A. Moeini, H. Iman-Eini, M. Bakhshizadeh, "Selective harmonic mitigation-pulse-width modulation technique with variable DC-link voltages in single and three-phase cascaded H-bridge inverters", *Power Electronics, IET*, vol. 7, no. 4, pp. 924-932, Apr. 2014.

- [5] A. Moeini, A. Marzoughi, H. Iman-Eini, S. Farhangi, "A modified control strategy for cascaded H-bridge rectifiers based on the low frequency SHE-PWM", Environment and Electrical Engineering (EEEIC), 2013 12th International Conference on , vol., no., pp.501,506, 5-8 May 2013.

- [6] A. Moeini, H. Iman-Eini, A. Marzoughi, "DC link voltage balancing approach for cascaded H-bridge active rectifier based on selective harmonic elimination-pulse width modulation", *Power Electronics, IET*, vol. 8, no. 4, pp. 583-590, 2015.

- [7] A.J. Watson, J.C. Clare, P.W. Wheeler, "A Selective Harmonic Elimination approach to DC link balancing for a Multilevel Rectifier", Power Electronics and Motion Control Conference, 2006. EPE-PEMC 2006. 12th International, vol., no., pp.154-159, Aug. 30 2006-Sept. 1 2006.

- [8] M. Aleenejad, H. Iman-Eini, S. Farhangi, "Modified space vector modulation for fault-tolerant operation of multilevel cascaded H-bridge inverters," *Power Electronics, IET*, vol.6, no.4, pp.742,751, April 2013

- [9] M. Aleenejad, H. Iman-Eini, S. Farhangi, "A minimum loss switching method using space vector modulation for cascaded H-bridge multilevel inverter," *Electrical Engineering (ICEE), 2012 20th Iranian Conference on*, vol., no., pp.546,551, 15-17 May 2012

- [10] M. Aleenejad, R. Ahmadi, P. Moamaei, "Selective harmonic elimination for cascaded multicell multilevel power converters with higher number of H-Bridge modules," *Power and Energy Conference at Illinois (PECI)*, 2014, vol., no., pp.1,5, Feb. 28 2014-March 1 2014

- [11] N. Mohan, Power Electronics Converters Applications and Design. Michigan: John Wiley and Sons. pp. Chapter 1. ISBN 978-0-471-22693-2.

- [12] N. Davoudzadeh, M. Tafazoli, M.R. Sayeh, "On linearity of all optical asynchronous binary delta-sigma modulator," Optics Communications, Volume 308, 1 November 2013, Pages 49-53.

- [13] N. Davoudzadeh, M. Tafazoli, M.R. Sayeh, "All-optical proteretic (reversed-hysteretic) bi-stable device, Optics Communications," Volume 331, 15 November 2014, Pages 306-309.

- [14] M. Tafazoli, N. Davoudzadeh, M.R. Sayeh, "All optical asynchronous binary delta-sigma modulator, Optics Communications," Volume 291, 15 March 2013, Pages 228-231.

- [15] Ferdowsi, F.; Yazdankhah, A.S.; Rohani, H, "A combinative method to control output power fluctuations of large grid-connected photovoltaic systems," in Environment and Electrical Engineering (EEEIC), 2014 14th International Conference on , vol., no., pp.260-264, 10-12 May 2014

- [16] [16] Ferdowsi, F.; Yazdankhah, A.S.; Abbasi, B., "Declining power fluctuation velocity in large PV systems by optimal battery selection," in Environment And Electrical Engineering (EEEIC), 2012 11th International Conference on, vol., no., pp.983-988, 18-25 May 2012

- [17] S.M Sajjadi, A.Sadeghi Yazdankhah, F. Ferdowsi. "A new gumption approach for economic dispatch problem with valve-point and losses effect based on valve-point active power" Elsevier, International journal of Electric Power Systems Research (EPSR), 2012.

- [18] A. Ates, B.B. Alagoz, G.T. Alisoy, C Yeroglu and H.Z. Alisoy," Fuzzy Velocity and Fuzzy Acceleration in Fractional Order Motion", BALKAN JOURNAL OF ELECTRICAL & COMPUTER ENGINEERING, DOI: 10.17694/bajece.52354.

- [19] Muddasani Satyanarayana, P. Satish Kumar,"Analysis and Design of Solar Photo voltaic Grid Connected Inverter", Indonesian Journal of Electrical Engineering and Informatics (IJEEI), DOI: 10.11591/ijeei.v3i4.174

- [20] Ferdowsi, F.; Edington, C., El-Mezyani T "Real-Time Stability Assessment Utilizing Non-Linear Time Series Analysis, Case Study: Solid State Transformers" 2015 North American Power Symposium Conference, 4-6 Oct 2015, Charlotte, NC.

- [21] Moosavi, M.; Farivar, G.; Iman-Eini, H.; Shekarabi, S.M., "A Voltage Balancing Strategy With Extended Operating Region for Cascaded H-Bridge Converters," in Power Electronics, IEEE Transactions on , vol.29, no.9, pp.5044-5053, Sept. 2014

- [22] Moamaei, P.; Mahmoudi, H.; Ahmadi, R., "Fault-tolerant operation of cascaded H-Bridge inverters using one redundant cell," in Power and Energy Conference at Illinois (PECI), 2015 IEEE, vol., no., pp.1-5, 20-21 Feb. 2015