International Journal of Electrical and Computer Engineering (IJECE) Vol. 6, No. 3, June 2016, pp. 1260 ~ 1273 ISSN: 2088-8708, DOI: 10.11591/ijece.v6i3.8193

**1**260

# Direct Instantaneous Power Control for Three-Level Grid-Connected Inverters

# Yong Yang

School of Urban Railway Transportation, Soochow University, China

# Article Info

# ABSTRACT

# Article history:

Received May 12, 2015 Revised Nov 5, 2015 Accepted Nov 25, 2015

#### Keyword:

Direct Instantaneous Power Control Grid-Connected Inverters MPPT PSD

Power electronic grid-connected inverters are widely applied as grid interface in renewable energy sources. This paper presents direct instantaneous power control of three-phase three-level Neutral Point Clamped (NPC) gridconnected inverters in photovoltaic generation systems. The system consists of a PV array, DC/DC converter, three-level NPC inverter, LC filter and the grid. In order to achieve maximum power point tracking (MPPT), an adaptive perturb and observe MPPT is used. For balancing the neutral point (NP) voltage, the control scheme through proportional integral (PI) control according to the direction of the NP current based on redundant vector selection is used. Direct instantaneous power control is developed in a rotating synchronous dq reference frame with space vector modulation with improved operation performance. In addition, the paper gives a performance study of the positive sequence detector (PSD) plus a synchronous reference frame phase-locked loop (PLL) as the synchronization method. The performance of the proposed method is investigated by a grid-connected photovoltaic system with a nominal power of 12kW. The feasibility of the proposed method is verified through experimental results, showing good steady-state and dynamic performance.

> Copyright © 2016 Institute of Advanced Engineering and Science. All rights reserved.

#### Corresponding Author:

Yong Yang, School of Urban Railway Transportation, Soochow University, 2A321, Yangchenghu Campus, JiXue Rd.No.8, Xiangcheng Area, SuZhou, China. Email: yangy1981@suda.edu.cn

# 1. INTRODUCTION

Nowadays, the distributed generation based on renewable energies, such as photovoltaic (PV) energy, wind energy and hydropower energy have come to assume an ever-growing [1]-[2]. The renewable energy source will reduce carbon emission. Photovoltaic generation can be currently regarded as one of the most promising energy sources in the renewable energy sources. Due to the nonlinear characteristics of PV array, the maximum power point (MPP) tracking (MPPT), which captures the maximum power from the PV array, becomes an essential part of PV power generation systems. Many MPPT algorithms have been proposed for improving the efficiency of the PV generation systems. The existing techniques vary in simplicity, accuracy, time response, cost, and other technical aspects. Among them, perturb and observe (P&O) method is the most common for simplicity, ease of implementation. However, the method itself is not quite accurate and is prone to failing in quickly tracking the MPP [3]-[4]. The incremental conductance of PV array [5]-[6]. It is much more sophisticated and needs complicated implementation of hardware and software, but it seldom reaches the MPP in practical situations. Fuzzy logic controllers, genetic algorithms and chaotic algorithms are the most recent advanced MPPT methods, which own their important capability of capturing MPP, even under partially shading for PV systems [7]. When selecting a MPPT method among many MPPT

methods, a DC-DC converter should be connected between the PV array and the load. The Boost converter has the high efficiency among non-isolated DC-DC converters [8].

In the last decades, multilevel inverters have attracted great interest in distributed power generation systems. They are many kinds of topologies, such as diode-clamped, clampling-capacitor, isolated H-bridge and so on [9]-[10]. Among these topologies, the three-level neutral point clamped (NPC) voltage source inverter (VSI) has become the most widely used in industry [11]. It does not require clamping capacitors and isolation transformers and thus its hardware is simple and the total harmonic distortion in its output voltages and currents is smaller than that in the conventional two-level VSI, for which the three level NPC VSI has come to widespread use in distributed power generation systems, especially in PV generation systems. Yet it raises a widely recognized question how to achieve the neutral-point (NP) voltage balancing. So far, various strategies have been presented and successful balancing operations have been demonstrated. One common strategy is to employ two separate dc sources, which are usually supplied by a transformer with two separate windings via diode full-bridge rectifiers. However, the dc sources are large, expensive and of low efficiency. Another strategy, as presented in [12], is injecting a current into the NP through an additional converter, which adds to the system cost and control complexity.

The grid synchronization techniques can be split into two main categories. The methods based on zero-crossing detection (ZCD) which does not contain a phase controller and the methods based on phase locked loop (PLL) that involves a phase controller. Since the ZCD method can be detected only at every half cycle of the grid frequency, so a fast dynamic performance cannot be obtained. Recently, there has been an increasing interest in PLL techniques for grid-connected inverter systems [13]-[14]. The main task of the PLL algorithm is to provide the phase angle of the grid voltages which is mostly used to synchronize the output currents of the three-phase inverter with the grid voltages at the point of common coupling (PCC). The dq-PLL method, also known as synchronous reference frame phase locked loop is the classical synchronization algorithm, that is easy to implement, but it is also very sensitive to the utility grid voltage unbalances, which will produces second order harmonics in dq synchronous reference frame (rotating at the angular speed  $\omega$ ) due to the effect of the negative sequence voltage (rotating at the angular speed  $-\omega$ ) of the unbalanced utility grid voltages. For this reason, a large amount of studies have been carried out in this area in order to find a solution. The positive sequence detector plus a dq-PLL (PSD+dq-PLL) method was proposed in [14], which have analyzed and tested using a model of a grid-connected system and introducing some disturbances to the three-phase utility grid such as voltage unbalances, frequency variations and harmonic distortions.

Various control methods for PWM inverter have also been proposed in recent works. But most of the works focus on the two-level topology and few dwell on the three-level PWM inverter. Moreover, owing to the special requirements of the three-level PWM inverter, such as NP voltage balance, the control strategies for the two-level PWM inverter cannot be directly applied. And the well-known method of voltage-oriented control (VOC) that are suitable for the three-level PWM inverter employs an outer dc link voltage control loop and an inner current control loop to guarantee an excellent dynamic performance [15]-[18]. However, the final configuration and performance of the system largely depend on the quality of the applied current control strategy. In [18], the three-phase three-level NPC inverter using VOC is also applied in photovoltaic generation systems, but NP voltage balance is not considered.

In this paper, direct instantaneous power control with space vector modulation (SVM) is implemented in a rotating synchronous dq reference frame, which possesses the capability of eliminating steady-state error and fast transient response by decoupling control. The paper uses three-level NPC grid-connected inverters based on Boost converter, which is able to simplify the process of MPPT control and broaden the range of PV array input voltage. The NP voltage balance is achieved through proportional integral (PI) control according to the direction of the NP current based on redundant vector selection. The positive sequence detector (PSD) plus a synchronous reference frame phase-locked loop (PLL) as the synchronization method is adopted. The PV system using a 32 bit digital signal processor (TMS320F2808) is implemented. Experimental results obtained on a 12kW prototype show high performance, such as a near-unity power factor (99.9%), high MPPT efficiency (99.95%), high power conversion efficiency and low current total harmonic distortion (THD) less than 3%.

# 2. SYSTEM MODEL AND CONTROL STRATEGY

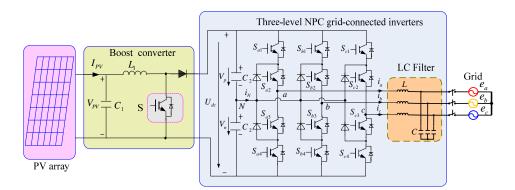

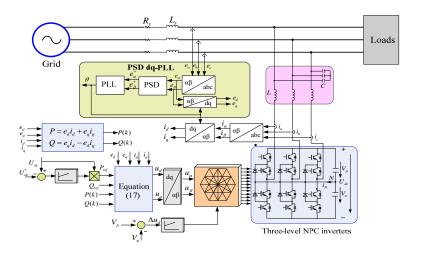

Figure 1 shows the overall configuration of a transformerless three-phase three-level NPC gridconnected inverter system. The system is composed of a PV array, DC/DC Boost converter, three-level NPC grid-connected inverter, LC filter and the grid. The Boost converter performs MPPT control. The Boost converter allows for a wide range of PV voltages. The output voltage of the PV array is widely varying from 300 V to 900 V. The dc bus contains two nominally identical capacitors. The clamped point of the NPC inverter is connected to the capacitors at the midpoint *N* which is assumed to be the circuit voltage reference. The NPC inverter regulates dc link voltage and controls the active and reactive powers. For the utility grid, the output of the inverter system is defined as 12 kW, 400 V, 50 Hz. To obtain high system efficiency, a low PWM switching frequency is chosen, which is set to be 10 kHz for both the DC/DC Boost converter and the NPC inverter.

Figure 1. Diagram of the three-phase three-level NPC grid-connected inverter system

# 2.1. MPPT control

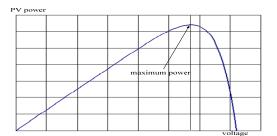

A PV array is consisted by numbers of solar cell in series or parallel, and the total power of the PV array is the sum power of all of the individual solar cells. Many methods have proposed for modeling the PV cell. The PV array produces different levels of power under different solar irradiation and temperature. Figure 1 displays the P-V curve of a PV array. As shown in Figure 2, there is one operating point where the PV array generates maximum power.

Figure 2. Characteristic of a PV array

P&O method is the most widely used in commercial PV converters, where the method is considered as "trial and error". The main advantage of the MPPT algorithm is its simple control and structure, but it has some drawbacks such as oscillations in steady-state around MPP and failing to track the MPP under sudden irradiation change [18]. For P&O algorithm, a larger perturbation size will lead to faster dynamics for capturing power from the PV array but will causes oscillations in PV current and PV voltage, a small perturbation size will reduces in PV current and PV voltage but will produce a slower dynamics of extracting power from the PV array [18]. As a compromise, a variable step P&O method is employed to extract maximum power from the PV array and to deliver it to the inverter. The reference voltage for the PV arrays is calculated as follows [18]:

$$V_{\text{ref},k+1} = V_{\text{ref},k} + M \,\frac{\Delta P_k}{\Delta V_k} \tag{1}$$

where k and k+1 are the sampling instants, M is the step size and  $\Delta P_k / \Delta V_k$  is the instantaneous power slope at the PV array output.

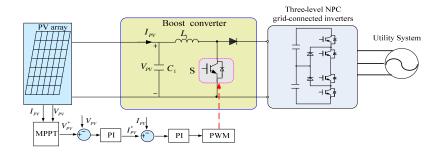

The main job is to choose and design a highly efficient converter when the variable step P&O method is used, which is considered as the main part of the MPPT. The Boost converter has low switching losses and high efficiency among nonisolated DC-DC converters. Thus, the Boost converter is employed in designing the MPPT. Control of Boost converter is based on two control loops and two serial-connected PI controllers, which is shown in Figure 3. The reference PV array voltage  $V_{PV}^*$  in outer loop is set by an adaptive P&O MPPT method. The reference PV array voltage  $V_{PV}^*$  is compared with the measured PV array voltage  $V_{PV}$  and the error is sent to proportional integral (PI) controller. The output signal from the PV array voltage  $I_{PV}^*$  is the reference current of the PV array. Then the output of current control loop is used by simple modulation to generate switching pulse of Boost converter.

Figure 3. Control scheme of MPPT based on Boost converter

#### 2.2. Grid synchronization

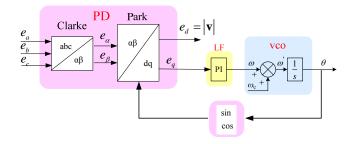

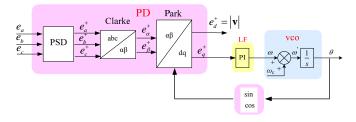

PLL will detect the phase angle and the magnitude of the three-phase utility grid voltages with good steady-state and dynamic response. There are many studies which show different structures and algorithms for PLL methods. The synchronous reference frame PLL method, which has used in many renewable generation systems, is displayed in Figure 4. The structure is consisted by Clarke transformation and Park transformation as phase detection (PD), the PI regulator as the loop filter, and the integrator as the voltage-controlled oscillator (VCO). As shown in the Figure 4, the input variables of the PLL are the three-phase utility grid voltages, and the output variables of the PLL are the phase angle of the three-phase utility grid voltages.

Figure 4. Block diagram of the dq-PLL method

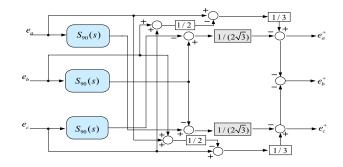

The measured signals of the three-phase utility grid voltages are contaminated with harmonics, voltage unbalances, and frequency variations. A solution for these problems caused by the unbalanced three-phase utility grid voltages is to add a positive sequence detector (PSD) block, which is based on the symmetrical component method. Applying the theorem, the unbalanced three-phase utility grid voltages can be decomposed into its positive, negative and zero sequences. The instantaneous positive sequence components  $(e_a^+, e_b^+, e_c^-)$  of an unbalanced utility grid voltages  $(e_a, e_b, e_c)$  is given by:

$$\begin{bmatrix} e_a^+ \\ e_b^+ \\ e_c^+ \end{bmatrix} = \frac{1}{3} \begin{bmatrix} 1 & \beta & \beta^2 \\ \beta^2 & 1 & \beta \\ \beta & \beta^2 & 1 \end{bmatrix} \begin{bmatrix} e_a \\ e_b \\ e_c \end{bmatrix}$$

(2)

where:

$$\begin{cases} \beta = e^{j2\pi/3} = -1/2 - \sqrt{3}(e^{-j\pi/2})/2\\ \beta^2 = e^{j4\pi/3} = -1/2 + \sqrt{3}(e^{-j\pi/2})/2 \end{cases}$$

(3)

Using (3) and (4), the instantaneous positive sequence components  $(e_a^+, e_b^+, e_c^+)$  can be obtained as:

$$\begin{cases}

e_a^+ = \frac{1}{3}e_a - \frac{1}{6}(e_b + e_c) - \frac{1}{2\sqrt{3}}S_{90}(e_b - e_c) \\

e_b^+ = \frac{1}{3}e_b - \frac{1}{6}(e_c + e_a) - \frac{1}{2\sqrt{3}}S_{90}(e_c - e_a) = -(e_a^+ + e_c^+) \\

e_c^+ = \frac{1}{3}e_c - \frac{1}{6}(e_a + e_b) - \frac{1}{2\sqrt{3}}S_{90}(e_a - e_b)

\end{cases}$$

(4)

where  $S_{90}$  is a 90 degree phase shift operator, which can be realized by a simple first-order filter and its following transfer function can be obtained as:

$$S_{90}(s) = \frac{1 - (s / \omega_0)}{1 + (s / \omega_0)}$$

(5)

where  $\omega_0$  is the angular frequency of the utility grid voltages.

Figure 5. Block diagram of the PSD block

According to (5), the PSD block can be achieved, which is shown in Figure 5. The PSD dq-PLL synchronization algorithm will be achieved by adding the PSD block to the classical dq-PLL structure shown in Figure 4, which can achieve a reliable detection of the positive sequence voltage of the phase and frequency of the unbalanced three-phase utility grid voltages. The overall structure of the PSD dq-PLL is displayed in Figure 6.

Figure 6. Block diagram of the PSD dq-PLL method

# 2.3. PWM modulation

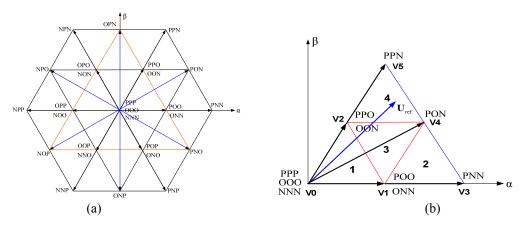

The three-level NPC generates 27 vectors as shown in Figure 7 (a): 3 zero voltage vectors (ZVVs) (NNN,OOO,PPP), 12 small voltage vectors (SVVs) (ONN,POO, OON, PPO, NON, OPO, OPP, NOO, OOP, NNO, POP, ONO), 6 medium voltage vectors (MVVs) (PON, OPN, NPO, NOP, ONP), and 6 large voltage vectors (LVVs) (PNN, PPN, NPP, NNP, PNP). LVVs divide the plane into six sectors, where each sector covers the space corresponding to 60 degree. For the sake of brevity, mathematical formulations are presented only for the first sector. Figure 7 (b) shows the space vector representation of the first sector and consists of four triangles numbered from 1 to 4. Based on the space vector modulation (SVM) theory, the expected voltage vector of an NPC converter is synthesized by three adjacent voltage vectors.

In the NPC converter, ZVVs or LVVs do not affect the neutral point (NP) balance because they connect the phase currents not to the NP, but to the positive or negative dc rail. MVVs connect one of the phase currents to the NP thus making the NP voltage dependent partly on the loading conditions, which become the main factor resulting in NP voltage unbalance. SVVs come in pairs and each pair exports a pair of voltages of the same value but in opposite directions. Hence, SVVs can be further divided into positive SVVs and negative SVVs. Consequently, in order to maintain balanced voltages in the dc-link capacitors, the present voltage imbalance and the direction of the instantaneous output should be known. If the NP current  $i_N$  is positive/negative, it will discharge/charge the lower capacitor. Take Figure 1 for example, if the output current  $i_a$  is positive, ONN will discharge the lower capacitor ( $i_N = i_a$ ), and POO will charge the lower capacitor ( $i_N = i_a$ ), and they exert exactly opposite effects on the NP voltage. Consequently, control of the NP voltage is achieved through selecting the switching pattern of the vectors. Modulation for the NPC converter utilizes symmetrical placement vectors, of which the first effective vector is a negative SVV. Switching patterns for different voltage vectors in the first sector are presented in Table 1.

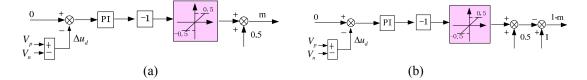

Supposing the total onduration time of SVVs is  $T_{SVV}$ , and the onduration time of a negative SVV is  $T_{sn} = mT_{SVV}$  ( $0 \le m \le 1$ ), that of the corresponding positive SVV  $T_{sp}$  can hence be determined via the following expression:

$$T_{sp} = (1-m)T_{sVV} \tag{6}$$

The NP voltage can be balanced through a linear PI controller according to the direction of the NP current, the relationship between switching states of SVVs and output phase currents which is shown in Table 2. Control scheme for balancing NP voltage is displayed in Figure 8 and the symbol  $\Delta u_d$  is defined as the difference between  $V_p$  and  $V_p$ .

Figure 7. Space voltage vector for three-level NPC inverter

| Tabl   | le 1. Vector sequence in the first sector |

|--------|-------------------------------------------|

| Region | Vector sequence                           |

| 1      | ONN-OON-OOO-POO-POO-OOO-OON-ONN           |

| 2      | ONN-PNN-PON-POO-POO-PON-PNN-ONN           |

| 3      | ONN-OON-PON-POO-POO-PON-OON-ONN           |

| 4      | OON-PON-PPN-PPO-PPO-PPN-PON-OON           |

Direct Instantaneous Power Control for Three Level Grid Connected Inverters (Yong Yang)

| able 2. Relations | inp between switch | ing states of SVV a | nu output phase currents |

|-------------------|--------------------|---------------------|--------------------------|

| Negative SVV      | NP current         | Positive SVV        | NP current               |

| ONN               | $i_N = i_a$        | POO                 | $i_N = -i_a$             |

| OON               | $i_N = -i_c$       | PPO                 | $i_N = i_c$              |

| NON               | $i_N = i_b$        | OPO                 | $i_N = -i_b$             |

| NOO               | $i_N = -i_a$       | OPP                 | $i_N = i_a$              |

| NNO               | $i_N = i_c$        | OOP                 | $i_N = -i_c$             |

| ONO               | $i_N = -i_b$       | POP                 | $i_N = i_b$              |

|                   |                    |                     |                          |

Table 2. Relationship between switching states of SVV and output phase currents

Figure 8. Control scheme for balancing NP voltage (a) when  $i_N > 0$  (b) when  $i_N < 0$

#### 2.4. NPC inverter control

In the stationary  $\alpha\beta$  reference frame for a balanced three-phase system, the inverter output currents in Figure 1 can be expressed as follows:

$$\begin{cases} L \frac{\mathrm{d}i_{\alpha}}{\mathrm{d}t} = u_{\alpha} - e_{\alpha} - Ri_{\alpha} \\ L \frac{\mathrm{d}i_{\beta}}{\mathrm{d}t} = u_{\beta} - e_{\beta} - Ri_{\beta} \end{cases}$$

(7)

where  $u_{\alpha}$  and  $u_{\beta}$  are the  $\alpha$  and  $\beta$  components of NPC inverter output voltages respectively.  $e_{\alpha}$  and  $e_{\beta}$  are the  $\alpha$  and  $\beta$  components of grid voltages, respectively.  $i_{\alpha}$  and  $i_{\beta}$  are the  $\alpha$  and  $\beta$  components of inverter output currents, respectively. *L* is the filter inductance. *R* is the total resistance of the NPC inverter.

Transformation (7) from stationary  $\alpha\beta$  reference frame to rotating dq coordinates, the synchronous dq reference frame grid currents can be obtained as

$$\begin{cases} L \frac{\mathrm{d}i_d}{\mathrm{d}t} = u_d - e_d - Ri_d - \omega i_q \\ L \frac{\mathrm{d}i_q}{\mathrm{d}t} = u_q - e_q - Ri_q + \omega i_d \end{cases}$$

(8)

where  $u_d$  and  $u_q$  are *d*-axis and *q*-axis output voltages of the NPC inverter respectively.  $e_d$  and  $e_q$  are *d*-axis and *q*-axis grid voltages, respectively.  $i_d$  and  $i_q$  are *d*-axis and *q*-axis grid currents, respectively.  $\omega$  is grid voltage angular frequency.  $\omega i_d$  and  $\omega i_q$  are induced voltages due to the transformation of filter inductance from  $\alpha\beta$  frame to dq.

Applying a sampling period  $T_s$ , the equation (8) can be discretized as follows:

$$\begin{cases} i_d(k+1) = (1 - \frac{T_s R}{L})i_d(k) + \frac{T_s}{L}(u_d(k) - e_d(k)) - \omega T_s i_q(k) \\ i_q(k+1) = (1 - \frac{T_s R}{L})i_q(k) + \frac{T_s}{L}(u_q(k) - e_q(k)) + \omega T_s i_d(k) \end{cases}$$

(9)

The instantaneous power can be computed in stationary  $\alpha\beta$  coordinates as follows:

$$\begin{cases}

P = e_{\alpha}i_{\alpha} + e_{\beta}i_{\beta} \\

Q = e_{\beta}i_{\alpha} - e_{\alpha}i_{\beta}

\end{cases}$$

(10)

After this transformation, the three-phase active power and reactive power can be obtained in dq rotating frame as follows:

$$\begin{cases} P = e_d i_d + e_q i_q \\ Q = e_q i_d - e_d i_q \end{cases}$$

(11)

The active and reactive powers in the rotating reference frame at (k+1) sampling instant can be given as

$$\begin{cases} P(k+1) = e_d(k+1)i_d(k+1) + e_q(k+1)i_q(k+1) \\ Q(k+1) = e_q(k+1)i_d(k+1) - e_d(k+1)i_q(k+1) \end{cases}$$

(12)

For a small enough sampling time, it can be obtained as

$$\begin{cases} e_d(k+1) = e_d(k) \\ e_q(k+1) = e_q(k) \end{cases}$$

(13)

By substituting (9) and (13) in (12), we obtain:

$$\begin{cases} P(k+1) = [(1 - \frac{T_s R}{L})i_d(k) + \frac{T_s}{L}(u_d(k) - e_d(k)) - \omega T_s i_q(k)]e_d(k) \\ + [(1 - \frac{T_s R}{L})i_q(k) + \frac{T_s}{L}(u_q(k) - e_q(k)) + \omega T_s i_d(k)]e_q(k) \\ Q(k+1) = [(1 - \frac{T_s R}{L})i_d(k) + \frac{T_s}{L}(u_d(k) - e_d(k)) - \omega T_s i_q(k)]e_q(k) \\ - [(1 - \frac{T_s R}{L})i_q(k) + \frac{T_s}{L}(u_q(k) - e_q(k)) + \omega T_s i_d(k)]e_d(k) \end{cases}$$

(14)

By using PSD dq-PLL synchronization algorithm, the q-axis grid voltage  $e_q$  will be zero, and the above equation (14) for the instantaneous powers can be simplified as:

$$\begin{cases} P(k+1) = \left[ (1 - \frac{T_s R}{L}) P(k) + \frac{T_s}{L} (u_d(k) e_d(k) - e_d^2(k)) - \omega T_s e_d(k) i_q(k) \right] \\ Q(k+1) = (1 - \frac{T_s R}{L}) Q(k) - \frac{T_s}{L} u_q(k) e_d(k) - \omega T_s e_d(k) i_d(k) \end{cases}$$

(15)

In order to make the NPC inverter output active and reactive powers at the (k+1) sampling instant equal to the given active and reactive powers at the (k) sampling instant, it can be obtained as:

$$\begin{cases} P(k+1) = P_{ref}(k) \\ Q(k+1) = Q_{ref}(k) \end{cases}$$

(16)

Substituting (16) in (15) and rearranging the results,  $u_d(k)$  and  $u_q(k)$  be calculated as:

$$\begin{cases} u_d(k) = \frac{1}{e_d} [\frac{L}{Ts} (P_{ref} - P(k)) + RP(k)] + e_d - \frac{L}{e_d} \omega Q(k) \\ u_q(k) = \frac{1}{e_d} [\frac{L}{Ts} (Q(k) - Q_{ref}) - RQ(k))] - \frac{L}{e_d} \omega P(k) \end{cases}$$

(17)

The equation (17) contains the d-axis and q-axis components of the NPC inverter output voltages in the rotating reference frame. After transformation from rotating dq coordinates to static  $\alpha\beta$  reference frame, the gating signals will then produced according to above mentioned PWM technique for three-level NPC inverters.

The direct instantaneous power control with space vector modulation control algorithm shown in Figure 9 contains the following blocks: three-level three-phase SVM, the three-phase active power and reactive power calculation, one outer dc-link voltage control loop, grid synchronization (PSD dq-PLL) and required NPC inverter voltage calculation. The dc-link voltage difference (error) of the given dc-link voltage  $U_{dc}^{*}$  and the measured dc-link voltage  $U_{dc}$  is delivered to the linear PI controller, which will achieve stabilizing the dc-link voltage of the three-level three-phase inverter. The reactive power reference can be set depending on the needs of the power system and the three-phase inverter can send or absorb reactive power, while the reference value of the active power is calculated based on measured dc-link voltage of the inverter and the output value of the outer dc-link voltage control. The required NPC inverter voltage in synchronous rotating frame in each sampling period can be directly calculated according to the given active and reactive powers, the measured active and reactive powers, the measured grid voltages, the measured grid currents, filter inductance and the total resistance, through simple mathematical calculations. After coordinate transformation  $(dq/\alpha\beta)$  from synchronous rotating frame dq into stationary coordinates  $\alpha\beta$  using grid synchronization (PSD dq-PLL), the transformation signals are given to SVM block input. And in order to balance NP voltage through the redistribution of the positive and negative small vectors usage, a PI controller has been included. The output SVM signals determinate current states of the power switches. There is a possibility to control both active power and reactive power independently.

Figure 9. Direct instantaneous power control scheme for three-level NPC inverters

# 3. EXSPERIMENTAL RESULTS

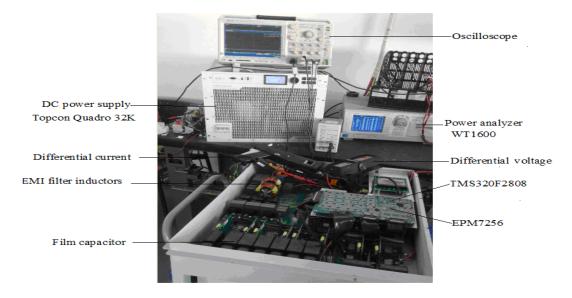

In order to verify the performance of the proposed control strategy, an experimental test bench has been developed as shown in Figure 10. Some experiments have been carried out on a laboratory setup of a 12-kW three-phase three-level NPC inverter which consists of a microprocessor based on a control circuit and a power circuit. For the control circuit, the control strategy is implemented in a software adopting a 32-bit fixed-point DSP TMS320F2808, the PWM pulses are generated through the internal pulse generator of the DSP and extended by the complex programmable logic device (CPLD) EPM7256, and voltage and current signals are measured via a 12-bit resolution of internal analog-to-digital (A/D) converter integrated in the DSP TMS320F2808. For the power circuit, it uses the Vincotech's IGBT 600V-75A for the NPC

inverter. Table 3 presents the experimental parameters. To facilitate the operational evaluation of the system performances, a PV array emulator is of particular importance in order to avoid any significant impact on the MPPT and direct power control of the three-phase three-level NPC inverter. In the experiment, the Topcon Quadro 32K programmable DC power supply is utilized as the PV array emulator, which functions as a real-time emulator of the PV array output characteristics. The PV characteristic curves and operating points can be graphically monitored through communication between the setup and a computer.

In the experiment, there are two PV array curves. The first PV array curve is set at the PV array open-circuit voltage  $V_{oc1} = 650$ V, the PV short-circuit current  $I_{sc1} = 27$ A and the PV array MPPT voltage  $V_{MP1} = 520$ V while the second PV array curve is set at the PV array open-circuit voltage  $V_{oc2} = 650$ V, the PV short-circuit current  $I_{sc2} = 13.5$ A and the PV array MPPT voltage  $V_{MP2} = 520$ V.

Figure 10. Photograph of experimental test bench

| Table 5. Experimental parameters |                                  |              |         |                                  |        |  |  |  |

|----------------------------------|----------------------------------|--------------|---------|----------------------------------|--------|--|--|--|

| Symbol                           | Description                      | Value        | Symbol  | Description                      | Value  |  |  |  |

| Р                                | Rated output power               | 12kW         | $e_{g}$ | Nominal grid phase voltage (rms) | 230V   |  |  |  |

| $f_s$                            | Switching frequency              | 10kHz        | $f_{g}$ | Nominal grid frequency           | 50Hz   |  |  |  |

| $V_{\scriptscriptstyle PV}$      | PV input voltage                 | 300V-900V    | L       | Grid filter inductance           | 0.8mH  |  |  |  |

| $L_1$                            | Boost inductance                 | 1.2mH        | С       | Grid filter capacitor            | 4.7 µF |  |  |  |

| $C_1$                            | Boost capacitor                  | $100  \mu F$ | R       | Total resistance                 | 0.1Ω   |  |  |  |

| $C_2$                            | Dc-link bus voltage<br>capacitor | 800 µF       | М       | MPPT step size                   | 0.2    |  |  |  |

# Table 3. Experimental parameters

#### 3.1. PSD dq-PLL method operation

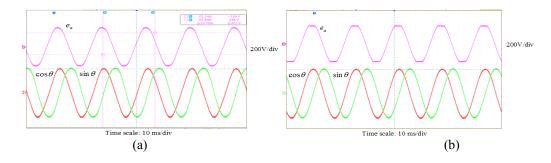

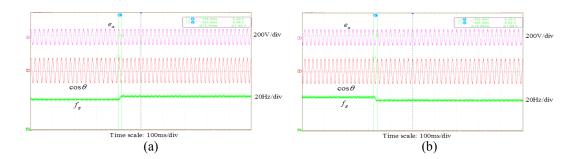

In this section, the performance of the designed PSD dq-PLL method is evaluated through experiments. In the first study, the steady-state performance is investigated. The cosine value of the grid angle  $\cos\theta$  and the sine value of the grid angle  $\sin\theta$  as well as the phase a grid voltage  $e_a$  under the nominal grid are shown in Figure 11 (a). Figure 11 (b) displays the grid angle  $\cos\theta$  and the grid angle  $\sin\theta$  as well as the phase a grid voltage  $e_a$  under the distorted grid. In the second study, the dynamic performance is investigated. Figure 12 (a) illustrates the experimental results of the phase a grid voltage  $e_a$ , the grid angle  $\cos\theta$  and grid voltage frequency  $f_g$  when the grid voltage undergoes a frequency step change from 50 Hz to 56 Hz. Figure 12 (b) shows the phase a grid voltage  $e_a$ , the grid angle  $\cos\theta$  and grid voltage changes a frequency step from 56 Hz to 50 Hz. From the Figure 11, it can be concluded that the designed PSD dq-PLL method has excellent steady-state performance even under

the distorted grid. As shown in the Figure 12, it depicts that the dynamic response of PSD dq-PLL method is very fast. The output grid frequency gets to steady state less than 20ms even the grid frequency changes 6 Hz, which is little occurrence in practical situation.

#### 3.2. Steady-state operation of NPC Inverters

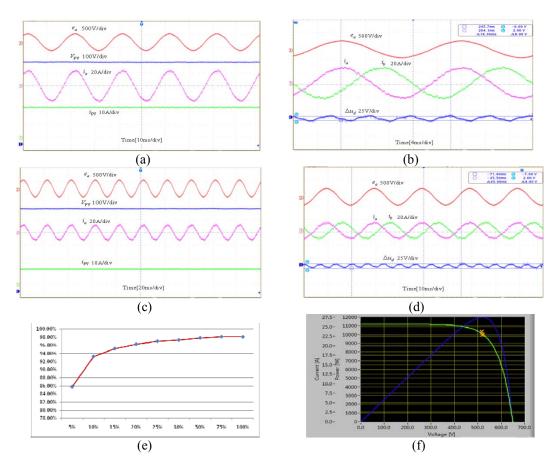

In order to achieve unity power factor, the q-axis reference reactive is set to zero. Figure 13 (a)-(d) show the steady-state experimental waveforms of phase a grid voltage  $e_a$ , phase a output current  $i_a$ , phase b

output current  $i_b$ , PV array input voltage  $V_{PV}$ , PV array input current  $i_{PV}$  and NP fluctuation voltage  $\Delta u_d$ under different PV array curve conditions after the NPC grid-connected inverter has reached the MPP. Figure 13 (a)-(b) show waveforms obtained under the first PV array curve and Figure 13 (c)-(d) display waveforms obtained under the second PV array curve. It can be seen from Figure 13, for the first PV array curve, the voltage is about 520 V and the current is around 24 A, and for the second PV array curve, the voltage is about 520 V and the current around 12 A. This figure demonstrates that the proposed MPPT control strategy is capable of reaching the MPP and of producing a nearly perfect sinusoidal current with few steady-state error and low THD less than 5%, which is recommended in IEEE Std 929-2000. Moreover, Figure 13 reveals that output currents of the NPC inverter are very well synchronized with grid voltages and the power factor is larger than 0.99 as indicated by the digital power meter (WT1600). Additionally, from Figure 13 (b) and Figure 13(d), it can be found that the NP fluctuation voltage is less than 8 V, which indicates that the NP voltage balance control scheme is fairly effective. Figure 13 (e) shows system efficiency measured by the WT1600 digital meter. It is clear that the proposed 3-level NPC inverter can achieve 98.2 % maximum efficiency and 97.5% European efficiency. Figure 13 (f) displays MPPT efficiency measured by the SAS Control software of the Topcon Quadro 32K programmable DC power supply, it can achieve 99.95 % MPPT efficiency.

#### 3.3. Dynamic performance of NPC Inverters

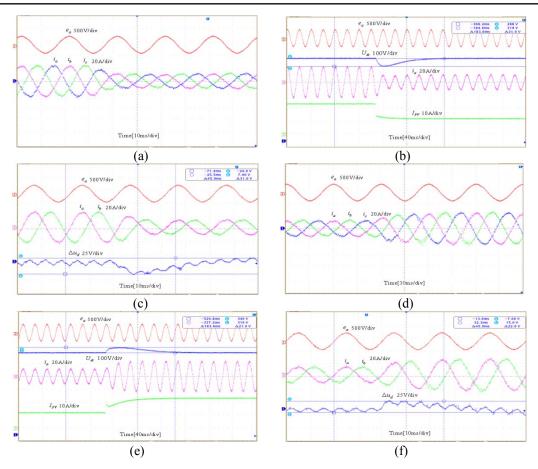

Figure 14 (a)-(f) shows the dynamic experimental waveforms of phase a grid voltage  $e_a$ , phase a output current  $i_a$ , phase b output current  $i_b$ , phase c output current  $i_c$ , PV array input current  $I_{PV}$ , dc-link bus voltage  $U_{dc}$  and NP fluctuation voltage  $\Delta u_d$  under different conditions. Figure 14 (a)-(c) displays the dynamic performance when the given PV array curve is abruptly changed from the first PV array curve to the second PV array curve, and Figure 14 (d)-(f) shows the similar transient response when changing from the second PV array curve to the first PV array curve. From this Figure, it can be concluded that the three-phase NPC inverter exhibits excellent dynamic response. Following a stepwise changing of the input PV array, the output currents of the NPC inverter can achieve steady state only needing a half cycle of the grid voltage. Figure 14 (b) and Figure 14 (e) show that the dc link voltage variation is small when the PV array power is changed abruptly, and it only needs about 3 grid voltage cycles to achieve steady state for the NPC inverter. From Figure 14 (c) and (f), it can be observed that the balance control method for the NP voltage adopted in the NPC inverter is effective, and the NP voltage is balanced not only in steady state but also in dynamic process.

Figure 11. Steady-state experimental results using PSD dq-PLL method (a) under the nominal grid condition (b) under the distorted grid condition

Figure 12. Dynamic-state experimental results using PSD dq-PLL method (a) grid voltage frequency step change from 50Hz to 56Hz (b) grid voltage frequency step change from 56Hz to 50Hz

Figure 13. Steady-state experimental waveforms of NPC inverters

Figure 14. Dynamic experimental waveforms of three-level NPC

# 4. CONCLUSION

The paper adopts a new application of three-level NPC inverter with a Boost converter as the conversion system for photovoltaic generation systems. Compared with two-level inverter, NPC inverter is capable of providing higher voltage which is desired to meet the requirement for higher efficiency. Due to the fast-changing irradiation, the simple variable step P&O method is employed to extract maximum power from the PV array. The direct instantaneous power control of three-level NPC inverter is based on required converter voltage in each sampling period being directly calculated with SVM and the NP voltage is balanced via PI control. Such a developed algorithm is featured in the following characteristics: (1) constant switching frequency of power transistors; (2) decoupling control for active and reactive power; (3) a simple MPPT control with high-accuracy tracking; (4) a simple control with good NP voltage balance.

All algorithms and controllers are implemented on the TMS320F2808 microcontroller. The proposed control strategy is verified by experimental results under various steady-state and dynamic operations. Experimental results obtained on a 12-kW prototype show high performance of the proposed algorithm.

#### ACKNOWLEDGEMENTS

This work was supported by the Research Fund for the National Young Science Foundation of China under Grant 51407124.

# REFERENCES

- [1] W. Li and X. He., "Review of Nonisolated High-step-up dc/dc Converters in Photovoltaic Grid-connected Applications," *IEEE Transactions on Industrial Electronics*, vol. 58, pp. 1239–1250, 2011.

- [2] T. Vu and M. Mufeed., "A Lyapunov Approach to Control Design for GridConnected Inverters," *TELKOMNIKA Indonesian Journal of Electrical Engineering*, vol. 12, pp. 3444-3459, 2014.

- [3] M. Peng, et al., "A Review of Current Control Strategy for Single Phase Grid Connected Inverters," TELKOMNIKA Indonesian Journal of Electrical Engineering, vol. 12, pp. 7143-7159.

- [4] T. Esram and P. L. Chapman., "Comparison of Photovoltaic Array Maximum Power Point Tracking Techniques," *IEEE Transactions on Energy Conversions*, vol. 22, pp. 439-449, Jun 2007.

- [5] M. W Enslin, *et al.*, "Integrated Photovoltaic Maximum Power Point Tracking Converter," *IEEE Transactions on Industrial Electronics*, vol. 44, pp. 769-773, 1997.

- [6] F. Liu, et al., "A Variable Step Size INC MPPT Method for PV Systems," IEEE Transactions on Industrial Electronics, vol. 55, pp. 2622-2628, 2008.

- [7] B. N. Alajmi, et al., "Fuzzy Logic-control Approach of a Modified Hill-climbing Method for Maximum Power Point in Microgrid Standalone Photovoltaic System," *IEEE Transactions on Power Electronics*, vol. 26, pp. 1022– 1030, 2011.

- [8] R. J. Wai, et al., "High-performance Stand-alone Photovoltaic Generation System," IEEE Transactions on Power Electronics, vol. 55, pp. 240–250, 2008.

- [9] H. Abu-Rub H., *et al.*, "Medium Voltage Multilevel Converters—State of the Art, Challenges and Requirements in Industrial Applications," *IEEE Transactions on Industrial Electronics*, vol. 57, pp. 2581-2596, 2010.

- [10] J. Rodríguez, et al., "Multilevel Inverters: A Survey of Topologies, Controls, and Applications," IEEE Transactions on Industrial Electronics, vol. 49, pp. 724-738, 2002.

- [11] M. Malinowski, et al., "Control of Three-level PWM Converter Applied to Variable-speed-type Turbines," IEEE Transactions on Industrial Electronics, vol. 56, pp. 69-77, 2009.

- [12] M. K. Mishra, et al., "Control Schemes for Equalization of Capacitor Voltages in Neutral Clamped Shunt Compensator," *IEEE Transactions on Power Delivery*, vol/issue: 18(2), pp. 538-544, 2003.

- [13] M. K. Ghartemani and M. R. Iravani, "A Method for Synchronization of Power Electronic Converters in Polluted and Variable-frequency Environments," *IEEE Transactions on Power Systems*, vol. 19, pp. 1263–1270, 2004.

- [14] F. D. Freijedo, et al., "Tuning of Phase Locked Loops for Power Converters under Distorted Utility Conditions," IEEE Transactions on Industrial Applications, vol. 45, pp. 2039–2047, 2009.

- [15] M. Malinowski, et al., "Simple Direct Power Control of Three Phase PWM Rectifier Using Space Vector Modulation (DPC-SVM)," IEEE Transactions on Industrial Electronics, vol. 51, pp. 447 – 454, 2004.

- [16] I. Etxeberria-Otadui, et al., "New Optimized PWM VSC Control Structures and Strategies under Unbalanced Voltage Transients," IEEE Transactions on Industrial Electronics, vol. 54, pp. 2902-2914, 2007.

- [17] Y. Suh and T. A. Lipo, "Control Scheme in Hybrid Synchronous Stationary Frame for PWM AC/DC Converter under Generalized Unbalanced Operating Conditions," *IEEE Transactions on Industrial Applications*, vol. 42, pp. 825-835, 2006.

- [18] Z. F. Ping and Y. Yong, "Three-Level Grid-Connected Inverter Based on Voltage-Oriented Control in Photovoltaic Generation Systems," *Advanced Materials Research.*, vol. 765, pp. 2494-2497, 2013.

# **BIOGRAPHIES OF AUTHORS**

**Yong Yang** received the B.Sc. degree in automation from Xiangtan University, Xiangtan, China, in 2003, and the M.Sc. degree in power electronics and drives from Guizhou University, Guiyang, China, in 2006 and the Ph.D. degree in power electronics and drives from Shanghai University, Shanghai, China, in 2010. He is currently an Assistant Professor at the School of Urban Railway Transportation, Soochow University. He has authored or coauthored more than 30 technical papers. His current research interests include distributed energy resource interfacing and control, microgrid and high-performance motor drive systems.