International Journal of Electrical and Computer Engineering (IJECE) Vol. 10, No. 4, August 2020, pp. 4008~4014 ISSN: 2088-8708, DOI: 10.11591/ijece.v10i4.pp4008-4014

# Review of high-speed phase accumulator for direct digital frequency synthesizer

# Abdulkareem Dawah Abbas

Department of Engineering of Computer Technology, Almaarif University College, Iraq

| Article Info                                                                                                                                                                               | ABSTRACT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Article Info<br>Article history:<br>Received Aug 9, 2019<br>Revised Feb 5, 2020<br>Accepted Feb 25, 2020<br>Keywords:<br>Adder<br>Phase accumulator<br>Pipelining technique<br>Register    | A review of high-speed pipelined phase accumulator (PA) is proposed in this paper. The detail explanation of ideas, methods and techniques used in previous researches to improve the PA throughput designs were surveyed. The Brent-Kung (BK) adder was modified in this paper to be applied in pipelined PA architecture. A comparison of different adder circuits, includes a modified BK, ripple carry adder (RCA), Kogge-Stone adder (KS) and other prefix adders were applied to architect the PA based on Pipeline technique. The presented pipelined PA design circuit with multiple frequency control word (FCW) and different adders were coded Verilog hardware description language (HDL) code, compiled and verified with field programmable gate array (FPGA) kit platform. The comparison result shows that the modified BK adder has fast performances. The shifted clocking technique is utilized in the proposed pipelined PA circuit to reduce the unwanted repetitive D-flip |  |  |  |

| <i>Corresponding Author:</i><br>Abdulkarim Dawah,<br>Department of Engineering of Comp<br>Almaarif University College,<br>31001 Al Ramadi, Al Anbar, Iraq,<br>Email: kerim.dawah@yahoo.com | flop (DFF) registers (coming from the pipeline technique), while preserving<br>the high speed.<br>Copyright © 2020 Institute of Advanced Engineering and Science.<br>All rights reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

# 1. INTRODUCTION

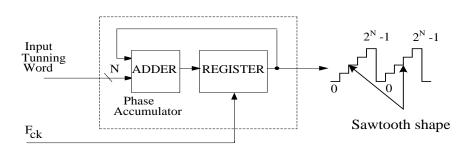

Phase accumulator can be defined as a digital circuit of adder and register that used to generate the digital values within  $(0-2\pi)$  range. Figure 1 describe the detail architecture of the PA circuit. The construction of Figure 1 describes that the adder sequentially accumulates the data control word. DFF register is defined as a storage element of the PA circuit and used to frequently repeat the feedback data to the adder in order to provide the desired digital values as a phase output (saw tooth shape).

Figure 1. Architecture of the PA circuit

**4**008

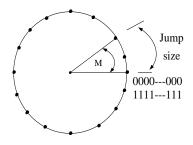

The phase output values steadily incrementally growth in the phase of  $(0: 2^{N}-1)$  with every timing pulse. The phase accumulator output can be clarified as a phase wheel in the direct digital frequency synthesizer (DDFS). It is used to represent the phase to amplitude converter (PAC) of the DDFS. The PAC digital values (also called read only memory (ROM)) are addressed regarding to the desired increment phase angle. The digital phase wheel is shown in Figure 2. The phase angle incrementally jumping with constant speed around the wheel of (0-360). One complete phase wheel cycle produces a digital sine wave in the range of  $(0-2 \pi)$ . This research addressed several approaches and techniques that able to generate fast PA throughput as well high-frequency resolution.

Figure 2. Digital phase wheel

# 2. PIPELINIED PHASE ACCUMULATOR DESIGN

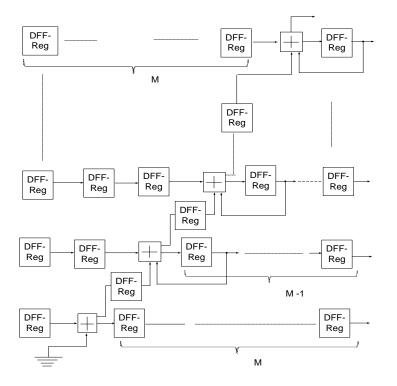

PA circuit is the component that used to provide the digital output values. The PA speed performance contributes the DDFS system. Pipeline technique is a basic technique that used to enhance the accumulator speed, this coming by splitting the main unit into a number of sequentially subs-units [1]. Pipelined PA can be classified into two types, namely; pipelined PA circuit with a single bit-layer, and with group of bit-layer of registers-adders. The block circuit diagram in Figure 3 shows the pipelined phase accumulator with single-bit layer. The mono-bit pipelined phase accumulator is used in the DDFS circuit with small PA input bits (<11-bit). As an example, in [2-4], this technique is applied to produce 9-, 12-, and 8-bit pipelined PA respectively.

Figure 3. Bloch circuit diagram of pipelined phase accumulator with single-bit layer

Another pipelined technique without pre-skewing registers in the pipelining levels is used in [5] to construct 12-bit PA. In addition to the XOR gates, a different types of speed registers are to complement the most-significant bits (MSB) values. A new pipelined PA is applied in [6] with 9-bit input. In this design, the 8-bit phase output can be obtained by complementing the high (9-th) most significant bit (MSB) to provide the output values. The benefit of the proposed pipelining technique with single-bit adder is clearly increasing the speed performance. However, this benefit accompanied by increasing the DFF registers which lead to increases the power consumption. The DDFS frequency resolution is depended on the frequency operating speed and the input bits' number (N) of the PA.

$$F_{Res} = \frac{F_{clk}}{2^N} \tag{1}$$

As shown in (1) shows that the DDFS resolution is calculated by the operating speed and the binary input bits N. As shown in (1) describes that the frequency resolution much better as much as the input bits larger. Due to that, the designers choose accumulators with a large bits input (24-32) bits to obtain the desired frequency resolution for the DDFS system.

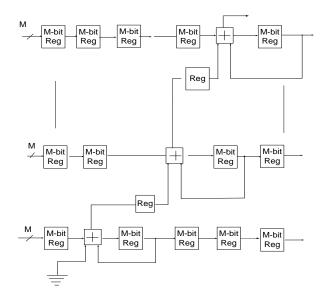

As we mentioned earlier, pipelining technique is a suitable technique for designing the fast accumulator. A using of large frequency control input bit for the pipelined PA required a group-bit stage register-adder to accomplish the suitable phase accumulator. The circuit diagram of pipelined PA with multi-bit layer is shown in Figure 4.

Figure 4. Pipelined PA circuit diagram with the multi-bit layers

An example of a large bit input is applied in [7] by Yong S. Kim to implement the pipelined PA with 32-bit. The presented design is used to achieve high-speed, as well high accuracy resolution. The clock partition approach is applied to reduce the DFF registers. This technique is used in [8] to architect pipelining PA with unequal pipelining stages (12-7-7-6 bits). The lower stage has been chosen with the high bit (12-bit), in order to avoid the growth of repetitive registers in the higher pipelined PA layers.

The phase jitter technique was applied in the classical pipelined PA circuit with 32-bit in [9]. Because it is the large bits input is used to enhance the DDFS resolution, therefore, PA output is truncated to the appropriate bit numbers that required to address the ROM phase angle. The suggested phase jitter injection is used to reduce the truncation error of DDFS output.

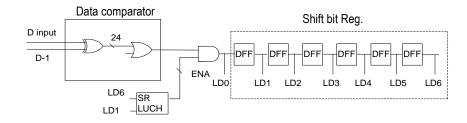

A new technique is used to design the 24- and 32-bit of pipelined PA in [10, 11] respectively, to minimize the DFF registers. The comparator block consists of OR and XOR gates detects the change in FCW and enable the output signal to the loading generator. The circuit diagram of the proposed technique is shown in Figure 5. The figure describes how is the first column LD0 be activated by the loading signal, the other (LD1-LD6) loading signals were being activated sequentially. Applying the proposed technique in the PA circuit can improve speed, and resolution a with minimum DFF registers.

Figure 5. Block circuit diagram of Loading signal generator[10]

# 3. PHASE ACCUMULATOR DESIGN BASED ON FAST ADDERS

A well-known that adder play a major role in increasing the PA speed. The conventional ripple carry adder (RCA) is the most used adder for the DDFS system. As an example, A single-bit adder in [12], is used to implement the 24-bit DDFS system with a minimum DFF registers. Carry look-ahead adder (CLA) defines as a sample of the widely used fast adder. This adder (CLA) is used in [13] ] with groups of 3-bit adder in two levels to design 9-bit PA. The CLA small group blocks are applied to avoid the circuit complexity. C Ekroot and S Long are used the 4-bit CLA circuit adder in [14], to design the 16-bit PA and enhance the DDFS performances.

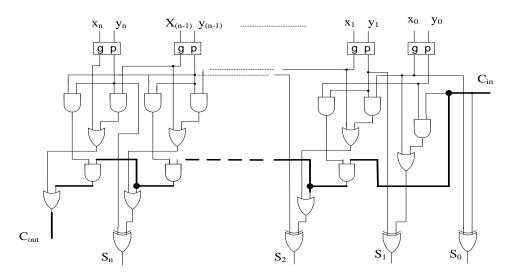

A known that prefix adders defines as a fast adder and used for binary addition in the PA design [15] for fast computations. The prefix concept defines as follows: The addition of several bit can be achieved as a time. The first level of the prefix adder circuit consists of AND and XOR gates, as a propagate (p), and generate (g) functions respectively. Figure 6 shows the circuit diagram of the prefix adder. A number of adders have been designed based on the prefix concept and used for binary addition in the phase accumulator designs. An example of these adders, as KS [16], Sklanski (SK) [17], Brent-Kunt (BK) [18], and Beaumont-Smith (BS) adder [19].

Figure 6. The prefix adder circuit

#### 3.1. Modified brent kung (BK) adder

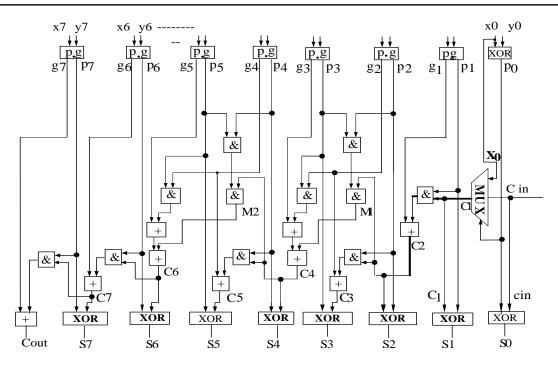

The architectures of 8-, 12-, or 24-bit of the Brent-Kung adder is available in blocks. The designers can use the BK block circuits as a fast adder. Pipelined PA requires the adder with carry in-out that sequentially pass through the accumulator stages. Due to that, a modification has been applied on the first bit adder in order to be compatible for pipelining procedure design.

R. Zimmermann in [20] was explained the prefix addition algorithm. Based on the explanation and [21], the BK adder in this review is modified to be suitable for using in the pipelined PA circuit in [22]. Figure 7 shows the modified BK adder circuit diagram. The figure describes the modification is done by removing g0 logic gate and insert a 2:1 multiplexer [23].  $P_0$  is used as a control selector of the multiplexer inputs  $X_0$  and  $C_{in}$ .

Review of high-speed phase accumulator for direct digital frequency... (Abdulkareem Dawah Abbas)

Figure 7. The modified 8-bit BK adder circuit

# 4. ARCHITECTURE OF PIPELINED PHASE ACCUMULATOR WITH DIFFERENT ADDER

Pipelined phase accumulator was designed based on RCA, modified BK adder, CLA adder, parallel-prefix adders such as SK, KS and BS adders. The comparison of the different adder was done for multiple input control words (12-, 18-, and 32-bit) to select the fast adder. The designed PA circuits were ceded Verilog hardware description language (HDL), elaborate, synthesized and verified with FPGA kit board (Cyclone III). The comparison results in the terms of maximum frequency operation in Table 1 shows the performance of the KS adder in lower bits and modified BK adder for the high number are faster adders.

| P                    | A operati | on based | on adder | (MHz)  |       |        |

|----------------------|-----------|----------|----------|--------|-------|--------|

| PA                   | RCA       | CLA      | SK       | KS     | BS    | BK     |

| 12-bit/(4-bit adder) | 319.4     | 407.2    | 354.3    | 430.11 | 420.1 | 392.4  |

| 18-bit/(6-bit adder) | 346.7     | 376.9    | 371.2    | 398.72 | 364.7 | 323.2  |

| 32-bit/(8-bit adder) | 234.6     | 2423     | 160.5    | 147.84 | 179.3 | 25/1 9 |

Table 1. Frequency operation speed of pipelined PA with different adder architecture

# 5. PIPELIND PA DESIGN WITH THE GATED CLOCKING TECHNIQUE

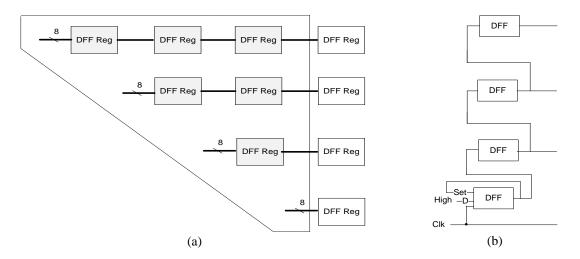

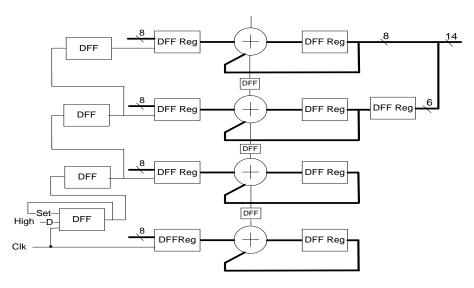

The prerequisites of the rapid PA design circuit with low-power consumption and small dimension area, demand techniques that improves the throughput yield while decreasing the number of logic cells. This trade off can be accomplished by utilizing the pipeline technique to enhance the PA speed. The disadvantage of this technique is to exponentially increase the growing of the DFF registers with expanding the pre-skewing registers of pipeline layers as shown in Figure 8(a).

To overcome the unwanted repetitive register while preserving the high speed, an appropriate method is applied to reduce the DFF registers; namely gated clocking technique. The basic idea of this method is to utilize the DFF register with Set feedback and high D input [23-25], shown in Figure 8(b), connect to another DFF register to divide the clock pulse in order to prepare it for the next layer. For the other pipeline stages, a single DFF register is suitable for the proposed design. Applying the presented gated clocking technique can remove all the gray blocks of the pre-skewing registers (48 DFF) in Figure 8(a) and replace it with 4 DFF registers in Figure 8(b). Combining the above-mentioned techniques together in the presented design as shown in Figure 9 will overcome the goal of the designers' target by achieving a high-speed PA design circuit and relatively decrease the number of registers (44 of 121 DFF registers). The proposed technique has demonstrated a 36% reduction in the term of the DFF registers.

Figure 8. (a) Pre-skewing registers of pipeline layers, (b) Gated clocking technique

Figuer 9. Pipelind PA design with the gated clocking technique

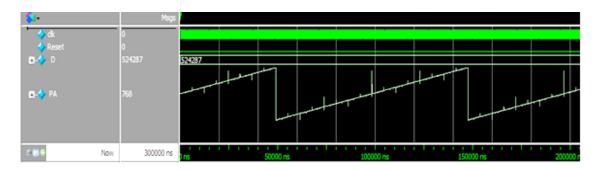

Pipeline PA design with the gated clocking technique was coded Verilog code, synthesized and elaborated using Quartus II programming software. Then, the gate level simulation has been done using cyclone III field programmable gate array (FPGA). The PA coded circuit operates with frequency speed of 286.29 MHz. The simulated results of the PA design shown in Figure 10. The figure declare the sawtooth shape of the PA output which is exponentially growth (0- $2\pi$ ) and match the mathematics results.

Figure 10. The simulation result of the pipelining PA

Review of high-speed phase accumulator for direct digital frequency... (Abdulkareem Dawah Abbas)

#### 6. CONCLUSION

This research investigates several approaches and techniques to achieve high-speed and high accuracy resolution. The modification has been applied to the BK adder to be used in the pipelined PA architecture. In addition to the CLA and RCA, multiple prefix adders such as; SK, KS, BS and modified BK adder were used in the design of the pipelined PA architecture to select the fast adder. The proposed PA circuits were coded, verified and simulated using Quartus II software. The comparison result shows BK adder perform higher-speed than the others. Based on the above good feature of the BK adder, it is used in the pipelined phase accumulator design. The clocking technique was utilized to the PA circuit in order to decrease the logic gates while preserving the high-speed throughput. The coded design of the proposed PA was verified with FPGA kit platform. The achieved results show the PA circuit operates with frequency speed of 286.29 MHz. Further, the proposed design has demonstrated a 36 % reduction in the term of the DFF registers.

#### REFERENCES

- [1] M. Abd-El-Barr and H. El-Rewini, "Fundamental of computer organization and architecture: Pipelining design techniques," *John Wiley & Sons, Inc Publication*, 2004.

- [2] X. Geng, F. F. Dai, J. D. Irwin, and R. C. Jaeger, "An 11-Bit 8.6 GHz direct digital synthesizer MMIC with 10-Bit segmented sine-weighted DAC," *IEEE Journal of Solid-State Circuits*, vol. 45, no. 2, pp. 300-313, 2010.

- [3] A. Shrestha, et al., "20 GHz clock frequency ROM-Less direct digital synthesizer comprising unique phase control unit in 0.25 μm SiGe technology," 13th Euro. Microwave Integrated Circuits Conf. (EuMIC), pp. 206-209, 2018.

- [4] G. Chen, D. Wu, Z. Jin, J. Wu. and X. Liu, "A 10GHz 8-bit direct digital synthesizer implemented in GaAs HBT technology," *Radio Frequency Integrated Circuits Symposium (RFIC), IEEE*, pp. 425-428, 2010.

- [5] B. S. Jensen, et al., "Twelve-bit 20-GHz reduced size pipeline accumulator in 0.25 μm SiGe:C technology for direct digital synthesiser applications," *IET Circuits, Devices & Systems*, vol. 6, no. 1, pp. 19-27, 2012.

- [6] C-Y. Yang, J-H. Wu, and H-Y. Chang, "A 5-GHz direct digital frequency synthesizer using an analog-sine-mapping technique in 0.35 μm SiGe BiCMOS," *IEEE Journal of Solid-State Circuits*, vol. 46, no. 9, pp. 2064-2072, 2011.

- [7] K. Yong Sin and K. Sung-Mo, "A high speed low-power accumulator for direct digital frequency synthesizer," *IEEE MTT-S International Microwave Symposium Digest*, pp. 502-505, 2006.

- [8] J. Chen, R. Luo, H. Yang, and H. Wang, "A low power ROM-less direct digital frequency synthesizer with preset value pipelined accumulator," 19th Int. Conf. on VLSI Des. held jointly with 5th Int. Conf. on Embedded Syst. Des., 2006.

- [9] W. Qing, H. Songbai, and Z. Ziming, "Design and simulation of an optimized DDS," 6th International Conference on Wireless Communications Networking and Mobile Computing (WiCOM), pp. 1-3, 2010.

- [10] Y-H. Jung, T. Yoo, S-J. Cho, and K-H. Baek, "Pipelined phase accumulator using sequential FCW loading scheme for DDFSs," *Electronics Letters*, vol. 48, no. 17, pp. 1044-1046, 2012.

- [11] Y. S. Kim, J. Lee, Y. Hong, J. E. Kim, and K-H. Baek, "Low-power pipelined phase accumulator with sequential clock gating for DDFSs," *Electronics Letters*, vol. 49, no. 23, pp. 1445-1446, 2013.

- [12] X. Geng, F. F. Dai, J. D. Irwin, and R. C. Jaeger, "24-Bit 5.0 GHz direct digital synthesizer RFIC with direct digital modulations in 0.13 μm SiGe BiCMOS technology," *IEEE Journal of Solid-State Circuits*, vol. 45, pp. 944-954, 2010.

- [13] X. Geng, F. F. Dai, J. D. Irwin, and R. C. Jaeger, "A 9-bit 2.9 GHz direct digital synthesizer MMIC with direct digital frequency and phase modulations," *IEEE MTT-S International Microwave Symposium Digest*, pp. 1125-1128, 2009.

- [14] C. G. Ekroot and S. I. Long, "A GaAs 4-bit adder-accumulator circuit for direct digital synthesis," *IEEE Journal of Solid-State Circuits*, vol. 23, no. 2, pp. 573-580, 1988.

- [15] Salah H. Ibrahim, Sawal H. Ali, and Sh. Islam, "Design a 24-bits pipeline phase accumulator for direct digital frequency synthesizer," Int. Symp. on Ins. & Meas., Sensor Net. and Auto. (IMSNA), vol. 2, pp. 393-397, 2012.

- [16] B. Tapasvi, K. B. Sinduri, B. G. S. S. B. Lakshmi, and N. U. Kumar, "Implementation of 64-bit kogge stone carry select adder with ZFC for efficient area," *IEEE Int. Conf. on Elec., Comp. and Comm. Technologies*, pp. 1-6, 2015.

- [17] A. Garg, et al., "Area efficient modified booth adder based on sklansky adder," 2nd International Conference for Convergence in Technology (I2CT), pp. 308-312, 2017.

- [18] N. U. Kumar, K. B. Sindhuri, K. D. Teja, and D. S. Satish, "Implementation and comparison of VLSI architectures of 16-bit carry select adder using Brent Kung adder," *Int. Conf. on Innov. in Power and Adv. Comp. Tech.*, pp. 1-7, 2017.

- [19] A. Beaumont-Smith and L. Cheng-Chew, "Parallel prefix adder design," 15th IEEE Symposium on Computer Arithmetic, pp. 218-225, 2001.

- [20] R. Zimmermann, "Binary adder architectures for cell-based VLSI and their synthesis," Disertation, Doctor of Technical Sciences, Swiss Federal Institute of Technology Zurich, 1998.

- [21] A. Anjit, et al., "FPGA based performance comparison of different basic adder topologies with parallel processing adder," *3rd Int. Conference on Electronics, Communication and Aerospace Technology (ICECA)*, pp. 87-92, 2019.

- [22] S. H. Ibrahim, S. H. M. Ali, and M. S. Islam, "High speed direct digital frequency synthesizer with pipelining phase accumulator based on Brent-Kung adder," *10th IEEE Int. Conf. on Semiconductor Elec. (ICSE)*, pp. 547-550, 2012.

- [23] S. H. Ibrahim, S. H. M. Ali, and Md. S. Islam, "Hardware implementation of 32-Bit high-speed direct digital frequency synthesizer," *The Scientific World Journal*, vol. 2014, pp. 1-9, 2014.

- [24] B-L. Tan, W-K. Lee, K-M. Mok, and H-G. Goh, "Clock gating implementation on commercial field programmable gate array (FPGA)," 4th Int. Conf. on Electrical, Electronics and Syst. Eng. (ICEESE), pp. 102-106, 2018.

- [25] S. H. Ibrahim, S. H. M. Ali and S. Islam, "Implementation of a 32-bit high speed phase accumulator for direct digital frequency synthesizer," *Asian Journal of Scientific Research*, vol. 7, no. 1, pp. 118-124, 2014.