# **International Journal of Electrical and Computer Engineering (IJECE)**

Vol. 10, No. 1, February 2020, pp. 719~727

ISSN: 2088-8708, DOI: 10.11591/ijece.v10i1.pp719-727

# A test architecture design for SoCs using atam method

# D. R. V. A. Sharath Kumar<sup>1</sup>, Ch. Srinivas Kumar<sup>2</sup>, Ragamayi S.<sup>3</sup>, P. Sampath Kumar<sup>4</sup>, K. Sai Kumar<sup>5</sup>, Sk Hasane Ahammad<sup>6</sup>

1,4,5,6 Department of Electronics and Communication Engineering

2,3 Department of Mathematics

1,2 KLEF, 1,2 Guntur, 2,3,5,6 AP-522502, 1,4 Mallareddy Institute of Technology 1,4 Secunderabad

#### **Article Info**

#### Article history:

Received Jun 25, 2019 Revised Aug 31, 2019 Accepted Sep 27, 2019

# Keywords:

Corebasedorganizations Entrenched core testing Mixedinteger linear programming SoC

#### **ABSTRACT**

Test arranging is a basic issue in structure on-a-chip (S.O.C) experiment mechanization. Capable investigation designs constrain the general organization check request time, keep away from analysis reserve conflicts, in addition to purpose of restriction control disseminating in the midst of examination manner. In this broadsheet, we absent a fused method to manage a couple of test arranging issues. We first present a system to choose perfect timetables for sensibly evaluated SOC's among need associations, i.e., plans that spare alluring orderings among tests. This furthermore acquaints a capable heuristic estimation with plan examinations designed for enormous S.O.Cs through need necessities in polynomial occasion. We portray a narrative figuring with the purpose of uses pre-emption of tests to secure capable date-books in favour of SOCs. Exploratory marks on behalf of an educational S-O-C plus a cutting edge SOC exhibit with the aim of capable investigation timetables be able to subsist gained in sensible CPU occasion.

Copyright © 2020Institute of Advanced Engineering and Science.

All rights reserved.

# Corresponding Author:

Sai Kumar Kayam, Department of Electronics and Communication Engineering, KL University, Vijayawada, Guntur, India.

Email: saikumarkayam4@gmail.com

# 1. INTRODUCTION

This work contracts through the arrangement of check models for specific S/O/C difficult. These structures contain wrapping along with ATAMs. For a specified S-O-C, among showed limitations of components also their assessments, we structure plans which restrain the necessary A.T.E vector reminiscence significance along amid test request occasion. In this broadsheet, we figure the issues of test building plan together for components in the company of settled with versatile distance end to end look at manacles. Along these lines, we decide a meaning of a plan self-governing test time cuts down set out toward SOCs and summary the lower set out characteristics toward the 'ITC'O3 SOC Test Benchmarks'. We absent a book building self-sufficient heuristic count to facilitate successfully redesigns the analysis plan for a prearranged S.O.C [1]. The computation beneficially chooses the amount of A\_TAMS furthermore their sizes, the errand of elements to TAMs, moreover the wrapper structure per section. We demonstrate how thus figuring container he second-hand on behalf of streamlining together Test motor vehicle plus Test Rail Architectures among consecutive moreover similar examination designs. Exploratory marks in favour of the 'I.T.C'O3 SOC Test Benchmarks' exhibit to facilitate stood out from in advance dispersed figuring's, we show signs of improvement test times at insignificant figure time [2, 3]. The usage of test traditions, tree-creating figuring's for power-obliged booking, and composed TAM plan and test arranging are different starting late.

720 🗖 ISSN: 2088-8708

Modular test developments

Isolated test enhancement is logically used for SOCs. Non-method of reasoning modules, for instance, embedded straightforward equipment along with reminiscences necessitate stay lone taxing unpaid to their 'unpredictable' route organization. Dim boxed outcast jogs, for instance, hard (plan) focuses and mixed focuses, for which no utilization purposes of intrigue are identified, ought to be attempted beside the investigations as given through their supplier, in addition to thusly furthermore necessitate stay lone taxing. Regardless, despite intended for justification sections of which the utilization unpretentious components are recognized, specific test progression is an engaging option [4-6]. At this point, a specific 'segment and-vanquish' check enhancement move towards lessens the test age enrol occasion with related information quantity. Ultimately, a deliberate check come near engages ordeal recycle, which particularly fulfills if a middle or else element is worn in various S.O.C structures. With the true objective to facilitate estimated examination enhancement, an entrenched element have to be inaccessible beginning it's incorporating equipment also electrical experiment get towards ought to exist given. Zorian et al. [1] introduce a traditional connected experiment get to building permitting confined trying of S.O.C.s including 3 parts for each module-under-test: (1)a analysis configuration basis along with descend, (2) a investigation get the opportunity to instrument (T.A.M), furthermore (3) a covering. The binding container withdraws the element beginning its condition moreover gives trading helpfulness flanked by utilitarian right of entry to the element plus test admission from side to side the T.A.M. The examination configuration have a far reaching crash together on the necessary vector reminiscence significance for each A.T.E canal, and under the analysis request instance of the S.O.C, 2 inputs parameter in the general SOC examination costs. In whatever is left of this newspaper, we unreservedly insinuate these II limitations as assessment time'.

This broadsheet watches out for the subject of organizing convincing as well as capable check get to structures including packaging furthermore T.A.M's. The broadsheet points of interest the official issue implications of assessment plan upgrade concerning compulsory A.T.E vector recollection significance also analysis submission instance, together on behalf of sections through settled extent check handcuffs and furthermore intended for At last, we there exploratory marks designed for the ITC'O2 S-O-C Test yardsticks, which demonstrate to facilitate TRARCHITECT give way centered investigation point in time grades in superfluous enlist instance [6-8].

- a. The continuation of this document is dealt with as seeks after. Fragment

- b. Reviews previous labour in this space. Territory

- c. Describe the issues of experiment building structure mutually on behalf of elements among settled moreover versatile duration channel manacles, tolerating the vital limitations of sections along with a maximal S-o-C T-A-M thickness are demonstrated.

- d. In sector underneath we decide an enhanced subordinate set out toward the analysis instance of a agreed S.o.C. Finally this displays our building independent heuristic progression figuring TR-ARCHITECT.

- e. Section 3 presents execution purposes of enthusiasm of building specific portions meant for TR-ARCHITECT pro the examination motor vehicle along with Test\_Rail Architectures. At end encloses test results for twelve yardstick SOCs. We take a gander at ordeal instance marks for TR-ARCHITECT in addition to those gained beside various systems to the theoretical inferior bounce. Zone 8 completes this manuscript.

#### 2. EXISTED WORK

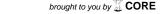

Different assessment models contain be portrayed in writing. Aerts plus Marinissen [41 portrayed the 3 sweep base analysis designs delineated in Figure 1 (a) the Multiplexing building, (b) the Daisychain Architecture, also (c) the Distribution Architecture.

Figure 1. (a) Multiplexing architecture; (b) Daisy\_chain arch; (b) Distribution arch

In the Multiplexing furthermore Daisy sequence Architectures, every elements gain induction to the occupied open T.A.M breadth. In the Multiplexing planning, only a solitary unit container be gotten to without a moment's delay. This recommends the total check moment is the entire of the personage component examination periods, yet, additional basically, in like manner with the intention of module-external difficult (i.e., hard the utensils plus cabling amidst the element) is ungainly before still incredible. This is a result of the way with the aim of merely a solitary element wrapper container be gotten to on the double, although designed for module-outside difficult the bindings of somewhere around two elements require to he got to in the meantime. In view of its bypass framework, the Daisychain construction does not contain this control [9]. In the sharing planning, the sum open T.A-M breadth is scattered more than the parts. This empowers sections to be attempted at the same time, and along these lines the total SOC test period is the most extraordinary of the separate unit test periods. With the ultimate objective to constrain the S.C.K investigation point in time, the breadth of an character T.A.M have to be promotional to the proportion of investigation information to facilitate ought to be elated to in addition to starting a unit related with the T-A-M. The analysis means of transport construction shown through Varma moreover Bhatia is a mix of the Multiplexing also Allocation Architectures.

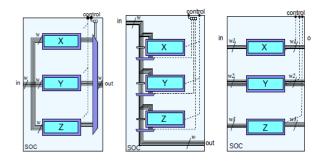

A singular analysis transport is on a very basic level the proportional as what is portrayed by the Multiplexing structural design: elements related with a comparative test transport must be attempted successively. The Test Bus Architecture considers various test transports on 1 S-O\*C, which work uninhibitedly, seeing that in the Distribution Building. Element linked to a periodic test shipment meet the negative effects of vague drawback from either the architecture of multiplexing, i.e. Difficult external module is troubling or unusual. The design Test Bus Architecture [10-14] is shown in Figure 2(a). The SOC includes six components, called A by F. This Test Bus Architecture starting point involves 3 experiment transportations. Modules An as well as B are associated with either the three-width Test Bus 1; modules C, D also E are associated with the four-width Test Bus 2; module F is associated with two-width Test Bus 3. Figure 2(b) demonstrates that the test plan can be examined. The three test transports be capable of be worked uninhibitedly. The modules related with an average test transport are attempted in a self-decisive anyway progressive demand.

We call this timetable successive, in light of the fact that per T-A-M the components are (a) (b) Figure 2 Example Test motor vehicle construction (an) as well as a possible looking at consecutive test plan (h). The analysis Rail Architecture obtainable by Marinissen et al. [6] is a mix of the Daisy chain with Allotment Architectures. A solitary assessment railing is for the most part the equal as what is portrayed through the Daisy chain Architecture: modules related with the proportional Test Rail can be attempted in the meantime and furthermore progressively. A Test Rail Architecture thinks about various Test rails on one SOC that works without reservation, as in the Architecture of Production. The advantage of Test Rail Architecture over Test Bus Design is that it simultaneously enables access to different or all wrappers, supporting subsystem-external testing. Figure 3 shows a model Test-Rail Architecture. Test Rail Architectures support various sorts of test designs. Figure 2 (b) as well as (c) demonstrate II probable looking at test designs. The timetable in Figure 2(b) is a consecutive timetable; the elements related with a run of the mill Test-Rail are attempted in a self-confident anyway progressive demand [15-17]. The timetable in Figure 2(c) is a parallel date-book. In this timetable, we detail to test all modules related with a common Test-Rail in similar.

Figure 2. (a) Example Test Bus Architecture and (b) a possible corresponding serial test schedule

# 2.1. Problems in Existed Method

To plan a trial building in support of a specified plan of element along with a known figure of experiment sticks, a S.O-C integrator needs to choose (1) the check designing make, (2) the amount of TAMs, (3) the breadths of these TAMs, (4) the undertaking of modules to T.A.Ms, furthermore (5) the covering structure for each module.

#### 2.1.1. Issue 1 [Fixed-duration Module-inner Scan handcuffs]

A game plan of elements M, furthermore for every section m E.M the amount of analysis structures p,the amount of practical data incurable I, the amount of utilitarian yield workstation om.the amount of helpful bidirectional incurable b,, the amount of range manacles s,, along with in favour of every yield series k, the extent of the yield sequence in flip disappointments l, m,k. In addition is agreed a numeral W max that addresses the most extraordinary amount of S.O.C-level TAM ropes with the aspire of can be worn. Choose a T\_A\_M designing and a wrapper plan for each module with the true objective that the general SOC-level test time (in clock cycles) is restricted also W max isn't outperformed.

#### 2.1.2. Issue 2 [Flexible-distance end to end Module-domestic Scan Chains]

All limitations as demonstrated in trouble 1, anyway as opposed to the amount of compass chains entire furthermore the span l,h in support of every yield series k, the whole integer of breadth flip disappointments is known. Choose a T-A-M building moreover a wrapper plan for each one element with the true objective to facilitate the general SOC-level test time (in clock cycles) is constrained as well as W max isn't outperformed [18-19].

#### 3. PROPOSED METHOD AND PROBLEMS SOLUTION

# 3.1. Problem 1 [fixed-length module-interior scrutinize cuffs]

A plan of sections M, along with aimed at every one Module m E-M the amount of check structures p. the amount of pragmatic data incurable I, the amount of utilitarian yield mortal om. the amount of valuable bidirectional fatals b,, the amount of scope chains s, moreover for all yield chain k, the piece of the range sequence in turn over disappointments l, m,k. Also is given a digit W max that addresses the most extraordinary integer of SOC-level TAM supports to facilitate container be use. Choose a T\_A\_M building and a wrapper structure for each module with the true objective that the general SOC-level test time (in clock cycles) is restricted in addition to W max isn't outperformed.

#### 3.2. Problem 2 [flexible-length module-internal scan chains]

All constraints as decided in trouble 1, yet as opposed to the amount of compass chains add up to along with the extent l,h on behalf of every yield chain k, the whole amount of range flip disappointments fm is specified. Choose a T.A.M designing in addition to a wrapping plan for each one module with the ultimate objective that the general SOC-level test time (in clock cycles) is constrained plus W max isn't out performed [20].

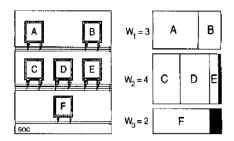

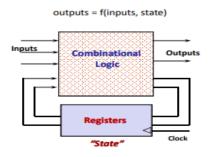

#### 3.3. Sequential circuit testing

In successive circuits the underlying state (enlist's qualities) isn't of course known. Subsequently, the refinement of flaws and the proliferation of the relating incorrect reactions may swing to be a hard undertaking. An answer is to utilize strategies for the correct instatement of the circuit state to known qualities. Use of appropriate test vector successions as well as the utilization of Set/Reset signs to setup the required state. Improvement of productive systems to set the underlying state and watch the consequent state after the reaction of the circuit.

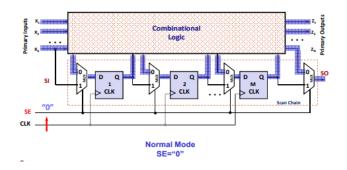

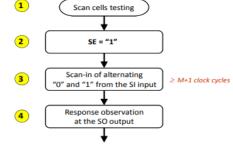

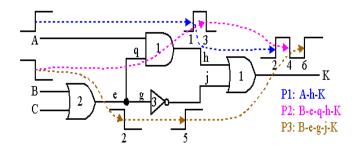

The memory components (locks or Flip-Flops) in a structure are legitimately associated with frame a brought together move enlist (filter enlist or chain). Along these lines the inside condition of the circuit is resolved (controlled) by moving in (examine in) to the sweep enlist the required test information to be connected to the combinational rationale. Besides, the current inward state (past rationale reaction) can be seen by moving out (examine out) the information put away into the sweep enlist. Figure 3 is testing related to scan sequentially. Figure 4 expalins about scaning regarding ting general test.

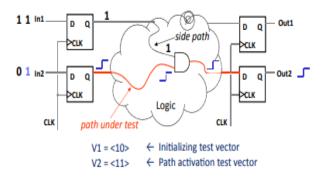

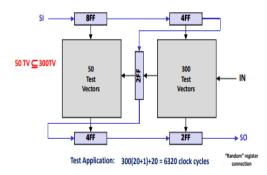

Figure 5 expalins about output way of testing here d-flip lemon assumes an imperative job so we are utilizing this strategy got issue 1 arrangement. Figure 6 expalins that output applications in the test procedure here we got high precision contrasted with existed strategies A center test wrapper called TestShell has remained projected through Marinissen et al. [3] similarly is right now exploited privileged Philips. The TestShell includes of the complementary segments. Figure 6 showns that application of scanning procedure [21-22].

A mortal test cell with each quarry. The test cell provides both transient response and discernibility. A (discretionary) bypass record allowing a TAM to sidestep center as well as packaging, throughthe ultimate goal of testing an extra center connected with a comparable TAM. A block of test controls (TCB). The TCB has a bit-cut environment along with encompass of a move in addition to a revive enlist. The TCB is principally future to manage the task of the Test Shell, throughout a little obligatory piece cuts. Additional customer branded bit cuts can be incorporated for manage of centre inner test manner.

Figure 7 is the path delay model regarding to chain of flipflops [23-24]. Figure 8 is the Flip flop chain reording with the help of scan test.

Scan-In Outputs

Scan-Out

Register

Figure 3. Sequential scan testing

Figure 4. General scan test

Figure 5. Scan path design

Figure 6. Scan applications

Figure 7. Delay fault testing

Figure 8. Reordering of scan chain Flip Flop

We have just examined various deformities that can cause postpone shortcomings:

- a. GOS deserts

- b. Resistive shorting deserts among hubs plus to the supply rails

- Scrounging transistor spillages, inadequate on intersections as well as wrong otherwise moved limit voltages

- d. Certain kinds of releases

- e. Procedure variety container similarly make gadget switch at a speed lesser than the particular.

Sweep chain reordering is a procedure utilized in the plan and testing of processing gadgets that empowers the streamlining of setting and sewing flip slump registers with an output chain. It is utilized to streamline and reorder the sweep chain process in the event that it gets isolates, ceased or congested.

#### 4. HAZARDS

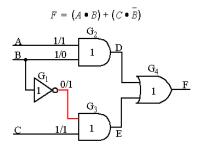

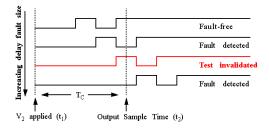

- 2 vector succession is ABC = (111), (101)

- a. Gate G 1 presents an extra postponement of 1 unit.

- b. Production E of entryway G 3 is headed to a rationale 1, once component following D > 0.

- c. Produce a malfunction on F

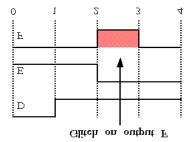

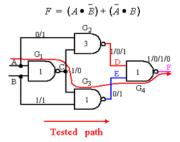

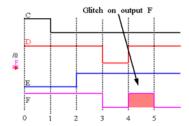

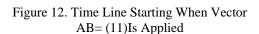

Figure 9 is the gate delays which are cicled in Figure 10 explains about time line vector ahen ABC=101 is applied. Figure 11 expalins that dyanamic hazards related to test path which is showed in Figure 12 shows that time loine starting when AB=11 applied Figure 13 is the static hazards processing with the help of dynamic hazards test generation.

Figure 9. Gate delays are circled

Figure 10. Time line starting when vector ABC=101 is applied

Figure 11. Dynamic Hazards

Figure 13. Static hazards can create dynamic hazards along tested paths and need to be considered during test generation

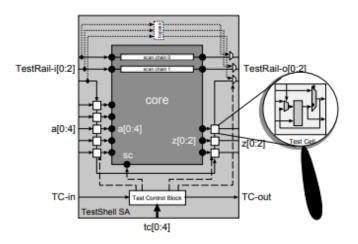

Two vector arrangement is AB = (01), (11).

Entryway G 2 has a defer estimation of 3 time units, owing whichever to an imperfection or an alternate physical execution of the NAND door. Note, in contrast to the past precedent, the anomaly happens previous to the planned change for this situation, also be able to nullify the test (e.g. blame isn't identified). Figure 14 explains that critical paths at 6 time uniuts shown in below [25-26].

Figure 14. The critical path(s) of this circuit is 6 time units

Let's set the clock period T = 7

#### Assume only one faulty path.

No delay mistake is detected if path stoppage the length of P3 is less than 7 units.

This experiment will not notice single wait faults the length of paths P1 or P2.

# Assume there can be multiple faulty paths.

Assume P2 moreover P3 are defective with P2 extend the "static glitch" at the production beyond 7 units, after that it mask P3's delay error.

This test is called a non-robust test for delay fault P3.

```

Algorithm 1 [TR-ARCHITECT]

1 CREATE START SOLUTION

2 OPTIMIZE- BOTTOM UP;

3 OPTIMIZE- TOP DOWN;

4 RESHUFFLE

Algorithm 2 [CREATE START SOLUTION]

do

{

item = 10;

value = value + item;

} while(value<100);

Item = 10;

do

{

value = value + item;

} while(value<100);

```

Figure .15 is the model of conceptual test shell using this test model ezily and fix problems in a simple manner [27]. All methods and techniques are reduces the problems 1 and 2 respectively and they give better quality design.

Figure 15. Conceptual view of Philips' Test Shell

#### 5. RESULTS

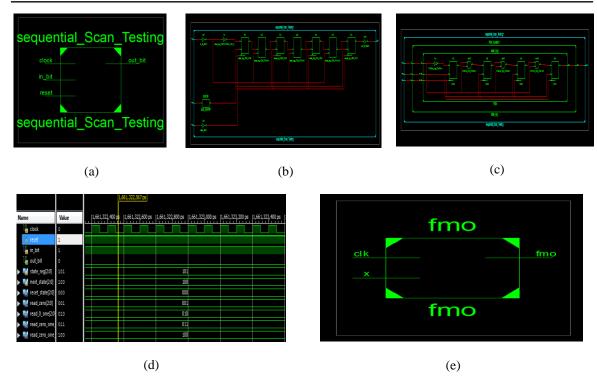

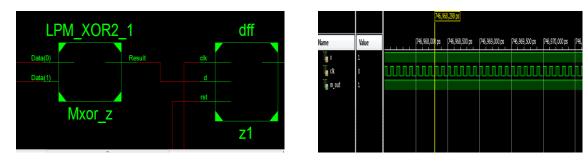

Figure 16 (a-e) is the block diagram of test cell and Figure 17 shows the internal block diagram of test cell and Figure 18 shows that the output waveforms of test cell. Table 1 explains about comparison of parameters at TAM and ATAM models here efficiency of existed is 80% but proposed method have 99.8% this is good achievement. P(E) is less compared to existed method

726 🗖 ISSN: 2088-8708

Figure 16. (a) Aseq\_scan\_test, (b). Technological schematic of seq\_scan, (c). RTL schematic of seq\_scaning\_test, (d). Output waveforms of seq\_scan\_test, (e). Test cell

Figure 17. Internal block of test cell

Figure 18. Simulation result of test cell

| rable 1. Comparions with ATAM |     |       |

|-------------------------------|-----|-------|

| PARAMETERS                    | TAM | ATAM  |

| Efficiency                    | 80% | 99.8% |

| Probability of error          | 0.1 | 0.01  |

# 6. CONCLUSION

At long last utilizing the above test cells like powerful perils, ATAM and reordering testing and postpone blame test squares we showed signs of improvement productivity and less likelihood of blunder. So contrasted with TAM, ATAM gives the better outcomes. Proficiency increments by 19.8% and likelihood of mistake is 0.01 this is great accomplishment contrasted with existed techniques.

# REFERENCES

- [1] Y. Zorian, et al., "Testing Embedded- Core Based System Chips," *Proceedings IEEE InlemationolTest Conference (ITC)*, Washington, DC, 1998.

- [2] E. J.Marinissen, et al., "ITC'02 SOC Test Benchmarks Web Site," Available: http://www.entra.research.philips.com.

- [3] E.J.Marinissen, et al., "A Set of Benchmarks for Madular Testing of SOCs," *Proceedings IEEE Invernational Test Conference (ITCJ), Baltimore, MD*, 2002.

- [4] E. J.Marinissen, et al., "Wrapper Design for Embedded Core Test," *Proceedings IEEE International Test Conference (ITC)*, Atlantic City, NJ, pp. 911-920, 2000.

- [5] V. Iyengar, et al., "Co-Optimization of TestWrapper and Test Access Architecture for Embedded Cores," *Journal of Electronic Testing: Theory and Applications*, vol. 18, pp. 213-230, 2002.

- [6] S. K.Goel and E. J.Marinissen, "Effective and Efficient Test Architecture Design for SOCs," Proceedings IEEE International Test Conference (ITC), Baltimore, MD, pp.529-538, 2002.

- [7] S. K.Goel and E. J.Marinissen, "Layout-Driven SOC Test Architecture Design for Test Time and Wire Length Minimization," *Proceedings Design, Automation, and Test in Europe (DATE)*, Munich, Germany, pp. 738-743, 2003

- [8] S. K.Goel and E. J.Marinissen, "SOC Test Architecture Design for Efficient Utilization of Test Bandwidth," ACM Transactions on Design Automation of Electronic Systems, vol. 8, pp. 399-429, 2003.

- [9] S. K.Goel and E. J.Marinissen, "Control-Aware Test Architecture Design for Modular SOC Testing," *Proceedings IEEE European Test Workshop (ETW)*, Maastricht, The Netherlands, pp. 57-62, 2003.

- [10] S. K.Goel, "A NovelWrapper Cell Design for Efficient Testing of Hierarchical Cores in System Chips," Proceedings IEEE European Test Symposium (ETS), Ajaccio, Corsica, pp. 147-152, 2004.

- [11] L. Krundel, et al., "User-Constrained Test Architecture Design for Modular SOC Testing," *Proceedings IEEE European Test Symposium (ETS)*, Ajaccio, Corsica, pp. 80-86, 2004.

- [12] A. Sehgal, et al., "P1500-Compliant Test Wrapper Design for Hierarchical Cores," *Proceedings IEEE International Test Conference (ITC), Charlotte, NC*, 2004.

- [13] S. K.Goel, et al., "Test Infrastructure Design for the NexperiaTM Home Platform PNX8550 System Chip," Proceedings Design, Automation, and Test in Europe (DATE), pp. 108-113, 2004.

- [14] J. Aerts and E. J.Marinissen, "Scan Chain Design for Test Time Reduction in Core-Based ICs," Proceedings IEEE International Test Conference (ITC), Washington, DC, pp. 448-457, 1998.

- [15] P. Varma and S. Bhatia, "A Structured Test Re- Use Methodology for Core-Based System Chips," Proceedings IEEE International Test Conference (ITC), Washington, DC, pp. 294-302, 1998.

- [16] E. J.Marinissen, et al., "A Structured and Scalable Mechanism for Test Access to Embedded Reusable Cores," Proceedings IEEE International Test Conference (ITC), Washington, DC, pp. 284-293, 1998.

- [17] K. Chakrabarty, "Design of System-on-a-Chip Test Access Architectures Using Integer Linear Programming," Proceedings IEEE VLSI Test Symposium (VTS), Montreal, Canada, pp. 127-134, 2000.

- [18] S. K. H. Ahammad, et al., "Fast and accurate feature extraction-based segmentation framework for spinal cord injury severity classification," *IEEE Access*, vol. 7, pp. 46092-46103, 2019.

- [19] K. Saikumar, et al., "A deep learning process for spine and heart segmentation using pixel-based convolutional networks," *Journal of International Pharmaceutical Research*, vol. 46, pp. 278-282, 2019.

- [20] V. Rajesh, et al., "A telemedicine technology for cardiovascular patients diagnosis feature using knn-mpm algorithm," *Journal of International Pharmaceutical Research*, vol. 46, pp. 72-77, 2019.

- [21] Sengupta, A., Dasgupta, S., Singh, V., Sharma, R., & Kumar Vishvakarma, S. (Eds.). (2019). VLSI Design and Test. Communications in Computer and Information Science. doi:10.1007/978-981-32-9767-8

- [22] Acharya, M., Pal, C., Maity, S., Chakrabarti, A., "Inexact implementation of wavelet transform and its performance evaluation through bit width reduction," In Chakrabarti, A., Sharma, N., Balas, V.E. (eds.) Advances in Computing Applications, pp. 227–242. *Springer*, Singapore (2016). https://doi.org/10.1007/978-981-10-2630-0\_14.

- [23] Venkataramani, S., Roy, K., Raghunathan, A., "Approximate computing," *Tutorial presentation at 29th International Conference on VLSI Design*, Kolkata, India, 4–8 January 2016 (2016).

- [24] Gupta, V., Mohapatra, D., Raghunathan, A., Roy, K., "Low-power digital signal processing using approximate adders," *IEEE Trans. Comput. Aided Des. Integr. Circuits Syst.* 32(1), 124–137 (2013).

- [25] Jiang, H., Han, J., Lombardi, F., "A comparative review and evaluation of approximate adders," In: *GLSVLSI 2015 Proceedings of the 25th Edition on Great Lakes Symposium on VLSI*, pp. 343–348 (2015).

- [26] Jiang, H., Liu, C., Maheshwari, N., Lombardi, F., Han, J., "A Comparative study of Approximate Adders and Multipliers. A Tutorial", University of Alberta, 2015.

- [27] Gogoi, A., Kumar, V., "Design of low power, area efficient and high speed approximate adders for inexact computing," In: 2016 International Conference of Signal Processing and Communication (ICSC), Noida, India, 26–28 December 2016. IEEE Xlopre (2016).