# Position and speed optimization of servo motor control through FPGA

#### Ahmed R. Ajel<sup>1</sup>, Huda M. Abdul Abbas<sup>2</sup>, Mohannad Jabbar Mnati<sup>3</sup>

<sup>1</sup>Control and Automation Engineering Electrical Engineering Technical College, Middle Technical University (MTU), Iraq <sup>2</sup>Department of Electrical Engineering, Collage of Engineering, University of Baghdad, Iraq <sup>3</sup>Department of Electronic Technology, Institute of Technology Baghdad, Middle Technical University (MTU), Iraq

#### **Article Info**

#### Article history:

Received May 30, 2020 Revised Jun 22, 2020 Accepted Aug 10, 2020

#### Keywords:

Altera DE1 board FPGA Optimization Position control Quartus II Servo motor Speed control

#### ABSTRACT

We have put our model in this paper in which we will be controlling the speed and direction of the servomotor through FPGA. So, as to guarantee the precision from the check control procedure, we have made a project in which the document provides the control plane associated with servo motor depending on Altera DE1 board gentle primary processor as program controller. The system utilizes FPGA since the primary gadget, as well as within Quartus II 10.0 program atmosphere. The associated control components aremade to type a good executable control program in which speed and direction will be controlled the servo motor performance. The particular handle signs from your handle method are usually separated and amplified which results in the push to appreciate the particular handle with the servo motor. Based on the features associated with Altera, it is expounded through 2 facets of equipment's hardware as well as a software program that supplies an answer for that style associated with the servo control system. This particular document utilizes the actual PID control formula to manage the actual common screening device to attain versatile as well as precise control reasons.

This is an open access article under the <u>CC BY-SA</u> license.

#### Corresponding Author:

Ahmed R. Rashid, Control and Automation Engineering, Electrical Engineering Technical College, Middle Technical University (MTU), Iraq. Email: dr\_ahmed.R@mtu.edu.iq

#### 1. INTRODUCTION

With all the advancement regarding large-scale built-in routine engineering, specifically, the particular introduction regarding components outline terminology, the effective use of FPGA gadget in the field of engineering will be getting increasingly widespread [1, 2]. Altera DE1 board chip is a soft-core processor produced by Altera, the producer associated with FPGA. It's a user-oriented, versatile as well as easy to customize inlayed processor chip. This combines information bus, numerous peripherals (for example timer, SRAM, flash) as well as interfaces (for example SPI ,UART, PWM, PIO, SDRAM user interface) to mix benefits of the microprocessor using an extremely effective parallel features associated with PLD. With this document, the DE1 gentle primary processor can be used since the program controller to understand the actual control plan associated with servo motors. The DE1 bord gentle primary CPU can be used to procedure the info associated with servo program. Thus, PID formula can be used to result from the ability to run the driver. The SPI bus communication component can be used to contact the actual web

host pc to accomplish the actual control speed and performance associated with the servo control system. The particular basic principle regarding the normal PID controller will be quick and easy to be able to apply, and it's also trusted inside the professional method handle [3-6].

Nevertheless, underneath the dependence on higher powerful features from the screening device, you will find difficulties associated with inadequate pace as well as balance. In contrast to the most popular PID control technique, the actual PID control has got the features associated with the easy algorithm as well as little computation quantity and may make sure the actual balance from the program is great. So, the program may monitor the actual enter quicker as well as enhance the powerful reaction capacity for the machine [7-12].

The original general test equipment typically makes use of ARM or perhaps singlechip microcomputer because of the model and its particular math running ability will be gradual, as well as the energetic packing handle ability will be not enough [13-26]. For this finish, we created the common screening device depending on FPGA. By utilizing FPGA to attain the PID control formula ideal for the actual check device and by sending data for clouding which will enhance the speed as well as control the direction of the servomotor. The actual control overall performance from the check device had been confirmed underneath the fresh system.

#### 2. SYSTEM STRUCTURE AND OPERATING THEORY

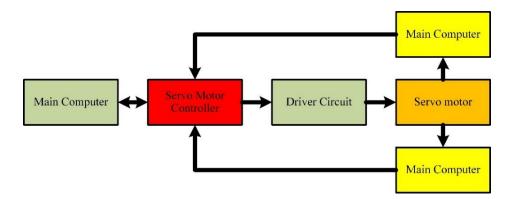

The actual servo program is definitely an essential control system. Its primary perform would be to manage force-displacement in order to monitor the actual directions precisely. The actual servo control program is principally made of top pc, driver, servo controller, AC motor as well as the position and the device of speed detection. The machine framework is actually proven in determine Figure 1. The positioning recognition gadget offers the placement of the servo controller. The positioning could be remedied with the actual mistake as well as strained through the servo controller. Mixing along with the positioning as well as speed directions from the web host pc, the actual speed directions in the following second tend to be distributed by a particular control algorithm, and the order indicators are supplied towards the servomotor.

Figure 1 present the full system block diagram, the actual servo controller may be the immediate emitter associated with movement control directions, and it is in the primary from the servo program. The positioning recognition from the program actually results by the coarsely fine dual-channel selsyn. The actual result actually launched to Selsyn-Digital Transducer (SDC) component associated with the servo controller to accomplish the actual transformation through analog transmission in order to electronic transmission. With the manage plan purchase as well as manage from the servo controller, the positioning indicators using the specs associated with  $-180^{\circ} \sim +180^{\circ}$  tend to be prepared.

Figure 1. System block diagram

#### 3. IMPLEMENTATION OF FEEDFORWARD PID ALGORITHM

The expression used for the decentralization of the PID controller is given in (1):

$$u(i) = K_P \left( e_i + \frac{T}{T_i} \sum_{K=0}^i e_k + T_d \; \frac{e_i - e_{i-1}}{T} \right) = K_P e_i + K_I \sum_{k=0}^i e_k + K_D (e_i - e_{i-1})$$

(1)

Int J Elec & Comp Eng, Vol. 11, No. 1, February 2021 : 319 - 327

Within the method KP is proportional amplification coefficient, Ki is essentially continuous, Kd is differential continuous, T is the sampling period. The actual living associated with essential phrase causes it to be not possible about regular PID control to ensure each rapidity as well as balance within techniques needing higher powerful overall performance [4-7]. The Feedforward control is a technique in charge program to create suitable control parameters to alter procedure parameters as well as maintain control parameters within these elections of arranged ideals by utilizing arranged ideals with exterior disruptions. Within the regular PID manage, utilizing pace as well as speed feedforward manage may slow the subsequent mistake as well as follow-up mistake from the program. This permits the actual program to monitor enter quicker and enhances the actual bodies' powerful responsiveness. Based on the invariant theory, feedforward control could make the entire program accomplish absolutely no stage mistake monitoring or even total monitoring without having a stability issue.

Within the method, Gc(s) is represent a transfer function and Gp(s) associated with an electro-hydraulic servo test-bed. H(s) is signifies the actual move perform from the suggestions channel and GF(S) signifies the actual move perform from the feedforward channel. Consider H(s) to get the transfer function in (2).

$$\frac{C(s)}{R(s)} = \frac{[G_C(s) + G_F(s)]G_P(s)}{1 + G_C(s)G_P(s)}$$

(2)

An error found in the transfer function given in (3):

$$1 - \frac{C(s)}{R(s)} = \frac{1 - G_F(s)G_P(s)}{1 + G_C(s)G_P(s)}$$

(3)

Once a transfer function from the feedforward channel pays an actual invariance situation (the actual control program is made of two components. The first is accustomed to combat the actual disturbance and the additional should be used for to understand the actual monitoring control), the actual control system can acquire in the next (4)

$$G_F(s) = \frac{1}{G_P(s)} \tag{4}$$

Once the program bys (4), the actual dynamic mistake coefficient from the program, decreases the transfer function move perform to zero. This particular implies that the actual result from the system may recreate the input. It may be observed through (5) how the intro from the feedforward channel does not impact the actual program attribute formula, which could enhance the program precision without having impacting the machine stability [5, 7]. Nevertheless, within the real scenario, since the real energy as well as a linear selection of the machine tends to be restricted, this cannot be unlimited, which means this scenario is extremely hard to attain.

Usually

$$GF(s) = (0.76 - 0.98) Gp(s) [10].$$

$$u(t) = K_P(e(t) + \frac{1}{T_i} \int_0^t e(t)dt + T_d \frac{de(t)}{dt}) + K_{\nu F} v_c + K_{aF} a_c$$

(5)

Kp, Ti, Td, u(t) e(t)has the same sense as PID control; Vc is the speed, ac is the acceleration value given; KVF is the feedforward gain; KaF is the feedforward gain for acceleration. Even though the procedure is straightforward, the actual primary, as well as trouble associated with PID control is based on the actual dedication associated with KP, Ki as well as Kd guidelines, that is the procedure associated with parameter tuning. These types of guidelines tend to be associated with the actual check regular from the screening device and the general character from the control system.

This particular document to melody the real experiential solution of trial-and-error guidelines. The technique would be progressively figure out the actual proportional coefficients, an actual essential parameter, and a differential continuous based on the features from the reaction contour inside a particular purchase. Within the real situation, the particular group of PID guidelines needed based on every various control setting [11-14]. Within the check procedure, it is essential to maintain a particular bodily amount inside a continuous condition. When the traditional feedforward PID control can be used, the actual servomotor is going to be often changed as well as reversed, producing heat, decreasing the life span as well

as leading to unneeded loss. Consequently, this particular document retreats into the feedforward PID manage formula along with lifeless area, that's, once the (6) is made, the actual feedforward PID will not are likely involved [18]. At this time, the machine utilizes the standard PID control.

$$|e(k) - e(k-1)| < \varepsilon \tag{6}$$

#### 4. METHOD STUCTORE AND FUNCTIONING OF OPERATING THEORY

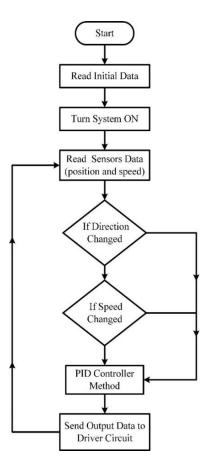

The flowchart in the Figure 2 present the full building associated with SOPC (system-on-aprogrammable-chip) equipment hardware, the person software program improvement package (SDK) is produced within the improvement atmosphere. SDK identifies the program look associated with personal hardware, such as storage mapping as well as the use of the information framework associated with hardware components within the program. Based on hardware building, software program style is made as well as software plan improvement is completed. The actual software program created below the Altera DE1 board atmosphere.

The primary features from the program software program tend to be following getting the actual control directions as well as guidelines from the main pc via SPI communication bus, phoning the related control plan, evaluating using the present suggestions worth from the control item, as well as finishing the actual high-precision control from the placement as well as speed from the program via the smart controlling algorithm. The actual control software program Consists mainly of primary timer disrupt processing plan. Included in this, the primary plan primarily finishes program initialization as well as main pc order reaction processing. The actual disrupts perform primarily scans the actual exterior information regularly, such as instruction for speed, instruction for the position, Feedforward speed, and so on. Centered on the instruction in the top pc instruction and the present condition from the program. This finishes the actual formula control for servo system and results in actual control directions towards driving circuit. Additionally, it finishes the actual features associated with delivering the present position as well as status towards the main pc.

Figure 2. Flowchart of main program

#### METHOD STRUCTURE AND FUNCTIONING BASIC PRINCIPLE 5.

## 5.1. Development passes with Quartus II

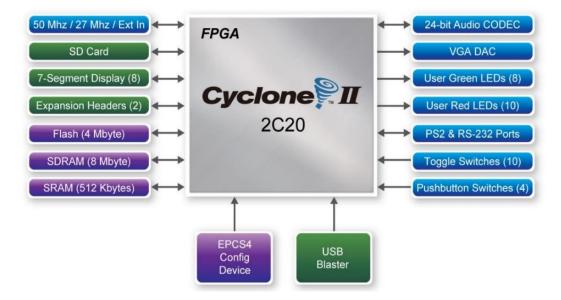

Based on the program hardware style, the task is made within the software program Quartus II. The hardware program depending on Quartus II soft-core processor is made through SOPC Contractor. The hardware program depending on the Cyclone II 2C20 processor is put together as well as settings documents tend to be produced within the Quartus II task. Then set up software package about hardware program within Quartus II IDE improvement atmosphere; put together executor to create executable document; burn off the actual delivery document to the FPGA to debug as well as operate the actual program.

#### 5.2. System interfacing design of module

The actual SDC component utilized in this technique is Cyclone II 2C20 chip to accomplish placement removal as well as electronic transformation. The pin description of the used chip in our project is described in the Figure 3 and Table 1. One of them, the particular handle pins have got electronic digital result locations with input and output and a great result in permitting slot plus a route assortment slot. The interfacing of a signal is thus shown in the lower table.

Figure 3. Pin diagram of the cyclone II 2C20 chip

| Table 1. The cyclone II 2C20 pin description |                      |  |  |  |

|----------------------------------------------|----------------------|--|--|--|

| Variable                                     | Description          |  |  |  |

| SDRAM                                        | 8MB                  |  |  |  |

| Flash                                        | 4MB                  |  |  |  |

| SPAM                                         | 512K                 |  |  |  |

| VGA Output                                   | RS-232; PS/2         |  |  |  |

| Audio Codec with Line-in                     | Line-out, and Mic-in |  |  |  |

| Two 40-pin GPIO Expansion Headers            |                      |  |  |  |

|                                              |                      |  |  |  |

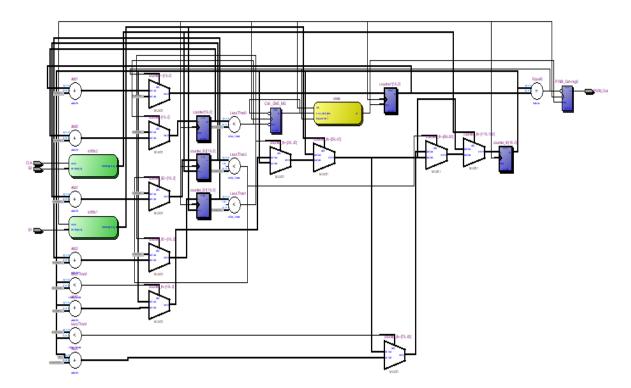

#### 5.3. Technique SOPC included design and style

On such a basis as the components layout, the SOPC integration layout will be performed. The particular SOPC built-in layout with the method will be called: creating Altera PC beneath SOPC Creator surroundings; incorporating 12 ms timer from your selection to perform the device timer disruption handle; incorporating on-chip memory space; merging the particular developed components, incorporating outside memory space SDRAM; incorporating of the self-customized of SDC software controller; incorporating the serial SPI connection controller that perform details swap together with sponsor personal computer; incorporating self-customized driver software controller; incorporating (I/O) software handle common sense, etc; producing a whole method. Ultimately, SOPC method data files are usually gathered also created inside SOPC Creator. Right after developing the device directly in the Quartus II10. Venture, pins usually are designated and gathered and also saved for the FPGA computer chip. The complete SOPC

324 🗖

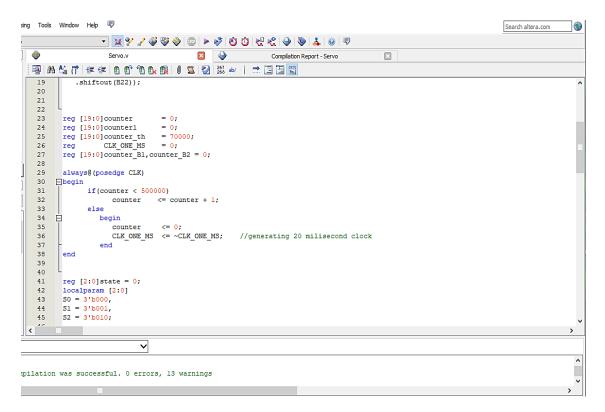

method will be produced. The RTL system diagram of feed-forward control is presented in the Figure 4 and the full VHDL code is presented in the Figure 5. Figure 6 shown the pin Signals Interfacing of SDC custom module seleted in the Quartus II softwear platform.

Figure 4. RTL system diagram of feed-forward control

Figure 5. Th quartus II code window of the main program

|                           | 🖌 👯 Edit: 💢 🛷 |          |          |            |                 |              |

|---------------------------|---------------|----------|----------|------------|-----------------|--------------|

| Node Name                 | Direction     | Location | I/O Bank | VREF Group | Fitter Location | I/O Standard |

| in_ B1                    | Input         | PIN_88   | 5        | B5_N0      | PIN_88          | 3.3-V LVCMOS |

| <u>ів_</u> В2             | Input         | PIN_89   | 5        | B5_N0      | PIN_89          | 3.3-V LVCMOS |

| in_ CLK                   | Input         | PIN_23   | 1        | B1_N0      | PIN_23          | 3.3-V LVCMOS |

| PWM_Out                   | Output        | PIN_141  | 8        | B8_N0      | PIN_141         | 3.3-V LVCMOS |

| < <new node="">&gt;</new> |               |          |          |            |                 |              |

Figure 6. Pins signals interfacing of SDC custom module

#### 6. HARDWEAR AND SYSTEM RESULTS

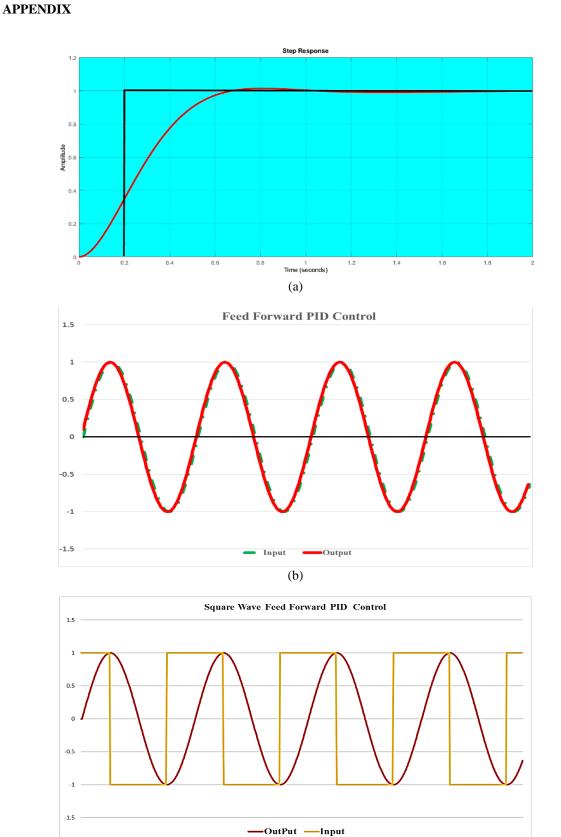

The actual equipment program cycle from the servo, control test-bed had been constructed, such as the total cycle from the control program because proven within Figure 2. Later on, several categories of position loading as well as force launching tests had been carried out. The Full system hardware is shown in the Figure 7. Figure 8 (see in Appendix) is ahown the test results for the full system hardware, Figure 8(a) present the stepe respons of PID controller and Figure 8(b) and (c), present the actual feedforward PID manage program offers significantly enhanced the actual powerful overall performance. The actual produced waves along with the actual launching rate of recurrence associated with the sine and square wave's inputs signals. The actual increase period from the program within the system, (a) is actually 0.05s, the actual overshoot is actually 10%, and the static mistake is actually 52N. Within (b), the actual program increase period is actually 0.04s; the actual overshoot is actually 32%, and the static mistake is actually 3.6N.

Figure 7. The full hardwear system platform

## 7. CONCLUSION

With this paper, a good inlayed servo control module for speed and direction depending on Altera DE1 board gentle primary CPU was created. It is referred to at length in the facets of software programs as well as hardware. The actual exceptional benefits of embedded system style depending on DE1 gentle primary processor tend to be quick, versatile hardware style, powerful expansibility, reduced hardware development period, as well as enhanced design dependability. The software program is quick. The processor or CPU is put in place through the gentle core. Its features could be personalized based on requirements. SOPC Contractor offers much more IP quests. This particular paper offers a few referrals for that style associated with the servo system and may be put on additional soft-core-based style strategies. In contrast to the standard control program, the system enhances the actual quick reaction capacity, control precision as well as constant condition precision from the control program. It completely Make the most of benefits of FPGA within information processing, optimizing the design, easy, secure and sound in consequence, the system is actually confirmed through the fresh system, and the actual acceptable control impact is actually acquired that enhances the actual balance, practicability as well as higher effectiveness from the control program from the common screening device. Nevertheless, you will find nevertheless a few hardware and algorithm optimization difficulties within the particular optimization style from the control program. So, it's nevertheless required to improve the actual control program.

(c)

Figure 8. Test results of the full hardwear system; a) PID response control signals, b) input and output signals with sine wave input signal and c) input and output signals with square wave input signal

#### REFERENCES

- X. S. Li, et al., "Analysis and Simplification of Three-Dimensional Space Vector PWM for Three-Phase Four-Leg Inverters," *IEEE Transactions on Industrial Electronics*, vol. 58, no. 2, pp. 450-464, 2011.

- M. J. Mnati, "Position Control for flexible Joint Maipulator using Artificaial Neutral Network," Department Of Electrical & Electriconics Engineering, University of Technology, 2005.

- [3] R. Arulmozhiyal and K. Baskaran, "Implementation of a Fuzzy PI Controller for Speed Control of Induction Motors Using FPGA," *Journal of Power Electronics*, vol. 10, no. 1, pp. 65-71, 2010.

- [4] M. J. Mnati, D. V. Bozalakov, and A. Van den Bossche, "PID Control of a Three Phase Photovoltaic Inverter Tied to a Grid Based on a 120-Degree Bus Clamp PWM," *IFAC-PapersOnLine*, vol. 51, no. 4, pp. 388-393, 2018.

- [5] D. Zhang, et al., "Common Mode Circulating Current Control of Interleaved Three-Phase Two-Level Voltage-Source Converters with Discontinuous Space-Vector Modulation," *IEEE Energy Conversion Congress and Exposition*, vol. 1-6, pp. 3906-3912, 2009.

- [6] H. Sun, M. J. Mnati, M. Nabil Ibrahim, and A. Van Den Bossche, "A Tuning Method for the Derivative Filter in PID Controller with Delay Time," Proc. 2018 9th Int. Conf. Mech. Aerosp. Eng. ICMAE 2018, pp. 574-578, 2018.

- [7] Z. Yinhai, et al., "A Novel SVPWM Modulation Scheme," *Twenty-Fourth Annual IEEE Applied Power Electronics Conference and Exposition*, pp. 128-131, 2009.

- [8] H. Sun, M. N. Ibrahim, M. Jabbar Mnati, and A. Van Den Bossche, "A Tuning Method for PI Controller for an Integrating System with Time Delay," *Proc. 2018 9th Int. Conf. Mech. Aerosp. Eng.*, pp. 410-414, 2018.

- [9] Sun, K., et al., "Summary of Embedded CPU Soft-core [J]," Computer Engineering, vol. 7, 2006.

- [10] Yuwen X., "Verilog digital system design course," Beijing University of Aeronautics and Astronautics Press, 2008.

- [11] Qing-qing Peng, et al., "Design of Image Compression of SPIHT Algorithm Card Based on NiosIIFire," Control and Command Control, vol. 42, pp. 174-177, 2017.

- [12] Abido, A. A., "Particle swarm optimization for multimachine power systemstabilizer design," IEEE Power Engineering Society Summer Meeting, 2001.

- [13] Boerlage, Matthijs, R. Tousain, and M. Steinbuch., "Jerk derivative feedforward control for motion systems," *American Control Conference IEEE*, 2005.

- [14] S. Palanidoss and S. V. T., "Experimental Verification of Three phase quasi Switched Boost Inverter with an Improved PWM Control," *International Journal of Power Electronics and Drive Systems (IJPEDS)*, vol. 10, no. 3, pp. 1500-1509, 2019.

- [15] F. A. Silaban, S. Budiyanto, and W. K. Raharja, "Stepper motor movement design based on FPGA," *International Journal of Electrical and Computer Engineering (IJECE)*, vol. 10, no. 1, pp. 151-159, 2020.

- [16] T. Dewi, et al., "Inverse kinematic analysis of 4 DOF pick and place arm robot manipulator using fuzzy logic controller," *International Journal of Electrical and Computer Engineering (IJECE)*, vol. 10, no. 2, pp. 1376-1386, 2020.

- [17] Hou Bojie, Li Xiaoqing, Zhou Yunfei and Teng Wei, "The Development of Feedforward Plus PID Controller for Linear Motor," *Machine Tool and Hydraulics*, vol. 37, no. 2, pp. 56-58, 2009.

- [18] Wang Wei, Zhang Jingtao, CHAI Tianyou, "A Survey of Advanced PID Parameter Tuning Methods," *Acta Automatica Sinica*, vol. 26, no. 3, pp. 347-355, 2000.

- [19] Hu Baogang, "A Study on Nonlinear PID Controllers Proportional Component Approach," Acta Automatica Sinica, vol. 32, no. 2, pp. 219-227, 2006.

- [20] A. Glumineau, M. Hamy, C. Lanier, and C. H. Moog, "Robust control of a brushless servo motor via sliding mode techniques," *Int. J. Control*, vol. 58, no. 5, pp. 979-990, 1993.

- [21] N. H. Jalani, "NCTF-FL controller for pendulum balancing system," *Bulletin of Electrical Engineering and Informatics (BEEI)*, vol. 4, no. 4, pp. 355-362, 2015.

- [22] A. R. Kardian, S. A. Sudiro, and S. Madenda, "Efficient implementation of mean, variance and skewness statistic formula for image processing using FPGA device," *Bulletin of Electrical Engineering and Informatics (BEEI)*, vol. 7, no. 3, pp. 386-392, 2018.

- [23] A. Rani and N. Grover, "An enhanced FPGA based asynchronous microprocessor design using VIVADO and ISIM," *Bulletin of Electrical Engineering and Informatics (BEEI)*, vol. 7, no. 2, pp. 199-208, 2018.

- [24] S. Sokolov, et al, "Hybrid neural networks in cyber physical system interface control systems," Bulletin of Electrical Engineering and Informatics (BEEI), vol. 9, no. 3, pp. 1268-1275, 2020.

- [25] G. C. Cardarilli et al., "Efficient FPGA implementation of high speed digital delay for wideband beamforming using parallel architectures," *Bulletin of Electrical Engineering and Informatics*, vol. 8, no. 2, pp. 422–427, 2019.

- [26] M. A. Bin Ilyas et al., "Comparison study of 8-PPM, 8-DPIM, AND 8-RDH-PIM modulator FPGA hardware design in term of bandwidth efficiency and transmission rate," *Bulletin of Electrical Engineering and Informatics* (*BEEI*), vol. 9, no. 2, pp. 707-715, 2020.