International Journal of Electrical and Computer Engineering (IJECE) Vol. 9, No. 2, April 2019, pp. 753~760 ISSN: 2088-8708, DOI: 10.11591/ijece.v9i2.pp753-760

753

# **Performance analysis of PV powered multilevel inverter**

K. Dhineshkumar<sup>1</sup>, C. Subramani<sup>2</sup>, A. Geetha<sup>3</sup>, C. Vimala<sup>4</sup>

<sup>1</sup>Departement of Electrical and Electroincis Engineering, Agni College of Technology, Chennai, India <sup>2,3</sup>Departement of Electrical and Electroincis Engineering, SRM Institute of Science and Technology, Kancheepuram, India

<sup>4</sup>Departement of Telecommunication Engineering, SRM Institute of Science and Technology, Kancheepuram, India

| Article Info ABSTRACT |

|-----------------------|

|-----------------------|

#### Article history:

Received Dec 27, 2017 Revised Oct 8, 2018 Accepted Dec 5, 2019

#### Keywords:

Boost chopper Multilevel inverters Sinusoidal PWM Solar PV system This article deals with the PV based DC/DC boost chopper integrated nine level inverter. This topology requires 7 switches in minimum to obtain a nine level stepped wave output. So the main objective of this paper is to develop a 9 level AC output using PV based DC/DC boost chopper. In the case of conventional multi-level inverter, 16 switches were utilized and the number of sources needed was also more. Here the proposed system comprises of single PV panel and the switches used are also less. Also PV is integrated with DC/DC boost chopper is used to increase the source input level of the inverter. Using MATLAB platform, the proposed system is simulated with a resistive and inductive load. The similar results are obtained in prototype which validates the designed converter.

Copyright © 2019 Institute of Advanced Engineering and Science. All rights reserved.

#### **Corresponding Author:**

C. Subramani,

Departement of Electrical and Electronics Engineering, SRM Institute of Science and Technology, Kancheepuram, India. Email: csmsrm@gmail.com

#### 1. INTRODUCTION

The Multi-level inverters (MLIs) were highly used in many recent applications because of its nature of high voltage handling capacity. It can able to deliver multi-level output with least composition on exchanging appliances. In contrast to the conventional single level inverter, the multilevel inverter becomes the score seeding to multi switching. MLI has the capability of producing typical output voltage levels by interchanging the inverter groups. In the case of MLI, as the level of voltage increases, the output delivered by the converter will also have moderately diminished output waveform. In general, H type connected MLIs have been utilized in many applications as discussed in [1]. The purpose and special implementation of the MLIs are examined by the re-enactment after-effects of a existing stage nine leveled symmetric as well as seventeen level asymmetric MLI and testing out comes of a nine-altitude and seventeen stages MLI. Eventually the suggested topology evokes reduction of establishment region and expenses and has efforts of control strategy is discussed in [2]. This design may be developed to have lesser number of electronic devices such as switches, power devices thyristor families, DC energy sources, driver circuit etc. Also it can be utilized to yield a better quantity of energy stages [3].Suggested SOP technique licensed MLI can perform like conventional inverter with moderate change in recurrence constrained to assessed key recurrence without trading off on consonant twisting were elaborated in [4].Reference [5] elaborates the total harmonic distortions (THD) of a stepped level output of a single state MLI. A 15 – Level MLI was investigated by [6]. It describes how the voltage control of the output occurs and its operation. An high frequency source based MLI is designed in [7]. The design and its operation of HFAC and PDS were well explained by the authors. Each module is composed of H bridge and semi extended bridge and two different DC equivalent source [8], [9]. The 3 stage 7 – Level H bridge MLI is developed and presented in [10].

#### 2. SINUSOIDAL PUSE WIDH MODULATION

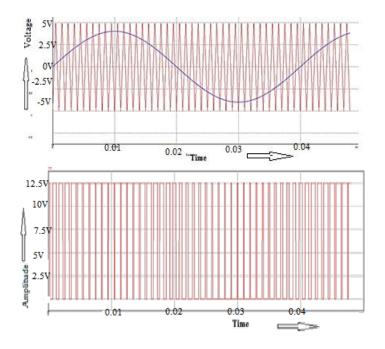

Figure 1 depicts the sinusoidal pulse width modulation (Sinusoidal – PWM) output taking amplitude along Y axis and time period along X axis. It has two signals namely carrier signal and reference signal. Those two signals were compared to obtain the PWM output waveform. Sinusoidal waveform is considered as reference signal and triangular wave is considered as carrier signal. The obtained sinusoidal – PWM is utilized for the triggering of power switches in 9 level MLI. Since sinusoidal – PWM is used in this work, the resonance of inverter found to be reduced when compared with the conventional PWM. The width of the pulse is tweaked to a specific value in order to get the controlled output voltage with less reverberation.

Figure 1. Sinusoidal – PWM output

Sinusoidal – PWM seems to be the most commonly utilized technique for the inverter fed speed control of a motor. The operating frequency of the carrier signal as well as reference signal is used as discussed in [11]. Also this kind of PWM pulses are progressively used in AC drives with more perspective towards the diminishing symphonious current and to obtain the best output voltage to drive the motor [12]. Analyzed all the PWM techniques acting in the history and its fundamentals principles.

#### 3. PV SYSTEM

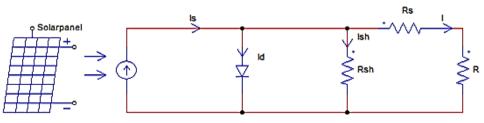

A DC supply obtained a PV panel is used as the input for the proposed MLI. For example, a 10W PV panel that has 17.6V and 0.56A is used as an input for MLI. PV cell is the basic unit of a PV panel. Combination of number of PV cells forms a PV module. Combination of number of PV modules forms a PV panel. Figure 2 represents the equivalent circuit of a PV module.

The energy arises from the earth's sun is termed as earth's radiation. It is of float type or diffused type. The diffused type radiation can deflect part of radiation back to the surface which consumes mists.

PV oriented cell arrangement towards sun can gather the energy released from the sun during day. This arrangement comprises of a diode connected in parallel and an inverter. This can be termed as a current source connected to a parallel diode and parallel resistance. The PV current obtained from the sun's radiation is given in Equation (1).

$$I_d = I_s[exp \ exp \ \frac{qv}{kt} - 1] - I_{\rm ph} \tag{1}$$

Whereas,  $I_d$  represents diode current,  $I_s$  is the dispersion current, t is temperature, q is the charge (1.6 ×10–19 C) and k is the Boltzmann consant (1.3805×10–23J/K),

(2)

The PV circuit comprises of two distinguished resistances  $R_s$  and  $R_p$  respectively in proportions. Here  $R_s$  denotes the setbacks due to the relations and contacts and  $R_p$  denotes in the diode for the case of its spillage streams as identified and termed to in [13].

In recent trends PV's source are greatly utilized in enormous applications such as charging a battery, house power supplies, pumping of dehydrogenated monoxide, satellite power systems etc. Since PV is noted to be a progressively high since it has inexhaustible energy. It has many advantages like contamination free, commotion free and toll free. The major drawback of PV system is it is more dependent on climatic condition changes. Hence offers energy that depends on the light as well temperature.

Figure 2. Equivalent circuit of a PV module

# 4. VARIOUS MLI SCHEMES

#### 4.1. Existing system

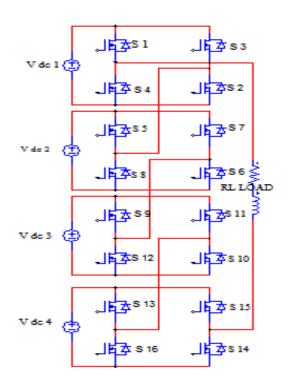

The full MLI, 4 - H Bridges were interconnected back to back in series with an individual source as shown in Figure 3. A cascaded MLI utilize 16 power switches to offer 13-level output voltage. The pulses for switching the power switches in inverter are sinusoidal PWM triggering technique. While comparing the number of inputs of an inverter with its MLI output, the output seems to be more than the input. The levels of output voltages appeared to be 4V-3V-2V-V-0-(-V)-(-2V)-(-3V)-(4V).Symmetrical cascade is an individual cascade of full bridge with 4 power switches. So it required more number of voltage sources and power switches. Hence the capital cost of the system also increases. It may also lead to high THD and switching misfortunes as explained in [14].

Number of level =

$$2^n - 3$$

Figure 3. Single phase cascaded full bridge Inverter

#### 4.2. Proposed system

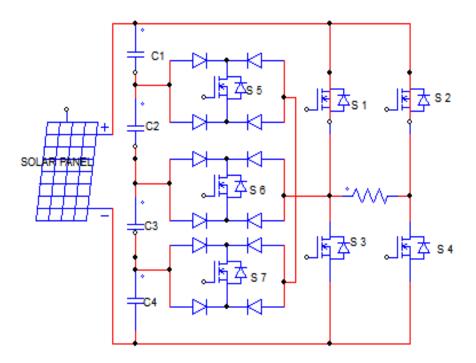

The earth's sun based 9 - Level inverter is discussed in this article. It is generated from a 9 - Level inverter. It consists of a basic H bridge connected MLI along a 3 bidirectional power switches and 4 numbered capacitor as voltage cutter as shown in Figure 4. This typical new topology is utilized in this work. It uses earth's sun rather than like a conventional DC voltage. There are different types of loads such as R, RL etc can be connected to the proposed topology. There exists nine different operations which are sequentially performed by the sinusoidal pulse width modulated signals offered to the power switches. All these operations were performed in MATLAB platform for different types of loads assumed. The hardware model of the proposed MLI utilizes PIC microcontroller. Embedded C language program has been fed to the microcontroller. This program can generate the pulses required to power switches. Table 1 elaborates the switching sequences states of the proposed MLI.

Number of level =

$$2^n - 1$$

(3)

The overall voltage is obtained as the output by operating the power switches 1 and 4. Then 0.75 DC voltage is obtained across the output when the power switch 1 and 5 are operated. Similarly 0.5 DC voltage is gained in output when power switches 4 and 6 are on. Nil output voltages is found to be present across the output when switch 2 or 1 and 3 and 4 are working. For the rest of the periods the switches were said to be in off states. Whenever the power switches 1 and 5 are turned on -0.25 DC voltage is gained across the load. Similarly -0.5 DC output voltage is obtained when power switches 2 and 7 are on. -0.75 negative voltage across load is found when switches 2 and 8 are operated. The rated output voltage is obtained for the switches 2 and 3 working conditions. This repeats for every cycle.

Figure 4. Solar based 9 - level inverter

| Table 1. Switching Sequence of the Proposed MLI |            |    |    |    |    |    |            |  |

|-------------------------------------------------|------------|----|----|----|----|----|------------|--|

| Vo                                              | <b>S</b> 1 | S2 | S3 | S4 | S5 | S6 | <b>S</b> 7 |  |

| Vdc                                             | 1          | 0  | 0  | 1  | 0  | 0  | 0          |  |

| 3Vdc/4                                          | 0          | 0  | 0  | 1  | 1  | 0  | 0          |  |

| Vdc/2                                           | 0          | 0  | 0  | 1  | 0  | 1  | 0          |  |

| Vdc/4                                           | 0          | 0  | 0  | 1  | 0  | 0  | 1          |  |

| 0                                               | 0          | 0  | 0  | 0  | 0  | 0  | 0          |  |

| -Vdc/4                                          | 0          | 1  | 0  | 0  | 1  | 0  | 0          |  |

| -Vdc/2                                          | 0          | 1  | 0  | 0  | 0  | 1  | 0          |  |

| -3Vdc/4                                         | 0          | 1  | 0  | 0  | 0  | 0  | 1          |  |

| -Vdc                                            | 0          | 1  | 1  | 0  | 0  | 0  | 0          |  |

## 5. **RESULTS AND DISCUSSIONS**

## 5.1. Simulation of 9-level MLI with R- load

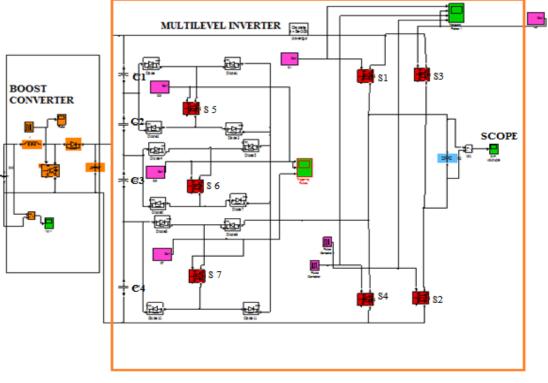

The Figure 5 describes the solar PV based DC - DC boost converter integrated with 9 – Level MLI in simulation platform. The load connected to the above system is R load. The scope reads the output voltage obtained. The Output voltage of the MLI greater than input voltage. The inverter iuses seven switches to produce 9 level Output Voltage waveform. The 9 level inverter simulated using Matlab. This inverter consist of H bridge and along with three source switches.

Figure 5. Simulation of solar PV based 9 - level MLI with R load

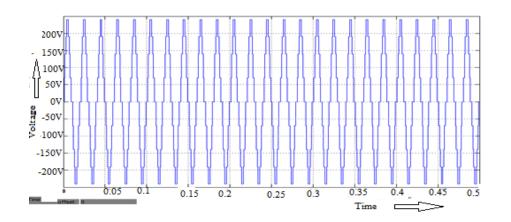

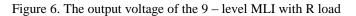

## 5.2. Outputvoltage for 9 – level MLI with R load

The Output voltage of the 9 – Level MLI with R load stack is given in Figure 6. Output voltage is taken along y axis and time period is taken along x axis. Figure 7 represents the total harmonic distortions (THD) of the proposed 9 – Level MLI with R load.

Performance analysis of pv powered multilevel inverter (K.Dhineshkumar)

Figure 7. THD of the 9 - level MLI with R load

## 5.3. Block diagram of of nine level proposed inverter with RL load

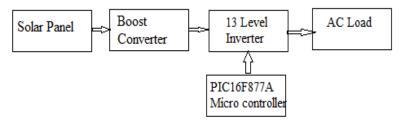

This Proposed solar based Nine level Hybrid type multilevel inverter using AC Load is appeared in the Figure 8.

Figure 8. Block diagram of 9 level multilevel inverter

## 5.4. Simulation f output voltage waveform for nine level cascaded inverter

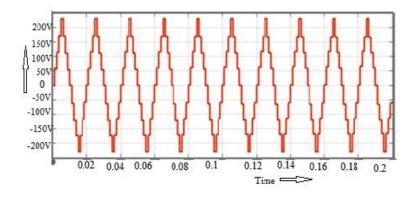

The Figure 9 shows the output voltage of the Nine level inverter. The 9 level output voltages are 55V,110V,165V,220V,0,-220V,-165V,-110V,-55V are obtained.

Figure 9. The output voltage of the nine levels inverter for RL load

## 6. EXPERIMENTAL RESULT

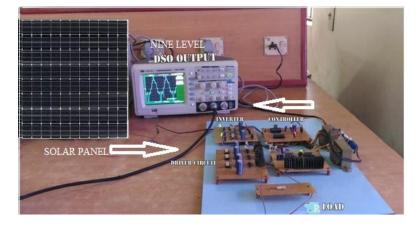

The Figure 10 shows the hardware experimental setup for 9 - Level MLI with Resistive load and digital CRO is used to display the measured output voltage of the proposed inverter. The hardware setup is made with the reduced scale to make it as a prototype model.

Figure 10. Solar b PV based 9 - Level MLI with R load

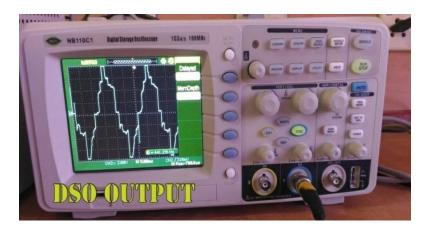

The 9 – Level MLI's voltage obtained across the resistive load that obtained in digital CRO is showcased in the above Figure 11.

Figure 11. Output voltage for a solar PV based 9 - Level inverter with R load

# 7. CONCLUSION

In this article, the earth's sun powered driven based DC/DCboostchopper synchronized with a 9 - Level MLI is performed in both software as well as hardware. The results obtained in both the cases confirmed the promising output of the proposed system for various loads. The proposed system utilized sinusoidal PWM pulses for switching the power switches. The conventional MLI uses 16 power switches to offer 9 - Levels of the output voltage with more number of DC sources. Whereas in the proposed MLI requires 7 power switches with a single solar PV sources DC voltage. The proposed MLI represented and differentiated for various loads such as R, RL using MATLAB. The prototype model doubt fully confirmed the proposed system.

## REFERENCES

- Prakash G and Subramani C, "Space Vector and Sinusoidal Pulse Width Modulation of Quasi Z-Source Inverter for Photovoltaic System,"*International Journal of Power Electronics and Drive Systems*, vol. 7, no. 3, pp. 601-609, 2016.

- [2] Alex Van den Bossche, *et al.*, "Developed Cascaded Multilevel Inverter Topology to Minimize the Number of Circuit Devices and Voltage Stresses of Switches," IET Power Electron, vol.7, no. 2, pp. 459-466, 2014.

- [3] EbrahimBabaei, et al., "Cascaded Multilevel Inverter with Series Connection of Novel H-Bridge Basic Units," *IEEE Transactions on Industrial Electronics*, vol. 61, no. 12, pp. 6664-6671, 2014.

- [4] AmarendraEdpuganti and Akshay K. Rathore, "Optimal Low Switching Frequency Pulse width Modulation of Nine-Level Cascade Inverter,"*IEEE Transactions on Power Electronics*, vol. 30, no. 1, pp. 482-495, 2015.

- [5] Bill Diong, et al., "Harmonic Distortion Optimization of Cascaded H-Bridge Inverters Considering Device Voltage Drops and Non integer DC Voltage Ratios,"*IEEE Transactions on Industrial Electronics*, vol. 6, no. 8, pp. 3106-3114, 2013.

- [6] P.D.H.Darmawardana, et al., Nine Level Cascaded H Bridge Inverter 2015; MERCon; pp- 7-8.

- [7] Prakash, G, *et al.*, "A low Cost Single Phase Grid Connected Reduced Switch PV Inverter based on Time Frame Switching Scheme,"*International Journal of Electrical Power and Energy Systems*, Elsevier, vol. 77, no. 1, pp. 100-111, 2016.

- [8] Charles IkechukwuOdehEmeka S. Obe andOlorunfemiOjo, "Topology for Cascaded Multilevel Inverter,"*IET Power* Electron, vol. 5, no. 4, pp. 1-9, 2016.

- [9] G. Sandoval, *et al.*, "Passivity-based Control of an Asymmetric Nine-level Inverter for Harmonic Current Mitigation," *IET Power Electron*, vol. 5, no. 2, pp. 237-247, 2012.

- [10] SasanHashemizadehAshan and Mohammad Monfared, "Design and Comparison of Nine-Level Single-phase Inverter with a Pair of Coupled Inductors and Two DC Sources,"*IET Power Electronics*, vol. 9, no. 11, pp. 2271-2281, 2016.

- [11] JayaprakashSabarad and G.H. Kulkarni "Comparative Analysis of SVPWM and SPWM Techniques for Multilevel Inverter," *Power and Advanced Control Engineering (ICPACE), 2015 International Conference on IEEE Xplore*, vol. 27, no. 29, pp. 232-237, 2016.

- [12] Shijie Yan, et al., "A simplified SVPWM Control Strategy for PV Inverter,"24th Chinese Control and Decision Conference, pp. 225-229, 2012.

- [13] Usha S and Subramani C, "Performance Analysis of H-bridge and T-Bridge Multilevel Inverters for Harmonics Reduction,"*International Journal of Power Electronics and Drive Systems*, vol. 9, no. 1, pp. 231-239, 2018.

- [14] K.Dhineshkumar and C.Subramani, "Kalman Filter Algorithm for Mitigation of Power System,"*International Journal of Electrical and Computer Engineering*, vol. 8, no. 2, pp. 771-779, 2018.