# **International Journal of Electrical and Computer Engineering (IJECE)**

Vol. 6, No. 5, October 2016, pp. 1985~1993

ISSN: 2088-8708, DOI: 10.11591/ijece.v6i5.10492

# A Modulation Scheme for Floating Source Multilevel Inverter Topology with Increased Number of Output Levels

## Hussain M. Bassi

Department of Electrical Engineering at Rabigh, King Abdulaziz University, Jeddah, Saudi Arabia

### **Article Info**

## Article history:

Received Mar 14, 2016 Revised Jun 11, 2016 Accepted Jul 3, 2016

### Keyword:

Mulitlevel Inverter SPWM Pulse Width Modulation Total Harmonics Distortion Power Converters

### **ABSTRACT**

This paper presented and studied a new switching scheme for floating source multilevel inverters to produce more levels with the same number of switching devices. In the proposed scheme, the function of the dc sources, except the inner one, is to build up square wave or blocks that is close in the shape to the desired sinusoidal wave. The job of the inner switching devices is to increase the number of the levels to produce smother sinusoidal wave in the inverter output. This job can be done by adding or subtracting the value of the inner dc source to/from the blocks. The topology used in this paper is based on the conventional floating source multi-level inverter using two legs. This topology and modulation technique show substantial reduction in the total harmonics distortion when the modulation technique is the hybrid method. The performance of the proposed switching scheme in generating more levels has been evaluated by PSCAD/EMTDC simulation.

Copyright © 2016 Institute of Advanced Engineering and Science.

All rights reserved.

## Corresponding Author:

Hussain Bassi, Department of Electrical Engineering, King Abdulaziz University, Faculty of Engineering at Rabigh. Email: hmbassi@kau.edu.sa

# 1. INTRODUCTION

Multilevel inverters have attracted the attention of several researchers for different advantages such as its low output total harmonic distortion (THD), low switching device stress, and reduced switching stress [1]. Besides, it be used to improve systems power quality using modern FACTS application [2],[3]. In the industry, switching devices are used in Electric and hybrid Electrics vehicles but limitation of these devices is one of the issues that need to be solved [4]. The voltage across each switching devices in DC-DC converters can be reduced by connecting series capacitor in the input. This voltage is equal to total input voltage divided by the number of the capacitors. For instance, if there are five series capacitors, the voltage across each switching device is one-fifth the input voltage. This method is explained in [5] and [6] using three capacitors. Multilevel inverters applied the same concept of distributing the input voltage evenly among the switching devices by connecting a set of series capacitors in the input. The resulted output voltage of this configuration has lower harmonics and less voltage stress across the switching devices. Multilevel inverters are divided into three main types: neutral-point clamped or diode-clamped (NPC) [7], [8], flying capacitor (FC) [9], [10] and cascaded H-bridge inverters [11]-[13]. These multilevel inverters are controlled by several techniques, as in [14], where the most common technique is multicarrier sinusoidal pulse width modulation (SPWM) [15] and [16]. As the number of levels in the multilevel inverter output increases, the wave is near sinusoidal shape with less harmonics. However, the increase in the number of the levels is associated with several issues such as significant DC-link voltage balancing difficulties and additional clamping diodes as in the NPC and FC [17] and [18]. There are several topologies that produce decent number of levels in the output, however, they use H-bridge to generate the negative polarity [4], [19] with very high rating power switches. While the 1986 □ ISSN: 2088-8708

others used bidirectional switches instead of H-bridge as in [20] where it is preferable to use unidirectional switches instead of bidirectional ones due to its higher cost.

In this paper, a proposed switching scheme is evaluated and analyzed to control the floating source (FS-MLI) in [21] using two legs. This technique has the advantage of not utilizing H-bridge to produce negative levels. Besides, it uses unidirectional switches to with lower rates. The switching control method is can use hybrid modulation concept to further reduce harmonics distortion. This technique has a remarkable disadvantage that it lacks for modularity and is more suitable for medium- and low-voltage applications. The simulation results of 11-level inverter using PSCAD/EMTDC software are presented for the purpose of validity.

## 2. FLOATING SOURCE TOPOLOGY

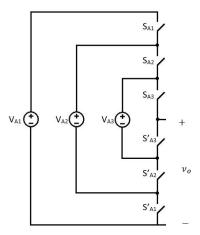

The floating source multilevel inverters (FS-MLI) configuration with one leg is shown in Figure 1. It is similar to the flying-capacitor (FC) inverter except that the capacitors are replaced with separate dc voltage sources. As it is shown in the figure, it consists of three separate dc sources and three pairs of switching devices ( $S_{A1}$ ,  $S'_{A1}$ ), ( $S_{A2}$ ,  $S'_{A2}$ ), and ( $S_{A3}$ ,  $S'_{A3}$ ). These switching devices are unidirectional and each one of them consists of IGBT and an anti-parallel diode. The switches ( $S_{A3}$ ,  $S'_{A3}$ ) must not turn on simultaneously or they will short-circuit the source  $V_{A3}$ . When the voltage ratio of the dc sources  $V_{A1}$ :  $V_{A2}$ :  $V_{A3}$  is 3 : 2 : 1, the output voltage of the inverter for each phase,  $v_o$ , is four levels. The general form of the FS-MLI should have the following expressions:

$$N_{switches} = 2N_{cells} \tag{1}$$

$$N_{levels} = N_{cells} + 1 (2)$$

Figure 1. Three-cells floating source multilevel inverters (FS-MLI)

# 3. PROPOSED SWITCHING SCHEME

In this paper, the proposed switching technique is analyzed on 11-level MLI and then on n-level MLIs.

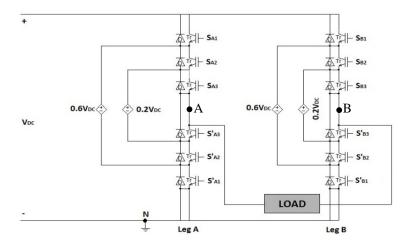

## 3.1. 11-level FS-MLI Configuration

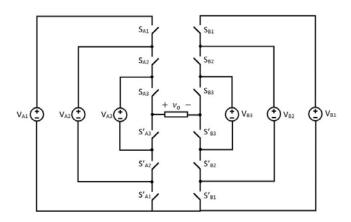

In the proposed switching scheme, the negative part must be generated using the structure of the FS-MLI with no H-bridge. Therefore, the proposed switching scheme is designed to work on two legs of the FS-MLI instead of one. 11-level FS-MLI with two legs is shown in Figure 2. The leg on the left side is noted as leg A and the leg on the right side is noted as leg B. Each leg consists of three dc sources and six switching devices. The inner dc sources  $V_{A3}$  and  $V_{B3}$  may get short-circuited accidently when  $(S_{A3}, S'_{A3})$  and  $(S_{B3}, S'_{B3})$ , respectively, turn on simultaneously. The voltage ratio of the dc sources  $V_{A1}: V_{A2}: V_{A3}$  and  $V_{B1}: V_{B2}: V_{B3}$  must be 5:3:1. This ratio is a mandate to generate more levels at the output line voltage. Table 1 presents the switching states to produce 11-level line voltages at the output of the inverter. This switching scheme has the advantage that all the voltages of the dc sources build up core blocks similar to the sinusoidal

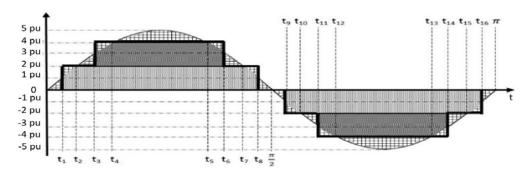

wave, Figure 3, except the inner dc sources,  $V_{A3}$  and  $V_{B3}$  where they are used to produce new levels at the mid of each block. In other words, the first block has the period between  $t_1 < T < t_8$  with the magnitude of 2 pu, while the second block has the period between  $t_3 < T < t_6$  is 2 pu as well. The sum of these two blocks is 4 pu to form a steps wave that mimics the desired sinusoidal wave.  $V_{A3}$  and  $V_{B3}$  are used to produce the levels 1 pu, 3 pu, and 5 pu by adding and deducting 1 pu (the magnitude of  $V_{A3}$  and  $V_{B3}$ ) to and from the two blocks.

Figure 2. 11-level floating source multilevel inverters (FS-MLI) with two legs

| Table 1 | Recommended         | Switch | Combina | tion for w |

|---------|---------------------|--------|---------|------------|

| Table L | <b>R</b> ecommended | 5 WHCH | Combina | HOH FOR Va |

|       |                                | Switch States |          |          |          |          |          |

|-------|--------------------------------|---------------|----------|----------|----------|----------|----------|

| State | Output $v_o$                   | LEG-A         |          | LEG-B    |          |          |          |

|       |                                | $S_{A1}$      | $S_{A2}$ | $S_{A3}$ | $S_{B1}$ | $S_{B2}$ | $S_{B3}$ |

| 1     | $V_{A1}$                       | 1             | 1        | 1        | 0        | 0        | 0        |

| 2     | $V_{A1}$ - $V_{A3}$            | 1             | 1        | 0        | 0        | 0        | 0        |

| 3     | $V_{A1}$ - $V_{A3}$ - $V_{B3}$ | 1             | 1        | 0        | 0        | 0        | 1        |

| 4     | $V_{A2}$                       | 0             | 1        | 1        | 0        | 0        | 0        |

| 5     | $V_{A2}$ - $V_{A3}$            | 0             | 1        | 0        | 0        | 0        | 0        |

| 6     | $V_{A2}$ - $V_{A3}$ - $V_{B3}$ | 0             | 1        | 0        | 0        | 0        | 1        |

| 7     | $V_{A3}$                       | 0             | 0        | 1        | 0        | 0        | 0        |

| 8     | 0                              | 0             | 0        | 0        | 0        | 0        | 0        |

| 9     | $-V_{B3}$                      | 0             | 0        | 1        | 0        | 1        | 0        |

| 10    | $-(V_{B2} - V_{B3} - V_{A3})$  | 0             | 0        | 0        | 0        | 0        | 1        |

| 11    | $-(V_{B2} - V_{B3})$           | 0             | 0        | 0        | 0        | 1        | 0        |

| 12    | $-V_{\mathrm{B2}}$             | 0             | 0        | 1        | 1        | 1        | 0        |

| 13    | $-(V_{B1} - V_{B3} - V_{A3})$  | 0             | 0        | 0        | 0        | 1        | 1        |

| 14    | $-(V_{B1} - V_{B3})$           | 0             | 0        | 0        | 1        | 1        | 0        |

| 15    | $-V_{B1}$                      | 0             | 0        | 0        | 1        | 1        | 1        |

# 3.2. n-level FS-MLI Configuration

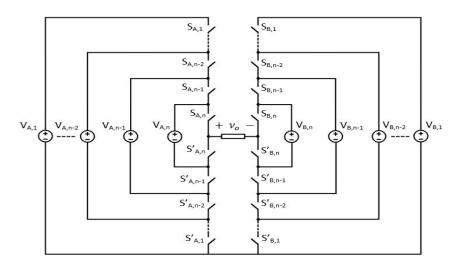

By analyzing the 11-level FS-MLI, a general structure can be developed. Figure 4 shows the n-cell FS-MLI. The number of levels ( $N_{levels}$ ), number of switching devices ( $N_{switches}$ ), number of dc sources ( $N_{sources}$ ), and total size of dc sources in pu ( $T_{sources}$ ) are calculated as follows:

$$N_{levels} = 2N_{cells} - 1 \tag{3}$$

$$N_{switches} = 2N_{cells} \tag{4}$$

$$N_{sources} = N_{cells}$$

(5)

$$T_{sources} = 2\sum_{i=1}^{N_{cells}} (2i - 1)$$

(6)

Figure 3. Desired sinusoidal wave with two blocks in each half-cycle

Figure 4. n-level floating source multilevel inverters (FS-MLI) with two legs

## 3.3. Hybrid modulation scheme

The switching frequency of the FS-MLI is equal to the frequency of the line, e.g., 60 Hz or 50 Hz. The inner switches  $(S_{A,n}$ ,  $S'_{A,n})$  and  $(S_{B,n}$ ,  $S'_{B,n})$  has the lowest stress, dv/dt. Therefore, these switches may turn at high frequency to reduce the THD without being subjected to high switching stress. When the switches operate at different frequency, the modulation scheme is denoted as hybrid modulation. The modulation of the inner switches is achieved by obtaining the waveform of the area shaded with large grid pattern Figure 3:

$$v_{ref} = V_1 \sin(2\pi f t) - 0.4[u(t - t_1) - u(t - t_8) - u(t - t_9) + u(t - t_{16})] - 0.4[u(t - t_3) - u(t - t_6) - u(t - t_{11}) + u(t - t_{14})$$

(7)

Where u(t) is a unit step function. One can obtain the general expression of the  $v_{ref}$  by first finding the number of blockes per half-cycle using the following equation:

$$N_{blocks} = N_{cells} - 1 \tag{8}$$

Then the peak of each block can be obtained as follows:

$$V_{block} = \frac{1}{N_{blocks} + 0.5} \tag{9}$$

By knowing the peak of the blocks it would be possible to find the intervals of each block. But first we need to find the number of starts and ends of the blocks per half-cycle, e.g.,  $t_1$ ,  $t_3$ . This step is achieved by using this formula

$$T_{blocks} = 4N_{blocks} \tag{10}$$

Finally, the general expression of

$$v_{ref}$$

is calculated as follows:

$$v_{ref} = V_1 \sin(2\pi f t) - V_{block} \left[ \sum_{i=1,3,5,\dots}^{\frac{T_{blocks}}{2}-1} u(t-t_i) - u(t-t_{i+T_{blocks}}) + \sum_{j=2,4,6,\dots}^{\frac{T_{blocks}}{2}-2} u(t-t_{T_{blocks}-j}) - u(t-t2Tblocks-j+) \right]$$

(11)

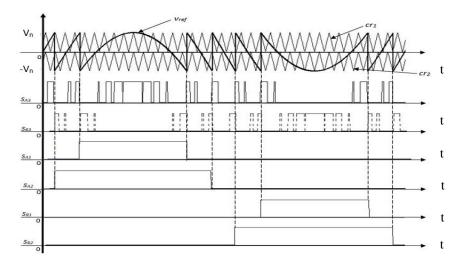

In Figure 4, the reference wave  $v_{ref}$  is presented along with the gate signals. The reference wave  $v_{ref}$  is modulated using two triangular carriers,  $cr_1$  and  $cr_2$ . The positive side of  $v_{ref}$  is compared with the carrier wave  $cr_1$  to drive the switch  $S_{A3}$ . And the carrier wave  $cr_2$  is compared with  $v_{ref}$  in the negative side to control the switch  $S_{B3}$ . The modulation index, m, that has range from 0 to 1 is defined as

$$m = \frac{v_{\text{ref}}}{\operatorname{cr}_{1,2(\text{peak})}} \tag{12}$$

The total harmonics distortion is one of the major performance evaluation factors and it can be calculated using Fourier series. First, we need to obtain the amplitude of the nth-harmonics of the FS-MLI output:

$$b_n = \frac{4V_{dc}}{n\pi} \left[ 1 + \sum_{i=1}^{N_{levels}-2} \cos(n\alpha_i) \right] for \ n \ odd \tag{13}$$

Where  $\alpha_i$  is the angle corresponds to  $t_i$  and obtaind by multiplying the time by  $360\pi$ . The calculation of  $b_1$  when m = 0.9, 0.6, and 0.3 are listed in Table 2. According to the data shown in this table, when the modulation index m decreases, the number of the switching angles decreases as well.

Figure 5. Outer reference wave and two carriers with gate signals

Finally the THD can be calculated using the following expression:

$$THD = \frac{\sqrt{(\sum_{n=3,5,7,\dots}^{\infty} b_n)}}{b_n} \tag{14}$$

Table 2. The value of Inverter Output with Corresponding Switching Angles (without Hybrid Modulation)

| m          | b <sub>1</sub> (rms) in pu* | $\alpha_1$ | $\alpha_2$ | $\alpha_3$ | $\alpha_4$ |

|------------|-----------------------------|------------|------------|------------|------------|

| 0.9        | 0.73                        | 12.84 °    | 26.39°     | 41.81°     | 62.73°     |

| 0.6        | 0.48                        | 19.47°     | 41.81°     | -          | -          |

| 0.3        | 0.31                        | 41.81°     | -          | -          | -          |

| *Base Valu | ie is 1                     |            |            |            |            |

1990 □ ISSN: 2088-8708

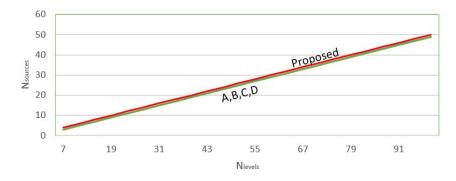

### 4. COMPARATIVE ANALYSIS

The proposed switching method has advantages and disadvantages. To provide these advantages and disadvantages it is of greate importance to compare it with some other topologies and modulation techniques mentioned in the literature. In [4], the DC sources has the freature of switching in series and in parallel. It contains an H-bride to produce negative levels as well as the positive level. In this paper, this topology is indicated as "A" in the comparison. "B" notation is for the topology described in [19] that has several DC sources connected in series. In this topology, the DC sources have to be symmetric, i.e.,  $V_{DC1} = V_{DC2} = V_{DC3}$  $= V_{DC4} = ... = V_{DCn}$ . The classical structure that the proposed switching scheme is based on is described in [21]. This topology is indicated as "C" in the comparison. The switches in the mentioned topologies are unidirectional while in [20] the switches are bidirectional. In this topology, each cell consists of one DC source and two bidirectional switch to generate two levels (one positive and the other is negative) and is indicated as "D" in the comparison. NPC-MLI, FC-MLI and CHB topologies are the conventional multilevel inverters that have been discussed in several articles, [7]-[12] and will be denoted as "E", "F" and "G", respectively, in the comparison. The comparison of the topologies based on the number of DC sources is shown in Figure 6. The number of the proposed technique is greater than the other topologies by one source only. Unlike the other topologies, the proposed technique does not rely on H-bridge to generate positive and negative levels. This a crucial disadvantage in the other topologies where the power switches in the H-bridge have to withstand high dv/dt stress.

Figure 6. Comparison of N<sub>sources</sub> versus N<sub>levels</sub>

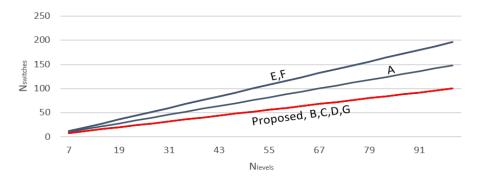

Figure 7 shows the comparison based on the number of switching devices. It is obvious that the proposed technique has the lowest number of switches and rating. As mentioned before at "A", "B", "D" require high rating power switches to avoid any damages may are caused by high stress dv/dt. Also, "C" uses bidirectional switches which in most of the cases more expensive than the unidirectional switches. Therefore, it would be clear that the proposed technique outperformed the other topologies and modulation techniques.

Figure 7. Comparison of  $N_{\text{switches}}$  versus  $N_{\text{levels}}$

## 4. SIMULATION RESULTS

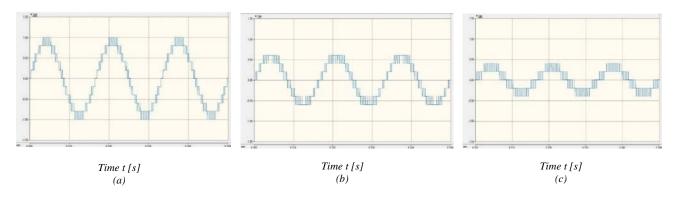

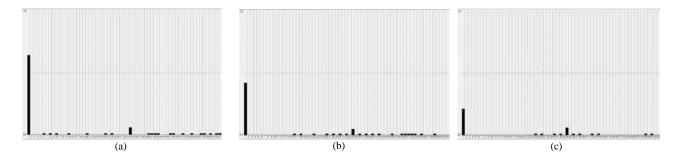

The studied circuit is simulated using PSCAD/EMDCT, Figure 8. The value of  $V_{dc}$  is set to be 1000 V, the modulation index  $m=0.9,\ 0.6,\$ and 0.3 respectively. The load is resistive and the modulation frequency is 2040 Hz. The output waveforms of the 11-level inverter with  $m=0.9,\ 0.6,\$ and 0.3 are shown in Figure 9. The spectrum of the inverter output using the proposed scheme is shown in Figure 10. The values of  $b_1$  in the simulation are 0.64 pu, 0.42 pu, and 0.21 pu. These values are close to the calculated values in Table 2. The difference in the resulted values is caused by applying the optional hybrid modulation in the simulation where it can be noticed that the calculated values are larger. Therefore the amplitude of the inverter output in the simulation is confirmed with the theoretical value. The highest magnitude of harmonics is present in the  $34^{th}$  harmonics. This happened because the switching frequency is 34 times 60 Hz. The THD of the investigated, NPC, and FC inverters are listed in Table 3.

Figure 8. Simulation of the investigated 11-level inverter

Figure 9. Simulation output of the proposed switching technique. (a) m = 0.9. (b) m = 0.6 (c) m = 0.3

Figure 10. Inverter output spectrum when (a) m = 0.9. (b) m = 0.6. (c) m = 0.3

1992 □ ISSN: 2088-8708

When m=0.9, the THD of the studied multilevel inverter is substantially smaller than the other conventional inverters. That is obvious because the inverter output has more levels than that when m=0.6 and m=0.3. This is expected because at that moment the number of the levels is low just like the conventional inverter. This circuit has disadvantages; it requires four DC sources as a total, two DC sources for each leg.

Table 3. Comparison of the Values of THD

| M   | -        | THD % |      |

|-----|----------|-------|------|

| IVI | Proposed | NPC   | FC   |

| 0.9 | 10.9     | 19    | 13.9 |

| 0.6 | 14.7     | 21    | 19.8 |

| 0.3 | 33.5     | 35    | 35.5 |

### 5. CONCLUSION

In this paper, a studied modulation scheme that produces more levels in inverters output has been presented. The proposed technique is based on a conventional MLI circuit that uses separate dc voltage sources. The modulation technique may operate using the hybrid method. The mechanism of the switching technique is that all switching devices in the inverter circuit turn on once per cycle while the inner switching devices double up the number of levels and may operate at high frequency. This technique is compared with other recent MLI. The number of dc sources is greater than the other techniques by one while the number of switches is lowest. Besides, the proposed technique has an advantage that it uses low unidirectional switch ratings. This technique has a drawback that it is based on asymmetrical separate dc sources which would be more practical for low- and medium-voltage applications.

## **ACKNOWLEDGEMENTS**

This paper was funded by the Deanship of Scientific Research (DSR), King Abdulaziz University, Jeddah, under grant No (565 - 829 - 1434). The author, therefore, acknowledge with thank DSR technical and financial support.

# REFERENCES

- [1] Z. Jing, et al., "Novel PWM Control Method for Hybrid-Clamped Multilevel Inverters," *IEEE Transactions on Industrial Electronics*, vol/issue: 75(7), pp. 2365-2373, 2010.

- [2] S. Chandrasekhar, et al., "Mitigation of Voltage Flicker and Reduction in THD by using STATCOM," International Journal of Electrical and Computer Engineering (IJECE), vol/issue: 3(1), pp. 102-108, 2013.

- [3] G. F. Reed, *et al.*, "Analysis of high capacity power electronic technologies for integration of green energy management," em *IEEE PES T&D 2010*, New Orleans, LA, USA, 2010.

- [4] Y. Hinago and H. Koizumi, "A Single-Phase Multilevel Inverter Using Switched Series/Parallel DC Voltage Sources," *IEEE Transactions on Industrial Electronics*, vol/issue: 57(8), pp. 2643-2650, 2010.

- [5] T. T. Song, et al., "Modeling and Analysis of a High-Voltage DC-DC Converter with Vin/3-Voltage Stress on the Primary's Switches," em APEC 07 Twenty-Second Annual IEEE Applied Power Electronics Conference and Exposition, Anaheim, CA, USA, 2007.

- [6] T. T. Song, et al., "A High-Voltage ZVZCS DC--DC Converter With Low Voltage Stress," *IEEE Transactions on Power Electronics*, vol/issue: 23(6), pp. 2630-2647, 2008.

- [7] G. P. Adam, et al., "Capacitor Balance Issues of the Diode-Clamped Multilevel Inverter Operated in a Quasi Two-State Mode," *IEEE Transactions on Industrial Electronics*, vol/issue: 55(8), pp. 3088-3099, 2008.

- [8] S. Daher, et al., "Multilevel Inverter Topologies for Stand-Alone PV Systems," Transactions on Industrial Electronics, vol/issue: 55(7), pp. 2703-2712, 2008.

- [9] L. G. Franquelo, *et al.*, "The age of multilevel converters arrives," *IEEE Industrial Electronics Magazine*, vol/issue: 2(2), pp. 28-39, 2008.

- [10] J. Huang and K. A. Corzine, "Extended operation of flying capacitor multilevel inverters," *IEEE Transactions on Power Electronics*, vol/issue: 21(1), pp. 140-147, 2006.

- [11] C. Rech and J. R. Pinheiro, "Hybrid Multilevel Converters: Unified Analysis and Design Considerations," *IEEE Transactions on Industrial Electronics*, vol/issue: 54(2), pp. 1092-1104, 2007.

- [12] R. Gupta, et al., "Switching Characterization of Cascaded Multilevel-Inverter-Controlled Systems," IEEE Transactions on Industrial Electronics, vol/issue: 55(3), pp. 1047-1058, 2008.

- [13] S. Dasam and B.V.Sankerram, "Voltage Balancing Control Strategy in Converter System for Three-Level Inverters," *International Journal of Electrical and Computer Engineering (IJECE)*, vol/issue: 3(1), pp. 7-14, 2013.

- [14] H. M. Bassi, "Optimized carrier-based pulse width modulation technique with double switching frequencies for three-phase inverters," em *Power Engineering Conference (UPEC)*, 2015 50th International Universities, Stoke on Trent, 2015.

- [15] A. Valderrabano-Gonzalez, et al., "Implementation of a 84-pulse voltage-source converter for special applications," *IET Power Electronics*, vol/issue: 5(7), pp. 984-990, 2012.

- [16] R. Rabinovici, et al., "Thirteen-level cascaded H-bridge inverter operated by generic phase shifted," *IET Power Electronics*, vol/issue: 6(8), pp. 1516 1529, 2013.

- [17] X. Yuan and I. Barbi, "Fundamentals of a new diode clamping multilevel inverter," *IEEE Transactions on Power Electronics*, vol/issue: 15(4), pp. 711 718, 2000.

- [18] B. P. McGrath and D. G. Holmes, "Analytical Determination of the Capacitor Voltage Balancing Dynamics for Three-Phase Flying Capacitor Converters," *IEEE Transactions on Industry Applications*, vol/issue: 45(4), pp. 1425-1433, 2009.

- [19] W. K. Choi and F. S. Kang, "H-bridge based multilevel inverter using PWM switching function," em *INTELEC* 2009 31st International Telecommunications Energy Conference, Incheon, 2009.

- [20] E. Babaei, "A Cascade Multilevel Converter Topology With Reduced Number of Switches," *IEEE Transactions on Power Electronics*, vol/issue: 23(6), pp. 2657 2664, 2008.

- [21] Y. Ounejjar, et al., "Packed U Cells Multilevel Converter Topology: Theoretical Study and Experimental Validation," *IEEE Transactions on Industrial Electronics*, vol/issue: 58(4), pp. 1294 1306, 2011.

### **BIOGRAPHIES OF AUTHORS**

Dr.Bassi received Bc.S degree in Electrical and Computer Engineering from King Abdulaziz University in 2003 and M.S Degree in Electrical Engieering from Florida Institute of Technolgy in 2008 PhD in Electrical Engieering from University of Pittsburgh in 2013. He is currenty an assistant professor at King Abdulaziz University to teach major courses in the department of electrical engineering ranges from the low-level courses to more advanced ones such as power system transients. He contributes effectively to his discipline by adding innovative ideas and compete to add upon the state-of-the-art in power electronics technologies and renewable energy.

Dr. Bassi woked as a site superintendent to monitor day-to-day construction activities at the working sites, even under high-pressure conditions, while maintaining the required loss prevention regulations. He was continuously updating his technical and managerial knowledge to handle the projects professionally. He worked for project management team (PMT) department at SAUDI ARAMCO to complete projects in instrumentation and power engineering areas until 2005

E-mail: hmbassi@kau.edu.sa