International Journal of Electrical and Computer Engineering (IJECE) Vol. 3, No. 2, April 2013, pp. 197~206 ISSN: 2088-8708

**D** 197

## Design of Real Time Walsh Transform for Processing of Multiple Digital Signals

Zulfikar\*, Shuja A. Abbasi\*\*, A. R. M. Alamoud\*\*

\* Departement of Electrical Engineering, Syiah Kuala University \*\* Departement of Electrical Engineering, King Saud University

### Article Info ABSTRACT

#### Article history:

Received Dec 22, 2012 Revised Feb 27, 2013 Accepted Mar 6, 2013

#### Keyword:

Fast Hadamard transform Walsh transform Real time Walsh transform Inverse Walsh transform Dyadic convolution This paper presents the design and implementation of multiple digital signals processing using real-time Walsh transforms. The design of real time Walsh transform is done in such a way that it starts producing outputs instantly even before all input data have entered the system. The system consists of Walsh Transform circuit, several Digital Signal Processing (DSP) circuits, and an inverse Walsh transform circuit. The real time Walsh and inverse Walsh transforms are also designed to produce right results for any possible combinations of input data. DSP blocksare able to perform addition, subtraction, and dyadic convolution process of Walsh coefficients of more than one digital signals. Comparisons to the previous methods are briefly presented. It was found that the design of real time Walsh transform structure has better performance than many of the previously reported results in the literature.

Copyright © 2013 Institute of Advanced Engineering and Science. All rights reserved.

#### **Corresponding Author:**

Zulfikar, Departement of Electrical Engineering, Syiah Kuala University, Darussalam, Banda Aceh 23111, Indonesia, phone: +62 651 7554336 Email: zulfikarsafrina@yahoo.co.id

#### 1. INTRODUCTION

The area ofDigital Signal Processing (DSP) is currently a well established area of research. The techniques for analysis, synthesis and processing of two or more digital signals have been established. However, some of them required certain tasks of DSP which are difficult to be performed in time domain and hence the information has to be transformed to other domains.

Frequency domain is the most popularly used domain for the tasks which cannot be, or are difficult to be done in the time domain. Fourier transform is the most widely used technique for transforming information from time domain to frequency domain. This is a very useful tool in DSP. In the group of 2m transform length, the Fourier transform is better described as the Walsh transform.

The Walsh transform (WT) may be obtained using the Walsh functions. It is also well known that the Walsh functions may be evaluated using Rademacher functions [1]-[3]. We preferred this technique since the Rademacher functions may be conveniently realized using a binary counter [4], [5]. However, it should be noted that it is not always necessary to use the above technique and the Walsh transform (WT) may be performed just by using adders and subtractors [6]. This idea interested many scientists and engineers for hardware realization of the Walsh transform. This method is known as Fast Hadamard Transform (FHT) since it is derived from Hadamard matrices [7]-[10].

Distributed Arithmetic (DA) and Systolic Architecture (SA) are two types of structures that have been proposed in order to further simplify the FHT [7]-[10]. Amira et al [11] proposed an improved structure and claimed better performance on the basis of an elaborate comparative study. They also reported the results of power analysis. Later on, Meher and Patra [12] introduced a very simple technique based on combination of unified algorithm [6] and Rademacher functions. This technique is based upon the use of simple 4 points FHTs arranged in such a way that the higher points FHTs (8, 16, 32) may be obtained easily. The technique was also implemented on FPGAs. Superior results were claimed.

It is found that the original Walsh functions, defined in terms of products of Rademacher functions can be used to transform the information into frequency domain faster than FHT and thus leads to speed up the DSP process. Therefore, the original Walsh transform technique based on Walsh functions and Rademacher functions is proposed and the results of hardware realization on FPGAs are presented. Moreover, a good design of Walsh transform is able to produce output immediately. Further, we also designed and implemented the Inverse Walsh Transform (IWT) for conversion from frequency domain to time domain.

FPGA based hardware realization has been used to process two digital signals using the Walsh transform and the Inverse Walsh transform techniques. The results of hardware realization like the occupied area and delays have been compared with the results reported by other workers.

The paper is organized as follows. In section 2, the basic theory of Walsh transform and signal processing is presented. Section 3 deals with the proposed structure of real time Walsh transform and inverse Walsh transform. Section 4 deals with control signals of the design system. The hardware implementation on FPGAs is presented in section 5. Section 6 deals with analysis and discussions of the proposed Walsh and inverse Walsh transforms. Conclusions are presented in Section 7.

#### 2. WALSH TRANSFORM AND SIGNAL PROCESSING

Definition of Walsh functions based upon derivation from Rademacher functions is found to be more appropriate for hardware implementation. The Rademacher functions are defined as follows [1]-[3]:

$$\phi(n+1,x) = Sgn(\sin 2\pi 2^n x), n = 0, 1, 2, \dots 0 \le x < 1$$

(1)

Where,  $\phi(0, x) = 1$  and the signum function Sgn(y) is defined by:

$$\operatorname{Sgn}(y) = \begin{cases} +1, & y \ge 0 \\ -1, & y < 0 \end{cases}$$

(2)

Walsh functions are defined in terms of product of Rademacher functions as follows [1]-[3]:

$$\psi(n,t) = \prod_{i=0}^{N} \left[ \phi(i+1,t) \right]^{n_i}, \qquad n_i \in \{0,1\}$$

(3)

$$n = \sum_{i=0}^{N} 2^{i} n_{i} \tag{4}$$

A digital signal x(t) of length N may be represented as a Walsh series which is given by [1]-[3]:

$$x(t) = \sum_{n=0}^{N-1} A_n \psi(n, t)$$

(5)

The Walsh coefficients An are evaluated as [1]-[3]:

$$A_{n} = \frac{1}{N} \sum_{n=0}^{N-1} x_{n} \psi(n, t)$$

(6)

If the signals h(t), p(t) and q(t) are defined as the summation, subtraction and multiplication of two signals given by:

$$h(t) = x(t) + g(t) \tag{7}$$

$$p(t) = x(t) - g(t) \tag{8}$$

IJECE Vol. 3, No. 2, April 2013: 197-206

ISSN: 2088-8708

199

Where the function x(t) has the Walsh series expansion as in (5) and g(t) has the following Walsh series expansion:

$$g(t) = \sum_{n=0}^{N-1} B_n \psi(n, t)$$

(10)

Then the Walsh expansion of h(t), p(t) and q(t) are given by [1]:

IJECE

$$h(t) = \sum_{n=0}^{N-1} C_n \psi(n, t)$$

(11)

$$p(t) = \sum_{n=0}^{N-1} D_n \psi(n, t)$$

<sup>(12)</sup>

$$q(t) = \sum_{n=0}^{N-1} E_n \psi(n, t)$$

(13)

Where the expansion coefficients of  $C_n$ ,  $D_n$  and  $E_n$  are computed as [1], [13], [14]:

$$C_n = A_n + B_n \tag{14}$$

$$D_n = A_n - B_n \tag{15}$$

$$E_n = \sum_{m=0}^{\infty} A_{n \oplus m} B_m \tag{16}$$

Where  $\oplus$  refers to dyadic addition (XOR) and the last expression is the well known dyadic convolution.

# 3. DESIGN OF COMPLETE SET OF REAL TIME WALSH AND INVERSE WALSH TRANSFORMS

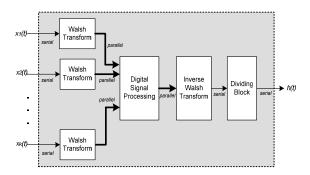

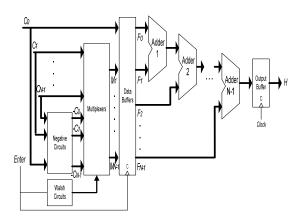

Figure 1 shows complete set of circuits which perform signal processing of multiple digital signals. The design consists of Walsh transform blocks, a DSP block, one Inverse Walsh Transform block and a dividing block. Input digital signals  $x_1(t)$ ,  $x_2(t)$ ...etc are passed into the system serially. Similarly, the output signal h(t) is also produced in series.

Figure 1. Walsh and Inverse Walsh for signal processing

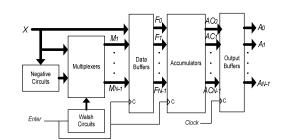

Number of Walsh transform blocks used depends on number of input signals. Figure 2 views basic design of the Walsh transform. The design consists of a negative circuit, a circuit to produce (N-1) orders of Walsh functions, a block of N-1 number of 2 to 1 multiplexers, N data buffers, N accumulators, and N output buffers.

Figure 2. Design of Walsh transform for transform length of N

Input data (samples) of X are passed serially. Walsh circuit is used to select the suitable data X or - X and pass it through the multiplexers. The outputs of the multiplexers will accumulate at the accumulators and they will form the output transformed coefficients (A's).

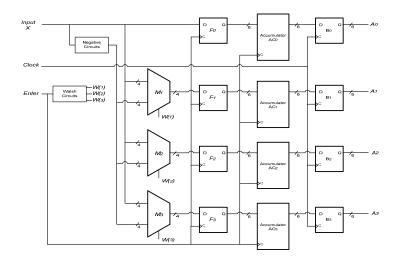

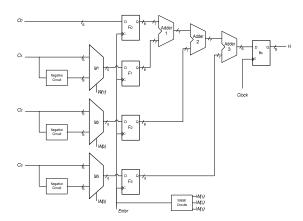

Figure 3 views circuit realization of the proposed Walsh transform for N=4 and input word lengths WI=4 (used to represent input data X). The output transformed coefficients (A's) have to be represented in 6 bits (output word lengths WO=6) [13].

Figure 3. Circuit realization of WT for N=4 and WI=4

The proposed WT is able to start producing output results instantly even before all input data have been given to the system. For example, if input data of N=4 are X{-6, -2, 3, 7}, WT (Walsh coefficients) of these data can be calculated as follows,

$$A_0 = (-6) + (-2) + 3 + 7 = 2$$

$$A_1 = (-6) - (-2) + 3 - 7 = -8$$

$$A_2 = (-6) + (-2) - 3 - 7 = -18$$

$$A_3 = (-6) - (-2) - 3 + 7 = 0$$

When input data X have not completely entered into the system, say only -6 and -2 have just passed, the output Walsh coefficients are:

$$A_0 = (-6) + (-2) + 0 + 0 = -8$$

$$A_1 = (-6) - (-2) + 0 - 0 = -4$$

$$A_2 = (-6) + (-2) - 0 - 0 = -8$$

$$A_3 = (-6) - (-2) - 0 + 0 = -4$$

Those coefficients are true by assuming the rest of input data are all zero. For transform lengths N, the coefficients will be produced N times. Therefore, we call the design of Walsh transform as real-time Walsh transform.

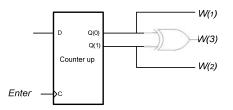

The Walsh circuit realization for N=4 is shown in Figure 4. It is designed to produce complement of 2nd, 3rd and 4th orders of Walsh functions based on Hadamard ordering. For higher transform lengths, obviously it will require more XOR gates in order to perform multiplications of Rademacher functions.

Figure 4. Walsh Circuit realization for N=4

The inverse Walsh transform may be obtained using most of the blocks designed for Walsh transform. The complete block diagram is shown in Figure 5. The circuit requires a set of N negative circuits to receive N parallel inputs, (N-1) number of 2 to 1 multiplexers, N data buffers, (N-1) adders, and an output buffer.

Figure 6 views circuit realization of the proposed Inverse Walsh transform for N=4 and input word lengths WI=6 (used to represent input coefficient C's). The output data (H) are represented in 4 bits (output word lengths WO=4). This (WO<WI) is due to dividing by factor of N=4.

Figure 5. Design of inverse Walsh transform for transform length of N

Figure 6. Circuit realization of IWT for N=4 and WI=6

The process flow of inverse Walsh transform is similar to Walsh transform, all input data either C or -C are selected to pass the multiplexers based on outputs of Walsh circuits. These data will then be added one by one using the adders sequentially.

In determining coefficients A's and B's, and to avoid floating numbers, factor 1/N in Eq. 6 is ignored for the time being. This factor will be implemented towards the end of the process in dividing block. The circuits to perform this job are installed together with the Inverse Walsh transform circuit. For addition and subtraction, the outputs of inverse Walsh transform have to be divided by N. Meanwhile, for multiplication process, the outputs should be divided by factor of N<sup>2</sup> [13].

#### 4. CIRCUIT CONTROL SIGNALS

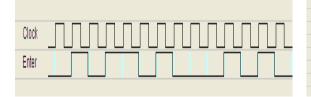

The operation of the proposed WT and IWT has to be controlled carefully in order to gather optimum results. There are three basic control signals as follows:

1. Clock; it is used to synchronize buffers and other storage elements.

(17)

- 2. Reset; it is used to reset (clear) all buffers and storage elements. Before input data are fed to the circuit, signal Reset normally goes high.

- 3. Enter; it is used to control input data. How fast the data enters the system, is based upon this signal. This signal has to be high for at least twice of clock period.

$$T_{Enter} \geq 2 T_{Clock}$$

Therefore, this signal is non periodic. Figure 7 shows relation between signal Enter and Clock.

Figure 7. Relation between Clock and signal Enter

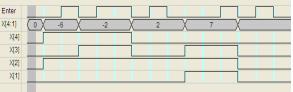

Figure 8. Relation between signal Enter and input data (X)

The availability of this signal is based on the availability of input data. The signal arrives just after the input data (X) available at input port of the circuits. Figure 8 shows relation between signal Enter and input data.

#### 5. IMPLEMENTATION RESULTS

In order to show step by step process of the design on chip, the implementation will be performed and displayed for every step (Walsh transform, DSP, Inverse Walsh transform) and limited to two input signals only. Three types of signal processing steps viz. addition, subtraction and multiplication will be demonstrated for transform length N=4 and word lengths of input signals WI=4 based on natural or Hadamard ordering. The implementations are targeted to Virtex chips from Xilinx.

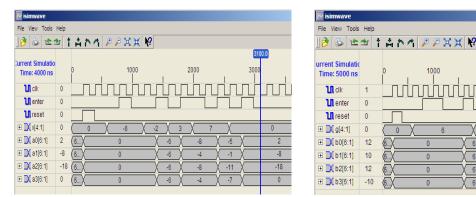

Figure 9 and 10 show Walsh transforms of input signals x(t) and g(t). The transformed coefficients A and B are represented in word lengths WO=6 bits.

Figure 9. Walsh transform of signal x(t)

3000

17

Output coefficients A and B are produced in real-time by the system. Here, the coefficients are produced four times. The first coefficients are available just after two cycles of signal Enter. The second and the third series of coefficients are available after three and four cycles of signal Enter respectively. The last coefficients will be available after signal Enter goes high five times.

Since the Walsh coefficients for A's and B's are available, we may now perform addition, subtraction and multiplication of signal x(t) and g(t). As mentioned earlier in section II, the addition and subtraction can be performed by simply adding and subtracting both coefficients A's and B's as follow [13]:

Addition process:

$$\begin{split} C_0 &= A_0 + B_0 = 2 + 12 = \textbf{14} \\ C_1 &= A_1 + B_1 = \textbf{-8} + 10 = \textbf{2} \\ C_2 &= A_2 + B_2 = \textbf{-18} + 12 = \textbf{-6} \\ C_3 &= A_3 + B_3 = 0 + (\textbf{-10}) = \textbf{-10} \end{split}$$

Subtraction process:

$$\begin{split} D_0 &= A_0 - B_0 = 2 - 12 = \textbf{-10} \\ D_1 &= A_1 - B_1 = \textbf{-8} - 10 = \textbf{-18} \\ D_2 &= A_2 - B_2 = \textbf{-18} - 12 = \textbf{-30} \\ D_3 &= A_3 - B_3 = 0 - (\textbf{-10}) = \textbf{10} \end{split}$$

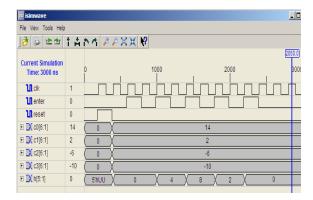

The coefficients C's and D's are then transformed back into the time domain by using IWT proposed in Figure 6. The results are shown in Figs. 11 and 12 for addition and subtraction of signal x(t) and g(t) respectively.

Figure 11. Inverse Walsh transform of addition coefficients A's and B's

Figure 12. Inverse Walsh transform of subtraction coefficients A's and B's

For multiplication process, we need to perform dyadic convolution between coefficients A's and B's in order to find Coefficients E's [14]. Manual calculations for this process based on Equation 16 are listed below:

$$\begin{split} \mathbf{E}_0 &= \mathbf{A}_0 * \mathbf{B}_0 + \mathbf{A}_1 * \mathbf{B}_1 + \mathbf{A}_2 * \mathbf{B}_2 + \mathbf{A}_3 * \mathbf{B}_3 \\ &= 2 * 12 + (-8) * 10 + (-18) * 12 + 0 * (-10) = \textbf{-272} \\ \mathbf{E}_1 &= \mathbf{A}_1 * \mathbf{B}_0 + \mathbf{A}_0 * \mathbf{B}_1 + \mathbf{A}_3 * \mathbf{B}_2 + \mathbf{A}_2 * \mathbf{B}_3 \\ &= -8 * 12 + 2 * 10 + 0 * 12 + (-18) * (-10) = \textbf{104} \\ \mathbf{E}_2 &= \mathbf{A}_2 * \mathbf{B}_0 + \mathbf{A}_3 * \mathbf{B}_1 + \mathbf{A}_0 * \mathbf{B}_2 + \mathbf{A}_1 * \mathbf{B}_3 \\ &= -18 * 12 + 0 * 10 + 2 * 12 + (-8) * (-10) = \textbf{-112} \\ \mathbf{E}_3 &= \mathbf{A}_3 * \mathbf{B}_0 + \mathbf{A}_2 * \mathbf{B}_1 + \mathbf{A}_1 * \mathbf{B}_2 + \mathbf{A}_0 * \mathbf{B}_3 \\ &= 0 * 12 + (-18) * 10 + (-8) * 12 + 2 * (-10) = \textbf{-296} \end{split}$$

The FPGA implementation of this convolution is shown in Figure 13. These coefficients are then passed to the inverse Walsh circuit and the result signal h(t) is shown in Figure 14.

| 🔤 isimwave                          |      |           |                  |     | n isimwave        |      |              |                          |        |

|-------------------------------------|------|-----------|------------------|-----|-------------------|------|--------------|--------------------------|--------|

| File View Tools Help                | )    |           |                  |     | File View Tools   | Hala |              |                          |        |

| ] 🖻 🖄 🕹                             | t 📩  | ሶ ሳ 🎾 🎤 🔀 |                  |     |                   | 1.1  |              |                          |        |

| Current Simulation<br>Time: 2000 ns |      | 0 400     | 800 1200 1600 20 | D I |                   |      | ሐሶኅ /        | ◎ ❷ 異 其 😢                | 2800.0 |

| LI clock                            | 1    |           |                  |     | Current Simulatio |      | 0            | 1000 2000                | 3000   |

| 🔟 start                             | 0    |           |                  |     | Time: 4000 ns     |      | ľ i          |                          | 1 3000 |

| 🕀 📉 a0[6:1]                         | 2    |           | 2                |     | 11 clk            | 4    |              |                          |        |

| 🕀 💢 a1[6:1]                         | -8   |           | -8               |     |                   |      |              |                          |        |

| 🗉 📉 a2[6:1]                         | -18  |           | -18              |     | 🗓 enter           | 0    |              |                          |        |

| 🕀 📉 a3[6:1]                         | 0    |           | 0                |     | 1 reset           | 0    |              |                          |        |

| 🕀 💢 b0[6:1]                         | 12   |           | 12               |     |                   | 070  |              | V                        |        |

| 🕀 💢 b1[6:1]                         | 10   |           | 10               |     | 🕀 💢 c0[13:1]      | -272 | (            | X                        |        |

| 🗉 💢 b2[6:1]                         | 12   |           | ( 12             |     | 🗄 📜 c1[13:1]      | 104  | ( 0          | X 104                    |        |

| 🕀 💢 b3[6:1]                         | -10  |           | -10              |     |                   | -112 |              | X -112                   |        |

| 🕀 💢 c0[13:1]                        | -272 | (13) 0    | -272             |     |                   |      | <u> </u>     | A                        |        |

| 🕀 💢 c1[13:1]                        | 104  | (13) 0    | 104              |     | 🗄 💢 c3[13:1]      | -296 | ( 0          | X -296                   |        |

| 🕀 📉 c2[13:1]                        | -112 | (13) 0    | -112             |     | 🕀 🔀 h[9:1]        | -36  | (9) 0        | X -36 X -12 X 15 X -35 X | -36    |

| 🕀 📉 c3[13:1]                        | -296 | (13) 0    | -296             |     | C. Scolord        |      | \ <u>a</u> / |                          |        |

Figure 13. Dyadic convolution between coefficients A's and B's

Figure 14. Inverse Walsh transform of dyadic convolution between coefficients A's and B's

To summarize the implementation of the proposed design, all the signals and coefficients are listed in Table 1.

| Table 1. List | t of all sig | gnals and | d coeffic | ients |

|---------------|--------------|-----------|-----------|-------|

| Signal/       | 1            | 2         | 3         | 4     |

| Coefficients  |              |           |           |       |

| x(t)          | -6           | -2        | 3         | 7     |

| g(t)          | 6            | 6         | 5         | -5    |

| А             | 2            | -8        | -28       | 0     |

| В             | 12           | 10        | 12        | -10   |

| С             | 14           | 2         | -6        | -10   |

| D             | -10          | -18       | -30       | 10    |

| E             | -272         | 104       | -112      | -296  |

| h(t)          | 0            | 4         | 8         | 2     |

| p(t)          | -12          | -8        | -2        | 12    |

| q(t)          | -36          | -12       | 15        | -35   |

#### 6. ANALYSIS AND DISCUSSIONS

In the design of the proposed real-time Walsh transform and its inverse, special care is needed for the selection of word lengths representing input signals, coefficients and the output signal. This requires detailed analysis of each step of the processes. The implementation results shown in the previous section clearly indicate that the word lengths for different coefficients and output signals vary.

The design is implemented on Xilinx Virtex-4 chip (xc4vlx15-12-sf363). Various results are shown in Table 2.

| Table 2. Comparison of area. | speed and word lengths for | r Walsh transform, inverse | Walsh and dvadic |

|------------------------------|----------------------------|----------------------------|------------------|

|                              | , - p                      |                            |                  |

| convolution            |       |       |      |       |       |       |  |  |

|------------------------|-------|-------|------|-------|-------|-------|--|--|

| Process                | Slice | Flip  | LUTs | Speed | WI    | WO    |  |  |

|                        |       | Flops |      | (MHz) | (bit) | (bit) |  |  |

| Walsh Transform        | 20    | 39    | 36   | 636   | 4     | 6     |  |  |

| Inverse Walsh          | 27    | 20    | 46   | 828   | 6     | 5     |  |  |

| Transform <sup>+</sup> |       |       |      |       |       |       |  |  |

| Inverse Walsh          | 74    | 43    | 116  | 816   | 13    | 9     |  |  |

| Transform              |       |       |      |       |       |       |  |  |

| Dyadic Convolution     | 428   | -     | 732  | -     | 6     | 13    |  |  |

Note: + Inverse Walsh transform of addition or subtraction of coefficients A's and B's ^ Inverse Walsh transform of dyadic convolution of coefficients A's and B's

In order to make a comparison with the results reported by other works, we implemented real-time Walsh transform for N=4, 8, 16 and WI=8 on Xilinx Virtex-IIP and Virtex-4. The results of comparison are presented in Table 3.

| Table 3. Comparison the proposed Walsh transform to previous methods for various Xilinx Virtex series |  |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| (WI=8)                                                                                                |  |  |  |  |  |  |  |

| (11-0)     |    |          |       |        |          |                |       |  |  |

|------------|----|----------|-------|--------|----------|----------------|-------|--|--|

| FPGA       | Ν  | Proposed |       | Struct | ure [11] | Structure [12] |       |  |  |

| Platform   |    | Slice    | Speed | Slice  | Speed    | Slice          | Speed |  |  |

|            |    | s        | (MHz) | s      | (MHz)    | s              | (MHz) |  |  |

| Virtex-IIP | 4  | 37       | 370   | 32     | 294      | 83             | 204   |  |  |

|            | 8  | 83       | 357   | 96     | 283      | 163            | 183   |  |  |

|            | 16 | 163      | 335   | 256    | 288      | 377            | 100   |  |  |

| Virtex-4   | 4  | 37       | 586   | 32     | 294      | 82             | 227   |  |  |

|            | 8  | 83       | 573   | 96     | 471      | 163            | 212   |  |  |

|            | 16 | 165      | 530   | 256    | 418      | 358            | 121   |  |  |

It may be seen that the proposed structure for the Walsh Transform is superior to the others except for N=4, in which case, the area occupied is a bit higher than the one proposed in [11].

We also implemented the Inverse Walsh transform for N=4, 8, 16 and WO=8 on Xilinx Virtex-IIP and Virtex-4 based on Hadamard ordering. Table 4 shows the results of these implementations.

Table 4. Implementation of Inverse Walsh transform to various Xilinx Virtex series (WO=8)

| FPGA Platform | Ν  | Inverse W | alsh Transform |  |

|---------------|----|-----------|----------------|--|

|               |    | Slices    | Speed (MHz)    |  |

| Virtex-IIP    | 4  | 40        | 630            |  |

|               | 8  | 108       | 468            |  |

|               | 16 | 275       | 437            |  |

| Virtex-4      | 4  | 40        | 835            |  |

|               | 8  | 108       | 636            |  |

|               | 16 | 276       | 628            |  |

#### 7. CONCLUSION

A complete set of real-time Walsh and Inverse Walsh transforms for signal processing has been proposed and demonstrated on various Xilinx Virtex chips. The design consists of real-time Walsh transforms, inverse Walsh transform, DSP block and dividing block.

Real-time Walsh transform is controlled by independent, random signal Enter. The availability of this signal is based on the availability of data in input ports of the design system. It requires N+1 cycles of signal Enter for completing the process of transforming input data to the frequency domain.

On the basis of implementation results, it is concluded that the proposed Walsh transform structure is superior to many of the structures reported in literature. The Inverse Walsh transform, requires more area but is faster than the Walsh transform itself. The results clearly show that the DSP (Dyadic convolution) for multiplication process requires 7 times larger area than other processes. When combining the proposed realtime Walsh transform, DSP block and inverse Walsh transform into a single system, the designed inverse Walsh transform is fully controlled by Clock, instead of signal Enter.

#### ACKNOWLEDGEMENTS

The authors gratefully acknowledge the financial support from National Plan for Science, Technology and Innovation (NPST), Saudi Arabia under project no. 09-ELE854-02.

#### REFERENCES

- [1] M Maqusi. Applied Walsh Analysis. 1<sup>st</sup>ed., *Heyden and Son Ltd.* London. 1981.

- [2] KG Beauchamp. Applications of Walsh and Related Functions With an Introduction to Sequency Theory. *Academic Press.* 1984.

- [3] MG Karpovsky, *et al.* Spectral Logic and Its Applications for The Design of Digital Devices. *John Wiley & Sons Inc. Publication. New Jersey.* 2008.

- [4] AMA Bin Ateeq, *et al*.Hardware Realization of Walsh Functions and Their Applications Using VHDL and Reconfigurable Logic. *ICM-2002. Beirut, Leban*on. 2002; 58-61.

- [5] SM Qasim, SA Abbasi. Single Chip FPGA Based Realization of Arbitrary Waveform Generator using Rademacher and Walsh Functions. Proceedings of the Second International Conference of Emerging Technologies (ICET), Peshawar, Pakistan. 2006; 205–210.

- BJ Fino, VR Algazi. Unified Matrix Treatment of the Fast Walsh-Hadamard Transform. *IEEE Transactions on Computers*. 1976; 42: 1142-1146.

- [7] A Amira, et al. An FPGA Implementation of Walsh-Hadamard Transforms for Signal Processing. Proceeding of IEEE International Conference on Acoustic. Speech and Signal Processing. 2001; 2: 1105-1108.

- [8] A Amira, et al. A Novel Architecture of Walsh Hadamard Transform using distributed Arithmetic Principles. Proceeding of The 7th IEEE International Conference on Electronics, Circuit & Systems (ICECS'2K), Beirut, Lebanon, 2000.

- [9] A Amira, et al. Novel FPGA Implementations of Walsh-Hadamard Transforms for Signal Processing. Proceeding of IEE Vision, Image, and Signal Processing. 2001; 148(6).

- [10] BJ Falkowski, T Sasao. Unified Algorithm to Generate Walsh Functions in Four Different Orderings and Its Programmable Hardware Implementations. *Proceeding of IEE on Vision, Image and Signal Processing.* 2006; 152(6): 819-826.

- [11] A Amira, S Chandrasekaran. Power Modeling and Efficient FPGA Implementation of FHT for Signal Processing. IEEE Transactions on Very Large Scale Integration (VLSI) Systems. 2007; 15(3): 286-295.

- [12] PK Meher, JC Patra. Fully-Pipelined Efficient Architechtures for FPGA Realization of Discrete Hadamard Transform. Proceeding of International Conference on Application-Specific Systems, Architechture and Processors (ASAP 2008). 2008: 43-48.

- [13] Zulfikar, *et al. FPGA Based Processing of Digital Signals Using Walsh Analysis.* Proceeding of IEEE International Conference on Electrical Control & Computer Engineering (INECCE 2011), Pahang. 2011.

- [14] MY Zulfikar, et al. FPGA Based Analysis and Multiplication of Digital Signals. IEEE Proceeding of Second International Conference on Advances in Computing, Control and Telecommunication Technologies (ACT 2010). Jakarta. 2010: 32-36.

#### **BIOGRAPHIES OF AUTHORS**

**Zulfikar** was born in Beureunuen, Aceh, Indonesia, in 1975. He received his B.Sc. degree in Electrical Engineering from North Sumatera University, Medan, Indonesia, the M. Sc. Degree in Electrical Engineering from King Saud University, Riyadh, Saudi Arabia, in 1999 and 2011, respectively. In 2006, he joined the Electrical Engineering Department, Syiah Kuala University. His current research interests include VLSI design and System on Chips (SoC).

**Shuja A. Abbasi** was born at Amroha, India in 1950. He obtained the degrees of B.Sc. Engineering and M.Sc. Engineering in Electrical Engineering in 1970 and 1972 respectively from Aligarh Muslim University (AMU), Aligarh, India with first position in the University. He did Ph.D. from University of Southampton, England in 1980 in Microelectronics.

He joined as Assistant Proffessor in the Department of Electrical Engineering at Aligarh Muslim University, Aligarh, India in 1971, was promoted to the positions of AssociateProfessor and Professor in 1982 and 1986 respectively. He shifted to the newly created Department of Electronics Engineering at AMU as Professor in 1988. He served as Chairman, Department of Electronics Engineering, AMU from 1996 to 1999. He held many Academic/ Administrative positions in the past at AMU and outside. He joined as Professor of Electronics Engineering at College of Engineering, King Saud University, Riyadh, Saudi Arabia in 1999 and is continuing there since then. He has more than 100 research publications to his credit so far. He has completed many client funded projects from various organizations. His current interests include VLSI design and technology.

Abdul Rahman M. Alamoud was born in Onaizah, Saudi Arabia on Sept. 21, 1946. He earned his B.Sc. degree in Electrical Engineering, College of Engineering (COE) from the University of Riyadh (renamed later as KSU). He earned his M.Sc., in Microelectronics, and Ph.D., in photovoltaic solar cells, from West Virginia University, Morgantown, W.V., USA in 1974 and 1984 respectively. In June 1984, he joined the Department of Electrical Engineering, KSU as an Assistant professor and was promoted to the rank of Associate professor and Professor in 1989 and 1999 respectively. In 1991 he took a one year leave of absence from KSU and joined the Advanced Electronics Company AEC), Riyadh, Saudi Arabia as the Special Projects Director. In 1992 he was appointed as Director, Research Center, COE, KSU for a two term period in June 1996. In the academic year June 1996- Sept 1997 he was a Visiting Research Associate Professor, National Renewable Energy Laboratory, Golden, Colorado, USA (July15-Dec.15, 97) where he worked on the development of thin films CdTe Solar Cells and characterization of materials (such as semiconductors thin films and Saudi white sand rocks) and a Visiting Research Associate Professor, VLSI Research Group, Department of Electrical and Computer Engineering, University of Waterloo, Waterloo, ON, Canada. Worked on the design of VLSI circuits using Cadence (Mar.9-Aug.22, 97). He was chosen to be the Vice Dean for Administrative Affairs, COE, KSU during the period of June 1999- June 2005. His research interests are in both microelectronics, Solar Cells and Materials, and Photovoltaic Systems where he published more than forty papers.