# **International Journal of Electrical and Computer Engineering (IJECE)**

Vol. 4, No. 5, October 2014, pp. 648~657

ISSN: 2088-8708

# **Digital Encoder Designing for Mobile Robot Control**

## Alireza Rezaee\*, Reza Afshar\*\*

\*Department of system and Mechatronics Engineering, Faculty of New Sciences and Technologies, University of Tehran, Tehran, Iran, arrezaee@ut.ac.ir

\*\* Department of Electrical Engineering, Miyaneh Branch, Islamic Azad University, Miyaneh, Iran

#### **Article Info**

#### Article history:

Received May 27, 2014 Revised Sep 4, 2014 Accepted Sep 14, 2014

#### Keyword:

Control CPLD Decoder/counter Interface ic Motor

#### **ABSTRACT**

In this paper we present the design of a quadrature decoder/counter interface IC (ASIC) that performs the decoding, counting, and bus interface function in digital motor control systems, employing an Altra FLEX 10KA, 2s150fg456 Xilinx device. The ASIC contains a pair of digital filters, a quadrature decoder, an up/down counter, a latch and inhibit circuit, and an 8-bit bus interface to a digital processing system. The design of digital of the digital filter is based on the finite state machine model with datapath (FSMD). A novel scheme for detecting the motor rotation direction is also proposed. The ASIC can be applied to a digital motor control system forgetting the rotation speed or position of the motor, which is quipped with an optical encoder. The data acquisition can be extended to 16-bit integer format by two continuos reading cycles. Simulation and experimental tests are shown to verify the ASIC function properly.

Copyright © 2014 Institute of Advanced Engineering and Science.

All rights reserved.

#### Corresponding Author:

Alireza Rezaee,

Department of system and Mechatronics Engineering, Faculty of New sciences and technologies,

University of Tehran, Tehran, Iran

Email: arrezaee@ut.ac.ir

# 1. INTRODUCTION

In high-performance digital motor control systems with wide speed control range, certain interface integrated circuit (ICs) are still required through which to get the motor feedback position or speed signals, although sensorless control has got much attention recently [1]. Tachometers, potentiometers, resolvers, an optical encoder, for getting the motor rotation angle or speed. among them, the optical encoder is the most commonly used because its output signal is digital with high noise immunity and high resolution.

There are three types of optical encoder Commonly used in motion control. They are lockwise/counterclockwise, (CW/CCW), pulsedirection (pulse/DIR) and quadrature (A/B phase). Among them, the last one is the most popular because it can produce 4-time rate resolution.

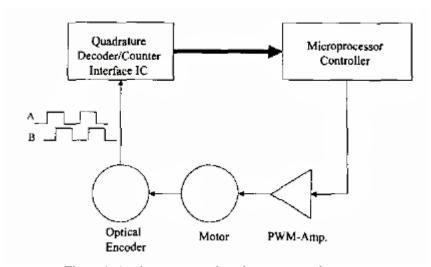

Over the past two decades, mostly the digital motor control was done by using microprocessors [2], as shown in Figure 1. Some interface ICs, such as HP HCTL2000 and HCTL2016, for quadrature decoding and counting the output signal of the optical encoder are also available in commercial arkets [3]. However, the construction of whole control system is complex and the cost is not cheap. Recently, the progress in VLSI technology has made possible the use of complex programmable logicdevices (CPLD) of field programmable gated arrays (FPGA) for the design of digital controller, interface IC, or other application-specific ICs (ASICs) in the same chip Although the design of the quadrature decoder/counter interface IC in Literature is not lacking [7], the work was done in transistor level.In this paper, we present the design of interface IC in ate and register level, employing an Altra FLEX 10KA and 2s150 Xilinx device [8]. Using the scheme, the implementation of the circuit is easier than the previous work. The interface IC can perform flitering, quadrature ecoding,positioning counting and bus interface function. Simulation and experimental tests are shown to verify the function of the interface IC properly. The circuit can be integrated as a part of circuit of an application-specific digital control IC for motion control.

Figure 1. A microprocessor-based motor control system.

## 2. THE REQUIRED FUNCTION

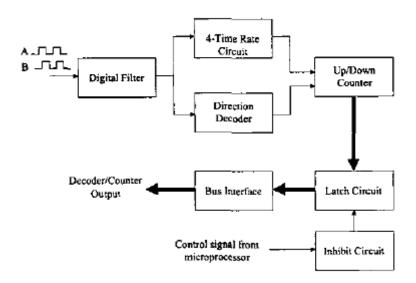

Figure 2 shows the system function block diagram of the interface IC, which has an two-phase interface to an optical encoder and an 8-bit interface to a standard microprocessor or application-specific digital system. The required function of the interface IC are described as follows. Since many motors are usually working in noisy environments, which might introduce unwanted noise in the encoder's ouput due to electromagnetic coupling or vibration. A pair of digital filters, one for the channel A and the other one for the channel B, are required to filter out the noise on the incoming signals. A uadrature decoder circuit is also required to decode the incoming filtered signals for determining the motor rotation direction and multiply the resolution of the input signals by a factor of four. A position couter is then needed to up or down count the resulting decoded pulse according to the rotation direction indication from one of the decoder outputs.

Figure 2. System function block of interface IC.

After the pulses been counted, the system can utilize the counter in two ways. First, the 16-bit latch and inhibit logic on the chip allows access to 16 bits of count required, a simple 8-bit mode is vailable by disabling the inhibit logic. The inhibit logic on the chip inhibits the transfer of data from the counter to the position data latch during the time interval that the latch output are being read. The inhibit logic allows the microprocessor or digital system to firstly read the low order byte form the latch. Meanwhile, the counter can

continue to keep track of the quadrature decoder states from the channel-A and channel-B input signal. In the following, only the designs for the digital filters Quadrature decoder, and inhibit logic are described. The position counter and latch circuit, which are very common, are not described here.

#### 3. DESIGN OF THE INTERFACE IC

# 3.1. Digital Filter

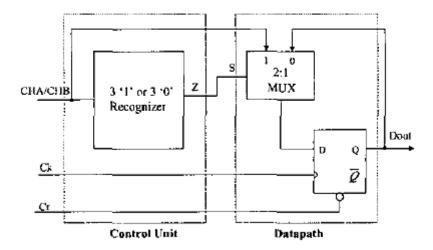

The design of the digital filters is based on the finite state machine model with datapath (FSMD) [9]. Figure 3 shows the circuit architecture of digital filter which consists of control unit and datapath on each channel. The control unit is recognizer that checks if the input from the optical encoder has short duration pulses, and a D flip flop. If the input level has same value (1 or 0) on at least threeconsecutive clock cycles, then the input is not considered as a noise. In this case the output of the recognizer is active high, which then allows the input data to flow through the datapath. The data value thus becomes the new output of filter. Otherwise the input is considered as a noise and the datapath output of the filter remain the same

Figure 3. Implementation of digital filter.

Figure 4. Design of the recognizer of digital filter: (a) state diagram (b) next state/ouput table, (c) excitation table, excitation and output equations.

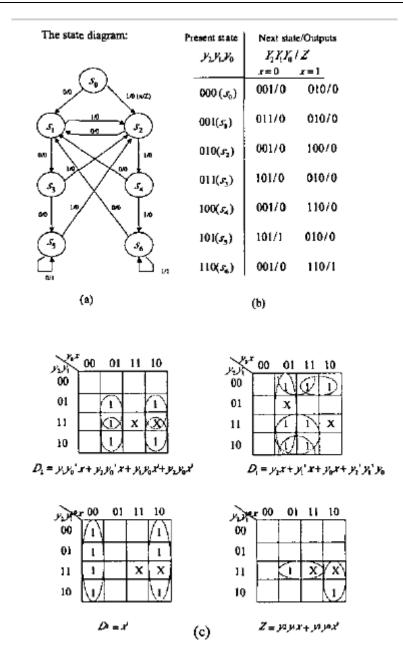

We assume that the design of control unit follows the finite state machine (FSM) model, consisiting of next-state logic, a state register, and an output logic [9, 10, 11].

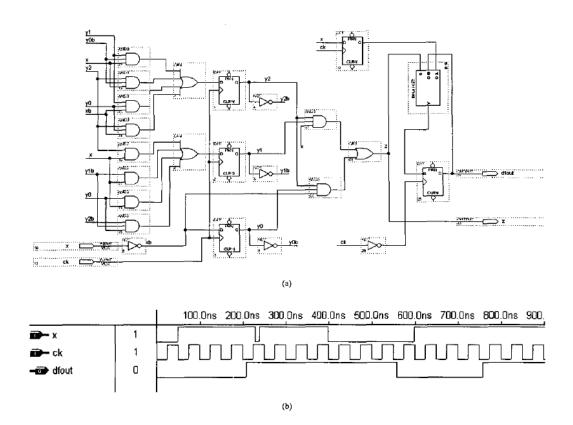

Construction of the model starts with the generation of state diagram and/or next state and output tables. Figure 4(a) shows the state diagram of the recognizer which contains seven optimized states, where each state has different next state or output for every input. The correcponding next-state/output table with appropriate state encoding is shown in Figure 4(b). After completing the processof state minimization and state encoding, we are ready to choose the proper type of flip flop forimplementation of the FSM model. Since D flip flops required fewer connections, they are chosen for our design. The excitation table, excitation and output equations by using the D flip flops acted as the state register are shown in Figure 4(c). The digital filter circuit and simulation result are shown in figure 5(a) and (b), respectively. As can be seen from Figure 5(b), the short-duration noise on the input signal (x) is rejected on the output (dfout) at the expense of three clocks time delay.

## 3.2. Quadratuer Decoder

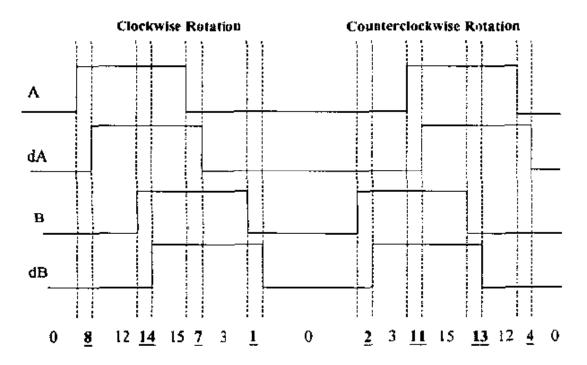

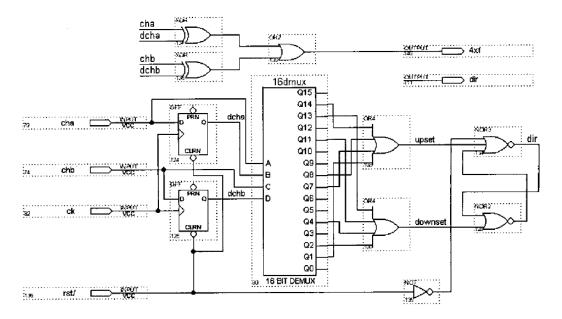

The aqadrature decoder section consisits of a direction decoder and a 4-time rate circuit. It samples the two quadrature signal from the digital filters outputs and observes changes in these outputs on therising clock edge. The two quadrature signals can be encodered as four states. The state changes can be detected by comparing the previously sampled state to the current sampled state. This can in turn multiply the input signal frequency by a factor of four. A new method for detecting the rotation direction of the motor is shown in Figure 6. It can be seen that the encoded state of 8, 14, 7, and 1 in clockwise direction are different from those states of 2, 11, 13, and 4. Thus we can use a 4-to 16 demultiplexer and some output logic to detect the direction. The count direction (up or down) is also determined by observing the previous and current states. The design circuit is shown in the bottom part of Figure 7. The upper part of Figure 7 shows the design of the 4-time rate circuit, the output of which is going to fetch into an up/down position counter.

Figure 5. (a) the digital filter circuit (b)simulation result

Figure 6. The determining strategy for rotation direction.

### 3.3. Inhibit Logic

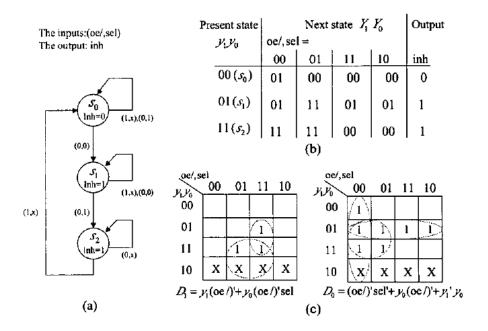

The inhibit logic section samples the oe/ and sel reading command signal from the microprocessor or digital system on the falling edge of the clock and inhibits the position data latch to avoid the latcheddata being updated during a two-byte reading cycles for a 16-bit data access. The desisn of the inhibit logic also follows the FSM models as described above. The state diagram and next – state/output able are shown in figure 8(a) and (b), respectively. As can be seen, there are three minimum states and only two flip flops are need for the implementation of the model. Similarly, we use the D flip flop as the state registers due to its simplicity. The excitation table equation logic are shown in figure 8(c). The output is just the same as second flip flop output state.

Figure 7. The Quadrature decoder and four-time rate circuit.

П

Figure 8. Design of inhibit logic (a) state diagram,(b) next-state/outputtable, (c) excitation table and excitation equation.

#### 4. SIMULATION AND TEST

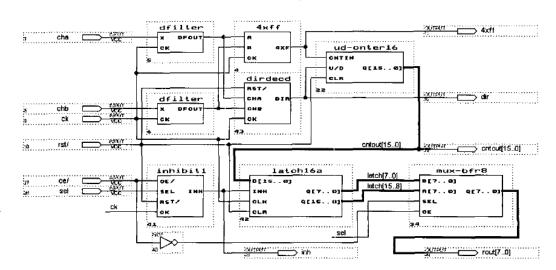

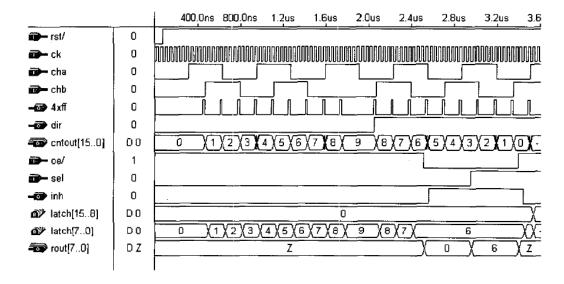

The overall circuit of the interface IC plotted by using the Altra MAXPLUS II and ISE Xilinx. Is shown in figure 9. The wave form simulation provided in this tool has verified each circuit symbol in this figure. An overall simulation result to test the function of the interface IC is shown in Figure 10 by giving two quadrature input signal (cha and chb) and a clock signal with much higher frequency than the input quadrature signals. As can be seen, a 4-time rate signal (4xff) whose frequency is four times of that of input pulses is successfully generated In addition, the direction signal (dir) is active low if thephase A signal is leading the phase B signal and active high if the phase Asignal is lagging the phas B signal. The position up/down counter up counts from 0 to 9 while the dir signal is active high.

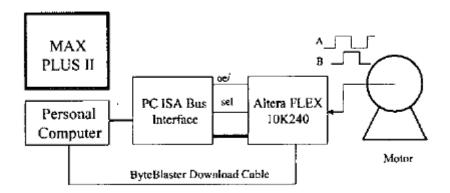

The position data latch output (latch [7..0]) Remains at 6 when the oe/signal is active low for a 16-bit data access. At the same time the inhibit logic output signal (inh) is active high and remains high until the low-byte data has been read out on the second reading cycle. The simulation results indicate that the function of quadrature decoder/counter interface IC are correct. The design circuit has been further tested by the experimental system, as shown in Figure 11. The motor optical encoder can produce two quadrature A/B phase signals with the rate of 2000 pulses per revolution. A test program in the personal computer has been designed to read the count number latched on the interface IC. For decoding and counting the pulses, we rotate the motor shaft manually in about every five seconds.

Figure 9. The overall circuit of quadrature decoder/counter interface IC.

Figure 10.Simulation result of the quadrature decoder/counter Interface IC

During the time interval, we can see the latched count number displayed on the PC monitor clearly. For one rotation in the clockwise rotation, there will be 8000 pulses to be counted, and then the display number is 1F40 in hex-decimal data format. Table I summaries the cout number corresponding to the rotation cycles in clockwise and counter clockwise direction, respectively. The results also verify the function of the quadrature ecoder/counter interface IC properly.

Figure 11. The experimental system fortesting the interface IC.

Table 1. The motor rotation cycles and corresponding counts.

| 1. The motor rotation eyeles and corresponding e |           |           |  |  |

|--------------------------------------------------|-----------|-----------|--|--|

| Rotation                                         | Counts in | Counts in |  |  |

| cycles per 5                                     | Clockwise | Counter   |  |  |

| sec                                              | Direction | Clockwise |  |  |

|                                                  |           | Direction |  |  |

| 1                                                | 1F40      | E0BF      |  |  |

| 2                                                | 3E80      | C17F      |  |  |

| 3                                                | 5DC0      | A23F      |  |  |

| 4                                                | 7D00      | 82FF      |  |  |

| 5                                                | 9C40      | 63BF      |  |  |

Implement in 2s150fg256 xilinxin ISE Device Utilization for 2s150fg4 56

| Device Chinzation for 251501g+ 50 |      |       |         |  |

|-----------------------------------|------|-------|---------|--|

| Resource                          | used | Avail | utilize |  |

| I/Os                              | 57   | 288   | 19.79%  |  |

| Function generator                | 57   | 3456  | 1.65%   |  |

| CLB Slices                        | 35   | 1728  | 2.03%   |  |

| DFFs                              | 70   | 4320  | 1.62%   |  |

|                                   | •    | •     | •       |  |

#### 5. CONCLUSION

This paper presents the design of quadrature decoder/counter interface IC in the gate and register level by using an Altra FLEX 10kA, XC95144XL Xilinx device. Implementation of the circuit using the CPLD device is easier than the previous work done in transistor level. Simulation and experimental tests are shown to verify the ASIC functions properly. The interface IC can be applied as an interface to a microprocessor – based motor control system. It can be also integrated as a part of circuit of an application-specific digital control IC for motion control.

# REFERENCES

- [1] L Zhen, L Xu. "Sensorless Field Oriention Control of Induction Machines Based on a Mutual MRAS Scheme". IEEE Industrail Electronics. 2012; 45: 824-831.

- [2] K Kubo, M Watanable, T Ohmae, and K Kamiyama. "A fully digitalized speed regulator usigmultimicroprocessor system for induction motor drivers". *IEEE Trans. Ind. Applicant*. 1985; IA- 1: 1001-1008.

- [3] Hewlett Packard. Quadrature Decoder/Counter Interface ICs HCTL- 2000. 2016 Datasheet.

- [4] H Le\_Huy. "Microprocessors and digital ICs for motion control". Proc. of the EEE. 1994; 82(8): 1140-1163.

- [5] EB Patterson, D Morley, CG Oswald, and PG Holmes. "Total digital ASIC control for an induction motor drive". *IEE Colloquium onASIC Technology for Power Electronics Equipment*. 2010: 2/1- 4.

- [6] J Pasanen, P Jahkonen, SJ Ovaska, O Vainio, H Tenhunen. "An integrated digital motion control unit". *IEEE Trans. on Instrumentation and Measurement*. 1991; 40(3): 654-657.

- [7] CC Wang, PM Lee, YL Tseng, and CF Wu. "Alow-cost quardrture decoder/counter interface integrated circuit for AC induction motor server control". *Int. J. Electronis*. 2000; 87(9): 1053-1063.

- [8] AltraInc, FLEX 10KA Handbook, 1997.

- [9] Daniel D Gajski. Principles of Digital Design. 1997.

- [10] Altera Inc, MAX+PLUS II Getting Started, Version 8.1, 1997.

- [11] A Talukder, R Chandramouli, SM Ali. "Autonomous resource management and control algorithms for distributed wireless sensor networks". In Proc. IEEE International Conference on Computer Systems and Applications. 2005.

#### **BIOGRAPHIES OF AUTHORS**

Alireza Rezaee received his B.Sc. degree in Control Engineering from Sharif University of Technology, Iran 2002 and M.Sc and Ph.D degree in Electrical Engineering from Amirkabir University of Technology, Iran (2005 and 2011 respectively).

From 2013 till now he is an assistance professor in department of system and mechatronics engineering in new sciences and technology faculty at university of Tehran. His research interest are in intelligent robotics, mobile robot, navigation, machine learning, bayesian networks, cognitive science.

Reza Afshar was born in Qazvin-Iran in 1989. He received the B.Sc. degree in electrical engineering from the Islamic Azad University, Buin Zahra, Iran, in 2014. Currently, he is working toward his M.S degree in Electrical Engineering at Islamic Azad University Miyaneh Branch, Miyaneh, Iran. His research interests include analysis and designing of Digital VLSI.