3536

# **International Journal of Electrical and Computer Engineering (IJECE)**

Vol. 8, No. 5, October 2018, pp. 3536~3543

ISSN: 2088-8708, DOI: 10.11591/ijece.v8i5.pp3536-3543

# Design and Simulation of Novel 11-level Inverter Scheme with Reduced Switches

R. Palanisamy, Gaurav Singh, Priyanka Das, D. Selvabharathi, Sourav Sinha, Arnab Nag

Departement of EEE, SRM Institute of Science and Technology, Chennai, India

## **Article Info**

## Article history:

Received Apr 17, 2018 Revised Jul 20, 2018 Accepted Jul 30, 2018

#### Keyword:

dsPIC microcontroller Multicarrier sinusoidal pulse Width modulation (MSPWM) Novel 11-level inverter Total harmonic distortion (THD)

# **ABSTRACT**

This work recommends the performance of coupled inductor based novel 11-level inverter with reduced number of switches. The inverter which engender the sinusoidal output voltage by the use of split inductor with minimised total harmonic distortion (THD). The voltage stress on each controlled switching devices, capacitor balancing and switching losses can be reduced. The proposed system which gives better controlled output current and improved output voltage with moderate THD value. The switching devices of the system are controlled by using multicarrier sinusoidal pulse width modulation algorithm by comparing the carrier signals with sinusoidal signal. The simulation and experimental results of the proposed 11-level inverter system outputs are established using matlab/Simulink and dsPIC microcontroller respectively.

Copyright © 2018 Institute of Advanced Engineering and Science.

All rights reserved.

## Corresponding Author:

R. Palanisamy, Departement of EEE, SRM Institute of Science and Technology, Chennai, India.

Email: palanisamy.r@ktr.srmuniv.ac.in

#### 1. INTRODUCTION

An inverter is an electronic device or circuitry that changes direct current (DC) to alternating current (AC). The input voltage, output voltage and frequency, and overall power handling depend on the design of the specific device or circuitry [1]. Nowadays many industrial applications have begun to meet the power demand. These high-power motor drives and utility applications require medium voltage. A multilevel inverter is a power electronic device which is capable of providing desired alternating voltage level at the output using multiple lower level DC voltages as an input [2], [3].

Nowadays the requirement of power equipment's is increasing rapidly, which increases the harmonic content within them [3], [5]. Various models and thesis have been proposed to reduce them. Levels of inverters are increased to reduce the harmonics. Some of them use greater number of switches to increase the level of the inverter [6], [7]. Contradicting this fact this inverter topology uses less number of switches and uses multicarrier sine waves as an interrupt. Unlike [8] it does not use triangular wave with phase disposition technique. Multicarrier pulse width modulation works with a constant carrier frequency not synchronized with fundamental stator frequency [9]. Multi carrier pulse width modulation gives an optimal utilization of switching frequency permitted, therefore PWM carrier frequency may be chosen to a value of two times the permitted switching frequency [10], [11].

Multicarrier PWM strategy is the widely-adopted modulation strategy for multi-level inverter. It is similar to that of the SPWM strategy except for the fact that several carriers are used. In this technique, several triangular inputs is compared with a sine wave [12]. The number of carriers required to produce m-level output is m-1. All carriers have the same peak to peak amplitude Ac and same frequency fc except for variable frequency PWM [13], [14]. The point of intersection of the triangular wave with sine wave gives

step input as output [15]. The reference sine wave is continuously compared with each of the triangular waves and whenever the reference is greater than the carrier signal, pulse is generated [16].

The proposed simulation uses multicarrier sinusoidal pulse width modulation technique to generate 11-level output voltage. It also uses lesser number of switches as compared to the previous proposed models.. This reduces the dv/dt loss and thus reducing the harmonics. For a particular output voltage, it uses only two switches. The voltage stress on each controlled switching devices, capacitor balancing and switching losses can be reduced. The proposed system which gives better controlled output current and improved output voltage with moderate THD value. The simulation and experimental results of the proposed 11-level inverter system outputs are established using matlab/Simulink and dsPIC microcontroller respectively.

## 2. CIRCUIT AND WORKING OF 11-LEVEL INVERTER

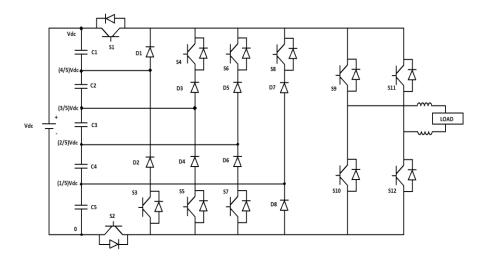

In Figure 1 shows power circuit of 7 level inverter, which consists of dc link capacitor  $C_1$ ,  $C_2$ ,  $C_3$ ,  $C_4$  and  $C_5$  across the applied dc source. Power semiconductor switches  $S_1$ ,  $S_2$ ,  $S_3$ ,  $S_4$ ,  $S_5$ ,  $S_6$ ,  $S_7$  and  $S_8$  and freewheeling diodes  $D_1$ ,  $D_2$ ,  $D_3$ ,  $D_4$ ,  $D_5$ ,  $D_6$ ,  $D_7$  and  $D_8$  are used to combine the voltages to acquire the 11 level voltages. And which contains conventional 2 level VSI circuit is added with front circuit, which consists of power switches  $S_9$ ,  $S_{10}$ ,  $S_{11}$ , and  $S_{12}$  and coupled inductor is used connect with load circuit.

Figure 1. Circuit of novel 11-level inverter

# 2.1. Modes of operation

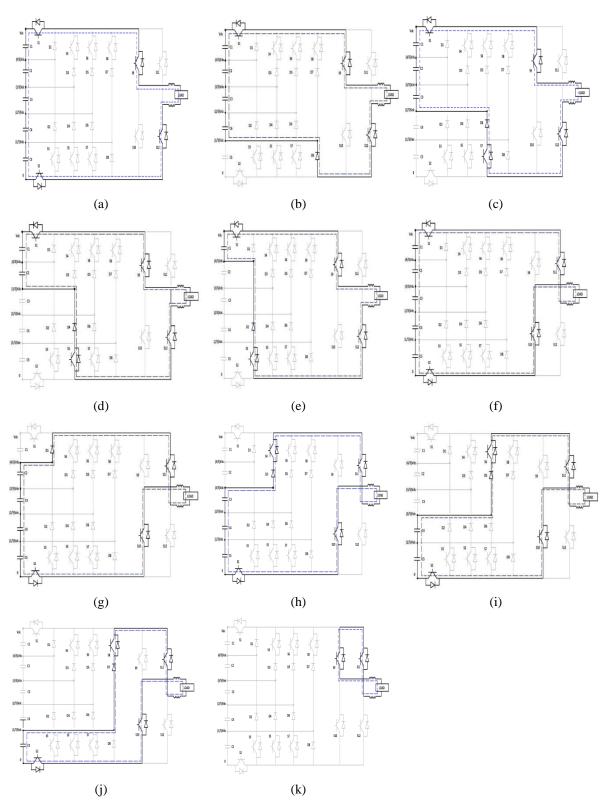

From the power circuit of 11-level voltage inverter has the following eleven switching mode combinations is shown in Figure 2.

Mode 1: to attain the output voltage level as +Vdc, the switches S1, S2, S9, and S12 are kept in ON condition. Here none of the freewheeling diode is in ON condition, which is shown in Figure 2(a).

Mode 2: to obtain the output voltage level as  $+\frac{4}{5}$  Vdc, the switches S1, S9, and S12 are kept in ON condition. And here freewheeling diode D8 is in ON condition, which is shown in Figure 2(b).

Mode 3: to acquire the output voltage level as  $+\frac{3}{5}$  Vdc, the switches S1, S9, S12 and S6 are kept in ON condition. And here freewheeling diode D6 is in ON condition, which is shown in Figure 2(c).

Mode 4: to generate the output voltage level as  $+\frac{2}{5}$  Vdc, the switches S1, S9, S12 and S5 are kept in ON condition. And here freewheeling diode D4 is in ON condition, which is shown in Figure 2(d).

Mode 5: to generate the output voltage level as  $+\frac{1}{5}$  Vdc, the switches S1, S9, S12 and S3 are kept in ON condition. And here freewheeling diode D2 is in ON condition, which is shown in Figure 2(e).

Mode 6: to obtain the output voltage level as - Vdc, the switches S2, S10, S11 and S1 are kept in ON condition. And none of the freewheeling diodes is in ON condition, which is shown in Figure 2(f).

Mode 7: to obtain the output voltage level as  $-\frac{4}{5}$  Vdc, the switches S2, S10, and S11 are kept in ON condition. And here freewheeling diode D1 is in ON condition, which is shown in Figure 2(g).

3538 □ ISSN: 2088-8708

$\begin{aligned} \text{Figure 2. Modes of operation (a)} + V_{dc} \; (b) + & \frac{4}{5} \, V_{dc} \, (c) + \frac{3}{5} \, V_{dc} \, (d) + \frac{2}{5} \, V_{dc} \; (e) + \frac{1}{5} \, V_{dc} \; (f) - V_{dc} \; (g) - \frac{4}{5} \, V_{dc} \\ & (h) - \frac{3}{5} \, V_{dc} \; (i) - \frac{2}{5} \, V_{dc} \; (j) - \frac{1}{5} \, V_{dc} \; (k) \; 0 \; V \end{aligned}$

Mode 8: to obtain the output voltage level as  $-\frac{3}{5}$  Vdc, the switches S2, S10, S11 and S4 are kept in ON condition. And here freewheeling diode D3 is in ON condition, which is shown in Figure 2(h).

Mode 9: to obtain the output voltage level as  $-\frac{2}{5}$  Vdc, the switches S2, S10, S11 and S7 kept in ON condition. And here freewheeling diode D5 in ON condition, which is shown in Figure 2(i).

Mode 10: to obtain the output voltage level as  $-\frac{1}{5}$  Vdc, the switches S2, S10, S11 and S8 are kept in ON condition. And here freewheeling diode D7 is in ON condition, which is shown in Figure 2(j).

Mode 11: to gain the output voltage level as 0, the switches S9 and S11 are kept in ON condition. And here none of the freewheeling diode is in ON condition, which is shown in Figure 2(k) and also modes of operation with position of components shown in Table 1.

| Table 1. Modes of | f C | Operation | with | Positio <sub>1</sub> | n of | C | Components |

|-------------------|-----|-----------|------|----------------------|------|---|------------|

|                   |     |           |      |                      |      |   |            |

| Output Voltage Level                            | Capacitors ON  | Switches ON       | Freewheeling Diode ON |

|-------------------------------------------------|----------------|-------------------|-----------------------|

| $+V_{dc}$                                       | C1,C2,C3,C4,C5 | S1,S2,S10,S11     | -                     |

| $+\frac{4}{5}\mathrm{V_{dc}}$                   | C1,C2,C3,C4    | S1,S9,S12         | D8                    |

| $+\frac{1}{5}V_{dc} + \frac{3}{5}V_{dc}$        | C1,C2,C3       | \$1,\$7,\$9,\$12  | D6                    |

| $+\frac{2}{5}V_{dc}$                            | C1,C2          | \$1,\$5,\$9,\$12  | D4                    |

| $+\frac{1}{5}V_{dc}$                            | C1             | \$1,\$3,\$9,\$12  | D2                    |

| 0                                               | -              | S9,S11            | -                     |

| $-V_{ m dc}$                                    | C1,C2,C3,C4,C5 | \$1,\$2,\$10,\$11 | -                     |

| $-\frac{4}{5}V_{dc}$                            | C2,C3,C4,C5    | S2,S10,S11        | D1                    |

| $-\frac{1}{5}$ $V_{dc}$ $-\frac{3}{5}$ $V_{dc}$ | C3,C4,C5       | S2,S4,S10,S11     | D3                    |

| $-\frac{2}{5}V_{dc}$                            | C4,C5          | \$2,\$7,\$10,\$11 | D5                    |

| $-\frac{1}{5}V_{dc}$                            | C5             | \$2,\$8,\$10,\$11 | D7                    |

## 3. MULTICARRIER SPWM (MCSPWM)

In order to preserve or reduce system cost or structure, imperative to maintain the shoot through ratio as constant. At the same to reduce the voltage stress across the power switches, the boosted voltage with proper variation of modulation index. In Figure 3 shows the multicarrier sinusoidal pulse width modulation scheme, which acquires better voltage gain with constant value of shoot through state. Based on the MBC control, the z-source inverter operated either on upper shoot through or lower shoot through mode.

Constant boost ratio of the proposed system defined as,

$$B = \frac{\pi}{[3sqrt(3)M] - \pi} \tag{1}$$

where the B is boost ratio & M is modulation index. And the ripple content in the inductor is,

$$\epsilon L_1 = \frac{V*K}{2*\pi*6f*L} \tag{2}$$

here V is applied voltage, K-constant, f-frequency, L- design value inductance

Figure 3. Multicarrier sinusoidal PWM scheme

A triangle carrier wave is evaluated with a three phase reference sine wave, each phase for a positive side switch shoot through state occurs every time the triangle peak value overshoots the sinusoidal peak amplitude, so twice for each phase in one cycle of operation. At other instants when the sinusoidal magnitude is greater, the inverter exhibits active vector switching states. Using minimum /maximum utility for the three phase sinusoidal its upper and lower wrapper waveforms are compared along side the same carrier to engender shoot through pulses for the positive and negative carrier peak values respectively, which added using OR gate circuit.

# 4. SIMULATION RESULTS AND DISCUSSION

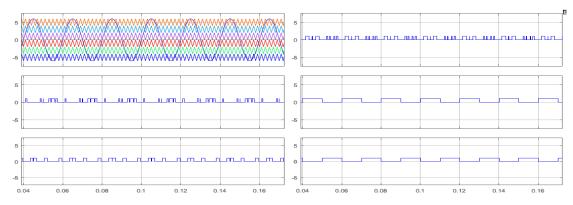

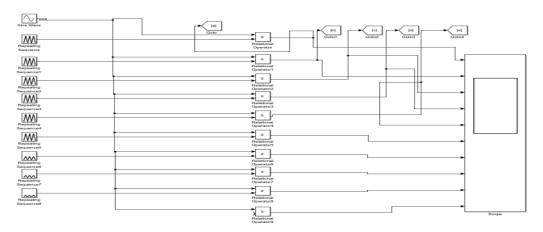

To validate the performance of novel 11-level proposed inverter topology was simulated using matlab17a. The IGBT control switches are equipped for this novel proposed 11-level 12 switch inverter, which is controlled by multicarrier sinusoidal pulse width modulation technique. The simulation of novel 11-level inverter topology with reduced switches is shown in Figure 4.

Figure 4. Simulink model of 11-level inverter circuit

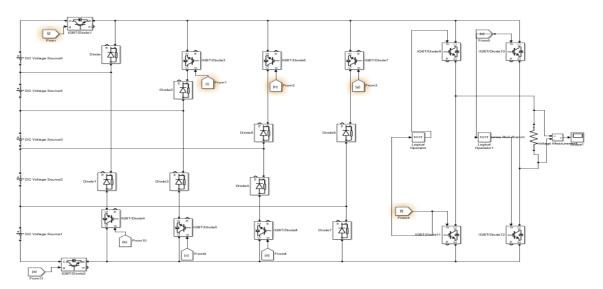

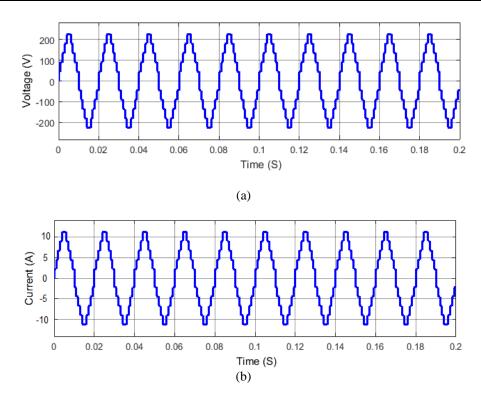

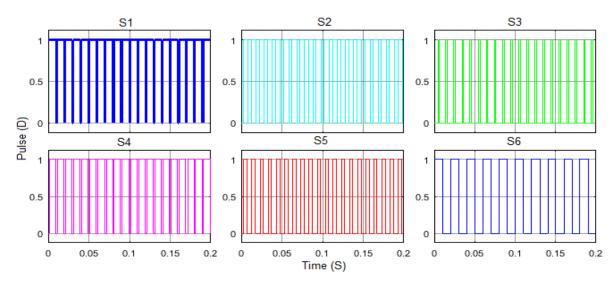

The simulink model of multicarrier sinusoidal pulse width modulation technique is shown in Figure 5, which is used to control proposed 11-level inverter. The Figure 6 shows the proposed 11-level inverter output voltage with 209.5V and output current of 9.46%. The switching pulse generation for proposed inverter switches S1-S6 using multicarrier SPWM is shown in Figure 7.

Figure 5. Simulink diagram of multicarrier sinusoidal pulse width modulation technique

Figure 6. Proposed 11-level Inverter (a) Output voltage (b) Output current

Figure 7. Switching pulse generation using multicarrier SPWM

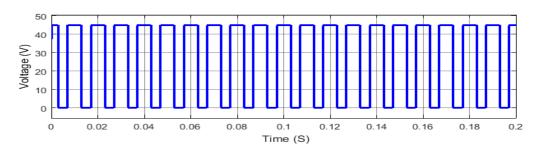

Figure 8. Voltage across the switch-6 of proposed inverter

3542 □ ISSN: 2088-8708

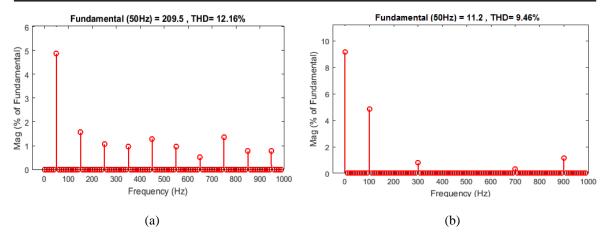

Figure.9. THD Analysis of Proposed System (A) Output Voltage (B) Output Current

Voltage across the switch-6 of proposed inverter is shown in Figure 8. And the Figure 9 shows THD analysis of proposed novel 11-level inverter system, in that THD for output voltage of 12.16% and for current THD of 9.46%.

#### 5. CONCLUSION

Design and simulation of transformerless split inductor based novel 11-level inverter power circuit with high consistency and with minimised THD has been presented in this paper. The proposed inverter features low voltage stress on switching device and constant common-mode voltage, which exists in the traditional 11-level inverter power circuit structure. At the same time, it avoids the shoot-through state condition and current control of inverter attained by multicarrier SPWM, which guarantee for minimisation of THD of the proposed system, which is 12.16% for voltage and 9.46% for current. The proposed inverter can achieve high efficiency, low cost, low leakage current and high reliability to satisfy the requirements of the transformerless split inductor based inverter.

# REFERENCES

- [1] SamirKouro, Pablo Lezana, Mauricio Angulo and José Rodríguez, "Multicarrier PWM with Dc-Link Ripple Feedforward Compensation for Multilevel Inverters", *IEEE Transactions on Power Electronics*, vol. 23, no.1, January2010.

- [2] S. Mohamed Yousuf, P. Vijayadeepan, Dr. S. Latha, "The Comparative THD Analysis of Neutral Clamped Multilevel Z-source Inverter Using Novel PWM Control Techniques", *IJMER*, vol. 2, no. 3, pp. 1086-1091, May-June 2012

- [3] Huafeng Xiao, ShaojunXie, Chen Yang, "Transformerless Split-inductor Neutral pointclamped Three-level PV Grid-Connected Inverter", *IEEE Energy Conversion congress and Exposition (ECCE)*, pp. 2929-2936, 2010.

- [4] Bharatiraja, C., Raghu, S., Rao, P., Paliniamy, K.R.S., "Comparative Analysis of different PWM Techniques to Reduce the Common Mode Voltage in Three-level Neutral-point-clamped Inverters for Variable speed Induction Drives", *International Journal of Power Electronics and Drive Systems*, vol. 3, no. 1, pp. 105-116, March 2013.

- [5] R. Palanisamy, K. Vijayakumar, Komari Nikhil, Madhumathi Iyer, Ramachandar Rao, "A Proposed SVM for 3-level Transformer-less Dual Inverter Scheme for Grid Connected PV System", *Indian Journal of Science and Technology*, vol. 9, no. 42, Nov. 2016.

- [6] Y. Cai, C. Wang, F. Zhao, and R. Dong, "Design of a High-frequency Isolated DTHB cLLC Bidirectional Resonant DC-DC Converter", in *Proc. IEEE Conf. Transp. Electrification Asia-Pac.*, 2014, pp. 1-6.

- [7] D. Y. Kim, J. K. Kim, and G.-W. Moon, "A Three-level Converter with Reduced Filter size using two Transformers and Flying Capacitors", *IEEE Trans. Power Electron.*, vol. 28, no. 1, pp. 46-53, Jan. 2013.

- [8] R. Palanisamy and K. Vijayakumar, "Maximum Boost Control for 7-level z-source cascaded h-bridge inverter", International Journal of Power Electronics and Drive Systems, vol. 8, no. 2, June 2017.

- [9] Poh Chiang Loh, Feng Gao, FredeBlaabjerg, and Sokweilim, "Operational Analysis and Modulation Control of Three Level Z-Source Inverters with Enhanced Output Waveform Quality", *IEEE Transaction on Power Electronics*, vol. 24, no. 7, July 2010.

- [10] R. Palanisamy, A.U Mutawakkil, K. Vijayakumar, "Hysteresis SVM for Coupled Inductor z Source Diode Clamped 3-level Inverter based grid Connected PV System", *International Journal of Power Electronics and Drive Systems*, vol. 7, no. 4, Dec 2016.

- [11] H. Shinohara, K. Kimoto, T. Itami, T. Ambou, C. Okado, K. Nakajima, S. Hojo, K. Owada, M. Kuniyoshi, and Y. Sato, "Development of a Residential use, Utility Interactive PV Inverter with Isolation Transformer-less Circuit-Development Aspects", in *Proc. IEEE Photovolt. Spec. Conf.*, 2009, pp. 1216-1218.

- [12] E. Gubra, P. Sanchis, A. Ursua, J. Lopez, and L. Marroyo, "Ground Currents in Single-phase Transformerless Photovoltaic Systems", *Prog. Photovolt: Res. Appl.*, pp. 629-650, May 2009.

- [13] O. Lopez, R. Teodorescu, F. Freijedo, and J. Doval-Gandoy, "Eliminating ground current in a Transformerless Photovoltaic Application", in *Proc. IEEE Power Eng. Soc. Gen. Meet.*, pp. 1-5, Jun. 2009.

- [14] T. Kerekes, R. Teodorescu, and M. Liserre, "Evaluation of Three-phase Transformerless Photovoltaic Inverter Topologies," *IEEE Trans. Power Electron.*, vol. 24, no. 9, pp. 2202-2211, Sep. 2012.

- [15] H. F. Xiao and S. J. Xie, "Leakage Current Analytical Model and Application in Single-phase Transformerless Photovoltaic Grid-connected Inverter", IEEE Trans. Electromagn. Compat. vol. 52, no. 4, pp. 902-913, Nov. 2010.

- [16] Palanisamy, R., Vijayakumar, K., Bagchi, A., Gupta, V., Sinha, S., "Implementation of Coupled Inductor based 7-Level Inverter with Reduced Switches", *International Journal of Power Electronics and Drive Systems*, vol. 8, no. 3, pp. 1294-1303, 2017.