## EXPLOITING FRAME COHERENCE IN REAL-TIME RENDERING FOR ENERGY-EFFICIENT GPUS

## Martí Anglada Sánchez

Doctor of Philosophy

Department of Computer Architecture Universitat Politècnica de Catalunya

Advisors: Joan-Manuel Parcerisa, Antonio González

March, 2020 Barcelona, Spain

## Abstract

The computation capabilities of mobile GPUs have greatly evolved in the last generations, allowing real-time rendering of realistic scenes. However, the desire for processing even more complex environments clashes with the battery-operated nature of the devices integrating these kind of GPUs, such as smartphones and tablets, for which users expect long operating times per charge and a low-enough temperature to comfortably hold them. Consequently, improving the energy-efficiency of mobile GPUs is paramount to fulfill both performance and low-power goals. Previous works determined that the work of the processors from within the GPU and, notably, their accesses to off-chip memory are the main sources of energy consumption in graphics workloads. Yet most of this energy is spent in redundant computations, as the high frame rate required to produce smooth animations results in a sequence of extremely similar images.

The goal of this thesis is to improve the energy-efficiency of mobile GPUs by designing microarchitectural mechanisms that leverage frame coherence in order to reduce the redundant computations and memory accesses inherent in graphics applications.

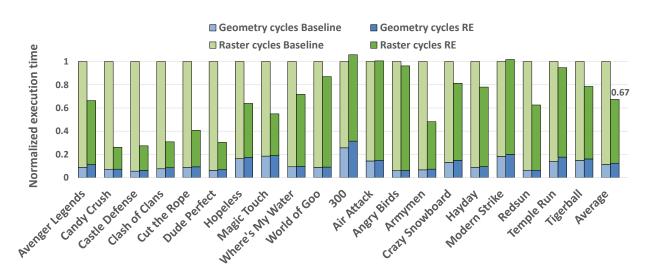

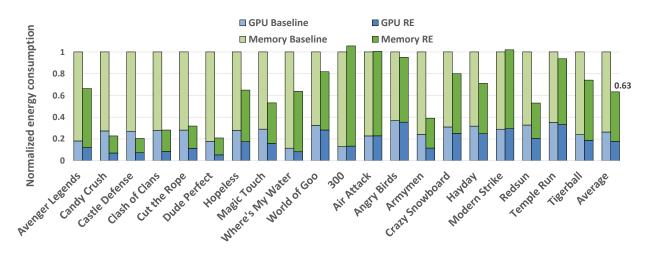

Firstly, we focus on reducing redundant color computations. Mobile GPUs typically employ an architecture called Tile-Based Rendering, in which the screen is divided into multiple tiles that are independently rendered in on-chip buffers, thus reducing memory bandwidth. An analysis of popular Android applications reveals that it is common that more than 80% of the tiles produce exactly the same output between consecutive frames. We propose Rendering Elimination, a mechanism that accurately determines such occurrences by computing and storing signatures of the inputs of all the tiles in a frame. If the signatures of a tile across consecutive frames are the same, the colors computed in the preceding frame are reused, saving all computations and memory accesses associated to the rendering of the tile. Using commercial Android applications and state-of-the-art cycle-accurate simulators and models, we show that Rendering Elimination vastly outperforms related memoization schemes found in the literature, achieving a reduction of energy consumption of 37% and execution time of 33% with minimal overheads.

Next, we focus on reducing redundant color computations of fragments that will eventually not be visible. In real-time rendering, objects are processed in the order they are submitted to the GPU by the application, which usually causes that the results of previously-computed objects are overwritten by new objects that turn out to be closer to the observer and, therefore, occlude them. This phenomenon occurs because visibility is resolved on-the-fly along with the rendering process. Consequently, whether or not a particular object will be occluded is not known until the entire scene has been processed. Based on frame coherence and, therefore, the fact that visibility tends to remain constant across consecutive frames, we propose Early Visibility Resolution, a mechanism that predicts visibility based on information obtained in the preceding frame. Early Visibility Resolution first computes and stores the depth of the farthest visible point after rendering each tile. Whenever a tile is rendered in the following frame, primitives that are farther from the observer than the stored depth are predicted to be occluded, and processed after the ones predicted to be visible. Additionally, this visibility prediction scheme is used to improve Rendering Elimination's equal tile detection capabilities by not adding primitives predicted to be occluded in the signature. With minor hardware costs, Early Visibility Resolution is shown to provide a reduction of energy consumption of 43% and execution time of 39%.

Finally, we focus on reducing computations in tiles with low spatial frequencies. Current GPUs produce pixel colors by sampling triangles once per pixel and performing color computations on each sampling location. However, an analysis of popular Android applications reveals that most regions of the screen do not include sufficient detail to require such high sampling rates, which leads to a significant amount of energy wasted computing the same color for neighboring pixels. Given that frame coherence implies that spatial frequencies are maintained across frames, we propose Dynamic Sampling Rate, a mechanism that analyzes the spatial frequencies of tiles once they have been rendered and determines the lowest sampling rate that maintains image quality, which is applied in the following frame. Results show that Dynamic Sampling Rate significantly reduces processor activity, yielding energy savings of 40% and speedups of 1.68x by only adding a small hardware unit to evaluate the spatial variations of a tile.

## Acknowledgements

Haré todo lo que pueda y un poco más de lo que pueda, si es que eso es posible. Y haré todo lo posible e incluso lo imposible, si también lo imposible es posible.

- Mariano Rajoy

Even though I have read countless theses during the past few years, I have always smiled when stumbling upon an acknowledgements section and experiencing the joy left in a few paragraphs by a PhD candidate ecstatic to finish, dreaming of the day I would sit down to write such lines. Unbelievably, the moment has finally come to say:

I am extremely grateful to have had Professors Antonio González and Joan-Manuel Parcerisa as advisors. Thank you for everything you have taught me, for your motivation, for your guidance, for your patience and for the opportunity to have worked with you.

I will always hold a special place in my mind for Professor Ramon Canal for introducing me to the ARCO group and accompanying me in my first research steps and my first paper presentation.

I would also like to thank the colleagues with whom I have shared lab during these years. Thank you to the ones that graduated before me (Gem, Martí, Hamid and Reza) and showed me all the different lights that there are at the end of the tunnel. Thank you Jose Maria for the titanic task of having pioneered the graphics line of research in the group and thank you Enrique for being my unofficial mentor and providing me with all the help I could have wished for. Thanks to the colleagues that will graduate alongside me (Marc, Josué, Franyell and Albert) for having kept me sane by sharing the same journey of ideas that do not work, painful rejects and the ying-yang of research: coffee and beer. And a selfish thank you to the future of the group (Dennis, Raúl, Pedro, Jorge and Mehdi) for putting a mirror in front of me and involuntarily revealing me all the road I had already walked; I wish you a very successful PhD. Finally, I would like to thank Diya for having taken over the baton of graphics research and having let me test the waters in the advising world; I hope you manage to awe everyone with your work.

An endless thank you to the people that have cheered me and helped me evade from the PhD routine: thanks to the amazing Barcelona MtG community for infusing me with the desire to continuously thrive and discover, specially to my Nucli friends with whom I have shared victories, lessons and banters. And thanks to Alberto and Àlex for our eye-opening symposiums, which cemented the true purpose of research.

Thank you to my family for their unflinching support and care: none of this would have been

possible without your words of wisdom and esteem.

And the biggest thank you goes to the person who has done the most heavy lifting during these years and, extraordinarily, a little bit of everything listed above. Kiona, you alone have managed to turn the PhD years into the best years of my life. Now, let us enjoy the rest of the best years of our lives.

$\mathbf{7}$

# Contents

| 1        | Intr | roduction                                                                                     | 19 |

|----------|------|-----------------------------------------------------------------------------------------------|----|

|          | 1.1  | The mobile Graphics Processing Unit: the driving force behind contemporary enter-<br>tainment | 19 |

|          | 1.2  | Problem statement                                                                             | 21 |

|          | 1.3  | Thesis objective and related work                                                             | 24 |

|          |      | 1.3.1 Reducing redundant colors across frames                                                 | 25 |

|          |      | 1.3.2 Reducing overshading                                                                    | 27 |

|          |      | 1.3.3 Reducing redundant colors within a frame                                                | 30 |

|          | 1.4  | Thesis contributions                                                                          | 32 |

|          |      | 1.4.1 Rendering Elimination                                                                   | 32 |

|          |      | 1.4.2 Early Visibility Resolution                                                             | 33 |

|          |      | 1.4.3 Dynamic Sampling Rate                                                                   | 33 |

| <b>2</b> | Bac  | ekground: Tile-Based Rendering                                                                | 35 |

|          | 2.1  | The Application Stage                                                                         | 36 |

|          | 2.2  | The Geometry Stage                                                                            | 37 |

|          | 2.3  | The Raster Stage                                                                              | 42 |

| 3        | Exp  | perimental Methodology                                                                        | 49 |

|          | 3.1  | Simulation Infrastructure                                                                     | 49 |

|          |      | 3.1.1 Improvements to the baseline infrastructure                                             | 52 |

|          | 3.2  | Benchmark Set                                                                                 | 53 |

#### CONTENTS

| 4 | Rer | ndering | g Elimination                                                                         | 59 |

|---|-----|---------|---------------------------------------------------------------------------------------|----|

|   | 4.1 | Early   | Discard of Redundant Tiles                                                            | 60 |

|   |     | 4.1.1   | Rendering Elimination Overview                                                        | 60 |

|   |     | 4.1.2   | Implementation Requirements                                                           | 61 |

|   |     | 4.1.3   | Incremental CRC Computation                                                           | 61 |

|   |     | 4.1.4   | Table-Based CRC Computation                                                           | 62 |

|   |     | 4.1.5   | Tile Inputs Bitstream Architecture                                                    | 62 |

|   | 4.2 | Imple   | mentation                                                                             | 64 |

|   |     | 4.2.1   | Signature Unit Architecture                                                           | 64 |

|   |     | 4.2.2   | Compute CRC Unit and Accumulate CRC Unit                                              | 66 |

|   |     | 4.2.3   | Transaction Elimination                                                               | 68 |

|   | 4.3 | Exper   | imental Results                                                                       | 69 |

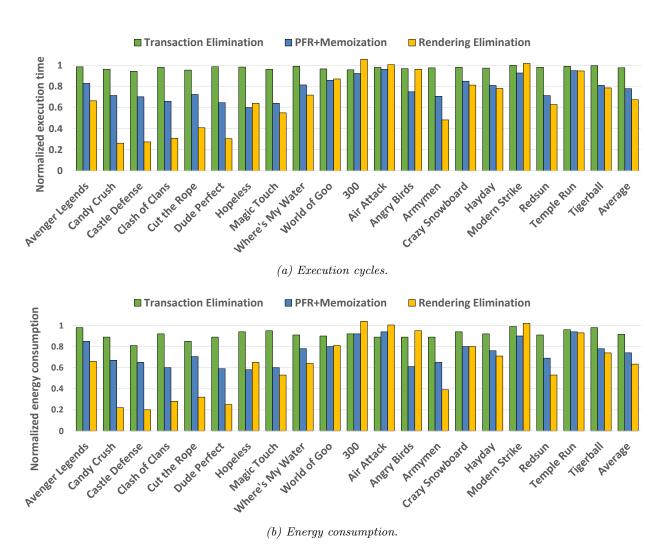

|   |     | 4.3.1   | Rendering Elimination compared to Fragment Memoization and Transaction<br>Elimination | 72 |

|   | 4.4 | Concl   | usions                                                                                | 74 |

| 5 | Ear | lv Vis  | ibility Resolution                                                                    | 77 |

|   | 5.1 | •       | Detection of Occluded Primitives                                                      | 78 |

|   |     | 5.1.1   | WOZ Primitives                                                                        | 79 |

|   |     | 5.1.2   | NWOZ Primitives                                                                       | 79 |

|   |     | 5.1.3   | Hybrid Scenes                                                                         | 80 |

|   | 5.2 | Remo    | ving Ineffectual Computations with EVR                                                | 81 |

|   |     | 5.2.1   | Overshading Reduction                                                                 | 81 |

|   |     | 5.2.2   | Rendering Elimination Improvement                                                     | 84 |

|   | 5.3 | Imple   | mentation                                                                             | 85 |

|   |     | 5.3.1   |                                                                                       | 86 |

|   |     | 0.0.1   | Layer Generator Table                                                                 | 00 |

|   |     | 5.3.2   | Layer Generator Table       Layer Buffer                                              | 87 |

|   |     |         |                                                                                       | 87 |

#### CONTENTS

|   | 5.4 | Experimental Results          | 38 |

|---|-----|-------------------------------|----|

|   | 5.5 | Conclusions                   | 92 |

| 6 | Dyr | namic Sampling Rate           | 95 |

|   | 6.1 | Sampling Rate Estimation      | 95 |

|   |     | 6.1.1 Frequency Analysis      | 95 |

|   | 6.2 | Dynamic Sampling Rate         | 98 |

|   | 6.3 | Heuristic Parameter Selection | 00 |

|   | 6.4 | Implementation                | 03 |

|   |     | 6.4.1 Pipeline Integration    | 03 |

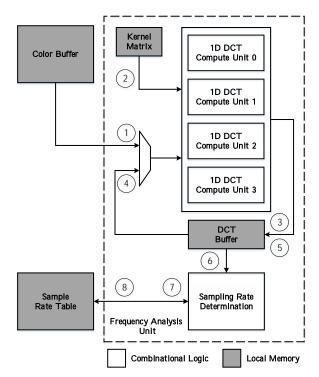

|   |     | 6.4.2 Frequency Analysis Unit | 04 |

|   | 6.5 | Experimental Results          | 06 |

|   | 6.6 | Conclusions                   | 10 |

| 7 | Con | nclusions 11                  | 11 |

|   | 7.1 | Conclusions                   | 11 |

|   | 7.2 | Open-Research Areas           | 12 |

# List of Figures

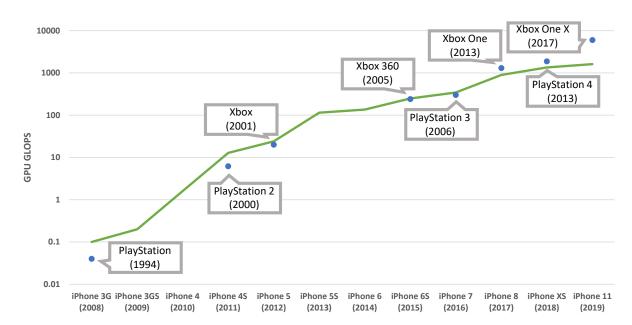

| 1.1  | Performance evolution of the GPU in Apple's iPhone smartphone series compared<br>to Sony's Playstation and Microsoft's Xbox console series. The release year of each<br>product is displayed in parentheses below its name                                                          | 21 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

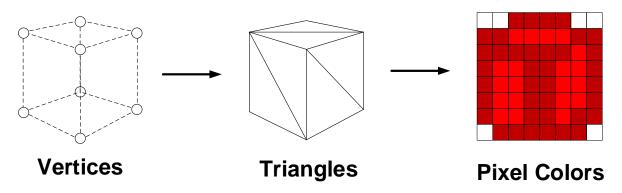

| 1.2  | Graphics Pipeline overview.                                                                                                                                                                                                                                                         | 21 |

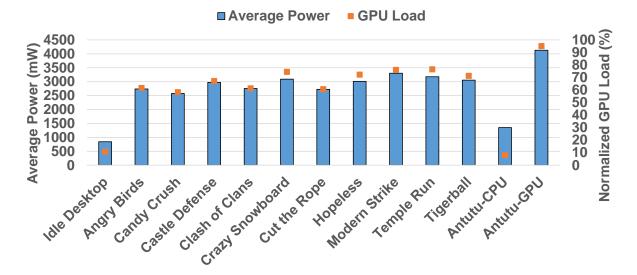

| 1.3  | Overall average power consumption. GPU load is normalized by weighting it by the ratio between operating and maximum GPU frequency. Data obtained using Trepn Profiler [59] for a Snapdragon 636 with connections disabled (Wi-Fi and Cellular Data) and minimum screen brightness. | 22 |

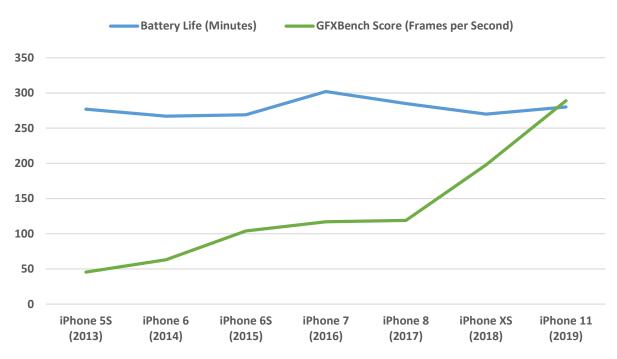

| 1.4  | Battery life and GFXBench score evolution of Apple's iPhone smartphone series                                                                                                                                                                                                       | 24 |

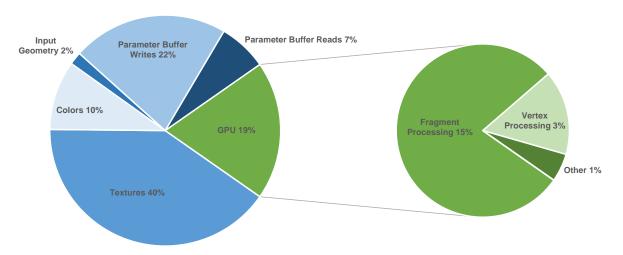

| 1.5  | Average energy breakdown of a Tile-Based Rendering system executing the graphics applications listed in Chapter 3                                                                                                                                                                   | 25 |

| 2.1  | Coarse view of the Graphics Pipeline.                                                                                                                                                                                                                                               | 36 |

| 2.2  | Geometry Pipeline                                                                                                                                                                                                                                                                   | 37 |

| 2.3  | Examples of primitives represented by a vertex stream. The subindex in each vertex corresponds to its submission order.                                                                                                                                                             | 38 |

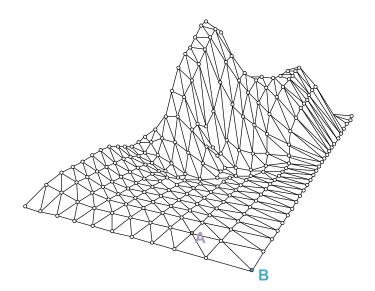

| 2.4  | 3D Model of a mountain hill. Vertex A is shared by 6 triangles. Vertex B is shared by 2 triangles                                                                                                                                                                                   | 39 |

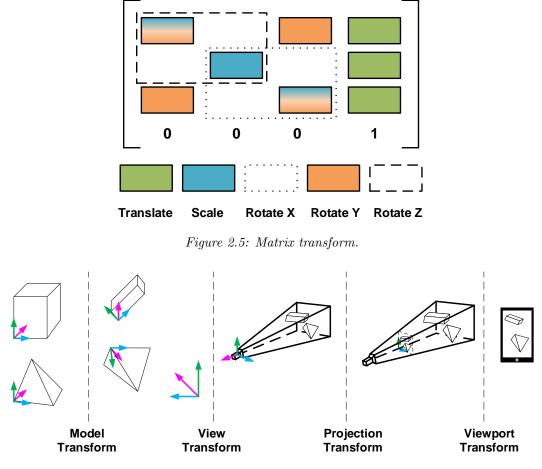

| 2.5  | Matrix transform.                                                                                                                                                                                                                                                                   | 40 |

| 2.6  | Vertex transforms.                                                                                                                                                                                                                                                                  | 40 |

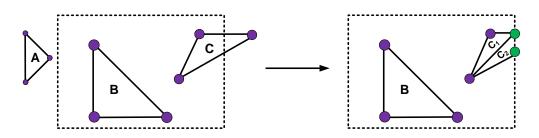

| 2.7  | Primitive A is clipped because it is completely outside the viewing volume. No change occurs to primitive B, as it is completely inside the viewing volume. Primitive C is partially outside, so new vertices are created, forming triangles $C_1$ and $C_2$                        | 41 |

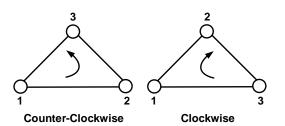

| 2.8  | Backface determination.                                                                                                                                                                                                                                                             | 41 |

| 2.9  | Raster Pipeline                                                                                                                                                                                                                                                                     | 42 |

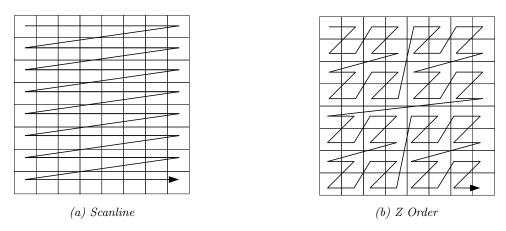

| 2.10 | Possible tile traversal orders.                                                                                                                                                                                                                                                     | 43 |

|      |                                                                                                                                                                                                                                                                                     |    |

#### LIST OF FIGURES

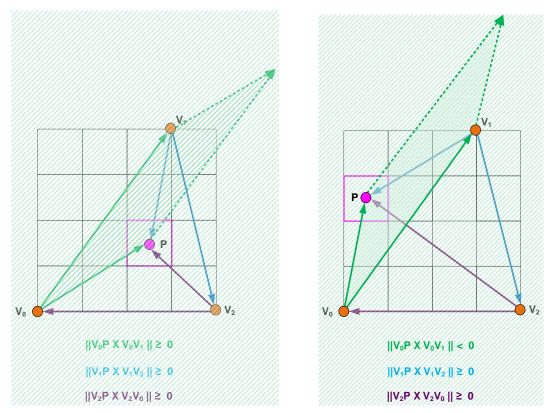

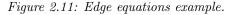

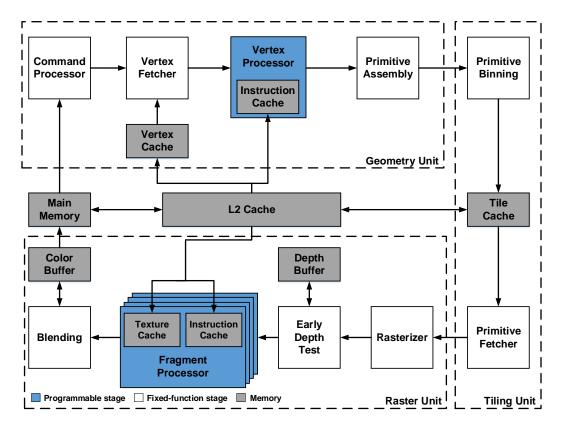

| 2.11 | Edge equations example                                                                                                                                                     | 44 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.12 | Barycentric coordinates computation.                                                                                                                                       | 45 |

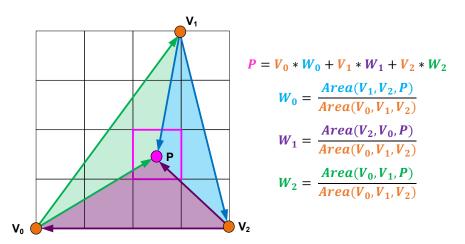

| 3.1  | Overview of the Teapot simulation infrastructure                                                                                                                           | 50 |

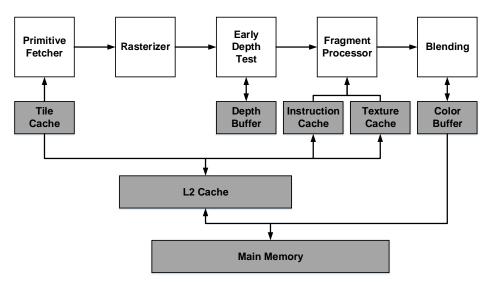

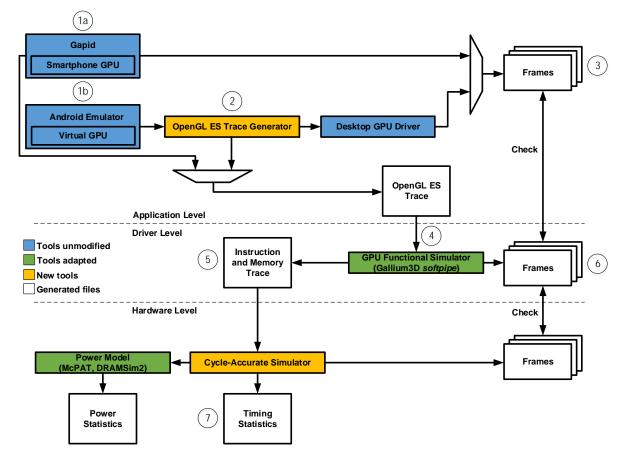

| 3.2  | Mali-400MP-like architecture modelled by the cycle-accurate simulator. $\ldots$                                                                                            | 51 |

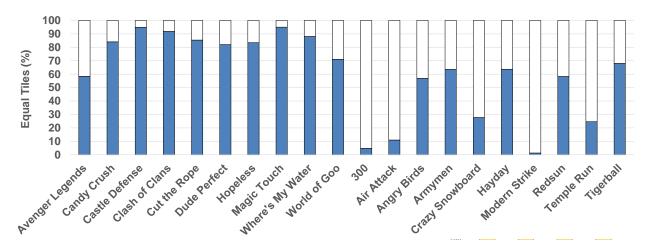

| 4.1  | Percentage of tiles producing the same result (the color is equal for all their pixels) as the preceding frame across 50 consecutive frames                                | 59 |

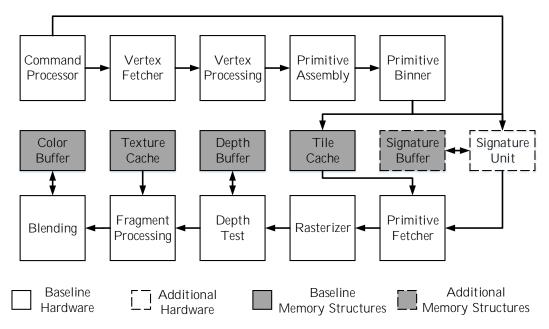

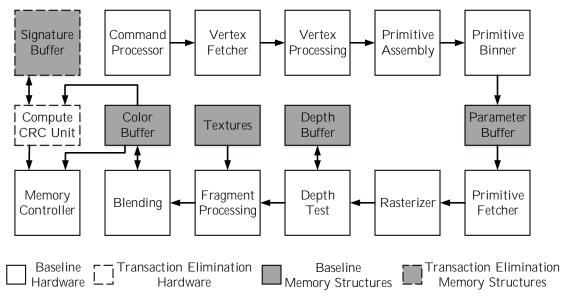

| 4.2  | Graphics Pipeline including Rendering Elimination                                                                                                                          | 60 |

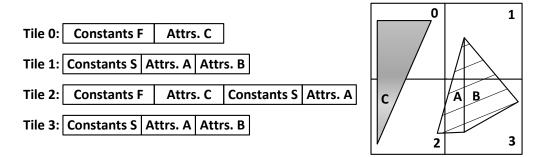

| 4.3  | Example of input message                                                                                                                                                   | 63 |

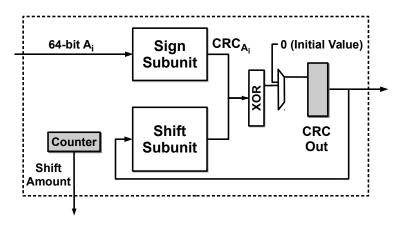

| 4.4  | Signature Unit block diagram                                                                                                                                               | 64 |

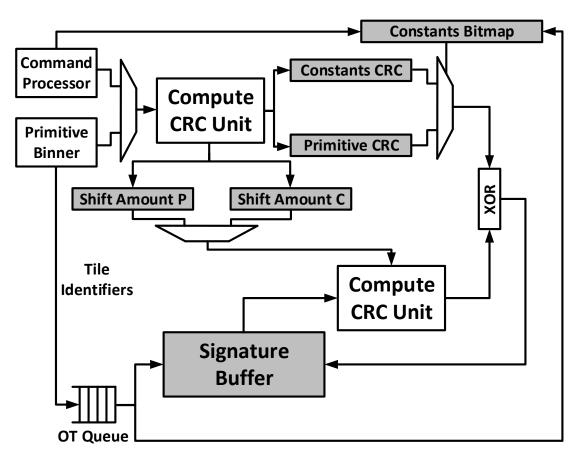

| 4.5  | Compute CRC Unit block diagram                                                                                                                                             | 66 |

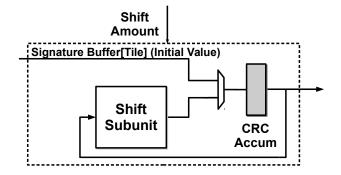

| 4.6  | Accumulate CRC Unit block diagram.                                                                                                                                         | 67 |

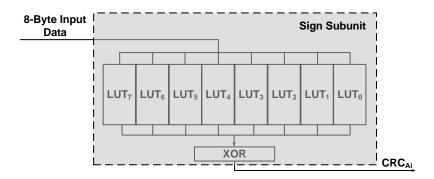

| 4.7  | Architecture of the Sign subunit.                                                                                                                                          | 67 |

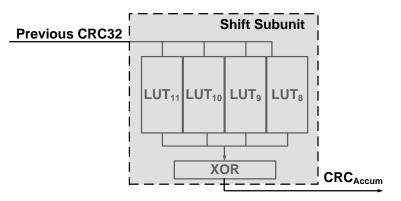

| 4.8  | Architecture of the Shift subunit.                                                                                                                                         | 68 |

| 4.9  | Graphics Pipeline including TE                                                                                                                                             | 69 |

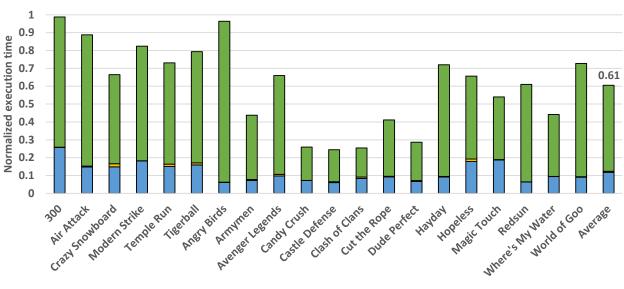

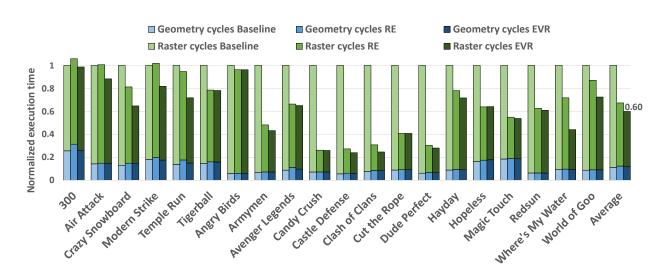

| 4.10 | Execution cycles of Rendering Elimination (RE) compared to the Baseline GPU                                                                                                | 70 |

| 4.11 | Energy consumption of Rendering Elimination (RE) compared to the Baseline GPU.                                                                                             | 70 |

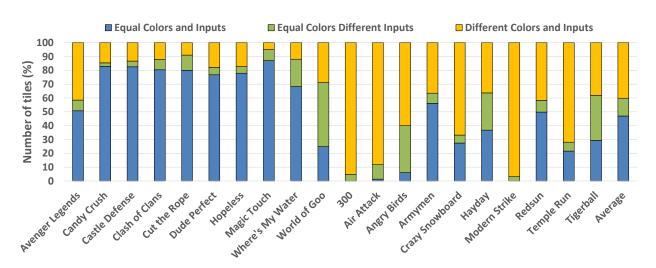

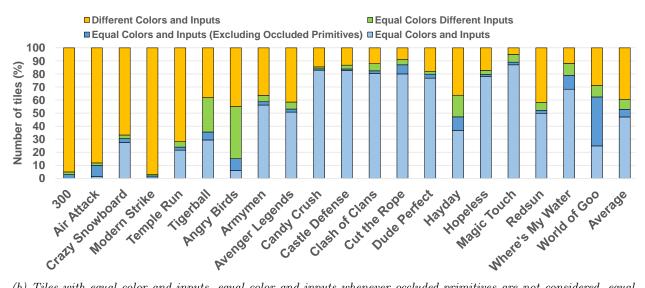

| 4.12 | Tiles with equal color and inputs, equal color and different inputs, and different color and inputs across neighboring frames.                                             | 72 |

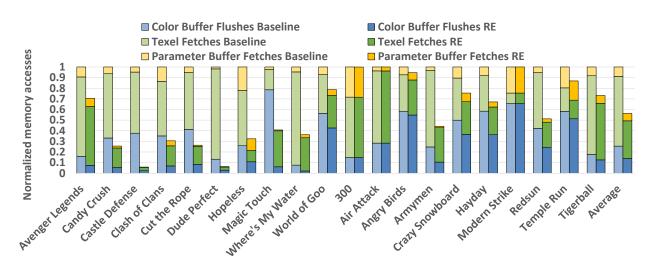

| 4.13 | RE memory bandwidth compared to baseline: Parameter Buffer and Texel fetches and Color Buffer flushes                                                                      | 73 |

| 5.1  | Effects of the baseline visibility resolution in the Graphics Pipeline                                                                                                     | 78 |

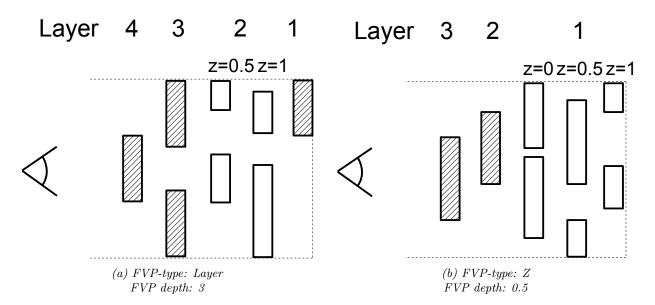

| 5.2  | FVP depth computation in tiles with both WOZ primitives (white) and NWOZ primitives (striped).                                                                             | 81 |

| 5.3  | Reordering algorithm example                                                                                                                                               | 83 |

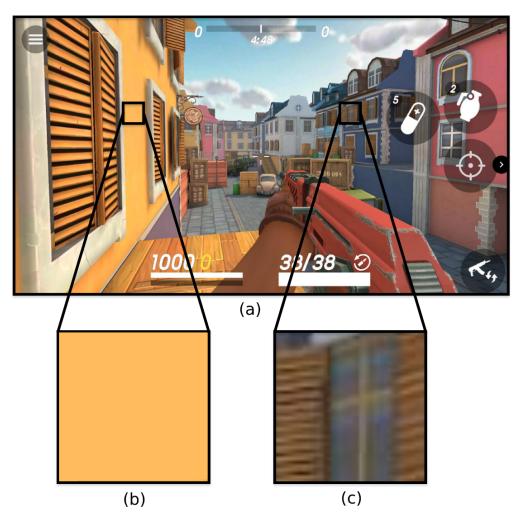

| 6.1  | Difference in level of detail across a frame. a) Frame of the game <i>Guns of Boom</i> . b)<br>Region with low level of detail. c) Region with significant level of detail | 96 |

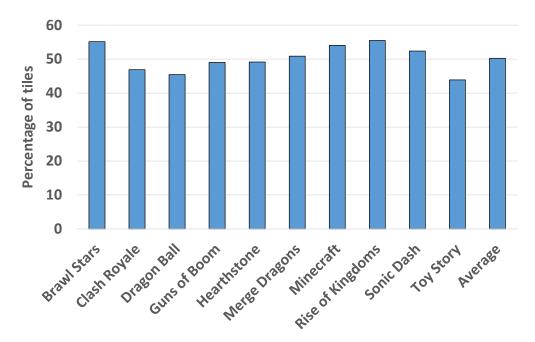

| 6.2  | Number of 16x16 tiles that can be sampled at a rate lower than one sample per pixel without generating per-tile visible artifacts. Section 6.3 describes the methodology employed for this categorization |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.3  | DCT basis functions for N=8 pixels                                                                                                                                                                        |

| 6.4  | MaxC determination example                                                                                                                                                                                |

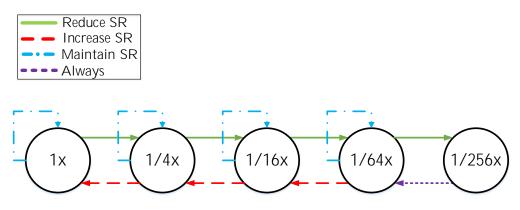

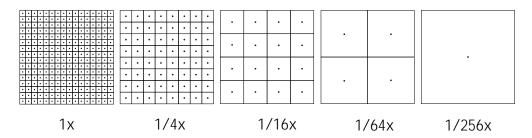

| 6.5  | Dynamic Sampling Rate Finite-State Machine                                                                                                                                                                |

| 6.6  | The five sampling rates considered in our experiments, from $1x$ (left) to $1/256x$ (right).100                                                                                                           |

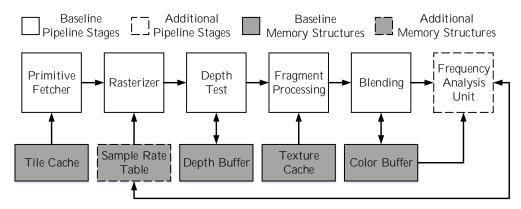

| 6.7  | Raster Pipeline with DSR                                                                                                                                                                                  |

| 6.8  | Frequency Analysis Unit overview                                                                                                                                                                          |

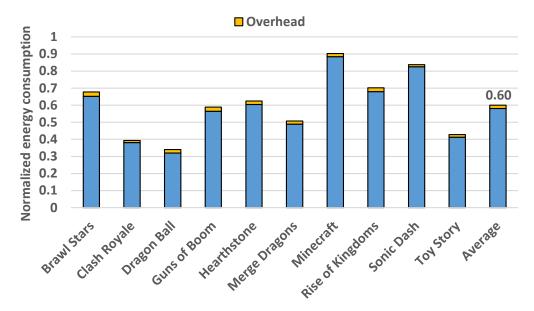

| 6.9  | Energy consumption of DSR compared to the Baseline GPU                                                                                                                                                    |

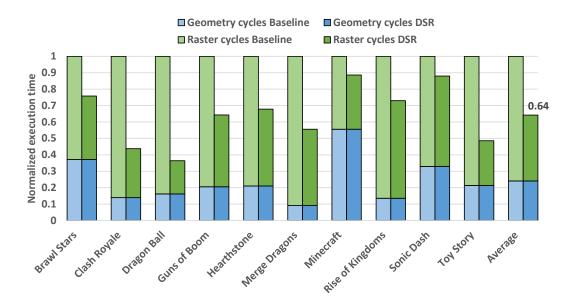

| 6.10 | Execution time of DSR compared to the Baseline GPU                                                                                                                                                        |

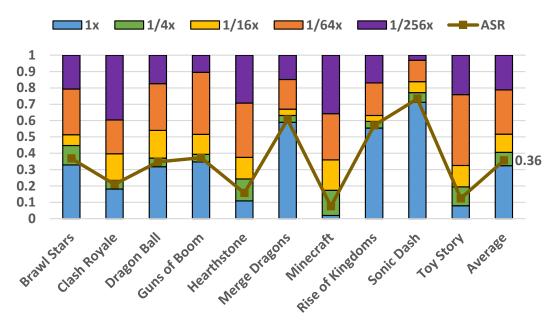

| 6.11 | Breakdown of sampling rates                                                                                                                                                                               |

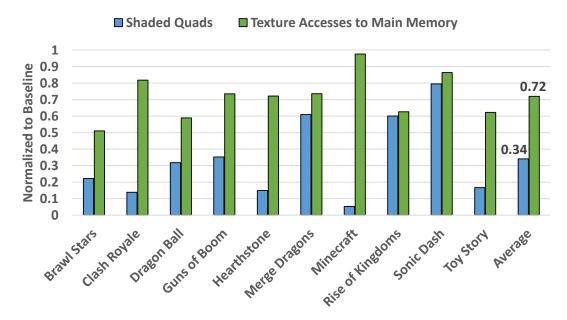

| 6.12 | Shader activity of Dynamic Sampling Rate compared to the Baseline GPU 108                                                                                                                                 |

# List of Tables

| 3.1 | GPU Simulation Parameters.                                                                                                                   | 52  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.2 | Benchmarks set.                                                                                                                              | 54  |

| 3.3 | Characterization of the geometry workload processed by the considered benchmarks.                                                            | 55  |

| 3.4 | Characterization of the fragment workload processed by the considered benchmarks.                                                            | 56  |

| 4.1 | Parameters considered in the experiments for the structures of Rendering Elimina-<br>tion, Transaction Elimination and Fragment Memoization. | 69  |

| 5.1 | Visibility casuistry                                                                                                                         | 84  |

| 5.2 | Parameters considered in the experiments for the structures of Early Visibility Res-<br>olution.                                             | 88  |

| 6.1 | Additional benchmarks for the image quality experiment.                                                                                      | 110 |

# Introduction

This chapter presents the motivation behind the research interest in mobile GPUs and defines the challenges in their energy-efficient designs. Then, the specific issues that this thesis addresses are introduced, with an outline of the proposals to solve them and a comparison against state-ofthe-art approaches. Finally, the main contributions of the thesis are listed.

# 1.1 The mobile Graphics Processing Unit: the driving force behind contemporary entertainment

Mobile devices have become essential for modern life [77]. They have greatly evolved in the past two decades and the so-called *Smartphones* are no longer tools for just calling or sending e-mails. Their broad connectivity, intuitive interfacing and remarkable computing capabilities allow for a wide variety of use cases, such as navigation or taking high-resolution pictures [21].

One of the paramount keys to the mobile revolution have been the *App Stores*, digital platforms to distribute third-party software to users [35]. These platforms tremendously streamlined the process of installing new programs, reducing it to a few taps in a screen. New applications were also extremely easy to discover, with clear browsing interfaces that sorted all the available offers into descriptive categories. Consequently, smartphones could add a myriad of functionalities, tailored to the individual needs of each user.

On the other side of the market, App Stores also provided advantages to developers, who experienced an abundant reduction in the overhead of releasing new applications: a centralized platform completely handled the connection with customers, software updates and, more importantly, monetization. Developers were rewarded for creating supply in a field full of user's demands (more than

100 billion dollars have been earned through Apple's App Store [7]), which led to a rapid increase in the number of available applications to download and purchase [78].

With an ever-increasing range of utilities, users began to perceive smartphones as tools that provided value in their daily lives. Soon, they were not only seen as useful but a necessity and their number of sales skyrocketed, becoming the technology that has been accepted the fastest in history [62]. Nowadays, smartphones have more than an 80% penetration rate in the majority of developed countries [19] and users prefer to carry out most of their ordinary activities on smartphone apps [18].

As societies have become accustomed to wear devices always connected to high-speed internet, their behavior has drastically changed, especially regarding entertainment [52]. In the smartphone era, immediacy and availability are favored above classical yearnings, such as product ownership. Consequently, streaming services are the way most of the media is consumed, from music to books or movies [55]. In particular, the ubiquity of smartphones has affected the video game industry the most.

The affordability and convenience of mobile devices in comparison with their console or PC counterparts have made them a video gaming phenomenon. As of 2019, a third of the world population plays games on their phones, spending more than 40% of their screen time on gaming applications [75]. The demographics have been hugely widened in the last few years and the traditional gender and age barriers have been blurred, with the average age of a mobile video gamer being 34 years old and the distribution between male and female users being nearly identical [76]. The video game market is extremely successful, responsible of the 76% of the overall app earnings and generating triple the revenue of the box office worldwide [74].

The industry has quickly adapted to these trends. On the one hand, software developers are continuously creating gaming mechanics that fit within what mobile technology provides. Smartphones have proven to be a very good interface thanks to their motion sensors and touch screens, which are a great way for interacting in dynamic and intuitive ways. Ease of control along with level designs that lend themselves to short bursts of gameplay have created the boom of the so-called *casual games* [44]: games without complex rules systems that can be played in the midst of day-to-day life, such as in the public transportation or in a break in the workplace. Developers have also managed to integrate geolocalization and cameras, smartphone-only features that were originally only functional, into completely revolutionary gaming experiences [61]. Nevertheless, studios have begun to successfully translate the traditional video game concept to mobile devices: rich scenes with detailed environments that can be interacted with intricate systems.

High-quality mobile graphics have become possible due to the incorporation of powerful Graphical Processing Units (GPUs). The release of the original iPhone in 2007 popularized a user interface design that required a dedicated graphics accelerator to enable its tactile direct manipulation interactions, such as pinch-to-zoom or inertial scrolling [36]. With smartphones integrating GPUs, a new era of mobile gaming started, where sophisticated applications could be rendered in real time. Semiconductor companies have consistently improved the capabilities of GPUs, achieving a performance evolution much faster than the one seen in previous decades with video game consoles. Figure 1.1 shows the performance in GFLOPS of the yearly releases of the iPhone, and compares them with the flagship consoles of Sony and Microsoft, the PlayStation and the Xbox. As can be

Figure 1.1: Performance evolution of the GPU in Apple's iPhone smartphone series compared to Sony's Playstation and Microsoft's Xbox console series. The release year of each product is displayed in parentheses below its name.

seen, smartphones have had the same GFLOPS increase in 10 years as video game consoles in 20. The performance gap between the two platforms is now closer than ever, with the iPhone 11 having an operation count similar to consoles at the start of the latest generation.

#### 1.2 Problem statement

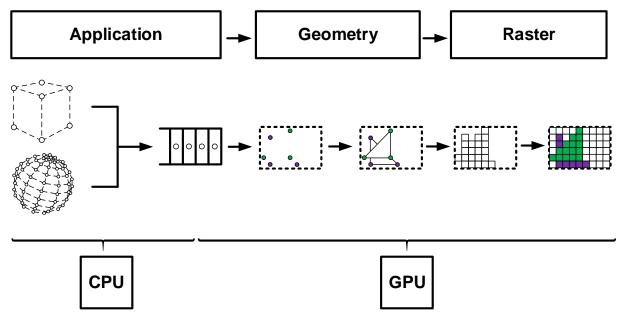

The Graphics Pipeline is the series of steps taken in real-time graphics to generate twodimensional images given a three-dimensional scene. Figure 1.2 gives an overview of the pipeline. The geometry of the three-dimensional objects is modeled with a set of vertices, which are first processed, assembled into flat polygons (normally triangles) and projected into the screen plane. Triangles are then rasterized into fragments, pixel-sized regions of triangles, upon which a final color is computed and written in main memory to be displayed.

The aforementioned stages of the pipeline are accelerated in current systems by a GPU, the evolution of which has brought great improvements in visual quality. Increasing the performance of the hardware has allowed for more vertices to be processed, which translates into more detailed models. Additional computational power and memory bandwidth have been the basis for more complex shading models to apply in each fragment, which create realistic light and texture effects.

However, being able to sustain a pleasant experience comes at a great energy cost. Current mobile devices have adopted 1080p resolution, where screens are composed of 1920 pixels horizon-tally and 1080 pixels vertically. This implies that the color of more than 2 million fragments needs to be computed to render a single frame. Additionally, several tens of frames need to be displayed

Figure 1.2: Graphics Pipeline overview.

Figure 1.3: Overall average power consumption. GPU load is normalized by weighting it by the ratio between operating and maximum GPU frequency. Data obtained using Trepn Profiler [59] for a Snapdragon 636 with connections disabled (Wi-Fi and Cellular Data) and minimum screen brightness.

within a second for the human eye to perceive smooth motion. Nowadays, users expect games to produce fluid animations, for which a frequency of at least 60 frames per second (FPS) is required [51].

Figure 1.3 shows the average power consumption and GPU load for three types of applications. The first is the Android homescreen (*Idle Desktop*), the main screen of the most popular mobile operating system, consisting in stationary icons and widgets organized in a grid. Next, there is a series of smartphone games (*Angry Birds* to *Tigerball*), selected as representatives of the mobile landscape due to their large number of downloads in the App Stores and their game play diversity. The last application shown is the Antutu benchmark [6], a well-known benchmarking tool to rank smartphone performance in several categories, such as memory writing speed or multithreading. Two different component benchmarks are selected from the suite: the CPU test (*Antutu-CPU*), comprised of several tasks like FFT processing, and the GPU test (*Antutu-GPU*), which renders a 3D scene containing multiple real-rime lights. As it can be seen, even applications with simple

scenes such as the popular match-three game *CandyCrush* incur a substantial amount of GPU load, which drives an amount of power comparable to a benchmark designed to stress the GPU. Additionally, the amount of power that these games require is significantly higher than applications that leave the GPU mostly idle, illustrated by the Android homescreen, and is twice as much as an application that only stresses the CPU. Consequently, the design of energy-efficient GPUs is a priority for smartphones.

Energy consumption is paramount in battery-operated devices, as it dictates their autonomy. For instance, the Xiaomi Redmi Note 6 Pro, the smartphone used to obtain the numbers in Figure 1.3, has a battery capacity of 15Wh when supplied its typical voltage of 3.85V. If any of the listed games, whose average power lies between 2.5W and 3.5W, were to be played in this device, its battery would completely be drained in less than 5 hours.

While smartphones have seen a huge performance increase in the last generations, battery technology has not improved at the same pace. The consequence has been a continuously-increasing gap between the complexity of the scenes that can be rendered and the time they can operate without needing a battery charge. This has put a lot of pressure into energy-efficient mobile GPU designs in order to sustain the additional computational capabilities without affecting battery life, one of the most desired smartphone features by consumers [25]. Figure 1.4 shows the battery life and performance increase for the last installments of the popular line of Apple iPhone measured by GFXBench's *T-Rex* benchmark. In this test, a 56-second scene filled with modern effects such as soft shadows or planar reflections is looped 30 times. Performance is measured by logging the number of frames rendered in each loop and keeping the lowest one. On the other hand battery life is measured by logging battery discharge across loops and extrapolating the number of minutes it would take to completely drain the device's battery. The results of these tests show that, while graphics performance has increased by a factor of more than 6x in the last generations, the battery life of the devices when executing these type of applications has remained somewhat constant.

Reaching the desired FPS goal at a low power budget is not only a requirement for battery life, but also for temperature control. Packages have a thermal ceiling that cannot be surpassed before they are destroyed [40]. However, the design of smartphones impedes the application of traditional cooling mechanisms. They are made extremely thin and light to fit in pockets and be comfortably worn, so they cannot incorporate the characteristic large fans present in desktop graphic cards. Furthermore, they are devised to be held in the palm of a single hand, which greatly restricts the area available to dissipate heat. The thermal constraints are also much stronger in mobile devices than in other computing systems such as desktops because their typical use cases imply having them in contact with the body and it must be guaranteed that their surface temperature is not unpleasant [82].

Previous research has found the GPU and, in particular, fragment processing and its accesses to main memory, to be the greatest source of energy consumption when running graphics applications [3, 12, 54]. Figure 1.5 shows, using the simulation infrastructure described in Chapter 3, a detailed breakdown of the contribution of the different components of the GPU-Memory system to the overall energy consumption. The results match the literature statements by depicting communication with main memory, and notably the texture fetches generated by the fragment processing stage as the main reason for energy drain. From within the GPU, the fragment processors are the components that consume the most, as the fragment workload generally exceeds the vertex and triangle workload

Figure 1.4: Battery life and GFXBench score evolution of Apple's iPhone smartphone series.

by more than two orders of magnitude.

However, most of this energy is spent in redundant operations. The high frame rate involved in creating smooth animations stems a succession of extremely similar images. This phenomenon, known as frame coherence, implies that a significant fraction of the inputs and outputs traversing the Graphics Pipeline in a particular frame are the same as in its preceding frame. In the next section, we outline three proposals to improve the energy efficiency of mobile GPUs by leveraging frame coherence to lessen redundancy in the most energy-consuming stage of the pipeline: fragment processing.

#### 1.3 Thesis objective and related work

The objective of this thesis is to improve the energy efficiency of mobile GPUs by reducing the redundant computations and memory accesses inherent in graphics applications. The thesis presents three approaches that leverage frame coherence by implementing simple hardware designs that collect information in a frame to guide the execution of the following one in a way that the overall energy consumption is lowered. The three techniques are applied on top of Tile-Based Rendering, a common pipeline organization in mobile devices that divides the screen into rectangular sections -tiles- and renders them in succession, allowing the storage of temporary values in on-chip buffers and avoiding their corresponding accesses to main memory.

The following subsections describe inefficiencies in the pipeline of current mobile GPUs and present the proposals of this thesis to enhance energy efficiency and their novelty over the existing

#### **1.3. THESIS OBJECTIVE AND RELATED WORK**

#### Main Memory Communication GPU

Figure 1.5: Average energy breakdown of a Tile-Based Rendering system executing the graphics applications listed in Chapter 3.

solutions in the literature.

#### 1.3.1 Reducing redundant colors across frames

The Graphics Pipeline in a TBR GPU is divided into two decoupled pipelines [49]: the Geometry Pipeline receives vertices and generates, after a set of transformations, output primitives (triangles) that are sorted into tile bins and stored into the main memory Parameter Buffer. After all the primitives have been sorted, the Raster Pipeline processes the tiles one at a time, fetching each tile's primitives, rasterizing each primitive into fragments, and shading and texturing each fragment to obtain a final pixel color. Once all the primitives of a tile have been processed, its resulting colors are stored in the Frame Buffer, the main memory region from which the image is read to be displayed in the screen.

Frame coherence implies that the outcome of most tiles is exactly the same between two consecutive frames, which means that a significant portion of the operations devoted to render a frame are redundant. Several previous works have attempted to exploit frame coherence in order to remove these ineffectual computations and memory accesses to improve energy efficiency.

Transaction Elimination [41] (TE) is a bandwidth saving feature included in the ARM Mali GPUs that detects identical tiles between the current frame being rendered and a previously rendered frame. TE computes a Cyclic Redundancy Check signature of the output colors of a tile and compares it with the signature of the same tile in the preceding frame. If the signatures are equal, the tile is considered to be redundant and is not flushed to the Frame Buffer. As communication with main memory is the greatest source of energy consumption, avoiding the color flushes to main memory yields significant energy savings.

Parallel Frame Rendering [9] (PFR) is another technique to reduce communication with main memory, focused on texture bandwidth. Due to frame coherence, the same textures are likely to be reused across frames. However, due to the large texture dataset within a frame, most textures have been evicted from the caches by the time they are required again. PFR divides the Raster Pipeline into clusters which process consecutive frames in parallel with a fraction of the original GPU resources. Under this organization, a single texture fetch can be reused among all clusters, typically 2, greatly reducing the number of memory accesses.

Arnau et al. proposed to employ memoization [8] to avoid not only the texture accesses but the complete processing of redundant fragments. A small hardware lookup table stores the color results of fragments along with a hash of their input as an address. Subsequent fragments form their signatures and check them against the signatures of the memoized fragments. In case of a hit, the fragment skips its processing and the color is reused. Because most redundancy resides between consecutive frames, the huge reuse distance makes impractical to store a frame's worth of signatures and output values. To help reduce the reuse distance, the memoization scheme is build on top of PFR, which unfortunately cuts in half the redundancy detection potential: even frames reuse values cached by the previous (odd) frame, but odd frames cannot because their previous-frame values are already evicted from the LUT by the time they are rendered.

Hardware memoization has also been used in Decoupled Shading [39], a proposal to separate shading from visibility determination to reduce the cost of processing complex effects such as motion and defocus blur, which require sampling over a 5D domain (lens aperture and shutter interval besides the pixel area). Despite the large number of samples required to compute these effects, the colors of the samples within the same aperture or interval are very similar. In this approach, shading is sampled at a much lower rate than visibility by mapping visibility samples to shading ones using a function that accounts for blurring effects. Additionally, by memoizing previously-shaded results, the number of processed fragments is further reduced by reusing values for the same location. However, decoupling visibility and shading requires significant changes in a TBR architecture due to the synchronization point in the middle of the pipeline execution which essentially couples the visibility determination and shading of pixels within a tile.

We make the observation that in a TBR GPU, primitives do not need to be discretized into fragments to know that the final result will be the same as in the preceding frame. Instead, by managing redundancy at a tile level, redundant tiles may be discovered much earlier than at fragment level and bypass the whole Raster Pipeline. Note that the Raster Pipeline computes the pixel colors using as inputs a set of primitives' attributes generated by the binning stage of the Geometry Pipeline plus a set of scene constants, so it knows all the input data required to render a tile when it starts processing it.

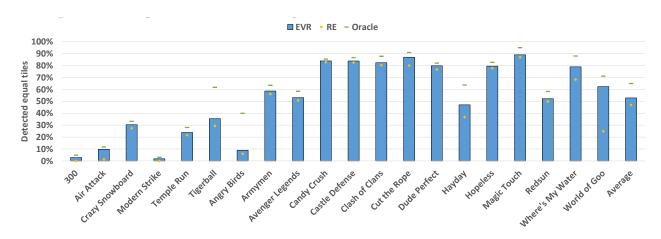

Based on the above observation, we propose Rendering Elimination (RE), a novel technique that employs the input data of a tile to anticipate if all of its pixels will have the same color as in the preceding frame, and to bypass the complete rendering of the tile. Since an entire frame of these input sets must be stored on-chip, they are compared by means of a signature. In parallel with the sorting of a primitive into tiles, RE computes on-the-fly the signatures of the tiles it overlaps and stores them in a local fixed-size on-chip buffer. Then, after the Geometry Pipeline has processed the frame, tiles are dispatched to the Raster Pipeline. For each tile, RE compares its current and preceding frame signatures and, if they match, all the rendering process is bypassed and the colors in the Frame Buffer are reused. Otherwise, the tile is rendered as usual.

By working at a much coarser grain than Fragment Memoization, RE can store on-chip all the frame signatures and detect all the available tile redundancy instead of just that of the even frames, which more than compensates for the marginal undetected redundancy at sub-tile level (our results show that RE almost doubles the amount of redundancy discovered). In addition, RE does not need to store output results because tile colors are reused from the Frame Buffer, thus saving storage and bandwidth. Besides this, while TE and Fragment Memoization each skip just a single stage of the Raster Pipeline (Color Buffer flush and Fragment Processing, respectively), RE completely skips all the Raster Pipeline stages. Additionally, unlike Decoupled Shading, implementing RE requires minimal changes to the common mobile graphics pipeline.

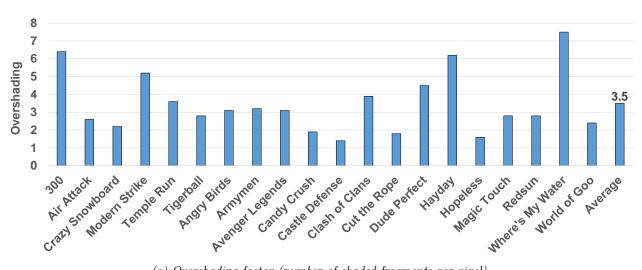

#### 1.3.2 Reducing overshading

The Graphics Pipeline is responsible for resolving the visibility problem: determining which surfaces and parts of surfaces are not visible from a certain point. In current GPUs, visibility of overlapping fragments is typically handled employing the Z Buffer, a memory region which stores the depth of the closest fragment to the camera for every pixel in the frame. Fragments perform an *Early Depth Test* before they are shaded: their depth is compared with the one stored in their same position and are only processed and written to the Frame Buffer if they are closer than the previously visible fragment. However, as GPUs process vertices in the order that they are submitted by the application and do not perform any type of sorting, it is common for previously-computed fragments to be occluded by newer fragments that turn out to be closer to the observer. This phenomenon is known as *overshading*, and leads to an important energy waste as the color of pixels is uselessly computed multiple times.

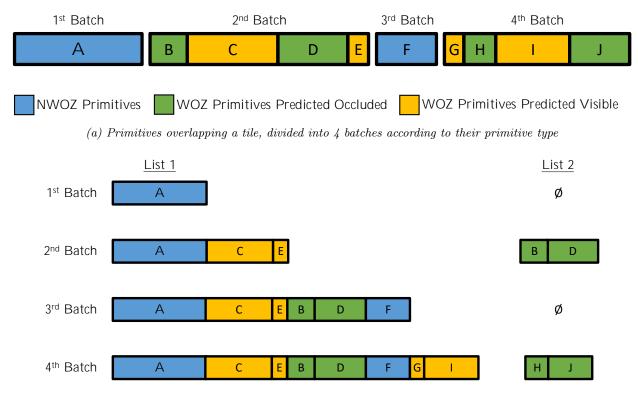

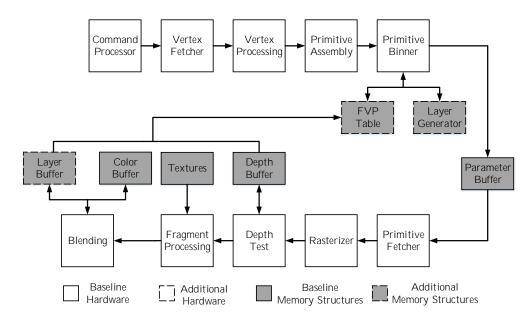

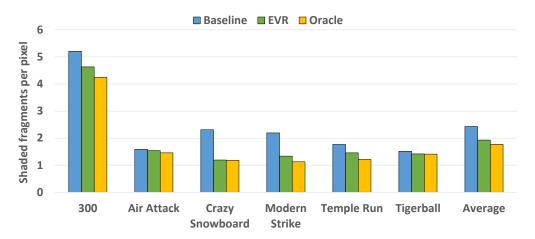

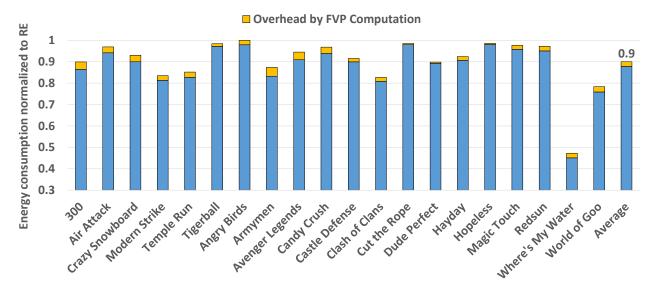

We propose Early Visibility Resolution (EVR), a mechanism to reduce overshading based on a per-tile visibility estimation in early stages of the pipeline. Within a tile, occluded primitives are the ones whose depth is farther away from the viewpoint than the farthest visible point in that tile. By virtue of frame coherence, visibility tends to remain very similar across consecutive frames: occluded primitives in a frame are prone to be occluded in the following frame as well. EVR obtains the depth of the farthest visible points (FVP) of each tile in a frame after they have been rendered, and uses these depths to predict the visibility of primitives in the next frame. Whenever a primitive is binned into a tile, its closest point to the camera is compared against the depth of the farthest visible point for that tile in the previous frame: if the former is farther, the primitive is predicted to be occluded for that tile, whereas if it is closer, the primitive is predicted to be visible.

We leverage this early visibility prediction scheme to reduce redundancy in a TBR Graphics Pipeline at two different granularities: First, at a fragment level, the effectiveness of the traditional Early Depth Test hidden fragment rejection is improved by processing primitives predicted to be occluded after those predicted to be visible. Second, at a tile level, the effectiveness of Rendering Elimination's redundant tile detection is significantly improved by ignoring primitives predicted to be occluded when computing similarities between tiles. By construction of both Early Depth Test and Rendering Elimination, mispredicting the visibility of a primitive does not generate any errors: on the one hand, reordered primitives still have to perform the Depth Test, which maintains

correctness of the result. On the other hand, a visibility change requires a change in the attributes of one or more primitives, which results in different signatures between frames and, consequently, the rendering of a tile.

Hidden surface removal, and an efficient solution to it in particular, is a fundamental problem in computer graphics, with an extensive literature spanning more than three decades.

The Hierarchical Z Buffer [30] is a variation of the baseline Z Buffer technique in which a depth pyramid is used to test visibility. The base level of the pyramid corresponds to the Z Buffer and higher levels are constructed by combining the depth of four pixels at the next lower level, typically by choosing the farthest one. Entire primitives can be discarded without accessing the Z Buffer by comparing their nearest depth against the values in higher levels in the pyramid. Our EVR proposal also compares the depth of primitives to a FVP depth, which would correspond to the top of the pyramid of the Hierarchical Z Buffer. However, the FVP depth contains final visibility information (the visibility after having shaded all the primitives in a frame) which allows, unlike the Z pyramid, to detect primitives that will be occluded by others processed later. Moreover, the FVP depth includes more information than just the top of the Z pyramid: the FVP abstraction allows EVR to also predict the visibility of primitives that do not use the Depth Test and instead are processed using the so-called Painter's Algorithm [46], where objects are processed in back-to-front order and displayed one over the other as if they were paint layers. EVR keeps track of the number of overlapping primitives within each tile that are processed in that manner using a counter named *Layer identifier*, which is used in the final FVP computation.

The concept of layers has been previously adopted in the context of occlusion culling, most notably in Depth Peeling [22], an algorithm that renders geometry multiple times. Each render pass processes only the fragments farther away from the closest depths in the previous pass and stores a new set of closest depths and colors, effectively peeling off the surface layer at each pass. After all the iterations have completed, all the generated layers are blended from back to front, guaranteeing correct transparency even for intersecting objects without the need to sort geometry. Recently, Andersson et al. [4] leveraged a two-layer representation of depths to avoid bandwidth spent in updating the Hierarchical Z Buffer. In a traditional pipeline with a Hierarchical Z Buffer, the coarser Depth Test is performed before rasterization to trivially accept or discard certain primitives, while the finer per-fragment Depth Test is performed before shading for all the non-trivial primitives. The results of the finer test may update one or more levels of the depth pyramid, which causes a feedback loop in the pipeline. This communication is undesirable because there may be a significant number of cycles of delay between the Hierarchical Buffer and the Depth Buffer, which increases the number of primitives passing the coarse test and, therefore, reducing its culling efficiency. In their approach, hierarchical tiles consist of one  $Z_{min}$  and a  $Z_{max}$  values per layer, which allows for depth information to be updated only during the coarse test and removing the feedback loop. In the work of Scheckel and Kolb [66], layers are used in combination with the alpha parameter to completely cull transparent fragments. It is common in 2D graphics applications to use the Painter's Algorithm to successively display objects stored in rectangular image buffers, which have their pixels completely transparent (their alpha component is set to 1) in areas outside the edges of the objects. This implies a significant energy waste in rasterizing and processing transparent fragments that do not contribute to the final color of the image. They propose to use min-max mipmaps to cull the completely transparent fragments. A pixel in a layer is completely opaque if its min value is 1 and it is completely transparent if its max value is 0. Every 4 consecutive pixels within a layer are combined into one to generate the subsequent layer, and a hierarchical algorithm classifies layer areas as opaque or transparent by recursively checking for maximum and minimum pixel values. Starting from the coarser level, if a pixel represents a fully opaque rectangular region, the related layer is processed by generating two triangles. Otherwise, the algorithm traverses the hierarchy to the next finer level. Unlike EVR, these layer-based approaches cannot combine visibility information of both primitives that use the Depth Test and ones that do not for a better visibility determination.

Computing visibility at a fragment level (known as image-precision [71]) is useful to solve certain problems, such as circular dependencies. However, resolving visibility at a coarser grain could reduce the number of computations needed. Occlusion queries [67] are a feature supported by modern GPUs in which the application asks for the number of visible fragments of simple geometry (bounding volumes, for instance) and the hardware replies by testing it with the current contents of the Depth Buffer. With Coherent Hierarchical Culling [11], queries are scheduled using a hierarchical representation of the scene. The number of queries can be minimized by applying them in large regions expected to remain occluded. Additionally, the entire hierarchy is not completely traversed each frame: by taking advantage of temporal coherence, the traversal starts from the visible regions in the preceding frame, which are predicted to be visible in the current one. N-Buffers [17] are a different representation of the depth hierarchy which allows querying within a shader program for the depth of a rectangular region of arbitrary size and position in constant time. An N-buffer is a set of textures of identical resolution where a pixel p in the *i*th level corresponds to the maximum depth within a square area of  $2^i \ge 2^i$  pixels around p. With this organization, it is possible to find the minimum depth in an arbitrary square area with only four texture accesses corresponding to four overlapping squares. While having a great potential to avoid the shading of occluded primitives, these queries involve a delay between issuing them and receiving the results, which greatly hinders performance. Furthermore, as with the Early Depth Test, in order for occlusion queries to perform well, both objects and queries must be sent in front-to-back order. EVR is transparent to the application in both axes: it requires neither synchronization nor ordering.

Several works perform additional auxiliary render passes to compute the depth of visible fragments and then execute the pass that shades them. Z-Prepass [14] is a software technique that draws the scene in two steps: first the geometry is rendered using null fragment shaders, that do not produce any color and are used to quickly fill the Z Buffer. Later, the geometry is rendered again with proper shaders, but now with perfect visibility information in-place, so that all occluded fragments can be discarded. The Hidden Surface Removal stage in PowerVR architectures [58] is a hardware version of Z-Prepass for TBR architectures. The geometry is processed only once, in order to bin all the primitives in the scene into tiles. Each tile is then rendered using two steps: first, visibility is resolved by using simple shaders and obtaining the depths of the closest fragment in each pixel. The second step fetches and rasterizes all the primitives of the tile again, but the Early Depth Test is able to cull most of the workload sent to the Fragment Processors. Saito and Takahashi [64] introduced the G-Buffer, per-pixel intermediate storage for geometry information, such as normals or screen coordinates, used to enhance fragment shading. In particular, the G-Buffer stores depth information, so a first render pass fills the G-Buffer while removing hidden surfaces and a second pass reads the contents of the G-Buffer to compute the color of each pixel. This additional render pass incurs in significant overheads, which may not always be offset by the

increase in the fragments discarded in the Early Depth Test. By working at a coarser granularity (primitive instead of fragment), EVR does not need to perform the pre-pass but still achieves results comparable to having complete visibility information.

Multiple works reduce overshading by means of reordering the primitives that make up a scene. Govindaraju et al. [29] propose an algorithm to sort objects in either front-to-back or back-to front order from a given viewpoint. The algorithm uses the Depth Buffer and the GPU to perform the image-space occlusion computations among objects. The work of Chen et al. [13] also creates a depth-sorted list for every possible viewpoint, focused on static objects that do not intersect. A preprocess creates back-facing duplicates for each input triangle in order to allow general triangle orderings. Cycles within the obtained occlusion graph are broken by using a heuristic that divides the space of viewpoints into a number of partitions and creating independent sorted lists for each partition. In the approach of Han and Sander [32], the preprocessing is extended to consider several key frames besides viewpoints, which generate sorted lists that can be indexed at runtime to reduce the overdraw in animated scenes. Weber and Stamminger [84] use a graph representation of dependencies in animated scenes with a fixed camera to sort primitives accordingly, and leverage frame-to-frame coherence to merge different graphs and keep the overall structure manageable. Unlike EVR, these approaches are not suited for interactive scenes in real-time rendering due to their preprocessing needs, which is limited to certain camera angles, animations or frames. Visibility Rendering Order [15] was proposed recently as an approach to dynamically sort objects in real time. By taking advantage of temporal coherence, a visibility graph can be constructed entirely in hardware after rendering each frame and use it as an approximation for the visibility of the next one. Objects are thus sorted in front-to-back order and overshading is reduced by processing objects predicted to be occluded after objects predicted to be visible. EVR is able to reduce the overshading even further by working at a finer granularity (primitives instead of objects).

#### 1.3.3 Reducing redundant colors within a frame

Primitives in the Raster Pipeline are discretized by sampling them across the screen and producing a fragment for each sampling location that they cover. Sampling points are usually placed in the center of pixels, which allows to capture the majority of details and avoid most aliasing effects like jagged edges or flickering. However, many regions of the screen do not contain enough level of detail to require such high sampling rates, leading to a significant amount of fragments wastefully producing the same color as their neighbours.

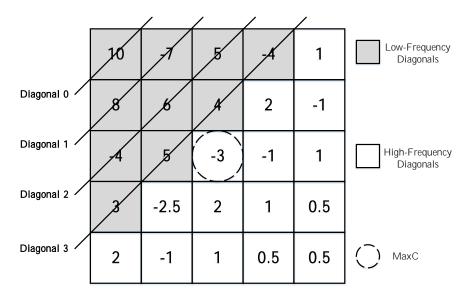

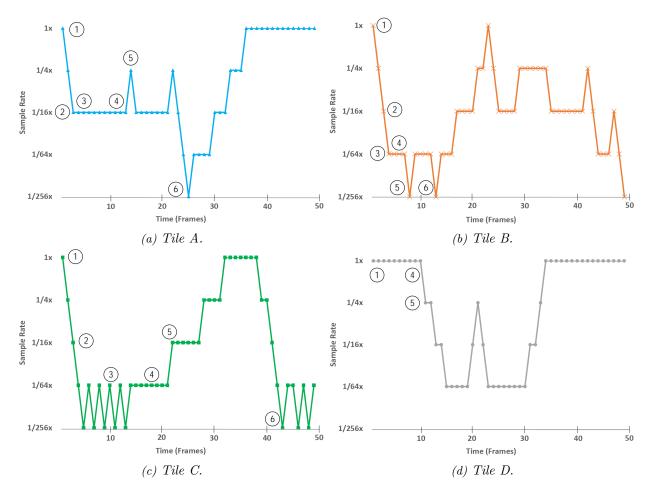

Based on that observation, we propose Dynamic Sampling Rate (DSR): a hardware mechanism that dynamically finds and applies, for each tile, the optimal sampling rate, i.e., the lowest sampling rate that does not cause visible artifacts in the rendered image. After the rendering of a tile to the on-chip color buffer finishes, DSR computes the 2D Discrete Cosine Transform of the resultant tile image, analyzes the spatial frequencies present in it and decides, based on a simple heuristic, the best sampling rate for the tile: whether it could have been sampled at a lower rate without sacrificing image quality, whether it contains enough detail that the sampling rate needs to be increased or whether the sampling rate is already optimal. Frame coherence implies that the level of detail of a tile across consecutive frames will be very similar, so the estimated-best rates for all the tiles are stored in a small on-chip Lookup Table and are queried during the rendering of each tile in the following frame.

There is a lot of interest in the graphics community in sampling at coarser granularities than pixels because it is a direct way to reduce the number of shading executions, which entails reductions in execution time and energy consumption. DSR addresses the main shortcomings of prior work on this area.

Several techniques dynamically detect regions of the screen that can be sampled at lower rates by adding additional pipeline stages before or after the shading process. Deferred Adaptive Compute Shading [43] divides the framebuffer into levels, subsets of pixels progressively denser, and starts by shading the pixels in the coarsest level, the left corner in square regions of 4x4 pixels. The levels in the hierarchy are then traversed in order, processing all the pixels in a level before advancing to the subsequent level. Before shading a pixel, the values of the 4 closest, equidistant pixels from the previous level are compared using a user-defined criterion, such as threshold between color values combined with material identifiers. If the neighbor pixels are similar, the color of the pixel is computed by averaging their results and all the shading computations and memory accesses are avoided. Otherwise, the pixel is shaded as normal. Multi-Sampling Anti-Aliasing (MSAA) emulates the quality of sampling more than once per pixel without having to shade all the samples. Visibility is sampled many times per pixel, but the color computation is only performed once per pixel and shared to all the visibility samples covered by the triangle in that pixel. MSAA improves image quality especially around object silhouettes, where typically there are both color and depth discontinuities. In the work of Sathe and Akenine-Möller [65], MSAA is extended to reuse shading computations along internal edges from different primitives of the same object. They present a unit that queues fragments before the processing stage and detects non-overlapping fragments from neighbouring primitives using their coverage information and vertex identifiers. In Adaptive Image-Space Sampling [69], the resolution is reduced in areas that contain less perceivable detail. Using the information available after the geometry processing, a visual perception method based on the human visual system evaluates the probability of a fragment being important to the final image. Only the fragments labelled as necessary are shaded, while the color of the others is obtained by interpolating other results. Unlike these approaches, DSR is architected to not introduce any time overheads by completely overlapping the sampling rate estimation for a tile with the rendering of the next one.

To avoid the runtime overhead of determining components with less detail, several works allow the programmer to statically determine the sampling rate. In Coarse Pixel Shading [79], the sample rate of a primitive can be controlled based on their vertex attributes. The sample rate may change for a primitive across different regions of the screen and different attributes may also be sampled at independent rates. He et al. [33] design new language abstractions that grant each shader program the ability to sample different components of the shading function at different rates. The rasterizer first generates coarse fragments, which execute their shader for effects that have low spatial variation, like certain lights. These fragments are then partitioned into finer fragments, which execute traditional shader programs for effects that have per-pixel variability. In the new Turing GPUs, NVIDIA has introduced Variable Rate Shading, a feature that allows the programmer to decide which sampling rate to apply in each 16x16-pixel region of the screen. DSR, on the other hand is able to continuously adapt to changes in the scene by dynamically estimating the best sampling rates in each tile using a hardware-only mechanism in a completely transparent manner

to the programmer.

Frame coherence has been previously leveraged to reduce the number of samples to process. In Checkerboard rendering [47], each frame shades an alternate half of the pixels in the screen. The color of the non-shaded half is obtained by applying reconstruction filters to the results obtained in the preceding frame. A large number of shading computations are avoided at the cost of some visual artifacts, since the lossy nature of the reconstruction and the fixed undersampling cannot perfectly reproduce neither motion nor visibility changes. In contrast, DSR estimates sampling rates at the finer granularity of tiles, can render tiles at the small rate of only one fragment per tile and does not affect image quality because it only reduces the sampling rate whenever a tile does not contain high spatial frequencies.

#### 1.4 Thesis contributions

This section presents the contributions and publications of this thesis' research on energy efficient mobile GPUs for graphics applications.

#### 1.4.1 Rendering Elimination

Rendering Elimination (RE) is a coarse-grained memoization scheme that avoids the entire processing of redundant tiles. The work has been published as:

Rendering Elimination: Early Discard of Redundant Tiles in the Graphics Pipeline. Martí Anglada, Enrique de Lucas, Joan-Manuel Parcerisa, Juan Luis Aragón, Pedro Marcuello and Antonio González. In 2019 IEEE International Symposium on High Performance Computer Architecture (HPCA'19).

Its main contributions can be summarized as follows:

- The observation that frame redundancy can be discovered in a Tile-Based Rendering GPU at the tile level much earlier in the pipeline than previous techniques do.

- An analysis of the large amount of tile-level redundancy in current graphics applications, which leads to energy waste when computing again the same colors for a tile than in its preceding frame.

- A detailed proposal of a mechanism to detect tile redundancy in early stages of the Graphics Pipeline and avoid its processing.

- An architectural implementation of the tile redundancy detection that can be integrated into the Graphics Pipeline with minimal hardware and performance overheads.

- An experimental evaluation of RE that shows that our proposal to discard redundant tiles yields energy savings of 37% and an execution time reduction of 33% over a conventional mobile GPU, and substantial improvements over previous works.

#### 1.4.2 Early Visibility Resolution

Early Visibility Resolution (EVR) is a mechanism to avoid the processing of fragments belonging to hidden surfaces. The work has been published as:

Early Visibility Resolution for Removing Ineffectual Computations in the Graphics Pipeline. Martí Anglada, Enrique de Lucas, Joan-Manuel Parcerisa, Juan Luis Aragón, and Antonio González. In 2019 IEEE International Symposium on High Performance Computer Architecture (HPCA'19).

Its main contributions can be summarized as follows:

- An analysis of the amount of overshading in current graphics applications, which leads to energy waste when computing the colors of a primitive that will eventually be occluded.

- A detailed proposal for a mechanism to estimate visibility at tile level in early stages of the Graphics Pipeline based on exploiting frame coherence.

- A mechanism to employ the visibility determination to reduce overshading by processing primitives predicted to be visible before primitives predicted to be occluded.

- A mechanism to employ the visibility determination to improve Rendering Elimination's redundant tile detection by not including primitives predicted to be occluded in the memoization scheme.

- An architectural implementation of a visibility prediction scheme that can be integrated into the Graphics Pipeline with minimal hardware overhead and without any performance penalty.

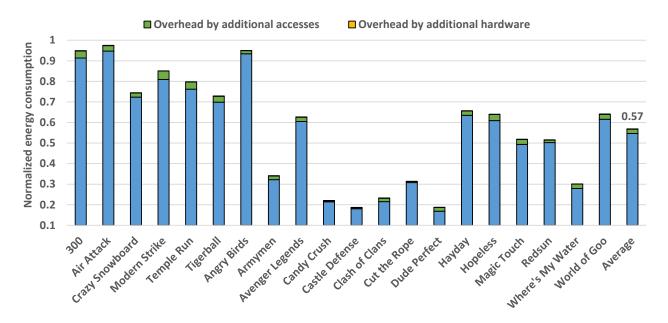

- An experimental evaluation of EVR that shows great reduction in overshading and improvements in redundant tile detection, yielding energy savings of 43% and an execution time reduction of 39%.

#### 1.4.3 Dynamic Sampling Rate

Dynamic Sampling Rate (DSR) is a technique that reduces the number of fragments generated in tiles with low spatial frequencies. The work is currently under review as:

Dynamic Sampling Rate: Harnessing Frame Coherence in Graphics Applications for Energy-Efficient GPUs. <u>Martí Anglada</u>, Enrique de Lucas, Joan-Manuel Parcerisa, Juan Luis Aragón, and Antonio González.

Its main contributions can be summarized as follows:

• An analysis of the number of tiles in current graphics applications that can be sampled at a lower rate than the baseline without producing visual artifacts, which leads to energy waste when processing the colors of fragments that do not improve image quality.

- A new hardware technique, completely transparent to the programmer, that estimates the lowest possible sample rate to which each tile may be rendered without producing visual artifacts and applies it during the following frame by taking advantage of frame coherence.

- A dynamic mechanism based on the real-time analysis of the spatial frequencies, that continuously adapts the sample rate of each tile to track the image changes that occur over time.

- An architectural implementation of the frequency analysis unit that can be integrated into the Graphics Pipeline with minimal hardware overhead and without any performance penalty.

- An experimental evaluation of DSR that shows great reduction in redundant shader activity, yielding energy savings of 40% and an execution time reduction of 36%.

2

### Background: Tile-Based Rendering

This chapter provides a brief overview on the Graphics Pipeline. While the Pipeline is a conceptual model that can be implemented in many ways, the focus of this chapter is set on how data is transformed and transported across the different stages in Tile-Based Rendering, an architecture designed with low power as a goal. The objective of the chapter is to give background on the tasks that the GPU solves and introduce the terminology that will be used throughout the document, in particular of Tile-Based Rendering, as it is the design that will be used as a baseline in the proposals of the thesis.

The Graphics Pipeline is the process that obtains a two-dimensional image given a threedimensional scene and a camera position and orientation. Three-dimensional scenes usually consist of light sources and three-dimensional objects, which are modelled by polygons. Rendering is a complex operation consisting of many operations and is, consequently, pipelined to improve its performance and throughput. All the required steps can be grouped in three coarse pipeline stages where each stage requires the output of the previous one as its input: Application, Geometry and Raster, as seen in Figure 2.1. The Application Stage corresponds to the program running on the CPU, and is responsible to create the geometry that defines the scene, to adapt it according to the user interaction and to send it to the GPU. The GPU implements the next two stages with a mix of fixed-function and programmable hardware: the Geometry Stage, in which the geometry is transformed and assembled into triangles in the screen plane, and the Raster Stage, in which triangles are discretized into "picture elements" (*pixels*) that are then shaded: a color is computed for each of them.

Figure 2.1: Coarse view of the Graphics Pipeline.

#### 2.1 The Application Stage

The Application Stage is the collection of software instructions required to set the state of the pipeline. This encompasses a plethora of operations, ones that manage interfacing and ones closer to managing the hardware.

On the high-level side, the application controls how the scene reacts to the user inputs, establishing the motion of the objects and the camera and deciding which objects should be displayed. The programmer also determines how objects interact with each other and the world by computing the effect of forces upon them, particularly collisions.

On the low-level side, a wide variety of capabilities and optimizations can be enabled, such as culling, depth test or blending, which will be discussed later in this chapter. The application also manages memory resources and how data is stored and handled. The most important function of the Application Stage is to load the objects belonging to the scene and transfer them to the GPU. Objects are comprised of vertices, points in three-dimensional space to which the application associates additional information known as *attributes*, such as normals or color. Attached to the objects are also *shaders*, code defined by the application that computes how different types of light interact with their surfaces, and *textures*, images that can be applied on top of polygons to add high-frequency detail. The application communicates with the GPU the state of the pipeline for a batch of vertices using *Commands* and triggers them using a *Drawcall*.

# 2.2 The Geometry Stage

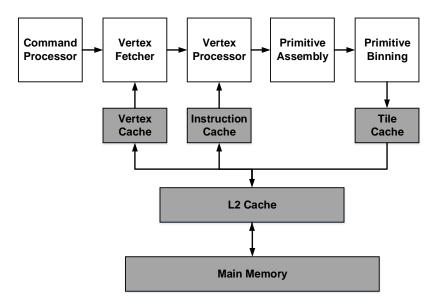

Figure 2.2 shows a block diagram of the Geometry Stage, which receives input streams of vertices from the GPU and transforms it into a series of 2D primitives.

Figure 2.2: Geometry Pipeline

#### **Command Processor**

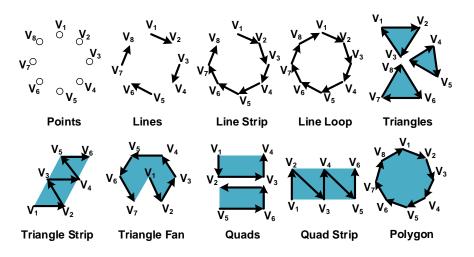

The Command Processor reads the commands sent by the application and configures the different stages of the GPU. In particular, it parses how the vertex information of each Drawcall must be interpreted: how do vertices form primitives and how their attributes are laid out in memory. The ordered list of vertices that the GPU receives can represent a wide variety of primitives, depending on the application specification. Figure 2.3 shows the different possibilities in which vertices can be connected. The most used primitive types are triangles, in which every group of 3 vertices forms a triangle, and triangle strips, in which successive vertices form triangles with the preceding two.

#### Vertex Fetcher

The Vertex Fetcher reads the vertices requested by a Drawcall and unpacks its attributes to be used as inputs in the vertex shader. As illustrated in Figure 2.4, vertices in three-dimensional objects tend to be shared by several triangles. Consequently, the Vertex Fetcher is aided by a Vertex Cache to capture that reuse and reduce vertex communication with main memory.