### Alma Mater Studiorum – Università di Bologna

## DOTTORATO DI RICERCA IN

# INGEGNERIA ELETTRONICA, TELECOMUNICAZIONI E TECNOLOGIE DELL'INFORMAZIONE

Ciclo XXXII

**Settore Concorsuale:** 09/E3

Settore Scientifico Disciplinare: ING-INF/01

### DESIGN TECHNIQUES TO ENHANCE LOW-POWER WIRELESS COMMUNICATION SOC WITH RECONFIGURABILITY AND WAKE UP RADIO

Presentata da: Francesco Renzini

### **Coordinatore Dottorato**

#### Supervisore

Prof.ssa Alessandra Costanzo

Prof.ssa Eleonora Franchi Scarselli

#### UNIVERSITÀ DI BOLOGNA

# Abstract

ARCES-DEI

Doctor of Philosophy

#### Design Techniques to Enhance Low-Power Wireless Communication SoC with Reconfigurability and Wake Up Radio

by Francesco RENZINI

Nowadays, Internet of things applications are increasing, and each end-node has more demanding requirements such as energy efficiency and speed. The thesis proposes a heterogeneous elaboration unit for smart power applications, that consists of an ultra-low-power microcontroller coupled with a small (around 1k equivalent gates) soft-core of embedded FPGA. This digital system is implemented in 90-nm BCD technology of STMicroelectronics, and through the analysis presented in this thesis proves to have good performance in terms of power consumption and latency. The idea is to increase the system performance exploiting the embedded FPGA to managing smart power tasks. For the intended applications, a remarkable computational load is not required, it is just required the implementation of simple finite state machines, since they are event-driven applications. In this way, while the microcontroller deals with other system computations such as high-level communications, the eFPGA can efficiently manage smart power applications. An added value of the proposed elaboration unit is that a soft-core approach is applied to the whole digital system including the eFPGA, and hence, it is portable to different technologies. On the other hand, the configurability improvement has a straightforward drawback of about a 20–27% area overhead. The eFPGA usage to manage smart power applications, allows the system to reduce the required energy per task from about 400 to around 800 times compared to a processor implementation. The eFPGA utilization improves also the latency performance of the system reaching from 8 to 145 times less latency in terms of clock cycles. The thesis also introduces the architecture of a nano-watt wake-up radio integrated circuit implemented in 90-nm BCD technology of STMicroelectronics. The wake-up radio is an auxiliary always-on radio for medium-range applications that allows the IoT end-nodes to drastically reduce the power consumption during the node idle-listening communication phase.

# Contents

| A | bstra | ct       |                                        | i  |

|---|-------|----------|----------------------------------------|----|

| 1 | Intr  | oductio  | on                                     | 1  |

| 2 | SoC   | CArchi   | tectures for Smart Power Applications  | 7  |

|   | 2.1   | Introc   | luction                                | 7  |

|   | 2.2   | Smart    | Power Technology                       | 9  |

|   | 2.3   | ULP 1    | Techniques                             | 10 |

|   | 2.4   | Progr    | ammable Device Scenario                | 11 |

|   |       | 2.4.1    | Microcontrollers                       | 13 |

|   |       | 2.4.2    | FPGAs                                  | 14 |

|   |       | 2.4.3    | Embedded FPGAs                         | 15 |

|   |       | 2.4.4    | System-on-Chips                        | 15 |

|   | 2.5   | Propo    | osed SoC                               | 16 |

| 3 | SoC   | E Elabo  | ration Unit                            | 19 |

|   | 3.1   | Micro    | controller                             | 19 |

|   | 3.2   | Embe     | dded FPGA Sub-System                   | 20 |

|   |       | 3.2.1    | Embedded FPGA Architecture             | 21 |

|   |       | 3.2.2    | Prescaler                              | 23 |

|   |       | 3.2.3    | Configuration Loader                   | 23 |

|   |       | 3.2.4    | Configuration Registers                | 23 |

|   |       | 3.2.5    | eFPGA Software Tools                   | 24 |

|   | 3.3   | Appli    | cation Programming Interface           | 24 |

| 4 | eFP   | GA Ar    | chitecture Details                     | 27 |

|   | 4.1   | Introc   | luction                                | 27 |

|   | 4.2   | Embe     | dded FPGA Interconnection Network      | 31 |

|   |       | 4.2.1    | Proposed eFPGA Interconnection Network | 34 |

|   |       |          | MSSN with Bypass Enhancement           | 36 |

|   |       | 4.2.2    | MSSN Programming Strategy              | 37 |

| 5 | Apr   | olicatio | n Analysis                             | 41 |

|   | 5.1   |          | mentation Choices                      | 41 |

|   |       | 5.1.1    | Proposed Reconfigurable SoC            |    |

|   |       | 5.1.2    | ASIC                                   |    |

|   |     | 5.1.3   | STM32 Microcontroller                                  |

|---|-----|---------|--------------------------------------------------------|

|   | 5.2 | Energ   | y and Latency Model                                    |

|   |     | 5.2.1   | eFPGA - Efficiency Model                               |

|   |     | 5.2.2   | PULPino - Efficiency Model                             |

|   |     | 5.2.3   | ASIC - Efficiency Model                                |

|   |     | 5.2.4   | STM32 - Efficiency Model                               |

|   |     | 5.2.5   | Energy Gain and Latency 48                             |

|   | 5.3 | Appli   | cation Results                                         |

|   |     | 5.3.1   | Control Applications                                   |

|   |     |         | Pulse-Width Modulation                                 |

|   |     |         | RGB LED Controller53                                   |

|   |     |         | Brushed Motor Controller                               |

|   |     |         | Stepper Motor Controller 55                            |

|   |     | 5.3.2   | Bitwise Streaming Applications                         |

|   |     |         | Cyclic Redundancy Check                                |

|   |     |         | Pseudo-Random Number Generation                        |

|   |     | 5.3.3   | Ultra Low-Power Applications                           |

|   | 5.4 | Result  | ts and Discussion                                      |

|   |     | 5.4.1   | Energy Efficiency Consideration    60                  |

|   |     | 5.4.2   | Latency Consideration                                  |

|   |     | 5.4.3   | Implementation Solutions Under Analysis                |

|   |     |         | Microcontroller Implementation                         |

|   |     |         | eFPGA Implementation                                   |

|   |     |         | ASIC Implementation 70                                 |

|   |     |         | Proposed SoC Implementation                            |

| 6 | Wał | ke Up F | Radio 73                                               |

|   | 6.1 | ULP C   | Communication Techniques                               |

|   | 6.2 | Wake    | Up Radio Architecture                                  |

|   |     | 6.2.1   | Demodulator-Amplifier Architecture                     |

|   | 6.3 | Schmi   | itt Trigger Design                                     |

|   | 6.4 | Result  | ts and Comparison                                      |

| 7 | Con | clusior | ns 87                                                  |

| Α | eFP | GA Int  | erconnection Network Details 89                        |

|   | A.1 | Multi   | cast Radix-2 MSSN Proprierties                         |

|   | A.2 | Multi   | cast Radix-k MSSN Proprierties                         |

|   | A.3 |         | rchical MSSN Performance                               |

|   |     | A.3.1   | MSSN Delay Model and Validation                        |

|   |     | A.3.2   | MSSN Effective Frequency Versus Bypass Exploitation 95 |

|   |     | A.3.3   | Hierarchical MSSN Radix Comparison                     |

# **List of Figures**

| Smart power system diagram                                                               | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BCD technology [9]                                                                       | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Programmable devices scenario. Picture reused from [1]                                   | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Proposed SoC architecture.                                                               | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

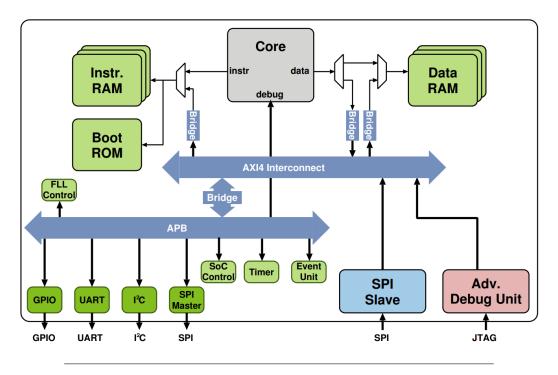

| PULPino architecture scheme [38]                                                         | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

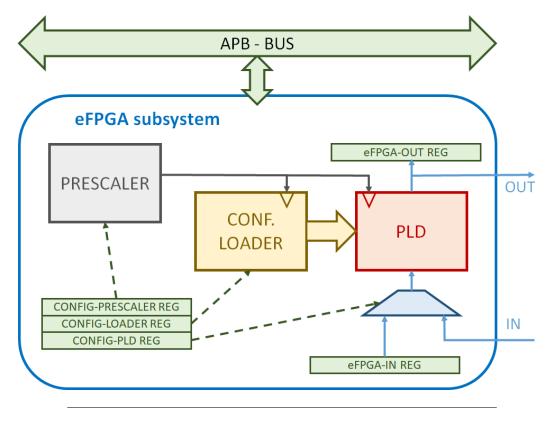

| The eFPGA subsystem interfaced through APB bus. Picture reused                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| from [1]                                                                                 | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

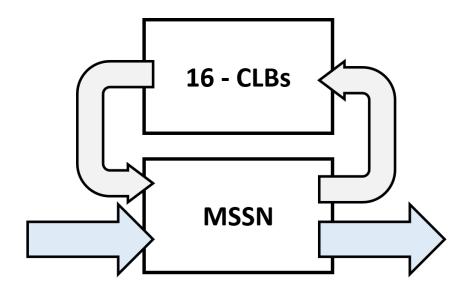

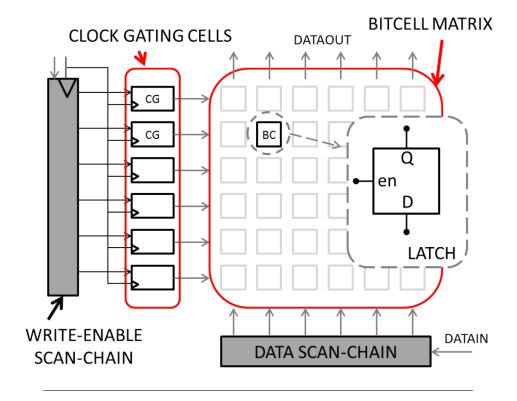

| Diagram of the eFPGA. Picture reused from [1].                                           | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

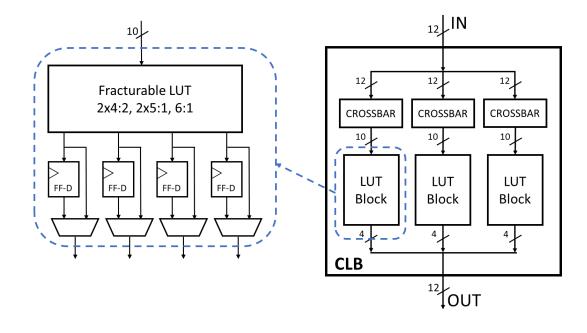

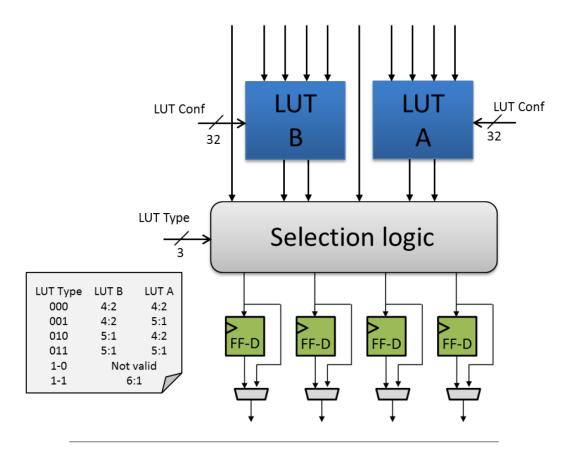

| eFPGA CLB structure [3]                                                                  | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

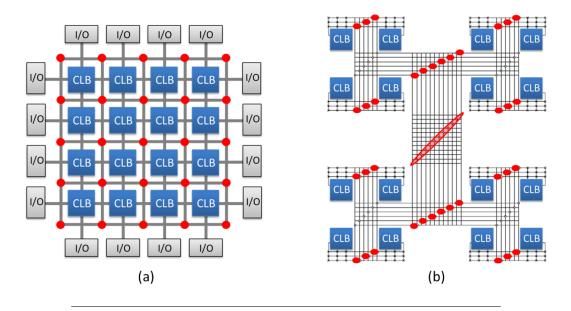

| FPGA structures: island-style (a) and hierarchical (b) [4].                              | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

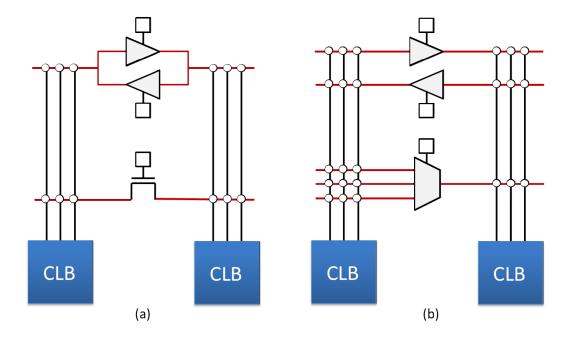

|                                                                                          | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

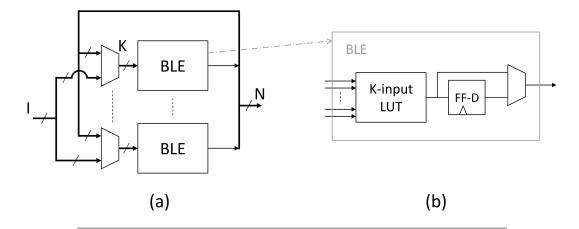

| •                                                                                        | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

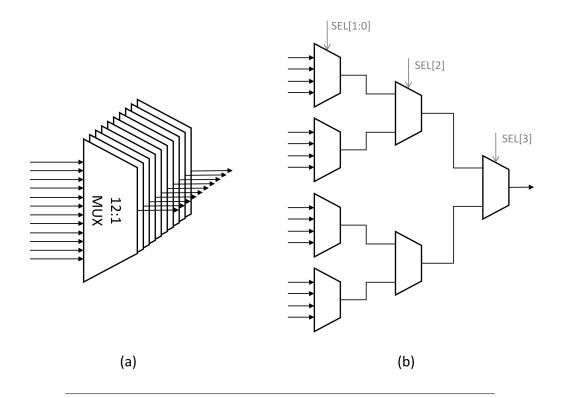

|                                                                                          | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| BLE architecture [4].                                                                    | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| BLE architecture [4].                                                                    | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

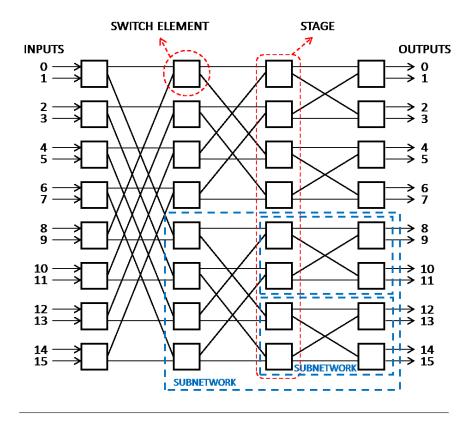

|                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                          | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

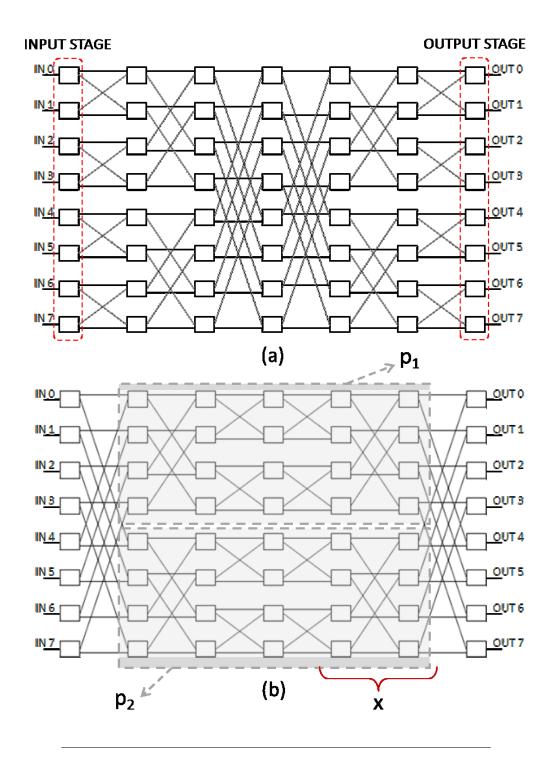

| topologically equivalent version (b). Picture reused from [40]                           | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

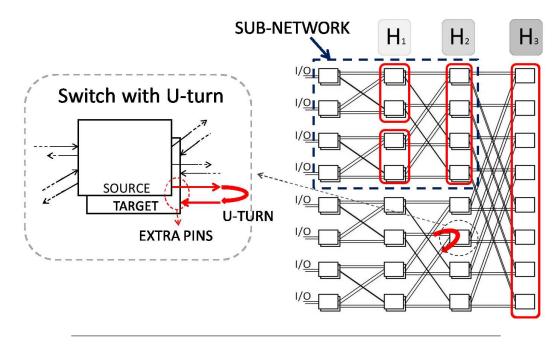

| Folded bypassed MSSN enhanced with <i>U-turn</i> bypasses [3]                            | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

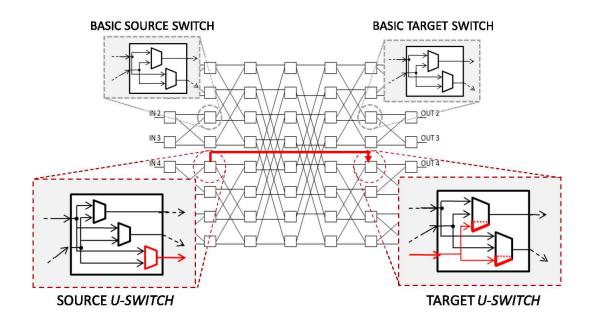

| MSSN with bypass enhancement: unfolded view and <i>U-switch</i> struc-                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ture description [4]                                                                     | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

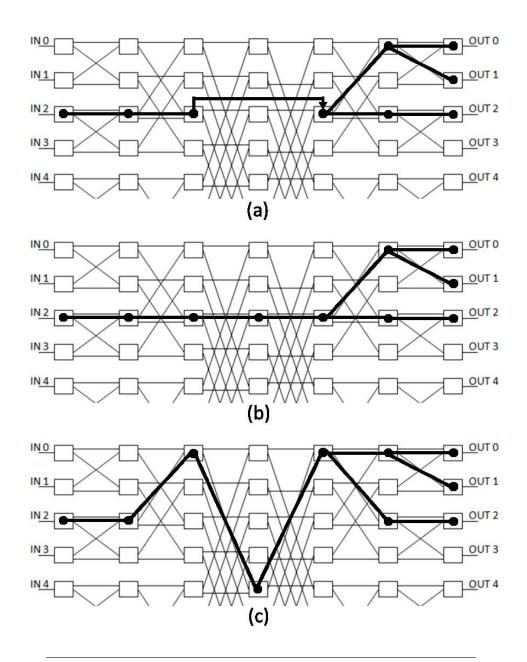

| Three different multi-fanout paths connecting IN2 to OUT0, OUT1,                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| and OUT2 in order of cost: with bypass enhancement ( <b>a</b> ), with the as-            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| straight-as-possible policy ( <b>b</b> ), and using diagonal wires ( <b>c</b> ). Picture |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| reused from [40]                                                                         | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

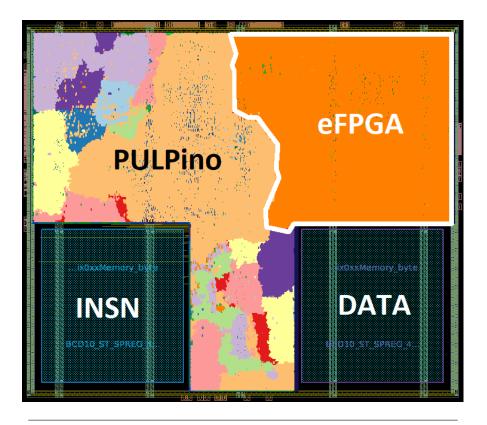

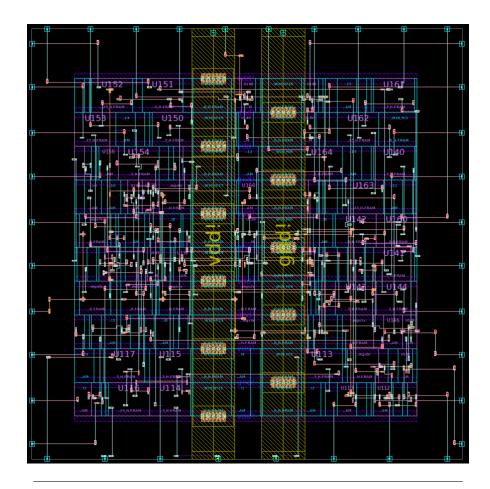

| Proposed SoC implemented in BCD 90 nm. Reused from [1]                                   | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RGB LED controller ASIC layout.                                                          | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

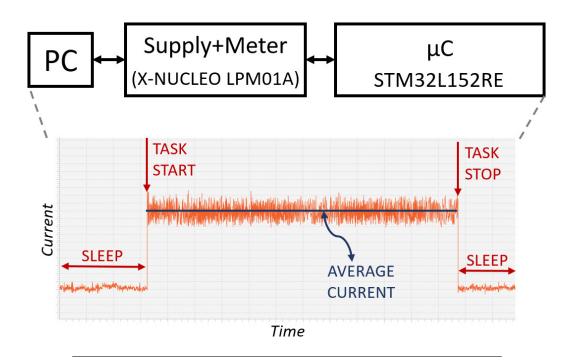

| Measurement setup and current profile. Reused from [1]                                   | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

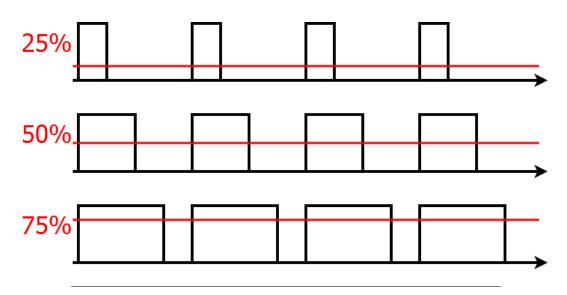

| PWM signals and corresponding average value with different duty                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| cycles: 25%, 50% and 75%                                                                 | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                          | BCD technology [9].Programmable devices scenario. Picture reused from [1].Proposed SoC architecture.PULPino architecture scheme [38].The eFPGA subsystem interfaced through APB bus. Picture reusedfrom [1].Diagram of the eFPGA. Picture reused from [1].eFPGA CLB structure [3].FPGA structures: island-style (a) and hierarchical (b) [4].Bidirectional (a) and unidirectional (b) wires [4].Example of both CLB architecture (a) and BLE (b).CLB internal Crossbar architecture (a). Multiplexer 12:1 structure (b).BLE architecture [4].An $N \times N$ (with $N = 16$ ) Banyan multistage switching network (MSSN)featuring butterfly topology. Picture reused from [40].An $N \times N$ (with $N = 8$ ) flat version of the proposed MSSN: originalarchitecture (a) and rearrangeably non-blocking (RNB)-proof unicasttopologically equivalent version (b). Picture reused from [40].Folded bypassed MSSN enhanced with $U$ -turn bypasses [3].MSSN with bypass enhancement: unfolded view and $U$ -switch structureture description [4].Three different multi-fanout paths connecting $IN2$ to $OUT0$ , $OUT1$ ,and $OUT2$ in order of cost: with bypass enhancement (a), with the asstraight-as-possible policy (b), and using diagonal wires (c). Picturereused from [40].Proposed SoC implemented in BCD 90 nm. Reused from [1].RGB LED controller ASIC layout.Measurement setup and current profile. Reused from [1]. |

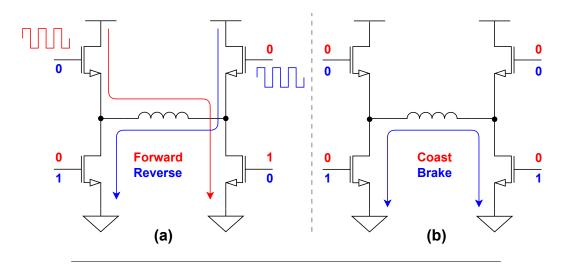

| 5.5  | Brushed controller H-bridge operating modes. (a) forward - red - and                   |    |

|------|----------------------------------------------------------------------------------------|----|

|      | reverse - blue - mode. (b) coast - red - and brake - blue - mode. Picture              |    |

|      | reused from [1]                                                                        | 54 |

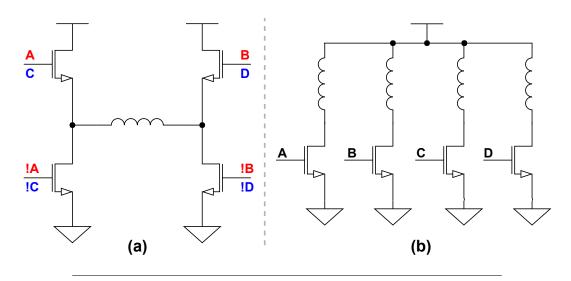

| 5.6  | Driver circuits for stepper motors. Two full H-bridges - respectively                  |    |

|      | red and blue inputs - for bipolar stepper motors (a). Transistor scheme                |    |

|      | for unipolar stepper motors (b). Picture reused from [1]                               | 55 |

| 5.7  | Signals patterns for unipolar - red - and bipolar - blue - for: full-step              |    |

|      | (a), half-step (b) and wave-drive control modes. Picture reused from                   |    |

|      | [1]                                                                                    | 56 |

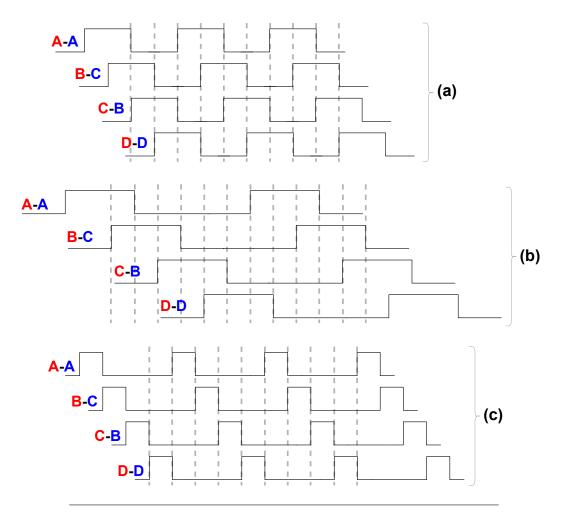

| 5.8  | Wake up radio correlator architecture. Picture reused from [1]                         | 59 |

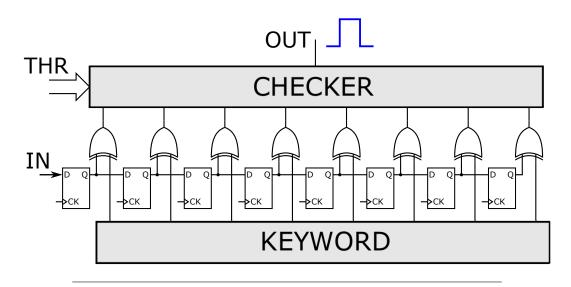

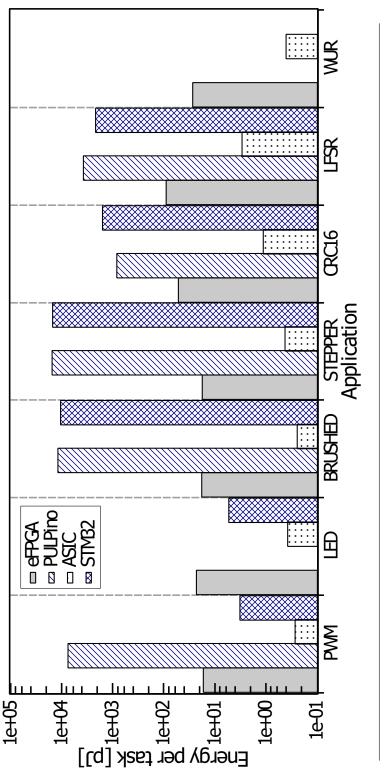

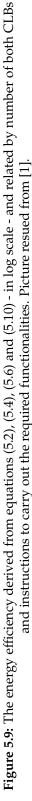

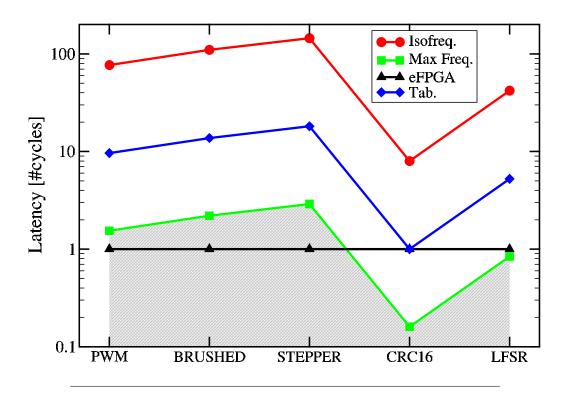

| 5.9  | The energy efficiency derived from equations (5.2), (5.4), (5.6) and                   |    |

|      | (5.10) - in log scale - and related by number of both CLBs and instruc-                |    |

|      | tions to carry out the required functionalities. Picture resued from [1].              | 61 |

| 5.10 | Energy gain - in log scale - defined by equation (5.11) for applications               |    |

|      | implemented in both eFPGA and PULPino. Picture reused from [1]                         | 63 |

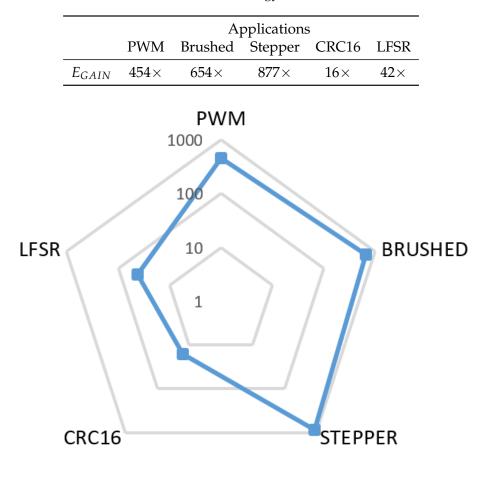

| 5.11 | PULPino and eFPGA latency (in clock cycles) for the applications un-                   |    |

|      | der analysis. Picture reused from [1]                                                  | 65 |

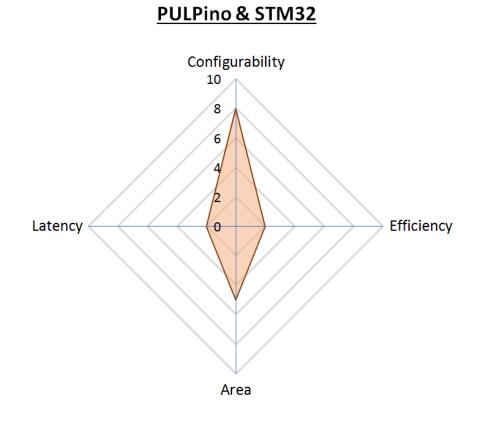

| 5.12 | Microcontroller PULPino and STM32 implementation features                              | 67 |

| 5.13 | Proposed eFPGA implementation features                                                 | 68 |

| 5.14 | ASIC implementation features.                                                          | 69 |

| 5.15 | Proposed SoC implementation features.                                                  | 70 |

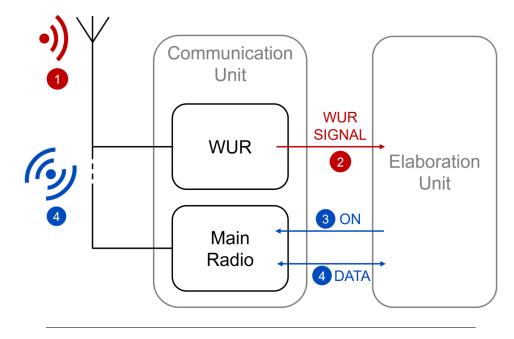

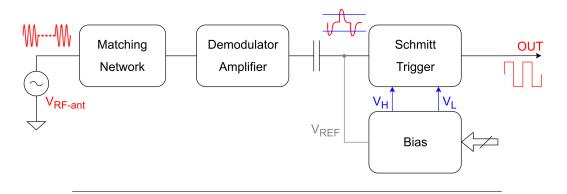

| 6.1  | System architecture with WUR.                                                          | 74 |

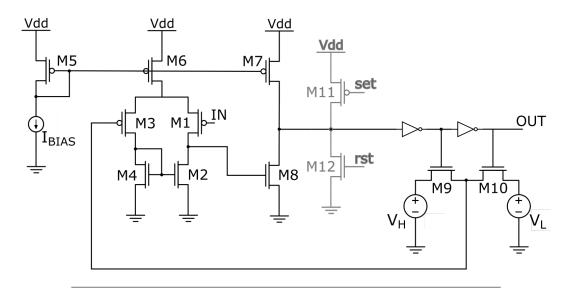

| 6.2  | Wake up radio architecture.                                                            | 75 |

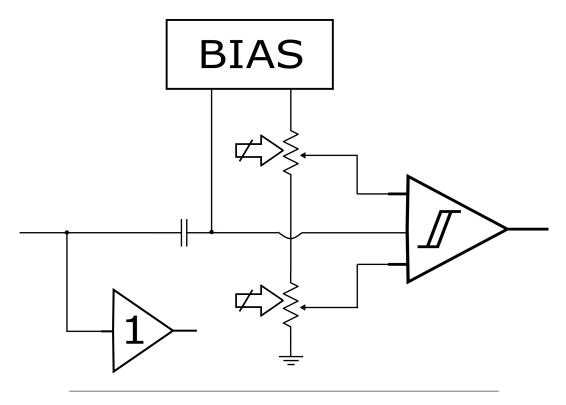

| 6.3  | Bias circuit function.                                                                 | 76 |

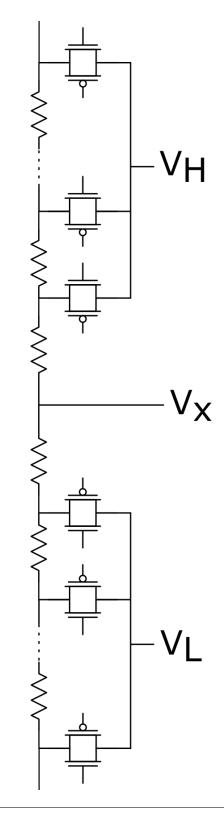

| 6.4  | Digital potentiometer structures used to generate the Schmitt Trigger                  |    |

|      | voltage references.                                                                    | 77 |

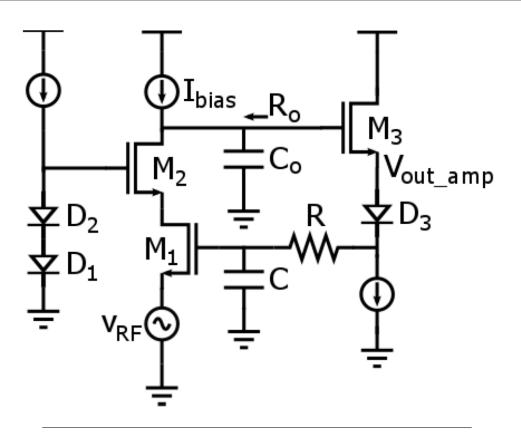

| 6.5  | Demodulator-amplifier architecture. Picture reused from [69]                           | 78 |

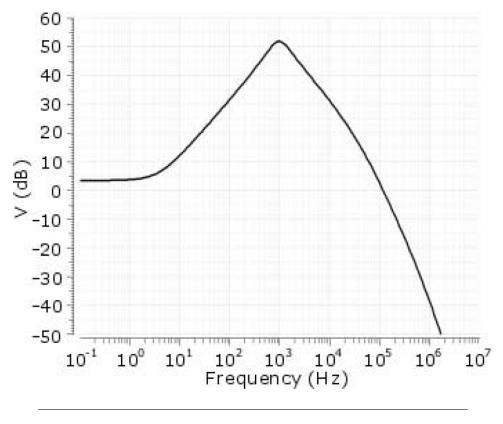

| 6.6  | Frequency response of the proposed circuit. Picture reused from [69].                  | 80 |

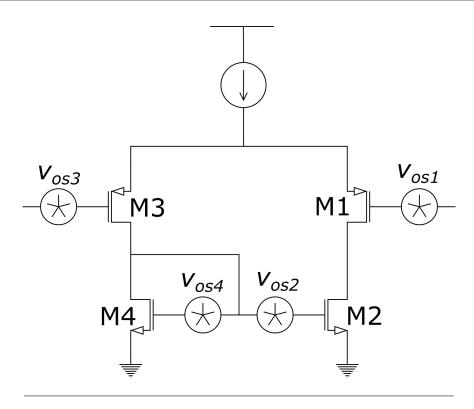

| 6.7  | Schmitt trigger schematic.                                                             | 81 |

| 6.8  | Equivalent offset model of the Schmitt trigger differential pair                       | 82 |

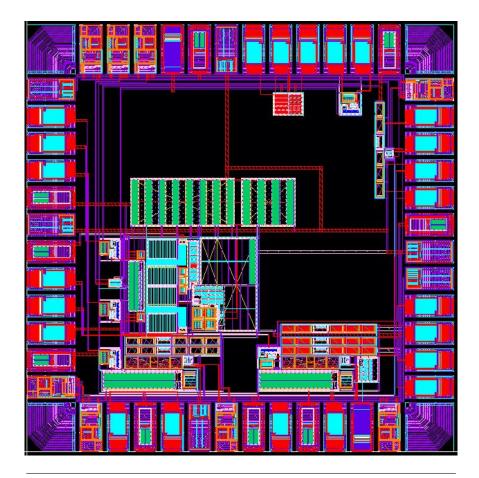

| 6.9  | Wake up radio test chip layout.                                                        | 83 |

| 6.10 | WUR system transient noise simulation. Picture reused from [69]                        | 84 |

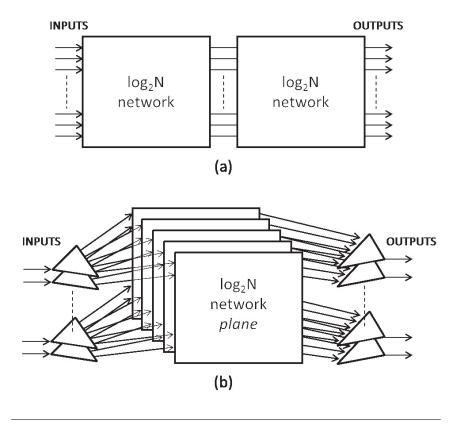

| A.1  | Example of construction of Multi- $\log_2 N$ networks: with horizontal                 |    |

|      | cascading (a) and vertical stacking (b) technique [40].                                | 90 |

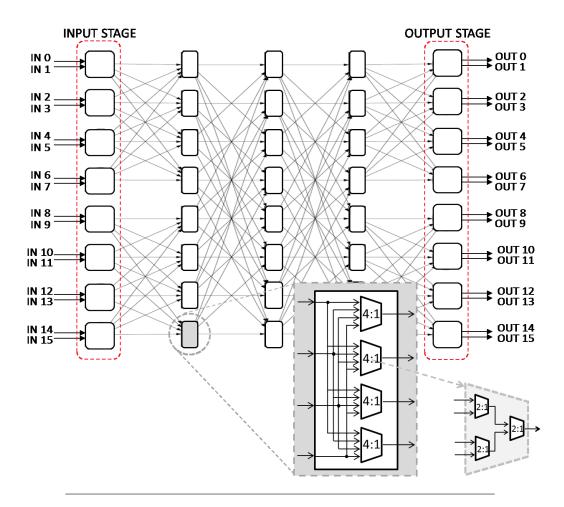

| A.2  | An example of <i>radix-4</i> $16 \times 16$ <i>flat</i> MSSN. Picture reused from [40] |    |

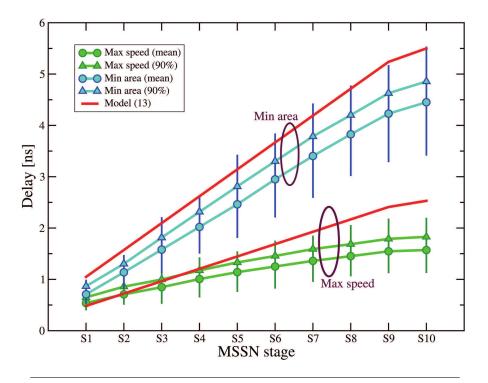

| A.3  | $1024 \times 1024$ I/Os <i>radix-2</i> MSSN in-to-out delays (with bypass exploita-    |    |

|      | tion at different stages) compared to model (A.10) varying the MSSN                    |    |

|      | stage <i>S</i> in which the <i>U</i> -turn connection is exploited. Picture reused     |    |

|      | from [40].                                                                             | 95 |

|      |                                                                                        |    |

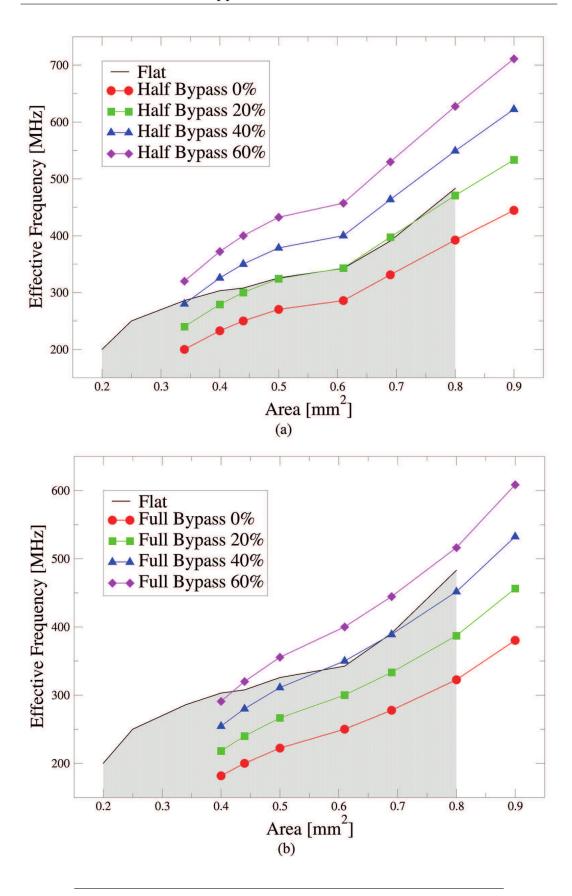

| A.4 | $1024 \times 1024$ I/Os <i>radix-2</i> MSSN effective frequency versus area for               |     |

|-----|-----------------------------------------------------------------------------------------------|-----|

|     | different <i>frequency gain</i> thanks to bypass exploitation: <i>flat</i> vs. <i>half-</i>   |     |

|     | <i>bypassed</i> ( <b>a</b> ) and <i>fully-bypassed</i> ( <b>b</b> ). Picture reused from [40] | 96  |

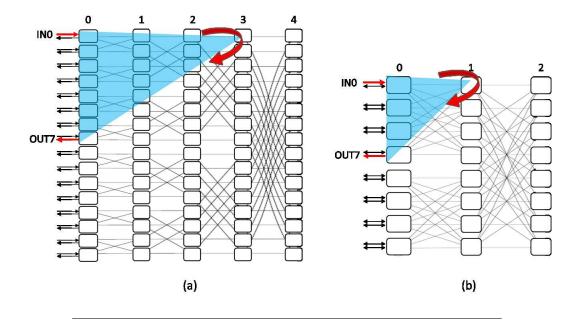

| A.5 | Example of fully-bypassed MSSN connectivity with $16 \times 16$ I/Os: <i>radix</i> -          |     |

|     | 2 ( <b>a</b> ) and <i>radix-4</i> ( <b>b</b> ). Picture reused from [40]                      | 98  |

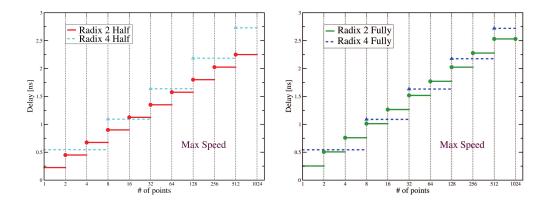

| A.6 | Max-speed implementations: delay vs. topological distance between                             |     |

|     | two I/Os for a 1024 $	imes$ 1024 <i>fully-bypassed</i> and <i>half-bypassed</i> MSSN. Pic-    |     |

|     | ture reused from [40]                                                                         | 99  |

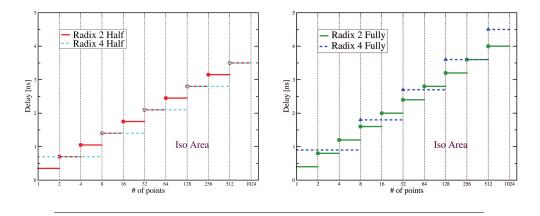

| A.7 | Iso-area implementations: delay vs. topological distance between two                          |     |

|     | I/Os for a $1024 \times 1024$ fully-bypassed and half-bypassed MSSN. Picture                  |     |

|     | reused from [40].                                                                             | 100 |

# **List of Tables**

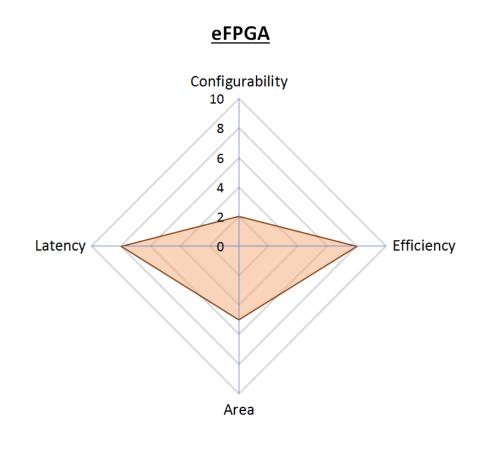

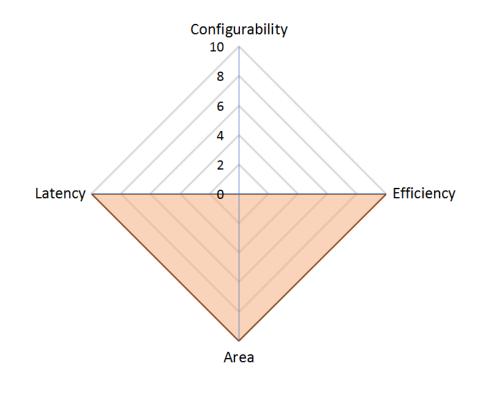

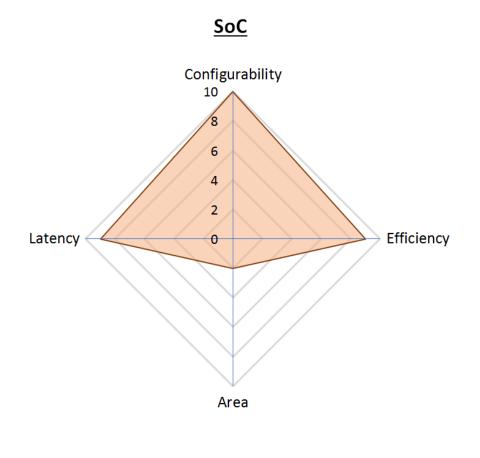

| 2.1 | Programmable Device Scenario. Reused from [1].                                | 12 |

|-----|-------------------------------------------------------------------------------|----|

| 3.1 | API Function Prototypes. Reused from [1].                                     | 24 |

| 5.1 | Proposed SoC implementation Results. Reused from [1]                          | 42 |

| 5.2 | Applications Results. Reused from [1]                                         | 50 |

| 5.3 | eFPGA - PULPino Energy Gain. Reused from [1].                                 | 63 |

| 6.1 | Wake up radio performance comparison. Reused from [69]                        | 85 |

| A.1 | CMOS 65 nm 1024 $\times$ 1024 radix-2 MSSN post-synthesis results [40]. $~$ . | 93 |

| A.2 | CMOS 65 nm 1024 $\times$ 1024 radix-4 MSSN post-synthesis results [40].       | 93 |

# **List of Abbreviations**

| AMBA   | Advanced Microcontroller Bus Architecture      |

|--------|------------------------------------------------|

| APB    | Advanced Peripheral Bus                        |

| ASIC   | Application-Specific Integrated Circuit        |

| ASIP   | Application Specific Instruction-set Processor |

| ASSP   | Application Specific Standard Product          |

| AXI    | Advanced eXtensible Interface                  |

| BCD    | Bipolar CMOS DMOS                              |

| CAD    | Computer Aided Design                          |

| CLB    | Configurable Logic Block                       |

| CMOS   | Complementary MOS                              |

| CRC    | Cyclic Redundancy Check                        |

| CTS    | Clock Tree Synthesis                           |

| DMOS   | Double-diffused MOS                            |

| DSP    | Digital Signal Processor                       |

| DTI    | Deep Trench Isolation                          |

| eFPGA  | embedded FPGA                                  |

| FD-SOI | Fully Depleted Silicon On Insulator            |

| FET    | Field Effect Transistor                        |

| FPGA   | Field Programmable Gate Array                  |

| FPU    | Floating Point Unit                            |

| FSM    | Finite State Machine                           |

| GPIO   | General Purpose Input/Output                   |

| HDL    | Hardware Description Language                  |

| IC     | Integrated Circuit                             |

| IoT    | Internet of Things                             |

| ISR    | Interrupt Service Routine                      |

| LB     | Logic Block                                    |

| LCD    | Liquid Crystal Display                         |

| LFSR   | Linear Feedback Shift Register                 |

| MAC    | Multiplier ACcumulator                         |

| MOS    | Metal Oxide Semiconductor                      |

| MSSN   | MultiStage Swithing Network                    |

| NRE    | Non-Recurring Engineering                      |

| OOK    | On-Off Keying                                  |

| PLD    | Programmable Logic Device                      |

|        |                                                |

**RF R**adio Frequency

**RISC** Reduced Instruction Set Computer

**RNB** Rearrangeable Non-Blocking

**RTL** Register Transfer Language

SE Switching Element

SoC System on Chip

SRAM Static Random Access Memory

- **uC**,  $\mu$ **C** MicroController

- ULP Ultra Low-Power

- **uP**, μ**P M**icro**P**rocessor

- VCD Value Change Dump

- VTR Verilog-To-Routing

- WSN Wireless Sensor Network

- WUR Wake Up Radio

## Chapter 1

# Introduction

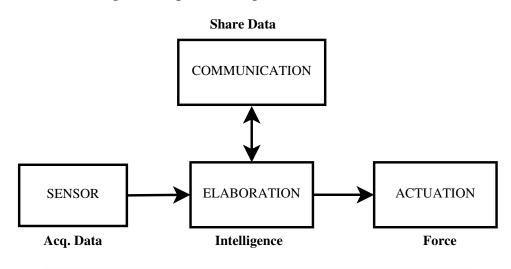

The well known Internet-of-Things (IoT) domain is becoming one of the most popular scenarios in every human activity field. In the IoT arena, everything, each object is connected to the others, composing a network. For instance, Wireless Sensor Networks (WSNs) are constantly growing in every kind of monitoring activities such as biomedical, structural, etc. IoT devices are becoming popular in many different applications for example domotic, industrial, automotive, etc. Hence, every network node should be able to carry out its native tasks and besides communicate with the other network elements. Thus, they can sense physical quantity, actuate some control policies and elaborate data based on the application requirements. In addition, they have a communication channel typically wireless (for obvious necessities) to interact with the other end-nodes. The development of these systems is subordinate to classical electronic system constraints such as energy efficiency, small size, and low cost. The energy restrictions and especially the required low power consumption, are due to both "green" environmental policies and evident technical issues since each element of the network could have battery power supply. Then, the research aims to improve both energy performance and energy efficiency in every end-node component. For instance, this thesis presents an architecture that provides configurability to the elaboration unit increasing its energy efficiency. It is also presented an additional circuit that allows the end-nodes to drastically reduce its power consumption during the idle-listening phase.

These systems are typically realized in printed circuit board systems combining many different integrated circuits as Application Specific Standard Products (AS-SPs), but nowadays, the technology scaling allows one to integrate as much as possible in a unique integrated circuit resulting system-on-chip. These system-on-chips can integrate different kinds of programmable and non-programmable elaboration units, communication systems and a huge variety of dedicated peripherals. The elaboration unit can be non-programmable like Application-Specific Integrated Circuit (ASIC) allowing the best performances but implying both non-negligible Non-Recurring Engineering (NRE) costs and the impossibility to reuse the same SoC in different applications. On the other hand, there exist programmable elaboration units such as Application Specific Instruction-set Processors (ASIPs), CPUs or Programmable Logic Devices (PLDs) which allow one to drastically reduce NRE costs and thanks to programmability to reuse the same SoC for different applications. Typically, the communication protocols between each end-node can vary from the transmission medium (wired or wireless), data distribution (serial or parallel) and clock behavior (synchronous or asynchronous), etc. For instance, SoCs can have either industrial or automotive fieldbus interfaces, otherwise low-power wireless communication systems.

Communication interfaces have not negligible impact on the overall system power consumption, hence, are requested optimization design procedures at each layer of the communication system. For instance, every network node has an idle-listening phase where the node turns on the RF receiving circuit waiting for instruction or data from other network elements. In order to avoid data package lost, this phase should be well extended and may be redundant, which results in a non-negligible extra power consumption. Therefore, to increase energy efficiency could be necessary an architectural change of the classical system structure. Thus, semiconductor companies are designing different kinds of SoCs for different types of applications, to optimize the offered capabilities and hence, the performances. These ICs are literally system-on-chips, since they can also have embedded sensors and in some cases power devices necessary to the cyber-physical interaction.

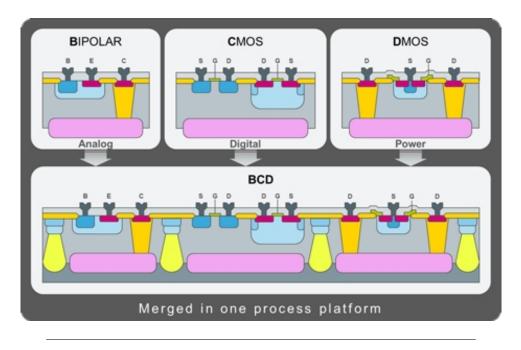

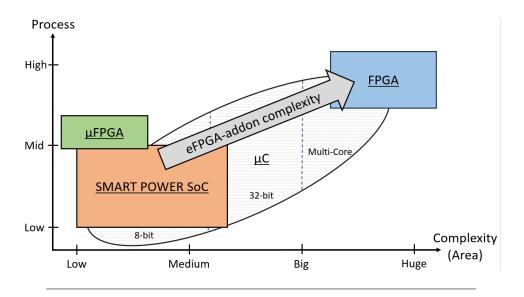

In this thesis, we are focusing on the smart power arena which is an excellent scenario for the SoC development, since smart power combines all the SoC features, from physical quantity sensing, both data elaboration and communication, and decision actuation to power circuits. Thus, in these systems, there is a coexistence of analog, digital and power circuits. In this kind of application, the elaboration unit does not need extremely high computation performance, since smart power tasks require just simple finite state machines as a computational base model instead of complex parallel computing structures. Thus, the elaboration unit should generate output patterns based on inputs and not intensively process data. This type of controller is very diffused for example in motion control, lighting control, and power management. In order to realize integrated circuits provided with analog, digital and power transistors there exists the BCD (Bipolar CMOS DMOS) technology. Certainly, this coexistence implicates numerous issues in terms of isolation, reliability, etc. addressed by both process and circuit designers, making this technology appealing for widespread usage in the IoT arena. Moreover, CMOS technology node of BCD technology is not too scaled as standard CMOS technologies, historically targeting ASIC solutions, whereas currently, BCD is becoming appealing for higher complexity CMOS programmable circuits since it can have 130 nm and 90 nm transistors even if it provides just few metal layers for the routing.

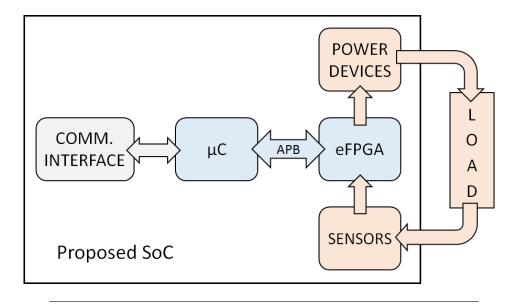

In this scenario, the core of my research is to design and evaluate the performance of an elaboration unit that consists of a microcontroller and an embedded FPGA (eFPGA). Starting from the system HDL code, to the layout generation, the elaboration unit is implemented in 90 nm BCD technology of STMicroelectronics. The performance evaluation is performed comparing data from back-annotate simulation and measurements (when possible) of different elaboration unit implementations, to carry out various kinds of applications. Starting from both microcontroller HDL code and eFPGA HDL code (presented by a previous Ph.D. student), through a standard cell-based digital design flow the system is implemented in BCD technology, which is, to the best of our knowledge the first reconfigurable heterogeneous system targeting smart power applications. The performance evaluation is carried out comparing both energy and latency data of different devices, in carrying out different kinds of applications, corresponding to different kinds of computational models.

Besides, the research work has also contributed to design a wake up radio integrated circuit in 90 nm BCD technology of STMicroelectronics, sent to fabrication. In this collaboration, the PhD work focuses on the design of some blocks of the wake up radio system at the transistor level, performing a full custom layout.

The proposed elaboration unit is a heterogeneous system (presented in [1]) composed of PULPino, which is an open-source ultra low-power microcontroller [2], coupled with a very small fully-synthesizable embedded FPGA [3], [4]. The idea is to use the eFPGA as a smart power application dedicated peripheral, while microprocessor can manage other kinds of more complex computations such as data processing, communication interface management, etc., or can be switched in sleep mode to reduce power consumption. This is also a new point of view for the eF-PGA usage, typically used for high-density parallel computing and hence, usually designed with a hard-macro approach, optimizing the circuit at the transistor level to optimize density, performances and thus costs. On the other hand, the reconfigurability addition has a non-negligible area overhead which is around 20%.

In order to justify the area overhead due to the eFPGA addition, it is evaluated an energy-aware analysis comparing the performance of PULPino, of the eFPGA, of a very common commercial microcontroller (STM32) and an ASIC implementation to carry out different applications. The resulting data show that using the eFPGA to perform smart power tasks, hence implementing simple finite state machines, is possible to obtain better performance in terms of energy consumption. Obviously, the eFPGA does not have the same performances of an ASIC implementation but it allows the system to be reused in different applications without integrated circuit refabrication. The energy gain reason is located in the nature of the different architecture circuits. eFPGA directly maps in hardware circuit a finite state machine whereas processor needs to execute many load/store, jump/branch instructions just to update few bits of both finite state machine state and outputs. There is also an advantage in terms of circuit latency, in fact, the eFPGA updates its output at every clock cycle and hence, in this case, the latency depends on the eFPGA clock frequency. Then, the SoC user can program the eFPGA clock frequency based on the application latency requirements. Using a processor implementation, the latency is

related to both the number of instructions needed to update the microprocessor outputs and the processor frequency (supposing the optimistic case that the processor can execute one instruction per clock cycle).

As already mentioned, the communication interface has a notable impact on system power consumption. Therefore, in order to improve the system-on-chip energy performance, we propose an additional always-on ultra low-power circuit for the wireless communication unit. The additional circuit aims to wake up the rest of the system after the receiving of a wake up radio signal transmitted from another element of the network. In this way, one can switch in sleep mode both the elaboration and the main radio transceiver, to reduce the power consumption, while keeping active just the wake up radio which is an ultra low-power circuit.

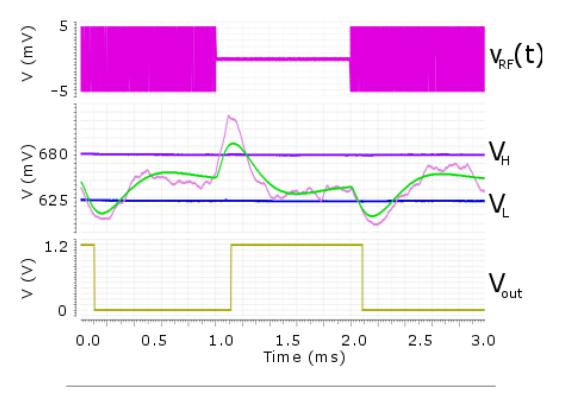

We propose a nano-watts wake up radio for On-Off Keying modulation working at 868 MHz, which consists of a demodulator/amplifier and a Schmitt trigger with 5-bits programmable threshold to generate a digital signal. The operating point of the overall wake up radio system is designed to be in subthreshold region. Then, exploiting the non-linearities of subthreshold MOSFET, the demodulator can detect the envelope of the received signal and provides the right amplification. Then, the detected envelope is digitalized through the Schmitt trigger. Thanks to enough level of amplification, the system performances are not restricted to the Schmitt trigger input offset voltage.

As already said, my research aims to analyze the proposed heterogeneous reconfigurable SoC in the smart power arena and to present our wake up radio integrated circuit. Therefore, the thesis is organized following a system top-down approach as follows:

- **Chapter 2** provides an introduction to the smart power arena. In particular, are explained the typical features of smart power applications and microelectronic technology which targets this kind of applications. In addition, are introduced different architectures to realize elaboration units.