Silicon photonic switching: from building block design to intelligent control

Yishen Huang

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy under the Executive Committee of the Graduate School of Arts and Sciences

COLUMBIA UNIVERSITY

© 2020

# Yishen Huang

All Rights Reserved

# Abstract

Silicon photonic switching: from building block design to intelligent control

## Yishen Huang

The rapid growth in data communication technologies is at the heart of enriching the digital experiences for people around the world. Encoding high bandwidth data to the optical domain has drastically changed the bandwidth-distance trade-off imposed by electrical media. Silicon photonics, sharing the technological maturity of the semiconductor industry, is a platform poised to make optical interconnect components more robust, manufacturable, and ubiquitous. One of the most prominent device classes enabled by the silicon photonics platform is photonic switching, which describes the direct routing of optical signal carriers without the optical-electrical-optical conversions. While theoretical designs and prototypes of monolithic silicon photonic switch devices have been studied, realizing high-performance and feasible switch systems requires explorations of all design aspects from basic building blocks to control systems. This thesis provides a holistic collection of studies on silicon photonic switching in topics of novel switching element designs, multi-stage switch architectures, device calibration, topology scalability, smart routing strategies, and performance-aware control plane.

First, component designs for assembling a silicon photonic switch device are presented. Structures that perform 2×2 optical switching functions are introduced. To realize switching granularities in both spatial and spectral domains, a resonator-assisted Mach-Zehnder interferometer design is demonstrated with high performance and design robustness. Next, multi-stage monolithic switching devices with microring resonator-based switching elements are investigated. An 8×8 switch device with dual-microring switching elements is presented with a well-balanced set of performance metrics in extinction ratio, crosstalk suppression, and optical bandwidth. Continued scaling in the switch port count requires both an

economic increase in the number of switching elements integrated in a device and the preservation of signal quality through the switch fabric. A highly scalable switch architecture based on Clos network with microring switch-and-select sub-switches is presented as a solution to reach high switch radices while addressing key factors of insertion loss, crosstalk, and optical passband to ensure end-to-end switching performance.

The thesis then explores calibration techniques to acquire and optimize system-wide control points for integrated silicon switch devices. Applicable to common rearrangeably non-blocking switch topologies, automated procedures are developed to calibrate entire switch devices without the need for built-in power monitors. Using Mach-Zehnder interferometer-based switching elements as a demonstration, calibration techniques for optimal control points are introduced to achieve balanced push-pull drive scheme and reduced crosstalk in switching operations. Furthermore, smart routing strategies are developed based on optical penalty estimations enabled by expedited lightpath characterization procedures. Leveraging configuration redundancies in the switch fabric, the routing strategies are capable of avoiding the worst penalty optical paths and effectively elevate the bottom-line performance of the switch device.

Additional works are also presented on enhancing optical system control planes with machine learning techniques to accurately characterize complex systems and identify critical control parameters. Using flexgrid networks as a case study, light-weight machine learning workflows are tailored to devise control strategies for improving spectral power stability during wavelength assignment and defragmentation. This work affirms the efficacy of intelligent control planes to predict system dynamics and drive performance optimizations for optical interconnect systems.

# **Table of Contents**

| List of F | iguresiv                                               |

|-----------|--------------------------------------------------------|

| List of T | ables xvii                                             |

| Glossary  | 7 xviii                                                |

| Acknow    | ledgmentsii                                            |

| Chapter   | 1: Introduction and Background1                        |

| 1.1       | An Optically Connected Globe                           |

| 1.2       | Silicon Photonics                                      |

| 1.3       | Photonic Switching                                     |

| 1.3.      | 1 Historical Photonic Switch Designs                   |

| 1.3.      | 2 Silicon Photonic Switch Designs                      |

| 1.4       | Scope of Thesis                                        |

| Chapter   | 2: Switching Elements for Spatial and Spectral Domains |

| 2.1       | Introduction17                                         |

| 2.2       | Working Principles                                     |

| 2.3       | Device Design and Characterization                     |

| 2.4       | Chapter Summary                                        |

| Chapter   | 3: Multi-stage MRR-based Switch Fabrics                |

| 3.1       | Introduction                                           |

| 3.2       | Dual-Microring-Based 8×8 Switch                        |

| 3.2.      | 1 Switch Architecture and Design                       |

| 3.2     | .2 Switching Element Design and Characterization                           | 38  |

|---------|----------------------------------------------------------------------------|-----|

| 3.2     | .3 Switch Fabric Performance                                               | 46  |

| 3.2     | .4 Summary                                                                 | 50  |

| 3.3     | Scalable Microring-Based Clos Switch Fabric with Switch-and-Select Stages  | 51  |

| 3.3     | .1 Clos Architecture with Switch-and-Select Sub-Switches                   | 52  |

| 3.2     | Silicon 4×4 Sub-Switch for a 16×16 Clos Switch Fabric                      | 61  |

| 3.3     | .3 Clos Switch Fabric Performance Exploration                              | 68  |

| 3.3     | .4 Summary                                                                 | 78  |

| 3.4     | Chapter Summary                                                            | 79  |

| Chapter | 4: Calibration Techniques for Photonic Switches                            | 80  |

| 4.1     | Introduction                                                               | 80  |

| 4.2     | Automated Calibration Techniques for MZI-based Switch Fabrics              | 82  |

| 4.2     | .1 Rearrangeably Non-blocking Switch Calibration without Built-in Monitors | 82  |

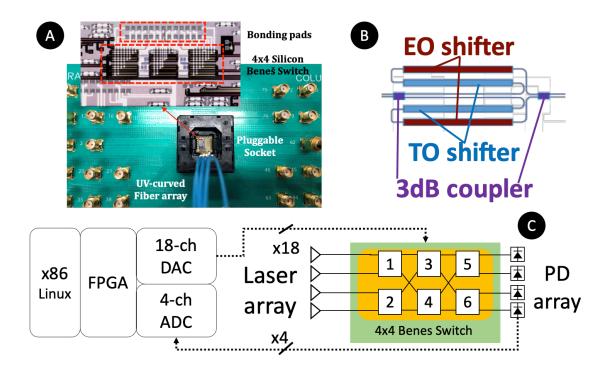

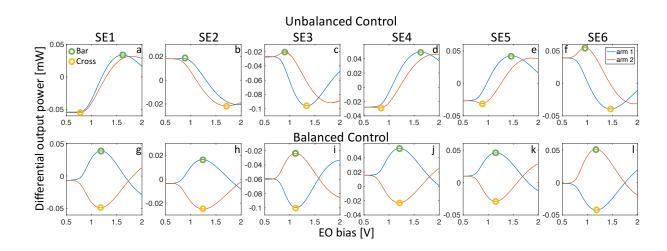

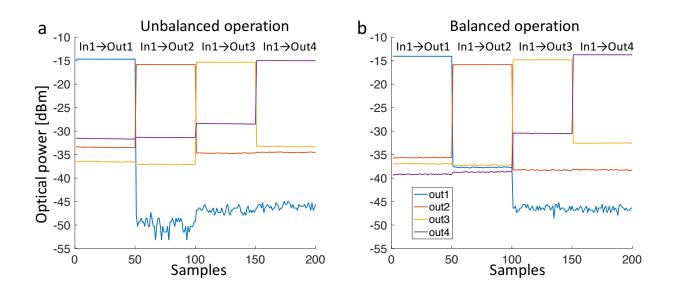

| 4.2     | .2 Demonstration of Rapid Switch Calibration                               | 87  |

| 4.3     | Crosstalk-aware Calibration Techniques for Switch Fabrics                  | 92  |

| 4.4     | Chapter Summary                                                            | 96  |

| Chapter | 5: Optical Switching Topologies and Smart Routing                          | 97  |

| 5.1     | Introduction                                                               | 97  |

| 5.2     | Switch Topologies and Switching States                                     | 99  |

| 5.3     | Fabric-wide, Penalty-Optimal Switch Routing Strategies                     | 106 |

| 5.3     | .1 Switch Path Characterization                                            | 107 |

| 5.3     | .2 Performance-Aware Switch Routing Schemes                                | 110 |

| 5.3.      | 3 Routing Control for a Beneš Switch Device                             | 112 |

|-----------|-------------------------------------------------------------------------|-----|

| 5.4       | Chapter Summary                                                         | 116 |

| Chapter   | 6: Intelligent Control Plane with Machine Learning                      | 117 |

| 6.1       | Introduction                                                            | 117 |

| 6.2       | EDFA Power Excursions                                                   | 119 |

| 6.3       | Mitigation of EDFA Power Excursions during Dynamic Channel Provisioning | 121 |

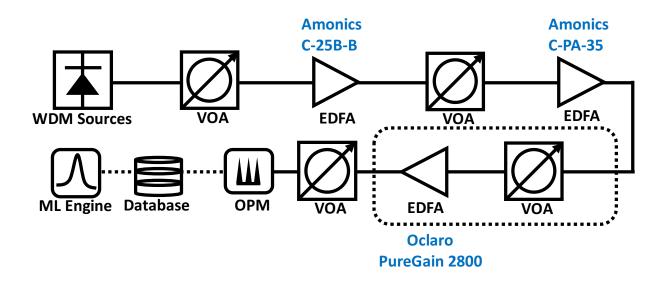

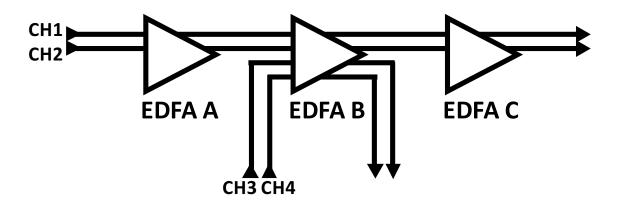

| 6.3.      | 1 Testbed Design                                                        | 122 |

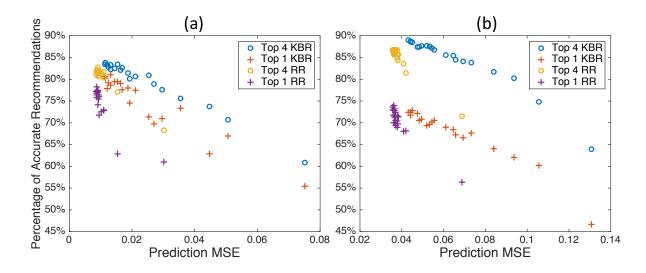

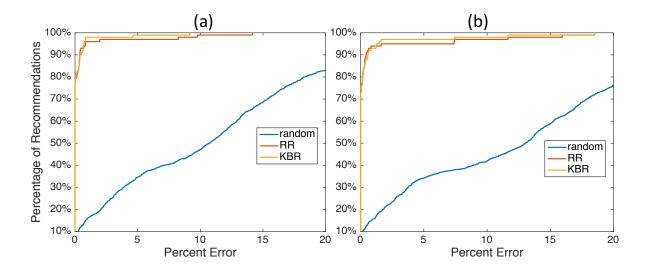

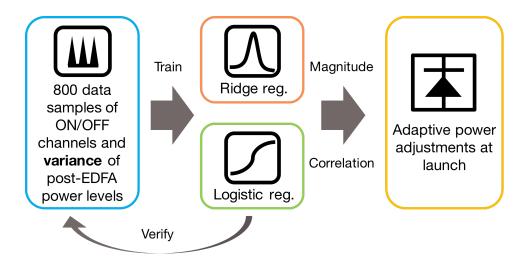

| 6.3.      | 2 Machine Learning Models and Analysis                                  | 124 |

| 6.3.      | 3 Machine Learning Assisted Channel Provisioning                        | 131 |

| 6.3.      | 4 Scalability of the ML Engine                                          | 139 |

| 6.3.      | 5 Summary                                                               | 141 |

| 6.4       | Power Excursion Mitigation for Flexgrid Defragmentation with ML         | 142 |

| 6.4.      | 1 Defragmentation Methods                                               | 143 |

| 6.4.      | 2 Methodology                                                           | 144 |

| 6.4.      | 3 Experimental Demonstration                                            | 151 |

| 6.4.      | 4 Scalability of the Approach                                           | 159 |

| 6.4.      | 5 Summary                                                               | 160 |

| 6.5       | Chapter Summary                                                         | 161 |

| Chapter   | 7: Final Remarks                                                        | 162 |

| 7.1       | Summary of Contributions                                                | 162 |

| 7.2       | Recommendations for Future Work                                         | 164 |

| Bibliogra | aphy                                                                    | 167 |

# **List of Figures**

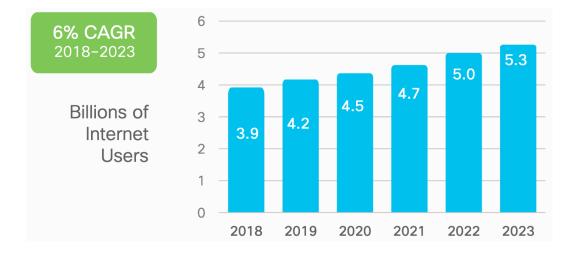

| Figure | 1-1: Past and projected number of internet users from [1]1                                               |

|--------|----------------------------------------------------------------------------------------------------------|

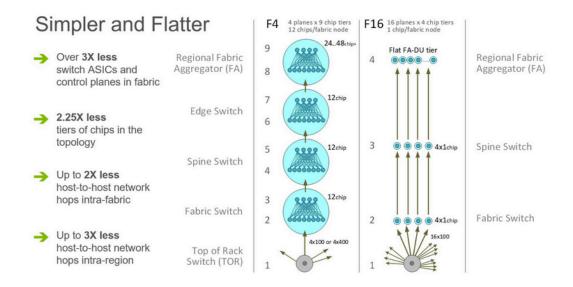

| Figure | 1-2: The upgraded architecture of Facebook datacenter network, F16, and its comparison                   |

|        | with the previous generation design, F4, from [3]2                                                       |

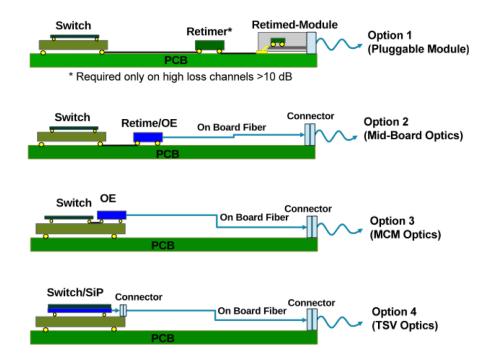

| Figure | 1-3: Schematics for increasingly integrated optics and switch ASICs from [5]                             |

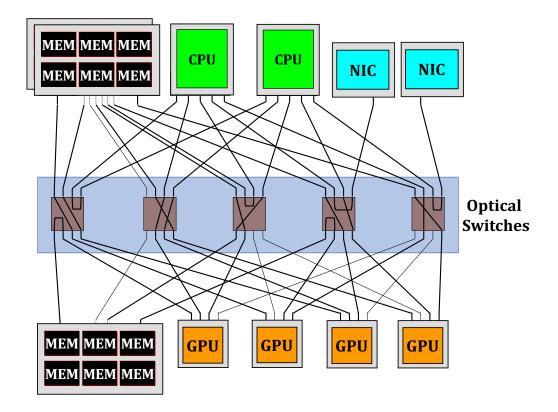

| Figure | 1-4: A conceptual photonic integrated network for hardware resource disaggregation with                  |

|        | photonic switches. Adopted from [8]4                                                                     |

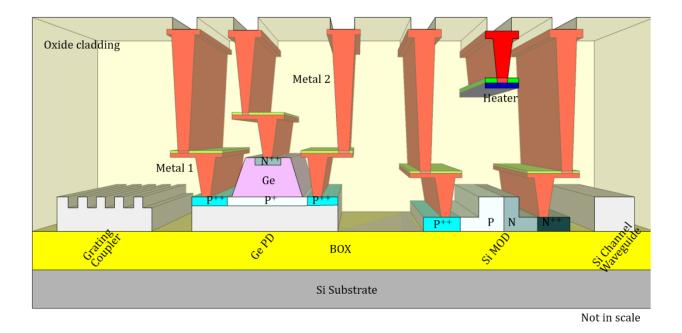

| Figure | 1-5: Example layer stack of the silicon photonic platform from AMF [13]                                  |

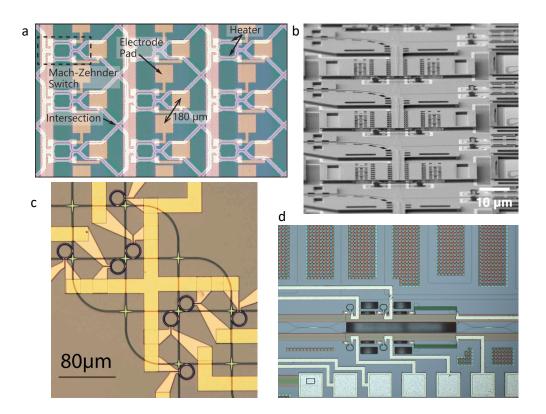

| Figure | 1-6: Micrographs of silicon photonic SEs implemented with (a) MZI [39], (b) MEMS-                        |

|        | actuated DCs [52], (c) MRRs [43], and (d) MRR-assisted MZIs [51] 10                                      |

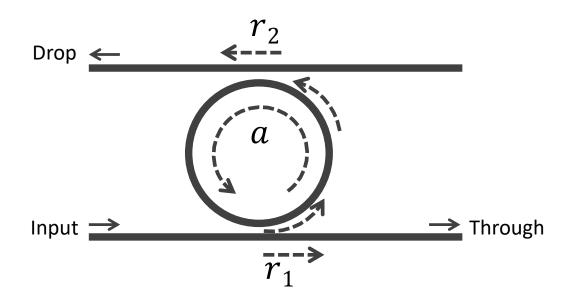

| Figure | 1-7: Schematic of an MRR SE in the through-drop configuration 12                                         |

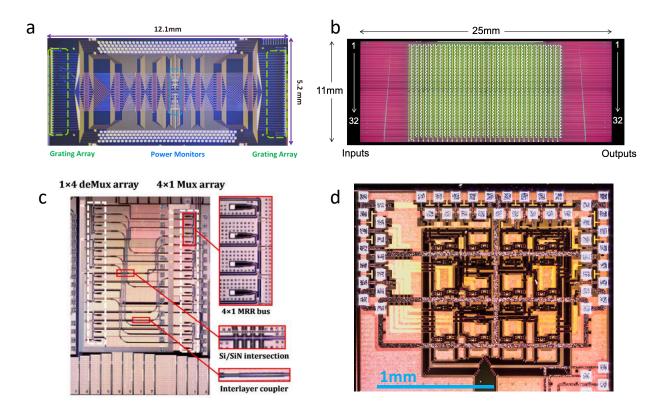

| Figure | 1-8: Notable silicon photonic switch fabric demonstrations with (a) 32x32 MZI-based                      |

|        | Beneš network [54], (b) 32x32 MZI-based PILOSS network [55], (c) 4x4 MRR-based                           |

|        | switch-and-select network [44], and (d) 8x8 MRR-based Omega network [56] 12                              |

| Figure | 1-9: Schematic of an MRR-assisted MZI SE                                                                 |

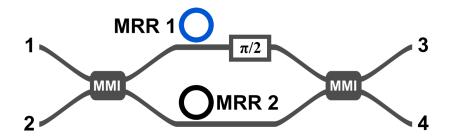

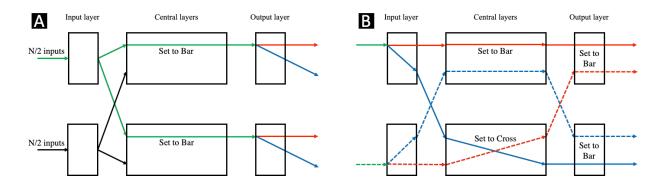

| Figure | 2-1: (a) Schematic design for space-and-wavelength selective switch with parallel                        |

|        | switching planes and wavelength (de)multiplexers. (b) Schematic design for space-and-                    |

|        | wavelength selective switch built on SEs with spatial and spectral switching granularity.                |

|        |                                                                                                          |

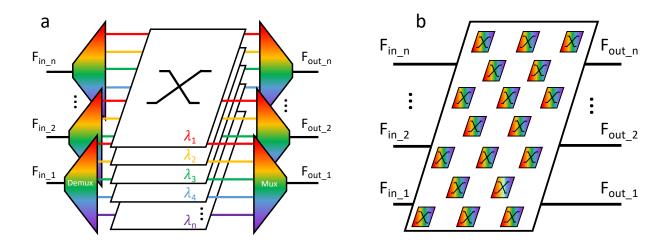

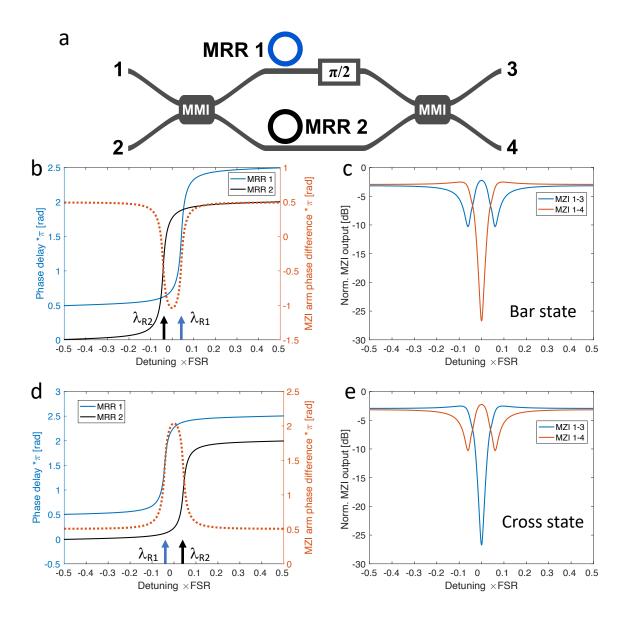

| Figure | 2-2: Schematic of a $2 \times 2 \times M\lambda$ SE with MRR phase shifters. Each pair of MRRs aligns to |

|        | the input wavelength channel of the same color                                                           |

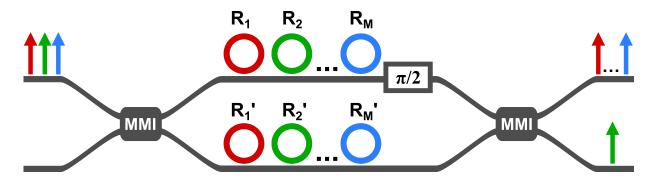

| Figure | 2-3: (a) Schematic of the single channel MRR-assisted MZI. (b) Induced phase by MRR 1                    |

|        |                                                                                                          |

and MRR 2 and the MZI arms' phase difference for Bar switching state, with center

| resonances of MRR 1 and MRR 2 labeled as $\lambda_{R1}$ and $\lambda_{R2}$ , respectively. (c) Bar-state MZI |

|--------------------------------------------------------------------------------------------------------------|

| output spectra for paths Port 1 to Port 3 and Port 1 to Port 4. (d) Induced phase by MRR 1                   |

| and MRR 2 and the MZI arms' phase difference for Cross switching state. (e) Cross-state                      |

| MZI output spectra for paths Port 1 to Port 3 and Port 1 to Port 4                                           |

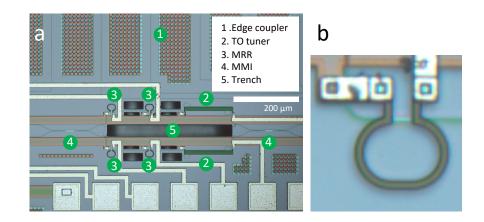

| Figure 2-4: (a) Micrograph of the $2 \times 2 \times 2\lambda$ SE. (b) MRR heater structure                  |

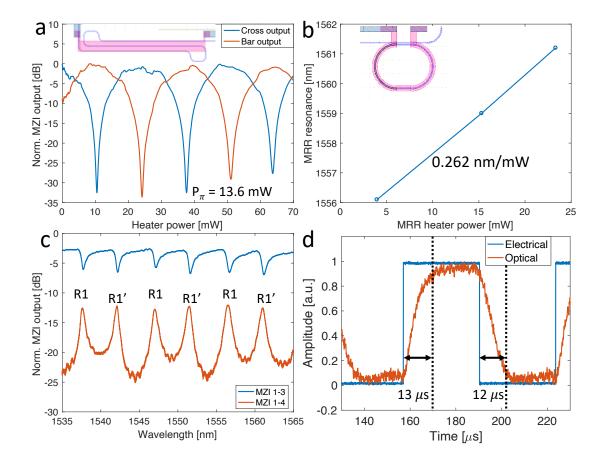

| Figure 2-5: (a) MZI switching output as a function of TO tuner power consumption; the inset                  |

| shows the TO tuner design. (b) Resonance tuning power with the TO MRR shifter. (c)                           |

| Offset MRR resonances while the MZI is biased to Bar state. (d) Optical rise and fall                        |

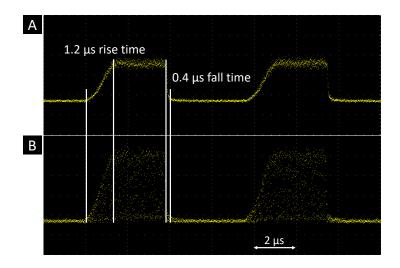

| times when the MRR TO shifter is driven with a 15 kHz electrical square wave signal. 23                      |

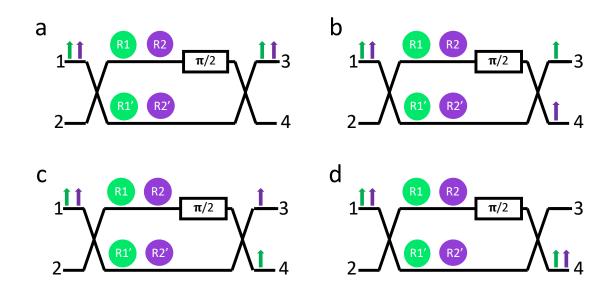

| Figure 2-6: (a)-(d) Illustrations of (Bar, Bar), (Bar, Cross), (Cross, Bar), and (Cross, Cross) states       |

| for the two independently switched channels                                                                  |

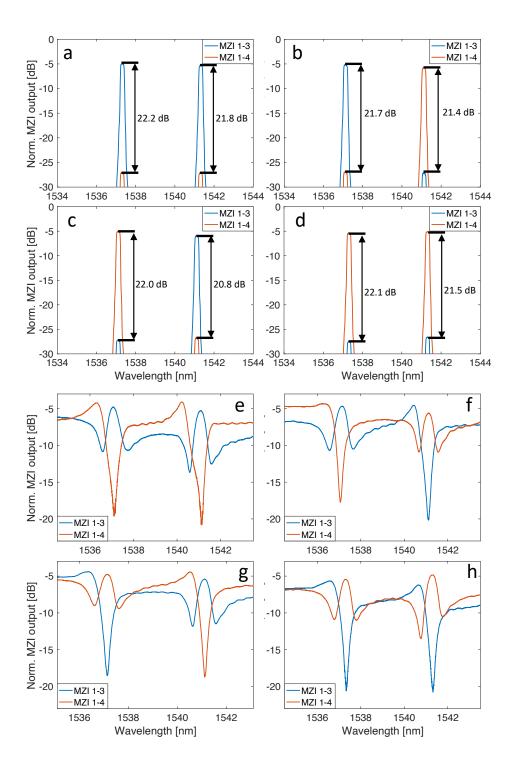

| Figure 2-7: (a)-(d) Signal and leakage power levels with two CW lasers in the four switching                 |

| states. Crosstalk suppression levels are indicated. (e)-(h) Transmission spectra for both                    |

| switch paths in the four switching states                                                                    |

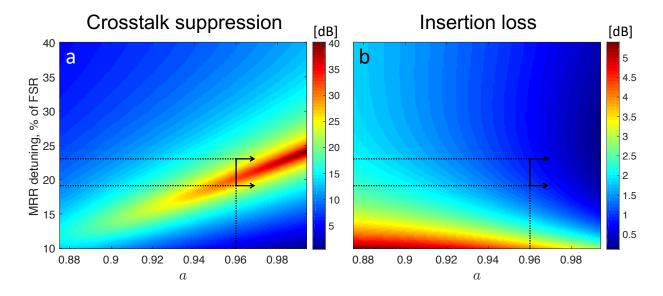

| Figure 2-8: Crosstalk suppression (a) and IL (b) over ranges of MRR detuning and roundtrip                   |

| amplitude transmission                                                                                       |

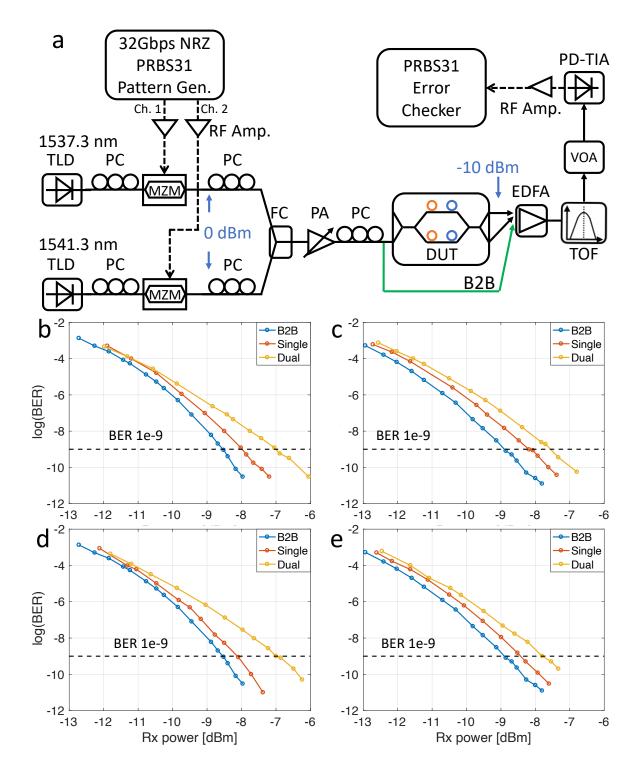

| Figure 2-9: (a) Data experiment setup schematic. (b)-(e) BER curve for Switching States (Bar,                |

| Cross)-Channel 1, (Bar, Cross)-Channel 2, (Cross, Bar)-Channel 1, and (Cross, Bar)-                          |

| Channel 2, respectively, compared among B2B, single- and dual-channel cases                                  |

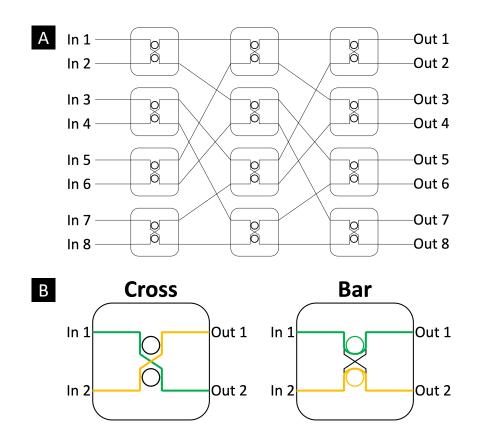

| Figure 3-1: (A) Schematic of the 8×8 Omega network implemented with 12 2×2 SEs. (B)                          |

| Illustration of the SE's Cross and Bar states and their corresponding dual-MRR                               |

| configurations                                                                                               |

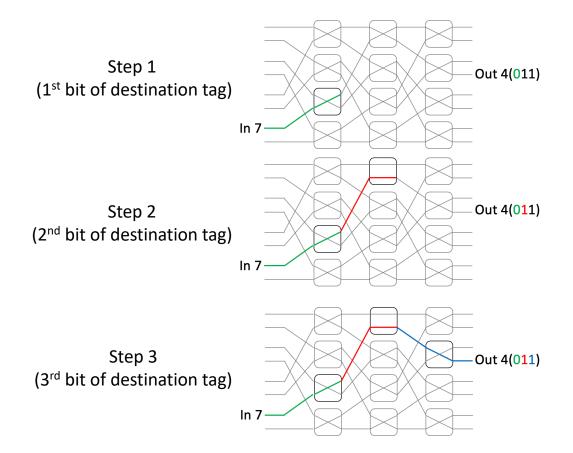

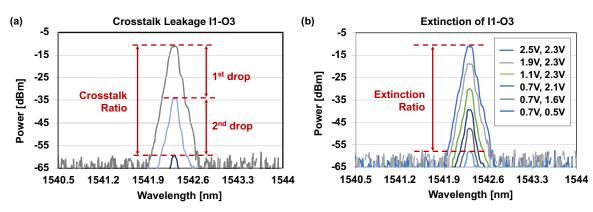

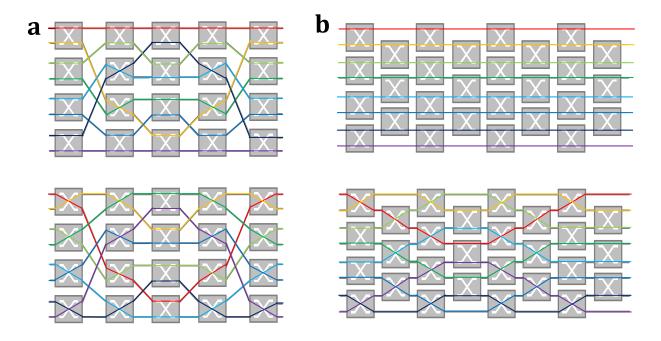

- Figure 3-3: An example of destination-based routing in Omega network. The output's binary label indicates the configuration states of the three SEs along the lightpath in the sequence of the SEs traversed by the optical signal, the bit 0 selects the upper output of the corresponding SE, and the bit 1 selects the lower output. Hence, a label 011 indicates setting the first SE to Cross, second SE to Bar, and third SE to Cross, to connect a link from Input 7 to Output 4.

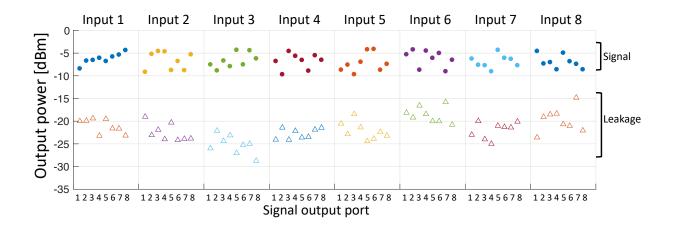

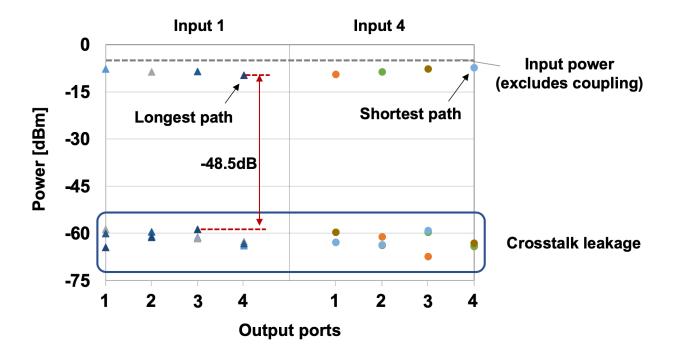

- Figure 3-12: On-chip signal power and worst-case leakage power levels for all switch paths connecting every input to every output. Grating coupler loss is compensated at injection.

Worst-case crosstalk is taken as the difference between signal and leakage power for each connection.

48

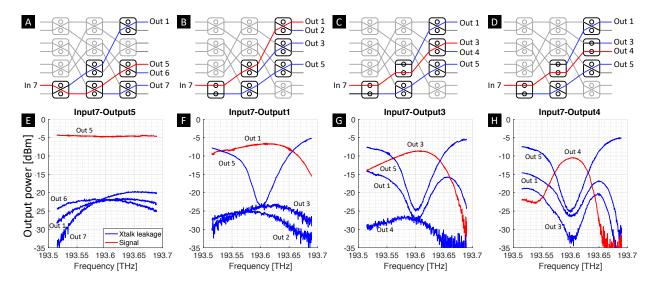

- Figure 3-13: (A-D) Illustration of the switch paths through 0 3 on-resonance SEs, respectively. (E-H) Signal and 1<sup>st</sup> order crosstalk spectra for the routing schemes shown in A-D. ...... 48

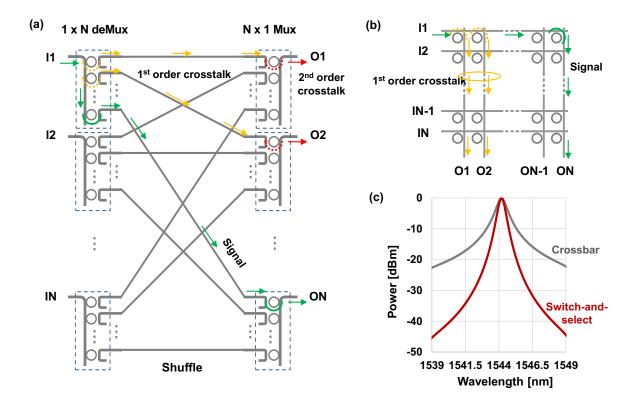

- Figure 3-15: (a) Schematic of the MRR-based switch-and-select topology. Signal (green lines) routes from input 1 to output N. (b) Schematic of the MRR-based crossbar topology.

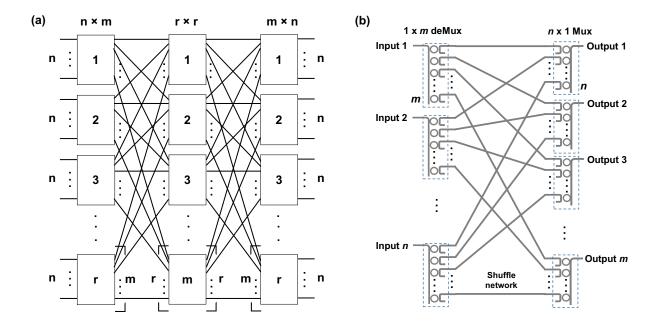

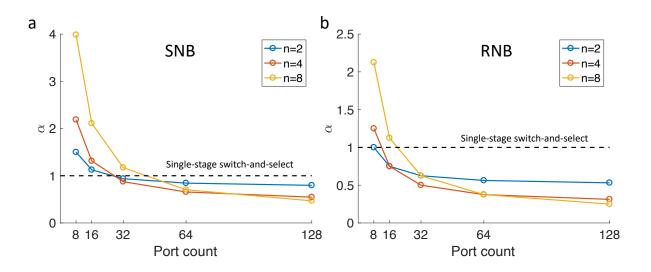

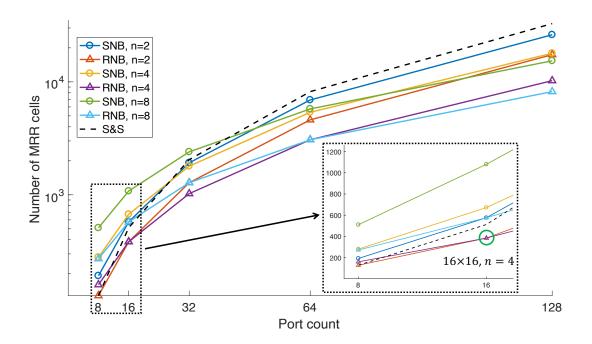

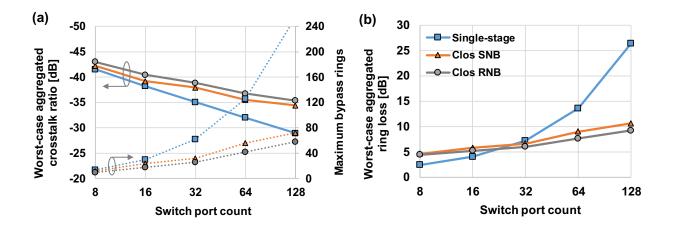

- Figure 3-17: Ratio between the number of switching elements in the (a) SNB Clos design and the single-stage switch-and-select, and (b) RNB Clos design and the single-stage switch-and-select, for n=2, 4, 8.

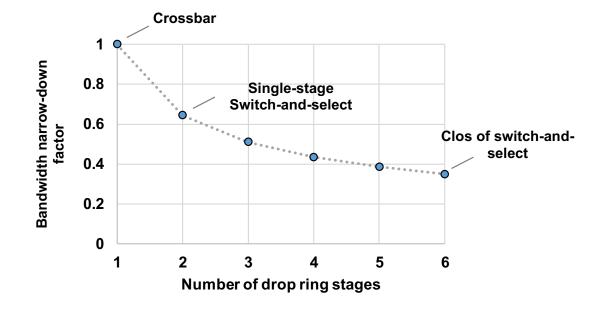

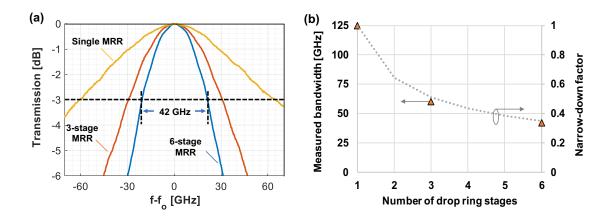

- Figure 3-20: Bandwidth narrow-down factor as a function of the number of drop MRRs per path.

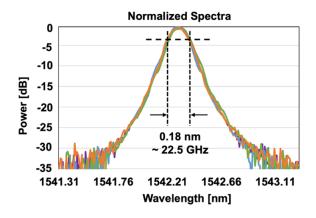

- Figure 3-25: (a) Normalized spectra with resolution at 0.1 nm. (b) BER as a function of received optical power at 12.5 Gb/s for path 1-4 and 4-4. Insets show the measured eye diagrams.

- Figure 3-27: (a) Measured optical spectra for single, 3-stage, 6-stage add-drop MRRs.

(b) Measured optical bandwidth with fitted narrow-down factor from Figure 3-20. ..... 68

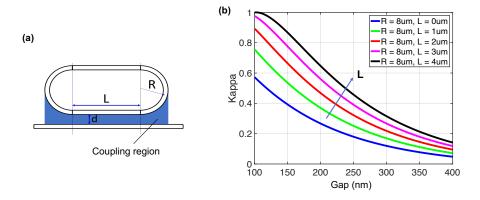

| Figure 3-32: (a) Schematic of a racetrack MRR with straight section length of $L$ , gap of d, and     |

|-------------------------------------------------------------------------------------------------------|

| radius of R. (b) Comparison of ring-bus coupling coefficient between $L=0, 1, 2, 3$ , and 4           |

| μm, as a function of MRR-bus gap76                                                                    |

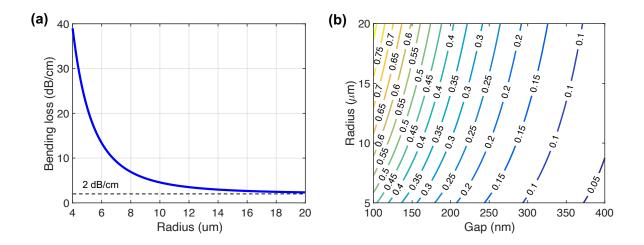

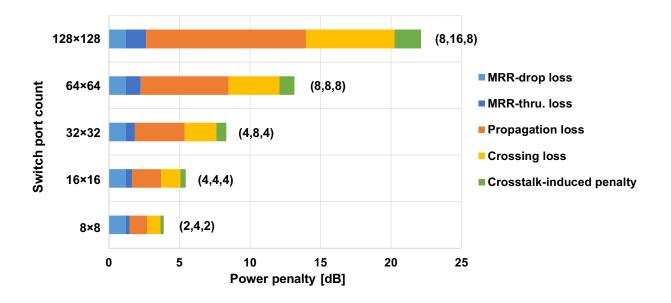

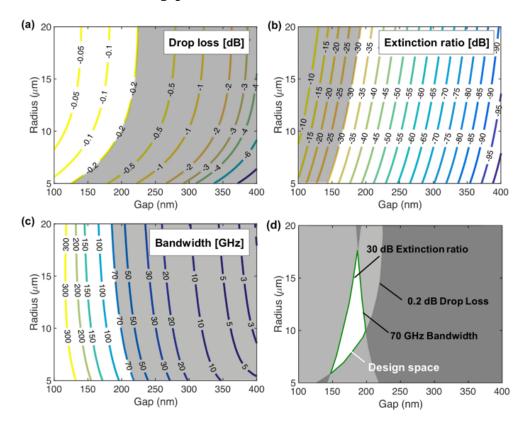

| Figure 3-33: Design space exploration of second-order add-drop MRR in racetrack structure with        |

| $L=2 \ \mu m$ for (a) drop-state insertion loss, (b) out-of-band ER, (c) 3 dB optical bandwidth,      |

| and (d) overall design space76                                                                        |

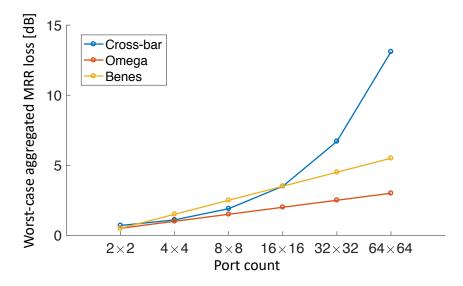

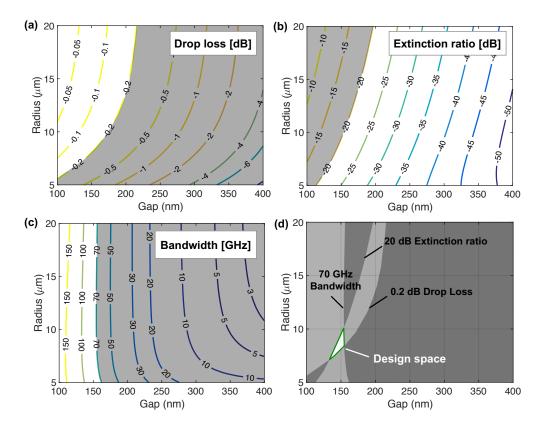

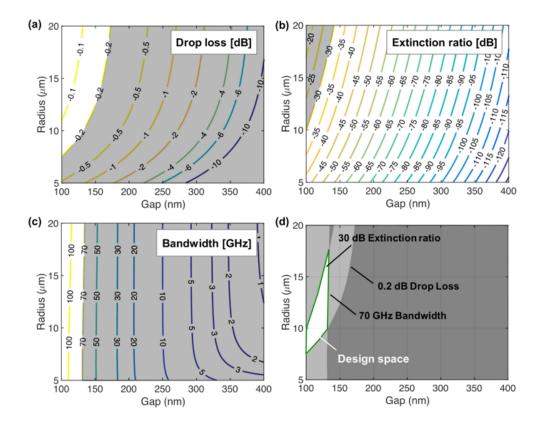

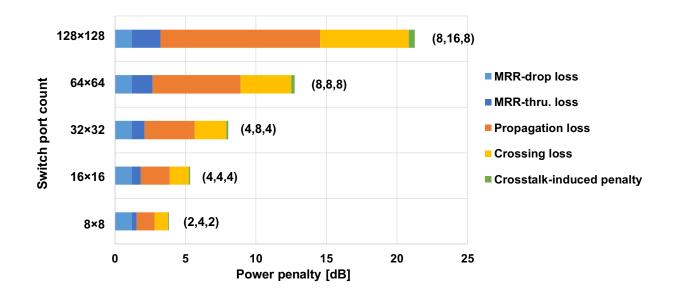

| Figure 3-34: Power penalty breakdown for the longest path in various Clos switch scales using         |

| second-order racetrack MRR units. The $(n, r, m)$ parameter values of each network are                |

| shown next to the corresponding bar                                                                   |

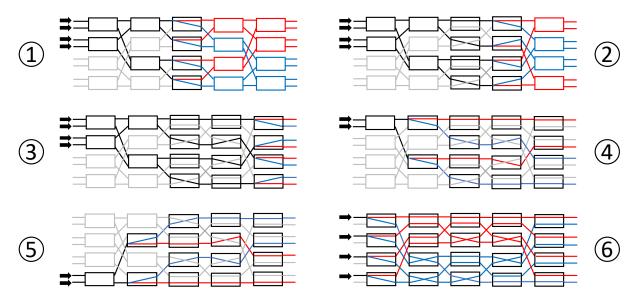

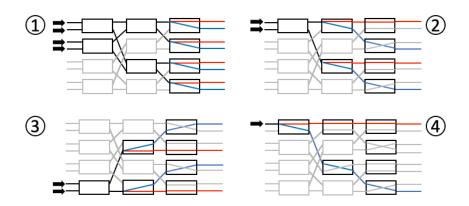

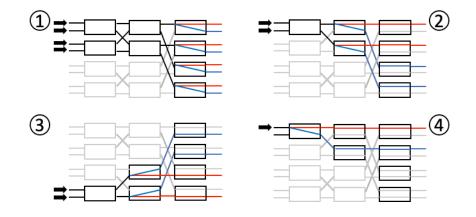

| Figure 4-1: (A) Illustration of the top half of inputs routed to top (red path) or bottom (blue path) |

| set of outputs by the sub-Beneš. (B) Recursive structure of Beneš architecture allows                 |

| upper fabric inputs to directly address the top input of SEs in the central layer                     |

| Figure 4-2: (A) Calibration of the output layer SEs while controlling the central layer. (B)          |

| Calibration of the input layer SEs while controlling the central layer and the output layer.          |

|                                                                                                       |

| Figure 4-3: Step-by-step calibration procedure for an 8×8 Beneš switch. 4 SEs in the central          |

| layer are calibrated in Step 1; 4 SEs in the central+1 layer are calibrated in Step 2; 4 SEs          |

| in the output layer are calibrated in Step 3; 4 SEs in the central-1 layer are calibrated in          |

| Step 4-5; 4 SEs in the input layer are calibrated in Step 6                                           |

| Figure 4-4: Step-by-step calibration procedure for an 8×8 Banyan switch. Step 4 is generalized to     |

| all SEs in the input layer for brevity                                                                |

| Figure 4-5: Step-by-step calibration procedure for an 8×8 Butterfly switch. Step 4 is generalized     |

| to all SEs in the input layer for brevity                                                             |

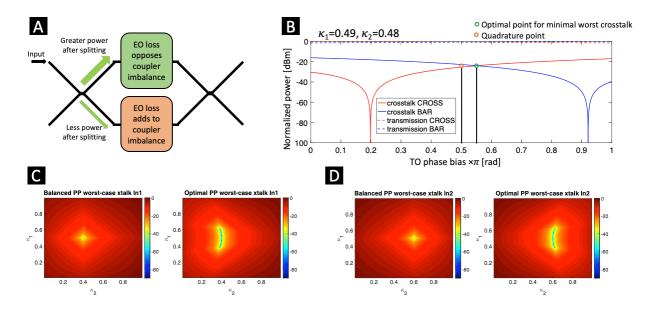

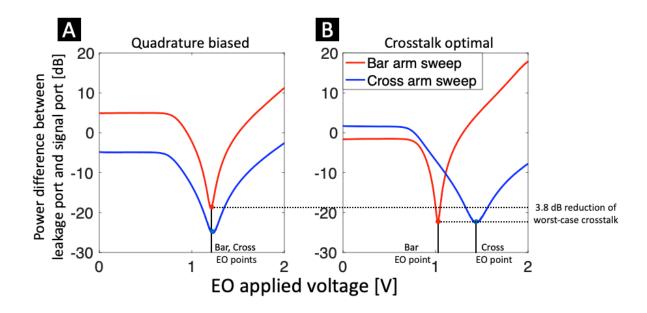

- Figure 4-9: (A) Illustration of the interactions between uneven splitting of in-coupler and the switching loss of EO shifters in both MZI arms. (B) Case study illustrating crosstalk levels of an MZI SE under quadrature bias and crosstalk-aware bias, given a pair of in-coupler and out-coupler power coupling coefficients  $\kappa_1$  and  $\kappa_2$ . (C-D) Comparison of the worst-case crosstalk heatmaps for a signal from Input 1 (C) and Input 2 (D) between quadrature biased balanced push-pull switching and crosstalk-optimal operation at wide range of coupler coupling coefficient values, showing the proposed methods can drastically increase tolerance margins of  $\kappa_1$  while maintaining low worst-case crosstalk.

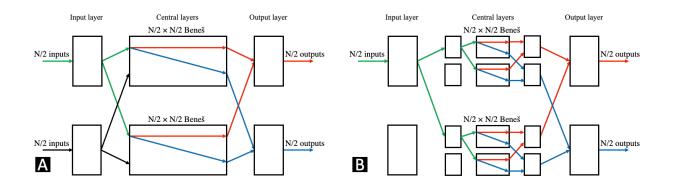

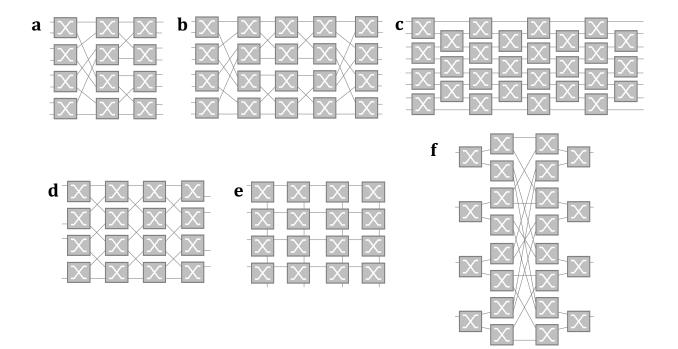

| Figure 5-1: Schematic of switch architectures: (a) Banyan, (b) Beneš, (c) N-stage planar, (d)  |  |

|------------------------------------------------------------------------------------------------|--|

| PILOSS, (e) crossbar, and (f) switch-and-select. Note that (a), (b), and (c) have 8×8 port     |  |

| count, while (d), (e), and (f) have 4×4 port count100                                          |  |

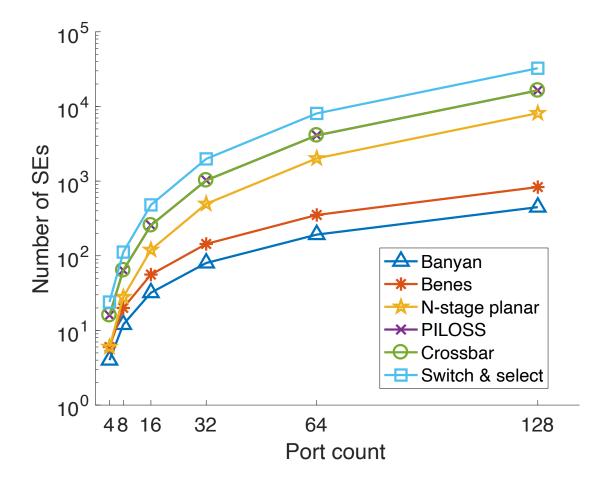

| Figure 5-2: Comparison of the total number of SEs among various switch topologies as a         |  |

| function of port counts in an N×N network103                                                   |  |

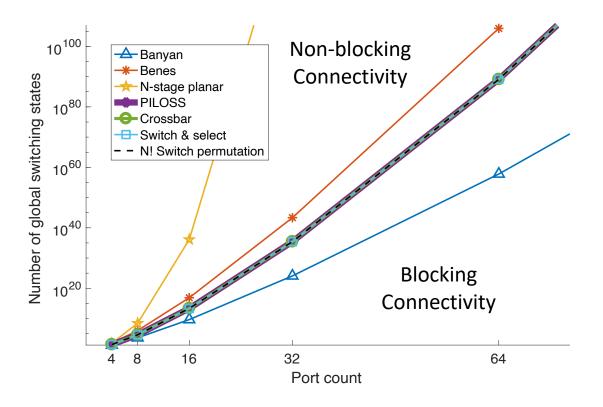

| Figure 5-3: Number of global switching states for Banyan, Beneš, N-stage planar, PILOSS,       |  |

| crossbar, and switch-and-select networks with different port counts                            |  |

| Figure 5-4: Redundant routing paths with same input-output permutations for (a) Beneš, (b) N-  |  |

| stage planar RNB switch fabrics105                                                             |  |

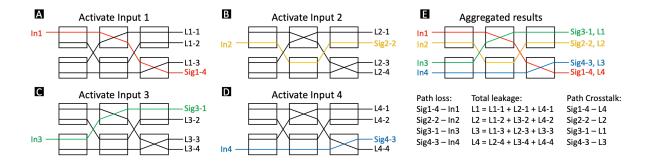

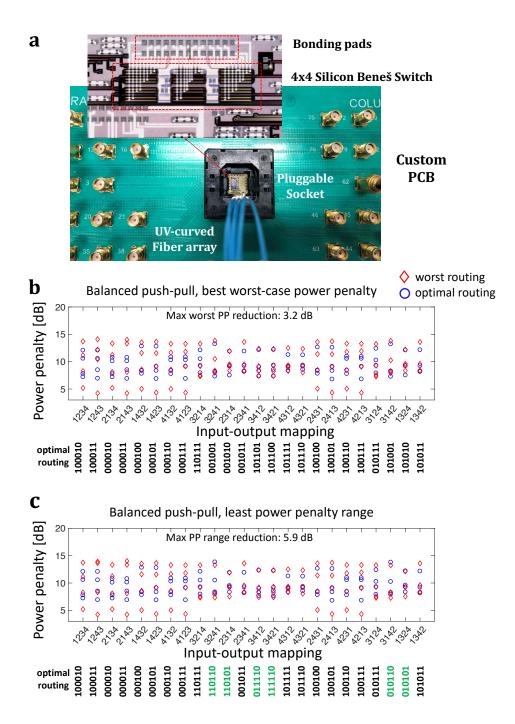

| Figure 5-5: (A-D) Single input results of the same switching state, showing signal power (Sig) |  |

| and leakage power (L). (E) Aggregated results showing loss and crosstalk of all paths for      |  |

| the same switching state                                                                       |  |

| Figure 5-6: (a) Switch test-bed with micrograph inset showing the OPSIS 4×4 silicon MZI-based  |  |

| Beneš switch photo. Comparison of the on-chip penalties between optimal and worst              |  |

| routing options under (b) worst-path-optimal routing and (c) range-optimal routing.            |  |

| Input-output mappings are denoted by how Inputs 1,2,3,4 are reordered at the outputs.          |  |

| Routing configurations are indicated as binary states of 0 (Bar) and 1 (Cross) in the          |  |

| sequence for SEs 1 to 6 for the 4×4 Beneš switch. Green routing states indicate                |  |

| differences in optimal routing as defined by the metrics                                       |  |

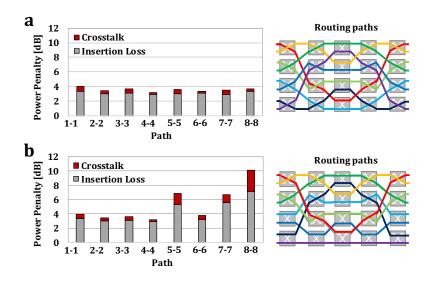

| Figure 5-7: Path power penalties and the switch state for (a) the RMSE-optimal routing option  |  |

| and (b) the least RMSE-optimal routing option115                                               |  |

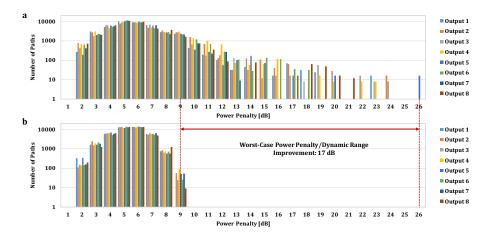

| Figure 5-8: Histogram of path power penalties for (a) worst-case routing and (b) optimized                |  |

|-----------------------------------------------------------------------------------------------------------|--|

| routing for all 40320 (8!) switch permutations, indicating an improvement of $\sim$ 17 dB for             |  |

| both the worst-case path power penalty and dynamic range                                                  |  |

| Figure 6-1: Setup of the multi-span EDFA system; the additional EDFA and VOA in the dashed                |  |

| box are included for the 3-span system                                                                    |  |

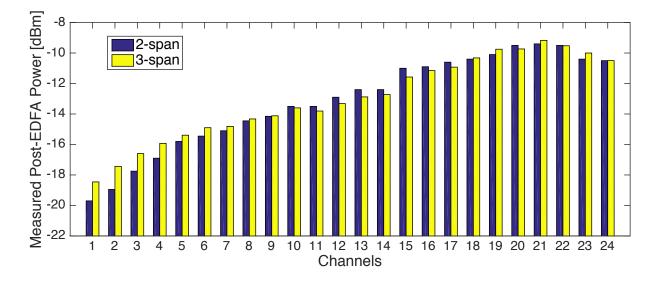

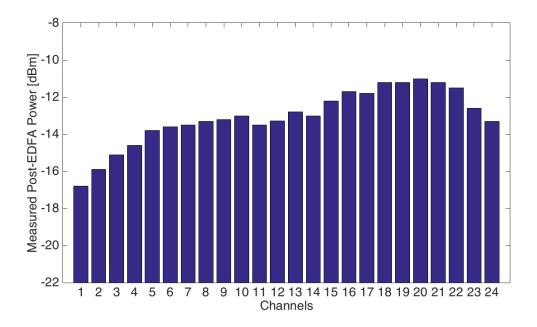

| Figure 6-2: Measured post-EDFA power spectra with 24 ON channels for both systems.                        |  |

| Channels 1 to 24 correspond to ITU-T C-band 194.40THz to 192.10THz with 100GHz                            |  |

| spacing. Channels are launched with uniform power                                                         |  |

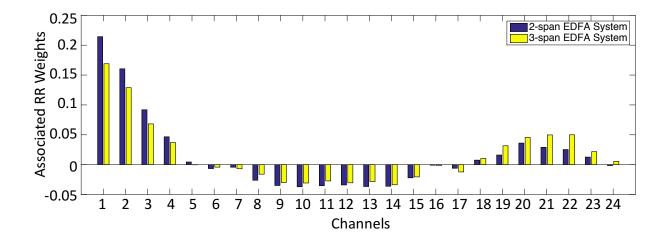

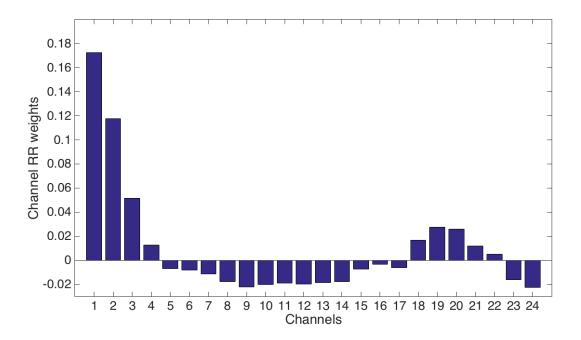

| Figure 6-3: Associated weights assigned to each channel by RR for the 2-span and 3-span EDFA              |  |

| systems, indicating each channel's contribution to the post-EDFA power discrepancy in                     |  |

| respective systems                                                                                        |  |

|                                                                                                           |  |

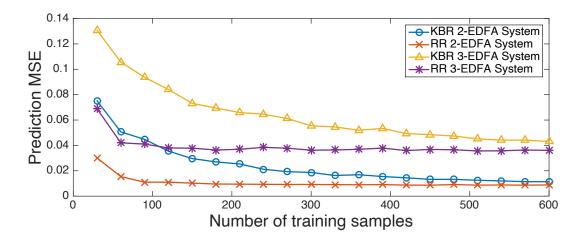

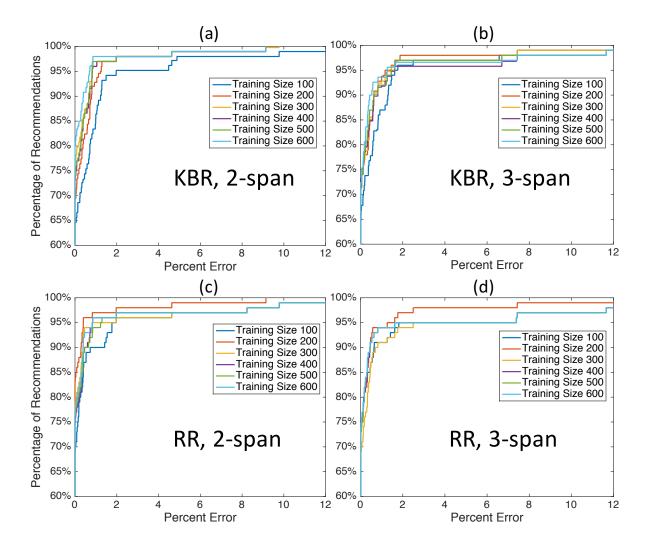

| Figure 6-4: Reduction of the ML models' prediction MSEs of power STDEV with increasing                    |  |

| Figure 6-4: Reduction of the ML models' prediction MSEs of power STDEV with increasing training data size |  |

|                                                                                                           |  |

| training data size                                                                                        |  |

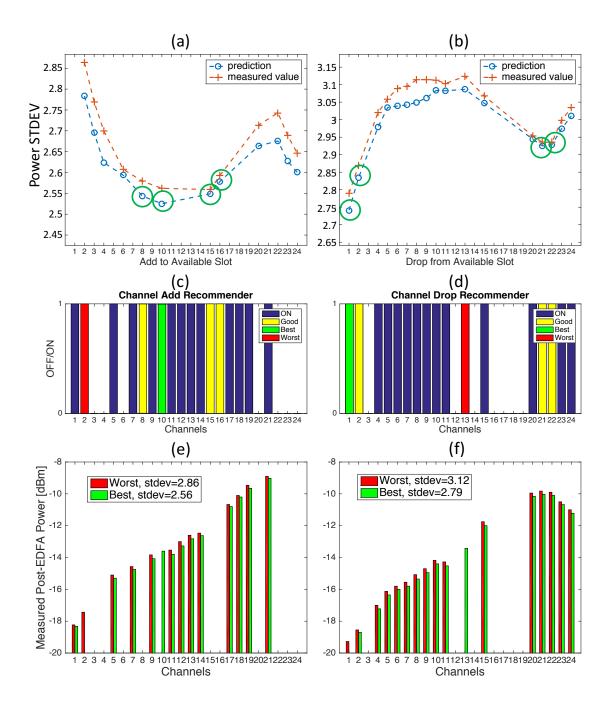

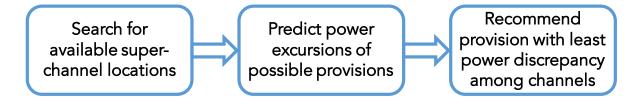

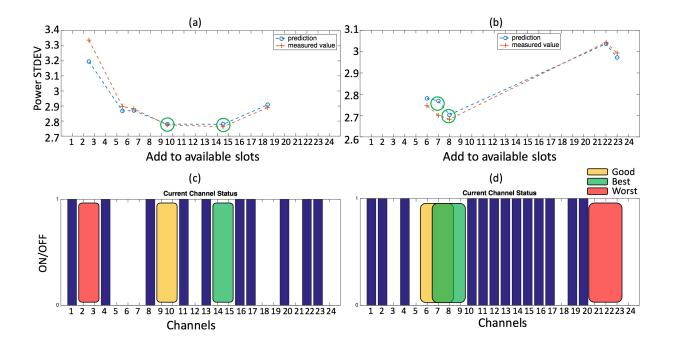

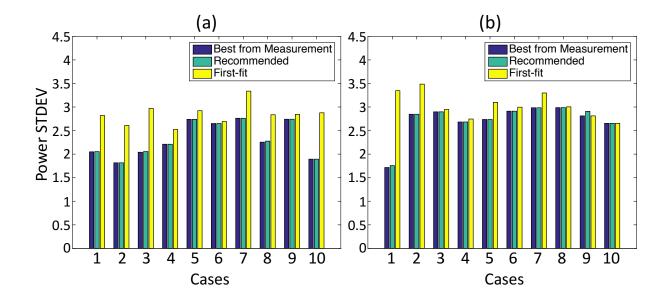

- Figure 6-10: Comparisons between predictions and measurements of post-EDFA power discrepancy for super-channel addition consisting of (a) two contiguous sub-channels and (b) three contiguous sub-channels. The top two super-channel candidates with the lowest predicted power STDEV are circled. (c) and (d) illustrate the best, good, and worst super-channel candidates.

| Figure 6-12: Illustration of channel add/drop operations at the intermediate EDFA node 140      |

|-------------------------------------------------------------------------------------------------|

| Figure 6-13: Values of the learned RR weights corresponding to the 24 channels of the           |

| experiment system                                                                               |

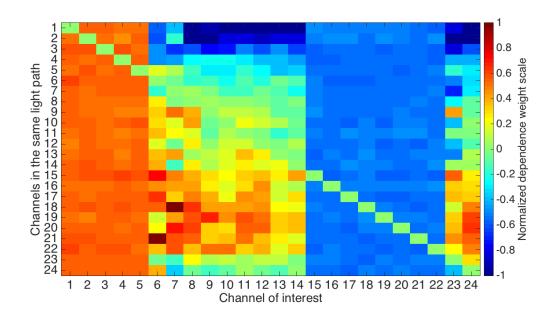

| Figure 6-14: Values of the learned channel-specific LR weights corresponding to the 24 channels |

| of the experiment system 147                                                                    |

| Figure 6-15: Workflow schematic of the ML engine showing training of RR and LR models,          |

| whose results are used to determine power adjustments                                           |

| Figure 6-16: Discrepant post-EDFA power levels from 24 channels launched at uniform power.      |

|                                                                                                 |

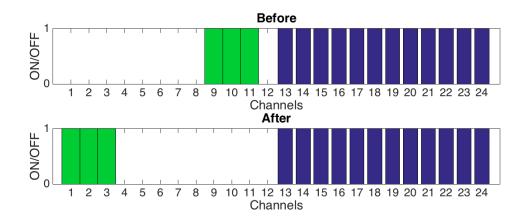

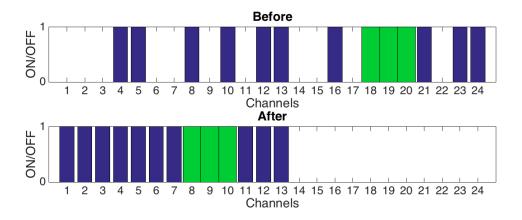

| Figure 6-17: Illustration of the first defragmentation experiment – relocated super-channel is  |

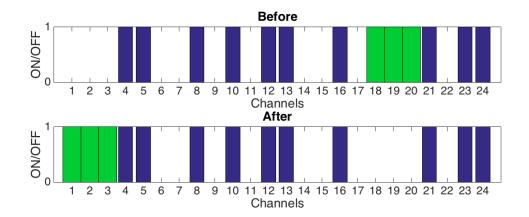

| shown in green; other ON channels are shown in blue 154                                         |

| Figure 6-18: Illustration of the second defragmentation experiment for Hop and MbB – relocated  |

| super-channel is shown in green; other ON channels are shown in blue 155                        |

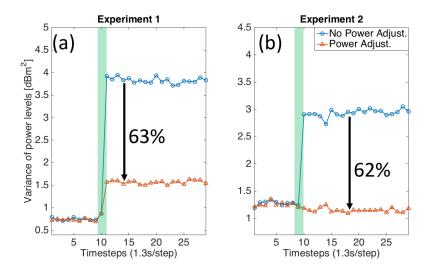

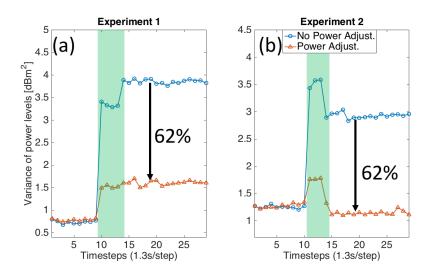

| Figure 6-19: Comparison of post-EDFA power variance with and without ML-enabled power           |

| adjustments in two experiments of Hop defragmentation, the duration of which is shaded          |

| in green                                                                                        |

| Figure 6-20: Comparison of post-EDFA power variance with and without ML-enabled power           |

| adjustments in two experiments of MbB defragmentation, the duration of which is shaded          |

| in green                                                                                        |

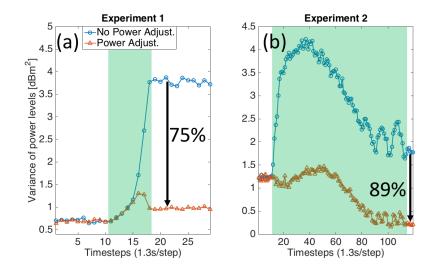

| Figure 6-21: Illustration of the second defragmentation experiment for Sweep – relocated super- |

| channel is shown in green; other ON channels are shown in blue                                  |

| Figure 6-22: Comparison of post-EDFA power variance with and without ML-enabled power |  |

|---------------------------------------------------------------------------------------|--|

| adjustments in two experiments of Sweep defragmentation, the duration of which is     |  |

| shaded in green                                                                       |  |

# List of Tables

| Table 1-1: Notable demonstrations of MRR-based silicon photonic switch fabrics    | 14  |

|-----------------------------------------------------------------------------------|-----|

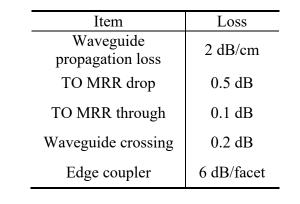

| Table 3-1: Key component loss                                                     | 47  |

| Table 3-2: Estimated component loss                                               | 65  |

| Table 3-3: Estimated shuffle loss                                                 | 67  |

| Table 3-4: Estimated total on-chip insertion loss of the 16×16 Clos switch fabric | 68  |

| Table 5-1: Common optical switch architectures       1                            | 100 |

| Table 6-1: Time consumption of training and prediction for RR and KBR             | 130 |

# Glossary

| ADC.  | analas ta disital conventor      |

|-------|----------------------------------|

| ADC:  | analog-to-digital converter      |

| AGC:  | automatic gain control           |

| ASIC: | application-specific integrated  |

|       | circuit                          |

| ASE:  | amplified spontaneous emission   |

| B2B:  | back-to-back                     |

| BER:  | bit error rate                   |

| CBR:  | case-based reasoning             |

| CDF:  | cumulative distribution function |

| CMOS: | complementary metal–oxide–       |

| CIU   | semiconductor                    |

| CW:   | continuous wave                  |

| DAC:  | digital-to-analog converter      |

| DC:   | directional coupler              |

| DFB:  | distributed feedback             |

| DUT:  | device under test                |

| DWDM: | e                                |

|       | multiplexing                     |

| EDFA: | Erbium-doped fiber amplifier     |

| EO:   | electro-optic                    |

| ER:   | extinction ratio                 |

| FC:   | fiber coupler                    |

| FoM:  | figure of merit                  |

| FPGA: | field programmable gate array    |

| FSR:  | free-spectral range              |

| FWHM: | full width at half maximum       |

| I/O:  | input/output                     |

| IPDR: | input power dynamic range        |

| IL:   | insertion loss                   |

| KBR:  | kernelized Bayesian regression   |

| LCoS: | liquid crystal on silicon        |

| LR:   | logistic regression              |

| LUT:  | look-up table                    |

| MbB:  | Make-before-Break                |

|       | (defragmentation method)         |

| MEMS: | micro-electromechanical system   |

| ML:   | machine learning                 |

| MMI:  | multi-mode interferometer        |

| MPW:  | multi-project-wafer              |

| MRR:  | microring resonator              |

| MSE:  | mean square error                |

| MZI:  | Mach-Zehnder interferometer      |

| MZM:    | Mach-Zehnder modulator                |

|---------|---------------------------------------|

| NRZ:    | non-return-to-zero                    |

| OOK:    | on-off keying                         |

| OPM:    | optical performance monitor           |

| OSA:    | optical spectrum analyzer             |

| OSNR:   | optical signal-to-noise ratio         |

| PA:     | power adjuster                        |

| PC:     | polarization controller               |

| PCB:    | printed circuit board                 |

| PD:     | photodiode                            |

| PDK:    | process design kit                    |

| PIC:    | photonic integrated circuit           |

| PILOSS: | path-independent loss                 |

| PLC:    | planar lightwave circuit              |

| PMF:    | polarization-maintaining fiber        |

| PRBS:   | pseudo-random bit sequence            |

| QoS:    | quality of service                    |

| RBF:    | radial basis function                 |

| RMSE:   | root mean square error                |

| RNB:    | rearrangeably non-blocking            |

| ROADM:  | reconfigurable optical add/drop       |

| KOADMI. | multiplexer                           |

| RSA:    |                                       |

| RR:     | routing and spectrum allocation       |

|         | ridge regression                      |

| SE:     | switching element                     |

| SerDes: | serializer-deserializer               |

| SNB:    | strictly non-blocking                 |

| SOA:    | semiconductor optical amplifier       |

| SOI:    | silicon-on-insulator                  |

| SSMF:   | standard single-mode fiber            |

| STDEV:  | standard deviation                    |

| TDM:    | time-division multiplexing            |

| TE:     | transverse electric                   |

| TIA:    | transimpedance amplifier              |

| TLD:    | tunable laser diode                   |

| TO:     | thermo-optic                          |

| TOF:    | tunable optical filter                |

| VOA:    | variable optical attenuator           |

| WDM:    | wavelength-division                   |

|         | multiplexing                          |

| WSNB:   | wide-sense non-blocking               |

| WSS:    | wavelength-selective switch           |

|         | e e e e e e e e e e e e e e e e e e e |

# Acknowledgments

First, I would like to thank my academic advisor, Prof. Keren Bergman, for her guidance and teaching throughout my studies and research at Columbia University.

To the members of my doctorate dissertation committee, Prof. Keren Bergman, Prof. Michal Lipson, Prof. Alexander Gaeta, Prof. Gil Zussman, and Prof. Christine Hendon, thank you for your time and feedback.

I would like to thank Dr. Qixiang Cheng, Dr. Alex Meng, Dr. Yuhan Hung, and Dr. Payman Samadi for their mentorship throughout my doctoral studies, and Nathan Abrams and Richard Dai, with whom I had the fortune and joy to share an office. Much appreciation to all my academic collaborators at the Lightwave Research Laboratory for your tremendous teamwork. I wish you all the best in your studies and endeavors.

The internships I did greatly enriched my studies with valuable industry perspectives. I would like to thank my mentors – Po Dong and Guilhem de Valicourt at Nokia Bell Labs, Brian Taylor, Gilad Goldfarb, Chris Berry, James Stewart, and Hans-Juergen Schmidtke at Facebook, for their guidance and help.

To my family, I thank you for your love, care, and support every step of the way.

To my parents, Qingmei and Yufei

# **Chapter 1: Introduction and Background**

# 1.1 An Optically Connected Globe

The ubiquitous connectivity to the internet has changed our lives in every way. Studies have projected that, by 2023, over 66% of the global population will have internet access [1], with 6% annual growth as shown in Figure 1-1. The accelerating increase in both the coverage and speed of mobile phones, broadband internet, and Wi-Fi hotspots has significantly enriched people's lives by instilling digital conveniences in areas such as communication, transportation, finance, and entertainment as necessities that we cannot live without. As the growing majority of the global population turns to mobile devices as the primary surface for digital interactions, the infrastructure of the internet that stores, processes, and transfers both the application and user data has centralized in hyperscale datacenters operated by cloud companies such as Google, Facebook, Microsoft, Amazon, Alibaba, Baidu, and Tencent.

## Figure 1-1: Past and projected number of internet users from [1].

While optical communication is commonly recognized as the main medium for continental and inter-continental connections, economic and power-efficient commodity optical transceivers are replacing electrical connections for short-distance links and becoming the dominant medium for intra-datacenter interconnects. This inevitable transition is due to the limitation of resistive loss in the electrical lines at both high signal bandwidth and link length [2]. As intra-datacenter link rate grows beyond 100 Gbps and the physical link lengths extend beyond 2 km, fiber-based optical communications become the only viable candidate to support the continued scaling of the datacenter infrastructure. Nevertheless, the shift to optical transceivers is only half of the datacenter network transformation. Hyperscale datacenters are built on a high-availability, scalable, and flat network of Ethernet switches, which perform parsing, caching, processing, and forwarding of traffic packets. Each switch device consists of an electronic switch fabric and hundreds of electrical SerDes I/Os. The upgrade of the datacenter network speeds and architecture are typically bounded by the capabilities and functionalities of the switch devices, rather than the speed of the optics. For instance, in the new datacenter architecture, F16, deployed by Facebook [3], the company is able to drastically flatten the network with higher-radix switch ASICs, as shown in Figure 1-2.

# Figure 1-2: The upgraded architecture of Facebook datacenter network, F16, and its comparison with the previous generation design, F4, from [3].

Analogous to the transition from copper cables to optical fibers, the next evolution in high-speed communication for datacenter networks will be realized by closing the gap between the optics and the

switch ASICs. The communication and networking industry are increasingly focused on methods to integrate optics with the switch ASICs to significantly reduce electrical trace loss on the PCB and SerDes requirements, albeit at the cost of increasing complexities in design, fabrications, and packaging. Several proposed approaches for tightly integrated optics are shown in Figure 1-3. A recent demonstration [4] from Intel has also shown a reference design of a co-packaged switch ASIC with optical transceiver I/Os on the same package substrate.

Figure 1-3: Schematics for increasingly integrated optics and switch ASICs from [5].

Photonic switching has the potential to further improve the efficiency and capability bottlenecks of the datacenter network by eliminating the pin and power constraints of the electronic switch ASICs, as well as the inefficiencies associated with opto-electronic conversions at every switch point of the network [6]. In addition, since the optical links are much more distance-agnostic than electrical links, performing switching in the optical domain can drive novel networking architectures and applications such as disaggregated hardware resources [7]. Disaggregation of the traditional server has been proposed as a solution to improve utilization efficiency [8] by pooling similar resources, with the possibility of adaptively configuring and upgrading the resources for optimized performance. A disaggregated data center requires a robust interconnection fabric to handle the additional traffic between pooled hardware resources while offering high bandwidth and low latency for the system performance. Figure 1-4 shows a promising hardware disaggregation concept by using a photonically switched interconnection network to adaptively provision different computing resources [9] [10]. To realize these novel networking applications effectively and reliably, high-performance, economic, and scalable photonic switching solutions must first be developed. In this work, we comprehensively explore silicon photonic switching through building block designs, multi-stage switch architectures, device calibration, topology scalability, smart routing strategies, and performance-aware control plane.

Figure 1-4: A conceptual photonic integrated network for hardware resource disaggregation with photonic switches. Adopted from [8].

# **1.2** Silicon Photonics

Silicon photonics is an emerging platform to design and fabricate nanoscale structures that guide and manipulate an optical field, and has experienced dramatic growth in adoption across a myriad of applications from data transmission, sensing, and photonic switching [11]. For datacenter interconnect applications, silicon photonics has the potential to enable highly energy efficient transceiver and networking systems [12]. The rise of silicon photonics can be attributed to three main factors: foundry manufacturability, efficient tuning mechanisms, and compact device footprints. On-going efforts on developing scalable testing and packaging techniques also contribute to fast iterations and optimizations in the silicon photonic design workflow.

## **CMOS-compatible fabrication**

The silicon photonic platform shares many of the same processes and layer stack with the CMOS industry that has matured over the past few decades, and therefore promotes the reuse of past CMOS fabrication facilities. This not only significantly reduces the cost associated with design flow and device fabrication, but also ensures high scalability in manufacturing, as the CMOS industry is already positioned to supply the volume of the global computer hardware. This also means that innovative designs in silicon photonics can be realized in industrial scale, which significantly expedites the timeline for technology to market. Many of the major commercial CMOS foundries, such as Advanced Micro Foundry (AMF), GlobalFoundries, Interuniversity Microelectronics Centre (IMEC), Taiwan Semiconductor Manufacturing Company (TSMC), TowerJazz, and AIM Photonics, now offer MPW wafer runs as economic options for fabless companies and research groups to participate in silicon photonics innovations. An example of layer structures of the silicon photonic platform offered by AMF is shown in Figure 1-5.

# Figure 1-5: Example layer stack of the silicon photonic platform from AMF [13].

# Efficient tuneability of optical properties

While silicon's indirect bandgap makes optical gain and emission infeasible, it provides very efficient mechanisms to manipulate the optical field by changing the refractive index of the material. Silicon's index has very strong temperature dependence at about 1.8e-4 K<sup>-1</sup> at room temperature [14], which is about 20 times greater than that of silica commonly used in PLC-based photonic circuits. Hence, the phase delay of the guided wave in a silicon PIC can be adjusted more efficiently by varying the temperature of the waveguide. Localized micro heaters in silicon can be achieved with resistive heater using a metal layer above the waveguide or through direct doping of the silicon itself. The former implementation induces no additional loss to the waveguide, but the latter can achieve higher tuning efficiency and faster tuning speed because the heat is generated directly at the waveguide core.

In addition, silicon's index has a strong carrier concentration dependence due to the plasma dispersion effect, making it feasible to modify the waveguide index through electro-doping. The free carrier induced index change, in both real and imaginary parts, is first empirically quantified in [15]. For common

telecom wavelengths around  $1.55 \,\mu\text{m}$ , the electro-optic changes in the real and imaginary parts of the index are:

$$\Delta n = -[8.8 \times 10^{-22} \Delta N_e + 8.5 \times 10^{-18} (\Delta N_h)^{0.8}], \quad (1-1)$$

$$\Delta \alpha = 8.5 \times 10^{-18} \Delta N_e + 6.0 \times 10^{-18} \Delta N_h, \quad (1-2)$$

where  $\Delta n$  and  $\Delta \alpha$  are the changes in the real and imaginary parts of the material index, respectively;  $\Delta N_e$ and  $\Delta N_h$  are the changes in electron and hole concentrations in silicon, respectively. The EO effect on silicon index can realize sub-nanosecond speed phase shifter designs with p-n or p-i-n junctions that are integral to high-bandwidth optical modulators [16] [17] [18] and fast switching devices [19] [20].

#### Highly compact photonic structures

The silicon photonics platform achieves waveguiding with silicon (n = 3.5) as the core and silicon oxide (n = 1.5) as the cladding. The large index contrast between the core and the cladding results in tight confinement of the guided mode ( $n_{eff}$ =2.35 @ 1.55 µm, 450 nm waveguide width), allowing tight bending structures with <10 µm bend radius and overall reduced footprint. This ensures high integration density in PIC designs and compact chip dimensions. The miniaturized index-tuneable structures also result in low tuning power consumption. In addition, the transparency window of silicon photonic platform extends from 1.1 µm to 3.7 µm, bounded by the band edge of silicon at the lower end and the mid-infrared absorption of silicon oxide at the higher end. This makes 1 – 2 dB/cm waveguide propagation loss possible under industrial fabrication processes.

## **1.3** Photonic Switching

#### **1.3.1** Historical Photonic Switch Designs

Photonic switching is a concept that entails on-demand connectivity change between a set of optical inputs and a set of optical outputs directly in the optical domain without conversion to electrical signals. To that end, there has been many commercial and research implementations to achieve viable photonic switch fabric designs. These historical efforts can be categorized based on their switching mechanisms:

#### Free space switching

Optical switching in free space typically relies on MEMS-actuated mirrors [21] [22] [23] or piezoelectric collimators [24] to deflect or steer collimated optical beams from an input fiber port to an output fiber port. Free space optical switches can offer <1 dB switching loss at high port count, and are insensitive to polarization and wavelength. However, due to the mechanical movements in the switching process, the switching speed of these systems are typically on the millisecond scale. In addition, the deflection and steering components need stringent alignment and calibration to ensure proper function, which results in bulky and expensive switching systems.

## Gain based switching

Optical switching can be achieved by broadcasting the input signal and selective amplify or attenuate at the desired output port. SOA-based switch gates can be implemented for such switching mechanism [25] [26] [27]. Because gain is applied to the switched signal, a commonly adopted FoM is IPDR, which is defined as the range of input power levels within which error-free data transmission can be achieved. The SOAs can effectively compensate for the insertion loss of the switch device in gain mode, and eliminate crosstalk due to leakage power in attenuation mode. However, the high power consumption of the SOA gates prohibits large integrated device with high port counts. Later devices tend to utilize hybrid

designs that combine interferometric non-gain switching sections and selective placements of SOA gates to improve the switching extinction and crosstalk [28] [29] [30] [31].

## Phase based switching

Steering of the optical signals can also be achieved by manipulating the phase of the optical field in an interferometer structure. Early demonstrations implemented in lithium niobate [32] [33] and silica PLC [34] [33] [35] have shown impressive results in achieving low loss, high extinction switching in integrated devices. In a different implementation, spatially and spectrally dispersed optical signals can be steered adeptly by phase changes actuated due to the birefringence in an LCoS array, enabling space-andwavelength selective switching [36] [37]. LCoS-based switching has become a key technology in commercial WSS systems because of its high performance. Lithium niobate, silica, and LCoS switch devices tend to require bulky systems due to large component footprint, which can be adeptly addressed with a high index contrast material system such as the SOI platform.

### **1.3.2** Silicon Photonic Switch Designs

Because of silicon photonics' unique benefits in foundry manufacturability, efficient tuning mechanisms, and compact device footprints, switch fabrics designed with silicon PICs are viable options to address many of the issues present in previous photonic switching demonstrations. CMOS-compatible processes lower the manufacturing cost of silicon switch fabrics. Highly efficient index tuning mechanisms enable flexible and low power controls to achieve high switching performance. Compact device footprint allows more structures and components to be integrated in the same chip while reducing packaging cost and system scale. Silicon integrated photonic switches are typically built by a fabric of 2×2 SEs. Impressive demonstrations of silicon switch fabrics have been shown employing SEs realized with MZIs [19] [38] [39], MEMS couplers [40] [41] [42], MRRs [43] [44] [45] [46] [47] [48], and MRR-assisted MZIs [49] [50] [20] [51]. Figure 1-6 shows notable examples of each of these SE implementations.

Figure 1-6: Micrographs of silicon photonic SEs implemented with (a) MZI [39], (b) MEMS-actuated DCs [52], (c) MRRs [43], and (d) MRR-assisted MZIs [51].

In comparison, MZI- and MEMS-based SEs can offer very high extinction and broadband switching, but they rely on couplers or phase shifters hundreds of microns in length, and the switch die area can reach about  $50 - 150 \text{ mm}^2$  [19] [38] [40]. In one demonstration of a high port count MEMS-based switch, the device exceeds the maximum reticle size for lithography and requires die-stitching [52]. In contrast, MRR-based SEs are usually tens of microns across and enable much higher integration density with greatly shrunk chip area. Leveraging traveling wave cavity dynamics, MRR SEs can perform narrowband through or drop operations around their resonance points [53]. Figure 1-7 shows a schematic of the through-drop configuration of the MRR SE, where the input optical field, when resonant with the MRR, can couple into the cavity, couple out into the top waveguide, and exit from the drop port. If the optical field is off resonant with the MRR, it bypasses the cavity and exits out of the through port. Figure 1-7 also identifies the self-coupling coefficients,  $r_1$  and  $r_2$ , for the input and output waveguides respectively, as well as the roundtrip amplitude transmission, *a*, which describes the ratio of the preserved field amplitude after one roundtrip in the cavity. The spectral transfer functions for the field at the through and drop ports are described by Equations (1-3) and (1-4), respectively.

$$T_{through} = \frac{r_2^2 a^2 - 2r_1 r_2 a \cos\phi + r_1^2}{1 - 2r_1 r_2 a \cos\phi + (r_1 r_2 a)^2}, \quad (1-3)$$

$$T_{drop} = \frac{(1 - r_1^2)(1 - r_2^2)a}{1 - 2r_1 r_2 a \cos\phi + (r_1 r_2 a)^2}, \quad (1-4)$$

where  $\phi$  is the phase detuning in radians from the center of the MRR's resonance and a full FSR is represented by  $2\pi$ .

Figure 1-7: Schematic of an MRR SE in the through-drop configuration.

Figure 1-8: Notable silicon photonic switch fabric demonstrations with (a) 32x32 MZIbased Beneš network [54], (b) 32x32 MZI-based PILOSS network [55], (c) 4x4 MRR-based switch-and-select network [44], and (d) 8x8 MRR-based Omega network [56]. Larger switch networks are formed by arranging and interconnecting numerous 2×2 SEs in specific topologies to connect more inputs and outputs, and the network architecture dictates the type of connectivity and the routing control of the switch device. Figure 1-8 shows some notable demonstrations of silicon switch fabrics constructed with MZI- and MRR-based SEs with different network topologies. The wavelength-selective nature of the MRR SEs requires wavelength alignment across the switching circuit, which is typically achieved through schemes of fast and efficient wavelength locking of the MRRs as demonstrated in [57] [58] [59]. Higher-order MRR elements enable broadened passband, which relaxes the wavelength alignment requirement for the input optical signal [45], but is at the cost of higher insertion loss and fabrication complexity. Table 1-1 summarises a number of notable demonstrations of MRR-based photonic switch fabrics, with port counts ranging from 2 to 8 [45] [43] [60] [61] [62] [46] [63] [44] [48]. Key metrics, such as port count, on-chip loss, crosstalk, and optical power penalty are highlighted and compared.

| Port<br>Count | Architecture                       | SE Type                            | On-<br>chip<br>loss<br>[dB] | Crosstalk<br>[dB]  | Optical power<br>penalty [dB] | Year<br>and<br>work |

|---------------|------------------------------------|------------------------------------|-----------------------------|--------------------|-------------------------------|---------------------|

| 4×4           | Hitless<br>router                  | 1 <sup>st</sup> -order<br>MRR      | -                           | >20                | -                             | 2008<br>[43]        |

| 5×5           | Bidirectional<br>optical<br>router | 1 <sup>st</sup> -order<br>MRR      | ~8                          | >16                | < 1.75 @<br>12.5 Gb/s         | 2011<br>[61]        |

| 8×7           | Crossbar                           | 5 <sup>th</sup> -order<br>MRR      | 2 to 10                     | 19.5 to<br>23.4    | < 1 @<br>10 & 40 Gb/s         | 2014<br>[45]        |

| 8×8           | N-stage<br>planar                  | 1 <sup>st</sup> -order<br>dual MRR | ~4                          | <-10               | -                             | 2017<br>[62]        |

| 8×8           | Crossbar                           | 2 <sup>nd</sup> -order<br>MRR      | >5                          | >-20               | -                             | 2017<br>[46]        |

| 4×4           | Benes                              | 2 <sup>nd</sup> -order<br>MRR      | ≤6.9                        | <-13.6             | -                             | 2018<br>[63]        |

| 4×4           | Switch-and-<br>select              | 1 <sup>st</sup> -order<br>MRR      | >1.8                        | -51.4 to -<br>31.6 | -1 @ 12.5 Gb/s                | 2019<br>[44]        |

| 8×4           | Crossbar                           | 2 <sup>nd</sup> -order<br>MRR      | 6 to 14                     | <-32               | 0.2 @ 40Gb/s                  | 2019<br>[48]        |

| 8×8           | Omega                              | 1 <sup>st</sup> -order<br>dual MRR | 4.4 to<br>8.4               | -18.8 to -<br>14.7 | < 2 @ 32 Gb/s                 | 2019<br>[56]        |

Table 1-1: Notable demonstrations of MRR-based silicon photonic switch fabrics

Another type of silicon photonic SEs is the MRR-assisted MZI, whose schematic is shown in Figure 1-9. This type of SEs resembles an MZI with its 4-port configuration and interferometer arms, but can be much smaller in footprint by replacing the linear waveguide phase shifters with compact, over-coupled MRRs. The sharp, narrowband phase delay induced by the MRR phase shifters across their resonances can be described by:

$$\varphi = \pi + \phi + \arctan \frac{r \sin \phi}{a - r \cos \phi} + \arctan \frac{r a \sin \phi}{1 - r a \cos \phi}$$

, (1-5)

where  $\phi$  is the phase detuning in radians from the center of the MRR's resonance; r is the self-coupling coefficient between the MRR and the single waveguide; a is the roundtrip amplitude transmission of the MRR. The MRR-assisted MZI inherits many of the benefits from both MRR- and MZI-based SEs and will be explored in more details and implementations in Chapter 2.

Figure 1-9: Schematic of an MRR-assisted MZI SE.

#### **1.4** Scope of Thesis

The scope of this thesis focuses on a comprehensive exploration on silicon photonic switching components and devices, calibration and control techniques, topology and routing strategies, as well as intelligent control plane design. The chapters of this thesis are derived from the author's works published in peer reviewed journals and research conference proceedings.

This work adopts a bottom-up approach to structure the topics on silicon photonic switching devices and systems. Chapter 2 focuses on the building block components of a switch fabric and presents a novel space-and-wavelength selective SE using MRR-assisted MZI structures with high performance and design robustness. Chapter 3 explores integrated silicon photonic switch devices based on MRR SEs. The design and characterization of an Omega 8×8 switch device with dual-MRR SEs is presented with a wellbalanced set of performance metrics in extinction ratio, crosstalk suppression, and optical bandwidth. For further increase in the switch port count, a Clos network of MRR switch-and-select sub-switches is proposed and analyzed to show optimal scalability and management of optical impairments. Chapter 4 discusses an approach for fast and efficient calibration techniques to address fabrication variations in switch devices and achieve precise and performance-optimal control points. Chapter 5 presents the analysis on the redundancies in switch configurations and derive routing strategies based on the redundancies to improve worst-case performance of the switch device. Chapter 6 examines how to best design ML-enabled control plane for optical systems to predict system dynamics and offer provisioning recommendations. As a case study, the ML approach introduced is applied to EDFA power excursion impairments and shows high efficacy in improving the spectral power stability during wavelength assignment and defragmentation.

# **Chapter 2: Switching Elements for Spatial and Spectral Domains**

### 2.1 Introduction

The capability and performance of a photonic switch system heavily depends on the design of the SEs, which are the fundamental building blocks of the switch fabric. Routing signal channels in both the spatial and spectral domains is one of the key functionalities to realize agile photonic switching in WDM applications. To perform space-and-wavelength selective switching in devices built with broadband DCs and MZIs, WDM channels need to be first distinguished spatially before being routed. Prior works [64] [65] [66] [67] of space-and-wavelength switch designs have introduced parallel switching planes bookended with wavelength (de)multiplexers, a generic schematic of which is shown in Figure 2-1a. In this design, the duplication of switching planes poses immense challenges to managing the complexity and footprint of the integrated systems. In contrast, space-and-wavelength selective switching can be significantly simplified by integrating independent controls for both spatial and spectral domains at the SE level, as shown in Figure 2-1b, with wavelength selective structures such as MRR [47], photonic crystal nanobeams [68], and waveguide Bragg gratings [69]. In particular, MRR-based SEs offer promising characteristics of large switching ER, high tuning efficiency, ultra-compact footprint (~100  $\mu$ m<sup>2</sup>), and commercial manufacturability, which are key factors for scaling to high-radix switch fabrics [47]. Previous works [48] [70] for MRR-based space-and-wavelength selective SEs have employed multiple MRRs with offset resonances as spectral add-drop filters. Achieving decent switching ER with add-drop MRRs requires careful examination of the critical-coupling conditions, which, however, are susceptible to fabrication variations. In contrast, over-coupled MRRs as phase shifters tend to have relaxed design constraints, and thus improved tolerance to variations.

Figure 2-1: (a) Schematic design for space-and-wavelength selective switch with parallel switching planes and wavelength (de)multiplexers. (b) Schematic design for spaceand-wavelength selective switch built on SEs with spatial and spectral switching granularity.

This chapter discusses a novel SE design that was first proposed in [51] with full space-andwavelength switching using a symmetrical MZI assisted by pairs of over-coupled MRRs. The MRRs are operated as highly efficient narrowband phase shifters to enable independent switching of multiple wavelengths in the MZI structure. As a demonstration, we design and characterize a  $2\times 2\times 2\lambda$  SE device, which shows high ER, highly suppressed crosstalk, and low signal penalty with push-pull control scheme when WDM signals are switched simultaneously.

## 2.2 Working Principles

Figure 2-2 shows a generic design of the proposed space-and-wavelength selective SE, independently switching M wavelength channels in an MZI structure with M-pairs of MRRs and a broadband  $\pi/2$  phase difference between the arms. The SE maintains a compact footprint by using overcoupled MRRs as efficient phase shifters, which induce a sharp and continuous  $2\pi$  phase change across their resonances. Each pair of identical MRRs aligns to a specific wavelength channel and operates differentially to create a symmetric MZI passband. By maintaining a 2-input and 2-output spatial configuration, the SE is a compatible building block for any multi-stage switch topologies based on 2×2 elementary cells [71] and can be interconnected to scale to larger N×N×M $\lambda$  fabrics. Since the MRRs have periodic resonances, the total number of channels supported in a single MZI structure, M, is limited by:

$$M \leq \left| \frac{\text{FSR}}{\Delta f + \text{FWHM}} \right|$$

, (2-1)

where FSR and FWHM are respectively the free-spectral range and full width at half maximum transmission of the MRRs, and  $\Delta f$  is the detuning between the pair of MRRs for a single channel.

Figure 2-2: Schematic of a  $2 \times 2 \times M\lambda$  SE with MRR phase shifters. Each pair of MRRs aligns to the input wavelength channel of the same color.

To illustrate the working principles of the MRR-assisted switching, we examine a single-channel wavelength-selective MZI with one pair of MRR phase shifters. This structure, as shown in Figure 2-3a, has been implemented in designs for efficient spatial SEs [49], modulators [72] [73], and wavelength interleavers [74]. With one MRR coupled to each arm, the MZI switching phase is achieved by slight

detuning of the MRRs' resonances. Figure 2-3b and Figure 2-3d visualize the phase delay induced by the MRRs, as well as the resultant phase differences between the MZI arms in the Bar and Cross switching states, respectively. The spectral transmission of the MZI outputs can be determined using the transfer matrix method:

$$\begin{bmatrix} E_{01} \\ E_{02} \end{bmatrix} = \begin{bmatrix} t & jr \\ jr & t \end{bmatrix} \begin{bmatrix} \alpha_{r1} e^{j(\varphi_{r1} + \phi_{bias} + \phi_{path})} & 0 \\ 0 & \alpha_{r2} e^{j(\varphi_{r2} + \phi_{path})} \end{bmatrix} \begin{bmatrix} t & jr \\ jr & t \end{bmatrix} \begin{bmatrix} E_{I1} \\ E_{I1} \end{bmatrix},$$

(2-2)

where  $E_{I1}$ ,  $E_{I2}$ ,  $E_{O1}$ , and  $E_{O2}$  are the electric field amplitudes at Input Ports 1 and 2 and Output Ports 3 and 4, respectively; t and r are the field transmission and cross-coupling coefficients of the MMI structures;  $\alpha_{r1}$  and  $\alpha_{r2}$  are the field amplitude modulation factor by MRR1 and MRR2, respectively;  $\varphi_{r1}$  and  $\varphi_{r2}$  are the phase delay imposed by MRR1 and MRR2, respectively;  $\phi_{bias}$ is the static phase bias difference between the two MZI arms; and  $\phi_{path}$  is the phase accumulated in the straight waveguides, which are assumed to be equal between the two arms. Note that  $\alpha_{r_1}$ ,  $\alpha_{r2}, \varphi_{r1}$ , and  $\varphi_{r2}$  are dependent on the detuning of the wavelength about the MRRs' resonances. In this work, we employ the push-pull control scheme for the pair of MRRs around the MZI's quadrature point – the resonances of the MRRs are driven in opposite directions about the switched channel, and a static and wideband phase bias of  $\pi/2$  is set between the arms. Under this control scheme, both the Bar and Cross switching states have identical transmission spectra, as determined by Equation (2-2) and shown in Figure 2-3c and Figure 2-3e, and thus eliminating state-dependent performance variations. To route the wavelength channel from Port 1 to Port 3 (Figure 2-3b and Figure 2-3c), MRR 1 is red-shifted from the channel wavelength at zero detuning, while MRR 2 is blue-shifted. To route the wavelength channel from Port 1 to Port 4 (Figure 2-3d and Figure 2-3e), MRR 1 is blue-shifted from the channel, while MRR 2 is red-shifted.

Figure 2-3: (a) Schematic of the single channel MRR-assisted MZI. (b) Induced phase by MRR 1 and MRR 2 and the MZI arms' phase difference for Bar switching state, with center resonances of MRR 1 and MRR 2 labeled as  $\lambda_{R1}$  and  $\lambda_{R2}$ , respectively. (c) Bar-state MZI output spectra for paths Port 1 to Port 3 and Port 1 to Port 4. (d) Induced phase by MRR 1 and MRR 2 and the MZI arms' phase difference for Cross switching state. (e) Cross-state MZI output spectra for paths Port 1 to Port 3 and Port 1 to Port 4.

## **2.3** Device Design and Characterization

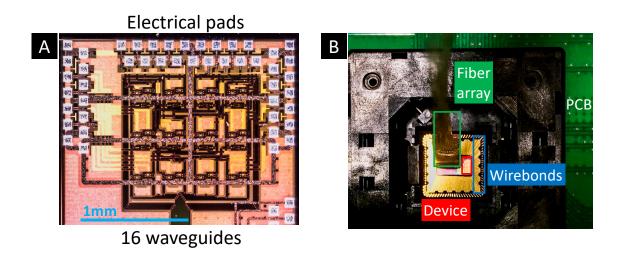

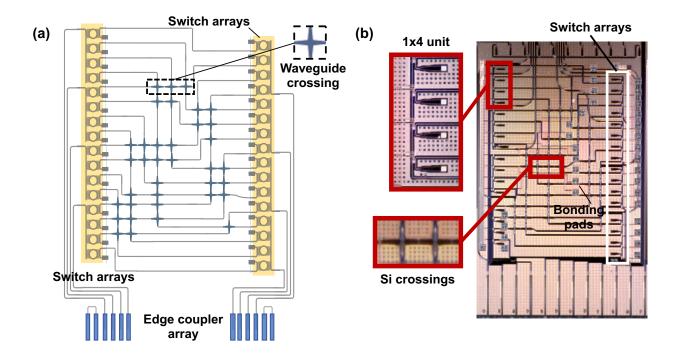

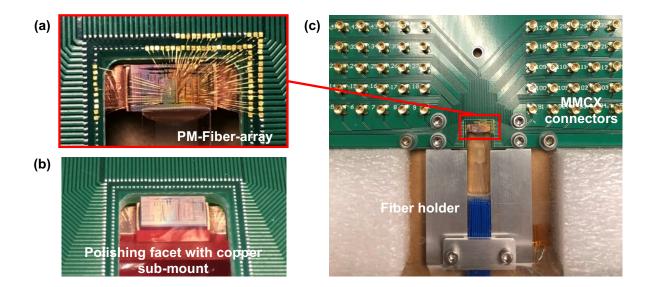

To demonstrate independent switching of multiple wavelength channels with the proposed switch design, we design and fabricate a  $2 \times 2 \times 2\lambda$  SE device that incorporates two pairs of MRRs for simultaneous switching of two wavelength channels. Figure 2-4a shows the micrograph of the device, integrating 2 MMIs, 4 MRRs, and 2 MZI TO tuners under a footprint of 0.17 mm<sup>2</sup>. The MRRs have a racetrack shape with an 8-µm bending radius and a 5-µm straight coupling section. The gap between the MRR and bus waveguide is 100 nm, imposing strong over-coupling conditions. Thermal isolation trenches are placed between the two MZI arms to reduce the thermal crosstalk between the phase shifters. The MZI tuners and the MRR phase shifters are implemented with TiN heaters to induce localized index change to the silicon waveguides without incurring additional IL. The switch chip is designed and fabricated in an MPW run through a commercial 200 mm SOI platform offered by Advanced Micro Foundry.

Figure 2-4: (a) Micrograph of the  $2 \times 2 \times 2\lambda$  SE. (b) MRR heater structure.

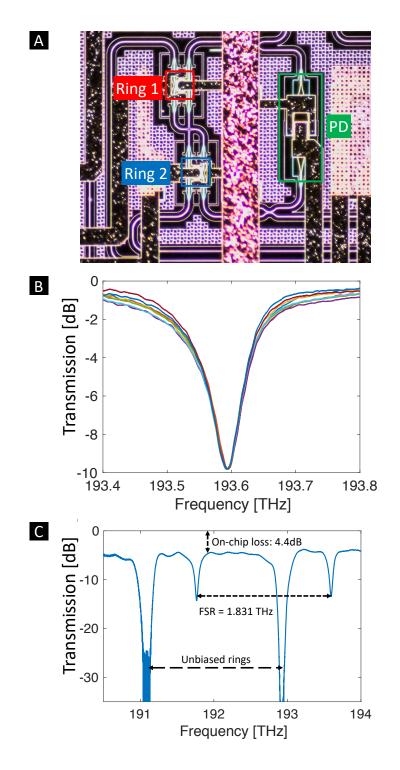

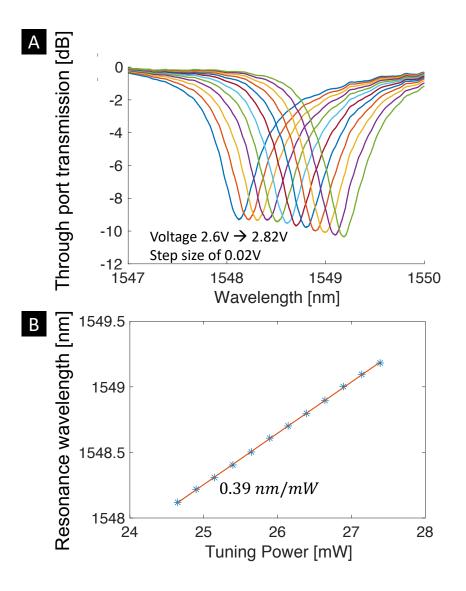

The fabricated device is accessed optically with TE-polarized light via edge coupled fiber arrays and electrically via probes. The coupling loss is measured to be ~3 dB per facet with lensed fibers. The TO phase shifter performances are shown in Figure 2-5a and Figure 2-5b. The MZI tuner shows a tuning efficiency of 13.6 mW/ $\pi$  and results in an MZI ER over 32 dB. The MRR shifter, shown in Figure 2-4b, has a tuning efficiency of 0.262 nm/mW and is used to both align the resonance point and perform switching. Figure 2-5c shows the transmission spectra of the MZI when a single pair of MRRs', R1 and R1', are far detuned. We measure the FSR of the MRRs to be 1.182 THz, and the 3dB-bandwidth to be 101 GHz, giving a finesse of 11.7. The switching speed of the switch is measured by applying a 2 V DC bias and a 15 kHz electrical square wave with 175 mV peak-to-peak amplitude to the MRR TO shifter. Observing the power levels of the resonant channel, the 0–90% optical rise and fall times of the MRR output are measured as 13 µs and 12 µs, respectively, as shown in Figure 2-5d.

Figure 2-5: (a) MZI switching output as a function of TO tuner power consumption; the inset shows the TO tuner design. (b) Resonance tuning power with the TO MRR shifter. (c) Offset MRR resonances while the MZI is biased to Bar state. (d) Optical rise and fall times when the MRR TO shifter is driven with a 15 kHz electrical square wave signal.

For switching characterization of the  $2 \times 2 \times 2\lambda$  SE, the TO tuner on the top MZI arm is set to a phase bias of  $\pi/2$ . Two CW laser signals at 1537.3 nm and 1541.3 nm, as Channel 1 and Channel 2 respectively,

are combined before inputting to Port 1 of the SE. We set the resonances of the first MRR pair, R1 and R1', at Channel 1, and the resonances of the second MRR pair, R2 and R2', at Channel 2. In contrast to spatial  $2\times2$  SE with binary states of Bar and Cross, the space-and-wavelength selective SE supports four switching states - (Bar, Bar), (Bar, Cross), (Cross, Bar), and (Cross, Cross) – for (Channel 1, Channel 2) respectively, as illustrated in Figure 2-6a-Figure 2-6d. Each pair of MRRs operates in push-pull for its corresponding channel. To switch a channel to Bar state, the MRR corresponding to that channel on the top arm (R1 or R2) red shifts its resonance with a slight increase of bias on its TO shifter, while the MRR on the bottom arm (R1' or R2') blue shifts with a slight decrease in its TO bias, resulting in a  $\pi$  phase difference between the MZI arms at the channel wavelength. To switch a channel to Cross state, the top arm's MRR blue shifts while the bottom arm's MRR red shifts, resulting in a  $2\pi$  phase difference between the MZI arms.

Figure 2-6: (a)-(d) Illustrations of (Bar, Bar), (Bar, Cross), (Cross, Bar), and (Cross, Cross) states for the two independently switched channels.

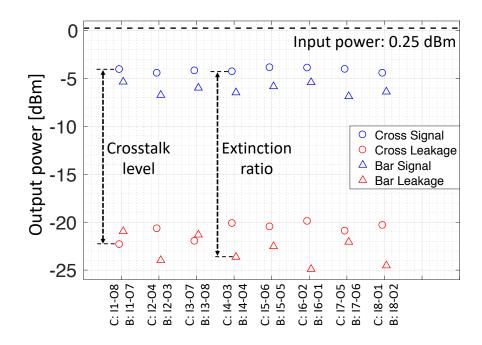

Switch outputs at Port 3 and Port 4 are monitored by an optical spectrum analyzer for the two wavelengths under operation. Figure 2-7a - Figure 2-7d show the output channel power levels for Path Port 1 - Port 3 and Path Port 1 - Port 4 in the four switching states. We observe an average crosstalk suppression

ratio of 21.7 dB, as indicated in Figure 2-7a – Figure 2-7d. The on-chip loss for the switched signal averages to 5.1 dB, which is due to a combination of MMI loss and intensity modulation by the MRRs in the overcoupling regime. For a specific wavelength channel, we define the switching ER as the difference between the signal power of the channel in one state and the leakage power of the same channel switched to other states. For instance, the ER for the Channel 1 in <u>Bar</u> is determined by the average signal power at 1537.3 nm between States (<u>Bar</u>, Bar) and (<u>Bar</u>, Cross), subtracted by the average leakage power for Channel 1 between States (<u>Cross</u>, Bar) and (<u>Cross</u>, Cross). Between the two channels, we measure an average ER of 21.8 dB for Bar state, and 21.6 dB for Cross state. Figure 2-7e – Figure 2-7h show the output spectra of all switching states measured with a broadband source. The signal passbands of both channels in all switching states are fairly consistent and average to 75.1 GHz.

Figure 2-7: (a)-(d) Signal and leakage power levels with two CW lasers in the four switching states. Crosstalk suppression levels are indicated. (e)-(h) Transmission spectra for both switch paths in the four switching states.

We numerically simulate the  $2 \times 2 \times 2\lambda$  SE using the transfer matrix method to optimize for the crossstalk suppression and IL during switching. In this analysis, the two wavelength channels are spaced at  $\Delta f$  + FWHM – the closest spacing as defined by Equation (2-1). We maintain the experimentally extracted value for the MRR's finesse,  $\mathcal{F}$ , which is a function of the product between the MRRs' self-coupling coefficient, r, and roundtrip amplitude transmission, a:

$$\mathcal{F} = \frac{\text{FSR}}{\text{FWHM}} = \frac{\pi\sqrt{ra}}{1-ra}.$$

(2-3)

We examine the MRR detuning between 10% - 40% of their FSR and *a* valued between 0.875 - 0.993, with corresponding *r* values to maintain the same finesse value of 11.7. The sweep in *a* can inform how to better design the intrinsic loss of the MRRs, while the sweep in MRR detuning can inform more precise push-pull control. From the results shown in Figure 2-8a and Figure 2-8b, the push-pull MRR-assisted switching is capable of achieving >25 dB crosstalk suppression and <1 dB IL by keeping *a* greater than 0.96 and MRR detuning between 19% and 23% of the FSR, as indicated. The improved IL and crosstalk suppression can further enhance the SE design's scalability in multi-stage switch topologies [71].

Figure 2-8: Crosstalk suppression (a) and IL (b) over ranges of MRR detuning and roundtrip amplitude transmission.

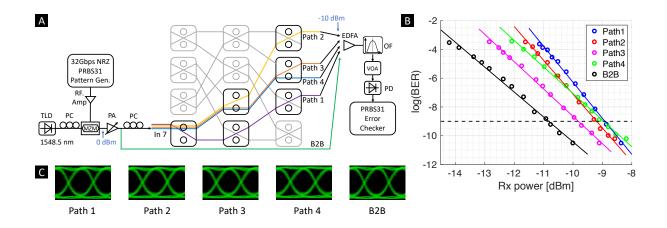

Data transmission was performed for switching states (Bar, Cross) and (Cross, Bar), where the two wavelength channels are launched into the same input port but switched to different output ports. A total of four switched signals are examined: (Bar, Cross)-Channel 1, (Bar, Cross)-Channel 2, (Cross, Bar)-Channel 1, (Cross, Bar)-Channel 2. We examine the switching states with one or both channels transmitting (singleor dual-channel cases) to study the impact of inter-channel crosstalk on the data routing performance. The data test schematic is shown in Figure 2-9a. An Anritsu MP1900A Signal Quality Analyzer generates two electrically decorrelated signals at 32 Gbps NRZ OOK using PRBS31. Two optical carriers at 1537.3 nm and 1541.3 nm are modulated by MZMs with 0 dBm output power and combined using a FC before entering the silicon photonic chip. A PA consisting of a VOA and an EDFA is used before the switch to compensate for coupling and propagation losses through the chip and ensure -10 dBm of optical power exits the chip. This PA is also used to replicate the device IL in the B2B reference case. A second set of EDFA and VOA adjusts the receiver optical power for the BER measurement. A TOF with a passband covering both wavelength channels is used to reject out-of-band ASE noise. The receiver consists of a Finisar XPDV3120 PD-TIA assembly, which performs the optical-to-electrical conversion and allows the data signal to be analyzed by the Anritsu error checker. For each switch path, the crosstalk channel is off for the single-channel case, and on for the dual-channel cases. Evident from Figure 2-9b – Figure 2-9e, all switch paths' dual-channel cases are within 1 dB power penalty at 10<sup>-9</sup> BER compared to their singlechannel cases without inter-channel crosstalk, and within 1.5 dB power penalty compared to the B2B reference case.

Figure 2-9: (a) Data experiment setup schematic. (b)-(e) BER curve for Switching States (Bar, Cross)-Channel 1, (Bar, Cross)-Channel 2, (Cross, Bar)-Channel 1, and (Cross, Bar)-Channel 2, respectively, compared among B2B, single- and dual-channel cases.

# 2.4 Chapter Summary

Space-and-wavelength selective switching can be simplified significantly by integrating spatial and spectral control granularity at the SE level. In this chapter, we introduce an MRR-assisted MZI SE that achieves independent switching of wavelength channels by using multiple pairs of MRRs as push-pull phase shifters. We discuss the working principles of the design and demonstrate a  $2\times2\times2\lambda$  switch block experimentally. The SE switches two wavelength channels independently in a total of four switching states, with both crosstalk suppression and switching ER exceeding 21 dB. Less than 1 dB signal power penalty is observed from inter-channel crosstalk when transmitting 32 Gbps NRZ data signals. We further show a path to achieve >25 dB crosstalk suppression and <1 dB IL through optimizing the MRR intrinsic loss and more precise push-pull control. The SE's high performance, compact footprint, and efficient control make this design a promising building block for scaling to multi-stage space-and-wavelength selective optical switch fabrics. In the next chapter, we explore the unique architectures, key performance parameters, and design space and scalability analysis for multi-stage silicon photonic switch fabrics.

# **Chapter 3: Multi-stage MRR-based Switch Fabrics**

#### **3.1** Introduction

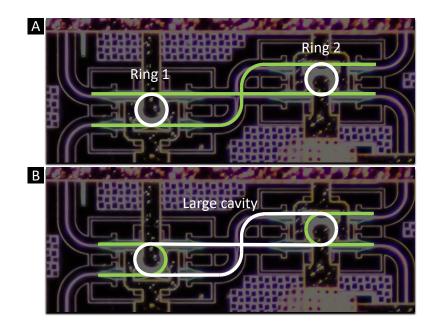

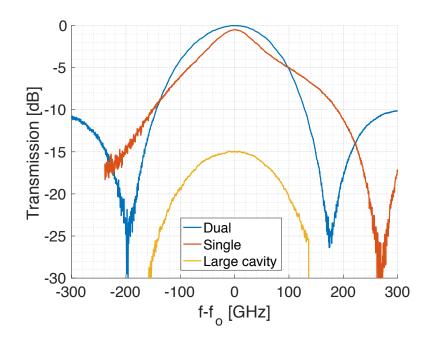

By assembling basic SE blocks in an interconnected network, higher port-count switch fabrics can be realized. The MRRs are ideal structures for highly integrated switch devices due to their miniaturized footprint. Leverage traveling wave cavity dynamics, each MRR-based SE is about 50-100 times smaller compared to MZI- or MEMS-based SEs, and thus enabling much higher integration density with significantly shrunk chip area. In this chapter, we showcase the designs for two multi-stage switch architectures using MRR-based SEs that have the potential to enable high performance, high radix photonic switch devices – an 8×8 Omega switch using dual-MRR SEs and a Clos network architecture with switch-and-select sub-switches for scaling to higher port count.

Designing MRR-based multi-stage switch requires co-optimizing the SE performance with the selection of the architectures [47]. The scalability of MRR-based fabric can be limited on three fronts: power penalties due to insertion loss and crosstalk of the resonator SEs in on- and off-resonance states, successive passband narrowing of cascaded MRRs, and control complexity of the large number of resonators. Previous demonstrations of MRR-based optical switches to date achieve a record of 8×8 connectivity [45] [46], and both adopt the crossbar architecture that requires only one SE to be controlled to connect an input to an output. However, the number of SEs in a crossbar architecture scales poorly as  $N^2$  for an N×N device, which poses a tremendous challenge in on-chip wiring and packaging complexity. In addition, a lightpath in a crossbar switch can traverse between 1 to (2N - 1) SEs, which means both the worst-case insertion loss and the variations of path-dependent power penalties would grow quickly with increasing port count [45]. In contrast, multi-stage architectures, such as the Beneš and Omega topologies, can provide a balance in the trade-offs between the total number of SEs and the number of cascaded switching stages [9] [75]. Individual MRR SE needs to possess a balanced set of performance metrics that