#### Algorithm and Hardware Co-Design for Local/Edge Computing

Zhewei Jiang

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy under the Executive Committee of the Graduate School of Arts and Sciences

COLUMBIA UNIVERSITY

© 2020

Zhewei Jiang

All Rights Reserved

#### Abstract

## Algorithm and Hardware Co-Design for Local/Edge Computing Zhewei Jiang

Advances in VLSI manufacturing and design technology over the decades have created many computing paradigms for disparate computing needs. With concerns for transmission cost, security, latency of centralized computing, edge/local computing are increasingly prevalent in the faster growing sectors like Internet-of-Things (IoT) and other sectors that require energy/connectivity-autonomous systems such as biomedical and industrial applications.

Energy and power efficient are the main design constraints in local and edge computing. While there exists a wide range of low power design techniques, they are often underutilized in custom circuit designs as the algorithms are developed independent of the hardware. Such compartmentalized design approach fails to take advantage of the many compatible algorithmic and hardware techniques that can improve the efficiency of the entire system. Algorithm hardware co-design is to explore the design space with whole stack awareness.

The main goal of the algorithm hardware co-design methodology is the enablement and improvement of small form factor edge and local VLSI systems operating under strict constraints of area and energy efficiency. This thesis presents selected works of application specific digital and mixed-signal integrated circuit designs. The application space ranges from implantable biomedical devices to edge machine learning acceleration.

### **Table of Contents**

| List of T | Tables                                                                                                                      | V  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------|----|

| List of F | Figures                                                                                                                     | vi |

| Acknow    | rledgments                                                                                                                  | X  |

| Introduc  | etion                                                                                                                       | 1  |

| Chapter   | 1: A Low Power Unsupervised Spike Sorting Accelerator Insensitive to Clustering Initialization in Sub-optimal Feature Space | 5  |

| 1.1       | Motivation                                                                                                                  | 5  |

| 1.2       | Algorithm                                                                                                                   | 8  |

|           | 1.2.1 Dataset                                                                                                               | 8  |

|           | 1.2.2 Informative Sample Screening                                                                                          | 10 |

|           | 1.2.3 Density-based Centroid Seeding                                                                                        | 12 |

|           | 1.2.4 Centroid based Clustering                                                                                             | 15 |

| 1.3       | Accelerator Architecture                                                                                                    | 15 |

| 1.4       | VLSI Implementation                                                                                                         | 17 |

| 1.5       | Summary                                                                                                                     | 20 |

| Chapter   | 2: 1.74-µW/ch, 95.3%-Accurate Spike-Sorting Hardware based on Bayesian Decision                                             | 21 |

| 2.1    | Motivation                                                                                                                  | 21 |

|--------|-----------------------------------------------------------------------------------------------------------------------------|----|

| 2.2    | Algorithm and Implementation                                                                                                | 22 |

|        | 2.2.1 Feature Space Distribution                                                                                            | 23 |

|        | 2.2.2 Cluster Validness Check                                                                                               | 23 |

|        | 2.2.3 Decision-Tree-like Sorting                                                                                            | 24 |

| 2.3    | Measurements and Comparisons                                                                                                | 26 |

| Chapte | 3: A sub-microwatt 96-Channel Neural Spike Processor for a Movement-Intention-<br>Decoding Brain-Computer-Interface Implant | 30 |

| 3.1    | Motivation                                                                                                                  | 30 |

| 3.2    | System Overview                                                                                                             | 31 |

| 3.3    | Spike Sorting                                                                                                               | 34 |

|        | 3.3.1 Supervised Training of the Constrained Bayesian Boundary Sorting                                                      | 34 |

|        | 3.3.2 Accuracy and Cost Evaluations                                                                                         | 37 |

| 3.4    | Intention Decoding                                                                                                          | 38 |

|        | 3.4.1 Ensemble Observation Kalman Filter                                                                                    | 38 |

|        | 3.4.2 Theoretical Basis                                                                                                     | 42 |

|        | 3.4.3 EOKF Evaluation                                                                                                       | 43 |

| 3.5    | NSP Processor Architecture                                                                                                  | 45 |

| 3.6    | Prototype Measurement                                                                                                       | 48 |

| 3.7    | Summary                                                                                                                     | 50 |

| Chapte | 4: XNOR-SRAM: In-Memory Computing SRAM Macro for Binary/Ternary Deep Neural Networks                                        | 52 |

| 4.1    | Motivation                                                                                                                  | 52 |

| 4.2     | IMC C  | OVERVIEW                                                                                    | 53 |

|---------|--------|---------------------------------------------------------------------------------------------|----|

|         | 4.2.1  | Multi-bit weights in IMC designs                                                            | 53 |

|         | 4.2.2  | Binary weights in IMC design                                                                | 53 |

|         | 4.2.3  | Multi-bit activation in IMC designs                                                         | 54 |

| 4.3     | XNOF   | R-SRAM Macro Design and Optimization                                                        | 54 |

|         | 4.3.1  | XNOR-SRAM Bitcell Design                                                                    | 55 |

|         | 4.3.2  | XNOR-SRAM Operation and Analysis                                                            | 58 |

|         | 4.3.3  | Transfer Function and ADC Optimization                                                      | 60 |

| 4.4     | Measu  | rement Results                                                                              | 62 |

|         | 4.4.1  | Energy Consumption and Performance Measurements                                             | 62 |

|         | 4.4.2  | Variability and Compensation                                                                | 63 |

|         | 4.4.3  | The Statistical Model of XNOR-SRAM and Voltage Scaling                                      | 65 |

|         | 4.4.4  | Strategy for Mapping DNNs onto XNOR-SRAM arrays                                             | 68 |

|         | 4.4.5  | DNN Accuracy Characterization                                                               | 68 |

| 4.5     | Summ   | ary                                                                                         | 72 |

| Chapter |        | SRAM: An In-Memory-Computing SRAM Macro Based on Robust Capace Coupling Computing Mechanism |    |

| 5.1     | Motiva | ation                                                                                       | 74 |

| 5.2     | Archit | ecture and Operation                                                                        | 75 |

|         | 5.2.1  | Memory Array Operation                                                                      | 75 |

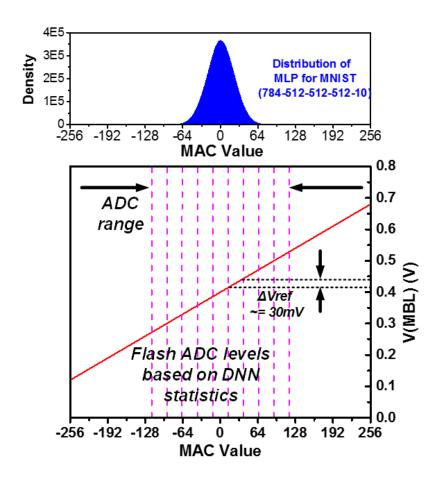

|         | 5.2.2  | ADC Operation                                                                               | 81 |

|         | 5.2.3  | Signal Switching Order                                                                      | 83 |

| 5.3     | Algori | thm Hardware Specification                                                                  | 84 |

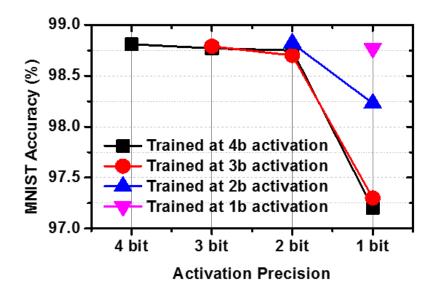

|         | 5.3.1 | Activation Bit Precision                | 84  |

|---------|-------|-----------------------------------------|-----|

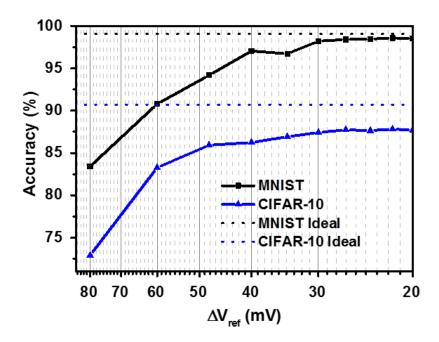

|         | 5.3.2 | Partial Convolution Quantization Levels | 86  |

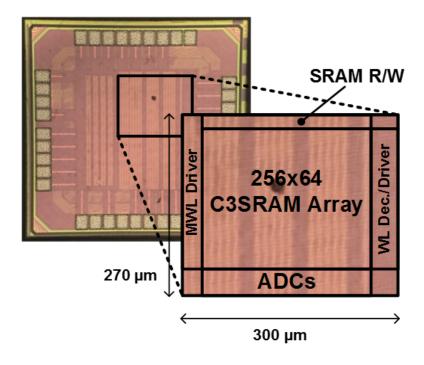

| 5.4     | Measu | rement and Analysis                     | 87  |

|         | 5.4.1 | Energy and Throughput                   | 87  |

|         | 5.4.2 | Transfer Function                       | 89  |

|         | 5.4.3 | Variability Measurement                 | 92  |

|         | 5.4.4 | Evaluation on Neural Network Tasks      | 95  |

| 5.5     | Summ  | ary                                     | 96  |

| Conclus | ion . |                                         | 98  |

| Referen | ces   |                                         | 106 |

### **List of Tables**

| 1.1 | Performance comparisons                                                                                          | 20 |

|-----|------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | Spike sorting accuracy                                                                                           | 37 |

| 3.2 | Comparison of number of calculations in EOKF and standard KF (20-neuron cortical map)                            | 42 |

| 3.3 | Comparison to prior BCI processors                                                                               | 51 |

| 4.1 | $V_{RBL}$ variance of a single column at 1.0V and 0.6V supply extracted from post-layout Monte-Carlo simulations | 64 |

| 4.2 | Measured MLP (for MNIST) and CNN (for CIFAR-10) accuracy summary using XNOR-SRAM at 0.6V supply                  | 73 |

| 5.1 | Comparison to prior IMC works                                                                                    | 91 |

| 5.2 | Measured MLP (for MNIST) and CNN (for CIFAR-10) accuracy summary using C3SRAM                                    | 96 |

## **List of Figures**

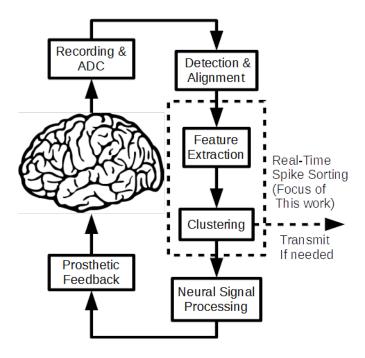

| 1.1  | A general brain-computer interface operation flowchart                                                                                                                      | 6  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

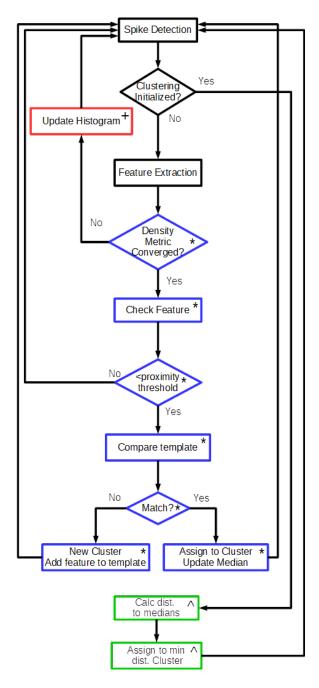

| 1.2  | Algorithm flow chart. The black, red, blue, and green boxes represent steps that are common operation and scheduling, phase 1, phase 2, and phase 3, respectively.          | ç  |

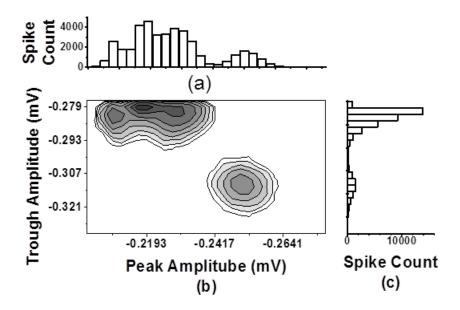

| 1.3  | (a) Histogram of spike peak amplitudes; (b) log scale contour plot of spike density in feature space, peak/trough amplitudes as X/Y axes; (c) histogram of trough amplitude | 11 |

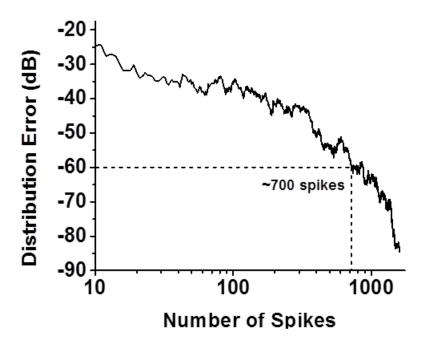

| 1.4  | The error in feature distribution decreases as more spikes are collected                                                                                                    | 13 |

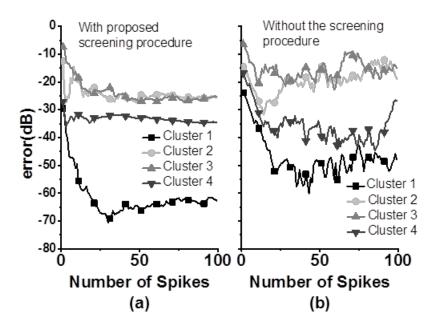

| 1.5  | The centroids convergence is shown to be more reliable in the algorithm with screening procedure (a) than without the procedure (b)                                         | 14 |

| 1.6  | Spike sorting accuracy at various initialization schemes                                                                                                                    | 16 |

| 1.7  | Block Diagram of the accelerator                                                                                                                                            | 16 |

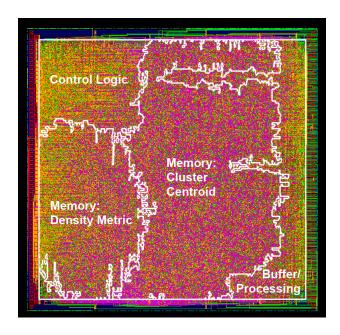

| 1.8  | The layout of the accelerator in a 65nm CMOS. The footprint is 226x226 $\mu m^2.\ .\ .\ .$                                                                                  | 18 |

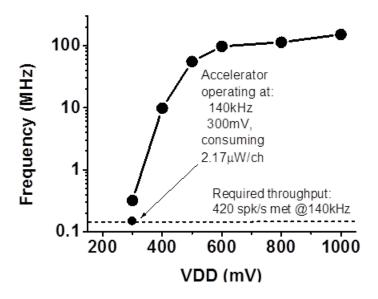

| 1.9  | Accelerator frequency based on critical path delay at various VDD levels                                                                                                    | 19 |

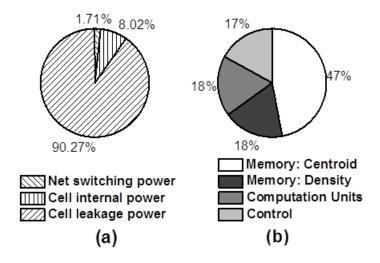

| 1.10 | (a) Power breakdown by type; (b) leakage power breakdown by source                                                                                                          | 19 |

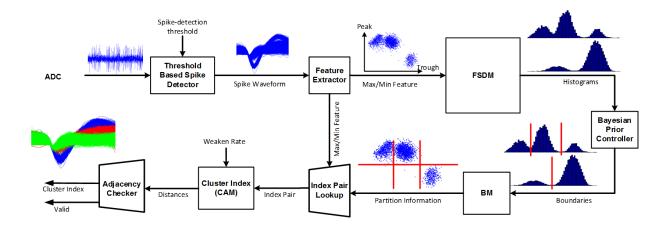

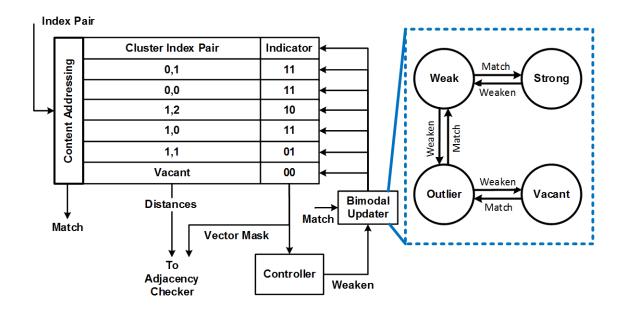

| 2.1  | Spike sorting accelerator block diagram                                                                                                                                     | 23 |

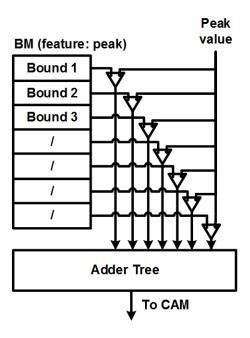

| 2.2  | Index Pair lookup for peak feature                                                                                                                                          | 24 |

| 2.3  | CAM architecture                                                                                                                                                            | 25 |

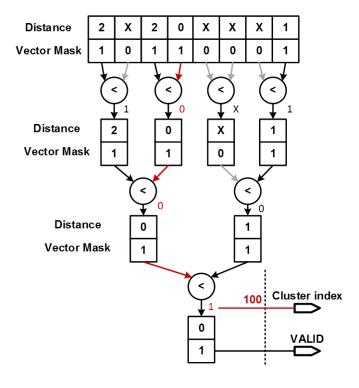

| 2.4  | Adjacency Checker                                                                                                                                                           | 25 |

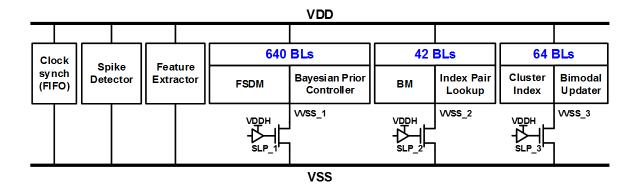

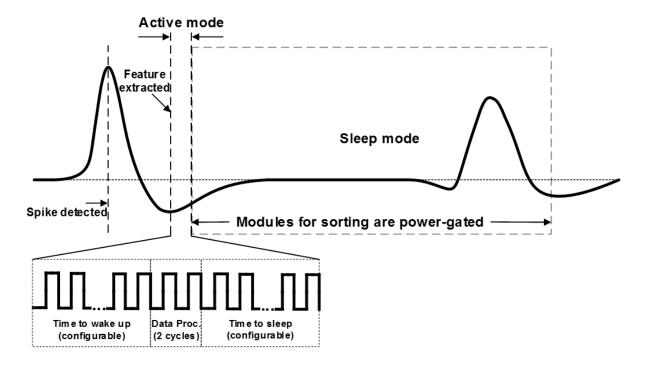

| 2.5  | Module power gating grouping.                                                                                                                                               | 26 |

| 2.6  | Power gating scheme                                                                                                                                                                                                            | 27       |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

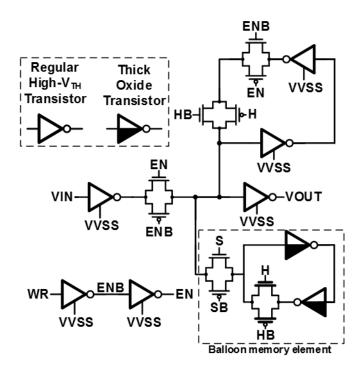

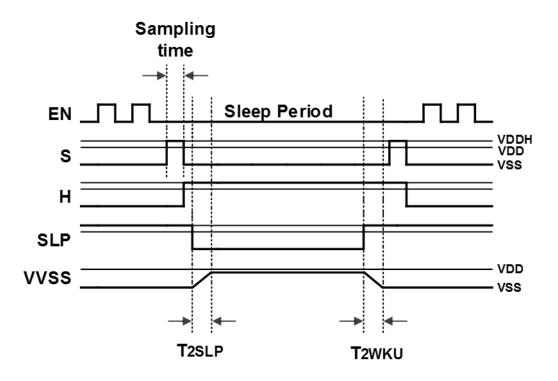

| 2.7  | Balloon latch schematics                                                                                                                                                                                                       | 27       |

| 2.8  | Balloon latch operation flow                                                                                                                                                                                                   | 28       |

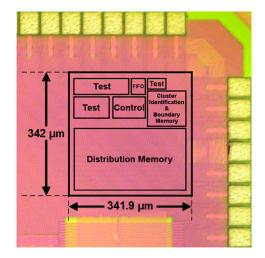

| 2.9  | Die photo                                                                                                                                                                                                                      | 28       |

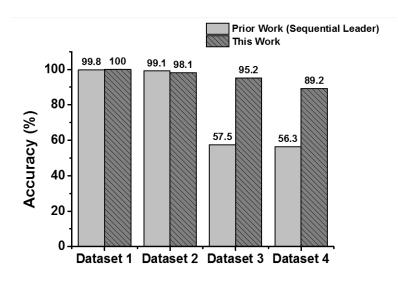

| 2.10 | Sorting accuracy comparison                                                                                                                                                                                                    | 29       |

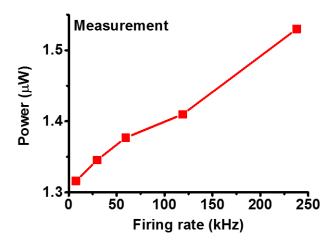

| 2.11 | Power vs. spiking rate                                                                                                                                                                                                         | 29       |

| 3.1  | Proposed prosthetic BCI task flow                                                                                                                                                                                              | 32       |

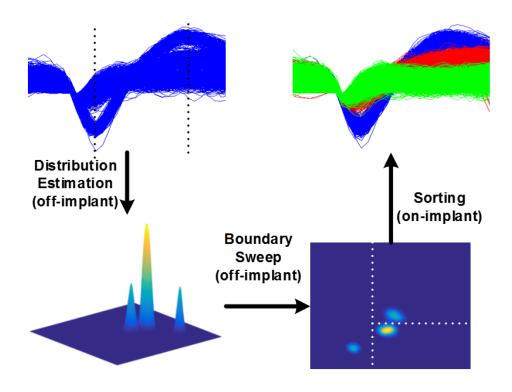

| 3.2  | Visualization of spike sorting via Bayesian approximate decision tree                                                                                                                                                          | 35       |

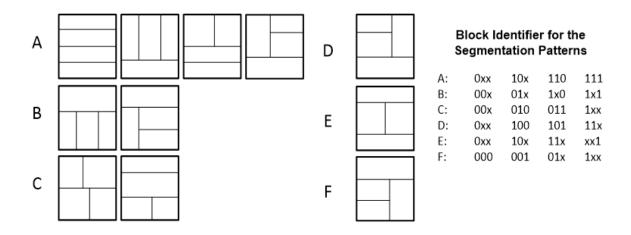

| 3.3  | Feature space segmented block identification coding                                                                                                                                                                            | 36       |

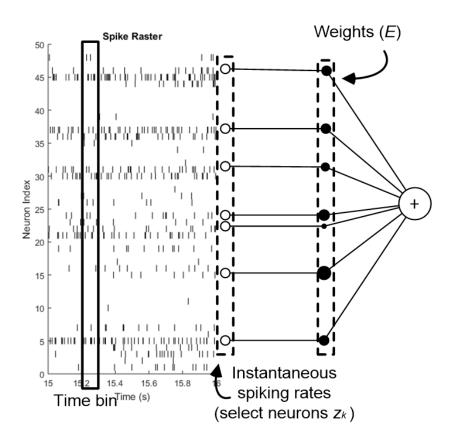

| 3.4  | Instantaneous spiking rates weighted in ensemble average for the observation based estimate of a kinematic state                                                                                                               | 40       |

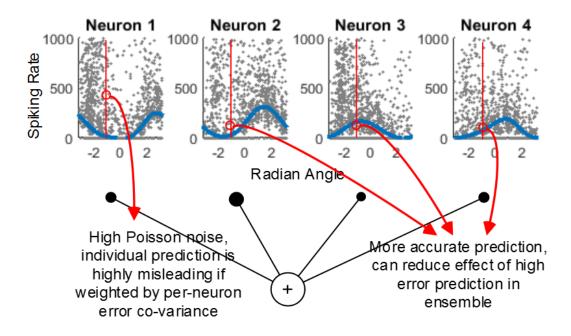

| 3.5  | Multivariat regression of ensemble neurons reduce the effect of noise                                                                                                                                                          | 44       |

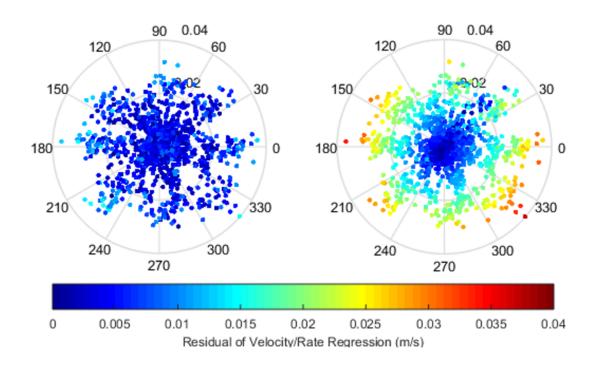

| 3.6  | State prediction error of ensemble prediction (left) and single neuron prediction (right) across angles and speed                                                                                                              | 45       |

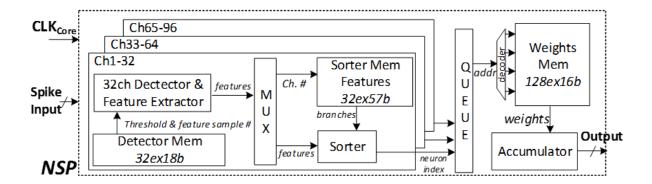

| 3.7  | The architecture of the proposed NSP                                                                                                                                                                                           | 46       |

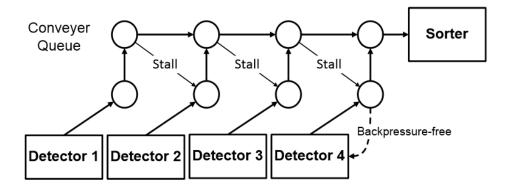

| 3.8  | Conveyor style queue of a 4-detector example                                                                                                                                                                                   | 47       |

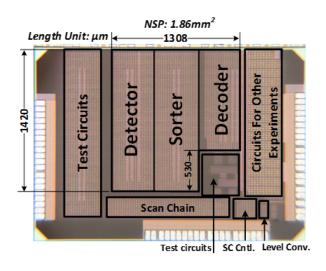

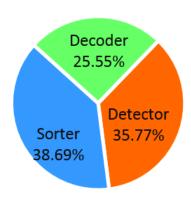

| 3.9  | Die photo and area breakdown                                                                                                                                                                                                   | 48       |

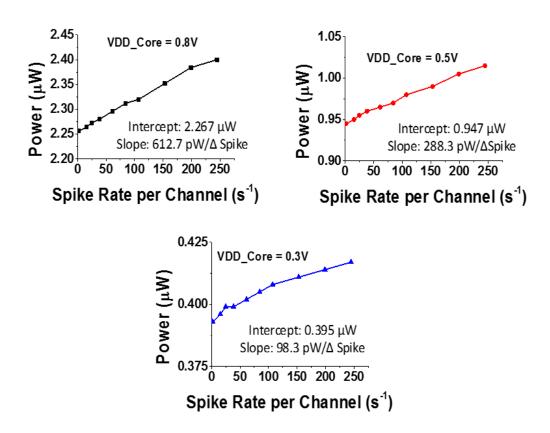

| 3.10 | Spike rate dependency of the NSP power                                                                                                                                                                                         | 49       |

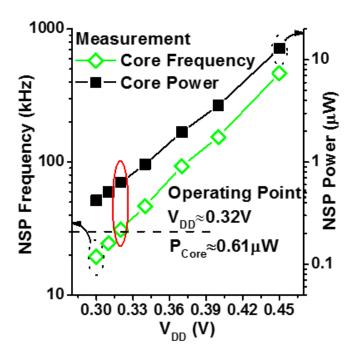

| 3.11 | Power and performance of the NSP                                                                                                                                                                                               | 50       |

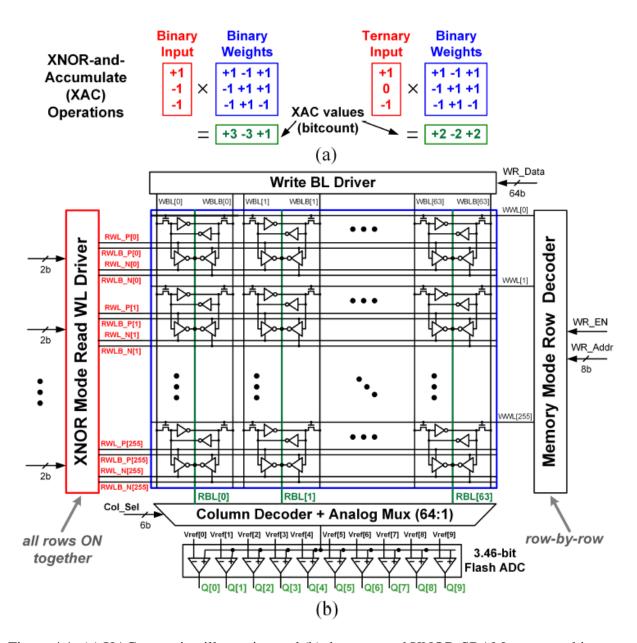

| 4.1  | (a) XAC operation illustration and (b) the proposed XNOR-SRAM macro architecture                                                                                                                                               | 56       |

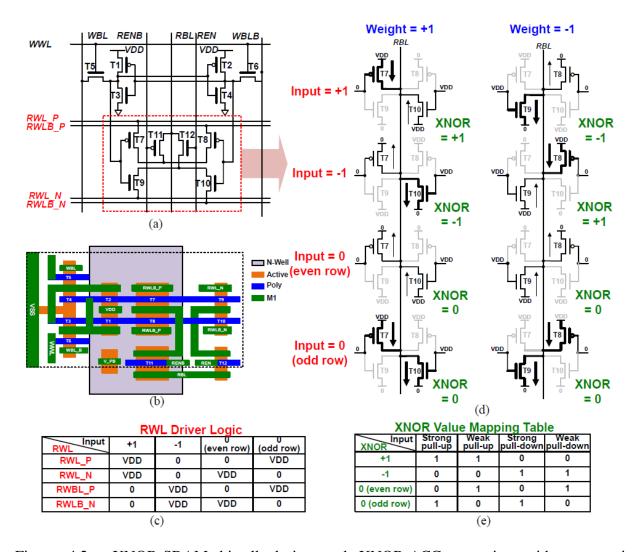

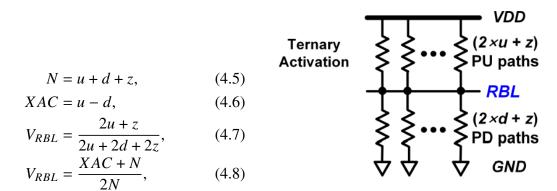

| 4.2  | XNOR-SRAM bitcell design and XNOR-ACC operation with ternary inputs/activation and binary weights. Bitwise ternary-XNOR output from each bitcell forms pull-up/-down paths on the RBL voltage, which represents the XAC value. | ns<br>57 |

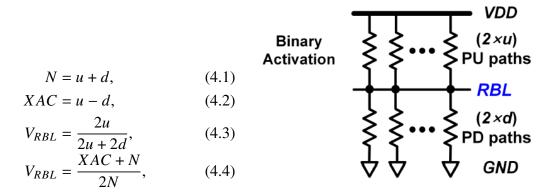

| 4.3  | PU/PD paths for $V_{RBL}$ with binary activations                                                                                                                                              | 59 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.4  | PU/PD paths for $V_{RBL}$ with ternary activations                                                                                                                                             | 59 |

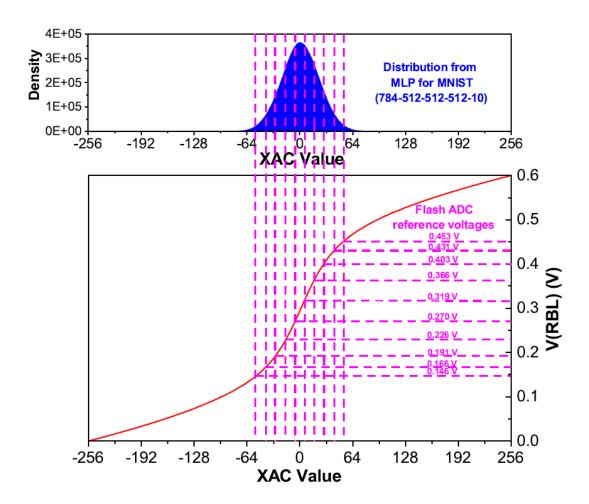

| 4.5  | XAC is mapped to $V_{RBL}$ . The confined linear quantization scheme is shown, along with the corresponding 10 reference voltages for the 11-level flash ADC                                   | 61 |

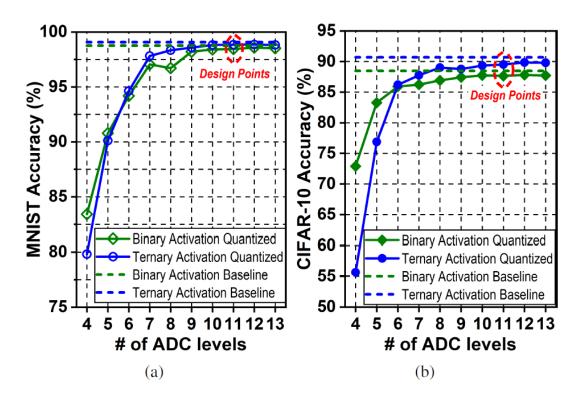

| 4.6  | The accuracy of the MLP trained for MNIST and that of the CNN for CIFAR-10 as a function of ADC levels                                                                                         | 62 |

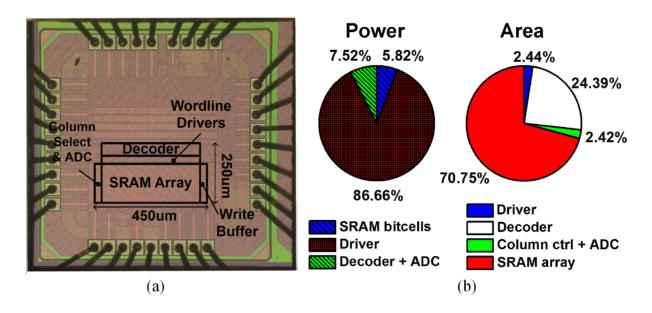

| 4.7  | (a) 65nm XNOR-SRAM prototype chip micrograph. (b) Power and area breakdown.                                                                                                                    | 63 |

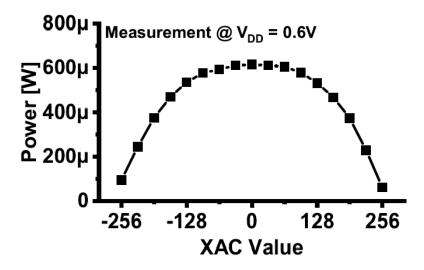

| 4.8  | Data dependent XNOR-SRAM power                                                                                                                                                                 | 64 |

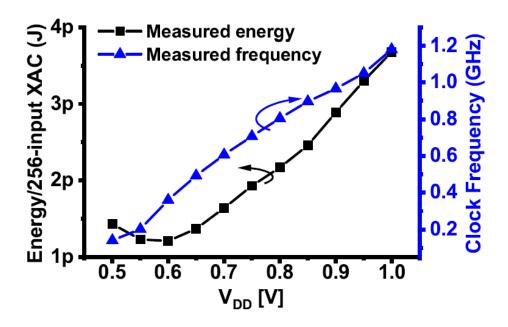

| 4.9  | Energy and frequency scaling with supply voltage                                                                                                                                               | 65 |

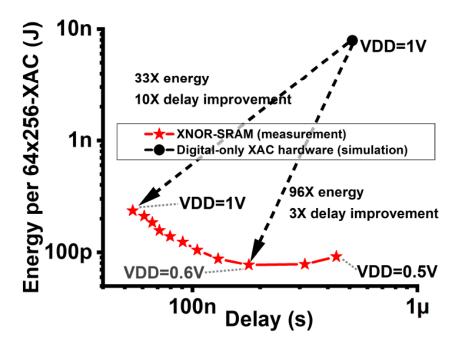

| 4.10 | Energy and delay comparison with digital baseline                                                                                                                                              | 66 |

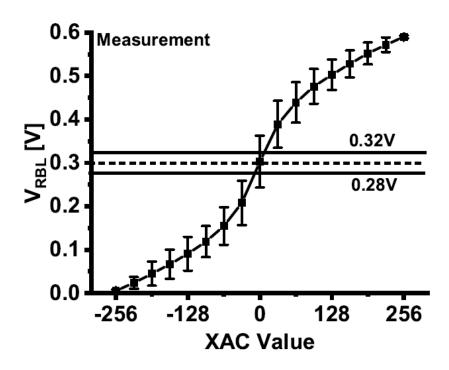

| 4.11 | Measured transfer function and variability                                                                                                                                                     | 67 |

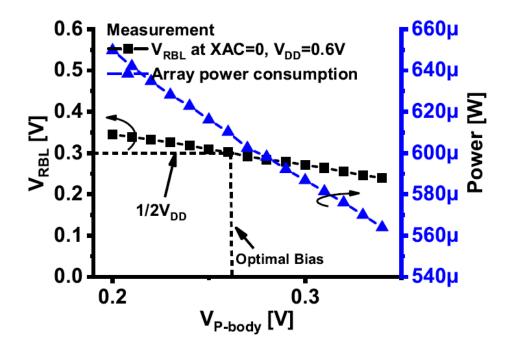

| 4.12 | Body bias tuning for PMOS/NMOS mismatch                                                                                                                                                        | 68 |

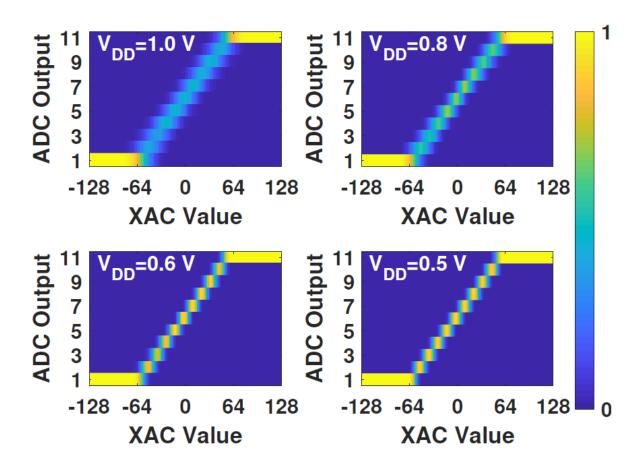

| 4.13 | Measured ADC output probability distribution as a function of XAC value at $V_{DD}$ of 1.0V, 0.8V, 0.6V, and 0.5V                                                                              | 69 |

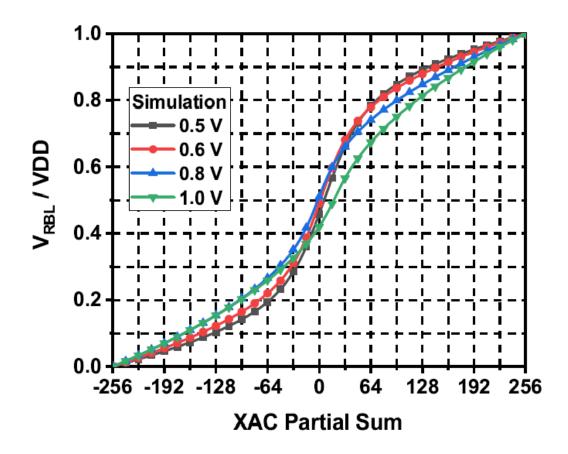

| 4.14 | Normalized transfer function at different $V_{DD}$                                                                                                                                             | 70 |

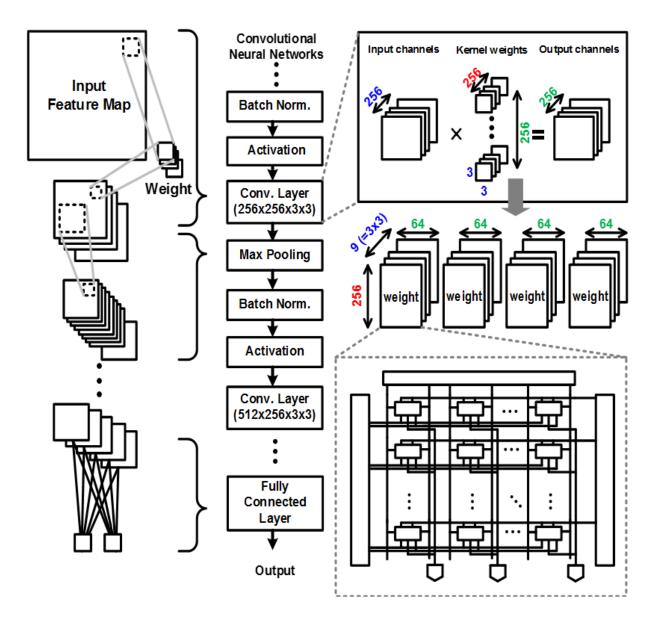

| 4.15 | Mapping convolutional neural networks to XNOR-SRAM-based in memory computing                                                                                                                   | 71 |

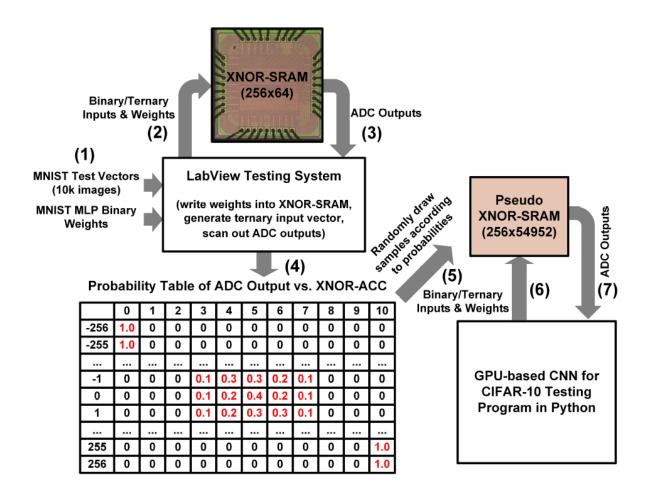

| 4.16 | Measurement based simulation framework for CIFAR-10 accuracy evaluation using XNOR-SRAM macros                                                                                                 | 72 |

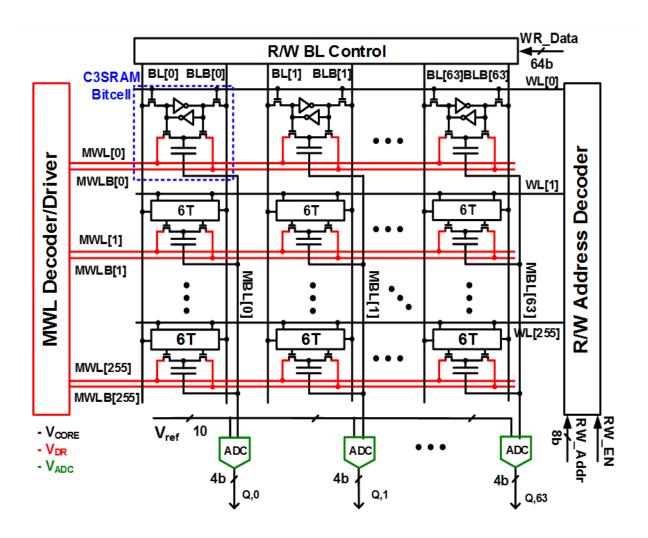

| 5.1  | Architecture of C3SRAM in-memory computing macro.                                                                                                                                              | 76 |

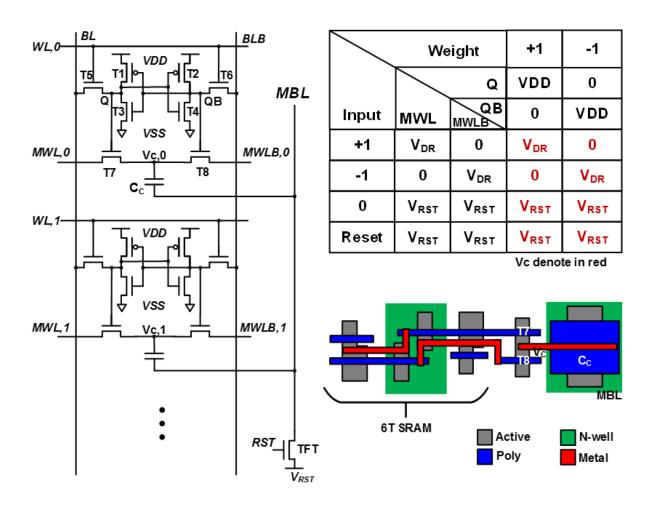

| 5.2  | C3SRAM bitcell design and in-cell bMAC operand table                                                                                                                                           | 77 |

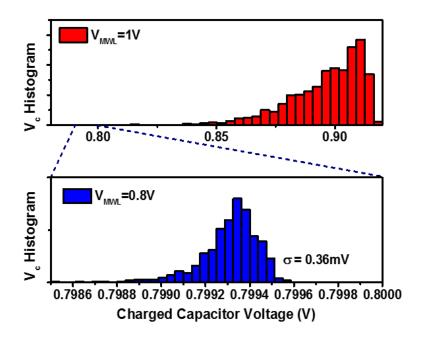

| 5.3  | Threshold voltage variability effects on charged capacitor voltage                                                                                                                             | 78 |

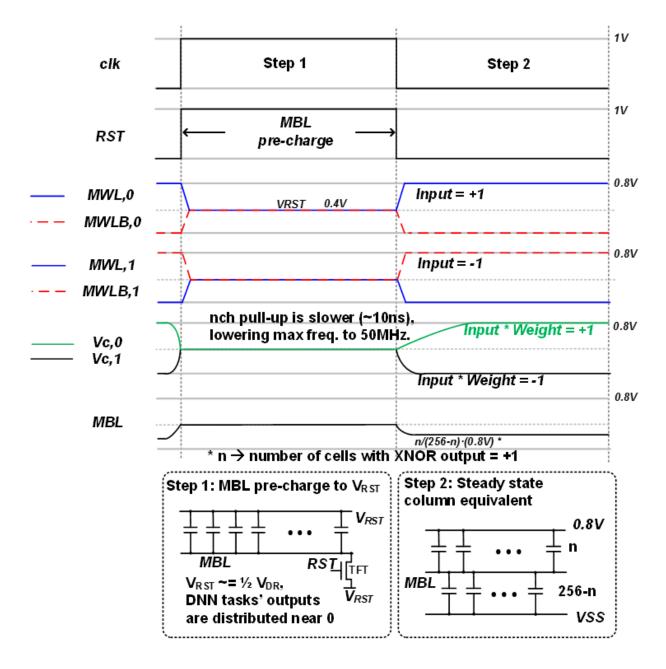

| 5.4  | Capacitive coupling based in-memory computation of bMAC                                                                                                                                        | 80 |

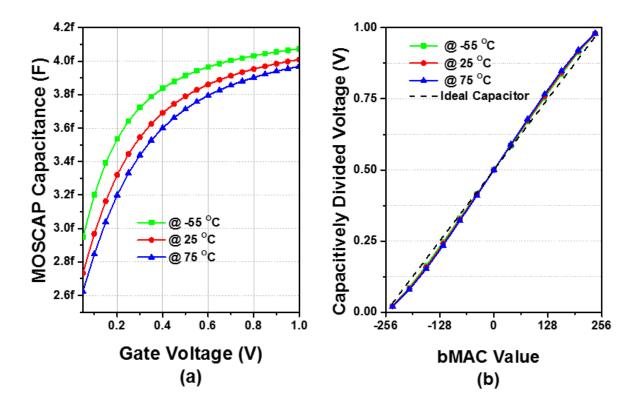

| 5.5  | (a) MOSCAP capacitance at TT corner simulation shows variation across temperature as well as the gate voltage; (b) MOSCAP capacitive voltage divider transfer function at various temperatures | 81 |

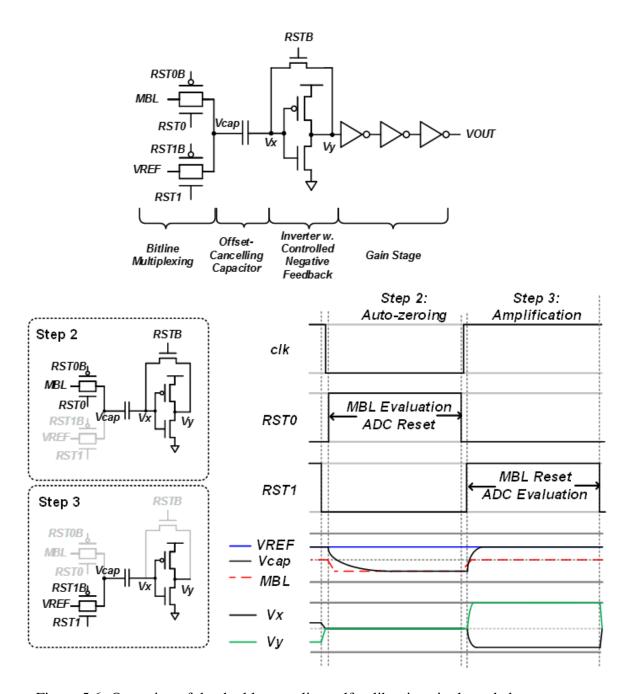

| 5.6  | Operation of the double-sampling self-calibrating single-ended comparator                                                                                                                   | 82 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

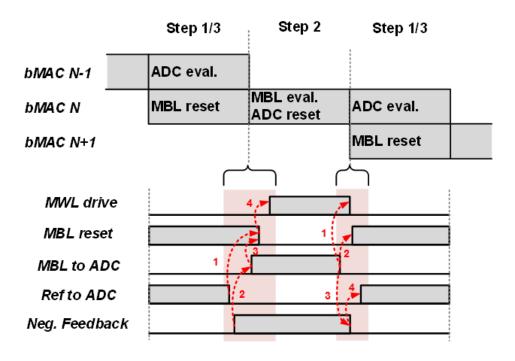

| 5.7  | Signal transition order for reducing analog non-idealities                                                                                                                                  | 84 |

| 5.8  | MLP on MNIST dataset inference accuracy losses at various levels of activation precisions                                                                                                   | 85 |

| 5.9  | MNIST and CIFAR-10 inference accuracies increase as quantization resolution of pre-activation partial sum (256 input) increases                                                             | 87 |

| 5.10 | The bMAC distribution of MLP for MNIST and quantization in limited ADC range.                                                                                                               | 88 |

| 5.11 | C3SRAM prototype chip micrograph                                                                                                                                                            | 89 |

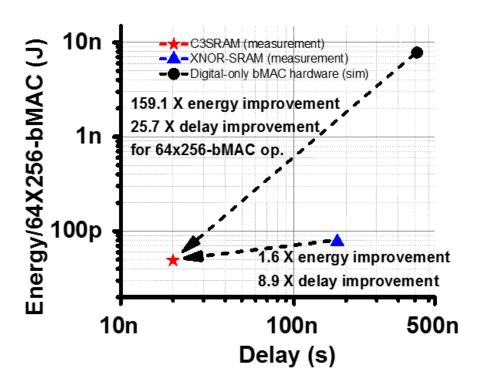

| 5.12 | C3SRAM energy and delay comparison with XNOR-SRAM and digital ASIC with traditional SRAM and ALU                                                                                            | 90 |

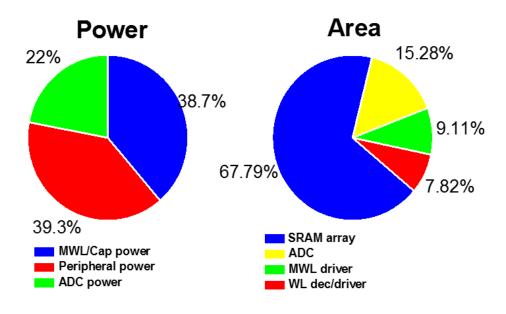

| 5.13 | Left: measured power consumption breakdown between the three supplies powering bMAC compute (blue), partial sum accumulation (red), ADC (green). Right: area breakdown of the C3SRAM module | 90 |

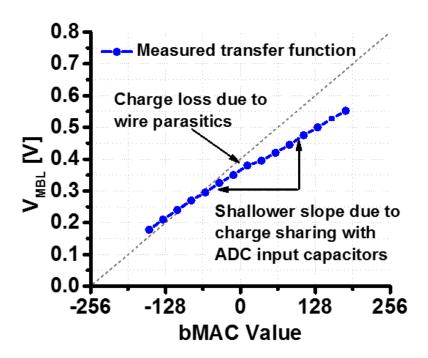

| 5.14 | Measured $V_{MBL}$ transfer curve shows lower FSR from ideal curve due to charge sharing with ADC input capacitors                                                                          | 92 |

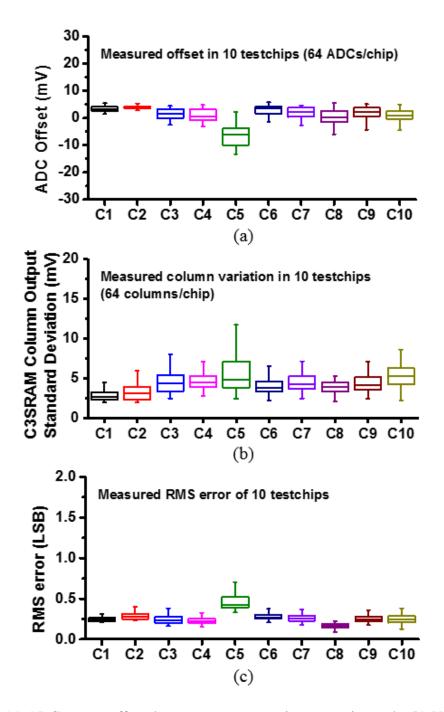

| 5.15 | (a) ADC output offset due to comparator gain stage mismatch, (b) $V_{MBL}$ error variation measurement, (c) RMS error of the macro                                                          | 94 |

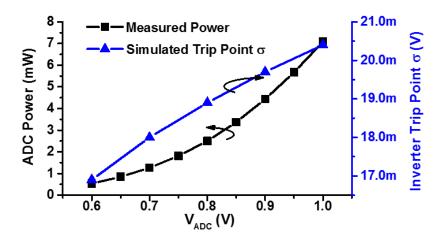

| 5.16 | ADC power increases exponentially as ADC power supply increases; the trip point variation increases linearly                                                                                | 95 |

#### Acknowledgements

I would like to thank my academic advisor, Prof. Mingoo Seok, for his assistance, support, and encouragement throughout my Ph.D. career at Columbia University. He set high standard in research, lead a great environment at the VLSI Lab, and has been a reliable source of technical guidance. I would like to thank Prof. Jae-sun Seo of Arizona State University, who I have collaborated with and has guided and shaped my research over the years. Many thanks to the other committee members of my thesis proposal and defense, Prof. Martha Kim, Prof. Dion Khodagholy, Prof. Xiaofan (Fred) Jiang, and Prof Charles Zukowski. They have graciously shared their valuable time with me and I greatly appreciate it.

I would like to thank the many outstanding people of VLSI Lab I've worked and collaborated with throughout my graduate career. Many thanks to Seongjong (Josh) Kim, Jiangyi Li, Joao Cerqueira, Minhao Yang, Pavan Chundi, and Sung Justin Kim. Beyond the VLSI lab, I'd like to thank Shihui Yin of Arizona State University who I have collaborated with for the last three years. Shihui's knowledge and meticulousness is indispensable in our work together. I am also grateful to my colleagues who I have learned from and enjoyed the company of. Many thanks to Teng Yang, Doyun Kim, Wei Jin, Tianchan Guan, Dongkwun Kim, Weiwei Shan, Bo Zhang, Daniel Kim, Ashish Shukla, and Peiye Liu.

I would also like to thank Prof. Richard Garner, Prof. Sean Bentley, and Prof. Gregory Mercurio of Adelphi University for not only shaping my academic career but also for their personal friendships.

Beyond academia, I would like to thank Dr. Vivek Joshi, Dr. 'Rumi' Muhammed Ahosan

Ul Karim, Dr. Xi Cao of GlobalFoundries for their guidance and mentorship during my internship at the Memory Solution Group. They imparted perspectives, insights, and advises to me that was and will continue to be valuable to my research career for my Ph.D. and beyond.

All of this was only made possible by the continued support by my mother, Fang Zhang. I am thankful for her love and support.

Zhewei Jiang

April 2020

#### Introduction

VLSI technology over the decades have created many computing paradigms for disparate computing needs in power, form factor, deployment environment, application, etc. In addition to the traditional pursuit of large scale and centralized computing, edge computing have increased in prominence in recent times, driven largely by the fast growing Internet-of-Things (IoT) in the consumer electronics sector. Similarly, local computing saw the same technological enablement in fields that demand energy or connectivity autonomy such as in biomedical and industrial applications.

Local and edge computing often operate under stringent resource constraints, the chief of which is power or energy efficiency. For many of these applications, the computing tasks and their associated parameters are limited in a way that embedding general purpose computing devices into such systems is inefficient and potentially infeasible. Such systems would benefit by unitizing application specific hardware, i.e. custom circuit that performs only the desired algorithms. Compartmentalized design methodology for algorithm and hardware takes system agnostic approach and develop algorithm independent of hardware, and to a less extent vice versa. Algorithm/hardware co-design is the design methodology that explores the large design space from algorithm and hardware perspectives simultaneously. Design efforts across multiple design stacks are often iterative, co-design methodologies are efficiency tools developed to address that, aiming to provide higher performance gain per design effort. Algorithm/hardware co-design has functionality and non-functionality specifications. Functionality spec simply refers to that the algorithm must be executable in the hardware. This is an open-ended problem with large design space. The non-

functionality specs refer to overall system performance like speed, power, and area. The co-design efforts are largely put toward the compliance of non-functionality specs.

At the most fundamental level, algorithm/hardware co-design is the optimization of an algorithm model that reflects hardware and system architectural behavior, with the inclusion of scheduling, data traffic model, and linkage between operators in the algorithm stack and processing element (PE) in the hardware stack.

The optimization method used in the presented projects is constraint allocation and partitioning. The process is as follows. First identify the baseline algorithm and the main constraints in the specification; then model the algorithm operators with the associated PE cost in the constraint domain; then experiment with applicable hardware techniques to allow re-allocation of constraint domain budget to in turn enable further modifications to PE/operator, scheduling, architecture; do so iteratively until design is optimized.

In the following chapter, 5 projects are presented, detailing designs achieved via constraint allocation based algorithm/hardware co-design.

In the first three chapters, the designs tackle implantable brain computer interface (BCI). For implantable hardware, the power and energy is the main design constraint, limited by battery life, charging mechanism, and most importantly the biological environment it interacts with. The projects make use of existing algorithms that were hardware-agnostic as they were not designed for implantable devices. Hence, there are many vectors for major hardware-aware augmentations through constraint allocation and partitioning.

Chapter 1 tackles the spike sorting problem for hardware with a power budget fit for implant. The baseline algorithm selected is the sequential leader algorithm. As with many clustering algorithms, there's an initialization challenge which can leads to high transient stage storage and computation cost. To re-allocate the resources, the transient memory units and high per-input runtime are targeted for optimization. The design implements a modified leader algorithm with an added screening stage. The screening stage samples the input data feature space and only performs cluster training using informative inputs, drastically reducing the memory and computations

necessary for centroid convergence.

Chapter 2 presents another spike sorting hardware. This project can be considered another iteration of the Chapter 1 design. By experimenting with power-gating memory elements, the sorting algorithm's constraint model is changed accordingly to trigger a constraint re-allocation. Schedule-based algorithm modifications is the new design goal. Given the algorithm/hardware for input feature distribution from the previous design iteration, a Bayesian boundary based sorting algorithm is devised to achieve improvements in energy and power by minimizing the per-input computing run-time.

Chapter 3 presents an end-to-end BCI system inclusive a Bayesian boundary based spike sorter from Chapter 2 and a partial neural intention decoding hardware. The baseline algorithm for neural decoding is the Kalman Filter. There are several vectors for modifications as there are on-chip/off-chip constraints in this project, giving it more freedom in constraint re-allocation. The major resource-consuming elements of the implant are the multiplier PE, wireless communication, and data traffic jam. In experimenting with a novel modified form of Kalman Filter, the algorithm allows data stream partition to reduce earlier than the baseline version, moving majority of high cost computations off-chip without incurring any on-chip cost, this in turn enables the replacement of multiplier PE with simpler adder, exploiting the discrete input of the on-chip portion of the neural decoding, which in turn solves the data traffic jam issue through the event-driven adder staggering the computations.

In the later two chapters, the in-memory-computing macros are designed to serve as components for larger ASIP systems handling the more flexible application of machine learning. In this fast growing sector, the energy and power limitation is imposed by the scaling of the already power hungry computations and memory wall. The co-design optimization goal is directed at the main computing primitive of machine learning tasks.

Chapter 4 presents a mixed-signal in-memory-computing macro which is capable of performing binary multiply-and-accumulate operation on the entire content of a memory module without explicit access. Chapter 5 presents another mixed-signal in-memory-computing macro which op-

| erate using a more robust and power efficient computing mechanism of capacitive coupling. |  |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|                                                                                           |  |  |  |  |  |  |  |

|                                                                                           |  |  |  |  |  |  |  |

|                                                                                           |  |  |  |  |  |  |  |

|                                                                                           |  |  |  |  |  |  |  |

|                                                                                           |  |  |  |  |  |  |  |

|                                                                                           |  |  |  |  |  |  |  |

|                                                                                           |  |  |  |  |  |  |  |

|                                                                                           |  |  |  |  |  |  |  |

|                                                                                           |  |  |  |  |  |  |  |

|                                                                                           |  |  |  |  |  |  |  |

|                                                                                           |  |  |  |  |  |  |  |

|                                                                                           |  |  |  |  |  |  |  |

|                                                                                           |  |  |  |  |  |  |  |

|                                                                                           |  |  |  |  |  |  |  |

# Chapter 1: A Low Power Unsupervised Spike Sorting Accelerator Insensitive to Clustering Initialization in Sub-optimal Feature Space

Online unsupervised spike sorting or clustering is an integral component of implantable closed-loop brain-computer-interface (BCI) systems. Robust clustering performance against various non-idealities such as poor initialization and order-of-arrival of inputs are desirable while meeting the minimal area and power requirements for implants. We explore an online and unsupervised spike-sorting algorithm utilizing a low-overhead feature screening process that improves feature discriminability in the use of sub-optimal features for reducing hardware complexity. Based on the algorithm, an accelerator architecture that performs feature screening and clustering is devised and implemented in a 65-nm high-V<sub>TH</sub> CMOS, largely improving clustering accuracy even with poor clustering initialization. In the post-layout static timing and power simulation, the power consumption and the area of the accelerator are found to be 2.17  $\mu$ W/ch and 0.052  $\mu$ m<sup>2</sup>/ch, respectively, which are 53% and 25% smaller than the previous designs, while achieving the required throughput of 420 sorting/s at the supply voltage of 300mV.

#### 1.1 Motivation

Advances in the BCI research have shown promising results in prosthetic, clinical, and other applications in laboratory settings [1, 2, 3]. In order to improve the practicality of these platforms, it is critical to develop a closed-loop BCI system which can be entirely integrated on a chip, and can autonomously operate with minimal need for user interference, thereby necessitates all processes to execute in a real-time unsupervised manner.

Figure 1.1 illustrates the operation flow of a typical invasive BCI system. The front-end begins with an implanted electrode array that probes the extracellular action potentials (i.e. multi-unit

Figure 1.1: A general brain-computer interface operation flowchart.

activities) near the target neurons. The analog waveforms are then digitized, followed by spike detection and alignment. After this, features of spikes are extracted for reducing the data dimensionality, and discriminable values in a chosen feature space are computed for clustering purpose. Then, each spike is assigned to a cluster by its waveform. Sorted spikes can be used in various ways depending on the application; the cluster indexes can be transmitted, or used to compute spike rates of targeted neurons which in turn can be inputs for various neural signal processing (e.g. regressions) to derive neural models for prosthesis, or, in a trained system, inputs to be translated into neuro-prosthetic intents and commands.

Feature-extraction and clustering are integral parts that are desirable to be performed in an unsupervised manner. Performing supervised training after placing an implant on a patient can require a significant amount of characterization efforts for creating and training with a patient specific dataset. In addition, the characteristics of spikes that an electrode array captures can vary over time, which may require regular expensive maintenance for re-training in case of long-term implants.

It is also critical to achieve online operation. The wireless communication between implants

and any external devices is expensive in power consumption. If all the detected spikes need to be wirelessly transmitted for offline feature-extraction and clustering, the power can be prohibitive [4, 5]. Online feature extraction and clustering have been shown to significantly reduce the required data rate for wireless communication, resulting in large energy savings in the system level [6].

Existing methods of feature extraction range from computationally intensive methods, e.g. principle component analysis (PCA), discrete wavelet transform (DWT), Bayesian algorithm, to computationally efficient ones which often extract time-domain features, e.g. peak-to-peak amplitude, spike width, zero-crossing feature, spike energy. Computationally intensive features like principle components and wavelet coefficients provide better inter-cluster discriminability but their power consumption and area, when implemented in a VLSI circuit form, can be prohibitive for resource-constrained implants.

On the other hand, time-domain waveform characteristics are intuitive to use and also inexpensive to extract but are not optimal in differentiating spike shapes [7]. Low discriminability negatively impacts clustering reliability by accentuating inherent non-idealities in many cluster algorithms such as sensitivity to initialization, input order-of-arrival, and disparate cluster membership. However, if we can mitigate those problems, i.e., improving clustering performance in sub-optimal feature space, the low complexity can help to significantly scale down power consumption and hardware footprint.

Therefore, we focus on developing a low-complexity yet robust multi-phase algorithm using sub-optimal features, and its efficient mapping onto VLSI accelerator architecture, for unsupervised and online feature extraction and clustering. The algorithm integrates three sub-algorithms, namely informative sample screening, density-based centroid seeding, and centroid-based clustering. The VLSI accelerator architecture of the algorithm is designed and implemented in a 65nm high threshold-voltage ( $V_{TH}$ ) CMOS. The post-layout static timing and power simulation shows that the accelerator consumes 53% less power (2.17  $\mu$ W/ch) and 25% smaller silicon footprint (0.05 $\mu$ m<sup>2</sup>/ch), as compared to the previous work [8], while easily meeting the required throughput (420 clustering/s) at the supply voltage (VDD) of 300 mV and the clock frequency of 140 kHz.

The chapter is organized as follows: Section 1.2 introduces the proposed algorithm; Section 1.3 details the VLSI architecture; Section 1.4 presents the circuit implementation, the delay and power consumption and the design, and the comparisons to the previous works; and Section 1.5 summarizes the chapter.

#### 1.2 Algorithm

This section explores a 3-phase unsupervised online spike sorting algorithm for improving clustering performance at low hardware complexity using sub-optimal features. Figure 1.2 shows the flow chart for the entire algorithm. The overview of the algorithm is: phase 1 informatively screens incoming samples based on a density-based metric, which is computed through constructing distribution histograms on feature space axes. The first phase concludes when a statistically significant amount of data is collected to faithfully represent the density distribution of the dataset. Phase 2 uses those selected informative samples to create centroids (i.e., centroid seeding). Cluster centroids are initialized and updated at the locally densest areas in the feature space. The second phase concludes when cluster centroids converge. Finally, in phase 3, spikes are assigned a cluster index via centroid-based clustering. No feature extraction is performed.

#### 1.2.1 Dataset

The algorithm and accelerator architecture is designed based on the dataset of single channel extracellular neuronal signals which were recorded in the sensory thalamus of vibrissa pathway in anesthetized rats. Neuronal signals were amplified, band-pass filtered (300–5 kHz), digitized in 8-bit resolution at 40 kHz/channel and collected using a 32-channel data-acquisition system (Plexon, Dallas, Tx). The dataset contains a total of 40k spikes originating from 4 neurons and has a signal-to-noise ratio of 2.9dB. A single spike consists of 32 samples. We also use the two other datasets which contain 40k spikes from 2 and 3 neurons, respectively, but mostly use the first dataset since it gives the lowest clustering success rate across all the experiments that we perform.

Detail procedures for creating the datasets were described previously [9, 10], approved by the

Figure 1.2: Algorithm flow chart. The black, red, blue, and green boxes represent steps that are common operation and scheduling, phase 1, phase 2, and phase 3, respectively.

Institutional Animal Care and Use Committee at Columbia University. Briefly, female rats (225 –300 g; Sprague Dawley) were sedated with 2% vaporized isoflurane and anesthetized with sodium pentobarbital (50 mg/kg, i.p., initial dose). Body temperature of the animals was maintained at 37 °C by a servocontrolled heating blanket (FHC, Bowdoinham, ME). After initial anesthesia, the animal was mounted on a stereotactic device (RWD Life Science, China) in preparation for the surgery and subsequent recordings. After the initial midline incision on the head, a small craniotomy (1 mm X 1 mm) was made on the left hemisphere over the ventroposterior medial nucleus (VPm) of the thalamus (2.0–4.0 mm caudal to the bregma, 2.0–3.5 mm lateral to the midline). A tungsten microelectrode was slowly advanced into VPm using a hydraulic micropositioner (Kopf Instruments, Tujunga, CA).

#### 1.2.2 Informative Sample Screening

Initialization sensitivity is a critical problem for centroid-based clustering such as k-means since they are heuristic [11] such that random initialization schemes can lead to drastically different results on the same data. Furthermore, fully implemented distance minimization is NP hard [12], hence reliable initialization are essential for enabling online unsupervised spike sorting.

For this purpose, we propose to perform informative sample screening in phase 1. The screening starts with establishing the knowledge of feature distributions. Specifically, using the early set of incoming spikes, histograms for features are generated, which are then used to determine if spikes are informative or not. Those informative spikes are passed to the phase 2 for the density-based cluster seeding, which serve as a critical foundation for the low-complexity centroid-based clustering in phase 3.

We select peak/trough amplitudes as spike features which are simple to extract but have large noise component in the feature space. Figure 1.3 (b) contour plot shows one dataset's feature space distribution. The features have multimodal distributions when projected onto feature space axes. As illustrated in the density histograms in Figure 1.3 (a) and (c), the low SNR of the dataset, however, contributes to the high variance in the distinguishable modes. High overlaps in modal

Figure 1.3: (a) Histogram of spike peak amplitudes; (b) log scale contour plot of spike density in feature space, peak/trough amplitudes as X/Y axes; (c) histogram of trough amplitude.

distribution represent poor inter-cluster separation. This makes the dataset ideal for evaluation of the proposed screening algorithm.

The distribution histograms of the peak and trough amplitudes are used as the density metric, devised with low hardware overhead by projecting each data points' amplitude features onto the axes which are segmented into bins with width  $\epsilon$ . The bins' width  $\epsilon$  is selected to match the proximity parameter of the density-based cluster seeding in phase 2. (Subsection 1.2.2 for details). The density is represented by the count of spikes in the bin and for each input, the peak and trough values are divided by bin size  $\epsilon$  and used as index to access and increment the density values (eq. 1.1 and 1.2). The screening rule relies on the multimodal density distributions in the feature space having distinguishable peaks in at least one dimension.

$$Density(\frac{max(spk_{in})}{\epsilon}) + + \tag{1.1}$$

$$Density(\frac{min(spk_{in})}{\epsilon}) + + \tag{1.2}$$

$$error_n = 20log \frac{rms(D_n - D_{final})}{rms(D_{final})}$$

(1.3)

If spikes have both peak and trough amplitudes that belong to target bins, they are chosen as informative samples. Target bins are bins that have local maximal density which corresponds to the peak of mode in the histogram. Fig. 3(b) shows that contours of highest density are located at coordinates where the bins are local maxima. The data shown in the Figure 1.3 is for the illustrative purpose. The full dataset has large ambiguity on border point assignment which might not be linearly separable.

The distribution histogram is found to be well converged, confirming the effectiveness of the informative sample screening. As shown in Figure 1.4 which shows the distribution error as more spikes are used to create the distribution, the error of the density metric reaches -60dB with normalized true density distribution at around 700 spikes. The error is defined as eq. 3.  $D_n$  and  $D_{final}$  are normalized distribution functions generated from n samples and the entire dataset respectively.

The approximate convergence period, i.e. the time to reach reliable density metric, is approximately 2 second based on the assumption maximum firing rate at 70 spikes per second from 6 neurons as specified by [8]. The 1-to-2 phase change can be scheduled by the use of a counter.

#### 1.2.3 Density-based Centroid Seeding

In the second phase, the proposed algorithm performs density-based centroid seeding, which estimates centroids using the informative samples screened in the phase 1. These parameters are passed to the phase 3 for centroid based clustering.

The proposed seeding part of the algorithm performs as such: screening process looks up each incoming spikes' feature in the density histogram, if both peak and trough belongs in local maximally valued bins, the spike is an informative sample. If it is the first spike found in a particular

Figure 1.4: The error in feature distribution decreases as more spikes are collected.

intersection, the spike waveform (not its features) is saved as the centroid of the cluster. All subsequent spikes with features matching the same bins are used to update the existing cluster median. Spikes that do not pass screening are discarded. After a period of time, the centroid for each cluster converges. And the converged median waveforms are used as seeds for the centroid-based clustering in phase 3.

The proposed density-based centroid seeding is developed based on a reduced DBSCAN (density-based spatial clustering in applications with noise) with the efforts to reduce computational complexity as well as the number of user-setting parameters.

The standard DBSCAN is an offline algorithm with  $O(n \log n)$  runtime, and requires two user setting parameters: proximity threshold  $\epsilon$  and minPts, the minimum number of data points within  $\epsilon$ -neighborhood to be considered density-reachable [13]. Setting appropriate minPts parameter requires prior knowledge of feature variance, which is non-trivial and costly to compute.

Density based informative sample selection allows the centroid seeding algorithm to execute without the parameter minPts. As mentioned previously, the proximity threshold  $\epsilon$  matches the

Figure 1.5: The centroids convergence is shown to be more reliable in the algorithm with screening procedure (a) than without the procedure (b).

bin width defined for the screening rule. As a result, all spikes in the same informative-sample-populated bins are of the same cluster, and no two such bins are adjacent in the feature space as they represent modal peaks in density distribution. Hence, there exists precisely one cluster centroid in or near each informative-samples-populated bin, provided that the features present distinguishable modes for each cluster.

In addition, the proposed algorithm has O(n) runtime. It does not need to visit all the points in its  $\epsilon$ -neighborhood while DBSCAN ( $O(n \log n)$  runtime) does. Rather, for each incoming spike that passes screening, it is immediately assigned to be a member of the cluster associated with the bins because the density-reachability is implicitly satisfied based on the distribution curve (modal peak).

Figure 1.5 illustrates the screening procedure's effect on centroid convergence error: (a) when using informative sample, (b) when using all incoming spikes. The convergence behavior of the proposed methods is shown to be more insensitive to initialization with on average 16dB lower error.

#### 1.2.4 Centroid based Clustering

Phase 3 has a simple winner-take-all scheme where the input spike is assigned to the cluster with the least distance to centroid. This clustering algorithm uses the converged median waveforms (seeds) found in the phase 2. The number of the centroids is also provided by the phase 2. Given that all centroids are initialized at less than -20dB deviation from the true centroids (Figure 1.5(a)), minimization of intra-cluster distance is implicitly met by assigning each incoming spike to the closest centroid. The distance metric we use is the L1 metric. L1 distance covers the full dimensions of the data. As pointed out in the previous work on on-chip spike sorting ASIC based on the sequential leader algorithm [8], L1 metric can provide noise tolerance and lower hardware cost comparing to the Euclidean distance. The L1 metric can be computed as shown in eq. 1.4:

$$d_{L1} = \sum_{n=1}^{N_{spk}} |spk_{in}(n) - spk_{centroid}(n)|$$

(1.4)

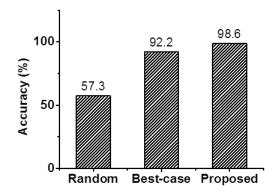

Finally, Figure 1.6 shows the performance of the algorithm. The first column shows an average of classification accuracy of 57.3% with randomly initialized centroids, algorithm based on sequential leader (used in [8]) with predetermined target for cluster number; second column shows an average classification accuracy of 92.2% with the best case initialization, i.e. the algorithm operates without informative sample screening just as that of the first column but is given an input order that initialized centroids near the true centroids; the third column shows an average of 98.6% accuracy rate with the propose algorithm, demonstarting superior insensitivity to order-of-arrival and the highest success rate among three.

#### 1.3 Accelerator Architecture

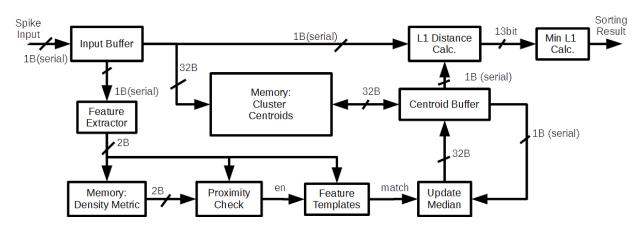

For the proposed algorithm, we devise the area and power efficient accelerator architecture (Figure 1.7). For phase 1, the features are used to aggregate the density metric, stored in a dedicated memory block (Memory: Density Metric in Figure 1.7). Memory address is feature values truncated to 6 bits MSB to represent  $\epsilon$  value of 4, i.e. feature valued 128 increments density value

Figure 1.6: Spike sorting accuracy at various initialization schemes.

Figure 1.7: Block Diagram of the accelerator.

in bin 32. The bin size is set to 1/64 of feature range to exploit binary encoding.

In phase 2, the features are used to read from the density metric memory values of the bin and its neighbors. Proximity check block then determines whether the input is an informative sample. If informative, the features are looked up in template memory block; if present, the waveform is used to update the centroid saved in cluster centroid memory block, if not present, the features are saved in template memory and the waveform is saved in centroid memory. Computations are performed on the centroid buffer block to reduce read/write accesses.

In phase 3, L1 distance calculation block computes the distance between input and each centroid, and minimum L1 calculation block determines the cluster index the input belongs to. The index is the final output of the accelerator.

The main goal in the architecture design is to minimize power consumption and silicon footprint. For this, we ensure large memories in the accelerator are not directly clocked to lower switching power on the clock tree. Switching activities in memories are therefore limited to reading and writing access only. Given that the majority of the circuits are devoted to memories, it is extremely important to reduce their switching activities.

In the accelerator design, most of the circuit is idle (zero switching activities) at any clock cycle. As a result, leakage dominates the power consumption. We implemented all computational blocks serially in order to reduce leakage on the architecture level. Higher switching activity associated with serial design is insignificant in this accelerator implementation, with only schedule controller and clock network being affected. Serial implementation decreases the computational blocks' silicon footprint by a factor of 32, and also significantly reducing idle leakage.

In addition, we select the lowest operating frequency for low power consumption while still yielding the comparable throughput reported in [8] where a single channel DSP operating at 480 kHz can process 6 neurons firing at 70 spikes/s. Our design benefits from informed initialization to achieve the same throughput with 140 kHz clock, on account of lesser transient clusters.

#### 1.4 VLSI Implementation

The accelerator is implemented in a 65nm CMOS. As previous works [8, 14] have identified leakage power as dominant in implantable chip power budget, the accelerator is synthesized with high- $V_t$  devices for minimizing leakage. The low clock frequency requirement also allows us to use near/sub-threshold supply voltage to minimize power consumption. Therefore, in order to ensure the robustness of gates at the aggressively-scaled supply voltage, we only use a subset of the industrial standard cell library during the synthesis that are found to be robust at near/sub-threshold supply voltages. While low-voltage optimized SRAM can be used for reducing the footprint for various memories, we decide to use the latches in the standard cell library for high robustness.

The design is automatic-place-routed (APR-ed), and the layout view of the implemented accelerator is shown in Figure 1.8. This is a single channel spike sorter unit with no dependency on

Figure 1.8: The layout of the accelerator in a 65nm CMOS. The footprint is  $226x226 \mu m^2$ .

external computation blocks or parameter, with fixed front end configurations built-in. The area of the design is 0.052 mm<sup>2</sup>.

We perform the static timing analysis using the libraries characterized at multiple supply voltages and the interconnect parasitic information generated by the APR tool. The accuracy of the timing and power characterization flow is calibrated and confirmed by comparing its result to the results of SPICE simulation for benchmark circuits.

As shown in Figure 1.9, at the supply voltage of 0.3V, the maximum clock frequency can be as high as 324 kHz, more than twice the required clock frequency of 140 kHz. At 0.3V, the power consumption is characterized to be  $2.17\mu W$ .

As shown in Figure 1.10(a), power consumption breakdown by type indicate that the leakage power consists of 90% of all power consumptions. Leakage breakdown by module in (b) indicates that majority of the power consumed is still from memory blocks, with the centroid and histogram memories consuming 65% of the total power (47% and 18% respectively).

Finally, Table 1.1 details comparison with previous works in spike sorting DSP. To our best knowledge, the architecture in [8] is the only other design that implementes real-time unsupervised spike sorting. Our accelerator is a single channel classifier that is scaled linearly and inter-unit

Figure 1.9: Accelerator frequency based on critical path delay at various VDD levels.

Figure 1.10: (a) Power breakdown by type; (b) leakage power breakdown by source.

Table 1.1: Performance comparisons.

|                                     | [15]  | [4]  | [14] | [8]  | This work |

|-------------------------------------|-------|------|------|------|-----------|

| No. of channels                     | 32    | 128  | 64   | 16   | 1         |

| Detection                           | Y     | Y    | Y    | Y    | N         |

| Feature extraction                  | N     | Y    | Y    | N/A  | Y         |

| Clustering                          | N     | N    | N    | Y    | Y         |

| Data-rate reduction                 | 12.5x | 80x  | 11x  | 240x | 85x       |

| Clock frequency (MHz)               | _     | _    | 0.4  | 0.48 | 0.14      |

| Throughput (sorting/ch/s)           | N/A   | N/A  | N/A  | 420  | 420       |

| Power (µW/channel)                  | 75    | 100  | 2.03 | 4.68 | 2.17      |

| Area (mm²/channel)                  | 0.11  | 1.58 | 0.06 | 0.07 | 0.05      |

| Power density (µW/mm <sup>2</sup> ) | 682   | 63.3 | 33.8 | 66.8 | 43.4      |

| Process(nm)                         | 500   | 350  | 90   | 65   | 65        |

| Core voltage (V)                    | 3     | 3.3  | 0.55 | 0.27 | 0.3       |

independent. The proposed design achieves considerably lower power consumption and silicon footprint.

#### 1.5 Summary

In this chapter, we propose a hardware spike sorting accelerator that provides online, unsupervised clustering with initialization and order-of-arrival insensitivity. By screening data using proximity to centroid in feature space, we can improve the performance of the clustering algorithm as well as reduce hardware complexity. Efficient hardware architecture and circuit techniques are devised in order to reduce power consumption and silicon footprint. For the dataset instrumented from rats, the designed accelerator achieves 98% accuracy in spike sorting. The converged centroid error is also improved by 16dB. Implemented in a 65nm CMOS, the accelerator exhibits the footprint of  $0.05\mu m^2$  and the power consumption of  $2.17\mu W$ , which are 25% and 53% better than the previous state-of-the-arts.

## Chapter 2: 1.74-µW/ch, 95.3%-Accurate Spike-Sorting Hardware based on Bayesian Decision

This chapter presents algorithm/hardware co-design for real-time unsupervised spike sorting hardware for reducing power and improving sorting accuracy. We devise an algorithm based on Bayesian decision, which enables high accuracy while using noisy and simple time-domain features. Those simple features significantly reduce computation complexity, memory requirement, and thus the required number of cycles per sorting. The latter, coupled with the sparsity of spikes in time, makes the hardware idle for most of time, and thus we employ aggressive power gating and balloon latches to sleep most of the circuits and wake them up only when a spike is detected for maximal power savings.

#### 2.1 Motivation

Online neural spike detection and sorting (clustering spikes by waveform features) is an important step between neural signal sensing and motor-intention decoding for closed-loop neural prosthetic systems. Implanted electrodes sense activities of multiple neurons while decoding often needs single-unit spiking rates. Therefore, implantable hardware for real-time spike detection and sorting [8, 16] is critical to close a loop and to reduce communication cost between an implant and an external receiver [4, 17].

One of the state-of-the-art hardware for spike sorting implements the sequential leader algorithm which computes sums of differences between samples of incoming and centroid waveforms [8]. While the simple time-domain feature allows it consume low power (4.68µW/ch) and compact area (0.07mm²/ch), the hardware suffers from low clustering accuracy (78.2% while sorting 96k spikes) mainly due to the use of less robust time-domain features.

In this chapter, we pursue algorithm/hardware co-design to increase clustering accuracy and minimize power dissipation. We propose a novel sorting algorithm that can self-learn a decision metric based on Bayesian boundary [18] from incoming spike waveforms. While the algorithm also uses very simple time-domain feature (i.e., min and max values of a spike), the self-learning capability enables the algorithm to robustly sort spikes. When mapped onto hardware architecture, indeed, the simple time-domain features can largely reduce computation and memory requirement, allowing the hardware to finish sorting a spike in 2 clock cycles, while the conventional sequential leader algorithm can take hundreds of cycles. The reduced computing complexity coupled with spike sparsity in time allows us to have the hardware in a sleep mode for most of the time via power gating switches and balloon latches (BL).

We prototype test chips for the proposed sorter having one channel, which can sort 420 spikes/s at the sorting accuracy of 95.3% while consuming 1.74µW at VDD of 0.6V, both significantly improved from the prior arts [8].

#### 2.2 Algorithm and Implementation

The sorter performs spike sorting in a per-channel basis. As shown in Figure 2.1, the hardware starts with a threshold based spike detector at the input. The detector is preconfigured with a threshold derived from channel noise, and operates on the continuous sample stream from the ADC. The features used in the spike-sorting task are the maximum (peak) and minimum (trough) value of each spike waveform. A feature extractor extracts the peak and trough of action potentials of each spike waveform for the following training or sorting process.

The theoretically optimal sorting solution in the 2-dimensional feature space is a set of free-form Bayesian boundaries from clusters' distribution intersects. This approach is, however, far too costly to on-implant processing as it requires large memory and complex computations. Instead, we project two of single-feature Bayesian distribution boundaries to the 2-feature space, forming a set of grid-constrained boundaries, effectively a 1.5-dimension feature space for a relaxed hardware requirement.

Figure 2.1: Spike sorting accelerator block diagram.

## 2.2.1 Feature Space Distribution

The first step of the training process is to identify Bayesian decision boundary. For each detected spike, the hardware updates the two histograms of the peak and trough values (Figure 2.1) in the Feature Space Distribution Memory (FSDM). After the specified number of spikes are used for updating histograms, the Bayesian Prior Controller traverses the FSDM for finding the local minima of each feature distribution and store them as Bayesian decision boundaries in the Boundary Memory (BM). The boundaries are used to orthogonally partition the feature space, with each partition identifiable by a pair of indexes.

#### 2.2.2 Cluster Validness Check

After the boundaries are found, each feature space partition is to be assigned a status as either a cluster or unnecessary segmentation. This is done by updating the confidence level of the cluster status of each partition in the feature space. The specific steps are as follow. First, the Index Pair Lookup (Figure 2.2) compares the features of an incoming spike with the Bayesian boundaries in the BM. This locates the specific partition that the spike belongs in. The pair of indexes is then fed to a CAM (Figure 2.3). If the CAM finds the pair of indexes in it, it increases the confidence level of the entry by setting the associated 2b indicator (00-vacant, 01-outlier, 10-weak cluster, 11-strong cluster). If no match, it places the index pair in the first vacant entry, with indicator set

Figure 2.2: Index Pair lookup for peak feature.

to 01. The controller periodically decreases all entries' indicators once per N spikes to remove outliers from strongly-recognized clusters (Figure 2.3).

## 2.2.3 Decision-Tree-like Sorting

The spike sorting process can start after a specified amount of training. It performs the same computation for finding an index pair, but the hardware no longer updates the CAM indicators. The result of the CAM which represents distances to partitions enters the Adjacency Checker, which then finds the closest partition that is a valid cluster. The checker performs min function with a vector mask that selects clusters only with 10 and 11 indicators. The partition index is found via the comparison paths (Figure 2.4).

The algorithm is similar to a decision tree. The branching conditions are Bayesian boundaries found during training. However, the cluster status update serves as a pruning process on the decision tree in a manner that leaves it in a partial coverage of the feature space. The pruned branches are recovered in the deployment stage via a least distance comparison.

The proposed architecture can greatly reduce memory requirement and computational com-

Figure 2.3: CAM architecture.

Figure 2.4: Adjacency Checker.

Figure 2.5: Module power gating grouping.

plexity. While the conventional sequential leader algorithm needs to store a full waveform per each cluster centroid, the proposed architecture stores only a pair of indexes and a few boundaries per each cluster. Assuming 48 samples/spike, 8b ADC resolution, 4 clusters/ch, and 2b/index, and 6b/boundary, the former requires 1,536 (= 48 \* 8 \* 4) bits while the latter can require only 36 (= 6 \* 2 + 4 \* 6) bits. Similarly, the proposed architecture requires eight 6b comparisons and single 6b equality operation per sorting while the sequential leader algorithm needs 48 8b additions and 45 14b additions per sorting.

Thanks to the low computational complexity, the proposed architecture takes only 2 clock cycles for sorting a spike. As incoming spikes are sparse in time, the hardware can be idle for most of the time. In order to minimize the power dissipation during idle time, as shown in Figure 2.5, the hardware aggressively employ power gating switches (PGS) and BLs. Therefore it can have most of the modules in a sleep mode and wake them up only when detecting a new spike (Figure 2.6). We design a BL in thick oxide devices for leakage savings (Figure 2.7). The control signals for PGS are bootstrapped to 1V via level converters for reducing wakeup time (T<sub>2WKU</sub>). Figure 2.8 shows the operating waveforms of a BL.

## 2.3 Measurements and Comparisons

We prototype test chips for the proposed sorter in a 65nm high- $V_t$ (Figure 2.9). The macro is of a single channel as online training has high area cost. In order to integrate the online training

Figure 2.6: Power gating scheme.

Figure 2.7: Balloon latch schematics.

Figure 2.8: Balloon latch operation flow.

Figure 2.9: Die photo.

Figure 2.10: Sorting accuracy comparison.

Figure 2.11: Power vs. spiking rate.

hardware in an implant, we designed the system to perform the training process for each channel in a time-multiplexed manner. The proposed architecture achieves the average accuracy of 95.3% in sorting 96k spikes in four datasets. For the same waveforms, the sequential leader algorithm can achieve the accuracy of only 78.2% (Figure 2.10). At VDD of 0.6V and the throughput of 420 spikes/s/ch, the proposed hardware consumes 1.74  $\mu W$ , 2.7X smaller than the prior art's power dissipation of 4.68  $\mu W/ch$  at the same throughput. Note that the power consumption scales with throughput (Figure 2.11). The proposed architecture takes 0.116mm² .

# Chapter 3: A sub-microwatt 96-Channel Neural Spike Processor for a Movement-Intention-Decoding Brain-Computer-Interface Implant

This chapter presents sub-microwatt end-to-end neural signal processing hardware for deployment-stage real-time upper-limb movement intent decoding. This module feature intercellular spike detection, sorting, and decoding operations for a 96-channel prosthetic implant. We design the algorithms for those operations to achieve minimal computation complexity while matching or advancing the accuracy of state-of-art BCI sorting and movement decoding. Based on those algorithms, we devise the architect of the neural signal processing hardware with the focus on hardware reuse and event-driven operation. The design achieves among the highest level of integration, reducing wireless data rate by more than four orders of magnitude. The chip prototype in a 180-nm high- $V_t$ , achieving the lowest power dissipation of  $0.78\mu W$  for 96 channels,  $21\times$  lower than the prior art at a comparable/better accuracy even with the partial decoding function integration.

#### 3.1 Motivation

Advances in brain-computer-interface (BCI) research is aiding the development of prosthesis for patients with limited mobility. Prosthesis can be categorized as passive or active. While passive prosthesis only provides structural support for patients, active prosthesis can perform the patients' intended motor function, autonomously or controlled. BCI can aid active prosthesis by mapping their neural activities to the intended movements and actuating them. Hence, BCI systems are invaluable in limited mobility rehabilitative services [19, 20, 21, 22, 23].

A prosthetic BCI operates by measuring neural activity and inferring the intended movement based on a learned model (cortical map) that relates the neural behavior to the movement intention. Neural activities useful for motor intention decoding can be sampled directly from residual muscle activation near the prosthesis site or deep within the motor cortex in the brain. Any neural signals encoding motor intention can support BCI prosthesis if the encoding scheme can be reliably modeled. For locked-in patients without residual muscle activation, only central nervous signals can aid the prosthesis. Extracellular spiking activity from pre-motor or motor cortex is currently the state of the arts for upper limb movement decoding [21], outperforming non-invasive systems based on signals such as EEG [22] or MEG [23]. Unlike EEG or MEG, the detection of spiking neural signal requires surgical procedure to implant probes and peripheral support devices. The invasiveness places additional physical design constraint, e.g. power consumption, to the already complex algorithmic challenges.

In this chapter, we present a full stack design and the prototype of a prosthetic Neural Spike Processor (NSP). The NSP decodes neural spike information into direction and velocity of intended muscle movement, enabling rehabilitative services for patients. We modify and improve existing neural decoding algorithms to implement our design.

The remainder of the chapter is organized as follows. In Section 3.2, we first briefly present the scope and tasks involved in the BCI system. In Section 3.3, we detail our spike sorting algorithm. In Section 3.4, we present our neural decoding approach and evaluate the accuracy and cost of our hardware. In Section 3.5, we present the architecture of the NSP chip. In Section 3.6, we present the prototype and measurements. Finally, Section 3.7 summarizes the chapter.

#### 3.2 System Overview

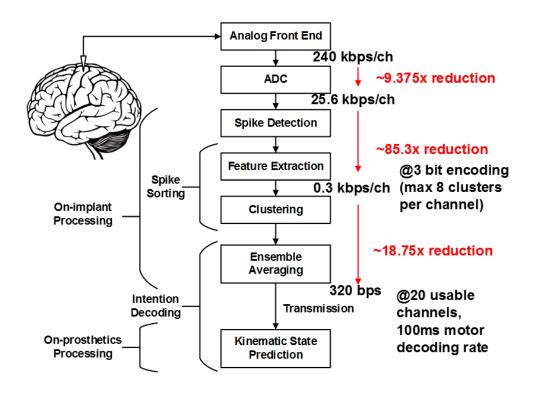

Figure 3.1 shows the processing stages of the targeted extracellular spike BCI system. The first stage is an implanted electrode array. The electrode array senses extracellular potentials, which originate from surrounding neurons. The signals are then filtered with band-pass or low-pass filters. Following the filtering stage, analog-to-digital converters (ADC) digitize the extracellular voltage signals and produce multi-channel digital data streams for later stages of the BCI system. The NSP initiates after the ADC stage of the BCI and terminates before the transmission of partially decoded neural data off chip.

Figure 3.1: Proposed prosthetic BCI task flow.

The motor intention-decoding task is delegated to both on-chip hardware processing at the implant site (NSP) and off-chip software processing at the prosthesis site. The on-implant computation includes spike detection, spike sorting (which includes feature extraction and clustering), and partial computation of intention decoding which estimate the movement state via ensemble-regressed spiking events. The near-prosthesis computation concludes the rest of intention decoding, notably the Kalman filter (KF) operation, which finalize the kinematic state prediction.

The main physical constraints of an implantable BCI device is power efficiency. The temperature sensitivity of the implant site tissues can render the targeted neurons useless when exposed to high power implant. Among the tasks performed by the implant, data transmission from implant to prosthesis is the dominate power consumer for existing BCI implants [8]. Hence, our NSP design is driven by the objective of achieving the highest data rate reduction while performing the minimum amount of computation on implant.

Based on the prior works [19, 20, 24], we optimize and improve the algorithms for spike sorting and intention decoding to reduce the on-chip computational complexity while improving

the decoding accuracy as compared to the unmodified algorithms. Consider a typical 96-electrode array sensing at 8-bit resolution at 30 kHz for prosthetic BCI, the data rate is nearly 3MB/s without any on-implant processing (Figure 3.1). If the full data streams are transmitted off-chip entirely, the required power would make the system unsuitable for long term deployment. Therefore, we implement spike detection, feature extraction, sorting, and the first part of decoding on the implant device. With the on-implant processing capability, we can reduce the wireless data rate by more than four orders of magnitude.