# NANOSCALE ELECTRONIC DEVICES BASED ON THE HYBRID STACKS OF TWO-DIMENSIONAL MATERIALS AND FERROELECTRIC METAL OXIDES

ΒY

# JIALUN LIU

## DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering in the Graduate College of the University of Illinois at Urbana-Champaign, 2020

Urbana, Illinois

Doctoral Committee:

Professor Joseph W. Lyding, Chair Assistant Professor Wenjuan Zhu, Director of Research Professor Xiuling Li Associate Professor Qing Cao

#### Abstract

Further scaling of complementary metal-oxide-semiconductor (CMOS) dimensions will soon lead to a tremendous rise in power consumption while limited gain in the performance of integrated circuits. "Beyond-CMOS" devices, based on two-dimensional (2D) materials, can potentially overcome these limitations and further improve the performance, reduce energy consumption, and add novel functionalities to the CMOS platform. In this Ph.D. dissertation, we investigated energy efficient electronic devices based on a new hybrid material platform consisting of two-dimensional materials and ferroelectric metal oxides. The ferroelectric metal oxides provide programmable and non-volatile doping in the 2D materials, while the atomically thin body in 2D materials enables strong electrostatic control over the channel by the polarized ferroelectric metal oxides.

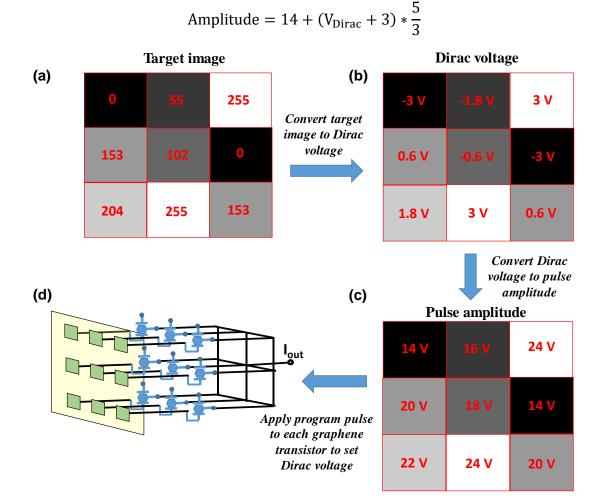

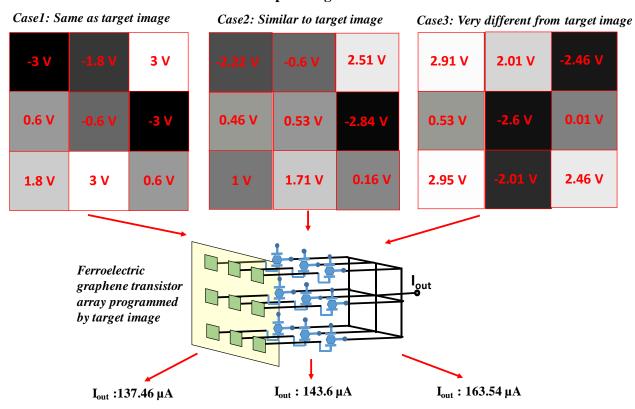

We design and demonstrate a new type of classifier using ferroelectric graphene transistors, which can perform the "comparison" function in the analog domain instead of the traditional digital domain. This new type of classifier utilizes the ambipolar transport and zero bandgap of the graphene to perform the absolute difference function, |A-B|, directly. Unlike the image classifier based on silicon CMOS, the classifier based on ferroelectric graphene transistors only needs ONE transistor per pixel, which will significantly reduce chip area and energy consumption. More importantly, the embedded ferroelectric layer in the graphene transistor enables the non-volatile storage of the target image inside the analog device. Therefore, a single graphene transistor can perform both image storage and comparison functions concurrently. This in-memory computing will eliminate the need for frequent image loading/unloading, which will further reduce the power consumption related to the data transfer.

ii

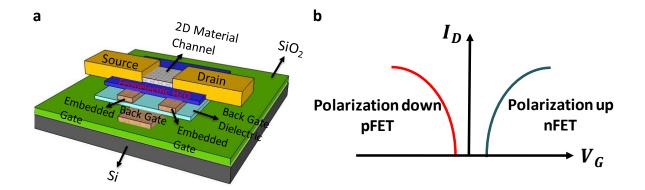

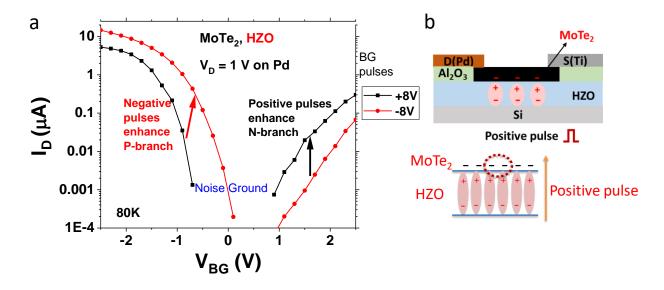

We also explored non-volatile reconfigurable devices based on the hybrid stacks of ferroelectric materials and 2D materials. In traditional silicon CMOS, once the device is fabricated, its function is fixed as either an n-type or a p-type transistor. In this work, we show that functionality of this new type of device can be dynamically reconfigured during operation and the reconfiguration is non-volatile and reprogrammable. We have successfully demonstrated the electrostatic controlled reconfigurable devices based on black phosphorus and non-volatile reconfigurable devices based on molybdenum telluride and ferroelectric hafnium zirconium oxides. These reconfigurable devices will enable the logic circuits to evolve their functions on-demand. The 3D monolithic integration of these reconfigurable devices/circuits and memory blocks will enable in-memory computing and reduce the energy consumption and latency related to the transportation of "Big Data".

This work will open a new path toward the design of novel nano-function circuits based on unique material properties that are absent in traditional circuits based on CMOS logic transistors and Von Neumann architectures. These new devices will also enable a new computing paradigm, where the process latency and energy consumption will no longer be limited by the memory bottleneck.

iii

# Acknowledgments

Firstly, I would like to deliver my most sincere gratitude to my graduate research adviser, Prof. Wenjuan Zhu, for letting me join her research group to pursue my Ph.D. degree. Her tireless guidance and encouragement have undoubtedly been the greatest support to my academic life in the University of Illinois. I would like to express my appreciation to my teammates, Dr. Kai Xu and Hojoon Ryu, for their kind and constructive suggestions during my projects. I also appreciate the help from my doctoral committee, for their suggestions and approval for my research progress throughout the preliminary exam and final defense. I would also like to thank the ECE Department advising and editorial service staff for their professional advice and service during my completion of this work. Finally, thanks to my family, my love, and my friends for their care and support.

We would like to acknowledge the support from the National Science Foundation (NSF) under Grants ECCS 16-11279 and ECCS 16-53241 CAR, from the Office of Naval Research (ONR) under grant NAVY N00014-17-1-2973.

# **Table of Contents**

| Chapter 1 Introduction                                              | 1  |

|---------------------------------------------------------------------|----|

| 1.1 2D Materials                                                    | 2  |

| 1.1.1 Graphene                                                      | 4  |

| 1.1.2 2D Transition Metal Dichalcogenides                           | 6  |

| 1.1.3 Black Phosphorus                                              |    |

| 1.1.4 Hexagonal Boron Nitride                                       |    |

| 1.2 Ferroelectric Materials                                         |    |

| 1.2.1 Polarization in Ferroelectric Materials                       |    |

| 1.2.2 PUND Measurement                                              |    |

| 1.2.3 Ferroelectric Memory                                          |    |

| 1.2.4 2D Material Electronic Devices with Ferroelectric Dielectrics |    |

| Chapter 2 Experimental Details                                      | 29 |

| 2.1 Exfoliation and Mechanical Transfer                             |    |

| 2.2 CVD Graphene and Wet Transfer                                   |    |

| 2.3 Identifying the Transferred 2D Materials                        |    |

| 2.4 Device Fabrication                                              |    |

| Chapter 3 Electrical Characterization of 2D Materials               |    |

| 3.1 Characterization of the Bandgap of Black Phosphorus             |    |

| 3.1.1 Experiments                                                   |    |

| 3.1.2 Results and Discussion                                        |    |

| 3.1.3 Summary                                                       |    |

| 3.2 Characterization of the Interface States in Black Phosphorus    |    |

| 3.2.1 Experiments                                                   |    |

| 3.2.2 Results and Discussion                                        |    |

| 3.2.3 Summary                                                       |    |

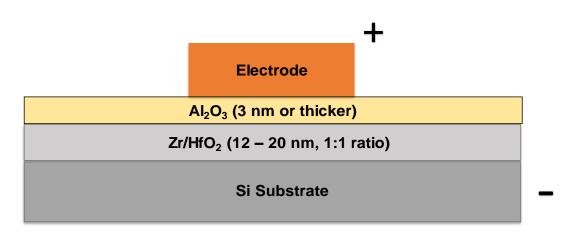

| Chapter 4 Ferroelectric Hafnium Zirconium Oxide                     | 60 |

| 4.1 Background of Ferroelectric Hafnium Oxide                       |    |

| 4.2 Synthesis of Ferroelectric Hafnium Zirconium Oxide              |    |

| 4.3 Remanent Polarization of Ferroelectric Hafnium Zirconium Oxide                          | 62   |

|---------------------------------------------------------------------------------------------|------|

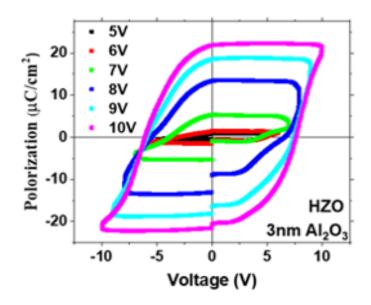

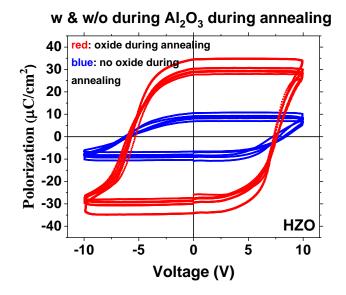

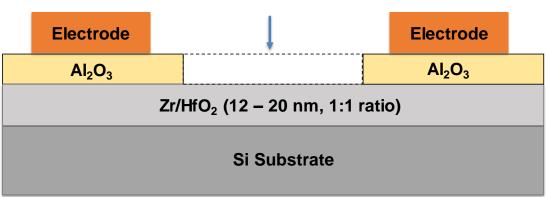

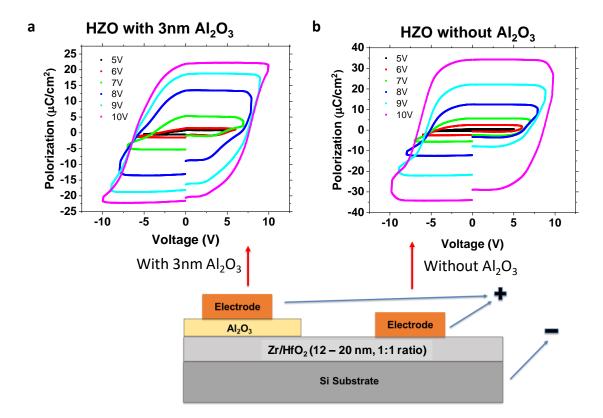

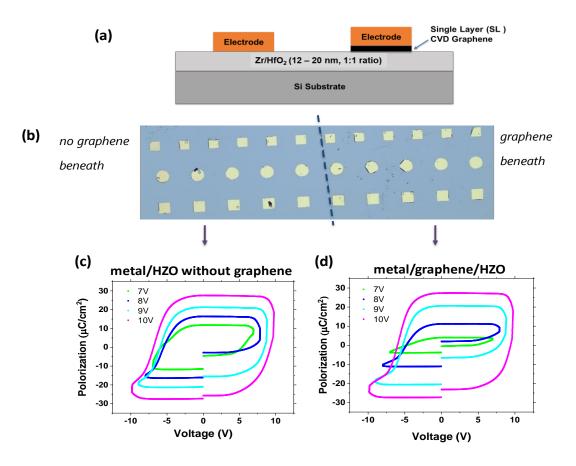

| 4.3.1 Influence of the Capping Layer on the Ferroelectricity of Hafnium Zirconium Oxide     | 63   |

| 4.3.2 Influence of 2D Material between HZO Layer and Electrode                              | 66   |

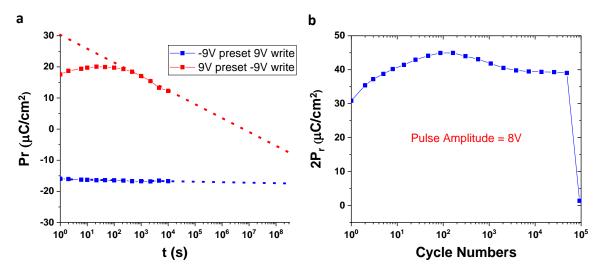

| 4.4 Retention and Endurance of Ferroelectric Hafnium Zirconium Oxides                       | 67   |

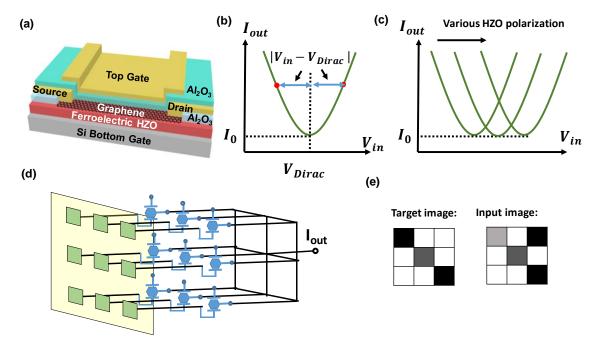

| Chapter 5 Non-Conventional Analog Classifiers Based on Ferroelectric Grapher<br>Transistors |      |

| 5.1 Motivation and Background                                                               | 69   |

| 5.2 Device Design and Operating Principle                                                   | 70   |

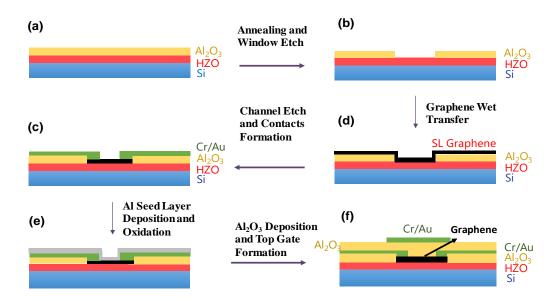

| 5.3 Device Fabrication and Methods                                                          | 71   |

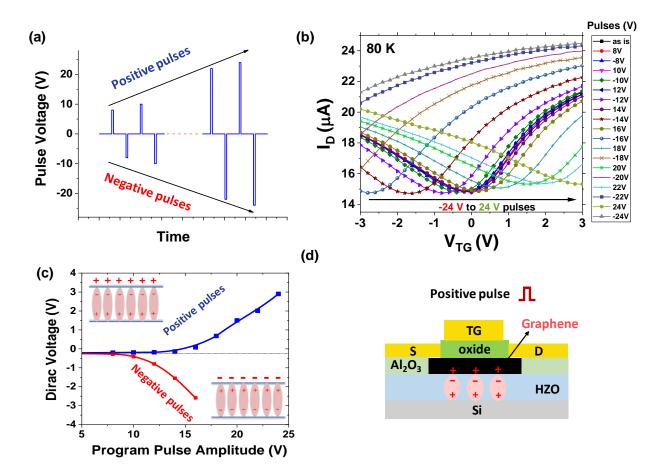

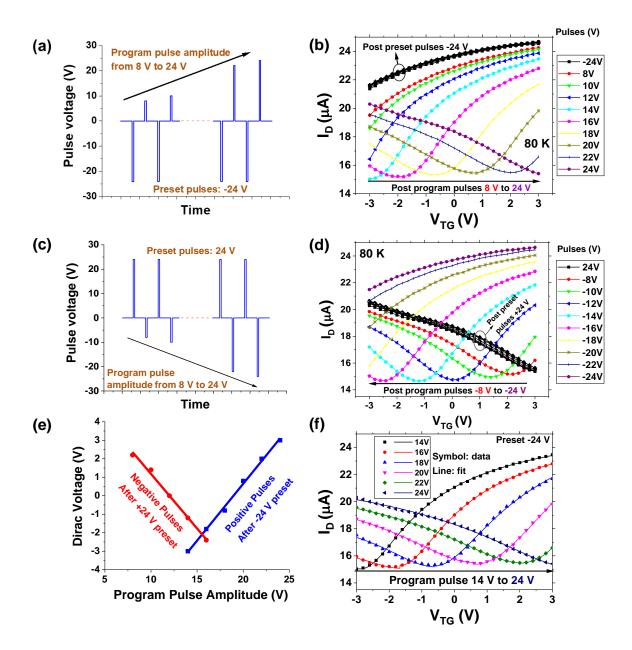

| 5.4 Tunable Polarization and Dirac Voltage in Ferroelectric Graphene FETs                   | 73   |

| 5.5 Image Comparison Based on Graphene Classifier                                           | 78   |

| 5.6 Future Directions for Improvements                                                      | 81   |

| 5.7 Summary                                                                                 | 82   |

| Chapter 6 Reconfigurable Logic Devices Based on Ferroelectric and 2D Materia                | ls84 |

| 6.1 Motivation                                                                              | 84   |

| 6.2 Background                                                                              | 85   |

| 6.3 Device Structure and Operating Principle                                                | 87   |

| 6.4 Device Fabrication                                                                      | 88   |

| 6.5 Results and Analysis                                                                    | 89   |

| Chapter 7. Conclusion and Future Work                                                       | 94   |

| 7.1 Conclusion                                                                              | 94   |

| 7.2 Future Work                                                                             | 96   |

| References                                                                                  | 97   |

# **Chapter 1** Introduction

The art of field-effect semiconductor devices is to use the electric field as a "switch" to control the current's on/off state. Following Moore's law [1], since the 1960s the semiconductor industry has been scaling down semiconductor devices and lowering their cost while improving the electrical performance and increasing the integrated circuit (IC) density. Various structural/material innovations (SOI, FINFET, high-K gate dielectrics, strained silicon, etc.) and lithography techniques (DUV/EUV, immersion lithography, double patterning, etc.) have been invented and they successfully maintain this trend of scaling down semiconductors. From 1971 to 2014, the typical semiconductor manufacturing process was driven from 10µm to 14nm node for metal-oxide-semiconductor field-effect transistors (MOSFETs) [2], the building blocks for most of today's consumer electronics. Nevertheless, a further device miniaturization/speed-up is exceptionally challenging given nanoscale physical limitations and high development cost. Specifically, shrunken channel length with higher doping undermines the control of the top gate of the channel over the source/drain [3]. Typically these short-channel effects (SCEs) lead to drain-induced barrier lowering (DIBL), carrier surface scattering, hot electron effects and other undesired sideeffects [4]. Electron mobility in silicon, severely degraded by surface roughness, is also inevitably affected by heavy doping in short-channel cases. Innovations in materials and structures are required to extend Moore's law, as many have suggested. Further scaling of complementary metal-oxide-semiconductor (CMOS) dimensions will soon lead to a tremendous rise in power consumption while limited gain in the performance of integrated circuits. "Beyond-CMOS" devices, based on nanowires, nanorods, and two-dimensional (2D)

materials, can potentially overcome these limitations and further improve the performance, reduce energy consumption, and add novel functionalities to the CMOS platform. In this project, we investigated energy efficient electronic devices based on a new hybrid material platform consisting of 2D materials and ferroelectric metal oxides. The ferroelectric metal oxides provide programmable and non-volatile doping in the 2D materials, while the atomically thin body in 2D materials enables strong electrostatic control over the channel by the polarized ferroelectric metal oxides. In this chapter, we will review the background in 2D and ferroelectric metal oxides.

#### **1.1 2D Materials**

2D materials are layered materials with strong covalent bonds in the layer while weak van der Waals bonds in between layers. There are several hundreds of 2D materials, which have been predicted or experimentally demonstrated. Among those 2D materials, graphene, transitional dichalcogenides, and black phosphorus are the most intensely studied materials. Graphene has exceptionally high mobility (~ 200,000 cm<sup>2</sup>/ (V·s) [5], but zero bandgap, which makes it difficult to be used in logic devices. Graphene based radio frequency (RF) devices have very high cut-off frequencies (up to 427 GHz) [6], but limited power gain, again due to the lack of a bandgap. After graphene as an atomic layer was discovered, transistors made from it showed extraordinary mobility among other merits [7]. Although graphene's zero semi-metallic behavior brings about low switchability for transistors, this group of materials is recognized as important for potential applications in novel devices. For this reason, graphene and other 2D materials developed later with similar structure have aroused interest. In addition to digital logic devices, 2D materials with a high surface-to-bulk ratio are naturally ideal for sensors with high sensitivity (e.g. biomedical sensors, piezoelectric sensors). Their sheet-like property suggests their suitability in flexible electronic applications beyond organic flexible electronics [8]. 2D materials are a relatively new and rapidly growing field of study, with new material findings and device breakthroughs emerging rapidly. Still, issues like large-scale production and doping remain challenging in the exploration.

Beyond graphene, transition metal dichalcogenides (TMDs) are another type of 2D material. TMDs have a general formula of MX<sub>2</sub>, where M is a transition metal atom (such as Ti, Zr, Hf, V, Nb, Ta, Re, etc.) and X is a chalcogen atom (such as S, Se, Te). There are over 30 different TMDs with diverse properties, ranging from semiconductors (MoS<sub>2</sub>, WSe<sub>2</sub>) to semimetals (1T' phase WTe<sub>2</sub> and TiSe<sub>2</sub>), metals (VSe<sub>2</sub>, NbS<sub>2</sub>), and superconductors (PbTe<sub>2</sub>, NbSe<sub>2</sub>) [9-24]. Among various TMDs, MoTe<sub>2</sub> is a promising material with small bandgap (0.88 eV in bulk, 1.02 eV in monolayer). This small bandgap makes it possible to fabricate ambipolar transistors and reconfigurable logic devices. In addition to MoTe<sub>2</sub>, black phosphorus is also a promising material for reconfigurable device due to its small bandgap (~ 0.3 eV in bulk).

For our main research focus in electronic devices, several kinds of 2D materials of interest are briefly reviewed in this section.

3

#### 1.1.1 Graphene

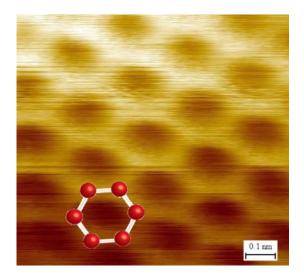

Graphene was the very first two-dimensional atomic crystal discovered [7] and its 2D structure gives it properties very different from those of other allotropes of carbon (graphite, Fullerene, carbon nanotube, etc.) [25]. A scanning tunneling microscope (STM) image for graphene atomic structure is shown in Fig. 1-1 [26]. Its advantages include superior mechanical strength, high electronic and thermal conductivity, and impermeability to gases, which attracts a lot of attention for potential applications. Since researchers successfully exfoliated single-layer graphene from its bulk counterpart (graphite) with its main contributor winning the Nobel Prize later in 2010, its enticing electrical properties have encouraged extensive research into making electronic devices beyond the current complementary metal oxide semiconductor (CMOS) technology. Graphene, a semi-metallic carbon layer with one atom thickness, has superior carrier density and mobility ~ 10,000 cm<sup>2</sup>/(V·s) and therefore is promising for lower energy dissipation and faster operating speed in electronics. Unfortunately, besides large-scale growth issues, the inherent gapless nature

Figure 1-1. Graphene's honeycomb structure shown in STM topographic image.

in graphene restricts the energy states variety and brings about great challenges for people to switch graphene on/off for digital device applications [8]. Cutting graphene into nanoribbons or depositing graphene onto certain substrates is done to show the structure change, hence non-zero bandgap, in graphene. But these changes are overall insignificant and damage graphene's appealing carrier transport properties, or turn out to need further investigation [27-30].

Despite this drawback for digital applications, graphene shows exciting prospects for conductive coating for flexible electronics due to its transparency, flexibility, low sheet resistance and high transmittance, provided contact resistance issues can be appropriately addressed. In addition, graphene-based transistors have proved promising for RF devices with high cut-off frequencies [31]. On the other hand, graphene's transparency in one or a few layers and its wavelength-independent absorption rate in a large range of light spectra make it a suitable candidate for a number of photonic devices. These include photodetectors, various kinds of laser devices, and optical modulators [8].

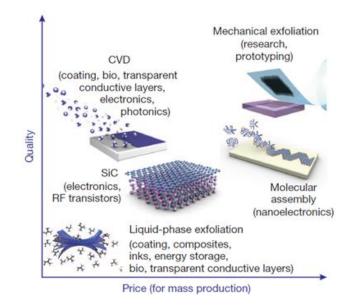

As an important factor to be considered for industrial products incorporation, production methods (Fig. 1-2 [8]) for large-scale and uniform graphene are great challenges in current development. For research purposes, mechanical exfoliation from bulk graphite is used frequently for graphene and other 2D materials for its convenience and high-quality flakes. An alternative common way to yield graphene is to grow it on copper or nickel with a mixture of methane and hydrogen at as high as 1000 °C [32, 33]. Another method includes precipitation of graphene layer on SiC wafer but is very costly [34].

5

Figure 1-2. Different methods for mass synthesis/production of graphene.

# 1.1.2 2D Transition Metal Dichalcogenides

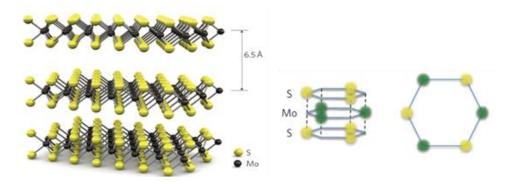

Two-dimensional transition metal dichalcogenides (TMDC) have chemical formula MX<sub>2</sub> with transition element M and chalcogen X [35]. Among this group of materials MoS<sub>2</sub>, WS<sub>2</sub>, and WSe<sub>2</sub> have been studied in recent years for their high quality and stability in the isolation process. Like graphene, these materials can be readily exfoliated into one or a few layers by breaking the interlayer weak van der Waals force without damaging intralayer covalent bonds (mechanical cleavage), or they can be grown by chemical vaporization deposition (CVD). As a representative example, a large area of atomic layer MoS<sub>2</sub> is often synthesized on a silicon wafer by CVD using MoO<sub>3</sub> and S powder with the help of PTAS as seeding material for nucleation. Figure 1-3 [36, 37] demonstrates the structure of MoS<sub>2</sub> layers.

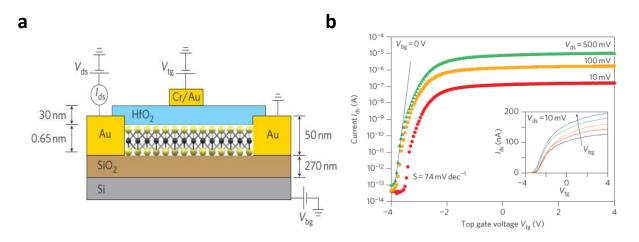

As the thickness decreases to a single layer, the band structure of TMDCs is changed by quantum confinement effects. A transition from indirect bandgap (1.2 eV) at  $\Gamma$  point to direct bandgap (1.9 eV) at K-point in the Brillouin zone is predicted and confirmed for MoS<sub>2</sub>. This suggests its appealing properties in possible logic devices and optoelectronics. A topgated single-layer MoS<sub>2</sub> FET was successfully fabricated in 2011 by Radisavljevic et al. [37] with appreciable mobility (~ 70 cm<sup>2</sup>/(V·s)), large on/off current ratio (~ 10<sup>8</sup>) and satisfactory subthreshold swing (~ 74 mV/decade) at room temperature (Fig. 1-4 [37]).

Figure 1-3. Honeycomb MoS<sub>2</sub> structures with alternating Mo and S atoms.

Figure 1-4. A single-layer MoS<sub>2</sub> top-gated FET. (a) Device structure. (b) I-V characteristics.

Despite the inherent p or n type body by impurity charges, progress toward doping the TMDCs in a controllable way was made by several groups utilizing chemical treatment during/after crystal growth, for electronics fabrication with reliability and repeatability [38].

The various bandgap range of the TMDC family and its layer structure free of surface dangling bonds also provide exciting possibilities for applications based on epitaxy and heterostructure/junctions. The various direct bandgap values and tunable features with layer numbers in visible light range also make TMDC optoelectronics attractive [39]. A phototransistor was made by single-layer (SL) MoS<sub>2</sub> to show its potential as a photodetector with photo responsivity of 880 A/W at 561 nm wavelength light [40]. Finally, due to TMDC's M-X composition, the piezoelectric effect was examined in SL MoS<sub>2</sub> thin films, with the finding that no net piezoelectric effect is present within even number of layers or bulk counterparts due to the opposite orientation of alternating layers [41].

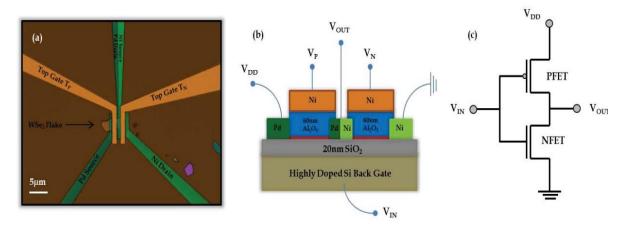

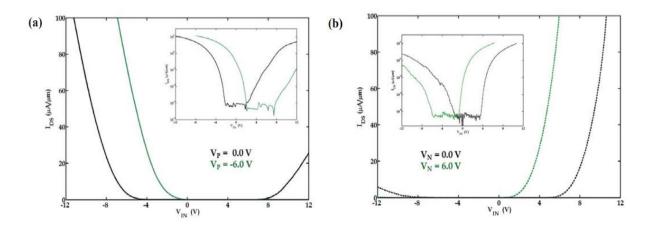

Within MoS<sub>2</sub>, a strong Fermi-level pinning effect is present, and it mostly demonstrates n-type unipolar characteristics around the conduction band [42, 43]. Tungsten diselenide (WSe<sub>2</sub>), with two layers of Se atoms sandwiching a single layer of W atoms is another addition to the TMDC family studied in these years. Unlike MoS<sub>2</sub>, WSe<sub>2</sub> could exhibit ambipolar carrier conduction from the effective Fermi level tuning relative to conduction and valence band edge [44-46]. A technique to facilitate the ambipolar transport is to utilize the contact metal engineering, where the source and drain of the FET device are deposited with different metals, each aligned closer to either conduction or valence band and favored for one of the carriers. An example ambipolar WSe<sub>2</sub> device with different contact electrodes is made by S. Das and J. Appenzeller (Fig. 1-5 and Fig. 1-6 [47]).

8

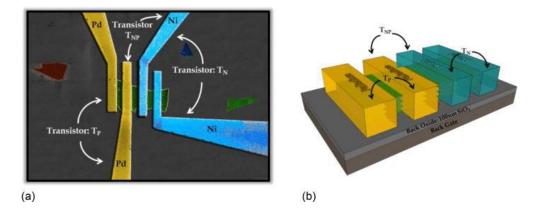

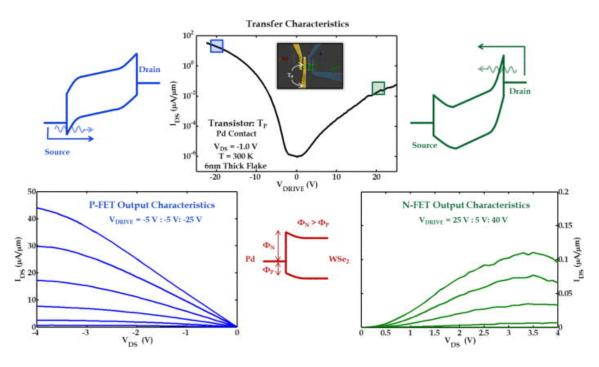

Figure 1-5. (a) SEM and (b) 3D structure of multilayer WSe<sub>2</sub> hetero-contact transistors.  $T_N$ :Ni is used for both the source and the drain contact electrode;  $T_P$ :Pd is used for both the source and the drain contact electrode; and  $T_{NP}$ :Ni is used as the source, and Pd is used as the drain contact electrode.

Figure 1-6. Transfer and output characteristics of the transistor  $T_P$  and the associated energy band diagram for the electron (green) and the hole (blue) injection. The energy band diagram in red shows the relative Schottky barrier heights for the electron and the hole injection from Pd contact to WSe<sub>2</sub>.

Another TMDC, molybdenum ditelluride (MoTe<sub>2</sub>), has a direct bandgap at  $\sim 1.1$  eV at the single-layer limit, smaller than the corresponding value  $\sim 1.6$  eV of WSe<sub>2</sub> [48, 49]. This suggests a potential higher barriers to suppress carrier injection in WSe<sub>2</sub> [50] and a

facilitated ambipolar transport in MoTe<sub>2</sub> [51]. Without the impeding fermi-level pinning effect, these two materials have adjustable barrier heights for n or p carriers depending on flake thickness, contact metal and other factors.

# **1.1.3 Black Phosphorus**

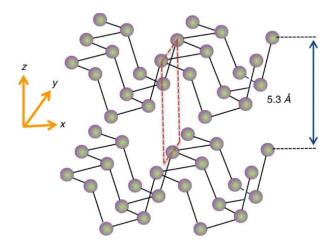

Compared to its allotropes (yellow/red/fibrous phosphorus), black phosphorus is most dense and least reactive due to its interlinked six-membered ring. This unique puckered hexagonal structure (Fig. 1-7 [52]) leads to anisotropic in-plane electrical and optical properties, which may offer special benefits in novel fields such as plasmonic devices [52]. Bulk black phosphorus has a direct bandgap around 0.3 eV, while single-layer black phosphorus is predicted to have a much larger bandgap from 1 eV to 2 eV, depending on the theory model. This large variation indicates black phosphorus might be an ideal candidate for purposes requiring tunable bandgap. Another notable point is this bandgap range corresponds to the infrared range in the optical spectrum. Combined with other 2D materials' optical range from the bandgap, heterostructures could be made for optoelectronics like high-efficiency solar cells. Black phosphorus used in devices is usually exfoliated from bulk crystal which could be made from red phosphorus under high temperature and/or high pressure although some innovative methods (including CVD) also exist [53-55].

Figure 1-7. Puckered sheets of linked phosphorus atoms. Layer-to-layer space is  $\sim$  0.5nm.

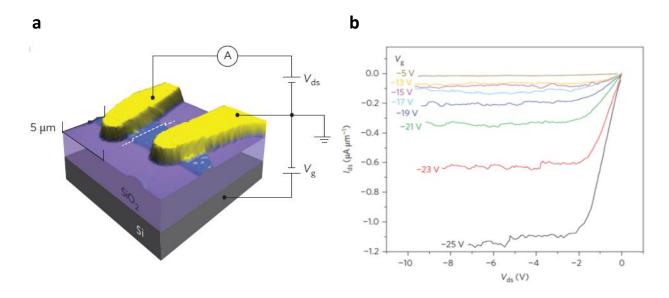

Back-gated FETs were fabricated by several independent groups [52, 56, 57]. In Figure 1-8 [57], experimental data from the Zhang group shows that a p-type FET device with 5nm thick BP channel is fabricated with ~ 200 cm<sup>2</sup>/(V·*s*) mobility with good on/off ratio at  $10^{5}$ . As a comparison, the data here suggests the black phosphorus FET has higher

Figure 1-8. (a) A BP back gated transistor. (b) I<sub>d</sub>-V<sub>d</sub> curves under different gate bias.

mobility than that of a typical TMDC transistor while having a moderate (lower) on/off ratio.

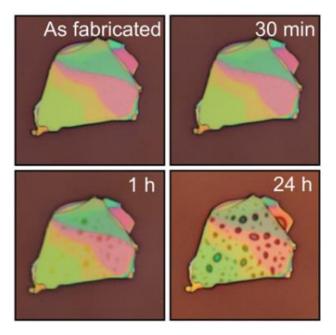

However, instability might be an issue for making black phosphorus thin film devices since a few layers of black phosphorus gradually react with water and oxygen (Fig. 1-9 [58]). Some recent experiments have assessed its surface reaction with the ambient environment and further work is expected to reveal this unstable nature of the material [59].

Figure 1-9. Optical images for mechanically exfoliated black phosphorus as time elapses.

# **1.1.4 Hexagonal Boron Nitride**

Hexagonal boron nitride (hBN) is a III-V compound insulator with a wide indirect bandgap around 6 eV [60]. It has a similar honeycomb structure to graphene except it is composed of alternating boron and nitrogen atoms. The hBN also has good mechanical strength and thermal/chemical stability. More importantly, it is experimentally suggested that graphene and other 2D semiconductors demonstrate remarkable mobility with hBN compared to other dielectrics due to their flat and low-impurity surfaces [61]. For these reasons, hBN is widely used as dielectric material or physical protection coating in 2D material transistors and heterostructures [62-65].

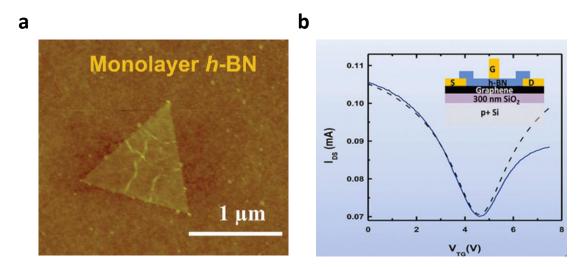

The first CVD growth of monolayer hBN was developed by Kong's group in 2012, using ammonia borane as precursor under LPCVD on copper foil [66]. Other CVD growth methods for hBN also exist using precursors such as borazine [67]. Figure 1-10 consists of an AFM image of hBN [62] and a graphene-hBN transistor device demonstration [63].

Figure 1-10. (a) CVD-grown hBN under AFM scanning. (b) Graphene transistor structure and transfer characteristics with hBN as top gate dielectric.

## **1.2 Ferroelectric Materials**

## **1.2.1 Polarization in Ferroelectric Materials**

As an important feature of ferroelectric material, the spontaneous polarization in ferroelectric (FE) material is a non-volatile property. The polarization value could be used to represent different states in the layer and the distributed charge could electrically interact

with the nearby material. In this section, a brief explanation for the origin of ferroelectricity is presented.

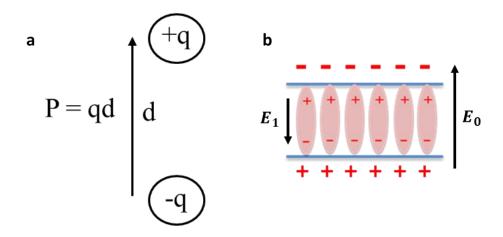

Material's electrical polarity is reflected by the separation of the positive and negative charges within, called electrical dipole moment. A pair of positive and negative charge (+q and -q) separated by distance d has polarization pointing from negative charge to positive charge with amplitude P = qd (Fig. 1-11a). Polarization introduces an electric field. For a capacitor with dielectric between two metal plates, if external electric field  $E_0$  is applied between the two plates, uniform polarization P =  $\chi \epsilon_0 E$  would be induced, where  $\chi$  is the material's dielectric susceptibility. Within the dielectric, depolarization field  $E_1$  is generated against the external field due to the induced polarization (Fig. 1-11b). The polarizability of material could be attributed to different factors: electronic polarization (displacements between ions), dipolar polarization (change of molecules with permanent dipole moment in electric field), and interfacial polarization (accumulation of charge at interface between materials or regions) [68-70].

Figure 1-11. (a) Demonstration of electric polarization's magnitude and direction. (b) Polarization induced in capacitor.

Ferroelectric materials are characterized as materials which exhibit robust and reversible spontaneous electrical polarization. The word "spontaneous" may mean that the polarization has a nonzero value in the absence of an applied electric field [68], which distinguish it from normal dielectric material. Ferroelectricity is a subset of pyroelectricity which describes spontaneous dielectric polarization from change of temperature [71]. If the dielectric material in external electrical field is normal dielectric, polarization within will disappear upon removal of the external field. However, if the dielectric is ferroelectric, partial polarization would remain even after the removal of external field if the field was large enough to orient the domains within it, and its amplitude and direction could depend both current external field and its previous state. Figure 1-12 exhibits a P – E diagram with double sweep of external electric field, which would indicate hysteresis if the dielectric material is ferroelectric, while a simple linear relationship is found if the dielectric material is non-ferroelectric.

Figure 1-12. P-E diagram for (a) normal and (b) ferroelectric material with direction of hysteresis labeled.

Ferroelectric materials have three important metrics, which are discussed as follows [68, 72]:

1. Remanent polarization (P<sub>r</sub>): As we introduced, the polarization's direction and amplitude within ferroelectric material domains could be switched or changed by the external field. When the external field drops to zero, ferroelectric material remains polarized and this remaining polarization is called remanent polarization (P<sub>r</sub>) [73]. Remanent polarization depends on the polarization states prior to external field application, and the applied external field's shape, amplitude, width, etc. A field with an amplitude higher than coercive field is required to "flip" and switch part or all of the domains' polarization in ferroelectric material. An external field lower than coercive voltage would not change the remanent polarization since only field-induced polarization is present and it disappears after field removal (like in normal dielectric layer).

2. Retention: The dipoles within ferroelectric layer tends to relax and depolarize as time elapses and remanent polarization decreases. Retention describes the ability of ferroelectric layer to retain the sign and magnitude of remanent polarization after writing with external field [74]. Retention time describes the duration a ferroelectric layer could maintain its remanent polarization until it drops to zero. The retention of a ferroelectric layer in a capacitor structure not only depends on the composition of the ferroelectric material and working environment (e.g. temperature), but also on the adjacent materials.

3. Endurance: For storage purposes, a ferroelectric layer needs to be written into different states (represented by the direction and amount of polarization). After repetitive writing pulses, ferroelectric material is subject to potential "fatigue effect" (a lowered remanent polarization after repetitive writing pulses) and may even break down, losing its ferroelectric properties. Endurance measures the number of cycles of consecutive opposite writing with pulses above coercive voltage that the ferroelectric layer could sustain before breaking down.

Ferroelectric materials were discovered in 1920 in the form of bulk single crystals of Rochelle salt. Traditional oxide ferroelectric materials include NH<sub>4</sub>H<sub>2</sub>PO<sub>4</sub> (ADP), KH<sub>2</sub>PO<sub>4</sub> (KDP), LiNbO<sub>3</sub> (LN), LiTaO<sub>3</sub> (LT), BaTiO<sub>3</sub> (BT), PbTiO<sub>3</sub> (PT), Pb (Zr,Ti) O<sub>3</sub> (PZT), (Pb,La)TiO<sub>3</sub> (PLT), SrBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub> (SBT) and (Pb,La)(Zr,Ti)O<sub>3</sub> (PLZT)), etc., developed in the form of bulk single-crystal and bulk polycrystalline ceramics. Various techniques (MBE, PVD, CVD) could be used for ferroelectric thin film deposition [75]. In addition to complex oxides, ferroelectric materials are also found in other material classes, like polymer (Polyvinylidene fluoride, or PVDF) and 2D materials (CuInP<sub>2</sub>S<sub>6</sub> and In<sub>2</sub>Se<sub>3</sub>). Ferroelectric materials usually only demonstrated their ferroelectric properties below certain temperature (Curie temperature) [68]. Nowadays, traditional ferroelectric materials mainly refer to complex perovskites, such as lead zirconate titanate (PZT), strontium bismuth tantalate (SBT), and lead magnesium niobate-lead titanate (PMN-PT). They have been widely used in ferroelectric devices [76, 77]. However, these traditional ferroelectric materials have a limitation in thickness scaling and are not compatible with CMOS processes. In the last few years, doped metal oxides, including hafnium oxide ( $HfO_2$ ) and zirconium oxide ( $ZrO_2$ ), were found to have ferroelectric phase [78-84]. Ferroelectric HfO<sub>2</sub> has the advantages of a high coercive field, excellent scalability (down to 2.5nm), and good compatibility with CMOS processing [84-87].

#### **1.2.2 PUND Measurement**

The polarization of the ferroelectric capacitors is commonly measured using the positive-up-negative-down (PUND) method. The capacitors are subjected to a series of five pulses consisting of a preset pulse, positive switching pulse, positive non-switching pulse, negative switching pulse and a negative non-switching pulse, illustrated in Fig. 1-13a. The preset pulse set the ferroelectric HfO<sub>2</sub> in negative spontaneous polarization  $-P_s$  state. The first positive pulse applied (P) will switch the polarization vector to  $+P_s$  state and the displacement current for this "switching" pulse will be [88]:

$$i_{s}(t) = \frac{\partial D}{\partial t} = \frac{\partial (\epsilon E + P)}{\partial t}$$

(1-1)

where P is the polarization due to the ferroelectric dipoles, E is the electric field, and  $\epsilon$  is the dielectric constant of the dielectric. Since the film already polarized positively +P<sub>s</sub>, applying the second positive pulse (U) will not switch the polarization, and displacement current for this "non-switching" pulse will be:

$$i_{ns}(t) = \frac{\partial(\epsilon E)}{\partial t}$$

(1-2)

The difference between the two currents will be given by:

$$\Delta i(t) = i_s(t) - i_{ns}(t) = \frac{\partial P(t)}{\partial t}$$

(1-3)

Then the positive polarization (+P<sub>r</sub>) can be extracted from P(t) =  $\int_0^t \Delta i(t) dt$  (Fig. 1-13 b [89]). Negative polarization (-P<sub>r</sub>) is measured with same logic from N and D pulses. An example pulse diagram and P – E diagram are shown below (Fig. 4-13c [74]), where +P<sub>r</sub> and -P<sub>r</sub> indicates positive and negative remanent polarization, respectively, P<sub>s</sub> refers to saturation polarization (when all the domains are polarized in one direction and no more

ferroelectric polarizarion could be added), and  $+E_c$  and  $-E_c$  means positive and negative coercive voltage.

Figure 1-13. (a) Pulse schematics during a PUND measurement. (b) The two polarization half-loops calculated from the integration of current and positive remanent polarization calculated from the difference. (c) An example P-E loop with the important parameters labeled.

# **1.2.3 Ferroelectric Memory**

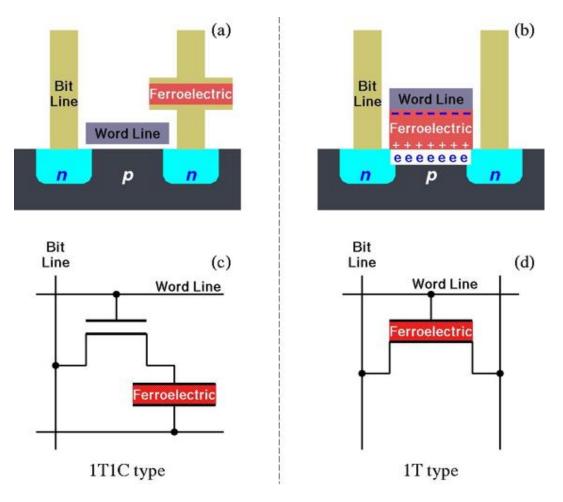

Ferroelectric material is widely studied for application in ferroelectric random-access memory (FRAM) based on polarization reversal with applied electric field across the ferroelectric thin film. The non-volatile ferroelectric film stores negative or positive remanent polarization even after field is revoked and therefore stores computational "0" and "1" states [72]. Two typical FRAM structures and their working principles are shown in Fig. 1-14 (taken with permission from website of program "feram" [90]).

In 1T1C (one-transistor-one-capacitor) FRAM (Fig. 1-14a), memory states are stored in the ferroelectric capacitor where ferroelectric layer's polarization orientation is written by electric field pulse across the plate. During reading, word line turns on the transistor and force the plate to reach the potential from the bit line. For example, in Fig. 1-14c, if the capacitor upper plate charge induced from ferroelectric polarization is positive, a brief current pulse could be sensed when the transistor turns on and force the plate to reach a low potential from bit line, hence a "1" state read from the capacitor. Since this read process overwrites the original state from capacitor when the current pulse is captured, the cell needs to be reprogramed after the reading.

1T (one-transistor) FRAM (Fig. 1-14b) structure is similar to conventional MOSFET except the dielectric layer is replace with a ferroelectric layer. During write operation, gate (word line) provides voltage pulse exceeding coercive voltage for the ferroelectric layer and program it into either an "up" or a "down" state depending on the remanent polarization orientation. The induced doping in channel therefore determined either the transistor would be on or off states with zero gate voltage. In this process, the read operation by sensing current in the channel is non-destructive and no reprogramming is required, while its main disadvantage is that the achievable retention time in current devices is very limited [91].

20

Figure 1-14. (a) FRAM with 1T1C structure. (b) FRAM with 1T structure. (c) Circuit diagram for 1T1C FRAM. (d) Circuit diagram for 1T FRAM.

#### **1.2.4 2D Material Electronic Devices with Ferroelectric Dielectrics**

2D materials have been combined with ferroelectric materials to make electronic devices in recent years. The non-volatile ferroelectric polarization is utilized for doping the 2D materials through electrostatic force. The doping level is determined by the remanent polarization, which could be adjusted to different levels by programming pulse conditions.

Beaumer et al. studied the bidirectional interdependency between graphene doping level and ferroelectric polarization in their graphene/PbZr0.2Ti0.8O3 hybrid structure [92]. In

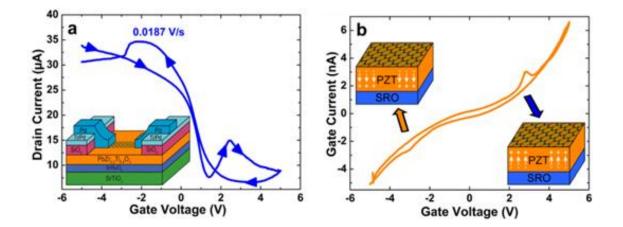

their work, single-layer CVD graphene was transferred onto laser deposition grown 140 nm PbZr<sub>0.2</sub>Ti<sub>0.8</sub>O<sub>3</sub> (FE layer)/60 nm SrRuO<sub>3</sub>/SrTiO<sub>3</sub> (bottom electrode) substrate and Pd contacts are used (Fig. 1-15a inset [92]). The control FE capacitor sample with graphene between top electrode and FE layer indicates a 2P<sub>r</sub> remanent polarization ~ 23  $\mu$ C/cm<sup>2</sup> with ~ 2.44 V coercive voltage and ~ 0.5 ms pulse duration.

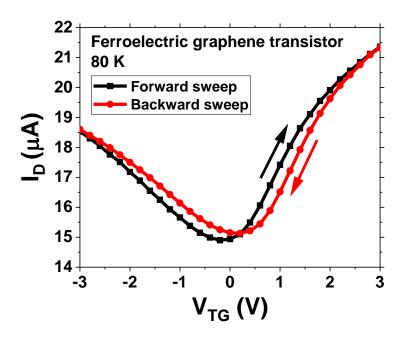

Due to the interfacial traps induced by  $H_2O$  or other absorbates between 2D material and dielectric interface, a clockwise hysteresis in  $I_d$ - $V_g$  double-sweep curve is usually observed due to the trapped charges at interface [93]. In ferroelectric FET, this phenomenon is competing with the signature counterclockwise hysteresis in the  $I_d$ - $V_g$  curve due to induced polarization switching if sweeping  $V_g$  exceeds coercive voltage of the ferroelectric layer. With a slow gate sweeping, the authors found an  $I_d$  drop deviating from traditional "Vshape" curve in non-ferroelectric graphene FET at around coercive voltage (Fig. 1-15a) and suggest it is due to the ferroelectric polarization switching, which is also observed in the gate

Figure 1-15. (a) Complex  $I_D-V_G$  characteristic for large gate voltages with a drain voltage of 50 mV and a gate voltage sweep rate of 0.0187 V/s. Inset: Schematic of a graphene transistor on PbZr0.2Ti0.8O3. (b) Gate current measured simultaneously to (a). Insets: Schematics of the ferroelectric polarization for different gate voltage regimes.

current peak at around same location (Fig. 1-15b). The Dirac point shift indicates an overall p-doping from gate-induced traps.

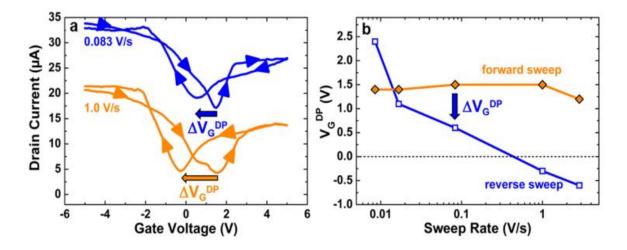

With increasing speed of gate sweeping, the influence from slow interfacial traps is reduced, a gradually diminishing p-doping is observed from the Dirac voltage shift until n-doping and a counterclockwise hysteresis loop is found, which could only be explained by ferroelectric polarization switching in PZT (Fig. 1-16 [92]).

Figure 1-16. (a) Complex  $I_D-V_G$  characteristics of another graphene/PZT transistor for two representative sweep rates as indicated and offset for clarity. (b) Sweep-rate dependent position of the current minima defined as the Dirac point voltage in the forward (orange, filled diamonds) and reverse sweep (blue, open squares). The dotted line represents zero gate voltage and separates the regimes of n- and p-doping.

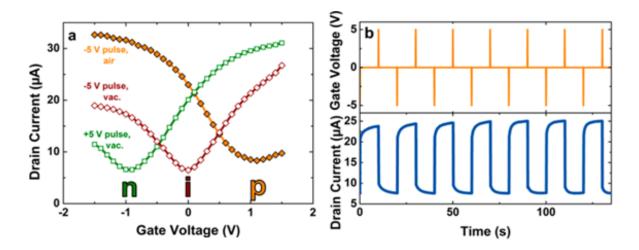

At last, the author demonstrated that, by managing the interfacial trap level (through high temperature annealing for hours) and ferroelectric polarization in the same device, their FE FET could demonstrate an I<sub>d</sub>-V<sub>g</sub> curve with different polarity through the channel carrier modulation, shown and explained in Fig. 1-17a [92]. In addition, with a constant drain voltage on and gate pulse schematics in Fig. 1-17b [92], the repetitive and consistent intrinsic/n-type device switching, and programming is realized, as a combined effect from ferroelectric layer polarization and reduced interfacial absorbates level.

Figure 1-17. (a) Small gate voltage sweeps not exceeding the coercive voltage measured after 1 ms gate voltage pulses. p-type, nearly intrinsic, and n-type behavior can be observed after a -5 V pulse in air (orange, filled diamonds), a -5 V pulse in vacuum (red, open diamonds), and a +5 V pulse in vacuum (green, open squares), respectively. (b) Multiple gate voltage pulses applied to a similar device in air (upper panel) and resulting reversible and reproducible switching between a highly p-doped state for the down-polarized state and a nearly intrinsic level for the up-polarized case.

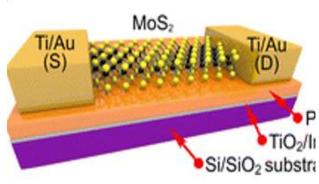

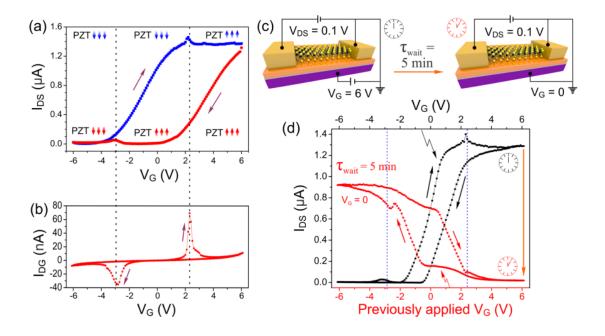

Another notable ferroelectric FET study is done by Lipatov et al. [94]. In their MoS<sub>2</sub>-PZT FET structure (Fig. 1-18 [94]), mechanically exfoliated few-layer MoS<sub>2</sub> was transferred with PMMA on to 100 nm polycrystalline (001) oriented tetragonal PbZt<sub>0.4</sub>Ti<sub>0.6</sub>O<sub>3</sub> grown by metal-organic chemical vapor deposition covered by conductive TiO<sub>2</sub>/Ir layer used as back gate. With a moderate bandgap channel material, their device shows large hysteresis of electronic transport with high on/off ratios, nondestructive data readout, low operation voltage, and wide memory window. Besides, their device exhibits possibility to write and erase the ferroelectric states both electrically and optically and therefor provides instant optical erase of large data arrays that is unavailable for many conventional memories.

Figure 1-18. MoS<sub>2</sub> – PZT FEFET structure.

From a direct I<sub>d</sub>-V<sub>g</sub> sweep at different speed, while the author confirmed I<sub>d</sub> and I<sub>g</sub> local peaks from ferroelectric polarization switching (Fig. 1-19a and b [94]), the clockwise hysteresis from interfacial trap in this work overcomes the counterclockwise hysteresis from ferroelectric polarization (Fig. 1-19a [94]). As a result, a set of current measurements for the device at zero gate voltage 5 mins after different gate pulse values (Fig. 1-19c [94]) from -6V to 6V is designed to eliminate the major influence from the trap charges after their dissipation. The result current after different level of gate pulses clearly indicates the different levels of current level and channel doping from polarization switching (Fig. 1-19d [94]). The hysteresis suggests a wide memory window for zero-gate current measurement. While this dissipation time limits the operation frequency between write/read in the memory and leads to unstable device performance depending on the trap charge dissipation, the authors obtained a long-term on/off ratio for zero-gate current around 22 and endurance ~ 500 cycles between 1ms +6V and -6V write/erase gate pulses.

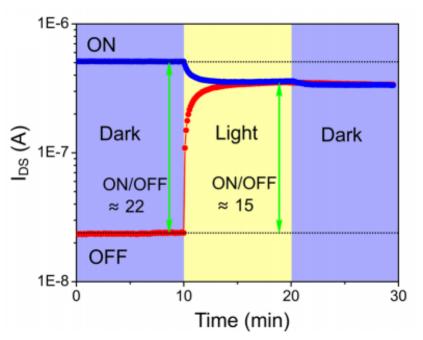

The moderate bandgap of MoS<sub>2</sub> enables a new approach to alter the polarization in ferroelectric layer due to its optoelectronic property. When the structure is illuminated with

Figure 1-19. Electronic properties of a MoS2-PZT FEFET with  $V_{DS} = 0.1 \text{ V}$ . (a)  $I_{DS}$ - $V_G$  characteristics. The arrows in the insets show the polarization directions of PZT at different VG, which were determined from PFM control sample measurements. (b)  $V_G$  dependence of the drain-gate (leakage) current ( $I_{DG}$ - $V_G$  measurements) for the same device. (c) Scheme of the electrical measurements revealing the polarization-dependent hysteresis of electronic transport in MoS2-PZT FEFETs (d)  $I_{DS}$ - $V_G$  characteristics for the same device measured using the method shown in (c). Black data points show  $I_{DS}$  values while VG was applied. Red data points show  $I_{DS}$  values measured at grounded gate voltage (VG = 0) 5 min after the corresponding gate voltages were applied. Arrows indicate the directions of hysteresis.

visible light, the photo-generated charge carriers in MoS<sub>2</sub> channel could affect the polarization of the PZT beneath. Figure 1-20 [94] shows that the stabilized zero-gate current level after 1 ms +6 V (erase) and -6 V (write) in dark environment would be degraded into an intermediate level that is indistinguishable after 5 mins of 150 W halogen bulb illumination. This intermediate state is close to the original "on" state and thus illumination could be used to "write" the device to "on" state, in addition to the electric pulse write option.

Figure 1-20. Effect of visible light illumination on the data retention characteristics of a MoS2-PZT FEFET.

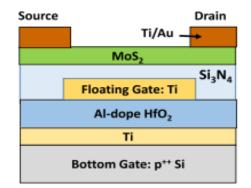

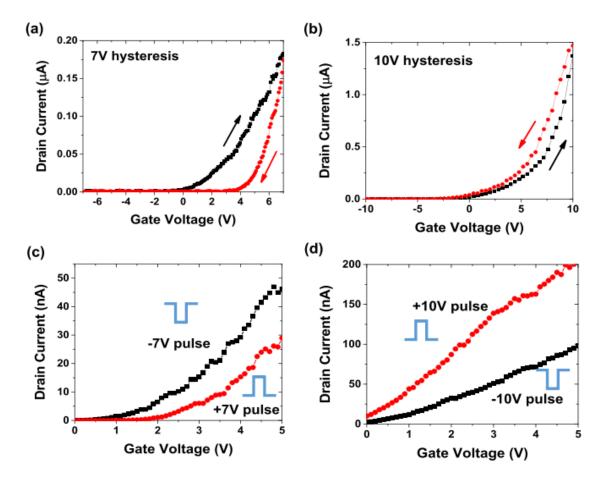

Other than graphene and MoS<sub>2</sub> on PZT, ferroelectric memory device with memory window from polarization-induced threshold voltage shift has also been fabricated with graphene and black phosphorus with PVDF ferroelectric polymer, which has comparable thickness to PZT layer but with smaller remanent polarization value [95, 96]. Other than back gate FET structure, 2D van der Waals heterostructure stack based on 2D ferroelectric material CuInP<sub>2</sub>S<sub>6</sub> and MoS<sub>2</sub> could also exhibit different traces for signature in transfer characteristics of FRAM [97]. A previous study done by our research group [98] demonstrated that Al-doped HfO<sub>2</sub> ferroelectric floating gate FET structure (Fig. 1-21) could successfully modulate the doping level in MoS<sub>2</sub> channel with the help of Ti intermediate gate (Fig. 1-22). These works provide valuable references toward our image classifier based on ferroelectric layer modulation.

Figure 1-21. structure of MoS<sub>2</sub> Al-doped HfO<sub>2</sub> ferroelectric floating gate FET.

Figure 1-22. (a)(b) A sweep gate voltage below (7V) and above (10V) coercive voltage generates clockwise/counterclockwise transfer characteristic hysteresis, indicating the interfacial trap/ferroelectric switching dominant processes. (c)(d) A gate pulse amplitude below ( $\pm$ 7V) and above ( $\pm$ 10V) coercive voltage generates opposite doping in channel, indicating the interfacial trap/ferroelectric switching dominant processes.

# **Chapter 2** Experimental Details

In this chapter, we discuss the experimental details including synthesis/characterization of 2D materials and fabrication of 2D material-based electronic devices. These processes include material yielding (CVD growth/mechanical exfoliation), identification, and transfer (bulk mass transfer or target transfer), along with device fabrication techniques (lithography, metal deposition and/or dielectric growth).

Compared to mature III-V material, Ge or Si growth techniques used in wafer-scale substrates, 2D material used in electronic devices for research nowadays is usually cleaved from bulk crystal (mechanical transfer) or taken as a membrane from corresponding CVD substrate (wet transfer). In general, mechanically transferred 2D material flakes are relatively intact but their shapes and thickness are more random and uncontrollable due to the irreproducible process while splitting the bulk material into fragmented pieces. Sizes of these 2D material flakes are hence typically small. On the other hand, CVD-grown material provides the possibility for a larger (even wafer-scale) area of continuous material and the thickness of the flakes is more consistent through growth parameters (growth seeds, gas flow, temperature, time, etc.). But the material is likely to suffer from quality issues from the growth process and following transfer process with chemical etchant involved. Typically, for both material sources, they need to be transferred (from either bulk material or growth substrate) to dielectric substrates (SiO<sub>2</sub>, quartz) to be further utilized in devices.

#### 2.1 Exfoliation and Mechanical Transfer

The method to yield "Scotch-tape graphene" used in the very first graphene transistor is widely known and forms the basis for the mechanical transfer method. For mass printing, magic tape or thermal-release tape is commonly used in labs. The following process describes typical steps for mechanical cleavage and transfer of 2D material from bulk crystal onto SiO<sub>2</sub> wafer or other substrates [99].

A wafer with 90 nm or around 280 ~ 300 nm SiO<sub>2</sub> thickness is preferred for visible contrast between substrate and transferred 2D material flakes [100]. Acetone/IPA cleaning followed by N<sub>2</sub> air gun blow-dry is often applied, preferably with sonication treatment. In many cases, Piranha solution (sulfuric acid to 30% hydrogen peroxide with 3:1 ratio in volume) cleaning and oxygen plasma etching are also applied to clean the wafer and promote adhesion between flakes and substrate [101]. The process should be finished within ~1 hour after substrate pre-treatment for enhanced transfer rate. In some special applications, quartz wafer or flexible polyimide substrates may be used to eliminate potential parasitic effects, depending on the device specification and requirements.

Then, a small piece of 2D material crystal is placed gently on the adhesive side of a piece of Scotch-tape/thermal release tape. Lay another piece of tape smoothly on previous tape to enclose the crystal piece in both tapes. Adhere tapes completely and uniformly. Split the tapes slowly from each other to exfoliate the flakes in the middle. During the exfoliation, maintain steady and slow speed ~ 1 mm per second. A small angle should be kept between the two tapes during the process and tension should be applied along the tape. This splitting process should be repeated several times to split the original crystal into thinner parts, either

between the same two original tapes, or with the help of new tapes. After crystals become sufficiently thin and cover a moderate area of the tape after several times of splitting, print the tape with thinnest flakes gently on the prepared substrate. Apply tension along the tape to make the contact between substrate and tape flat and uniform. Press gently to ensure sufficient contact.

Tape is the peeled away from the substrate after  $\sim 30$  s of contact. Similarly, exfoliation speed should be slow (~ 1 mm/sec) and tension should be exerted along the tape as well. A small angle between tape and substrate is important to a high yield of thin flakes on the target substrate. If thermal release tape is used, substrate with tape is placed on a hot plate, where a typical  $\sim 120$  °C temperature heats up the thermal release tape and curl it up to separate the tape from the substrate. This whole series of steps should be done with gloves on to minimized potential contamination. A glovebox could also help to reduce the degradation for air-sensitive 2D materials. Since the crystal shape is random at the beginning and the exfoliation process is arbitrary, it is very hard to precisely control the size and shape of the resulting 2D material flake. However, this method or many other recipes tend to yield large amount of atomically thin flakes of interest among thick crystal fragments. In order to better understand the unique two-dimensional properties of the material, various inspection techniques are required to locate appropriate flakes (for characterization or device fabrication) on the substrate. Since many flakes of varying size, thickness and shape are distributed on the substrate at the same time and we need to inspect the whole area in search of a target flake of interest (usually one or a few layers), this is an example of a bottom-up procedure.

Although the method above provides a standard way to produce large amount of thinned down flakes, in many cases, we require our 2D material flake to be at specific sites on the substrate instead of random locations. For example, if a heterostructure stacking different 2D material flakes is proposed, we need to transfer the second layer of material exactly on the first target flake layer. While the first layer of material could be mass printed on the substrate using the method described in last section, a targeting transfer is required to place the second layer on top of the first layer.

The key to accomplish such a goal is an appropriate transfer medium (usually some sacrificial adhesive solid/liquid chemical compound) which picks up the 2D material flakes from the tape or growth substrate. Then with help of the mechanical stage, the medium with flakes could be moved precisely and printed onto the target transfer area. Microscopes are often used to ensure accurate alignment before the contact between flakes on the medium and the target area on the substrate. The medium is then removed, leaving the transferred flake on the substrate.

In the past, the wedging method, polyvinylalcohol (PVA) method and Evalcite method have been used to place 2D material flakes on the target position [61, 102, 103]. The wedging method uses water as the transfer-active agent to lift off the spin-coated hydrophobic polymer layer on hydrophilic substrate. If 2D material flakes on the hydrophilic surface are partially taken away by the hydrophobic layer, they can then be transferred elsewhere. The sacrificial layer needs to be removed by solvent after transfer. In the PVA method, flakes are transferred onto polymer sacrificial layer from substrate after the water soluble PVA polymer layer is dissolved in water. The sacrificial layer is then scooped up and mounted onto the manipulator for transfer. It also needs to be removed after transfer is done. The Evalcite method makes use of low glass temperature polymer, which is applied between the glass slide and picked-up flakes. After flakes on the glass slide are moved to the desired location, heat is applied and the polymer melts, leaving flakes to drop easily on the acceptor substrate. In all these methods, chemicals from the sacrificial layer are involved and might degrade the crystal quality and give a rise to capillary force.

Compared to these wet agent transfer methods, dry transfer methods use solidated viscoelastic material as the transfer medium ("stamp") to carry the 2D material flakes without sacrificial layer dissolutions and they are low-cost, efficient and wet-chemical-free. Most dry transfer stamps are made of elastomer-based materials (polydimethylsiloxane, or PDMS, for example). For the dry transfer procedures used in our device fabrication based on Gelfilm (a polysiloxane based material similar to PDMS film) [104], the small piece of 2D material is first split into thinner flakes using methods described earlier. The flakes are then printed on the Gelfilm instead of SiO<sub>2</sub> substrates. Gelfilm is then observed under optical microscope so that flake with ideal size/thickness is located. The area of interest is then cut out and mounted on glass slide. A micromanipulator is then used to align the glass slide with target flake onto target area on the substrate. After the *Gelfilm* is brought into proximity with the substrate, continuous X-Y adjustment of the manipulator aligns the target flake on the *Gelfilm* to the target area on the substrate until flakes approach substrates in Z direction. Focus on the substrate and observe the alignment of target flake and target area while film starts to from contacts with substrate. The contrast between contacting and non-contacting regions during stamping could be easily differentiated by the contrast due to air gap. After complete adhesion is maintained for  $\sim$  30 s, apply heat on the substrate to soften and lower

the viscosity of the *Gelfilm* to facilitate dropping the 2D material onto the substrate. Lift and remove the glass slide quickly afterwards and inspect the substrate.

After 2D material flakes are transferred onto acceptor substrates, it is necessary to confirm their shape, size, thickness, and contact with substrate to ensure that proposed structures would be appropriately fabricated. In our work here, we mostly use optical microscope with camera and AFM to fulfill such tasks.

# 2.2 CVD Graphene and Wet Transfer

The previous section demonstrates how to extract 2D material flakes from bulk crystal. Instead of bulk synthesis, 2D material could also be grown with few layers on specific substrates (such as CVD graphene on copper/nickel films) and requires "peeling off" to be transferred onto other substrates for further characterization or device fabrication. Taking single-layer graphene grown on copper foil as an example, the following wet transfer steps provides a way to obtain CVD grown few layer 2D material on desired substrate. Note that the chemical (PMMA and copper etchant) may damage the grown layer's quality.

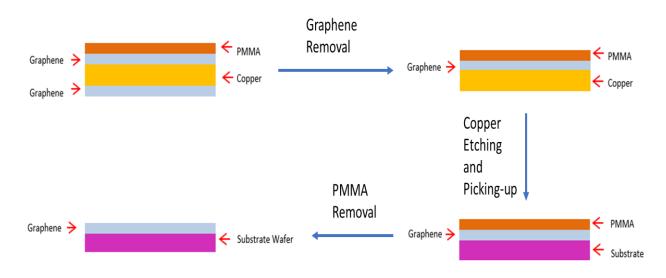

After transparent single-layer graphene is grown on both sides of the copper foil [33], PMMA is spun on top of graphene on one side, usually the outer surface during CVD process. A piece of PMMA/graphene/Cu/graphene stack is then put to float on copper etchant (FeCl<sub>3</sub>) in a beaker. After ~ 2 mins of floating, the graphene on back side (not protected by PMMA) are disappearing due to the partial copper removal. Repetitive rinsing between DI water beaker and copper etchant beaker should remove the copper and graphene on one side completely after ~ 10 mins etching. A silicon wafer piece is used to scoop and transfer the PMMA/graphene stack between beakers. Then the graphene/PMMA membrane is rinsed thoroughly in DI water before the desired substrate is used to scoop it up, leaving conformal single layer of graphene on substrate surface after gentle nitrogen gun blow and water evaporation. Acetone is then used to remove the PMMA sacrificial layer. Note that the chemical residue (PMMA and copper etchant) may degrade the material layer's quality. The cross section for the structure during this series of operation is shown in Fig. 2-1.

Compared to the mechanical exfoliation, the CVD layer wet transfer brings the possibility for large-scale and uniform 2D material coverage. Oxygen plasma against a photoresist layer could then selectively etch the graphene layer for device patterns.

Figure 2-1. CVD graphene cross section during procedures described in Section 2.2.

## 2.3 Identifying the Transferred 2D Materials

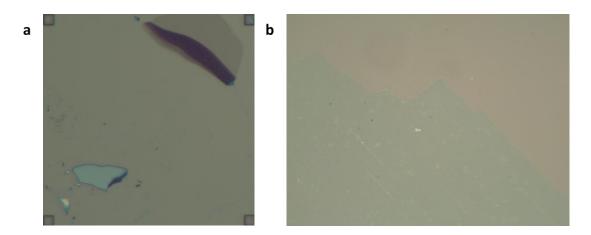

After 2D material flakes are transferred onto acceptor substrates, it is necessary to confirm their shape, size, thickness, and contact with substrate to ensure that proposed structures would be appropriately fabricated. An optical microscope is the most accessible and low-cost tool for rough inspection. Color contrast between the substrate and flakes transferred reveals the thickness. For atomic layers of 2D material, the color difference is barely visible. It generally holds that the thinner the layer, the lighter the contrast. For thick crystals among all the flakes transferred, their color ranged from green, to purple, to red, and to yellow, depending on specific material and thickness. An image process tool such as *ImageJ* could be used to numerically calculate the contrast between material body and substrate, providing a more reliable tool to determine material thickness [100]. Two example graphene optical images are shown below in Fig. 2-2.

Figure 2-2. (a) Mechanically exfoliated single-layer graphene (upright corner). Flake area with deeper color is multi-layer graphite. (b) Wet transferred CVD grown single-layer graphene (green area). Stripes on CVD-grown graphene are likely results from wet chemical etching and PMMA residue.

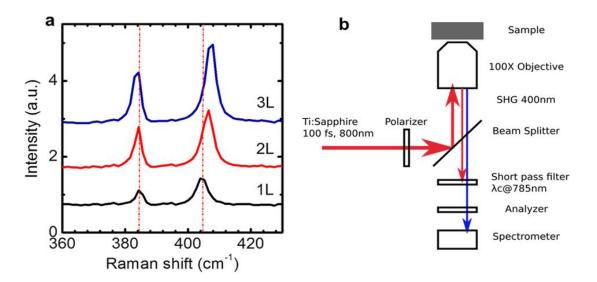

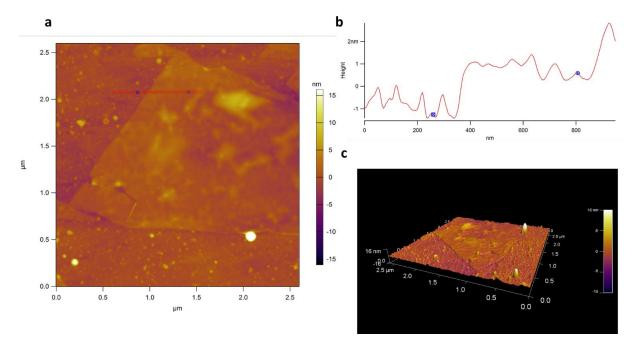

Raman spectroscopy and atomic-force microscopy (AFM) are widely used to determine the precise thickness of material. Specifically, the peak location and height of the Raman signal (with an example in Fig. 2-3 [41]) are signatures of the material since it reflects the unique vibration mode within the material and hence the interaction with incoming photons. Even for identical 2D material, samples with different thickness will slightly affect the peaks' relative location and height [41, 105]. AFM is commonly used to measure the thickness of the 2D flakes. Two-dimensional material has typical layer thickness from 0.4

nm to 1 nm [7, 37]. Figure 2-4 demonstrates a set of AFM data for a ~ 5-layer hexagonal boron nitride. Other identification methods include scanning electron microscopy (SEM), transmission electron microscopy (TEM), X-ray diffraction (XRD), etc., and are applied in various cases with different strengths and limitations [106].

Figure 2-3. (a) Raman signals from different thickness of MoS<sub>2</sub> and (b) tool setup.

Figure 2-4. AFM data for a 5-layer hBN. (a) Top view with color depth representing thickness in each region. (b) Line scan indicating the thickness along the red scan line in (a). (c) 3D rendered view.

#### **2.4 Device Fabrication**

As in other traditional semiconductor devices, optical and/or e-beam lithography can be used to pattern the structure layer with corresponding etching or metal deposition/liftoff. For example, if we need to form a specific dimension for the graphene channel in our FET or capacitor devices, an AZ photoresist pattern by regular optical lithography could be used as a mask to protect the channel beneath it while oxygen plasma could etch away the excessive part from our transferred 2D material flake or CVD layer. With the help of alignment marks on the wafer substrate, we could also align the physical location of the 2D material on a wafer with the mask designed by computer for e-beam lithography. Metal contacts are often designed this way prior to e-beam evaporation with lift-off due to the random position, size and shape of the 2D material flakes on the substrate.

Another common step involved in the construction of electronic devices is deposition of dielectrics. For 2D material devices, this could be done with a conventional dielectric growth method (atomic layer deposition of aluminum oxide/hafnium oxide, low pressure chemical vapor deposition of silicon nitride, etc.) or targeting transfer of a 2D insulator. Some channel materials, such as black phosphorus, are sensitive to high temperature and special treatment or an alternative path needs to be considered.

38

# **Chapter 3** Electrical Characterization of 2D Materials

Electrical characterization of capacitors and transistors based on 2D materials can provide important information on the material properties. In the past, most of the electrical characterization of 2D electronic devices is based on direct-current (DC) measurements. In this chapter we show that alternating-current (AC) measurements can provide unique insights on the properties of 2D crystals. More specifically, we show that the bandgap and the gap states of 2D materials can be extracted from capacitance and AC conductance measured at various temperatures. This information is critical for designing and optimizing electronic devices such as transistors, tunneling field-effect transistors (TFETs) and resonant tunneling diodes (RTDs) based on 2D materials. (Contents of this chapter was previously published in *Applied Physics Letters* [107] and is used here with permission)

# **3.1 Characterization of the Bandgap of Black Phosphorus**

The bandgap of black phosphorus (BP) is widely tunable, depending on the number of layers, external electric field and strain. Since the bandgap of black phosphorus is very narrow, it is difficult to measure using the standard photoluminescence and absorption spectroscopy in visible range. In this work, we propose a new approach to extract the bandgap of black phosphorus, using capacitance measured at various temperatures and frequencies. From the transition frequency or transition temperature, where the C-V changes from high-frequency to low-frequency behavior, we can extract the bandgap information. Using this method, we extracted the bandgap of the black phosphorus with 50 nm thickness as 0.30 eV. For comparison, we also extracted the bandgap of the black phosphorus using minimum conductance and threshold voltage methods, and the results are consistent with those of the C-V method. This C-V method can overcome the wavelength limitation of the photoluminescence measurement and spatial resolution limitation of Fourier transform infrared spectroscopy (FTIR). Another advantage of this C-V method is that the extracted bandgap is unaffected by the contact resistance and device area, making it reliable and convenient in determining the bandgap of narrow bandgap materials.

Black phosphorus has direct and tunable bandgap from 0.3 eV (bulk) to 1.4 eV (monolayer), corresponding to a broad energy spectrum from infrared to visible frequency range, which opens up a wide range of applications in photonics [56, 108-112]. The bandgap of the black phosphorus with layer number larger than five is less than 0.7 eV based on the density function theory (DFT) calculation [109, 113]. This narrow bandgap is beyond the wavelength range for most of the spectrometers in the photoluminescence (PL) measurements. In addition, the bandgap measured using PL is the optical gap, which is lower than the electronic bandgap due to the exciton binding energy. Recently, bandgap extractions based on current voltage (I-V) measurements using a Schottky metal-oxide field-effecttransistor (MOSFET) model were demonstrated, which can measure the transport gap directly [111, 112]. However, the accuracy of this method is highly dependent on the quality and the geometry of the devices, where the trap-assisted tunneling current and nonnegligible resistance along the channel can cause errors in the extracted bandgap values. In this chapter, we propose a new method to extract the bandgap of the black phosphorus using the C-V method and compare it with the bandgap extracted using minimum conductance and threshold voltage methods.

#### **3.1.1 Experiments**

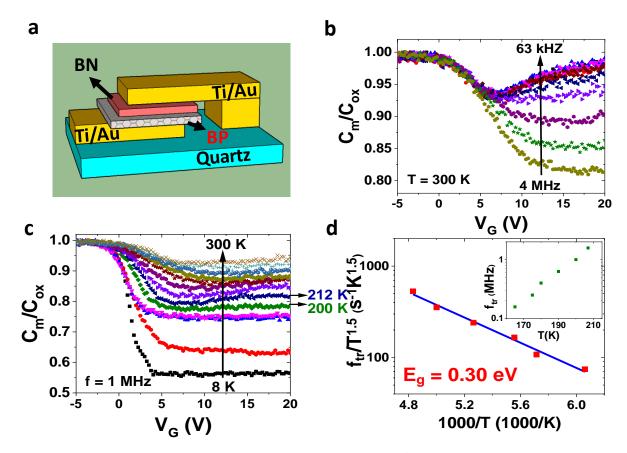

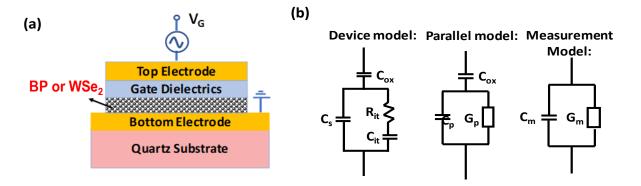

The black phosphorus capacitors were fabricated on quartz substrates to eliminate the potential parasitic capacitance between the probe pads and substrates. The black phosphorus flakes were exfoliated from bulk crystal and stacked onto the bottom metal electrodes using aligned dry transfer [104]. Hexagonal boron nitride (BN) was exfoliated from bulk crystal and used as the dielectric in the capacitor. C-V measurements were performed in vacuum at frequencies ranging from 10 kHz to 4 MHz and at temperatures ranging from 6 K to 300 K. Ti/Au (5nm/25nm) was deposited to form source and drain contacts in the BP transistors. The top gate dielectric is ~ 30 nm HfO2 deposited by atomic layer deposition (ALD).

## **3.1.2 Results and Discussion**

The device structure of a black phosphorus capacitor is illustrated in Fig. 3-1a. The BN thickness is ~ 32 nm and the black phosphorus thickness is ~ 50 nm. The multi-frequency C-Vs of the BP/BN capacitor measured at 300 K are shown in Fig. 3-1b. Here, the capacitance of the device, C, is normalized with respect to the gate dielectric capacitance, C<sub>ox</sub>. At 63 kHz measurement frequency, the C-V shows a typical low-frequency C-V behavior, where a local minimum is exhibited near the threshold voltage. As the frequency increases, the inversion capacitance decreases because the minority carriers in the inversion layer have more difficulty following the fast AC signal. At 4 MHz, the semiconductor capacitance shows high-frequency C-V behavior, where the inversion capacitance remains at minimum capacitance even beyond threshold voltage.

This transition from high- to low-frequency behavior is also observed in the temperature dependence of the capacitances. Figure 3-1c shows the C-Vs for BP/BN capacitors measured at 1 MHz from 8 K to 300 K. We can see that there is large temperature dispersion in the inversion over this temperature range. At low temperature (8 K), the minority carriers could not follow the 1 MHz signal; thus, a high-frequency behavior is observed. However, as temperature increases, minority carriers begin to follow because the generation and recombination rates ( $G_{gr}$ ) increase with temperature, so that the carrier response time ( $\tau_R = C_D/G_{gr}$ ) decreases. Here  $C_D$  is the depletion capacitance of the black phosphorus. As a result, the C-V curves change from high- to low-frequency behavior as the temperature increases from 8 K to 300 K. Here we define the transition frequency or transition temperature as the frequency or temperature where the C-V changes from a high-frequency to low-frequency behavior [114]. At 1 MHz frequency, the transition temperature is ~ 200 K for this BP capacitor, as shown in Fig. 3-1c.

By measuring the C-Vs at various temperatures and frequencies, the temperature dependence of the transition frequency can be determined. The inset of Fig. 3-1d shows the transition frequency as a function of temperature. Assuming the minority carrier response is dominated by the trap assistant process, the response time ( $\tau_R$ ) is inversely proportional to the intrinsic carrier density ( $n_i$ ):  $\tau_R \propto \frac{1}{n_i}$  [114]. Here the intrinsic carrier density can be expressed as:  $n_i = 2 \left(\frac{2\pi kT}{h^2}\right)^{3/2} \left(m_n^* m_p^*\right)^{3/4} e^{-E_g/2kT}$ , where  $m_n^*$  and  $m_p^*$  are the effective masses of electrons and holes respectively,  $E_g$  is the bandgap, h is Planck's constant, k is Boltzmann's constant, and T is the temperature. The transition frequency can be expressed as  $f_{tr} \approx 1/\tau_R$ . From these equations, we can see that the transition frequency follows:

$$f_{tr} \propto T^{3/2} e^{-E_g/2kT}$$

(3-1)

By plotting log  $(f_{tr}/T^{3/2})$  versus 1000/T, we can extract the bandgap from the slope, shown in Fig. 3-1d. The extracted bandgap is ~ 0.30 eV for this BP flake, which is consistent with the DFT calculation and the bandgaps extracted from Schottky barriers [109, 112].

Figure 3-1. Bandgap extracted using C-V method. (a) Illustration of the BP/BN capacitors on quartz substrate. (b) C-Vs of the BP/BN capacitor measured at 300 K with various frequencies. (c) C-Vs of the BP/BN capacitor measured at 1 MHz with various temperatures. (d) Transition frequency divided by T<sup>1.5</sup> as a function of 1000/T. From the slope, we extracted the bandgap of the black phosphorus to be 0.30 eV. The inset shows the transition frequency as a function of measurement temperature.

This transition frequency method provides a unique technique to extract the bandgap for narrow bandgap materials, such as black phosphorus. This C-V transition frequency technique can overcome the wavelength limit of the photoluminescence measurement and spatial resolution limit in Fourier transform infrared spectroscopy (FTIR). For indirect bandgap materials, since the photoluminescence signal is very weak, this electrical method to determine the bandgap will be very useful as well.

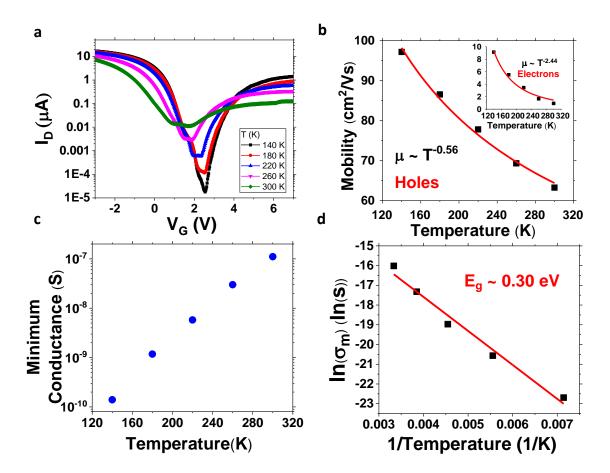

It has been reported previously that the bandgap of black phosphorus can be determined by minimum conductance. To compare the bandgaps extracted using these two methods, we fabricated BP transistors (with Al<sub>2</sub>O<sub>3</sub> dielectric) by same transfer and fabrications techniques and measured the temperature dependence of the transfer characteristics. Since the thickness of the BP flakes is typically above 30 nm and the flakes are exfoliated from the same crystal, we expect that they will have similar bandgaps [115]. The transfer characteristics of the BP transistors are shown in Fig. 3-2a. The motilities for holes and electrons are extracted from the linear regions of the transfer curves at the hole and electron branches respectively. The hole and electron mobilities are plotted as a function of temperature shown in Fig. 3-2b and the inset of Fig. 3-2b respectively. By fitting the temperature dependence of the mobility using the equation  $\mu \propto T^{-r}$  [116], we determine the r factor of this sample as 0.56 for hole mobility and 2.44 for electron mobility. The minimum conductance as a function of temperature is shown in Fig. 3-2c. The conductance ( $\sigma$ ) can be expressed as:  $\sigma = q(n\mu_e + p\mu_h)$ , where n and p are the carrier concentrations for electrons and holes,  $\mu_e$  and  $~\mu_h$  are the mobilities for electrons and holes, respectively. When the conductance reaches minimum, we have  $\frac{\partial \sigma}{\partial p} = 0$ . Considering  $np = n_i^2$ , we can derive that the minimum conductance:

$$\sigma_{\min} = 2qn_i \sqrt{\mu_e \mu_h} \tag{3-2}$$

Since the intrinsic carrier concentration  $n_i \propto T^{3/2}e^{-E_g/2kT}$  and  $\sqrt{\mu_e\mu_h} \propto T^{-3/2}$  based on the r factors extracted in our sample, the minimum conductance follows  $\sigma_{min} \propto e^{-E_g/2kT}$ . The BP bandgap could then be extracted from the plot of ln ( $\sigma_{min}$ ) versus (1/*T*), as shown in Fig. 3-2d. The extracted bandgap of the BP flake is ~ 0.30 eV, which is consistent with the result extracted from the C-V methods.

Figure 3-2. Bandgap extracted using minimum conductance method. (a) Ambipolar transfer characteristics of the BP transistor measured from 140 K to 300 K. (b) Effective hole mobility as a function of temperature. The inset shows the effective electron mobility as a function of temperature. (c) Minimum conductance as a function of temperature. (d) The bandgap of the black phosphorus extracted from the  $\ln (\sigma_{min})$  versus (1/*T*) plot is ~ 0.30 eV.

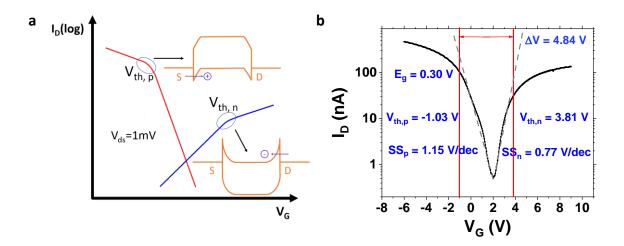

Another reported method to extract bandgap using IV measurement is based on the threshold voltages and subthreshold swing [117-119]. A transfer curve in semi-log scale is drawn in Fig. 3-3a and the band diagrams at the threshold voltages for the electron and hole

branches are illustrated in the insets of Fig. 3-3a. When the Fermi level in the source electrode is lined up with the conduction band edge of the semiconductor channel, the gate voltage applied on the channel is defined as threshold voltage for the electron branch,  $V_{th-n}$ . When the Fermi level in the drain electrode is lined up with the valence band edge of the semiconductor channel, the gate voltage applied on the channel is defined as threshold voltage for the valence band edge of the semiconductor channel, the gate voltage applied on the channel is defined as threshold voltage for the hole branch,  $V_{th-p}$  The subthreshold swing is  $SS \equiv \ln(10) \frac{\partial V_G}{\partial \ln(I_D)} = \frac{kT}{q} \ln(10) \frac{\partial V_G}{\partial \psi_s} = SS_{ideal} \frac{\partial V_G}{\partial \psi_s}$ , where  $\psi_s$  is the surface band bending in semiconductor and  $SS_{ideal} = \frac{kT}{q} \ln(10)$  is the thermodynamically limited subthreshold slope. Therefore, the bandgap of a semiconductor can be expressed as [117, 118, 120]:

$$E_{g} = q\left[\frac{\Delta V_{th}}{(SS_{p}+SS_{n})/2/SS_{ideal}}\right]$$

(3-3)

where q is the electron charge,  $\Delta V_{th} = V_{th-n} - V_{th-p}$  is the difference between the threshold voltages for electron and hole branches, and SS<sub>p</sub> and SS<sub>n</sub> are the subthreshold swings in p and n branches respectively. An example transfer curve measured at 300 K and the extracted threshold voltages are shown in Fig. 3-3b. The bandgap extracted is 0.30 eV, which is consistent with that extracted using C-V and minimum conductance methods discussed previously.

Among these three methods of extracting bandgap using electrical measurements, the C-V method uses the simplest device structure (two-terminal capacitor) and is least sensitive to the contact resistance. However, the C-V method is not practical for wide bandgap materials, since the transition temperature at the standard frequency range (1 kHz  $\sim$  5 MHz) can reach > 500 °C, which exceeds the temperature range for many probe stations. The threshold voltage method is the easiest and fastest method; however, its

accuracy is undermined by the ambiguity in determining the threshold voltage in real devices' transfer curves. The minimum conductance method has moderate accuracy and complexity for narrow bandgap materials but has very limited application in medium or wide bandgap materials, since the current at minimum conductance is below the detection level of the instrument if the bandgap is too large.

Fig. 3-3. (a) Expected Schottky-Barrier FET  $I_d$ - $V_g$  curve for small bandgap semiconductor and low work-function contact metal, with threshold voltages for both the electron and the hole branches labeled. When drain voltage applied is very small, band diagram is almost symmetric about source and drain sides. (b) I-V curve in log scale at 300K with extracted bandgap ~ 0.30 eV from threshold voltage difference and subthreshold swings (with  $v_{ds} = 1$ mV).

#### **3.1.3 Summary**

In conclusion, we proposed and demonstrated a new method to determine the bandgap of black phosphorus using C-V measurements. Based on the transition frequency, at which the C-V characteristics changes from high- to low-frequency behavior, we can extract the bandgap of the semiconductor. A 0.30 eV bandgap is determined for thick black phosphorus flakes (50 nm). For comparison, we also extracted the bandgaps using minimum conductance and threshold voltage methods. The bandgaps extracted from the three

methods are consistent with each other. This new method is especially useful for narrow and/or indirect bandgap materials, where photoluminescence measurements are beyond the spectrum range or detecting limit. The bandgap extracted using the C-V method is not affected by the contact resistance and device area, making it a convenient and accurate tool for charactering the bandgaps of narrow bandgap materials.

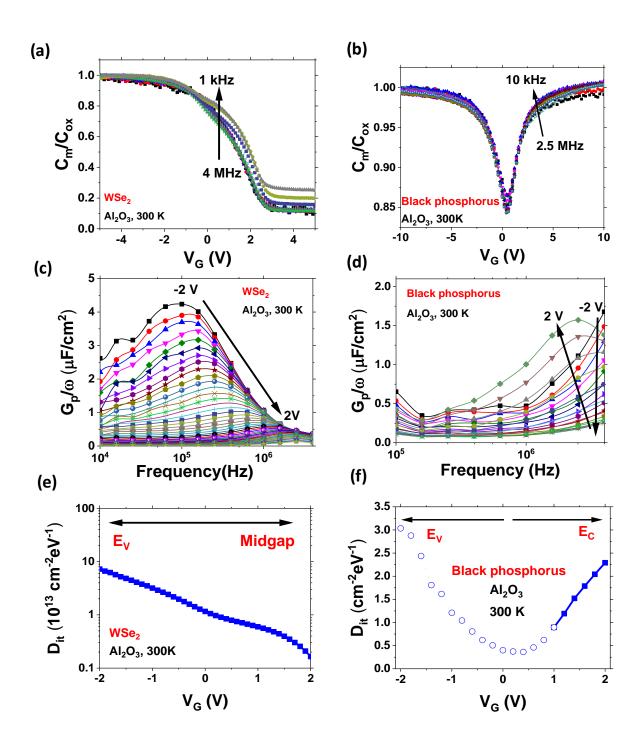

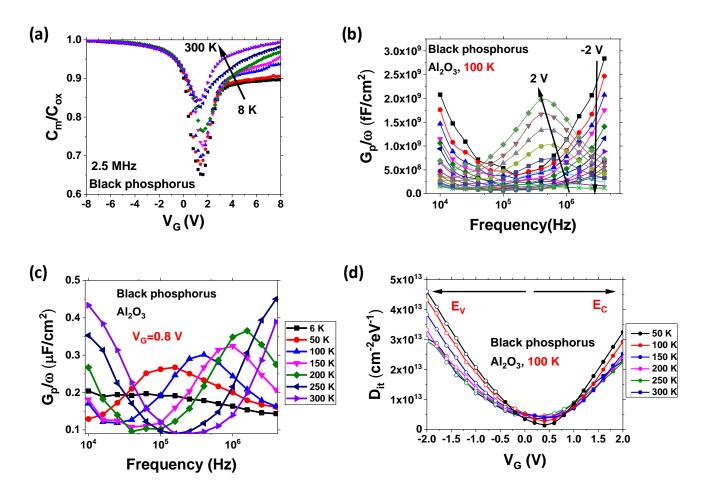

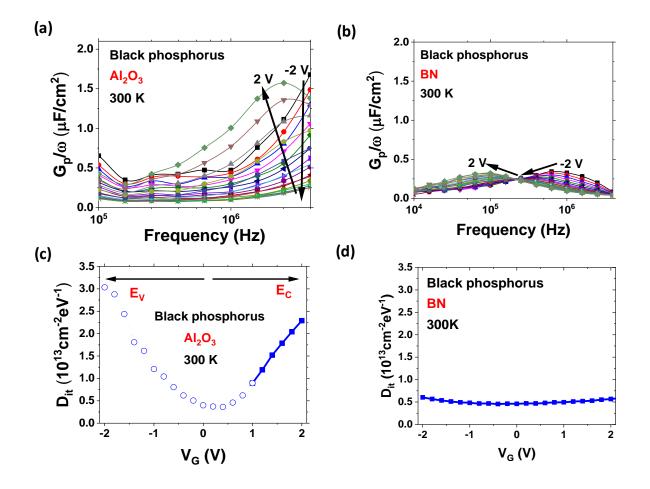

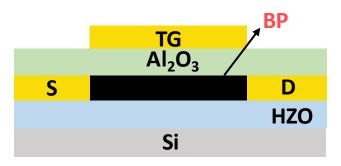

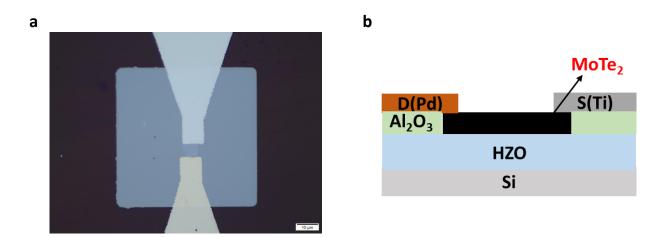

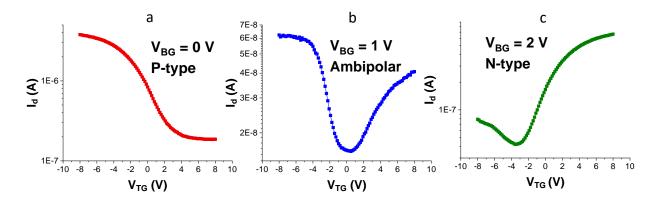

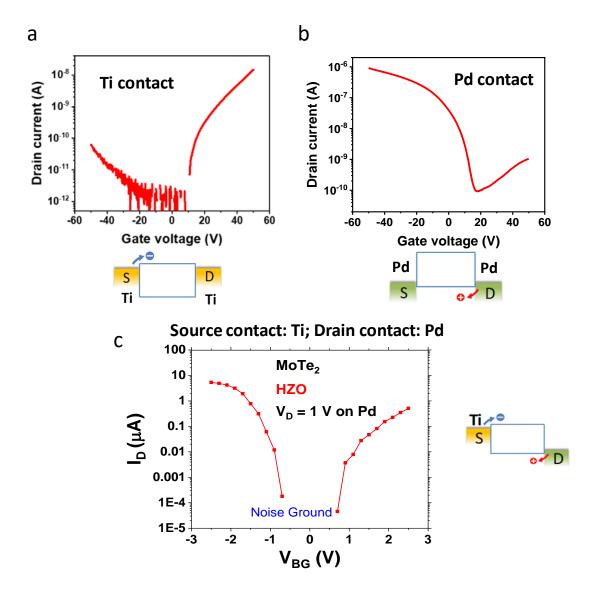

# **3.2 Characterization of the Interface States in Black Phosphorus**