Naik, Sneha A. (2020) On-detector electronics for high speed data transport, control and power distribution for the LHCb VELO and ATLAS Pixel Upgrades. MSc(R) thesis.

http://theses.gla.ac.uk/81585/

Copyright and moral rights for this work are retained by the author

A copy can be downloaded for personal non-commercial research or study, without prior permission or charge

This work cannot be reproduced or quoted extensively from without first obtaining permission in writing from the author

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given

Enlighten: Theses <u>https://theses.gla.ac.uk/</u> research-enlighten@glasgow.ac.uk

# On-detector electronics for high speed data transport, control and power distribution for the LHCb VELO and ATLAS Pixel Upgrades.

Sneha A. Naik

Thesis submitted for the degree of Master of Science by Research

School of Physics & Astronomy College of Science and Engineering University of Glasgow

July 2020

### Abstract

The Large Hadron Collider (LHC) will see an upgrade to higher luminosity to widen the scope of study of particle physics and this will be a major upgrade of the LHC. The LHC collides protons at an energy of 13 TeV in order to study the fundamental components of matter and the forces that bind them together. The High-Luminosity Large Hadron Collider (HL-LHC) will enter service after 2025, increasing the volume of the data for analysis by a factor of 10. The phenomena that physicists are looking for have a very low probability of occurring and this is why a very large amount of data is needed to detect them. Vertexing and tracking sub-detectors for these High Energy Physics (HEP) experiments deliver very high data rates that require multi-gigabit transmission links. Commercial solutions such as optical transmission or wire cabling are investigated, however, due to high radiation environments and low radiation length requirements, electrical transmission with low mass custom designs have to be considered. Designing transmission lines with this requirement does pose a challenge and optical data transmission is used when space and radiation limits allow.

The increase in luminosity will produce more data making it possible to study the phenomena in more detail by increasing the number of collisions by a factor of between five and seven. The increase in data will require an enhanced readout system and related electronics to be able to transmit and read out the data for further processing. At the same time powering systems need to be looked at to understand cost efficient and reliable techniques to be able to power such electronics. The thesis focuses on the readout electronics of the LHCb Vertex Locator (known as the 'VELO') Upgrade and the ATLAS Inner Tracker (known as the 'ITk') Upgrade including design of some components of the sub-systems, testing for high-speed data signaling, powering schemes and analysis of PCB designs and scope for improvements.

An introduction to the LHC and the four experiments that use its beam - ATLAS, CMS, ALICE and LHCb is outlined. The thesis work is focused on two of these detectors namely ATLAS (A Toroidal LHC ApparatuS) and LHCb (Large Hadron Collider beauty) and these are further explained and details of the sub-systems that make up these detectors are elaborated. Major differences to the upgrade of the experiments is explained highlighting the changes and the main challenges that would need to be addressed.

The work on the On-detector electronics of the LHCb VELO Upgrade with details of the design requirements and implementations for the different components is described and test

results are presented. Data tapes for carrying high speed data signals and control signals from the front-end chip to the Vacuum Feedthoough (VF) were designed and successfully tested to have a loss of < 10 dB at the Nyquist frequency of 2.5 GHz and a characteristic impedance of approximately 94  $\Omega$  which is within the 10% tolerance of 100  $\Omega$  for differential signals. Sensitivity to radiation damage as well as additional mass in the detector acceptance were some factors that motivated the design of the Opto Power board (OPB). In addition, there was a need to power the front-end ASICs but from outside the vacuum tank. The OPB was designed to meet these requirements in addition to be more easily accessible for repair and maintenance. The OPB is realised in an 8-layer stackup, with custom designed radiation hard ICs, and was designed for optical to electrical conversion of 20 high-speed data links at 5.12 Gb/s per link to be read by the Off-detector electronics. The board comprises 13 DC-DC converters for powering 12 ASICs, two front-end hybrids and the OPB itself with a total current supply of 26 A.

The ATLAS experiment will implement the Inner Tracker (ITk) which is a new tracker to be installed during the major ATLAS Upgrade during Long Shutdown 3. The work on the ATLAS ITK addresses two topics; a novel pixel powering scheme adopting layout techniques for high-speed design. A serial powering scheme was evaluated to be an optimal option and this scheme was tested to understand its scope and implementation in the pixel endcap design and results are presented. A study to understand the existing Crescent Tape PCB layout and techniques to improve the design for high-speed data transmission was evaluated.

Methods for analysing high-speed data using S-parameters and eye diagrams, sources of signal degradation and mitigation techniques, are detailed. The laboratory test setup for high-speed measurements with the equipments used is also explained.

## Acknowledgements

This thesis has become a reality with the blessings of the Almighty for giving me the strength, patience and keeping me focused though this journey. There are many people who have directly or indirectly contributed towards the completion of my thesis and I would like to express my deepest gratitude to all of them.

Firstly, I would like to thank my mentors, Prof. Lars Eklund and Dr. Richard Bates for helping and guiding me more than I could ever give credit for here. This accomplishment would not have been possible without their guidance and involvement, their support and encouragement at every stage of the thesis. They both were always there whenever I ran into a trouble spot or had any question related to my work or thesis writing. I would like to thank Dr. Kenneth Wraight, Dr. Cameron Dean, Dr. Manuel Schiller and Ms. Leyre Flores with whom I closely worked to complete some part of my thesis results. They have been extremely supportive and helpful colleagues and their extensive knowledge in physics and electronics has helped me a lot in meeting the objectives.

I am grateful to all of those with whom I have had the pleasure to work on both the ATLAS Upgrade and LHCb VELO Upgrade projects during this time. Each of the members I have worked with has provided me with professional guidance and support whenever needed.

I would like to express my thanks to the University of Glasgow for all the infrastructure made available that was much needed to carry out my research work. The atmosphere at the University, especially within the Detector Development Group, is incredibly collaborative and a wonderful learning environment. Not forgetting the Beans on Roast club for the lively environment in the office next door.

Finally, my thanks to my family for all of the love, support, encouragement and prayers they have sent my way along this journey. I must express my very profound gratitude to my parents who have been my ultimate role models and for always being with me in whatever I pursue. I am in debt to the unconditional love and care and the sacrifices they have done to help me be where I am today. I would like to thank my sister, Shradha, for always being there for me as a friend. Thanks to my parents-in-law who have believed in me and supported me in my goals.

From the thought of pursuing the Masters degree to its completion would not have been possible without the help of my husband, Amogh, who has provided me with unfailing love

#### Acknowledgements

and continuous support throughout my years of study and through the process of writing the thesis. Thanks for being patient with me when I was frustrated and for encouraging me to be focused to complete my thesis. I wish to thank my beautiful daughters, Anika and Aahana, who have tried to understand me and have helped me in their own way to complete this thesis. You both are my endless inspiration and have made me stronger and more fulfilled than I could have imagined.

## Declaration

This report is a product of my own work for the Masters degree and has not previously been presented for another degree in any other department or University.

Chapter 1 is a description of the LHC and specifically about the ATLAS and LHCb experiments and environments and doesn't contain any of my work.

Chapter 2 describes the methods and techniques used for design and testing and does not contain any of my work, apart from Section 2.5 where my contribution to the design of the CTLE is described. I have consolidated the information related to design guidelines and techniques which has been used in the work covered in the thesis.

Chapter 3 is a description of the LHCb Velo Upgrade where I have contributed to the systems design of the VELO electronics and my work on design is detailed.

Chapter 4 is a description of the LHCb VELO On-detector electronics testing. I designed all the PCBs that are described in the measurements except for the Vacuum Feedthrough Board where I was closely involved in the design and review. The Data tape measurements was a joint effort by Dr. Cameron Dean and myself. The high-speed links and Opto Power Board characterisation was a joint effort by Prof. Lars Eklund, Dr. Manuel Schiller, Dr. Cameron Dean along with me. The full link testing was mainly done by Dr. Cameron Dean with my help on the setup and testing, wherever needed. The testing of test coupons for high-speed performance before and after radiation was done by me.

Chapter 5 describes the systems design of the ATLAS ITk which does not involve my contribution. I have specifically worked on two topics described in this Chapter. I have collaborated with others to build a test system for testing serial powering scheme and I have designed all the test PCBs described in this section. Dr. Kenneth Wraight and myself together worked on debugging the hardware along with testing the different powering schemes. I was focused more on the electronics work while the the scans/plots for noise measurements were done by Dr. Wraight. For the high-speed measurements on the Crescent tape, all the test boards and measurements described were performed by me.

Wherever contribution of others is involved, every effort is made to indicate this clearly, with relevant reference to the literature and acknowledgment of collaborative research and discussions.

#### Sneha A. Naik

# Contents

| A | bstra | ıct                                                                              | i   |

|---|-------|----------------------------------------------------------------------------------|-----|

| Α | ckno  | wledgements                                                                      | iii |

| D | eclar | ation                                                                            | v   |

| 1 | Inti  | coduction                                                                        | 1   |

|   | 1.1   | The Large Hadron Collider                                                        | 1   |

|   | 1.2   | The LHCb Detector - The first version                                            | 3   |

|   | 1.3   | LHCb Upgrade and the Vertex Locator (VELO)                                       | 8   |

|   | 1.4   | ATLAS - The present System                                                       | 13  |

|   | 1.5   | ATLAS - Upgrade and Inner Tracker (ITk)                                          | 15  |

| 2 | Me    | thods and Techniques                                                             | 19  |

|   | 2.1   | Sources of Signal Degradation and Mitigation techniques                          | 20  |

|   | 2.2   | S-parameters                                                                     | 25  |

|   | 2.3   | Design for Manufacturing (DFM) / Design for Testing (DFT) $\ldots \ldots \ldots$ | 27  |

|   | 2.4   | Laboratory setup for S-parameter measurements.                                   | 28  |

|   | 2.5   | Continuous Time Linear Equalisation (CTLE)                                       | 29  |

|   | 2.6   | High-speed digital signalling and eye diagram                                    | 32  |

| 3 | LH    | Cb VELO Design                                                                   | 35  |

|   | 3.1   | Introduction                                                                     | 35  |

|   | 3.2   | On-detector electronics for the LHCb VELO Upgrade                                | 36  |

|   |       | 3.2.1 Front-end Hybrid and Kapton Tapes                                          | 36  |

|   |       | 3.2.2 High-speed Data tapes                                                      | 39  |

|   |       | 3.2.3 Vacuum Feedthrough Board (VFB)                                             | 45  |

|   |       | 3.2.4 Opto and Power Board (OPB)                                                 | 48  |

|   | 3.3   | Off-Detector Electronics                                                         | 54  |

| 4 | Ele   | ctronics Characterisation for the LHCb VELO Upgrade                              | 55  |

|   | 4.1   | Data Tape characterisation                                                       | 56  |

|    | 4.2   | High-speed links and Opto Power Board (OPB) characterisation $\ldots$ .              | 65  |

|----|-------|--------------------------------------------------------------------------------------|-----|

|    | 4.3   | Full link characterisation                                                           | 73  |

|    | 4.4   | Radiation tests on Test coupons                                                      | 76  |

| 5  | ATI   | LAS ITk (Inner Tracker) Pixel Designs                                                | 79  |

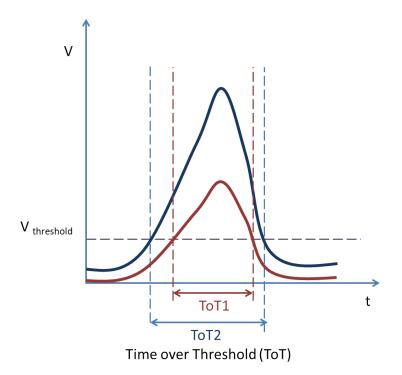

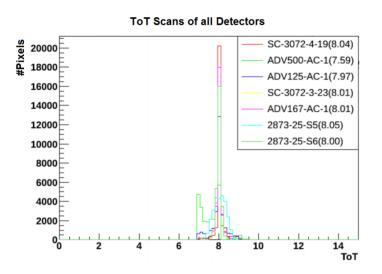

|    | 5.1   | Signal generation and Time over Threshold (ToT) in the FE-I4 pixel chip              | 80  |

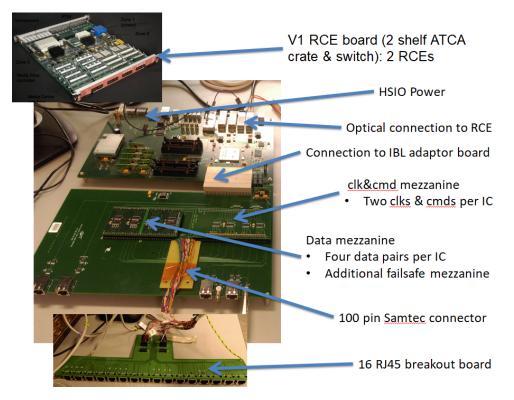

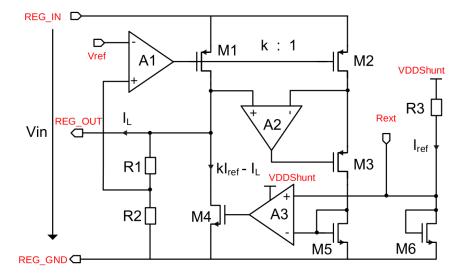

|    | 5.2   | Serial powering testing using Single Chip Card (SCC)                                 | 82  |

|    |       | $5.2.1$ Requirements for running multiple SSC in serial powering scheme $\therefore$ | 86  |

|    |       | 5.2.2 Connection of High Voltage (HV) return to the Low Voltage (LV) return          | 90  |

|    |       | 5.2.3 Measurements of Single Chip Card (SCC) with Serial powering                    | 91  |

|    | 5.3   | High-speed Tape Testing                                                              | 95  |

|    |       | 5.3.1 Requirements for testing the Crescent Tape                                     | 96  |

|    |       | 5.3.2 Results of Crescent tape testing                                               | 99  |

| 6  | Con   | aclusions 1                                                                          | .07 |

| Bi | bliog | graphy 1                                                                             | 11  |

# List of Tables

| 1.1 | Overview of global LHCb and LHCb Upgrade settings for simulations                     | 9  |

|-----|---------------------------------------------------------------------------------------|----|

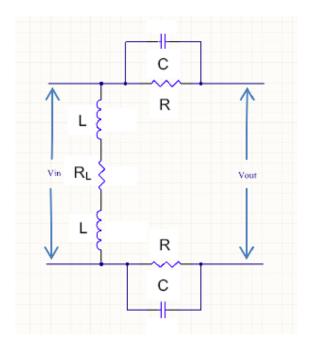

| 2.1 | Values for the passive CTLE components and the parameters of the filter               | 32 |

| 3.1 | Comparison of the key features and differences between TimePix3 and VeloPix.          | 37 |

| 3.2 | The initial three variants of the Data tapes with different trace width and           |    |

|     | trace spacing.                                                                        | 42 |

| 3.3 | PCB layer stackup for the prototype Vacuum Feedthrough Board (VFB)                    | 46 |

| 3.4 | $\operatorname{PCB}$ layer stackup for the production Vacuum Feedthrough Board (VFB). | 47 |

| 3.5 | Layer stackup of the production version of the OPB.                                   | 53 |

| 4.1 | The test coupon irradiation measurements at the facility at Birmingham                | 76 |

| 5.1 | Shunt-LDO circuit pins as implemented in FE-I4B.                                      | 85 |

| 5.2 | External resistor (Rext) and effective resistance (Reff) for analogue and digital     |    |

|     | regulator for FE-I4B.                                                                 | 86 |

# List of Figures

| 1.1  | A view inside the Large Hadron Collider (LHC) Tunnel.                                      | 1  |

|------|--------------------------------------------------------------------------------------------|----|

| 1.2  | Sketch of the LHC ring and the four experiments                                            | 2  |

| 1.3  | The LHC Schedule overview                                                                  | 3  |

| 1.4  | The schematic view of the LHCb present detector with the different sub-systems.            | 4  |

| 1.5  | Layout overview of the first version of the VELO detector, illustrating the                |    |

|      | vacuum tank, module positioning and RF foil.                                               | 6  |

| 1.6  | The schematic side-view of the Upgrade I detector. The figure highlights the               |    |

|      | changes that will be seen in the different sub-systems                                     | 9  |

| 1.7  | Evolution of interaction rates and average number of pp (proton-proton) in-                |    |

|      | teractions per bunch crossing visible in LHCb as a function of luminosity                  | 10 |

| 1.8  | Number of vertices per event for running at various values of $\mu$ (number of             |    |

|      | visible interactions per bunch crossing)                                                   | 11 |

| 1.9  | The conceptual layout of the VELO Upgrade detector within the LHCb coor-                   |    |

|      | dinate system.                                                                             | 12 |

| 1.10 | View of the Upgrade VELO system in closed position showing the 2 modules                   |    |

|      | with L-shaped geometry at the centre, close to the beam                                    | 12 |

| 1.11 | Cut-away of the overall ATLAS experiment showing the various sub-detectors                 |    |

|      | and the two magnet systems.                                                                | 13 |

| 1.12 | Schematic layout of the ITk for the HL (High luminosity)-LHC phase of AT-                  |    |

|      | LAS as presented in the Strip TDR                                                          | 17 |

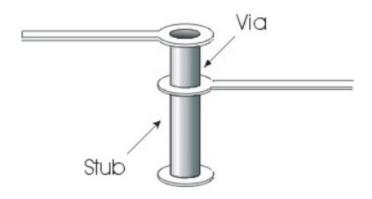

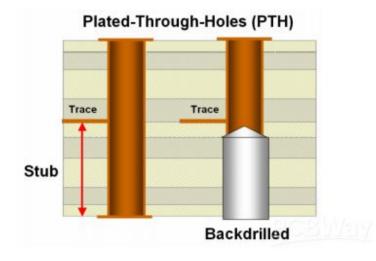

| 2.1  | Structure of a via showing the stub feature in via                                         | 21 |

| 2.2  | Back drilling technique for vias.                                                          | 22 |

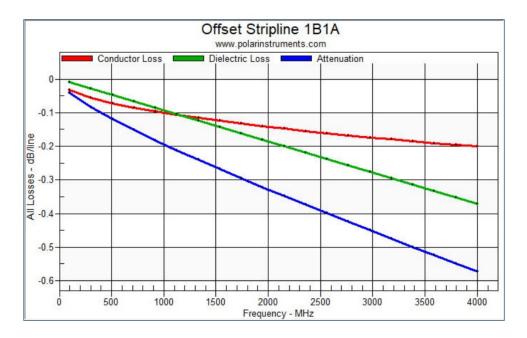

| 2.3  | Plot showing the effect of conductor and dielectric loss as a factor of frequencies.       | 23 |

| 2.4  | S-parameter for a two port network                                                         | 26 |

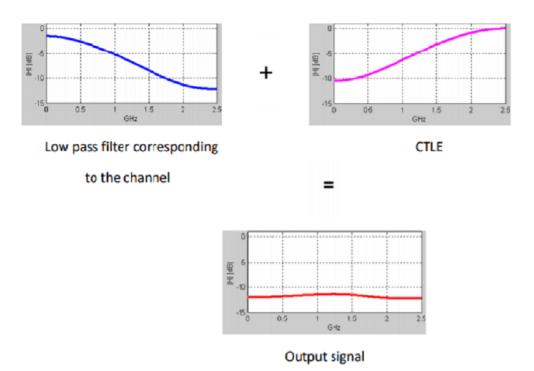

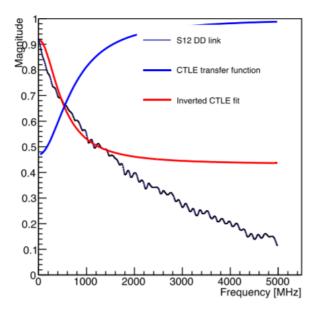

| 2.5  | Diagrams showing the principle of Continuous Time Linear Equaliser (CTLE).                 | 30 |

| 2.6  | Schematic of the passive CTLE with discrete components.                                    | 30 |

| 2.7  | The inverse of the transfer function $H(j\omega, R, C)$ fitted to the $S_{12}$ response to |    |

|      | attain the values of the passive CTLE components.                                          | 31 |

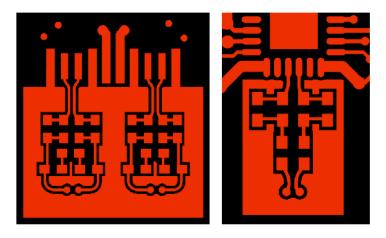

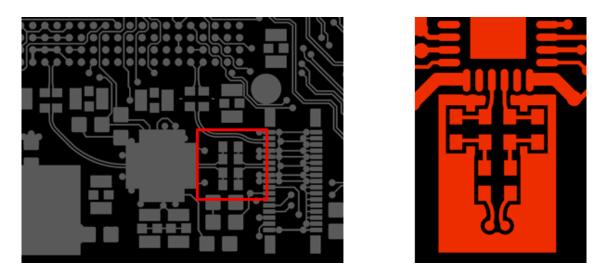

| 2.8  | Layout of the passive CTLE circuit for the data and control links as imple-                                                                            |          |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|      | mented on the OPB.                                                                                                                                     | 32       |

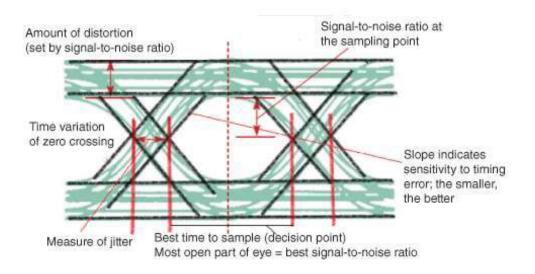

| 2.9  | Eye diagram showing a visual representation of the key electrical parameters.                                                                          | 34       |

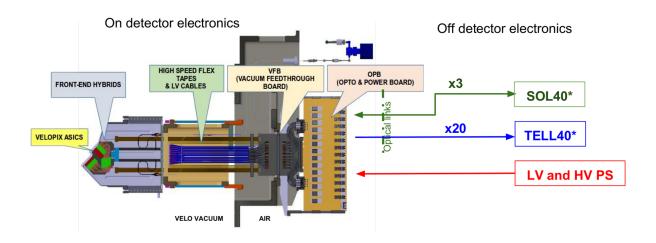

| 3.1  | An illustration of the upgraded VELO showing the On-detector and Off-                                                                                  |          |

|      | detector electronics.                                                                                                                                  | 36       |

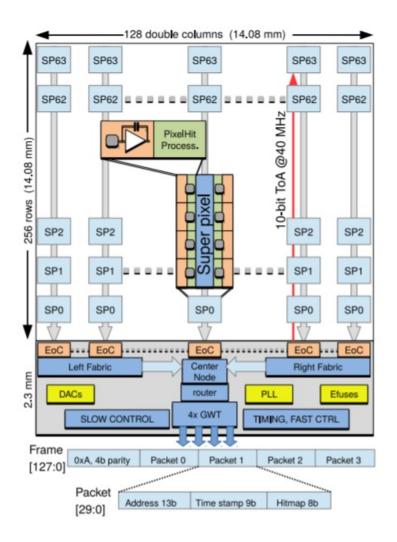

| 3.2  | Chip architecture of the VeloPix ASIC                                                                                                                  | 38       |

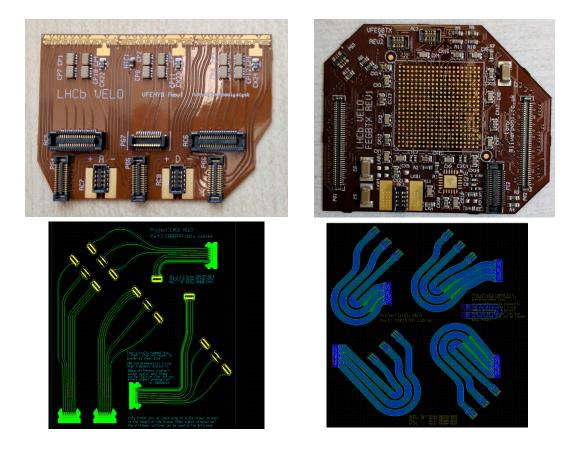

| 3.3  | Components of the front-end Hybrid assembly                                                                                                            | 39       |

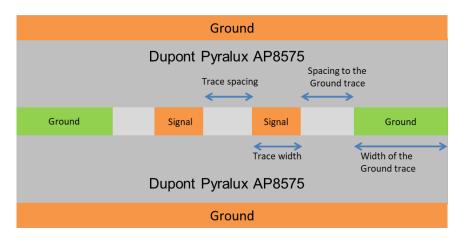

| 3.4  | Cross section of the Data tape.                                                                                                                        | 41       |

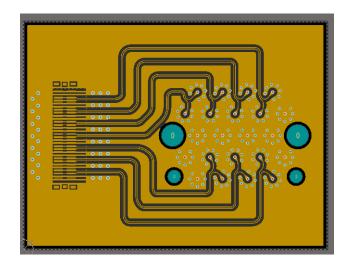

| 3.5  | PCB layout of the Data tape with trace width/trace spacing of $0.2 \text{ mm}/0.2 \text{ mm}$ .                                                        | 42       |

| 3.6  | PCB layout of the Test Board-variant 1.                                                                                                                | 43       |

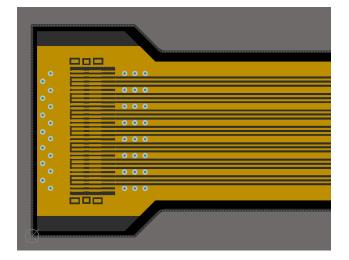

| 3.7  | PCB layout of TapeVar1.2.                                                                                                                              | 44       |

| 3.8  | PCB layout of the Test board-variant 3.                                                                                                                | 45       |

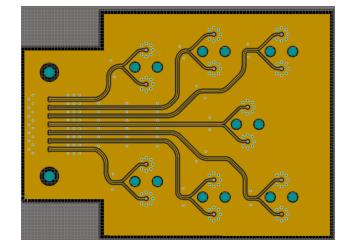

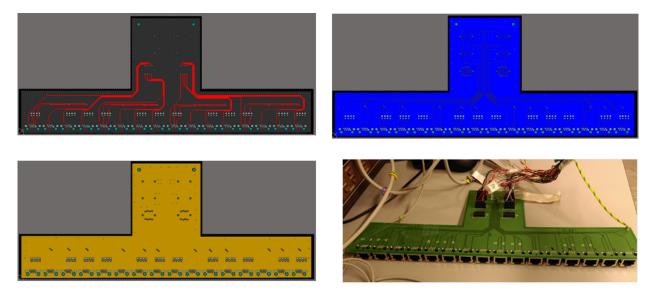

| 3.9  | PCB layout of the prototype of the Vacuum Feedthrough Board (VFB)                                                                                      | 46       |

| 3.10 | PCB layout of the production Vacuum Feedthrough Board (VFB)                                                                                            | 47       |

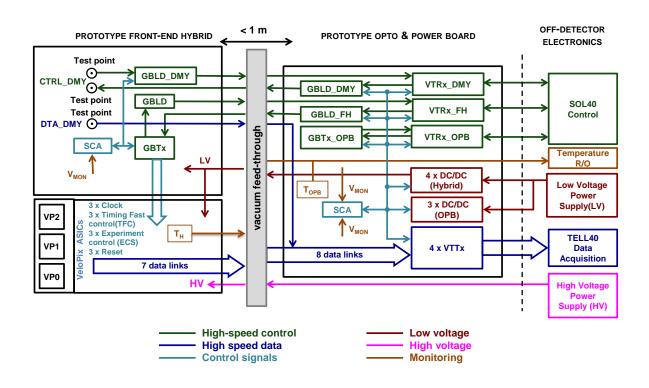

| 3.11 | Overview of the prototype system showing the role of the prototype OPB and                                                                             |          |

|      | the main components of the prototype front-end Hybrid and OPB                                                                                          | 49       |

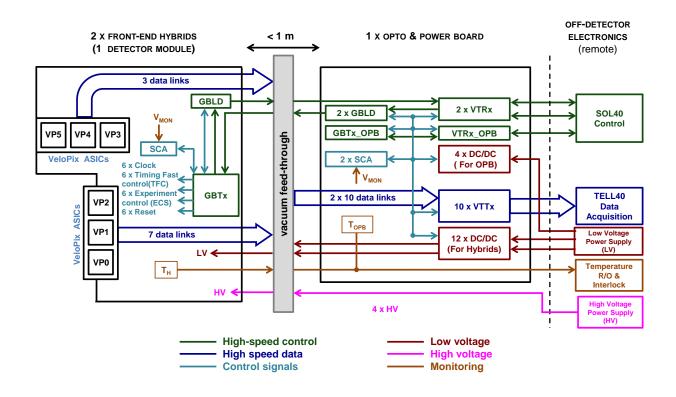

| 3.12 | Overview of the VELO Upgrade electronics showing the role and functionality                                                                            |          |

|      | of each block in the system.                                                                                                                           | 51       |

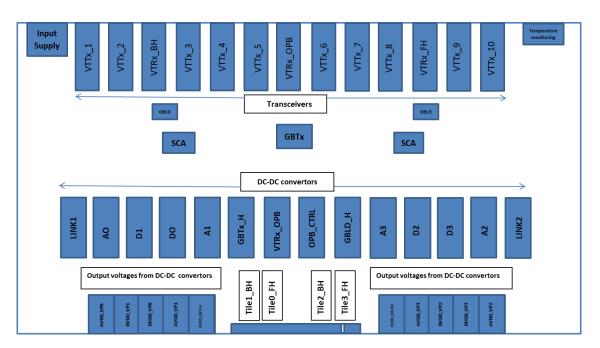

| 3.13 | Block diagram showing the placement of main components on full size OPB.                                                                               | 52       |

| 3.14 | DC-DC powering scheme on the OPB.                                                                                                                      | 52       |

| 3.15 | Measurement of the link from the front-end hybrid to the VTRx on the OPB.                                                                              | 53       |

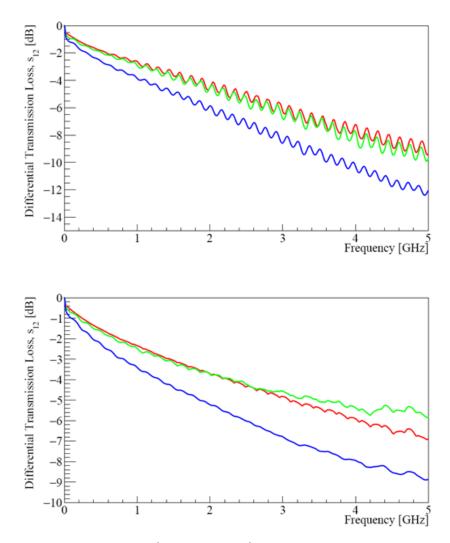

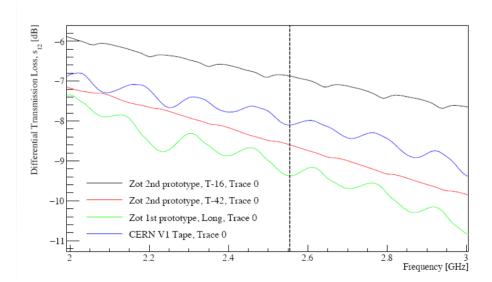

| 4.1  | Transmission results (S-parameters) comparing the three prototype tapes (fab-                                                                          |          |

|      | ricated at CERN) along a channel.                                                                                                                      | 57       |

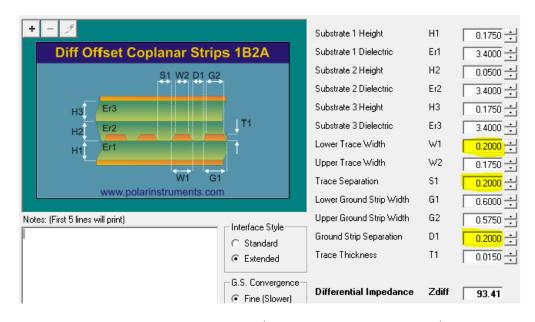

| 4.2  | Calculations of the trace width/trace spacing of $0.2~\mathrm{mm}/0.2~\mathrm{mm}$ for the data                                                        |          |

|      | tape using Polar calculator.                                                                                                                           | 58       |

| 4.3  | Transmission results (S-parameters) for Variant TapeVar1.1.                                                                                            | 59       |

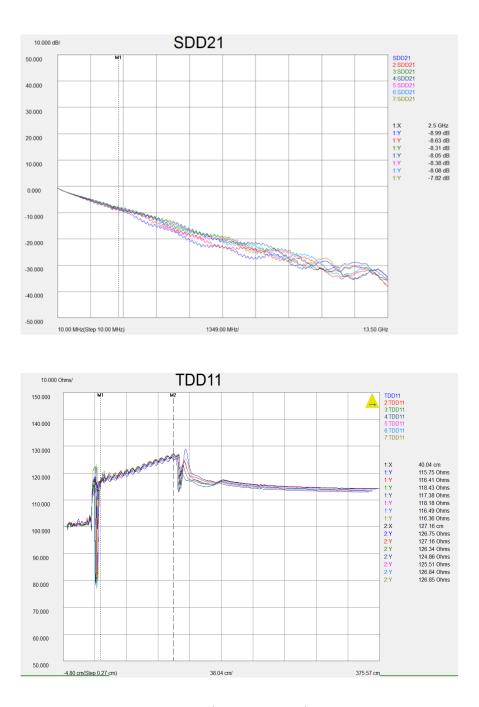

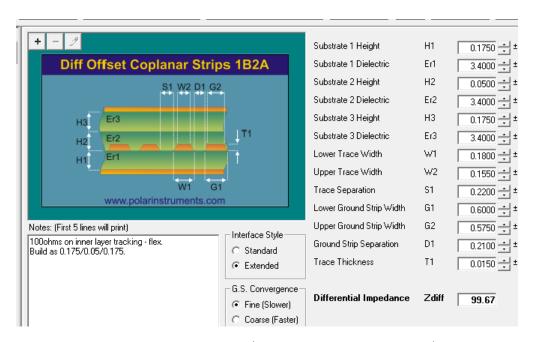

| 4.4  | Calculations of the trace width/trace spacing of 0.18 $\mathrm{mm}/0.22 \mathrm{mm}$ for the                                                           |          |

|      | data tape using Polar calculator.                                                                                                                      | 60       |

| 4.5  | Transmission results (S-parameters) comparing the losses from the different                                                                            |          |

|      | $tape \ designs. \ldots \ldots$ | 60       |

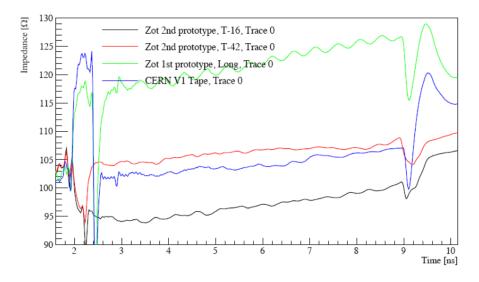

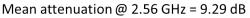

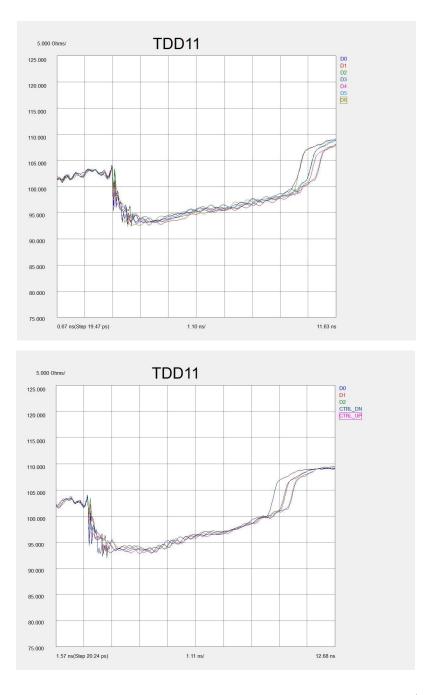

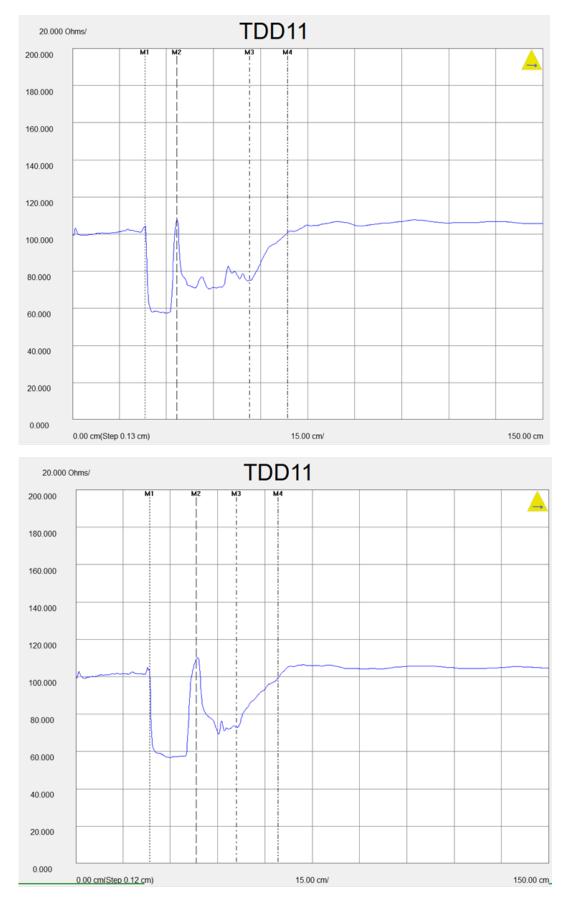

| 4.6  | Comparison of the impedance results of different tape designs. $\ldots$ $\ldots$ $\ldots$                                                              | 61       |

| 4.7  | Results (S-parameters) of the pre-production Left Hand Side (LHS) tapes. $\ .$                                                                         | 61       |

| 4.8  | Results (S-parameters) of the pre-production Right Hand Side (RHS) tapes.                                                                              | 62       |

| 4.9  | Differential impedance profile for Left Hand Side (LHS) tape and Right Hand                                                                            | 0.9      |

| 4.10 | Side (RHS) tape on (pseudo) TDR on the network analyser.                                                                                               | 63<br>64 |

| 4.10 | Results (S-parameter and impedance) of tapes from different production panels.                                                                         | 64       |

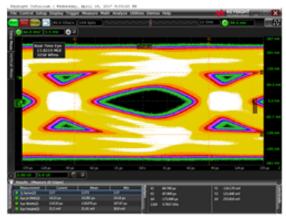

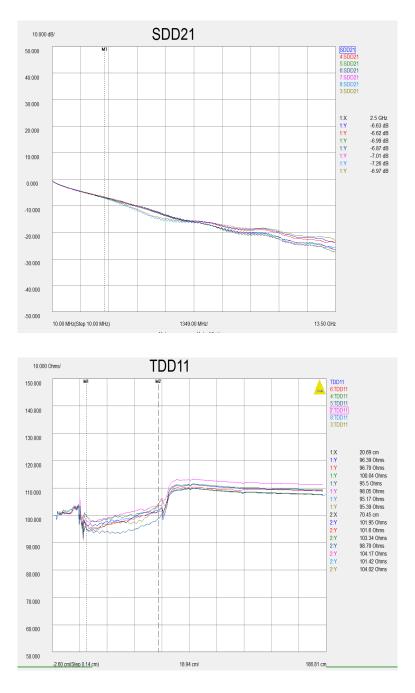

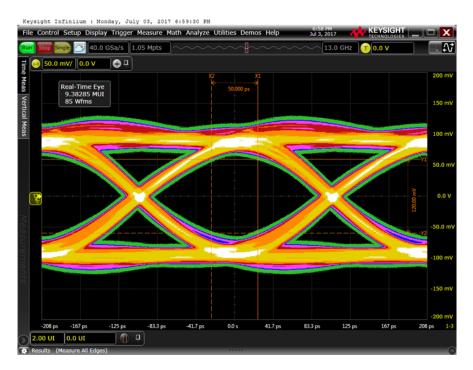

| 4.11 | The eye diagram produced by the prototypes for the full setup using a PRBS $2^7 - 1$ signal at 5.12 Gb/s | 65 |

|------|----------------------------------------------------------------------------------------------------------|----|

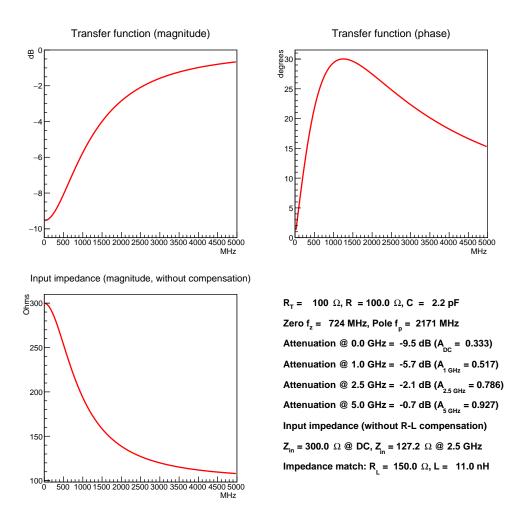

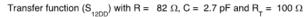

| 1 19 | The transfer function magnitude and phase plots and the impedance plot for                               | 00 |

| 4.12 | the passive CTLE network                                                                                 | 66 |

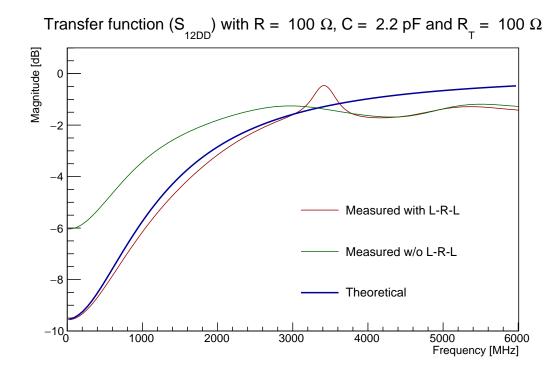

| 4.13 | Comparision of the CTLE transfer function: theoretical and with derived pas-                             |    |

|      | sive component values.                                                                                   | 67 |

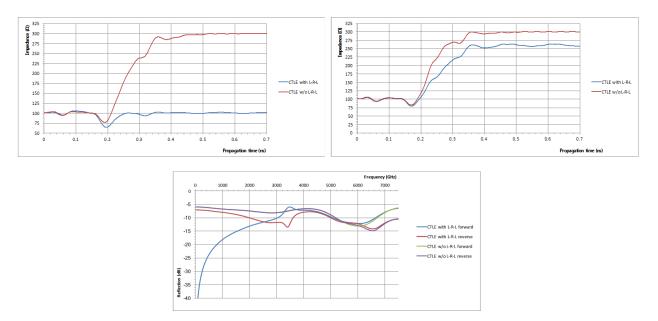

| 4.14 | Evaluation of the impedance plots for the passive CTLE with and without the                              |    |

|      | L-R-L circuit.                                                                                           | 67 |

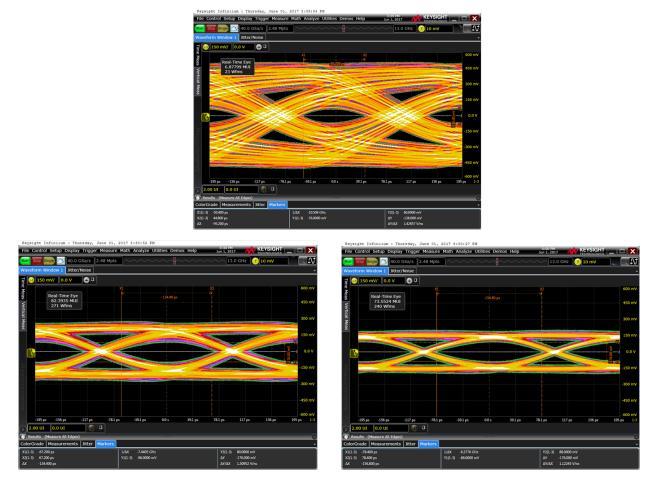

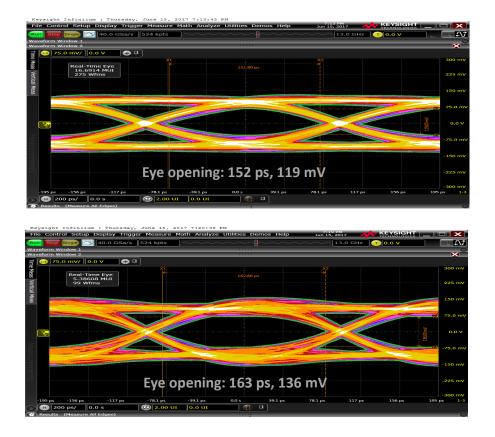

| 4.15 | Eye diagram with and without passive CTLE network.                                                       | 68 |

| 4.16 | Passive CTLE implementation on the front-end Hybrid and the OPB                                          | 69 |

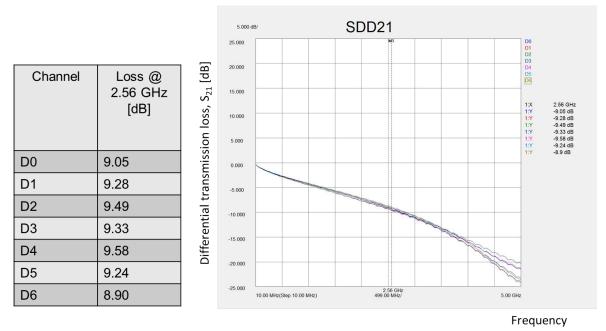

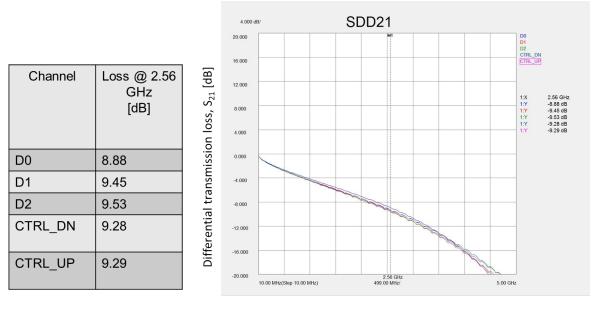

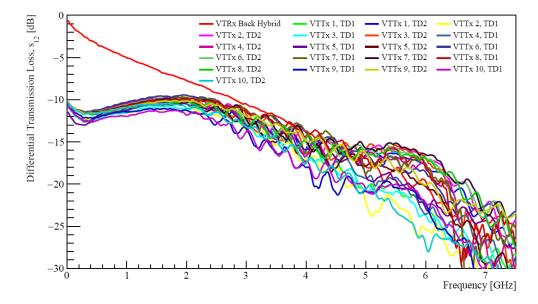

| 4.17 | Measurements for differential transmission losses for the full sized pre-production                      |    |

|      | prototype across 20 traces.                                                                              | 69 |

| 4.18 | A more moderate passive CTLE component values and its performance for the                                |    |

|      | control link.                                                                                            | 70 |

| 4.19 | Eye diagram for the control link with power-on GBLD settings. $\ldots$ $\ldots$                          | 70 |

| 4.20 | Eye diagram with modulation current of the GBLD set to $7\mathrm{mA}$ and with/without                   |    |

|      | pre-emphasis.                                                                                            | 71 |

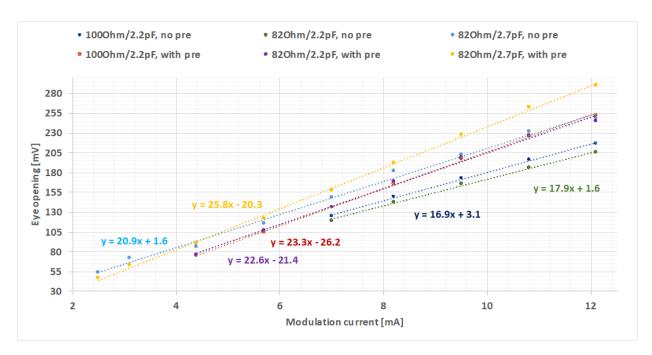

| 4.21 | Effect of the CTLE passive components and the GBLD parameters on the eye                                 |    |

|      | opening                                                                                                  | 72 |

| 4.22 | Eye diagram for the control link with tweaked GBLD settings                                              | 72 |

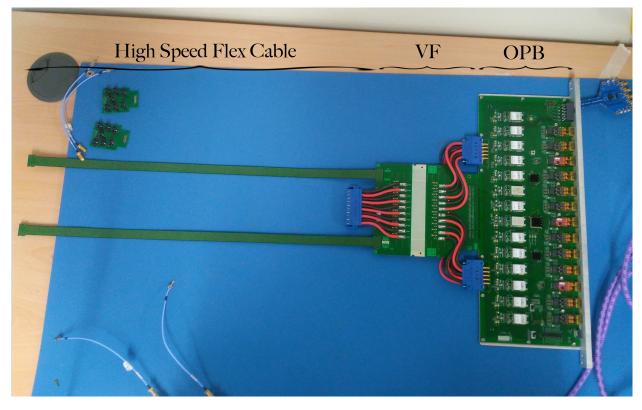

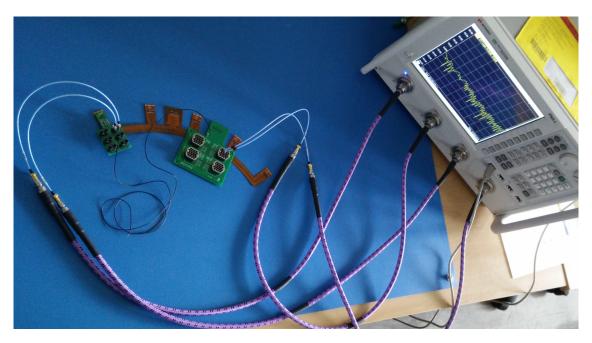

| 4.23 | Setup showing the prototype designs of the full sized Opto-Power Board (OPB),                            |    |

|      | Vacuum Feedthrough Board (VFB) and two Data tapes.                                                       | 73 |

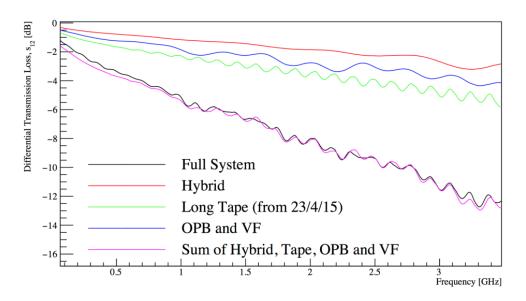

| 4.24 | Signal loss as a function of frequency for the front-end Hybrid, Data tapes,                             |    |

|      | VFB and the OPB                                                                                          | 74 |

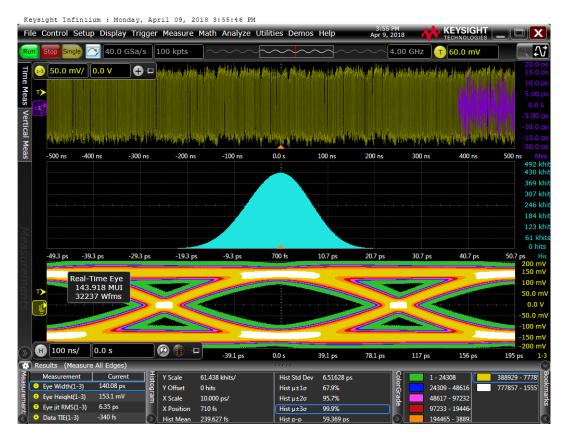

| 4.25 | A screenshot of a typical trace under test from the pre-propoduction prototype                           |    |

|      | using a PRBS $2^{31} - 1$ signal at 5.12 Gb/s                                                            | 75 |

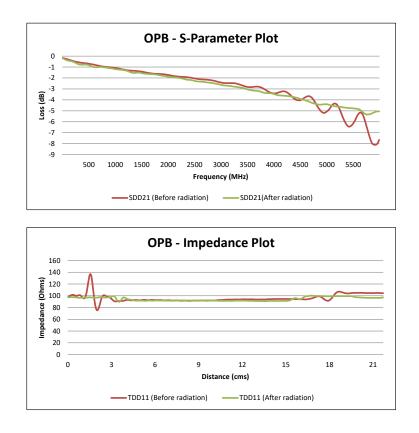

| 4.26 | PCB layout of the test coupon for radiation tests.                                                       | 76 |

| 4.27 | The measurement results (S-parameter and impedance) of the OPB test coupon                               |    |

|      | before and after radiation.                                                                              | 77 |

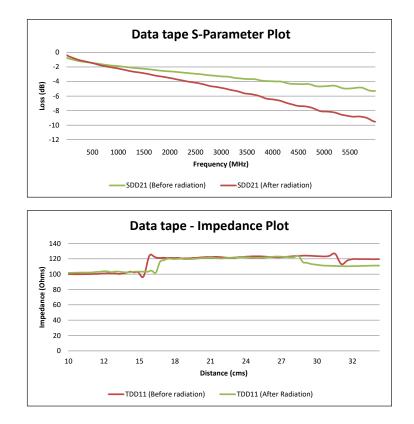

| 4.28 | The measurement results (S-parameter and impedance) of the Data tape test                                |    |

|      | coupon before and after radiation                                                                        | 78 |

| 5.1  | Time over threshold (ToT) digitizing scheme.                                                             | 81 |

| 5.2  | Time over threshold (ToT) scans of some operational detectors.                                           | 81 |

| 5.3  | Single Chip Card (SCC) with ASIC-Sensor assembly mounted on a Carbon                                     |    |

|      | Fiber Reinforced Polymer (CFRP) base board                                                               | 82 |

| 5.4  | Serial powering apparatus with RCE, HSIO-II, IBL adaptor Board, RJ45                                     |    |

|      | breakout Board that interfaces to Single Chip Card (SCC)                                                 | 83 |

|      | breakout Board that interfaces to Single Chip Card (SCC)                                                 | 83 |

| 5.5   | Low Dropout (LDO) regulator with Shunt capability (Shunt-LDO) as implemented in FE-I4B.                                   | 84       |

|-------|---------------------------------------------------------------------------------------------------------------------------|----------|

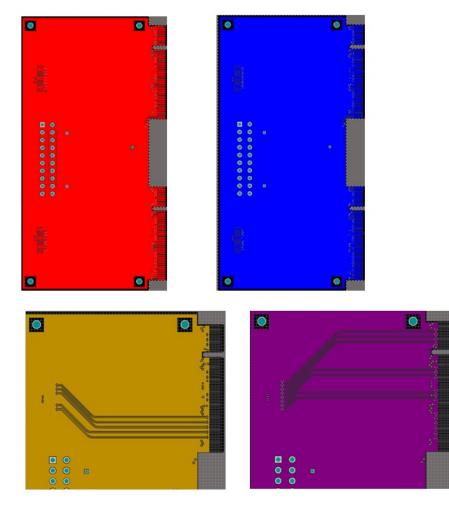

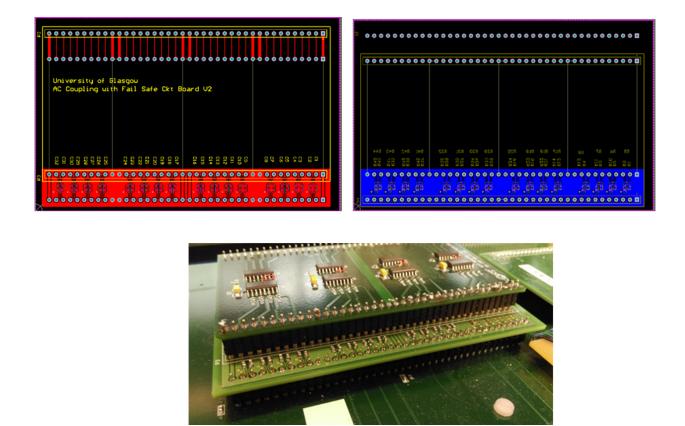

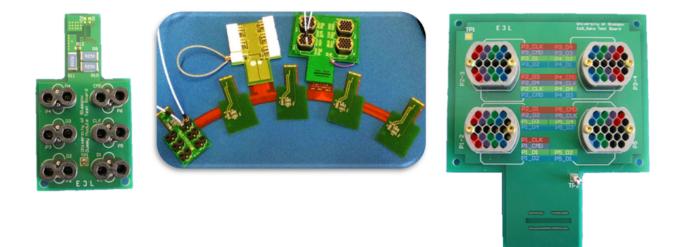

| 5.6   | RJ45 breakout Board for multi-module testing showing the PCB layout and                                                   |          |

| 0.0   | the assembled PCB.                                                                                                        | 87       |

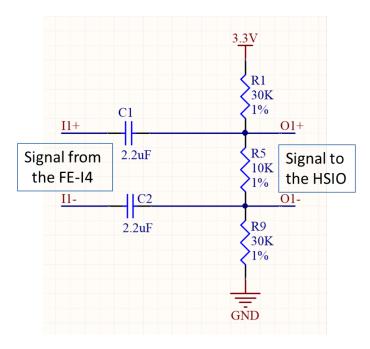

| 5.7   | AC coupling capacitors and the fail safe circuit implemented on one of the                                                |          |

|       | data pair.                                                                                                                | 88       |

| 5.8   | AC coupling board showing the PCB layout and the assembled PCB                                                            | 88       |

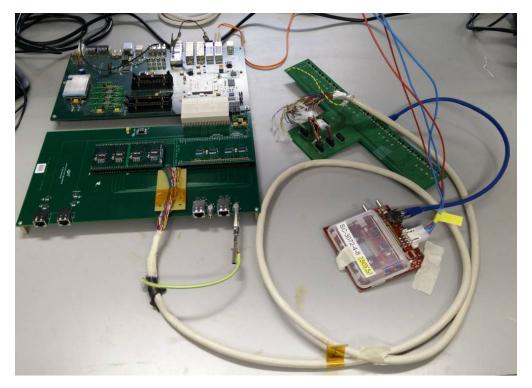

| 5.9   | Serial powering setup with HSIO and RCE, RJ45 breakout board and Single<br>Chip Card (SCC)                                | 89       |

| 5.10  |                                                                                                                           | 09       |

| 0.10  |                                                                                                                           | 90       |

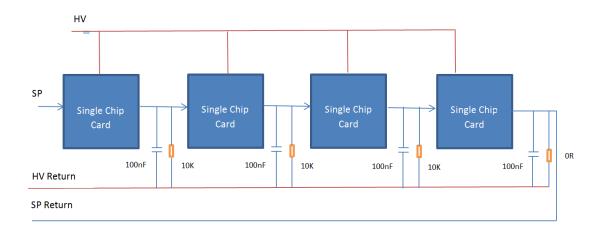

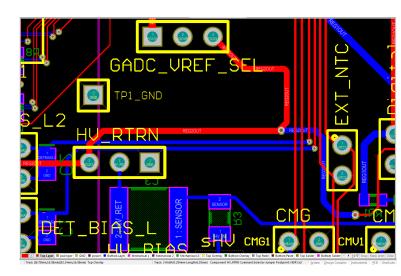

| 5.11  | the system for multi-module testing in serial powering scheme                                                             | 90<br>90 |

|       |                                                                                                                           | 90       |

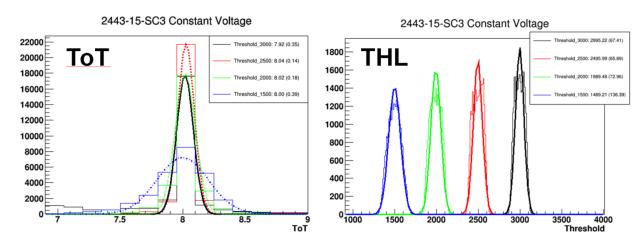

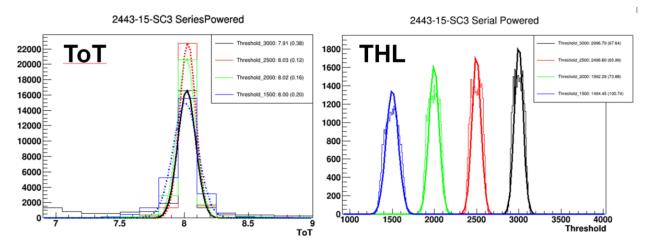

| 0.12  | Fitted Gaussian scans for Time over threshold (ToT) and histogram of the $V_{\rm const}$ value for a detector in LDO mode | 91       |

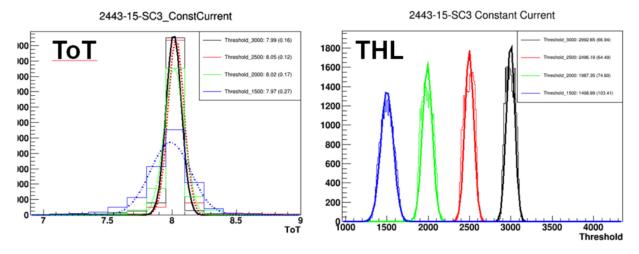

| 5.13  | $V_{\text{threshold}}$ value, for a detector in LDO mode                                                                  | 91       |

| 0.10  | $V_{\text{threshold}}$ value, for a detector in Shunt LDO mode                                                            | 92       |

| 5.14  | Fitted Gaussian scans for Time over threshold (ToT) and histogram of the                                                  | 92       |

| 0.14  | $V_{\text{threshold}}$ value, for a detector in serial powering mode                                                      | 93       |

| 5 1 5 | Overlap of a single tune scan for the constant voltage, constant current and                                              | 90       |

| 0.10  | serial powering and all the 3 overlap for 8 ToT@20k and Threshold value= $2500$                                           | 93       |

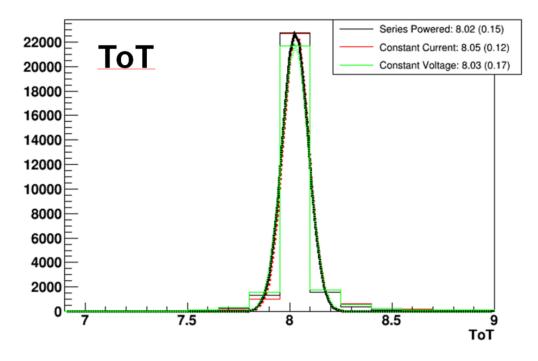

| 5.16  |                                                                                                                           | 50       |

| 0.10  | scans.                                                                                                                    | 94       |

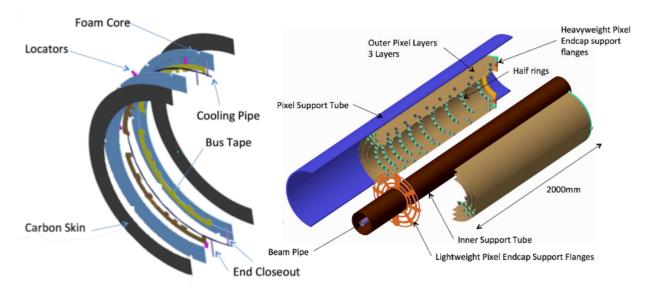

| 5.17  |                                                                                                                           | 01       |

|       | rings for mounting modules.                                                                                               | 95       |

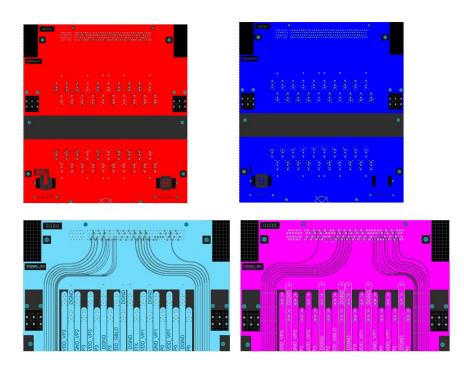

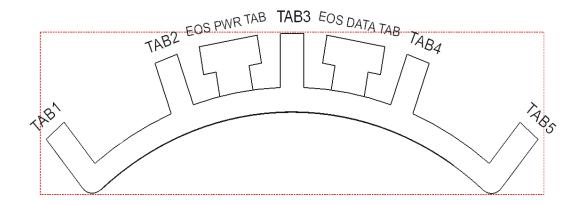

| 5.18  | Crescent Tape with positions of each TAB                                                                                  | 96       |

|       | Crescent tape build showing the layer assignments and the material build.                                                 | 96       |

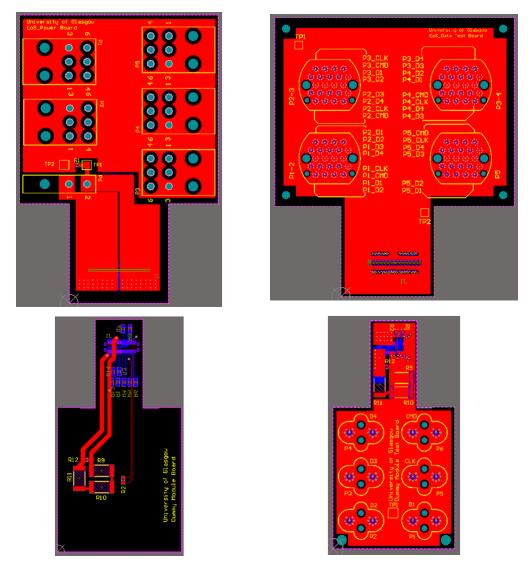

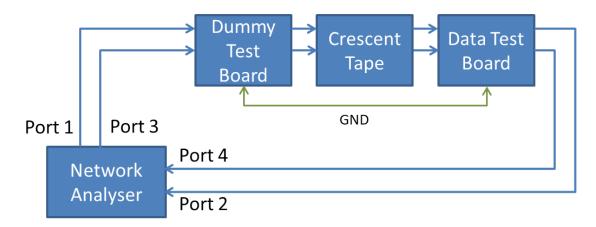

| 5.20  | Apparatus for measuring the Crescent Tape                                                                                 | 97       |

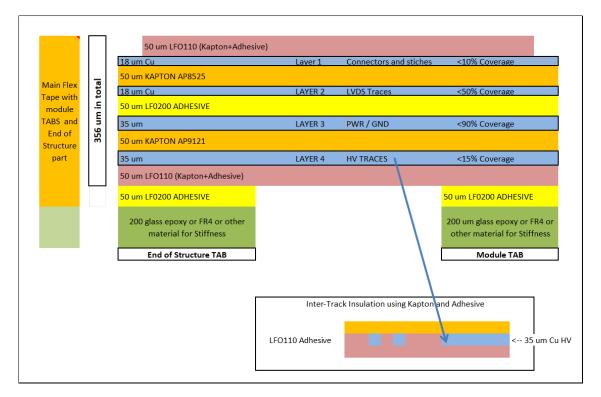

| 5.21  | Test PCBs for testing the Crescent Tape                                                                                   | 98       |

| 5.22  | Block diagram showing the connections between the network analyser, Cres-                                                 |          |

|       | cent Tape and the different test boards                                                                                   | 99       |

| 5.23  | Bench setup for characterising the Crescent Tape.                                                                         | 99       |

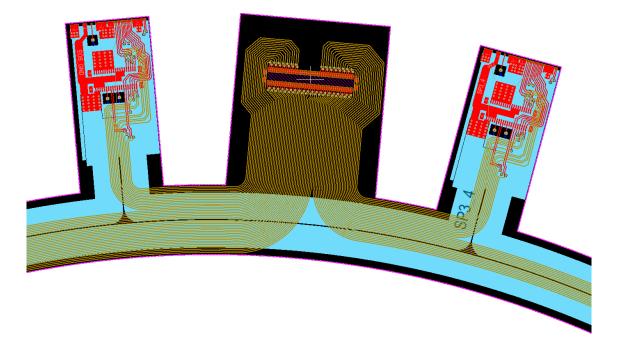

| 5.24  | Layout of part of the Crescent Tape showing the different layers                                                          | 100      |

| 5.25  | Setup for connecting an example signal under test. In this case TAB1-CMD                                                  |          |

|       | signal                                                                                                                    | 101      |

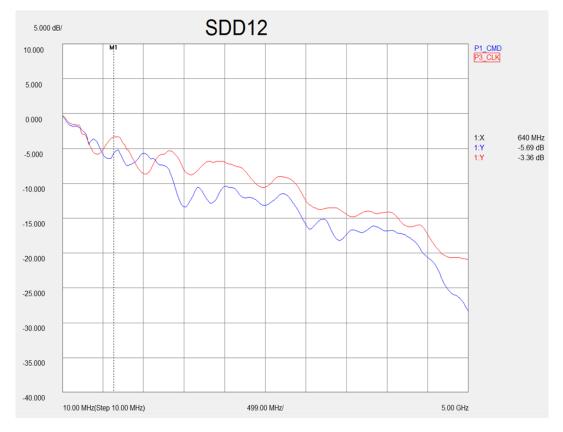

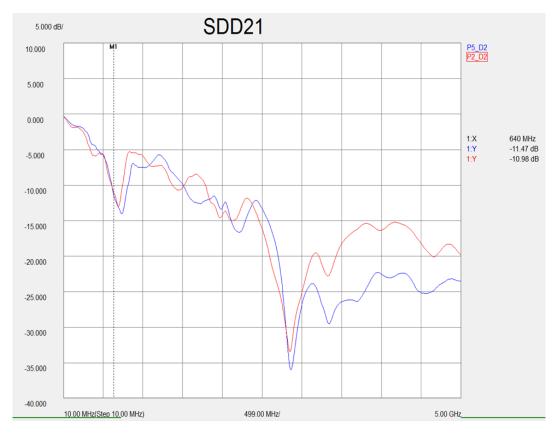

| 5.26  | Plot showing the S-parameter comparison for the for P1-cmd and P3-clk signals                                             | 102      |

| 5.27  | Impedance plots for the for P1-cmd and P3-clk signals on (pseudo) TDR on                                                  |          |

|       | the network analyser                                                                                                      | 103      |

| 5.28  | Plot showing the S-parameter comparison for the P2-D2 and P5-D2 signals.                                                  | 104      |

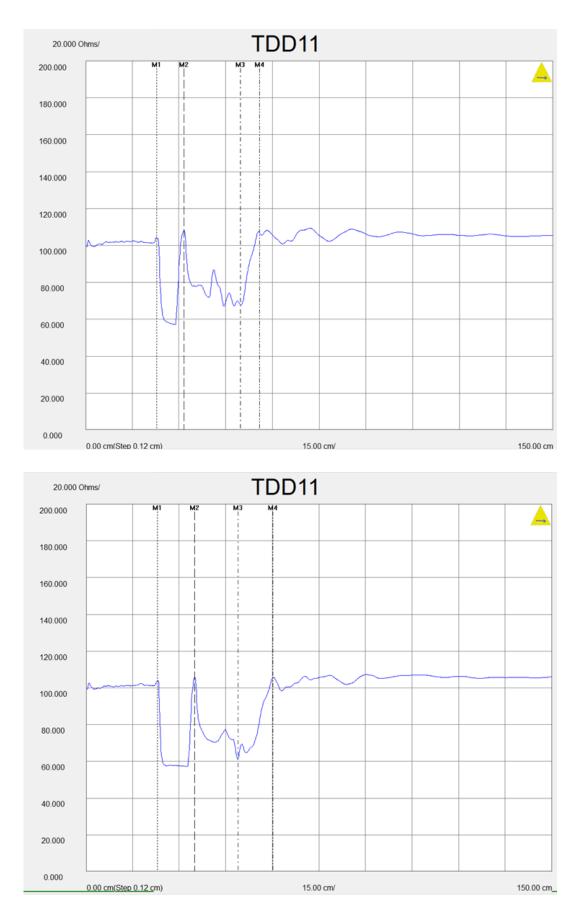

| 5.29 | Impedance plots for the for P2-D2 and P5-D2 signals on (pseudo) TDR on the |     |

|------|----------------------------------------------------------------------------|-----|

|      | network analyser.                                                          | 106 |

# Chapter 1

## Introduction

### 1.1 The Large Hadron Collider

The Large Hadron Collider [1] (LHC) is the world's largest and most powerful particle accelerator. It first started up on 10 September 2008, and remains the flagship of the CERN's (The European Organization for Nuclear Research) accelerator complex located in Geneva. The LHC consists of a 27-kilometre ring of superconducting magnets with a number of accelerating structures to boost the energy of the particles along the way. A view of the inside of the LHC tunnel is shown in Figure 1.1. Inside the accelerator, two high-energy particle

Figure 1.1: A view inside the Large Hadron Collider (LHC) Tunnel [2].

beams travel at close to the speed of light before they are made to collide. The beams travel in opposite directions in separate beam pipes, in two tubes kept at ultrahigh vacuum. They are guided around the accelerator ring by a strong magnetic field maintained by superconducting electromagnets. The electromagnets are built from coils of special electric cable that operates in a superconducting state, efficiently conducting electricity without resistance or loss of energy. This requires chilling the magnets to -271.3°C, a temperature colder than outer space. For this reason, much of the accelerator is connected to a distribution system of liquid helium, which cools the magnets, as well as to other services.

The LHC has thousands of magnets of different varieties and sizes that are used to direct the beams around the accelerator. These include; 1232 dipole magnets 15 metres in length which bend the beams, and 392 quadrupole magnets, each 5-7 metres long, which focus the beams. Just prior to collision, another type of magnet is used to focus the particles closer together to increase the chances of collisions. The particles are approximately of radius of  $10^{-15}$  m and the task of making them collide is analogous to firing two needles 10 kilometres apart with such precision that they meet halfway. All the controls for the accelerator, its

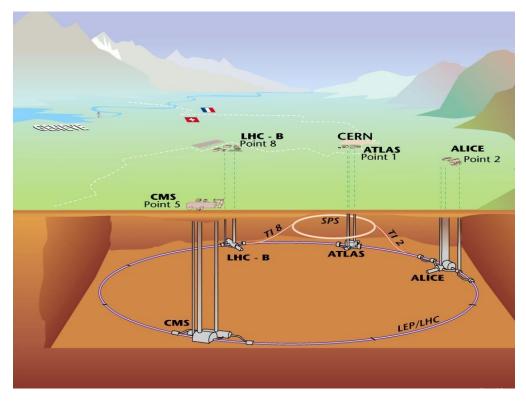

Figure 1.2: Sketch of the LHC ring and the four experiments. The beams are injected in the LHC from the Super Proton Synchrotron (SPS) at an energy of 450 GeV [7].

services and technical infrastructure are housed under one roof at the CERN Control Centre. From here, the beams inside the LHC are made to collide at four locations around the accelerator ring, corresponding to the positions of four physics experiments - ATLAS [3], CMS [4], ALICE [5] and LHCb [6] as shown in Figure 1.2. The LHC represents for the experiments both an unprecedented possibility to study physics at the TeV scale, as well as an extreme experimental environment. To satisfy the requirements for precision measurements, as well as to cope with high interaction rates, radiation doses, particle multiplicities and energies, these experiments have to be carefully designed.

After the consolidation of the electrical splices between the superconducting magnets in the Long Shutdown 1 (LS1), the LHC has operated in Run 2 at 13 TeV centre-of-mass

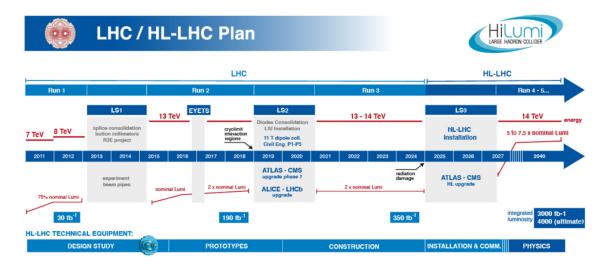

energy from 2015 and has progressively increased the luminosity attaining the nominal design luminosity of 1 x  $10^{34}$  cm<sup>-2</sup>s<sup>-1</sup> in 2016. Despite a reduced number of bunches (about 2200 cf. 2800 nominal) a peak luminosity up to  $1.2 \ge 10^{34} \text{ cm}^{-2} \text{s}^{-1}$  has been routinely obtained in 2016. This peak is largely thanks to reduced emittance from the injectors and a beta [8] value of 40 cm (cf. 55 cm nominal value) at the high luminosity interaction points. In the period 2017-2023 the LHC will hopefully further increase the peak luminosity and margins in the design of the nominal LHC are expected to allow about two times the nominal design performance. After Run 3 the statistical gain in running the accelerator without a significant luminosity increase beyond its design and ultimate values will become marginal. The running time necessary to halve the statistical error of a given measurement after 2020 will be more than ten years. Therefore, to maintain scientific progress and to exploit its full capacity, the LHC will need to have a decisive increase of its luminosity after 2020. A subsequent major luminosity upgrade to High Luminosity (HL-LHC) will make it possible to study the data produced in more detail by increasing the number of collisions by a factor of between five and seven. This upgrade together with focused research and development activities would boost the potential for physics discoveries after 2025. The LHC schedule and timelines are as shown in Figure 1.3.

Figure 1.3: The LHC Schedule overview [9].

#### **1.2** The LHCb Detector - The first version

The Large Hadron Collider beauty (LHCb) experiment [10] is a single arm spectrometer aimed at measuring  $CP^1$  [11] violation and rare decays of beauty (b) and charm (c) quarks,

$<sup>^{1}</sup>$ CP violation, in particle physics, is a violation of the combined conservation laws associated with charge conjugation (C) and parity (P) by the weak force, which is responsible for reactions such as the radioactive decay of atomic nuclei.

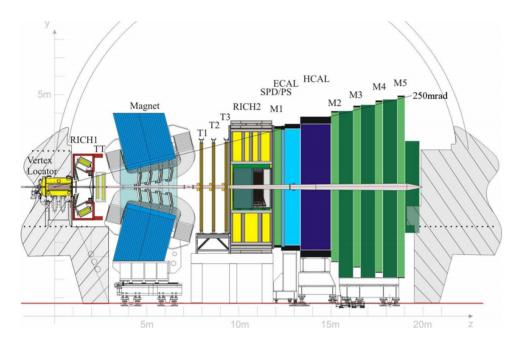

collectively known as heavy flavour hadrons (to include both the b and c physics programme, and baryons). The experiment's 5,600 tonne detector is specifically designed to reconstruct these particles and the products of their decay. The detector is 21 metres long, 10 metres high and 13 metres wide, and sits 100 metres below ground near the village of Ferney-Voltaire, France. About 27% of the bb quark pairs produced are in the LHCb acceptance and predominantly close to the beam axis which is reflected in the design of the detector. Other LHC experiments surround the entire collision point with layers of sub-detectors, but the LHCb detector stretches for 20 metres along the beam pipe, with its sub-detectors stacked behind each other. Each one of LHCb's sub-detectors specializes in measuring a different characteristic of the particles produced from the proton collisions. The system is designed to detect all the particle types produced except for neutrinos as they are so weakly interacting and their presence is inferred if the energy of the detected particles is less than the colliding ones. Collectively, the detector's components gather information about the identity, trajectory, momentum and energy of each particle generated, and can single out individual particles from the billions per second that spray out from the collision point. Figure 1.4 shows the schematic view of the LHCb detector showing the different sub-systems that are explained here.

Figure 1.4: Schematic view of the LHCb Present detector. VELO = Vertex Locator; RICH1,2 = Ring Imaging Cherenkov detectors; TT= Tracker Turicensis; T1, T2, T3 = Tracking stations; SPD/PS = Scintillating Pad Detector/Preshower; ECAL = Electromagnetic Calorimeter; HCAL = Hadron Calorimeter; M1, M2, M3, M4, M5 = Muon stations 1 to 5. [6].

The (High Rapidity Shower Counters) HeRSCheL detector : This detector is located not in the LHCb cavern but in the LHC tunnel itself, on both sides of the LHCb

interaction point. The HeRSCheL system comprises three stations at negative z, known as backward or 'B' stations, and two stations at positive z, known as forward or 'F' stations. The station closest to the interaction point, named 'B0', is located at  $z \sim 7.5$  m and the most distant stations, 'B2' and 'F2', are located at  $\sim \pm 114$  m, close to the point at which the beam pipe splits into two, one for each beam. The detector was built during 2014 and installed at the beginning of 2015 with the goal of enhancing studies of diffractive physics at LHCb. It consists of twenty square plastic scintillators, about 30 cm wide, in which tiny flashes of light are produced when a charged particle passes through. The scintillators are placed at a distance of only centimeters from the LHC beam, just outside the vacuum pipe, and can therefore be used to detect activity corresponding to particles produced by a particle collision in the main LHCb detector but whose deviation from the beam direction is so small that they escape down the beam-pipe and only emerge further along the tunnel, near the HeRSCheL detectors. This ability to detect particles at such small angles is crucial for a particular set of measurements made by physicists enhancing LHCb's capabilities in diffractive physics -in particular Central Exclusive Production (CEP) analyses [12]. These measurements revolve around the study of proton-proton interactions where rather than colliding head-on, the interacting protons merely glance off each other and, in doing so, produce a very small number of particles that can be detected using the standard LHCb detectors and should not lead to activity in HeRSCheL.

**The Vertex Locator** : The LHC proton beams pass through the full length of the detector, safely encased within a beryllium pipe. The only point where the beams collide, and particles containing b and anti-b quarks are produced, is inside the Vertex Locator (VELO) subdetector [13, 14]. The VELO reconstructs the production and decay vertices of the particles produced in the collisions. The first version of the VELO detector is manufactured with 84 single-sided radial (R) and azimuthal-angle ( $\phi$ ) measuring strip sensors operated in a secondary vacuum inside the LHC beam pipe. The R and  $\phi$  sensors are mounted on either side of a highly thermally conductive spine which also supports the readout hybrid, and the resulting double sided module is supported on a carbon fibre paddle stand. The modules are arranged perpendicularly to the beam along a length of about 1 m. Module cooling is provided by evaporative CO<sub>2</sub> circulating in stainless steel pipes embedded within aluminum pads which are clamped to the base of the module. The detector is divided into two moveable halves, allowing it to retract during LHC injection. The cabling between the modules and detector hood must be flexible enough to absorb these movements, which occur for every LHC fill. LHCb differs from the other experiments in that a VELO is inserted inside a vacuum tank [15] around the interaction point, separated from the beam vacuum by a 300  $\mu$ m thin aluminum foil (RF foil). In the beam pipe region the material is corrugated in such a manner as to reduce as much as possible the material traversed by particles before their first measured point. Additional corrugations are provided in order to allow the two sides of the VELO to close completely, ensuring full geometrical coverage with a small overlap added for alignment purposes.

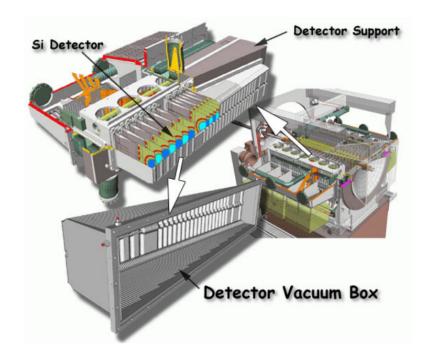

The arrangement of the array of VELO modules within the vacuum tank is shown in Figure 1.5.

Figure 1.5: Layout overview of the first version of the VELO detector, illustrating the vacuum tank, module positioning and RF foil. For the upgrade it will be necessary to change the modules, foil, module bases, and detector hoods, in addition to major refurbishment of the motion, vacuum and cooling system [16].

The vacuum tank and stand, which together represent a significant fraction of effort and investment in the construction of the current VELO, can be reused for the upgrade, along with the rectangular belows which allow the movement of the two halves. The concept of the mixed phase  $CO_2$  cooling system will be re-used for the design of the new cooling system for the upgrade.

**Ring Imaging Cherenkov (RICH) Detectors** : The two detectors (RICH-1 and RICH-2) [17] positioned on either side of LHCb's powerful magnet, are positioned for particle identification in different ranges of momenta. The RICH detectors work by measuring emissions of Cherenkov radiation. This phenomenon, often compared to the sonic boom produced by an aircraft breaking the sound barrier, occurs when a charged particle passes through a certain medium (in this case, a dense gas) faster than light does in that medium. As it travels, the particle emits a cone of light, which the RICH detectors reflect onto an array of sensors using mirrors. The opening angle of the cone of light depends on the particle's velocity, enabling the detector to determine its speed. This information is then combined with a record of its trajectory (collected using the tracking system and a magnetic field) to test and see which of the possible mass hypothesis (for kaons, pions, protons, etc) best match the observed Cherenkov rings.

**Tracking system** : The principal task of the tracking system is to provide efficient reconstruction of the charged particle tracks. The main tracking system comprises four tracking stations: one station (TT) is located between RICH-1 and the LHCb dipole magnet, while the other three stations (T1-T3) are located between the magnet and RICH-2. Two different detector technologies are employed in each tracker station. The silicon tracker [18], which is placed close to the beam pipe, uses silicon microstrip detectors to detect passing particles. Charged particles collide with silicon atoms, liberating charge carriers and creating an electric current, which indicates the passage of the original particle. It comprises the entire TT station and a cross-shaped area (the Inner Tracker) around the beam pipe in stations T1-T3. The outer tracker [19] is situated further from the beam pipe and is made up of thousands of gas-filled straw tubes. Whenever a charged particle passes through, it ionizes the gas molecules, producing electron-ion pairs. The position of the track is found by timing how long the electrons take to reach an anode wire situated in the centre of each tube. The outer tracker covers the largest fraction of the detector sensitive area in stations T1-T3. Silicon is more expensive per unit area but gives a better position resolution than the gas-filled straw tubes. The gas straw tube technology has a coarser resolution than the silicon detectors but is much cheaper and therefore very well suited to cover the large areas of the tracking system where particle densities are not as high. As the best resolution is required closer to the beam pipe the optimal performance-to-cost is obtained with the described arrangement of the tracker technologies.

**Magnets** : To help identify the explosion of particles produced when protons are smashed together, particle detectors typically include a powerful magnet. The charged particles experience a Lorentz force from the magnetic field and their trajectory is therefore bent. Particles with opposite charge polarity are bent in opposite directions and the amount of the deflection is determined by the particle's momentum and charge. This gives valuable information about the particle to allow it to be identified in combination with the sub-detectors. The experiment's enormous magnet consists of two coils, both weighing 27 tonnes, mounted inside a 1,450 tonne steel frame. Each coil comprises 15 individual monolayer 'pancakes' of trapezoidal racetrack shape, and bent at 45 degrees on the two traverse sides. Each pancake consists of 15 turns of conductor, wound from 300 m length of extruded aluminium.

**Calorimeters** : The calorimeters measure the energy a particle loses as it passes through the detector. It is usually designed to stop entirely or 'absorb' most of the particles coming from a collision, forcing them to deposit all of their energy within the detector. Calorimeters typically consist of layers of 'passive' or 'absorbing' high-density material, for example, lead, interleaved with layers of an 'active' medium such as solid lead-glass or liquid argon. The Calorimeter is composed of an electromagnetic calorimeter (ECAL), followed by a hadron calorimeter (HCAL), and before both of them there is a double detector made of three layers, the Scintillator Pad Detector (SPD), a 2.5 radiation lengths lead wall, and the Preshower (PS). The SPD/PS system helps the calorimeter to achieve good background rejection and reasonable efficiency on the detection of photons with reasonable precision. Electromagnetic calorimeters measure the energy of electrons and photons as they interact with matter. Hadronic calorimeters sample the energy of hadrons (particles that contain quarks, such as protons and neutrons) as they interact with atomic nuclei. Calorimeters can stop most known particles except muons and neutrinos.

LHCb uses both types of Calorimeter [20] with the ECAL followed by the HCAL. Both calorimeters have a sandwich-like structure, with alternating layers of metal and plastic scintillator plates. When particles hit the metal, they produce showers of secondary particles. These, in turn, excite polystyrene molecules within the plastic plates, which emit ultraviolet light. The amount of ultraviolet light produced is proportional to the energy of the particles entering the calorimeter.

**Muon system** : Muons are particles that usually pass through the Inner Detector and Calorimeter undetected. They are tiny, electron-like particles that are present in the final stages of many heavy flavour hadron decays, and so muon detection is important for the LHCb experiment. Muons are weakly interacting and as such are not stopped by the calorimeter system unlike the majority of the other particles produced (except for neutrinos). Located at the far end of the detector, the muon system [21] comprises five rectangular 'stations', gradually increasing in size and covering a combined area of 435 m<sup>2</sup>. Each station contains chambers filled with a combination of three gases: carbon dioxide, argon, and tetrafluoromethane. The passing muons deposit energy in the gas,ionising it and wire electrodes detect the results. In total, the muon system contains around 1,400 chambers and some 2.5 million wires.

### 1.3 LHCb Upgrade and the Vertex Locator (VELO)

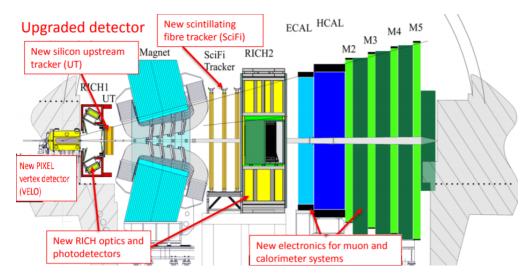

The development towards an upgrade of the LHCb detector are ongoing and installation will be completed in 2020. All LHCb sub-detectors at the upgrade will face increased occupancies and rates due to the increase in luminosity. Some of the sub-systems will see a change or upgrade to work with this increase in luminosity. The Tracker Turicensis (TT) will be replaced with a silicon strip tracker called the Upstream Tracker (UT) while the tracker T1T3 will be replaced with Scintillating Fibre (Sci-Fi) trackers. The RICH detectors will have new photodetectors and front-end electronics and RICH1 optics and mechanics will also see changes. The Calorimeter system will have an updated front-end electronics with the removal of the Scintillating Pad Detector/Preshower (SPD/PS). Finally, the Muon system will as well see an upgrade to the front-end electronics and M1 will be removed. The schematic sideview of the Upgrade I detector highlighting the changes that will be implemented is shown in Figure 1.6.

Figure 1.6: The schematic side-view of the Upgrade I detector. The figure highlights the changes that will be seen in the different sub-systems [22].

The upgraded VELO will comprise of a lightweight hybrid pixel detector with a triggerless system reading out the full detector at 40 MHz. The luminosity will increase to 2 x  $10^{33}$  cm<sup>-2</sup>s<sup>-1</sup>, which is a factor of five larger than at present. The comparison of the beam conditions for the current and the best estimates at the upgrade, which have been used in the simulation studies, are given in Table 1.1.

|                                          | LHCb                                                 | LHCb Upgrade                                  |

|------------------------------------------|------------------------------------------------------|-----------------------------------------------|

| Beam Energy                              | 7 TeV, 8 TeV, 13 TeV                                 | 14 TeV                                        |

| Number of bunches colliding at LHCb      | 2200                                                 | 2400                                          |

| Luminosity                               | $4 \text{ x } 10^{32} \text{ cm}^{-2} \text{s}^{-1}$ | $2 \ge 10^{33} \text{ cm}^{-2} \text{s}^{-1}$ |

| # visible interactions per crossing      | 1.7                                                  | 5.2                                           |

| z RMS luminous region $\sigma_{\rm tot}$ | $55 \mathrm{mm}$                                     | 63 mm                                         |

Table 1.1: Overview of global LHCb and LHCb Upgrade settings for simulations.

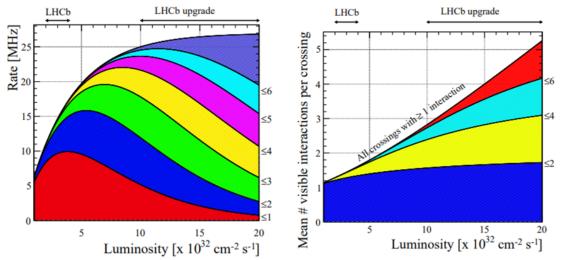

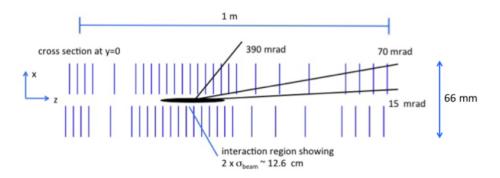

Of particular relevance to the VELO are the z RMS of the beam and the crossing angle, which together determine the extent of the luminous region in z in LHCb to be around  $\sigma_{\text{lumi}} =$ 63 mm. This affects the number of stations which must be distributed around the interaction region, and also has an influence on the minimum aperture available at LHCb. Another important parameter is the number of bunches colliding at the LHCb location (IP8), which has been put at a conservative 2400 bunches, but the expectations are to achieve the maximum possible 2622 bunches, which will slightly ease the occupancy situation at LHCb. The VELO upgrade performance has been evaluated for these conditions, corresponding to  $\mu$  (number of visible interactions per crossing) = 5.2. However, in order to understand the robustness of the system and to take into account the possibility of less favourable filling schemes, larger multiplicities than expected and increased numbers of secondaries the behaviour has been explored for higher data rates and number of primary vertices. The evolution of the interaction rates as the luminosity increases is shown on the left hand side of Figure 1.7.

Figure 1.7: Left - Evolution of interaction rates in LHCb (assuming 25 ns spacing) as a function of luminosity, split into categories of number of interactions per event shown on the right axis and colour coded as: red $\leq=1$ , blue $\leq=2$ , green $\leq=3$ , yellow $\leq=4$ , magenta $\leq=5$ , cyan $\leq=6$ , indigo>6. A significant increase in pile-up is visible when going from 1 to 2 x  $10^{33}$  cm<sup>-2</sup>s<sup>-1</sup>. Right - Average number of pp (proton-proton) interactions per bunch crossing visible in LHCb as a function of luminosity, for events with at least one visible interaction. [16].

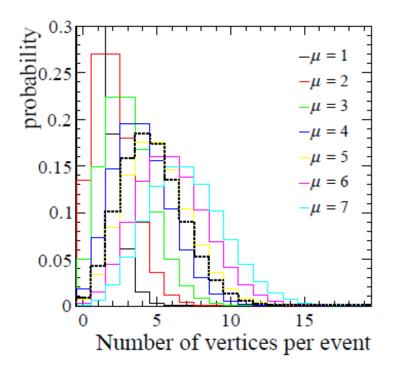

The right hand side of the figure shows the mean number of interactions per bunch crossing in LHCb. The collision rate is 40 MHz with a 25 ns spacing. However the bunches are not evenly spread but come in trains and there are gaps between them. In total there are 3564 'buckets', 25 ns apart in one full turn of the machine (which takes 89  $\mu$ s). The plan is for a filling scheme where 2400 of these are filled, which gives an interaction rate of 2400/3564 \* 40 MHz = 26.9 MHz which is the maximum seen in Figure 1.7 (left). Hence during the bunch trains, it is 40 MHz, but averaged over time it is less depending on the filling scheme. The instantaneous and average collision rates are both relevant for the readout and hence justifies the need of buffers to average out the rates. The displayed average rate being different from the instantaneous rate which can be as high as 40 MHz, which is the peak value used in the estimation of data rates. The expected distribution of the number of vertices per event visible in LHCb is shown in Figure 1.8. At the upgrade ( $\mu \sim 5.2$ ) the number of empty events is almost eliminated, in contrast to the situation in current running ( $\mu \sim 1.7$ ).

Figure 1.8: Number of vertices per event for running at various values of  $\mu$  (# of visible interactions per bunch crossing). The default value used in the simulation, corresponding to  $2 \ge 10^{33} \text{ cm}^{-2} \text{s}^{-1}$ , is indicated by the dotted line. [16].

As explained above, the upgraded VELO must maintain or improve its physics performance while delivering readout at 40 MHz in the operating conditions of the upgrade. This can only be achieved by a complete replacement of the silicon sensors and electronics. Following an externally refereed review, the collaboration has chosen to install a detector based on hybrid pixel sensors [13]. A new radiation hard ASIC called the VeloPix [23] capable of coping with the data rates is developed and is being tested. The module cooling system is being designed to protect the tip of the sensor from thermal runaway effects after significant irradiation, and to cope with the high-speed pixel ASIC power dissipation and for this reason, the upgrade cooling is integrated within the module, in contrast to the currently installed detector. The cooling is provided by  $CO_2$  circulating within miniature channels etched into thin silicon substrates which form the backbone of the modules [24]. The upgraded VELO reuses large parts of the current mechanical infrastructure, in particular the vacuum tank, and elements of the very successful mixed phase  $CO_2$  cooling system.

The conceptual layout of the VELO Upgrade detector within the LHCb coordinate system is shown in Figure 1.9. It is very similar to the current VELO layout, however the z positions of the modules have been changed in order to reach similar acceptance given the smaller module size and smaller distance from the beam line to the first measured point. The positions of the modules in the closed (LHC stable beam operation) position along with the

Figure 1.9: The conceptual layout of the VELO Upgrade detector within the LHCb coordinate system [16].

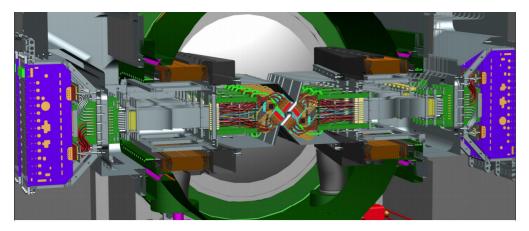

other components of the On-detector electronics is shown in Figure 1.10. In contrast to the current VELO no additional overlap is needed as due to the non projective L-shape geometry of the modules approximately 10% of tracks traverse both the left and right side, and can be used to align the sides. The reconstruction speed and precision of the detector is enhanced by this L-shaped pixel geometry and the distance from the beam to the first sensitive pixel is decreased from 8 mm to 5.1 mm.

Figure 1.10: View of the Upgrade VELO system in closed position showing the 2 modules with L-shaped geometry at the centre, close to the beam. Also seen are the data tapes, Vacuum Feedthrough Board (VFB) and the Opto Power Board (OPB) that make up the On-detector electronics [25].

### 1.4 ATLAS - The present System

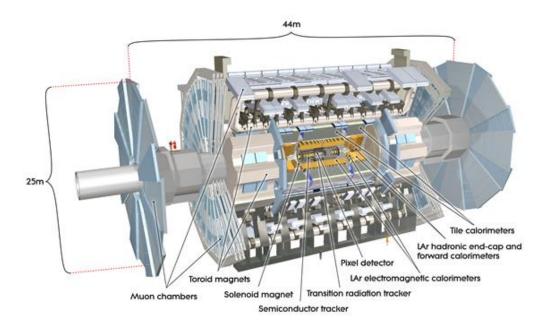

The ATLAS (A Toroidal LHC ApparatuS) [26] experiment at the LHC is designed with the primary goal of probing pp collisions at high luminosity and in order to maximize the potential for the discovery of physics beyond the standard model. Large acceptance in pseudo rapidity with almost full azimuthal angular coverage is required along with high detector granularity needed to handle the particle fluxes and to reduce the influence of overlapping events. Detector elements, such as electronics and sensors, should be fast and radiation-hard to survive in the LHC environment during the entire experiment lifetime. Different detector sub-systems should then assure a good charged particle momentum resolution and track reconstruction efficiency, as well as electron identification, and measurement of secondary vertices for identification of  $\tau$ -leptons and heavy quarks. In addition, a highly efficient trigger for particles at low-pT (low-transverse momentum) thresholds, with sufficient background rejection is needed to achieve an acceptable trigger rate for most physics processes of interest. These specifications have been used in the design of the ATLAS experiment resulting in the layout shown in Figure 1.11.

Figure 1.11: Cut-away of the overall ATLAS experiment showing the various sub-detectors and the two magnet systems [3].

The ATLAS experiment is a  $4\pi$  detector, forward backward symmetric with respect to the interaction point. The detector has a height of 25 m and it is 44 m long, with a total weight of 7000 tonne. The detector is the largest volume particle detector ever constructed and sits in a cavern 100 m below ground near the main CERN site, close to the village of Meyrin in Switzerland. The central detector region is called the barrel, and the two sides are the endcaps. In the ATLAS coordinate system the z-direction is set along the beam axis, while

x and y coordinates are in the transverse plane. Polar coordinates are used in the transverse plane, where the R coordinate describes the radial position from the beam axis, and the  $\phi$ coordinate describes the azimuthal angle. The pseudorapidity describes the angular position with respect to the beam axis, and it is defined as  $\eta = -\ln(\tan(\theta/2))$ , where  $\theta$  is the angle with the beam axis. The detector sub-systems can be seen as concentric cylinders, centered around the beam pipe. Pattern recognition, momentum and vertex measurements, and electron identification are achieved with tracking detectors, that make up the inner detector system, which is immersed in a solenoidal magnetic field of 2 T. The beams of the LHC consist of trains of particle bunches with the minimum time interval between passage of successive bunches within a train being 25 ns. Thus collisions can take place every 25 ns within a time interval determined by the lengths of the bunches, i.e. typically shorter than 1 ns. At an instantaneous luminosity of  $10^{34}$  cm<sup>-2</sup>s<sup>-1</sup> and bunch spacing of 25 ns the average number of interactions is about 23 per bunch-crossing, corresponding to about  $10^9$  interactions per second. A 3-level trigger system [27] is used to convert the 1 GHz interaction rate at design luminosity, to a final data taking rate of approximately 200 Hz. This system provides an overall rejection factor of 5 x  $10^6$  against minimum-bias processes, while maintaining maximum efficiency. The physical event rate from which events must be selected is 40 MHz: the rate at which the beam bunches are delivered to the LHC experiments. The three-level trigger system selects interesting events and cuts down the initial bunch crossing rate of 40 MHz to about 75 kHz at Level-1, to about 3 kHz at Level-2, and to about 200 Hz at the final stage. The different sub-detectors for ATLAS are described here.

**Inner Detector** : The Inner Detector [28] is the first part of ATLAS to see the decay products of the collisions, so it is very compact and highly sensitive. It is the most important detector used in the identification and reconstruction of secondary vertices from the decay of, for example, particles containing a b-quark or for b-tagging of jets. In addition, it provides excellent spatial resolution for reconstructing primary vertices coming from the pp interaction region within ATLAS even in the presence of the multiple interactions at the LHC design luminosity. The Inner Detector measures the direction, momentum, and charge of electricallycharged particles produced in each proton-proton collision. It consists of three different systems of sensors all immersed in a magnetic field parallel to the beam axis. The main components of the Inner Detector are: Pixel Detector, Semiconductor Tracker (SCT), and Transition Radiation Tracker (TRT). The Pixel Detector system [29, 30] is the innermost element of the Inner Detector that comprises the barrel (low-|z| region) in the central area and the endcaps (high-|z| regions) which are, at either ends of the barrel. There are 3 barrel layers (1456 modules) and 3 pixel discs (288 modules) on each side. There are in all 80 million pixels (80 million channels) covering an area  $1.7 \text{ m}^2$  and 15 kW of power consumption. The Semiconductor Tracker (SCT) comprises a silicon microstrip tracker consisting of 4088 twosided modules and over 6 million implanted readout strips. 60 m<sup>2</sup> of silicon is distributed over 4 cylindrical barrel layers and 18 planar endcap discs. The Transition Radiation Tracker (TRT) consists of 350000 read-out channels with a volume of 12 m<sup>3</sup>. It provides additional information on the particle type that fly through the detector i.e. if it is an electron or pion.

**Calorimeter** : The components of the ATLAS calorimetry system are: the Liquid Argon (LAr) Calorimeter and the Tile Hadronic Calorimeter [31,32]. Both the electromagnetic and hadronic calorimeters in ATLAS are at larger radius to the solenoidal magnet that surrounds the Inner Detector.

**Solenoid** : A superconducting solenoid is used to provide the B-field to deflect the charged tracks in the Inner Detector to aid particle identification [33].

**Muon Spectrometer** : The muon spectrometer [34], made up of 4000 individual muon chambers using four different technologies produced by 48 institutions in 23 production sites around the world, identifies and measures the momenta of muons. Subsections of the Muon System comprise Thin Gap Chambers, Resistive Plate Chambers, Monitored Drift Tubes, and Cathode Strip Chambers.

**Magnet system** : The magnet system bends the path of particles as they traverse the various layers of detector systems, making it easier to contain the tracks of particles. The magnet system bends the charged particles due to Lorentz force and from the direction of bend the sign of the charge can be determined while the amount of bend determines the momentum. The main sections of the magnet system are Central Solenoid Magnet, Barrel Toroid and 2 Endcap Toroids [35].

### 1.5 ATLAS - Upgrade and Inner Tracker (ITk)

The ATLAS detector has been assembled over a period of three years. Commissioning started in the second half of 2007, and data taking in 2009 with the first stable beams from the LHC. The detector performed remarkably during the first three years of operation, proving that the chosen design allows to investigate a wide spectrum of physical phenomena at the TeV energy scale in the harsh LHC environment. With the integrated luminosity recorded by the experiment, the ATLAS collaboration discovered a new boson whose properties confirm the hypothesis of a Standard Model (SM) Higgs boson [36]. The detector capability has to be consolidated and improved to maintain the capability of the experiment. This would enhance precision measurements and potential for the discovery of physics beyond the standard model, while meeting the new challenges of operating in a high luminosity environment. No major interventions were made to the detector system during LS1, as during Phase-0 the machine

operated at design parameter, only the pixel detector underwent the first upgrade project. In order to preserve performance strength and efficiency at higher than design luminosity, a new pixel layer, the Insertable B-Layer (IBL) [37], was added at a smaller radius inside the present detector. Insertion of the IBL was done during the first LHC shutdown 1 (LS1), and operation started during run 2 of the LHC, but is still considered Phase-0 of the ATLAS experiment. The Phase-I [38] upgrade of ATLAS concerned mostly an improvement of the trigger system to cope with luminosities higher than the LHC nominal value that will take place in LHC Run 3 from 2021 onwards. In particular the Level-1 trigger upgrade allows the maintaining of low- $p_{\tau}$  thresholds for isolated leptons, as required for precision measurements of the Higgs boson couplings in the low mass region, as well as for searches for supersymmetric (SUSY) particles in a large region of the SUSY parameter space. Improvement of the highlevel trigger leads to more efficient identification of events with isolated  $\tau$  leptons and Bhadrons, improving the selection of Higgs boson decays and the sensitivity to many other physics channels. The detector sub-systems involved in this upgrade are the calorimeters and the muon spectrometer. Phase-II [39] will see a major upgrade of the detector systems. In particular, the increased luminosity requires a new Inner Detector able to cope with the higher rates, higher pile-up, and higher radiation levels. A new all-silicon tracker and a new tracker readout will include the implementation of a track trigger to improve the ATLAS trigger capabilities. New readout systems are also required to maintain the performance of the calorimeters and of the muon spectrometer. Finally, a new trigger architecture will be implemented to exploit the upgrades of the detector readout systems, improving the event selection.

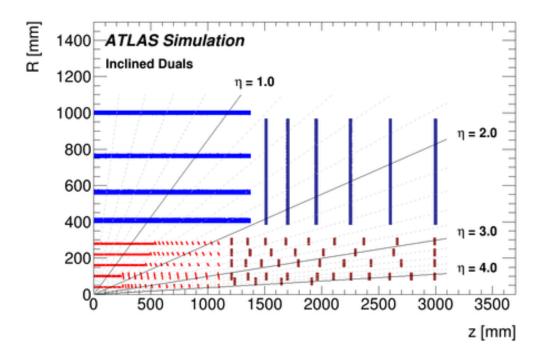

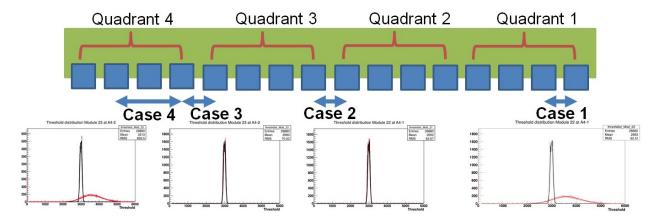

In order to maintain tracking and b-tagging performances in such a track-dense environment, a tracking detector with improved resolution, efficiency, and material budget will be required. Such a tracking detector will also have to cope with the increased radiation damage expected from the integrated luminosity of the High luminosity (HL)-LHC, compared to that of the LHC. The current ATLAS Inner Detector will be heavily radiation-damaged by the time the LHC reaches the end of its intended data-production period thereby requiring replacement. The layout shown in Figure 1.12 is based on one of the candidate layouts described in the Strip TDR called 'Inclined Layout' taken from reference [40]. The Inclined Layout represents a significant evolution compared to the layouts discussed in the ATLAS Phase-II Upgrade Letter of Intent [39] and in the Phase-II Upgrade Scoping document [41]. Like the reference detector layout from the Phase-II Upgrade Scoping document, the detector design presented in the Strip TDR combines precision central tracking in the presence of an average of 200 pile-up events with the ability to extend the tracking coverage to a pseudorapidity of 4 while maintaining excellent tracking efficiency and performance. The ITk comprises two subsystems: A Strip Detector surrounding a Pixel Detector. The Strip Detector has four barrel layers and six endcap petal-design disks, having modules on both sides of each layer

Figure 1.12: Schematic layout of the ITk for the HL (High luminosity)-LHC phase of ATLAS as presented in the Strip TDR [40]. The active elements of the barrel and endcap Strip Detector are shown in blue, for the Pixel Detector the sensors are shown in red for the barrel layers and in dark red for the endcap rings. Here only one quadrant and only active detector elements are shown. The horizontal axis is the axis along the beam line with zero being the interaction point. The vertical axis is the radius measured from the interaction region. The outer radius is set by the inner radius of the barrel cryostat that houses the solenoid and the electromagnetic calorimeter.

with a small stereo angle between the strip orientation to add z (R) resolution in the barrel (endcaps), respectively. The Strip Detector, covering  $|\eta| < 2.7$ , is complemented by a 5 layer Pixel Detector extending the coverage to  $|\eta| < 4$ . The Pixel Detector comprises 5 barrel layers and multiple forward disks. The Pixel and Strip Detector volumes are separated by a Pixel Support Tube (PST). In addition, and because of the harsh radiation environment expected for the HL-LHC, the inner two layers of the Pixel Detector are replaceable. The inner two pixel layers are separated from the outer three layers by an Inner Support Tube (IST), that facilitates a replacement of the inner layers. The combined Strip plus Pixel Detectors provide a total of 13 hits for  $|\eta| < 2.7$ , with the exception of the barrel/endcap transition of the Strip Detector, where the hit count is 11 hits. The Pixel Detector presented in the Strip TDR was designed to supply a minimum of at least 13 hits from the end of the strip coverage in pseudorapidity to  $|\eta|$  of 4. While the Strip Detector remains unchanged and is described in detail in reference [40], the Pixel Detector layout has evolved to further improve the performance, reduce cost and incorporate engineering constraints. With the increase in the instantaneous luminosity to 7 x  $10^{34}$  cm<sup>-2</sup>s<sup>-1</sup>, 2.5-3.5 times larger compared to the end of Phase-1, the pile-up also increases at the same rate and hence pile-up mitigation becomes important to maintain detector performance. Pile-up results in mis-association of the tracks from other collisions making it worse for the jet energy measurement [42]. Pile-up could also occur due to low or uncorrected detector response from particles of the previous bunch crossings. Some of the techniques that are looked into to mitigate the pile up issue [43] are high granularity and thin sensor active region, increase in the number of the tracking layers, removing hits coming from low-pT particles by using the hit pattern in the silicon tracker, and precise timing information to reject out-of-time pile-up.

## Chapter 2

## Methods and Techniques