#### Air Force Institute of Technology

#### **AFIT Scholar**

Theses and Dissertations

Student Graduate Works

3-2006

## Design and Characterization of a Radiation Tolerant Triple Mode Redundant Sense Amplifier Flip-Flop for Space Applications

Mark E. Martin

Follow this and additional works at: https://scholar.afit.edu/etd

Part of the Electrical and Electronics Commons

#### **Recommended Citation**

Martin, Mark E., "Design and Characterization of a Radiation Tolerant Triple Mode Redundant Sense Amplifier Flip-Flop for Space Applications" (2006). Theses and Dissertations. 3495. https://scholar.afit.edu/etd/3495

This Thesis is brought to you for free and open access by the Student Graduate Works at AFIT Scholar. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of AFIT Scholar. For more information, please contact richard.mansfield@afit.edu.

# DESIGN AND CHARACTERIZATION OF A RADIATION TOLERANT TRIPLE MODE REDUNDANT SENSE AMPLIFIER FLIP-FLOP FOR SPACE APPLICATIONS

#### **THESIS**

Mark E. Martin, Second Lieutenant, USAF AFIT/GE/ENG/06-39

## DEPARTMENT OF THE AIR FORCE AIR UNIVERSITY

## AIR FORCE INSTITUTE OF TECHNOLOGY

Wright-Patterson Air Force Base, Ohio

APPROVED FOR PUBLIC RELEASE; DISTRIBUTION UNLIMITED.

| The views expressed in this thesis are those of the author and do not reflect the offi policy or position of the United States Air Force, Department of Defense, or the United States Air Force, Department of Defense, or the United States Air Force, Department of Defense, or the United States Air Force, Department of Defense, or the United States Air Force, Department of Defense, or the United States Air Force, Department of Defense, or the United States Air Force, Department of Defense, or the United States Air Force, Department of Defense, or the United States Air Force, Department of Defense, or the United States Air Force, Department of Defense, or the United States Air Force, Department of Defense, or the United States Air Force, Department of Defense, or the United States Air Force, Department of Defense, or the United States Air Force, Department of Defense, or the United States Air Force, Department of Defense, or the United States Air Force, Department of Defense, or the United States Air Force, Department of Defense, or the United States Air Force, Department of Defense, or the United States Air Force, Department of Defense, or the United States Air Force, Department of Defense Air Force, Depar | icial<br>nited |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| States Government.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |

## DESIGN AND CHARACTERIZATION OF A RADIATION TOLERANT TRIPLE MODE REDUNDANT SENSE AMPLIFIER FLIP-FLOP FOR SPACE APPLICATIONS

#### **THESIS**

Presented to the Faculty

Department of Electrical and Computer Engineering

Graduate School of Engineering and Management

Air Force Institute of Technology

Air University

Air Education and Training Command

In Partial Fulfillment of the Requirements for the

Degree of Master of Science in Electrical Engineering

Mark E. Martin, BS

Second Lieutenant, USAF

March 2006

APPROVED FOR PUBLIC RELEASE; DISTRIBUTION UNLIMITED.

## DESIGN AND CHARACTERIZATION OF A RADIATION TOLERANT TRIPLE MODE REDUNDANT SENSE AMPLIFIER FLIP-FLOP FOR SPACE APPLICATIONS

Mark E. Martin, B.S. Second Lieutenant, USAF

| Approved:                     |                    |

|-------------------------------|--------------------|

| Yong C. Kim (Chairman)        | 15 MAR 106<br>date |

| Ronald F. Tuttle (Member)     | 15 MAR 06 date     |

| Kenneth M. Hopkinson (Member) | 15 MAR 06<br>date  |

#### **ABSTRACT**

One of the more recently proposed flip-flop designs has been the sense amplifier flip-flop. It has gained acceptance in the commercial realm because of its power consumption, speed, setup time, clock line loading, and data line loading characteristics.

In this thesis, a recently designed RADHARD version of D sense amplifier flip-flop was taken and a triple mode redundant version for space and radiation environment use was created. The design was created with valuable options to increase radiation hardness and to give end users greater flexibility in realizing their own radiation hardened version of flip-flop. In addition, a methodology for using a traditional circuit simulation tool, SPICE, was developed to test the operation of the flip-flop design for both normal conditions and under the influence of radiation.

The prescribed level of radiation resilience was chosen to reflect the upper bound of radiation tolerant design which is equivalent to a 100MeV Fe ion interaction with Si.

This work provides the results of the design effort and the characteristics of the final triple mode redundant sense amplifier flip-flop design both as a device which did not utilize any of the options created for use with the design and with various combinations of options employed.

This work also provides information on a revolutionary technology coined by the author (S&IC Technology, Sensor and Integrated Circuit Technology) which when used in conjunction with the triple mode design of this work would realize a self-sensing, self-correcting, and self-repairing triple mode design which would be of immeasurable benefit to space applications, avionics, and terrestrial applications the world over.

## AFIT/GE/ENG/06-39

## **DEDICATION**

To God and Country

## **ACKNOWLEDGEMENTS**

I would like to thank everyone who made this thesis possible.

Mark E. Martin

## **Table of Contents**

| Abstract                                                       | Page |

|----------------------------------------------------------------|------|

|                                                                |      |

| Dedication                                                     | V    |

| Acknowledgements                                               | vi   |

| Table of Contents                                              | vii  |

| List of Figures                                                | X    |

| List of Tables                                                 | xii  |

| List of Acronyms/Abbreviations                                 | xiii |

| I. Introduction                                                | 1    |

| 1.1 Overview                                                   |      |

| 1.2 Motivation                                                 |      |

| 1.3 Problem Statement                                          |      |

| 1.4 Plan of Attack                                             |      |

| 1.5 Contributions                                              |      |

| 1.6 Sequence of Presentation                                   | 4    |

| II. Background Information                                     | 5    |

| 2.1 Overview                                                   | 5    |

| 2.2 TID Effects on Circuits                                    |      |

| 2.3 Causes of SEU's in Circuits                                |      |

| 2.4 Choice of Radiation Tolerant Design                        |      |

| 2.5 Definition of Radiation Tolerant Design                    |      |

| 2.6 Definition of Basic TMR Design                             |      |

| 2.7 Justification For Use of TMR in Flip-Flop Design           | 12   |

| III. Methodology                                               | 16   |

| 3.1 Overview                                                   | 16   |

| 3.2 Background                                                 |      |

| 3.3 Choice of Basic Flip-Flop Technology in the TMRSAFF Design |      |

| 3.4 Choice of Specific Flip-Flop to Use in the TMRSAFF Design  |      |

| 3.5 Basic TMRSAFF Structure                                    |      |

| 3.6 Basic Functionality Determination                          |      |

| 3.7 Basic Timing Parameter Determination                       |      |

| 3.8 Basic Radiation Simulation                                 | 29   |

| 3.9 How TMRSAFF Counters TID Effects                               | 36  |

|--------------------------------------------------------------------|-----|

| 3.10 Radiation Hardening Options for the TMRSAFF Design            |     |

| 3.11 Transistor Sizing                                             | 43  |

| IV. Results                                                        | 47  |

| 4.1 Overview                                                       | 47  |

| 4.2 Summary of TMRSAFF Characteristics in This Work                |     |

| 4.3 Performance Difference for Different Option Usage              | 48  |

| V. Conclusions                                                     | 52  |

| 5.1 Overview                                                       |     |

| 5.2 Conclusion Statement                                           |     |

| 5.3 Applications                                                   |     |

| 5.4 Future Work                                                    | 34  |

| Appendix 1. Basic Functionality Test Vector (D Input)              | 61  |

| Appendix 2. Basic Functionality Test Vector (DB Input)             | 62  |

| Appendix 3. Low Current Barrage Test Vector                        | 63  |

| Appendix 4. High Current Barrage Test Vector                       | 72  |

| Appendix 5. Data Faults Test Vector.                               | 81  |

| Appendix 6. Majority Logic Output High Current Barrage Test Vector | 82  |

| Appendix 7. AMI05 Technology Family Transistor Parameters          | 97  |

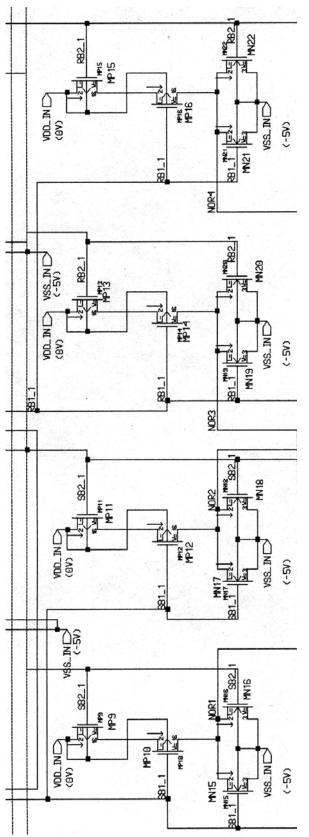

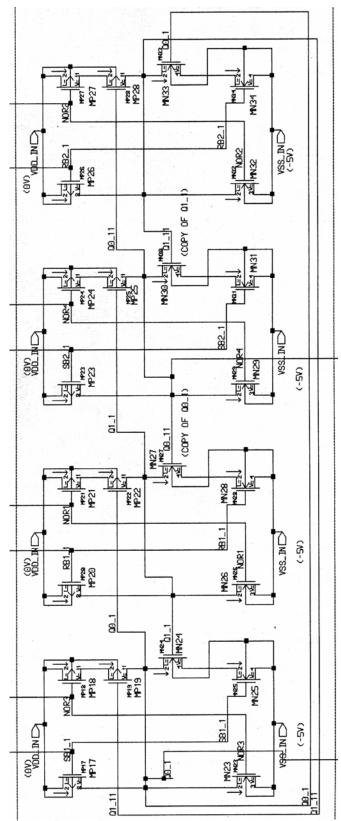

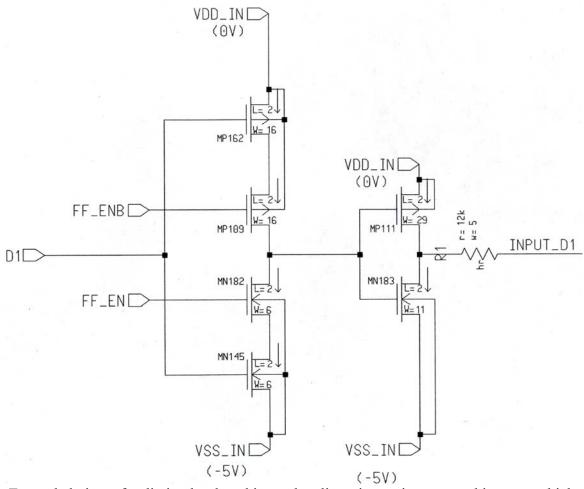

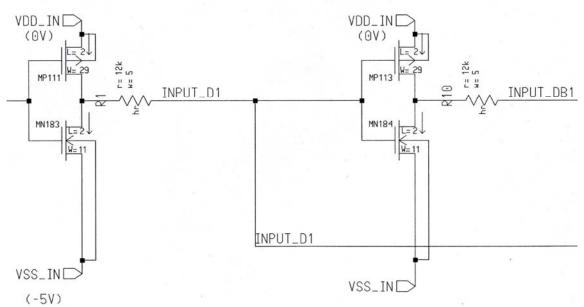

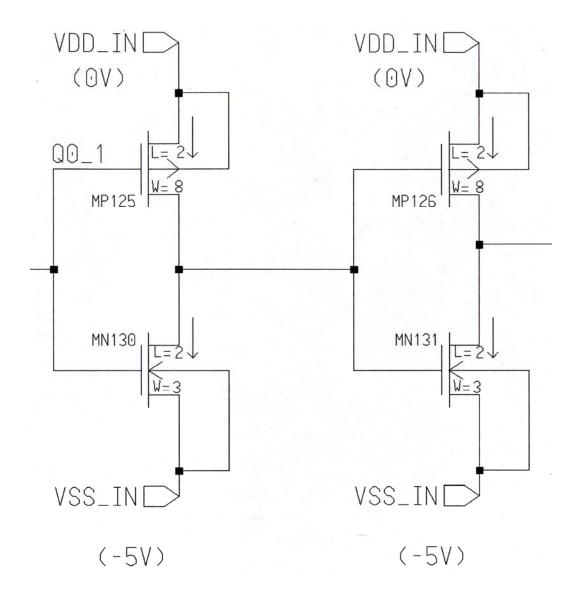

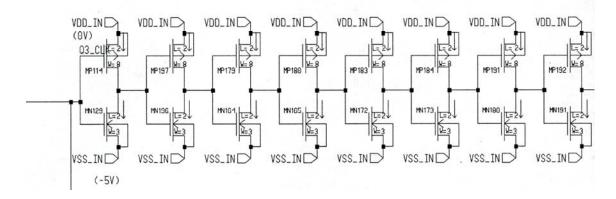

| Appendix 8. Input SAFF Schematics                                  | 99  |

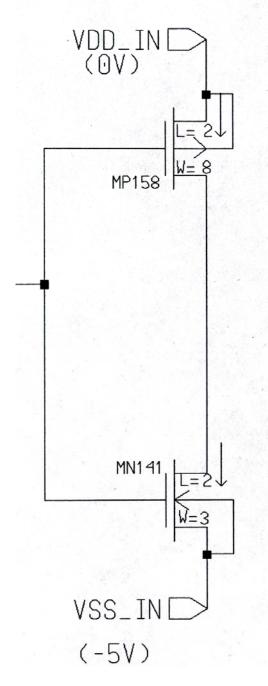

| Appendix 9. Inverter Load Schematic                                | 103 |

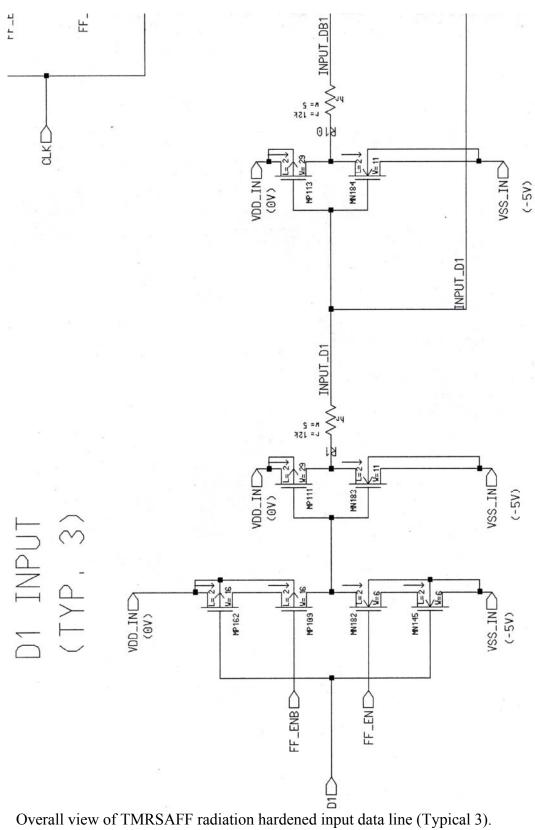

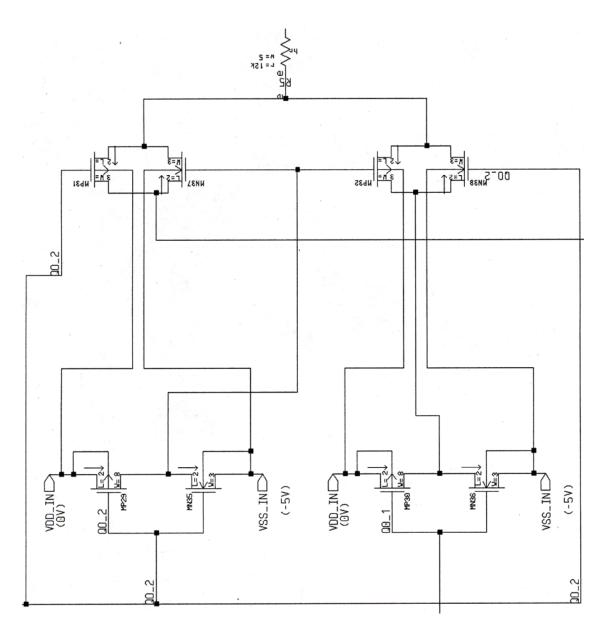

| Appendix 10. Hardened Input Data Line Schematics                   | 104 |

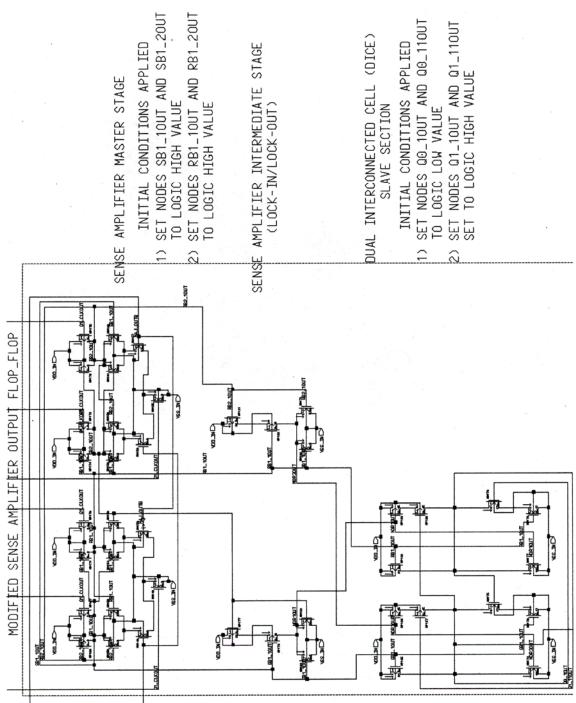

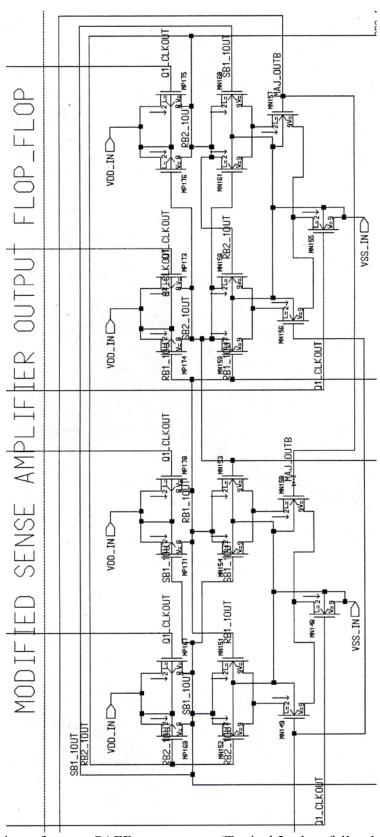

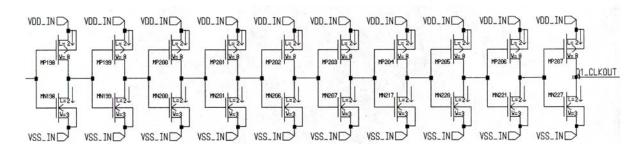

| Appendix 11. Output SAFF Schematics                                | 107 |

| Appendix 12. Hypothetical Output SAFF Schematics                   | 111 |

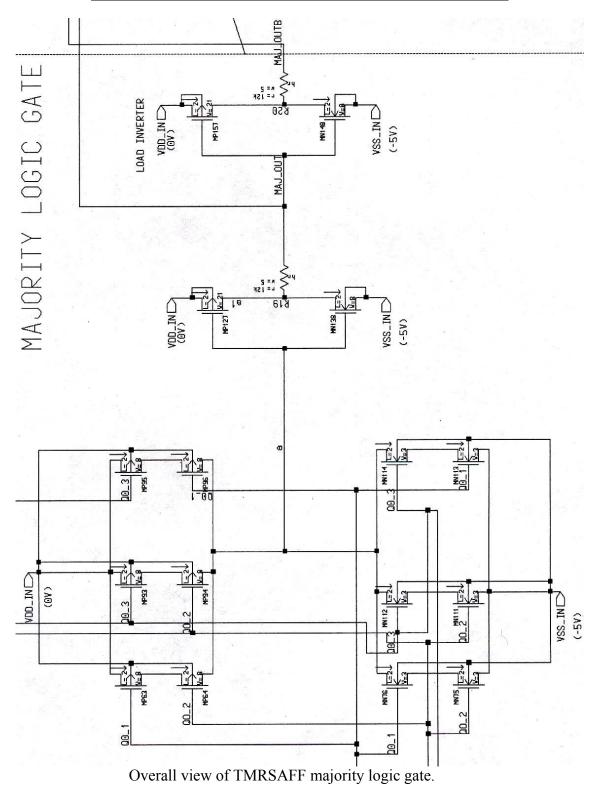

| Appendix 13. Majority Logic Gate Schematics                        | 113 |

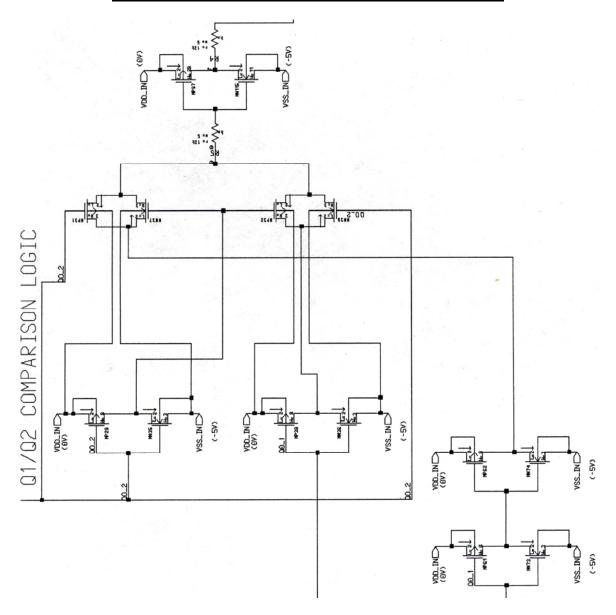

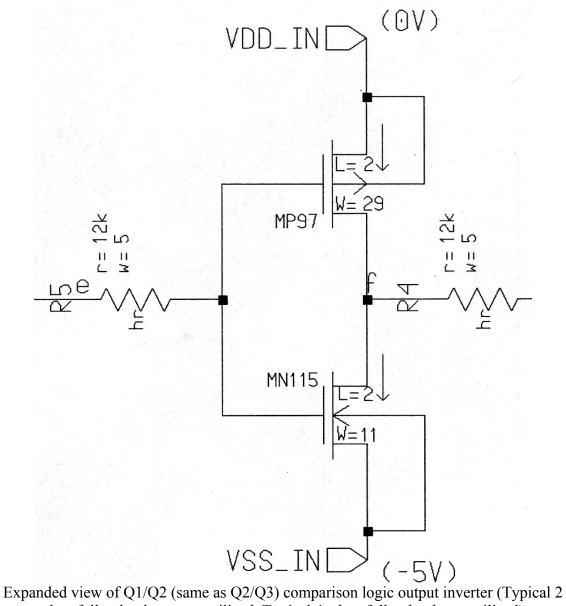

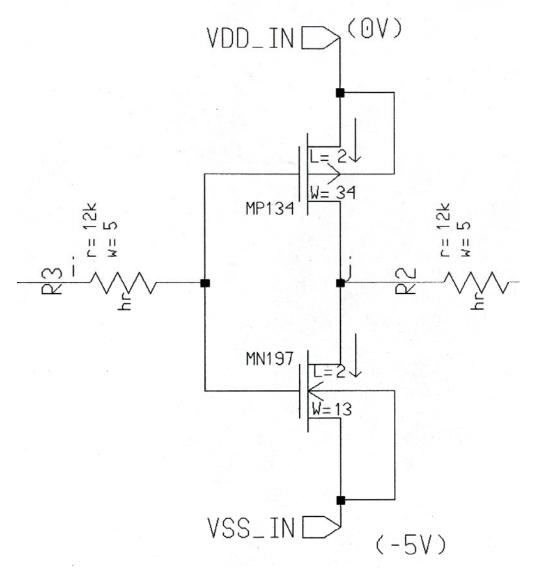

| Appendix 14. Comparison Logic Schematics                           | 114 |

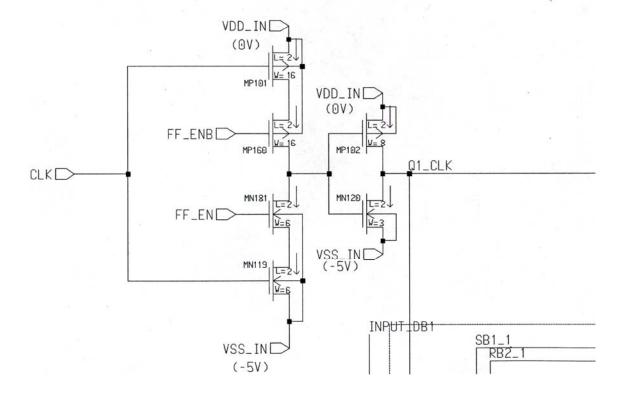

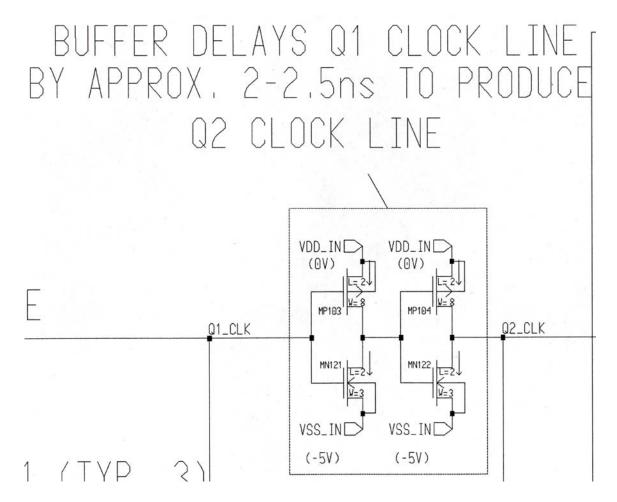

| Annendix 15 Clock Schematics                                       | 119 |

| Appendix 16. | TMRSAFF SPICE Netlist | 122 |

|--------------|-----------------------|-----|

| Bibliography |                       | 134 |

## **List of Figures**

| Figure | Page                                                                                                                                                                                        |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2.1  | Pie chart depiction of the amount of error attributable to static combinational logic, sequential elements and memory regardless of environment                                             |

| 2.2.1  | Formation of a shorting path between the source and drain of an NMOS device                                                                                                                 |

| 2.2.2  | Formation of a shorting path between adjacent NMOS MOSFET's7                                                                                                                                |

| 2.2.3  | NMOS and PMOS transistor threshold voltage shift                                                                                                                                            |

| 2.3.1  | Funnel formation in Si                                                                                                                                                                      |

| 2.3.2  | Electron-micrograph of charged particle interaction with NMOS transistor9                                                                                                                   |

| 2.4.1  | Bar graph representation of radiation design requirments of 225 recent NASA missions                                                                                                        |

| 2.6.1  | Basic TMR block diagram                                                                                                                                                                     |

| 2.7.1  | N-modal flip-flop                                                                                                                                                                           |

| 3.4.1  | Schematic of Wang and Gong SAFF design                                                                                                                                                      |

| 3.5.1  | Basic block diagram of the TMRSAFF design                                                                                                                                                   |

| 3.6.1  | Graph of applied inputs and corresponding output results for running the basic functionality test vector/vectors in checking the performance of the individual flip-flops used in this work |

| 3.7.1  | Basic determination of TMRSAFF clock to Q delay                                                                                                                                             |

| 3.8.1  | Graph of current response of 100MeV Fe ion interaction with an n+/p Si diode using the Dorkel model                                                                                         |

| 3.8.2  | Low current test model                                                                                                                                                                      |

| 3.8.3  | High current test model                                                                                                                                                                     |

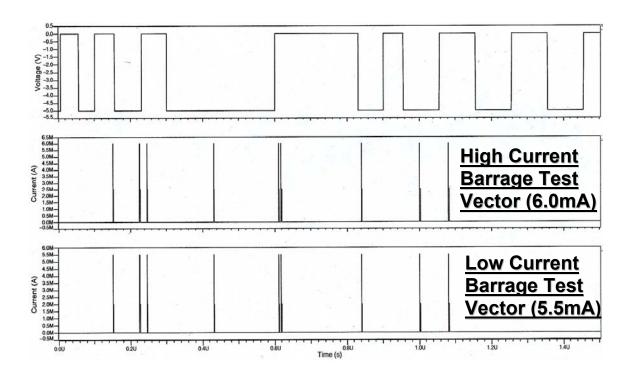

| 3.8.4  | Timing graph showing the application of one high current barrage test vector and its corresponding low current barrage test vector to a node under radiation simulation testing             |

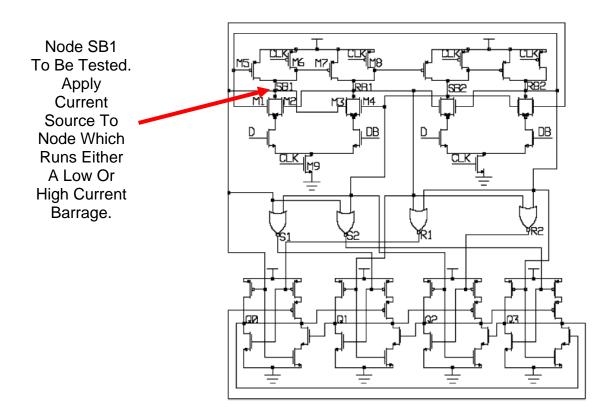

| 3.8.5  | Example node to be tested for radiation hardness                                  | 35 |

|--------|-----------------------------------------------------------------------------------|----|

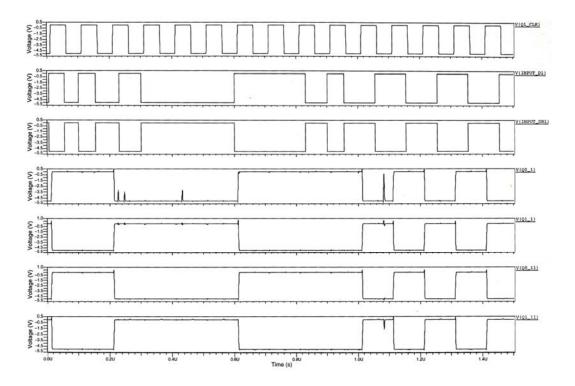

| 3.8.6  | Results of running a low current barrage test vector on node SB1 in Figure 3.8.5  | 35 |

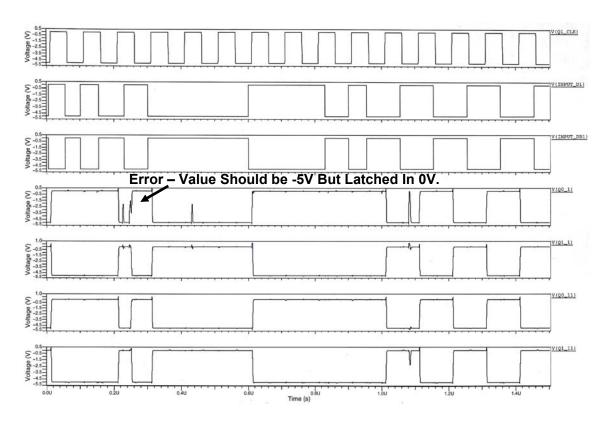

| 3.8.7  | Results of running a high current barrage test vector on node SB1 in Figure 3.8.5 | 36 |

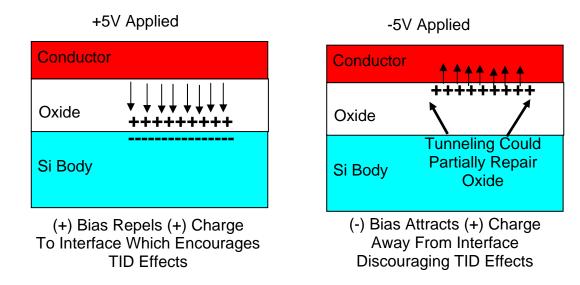

| 3.9.1  | Effects of using either positive or negative bias in circuits                     | 37 |

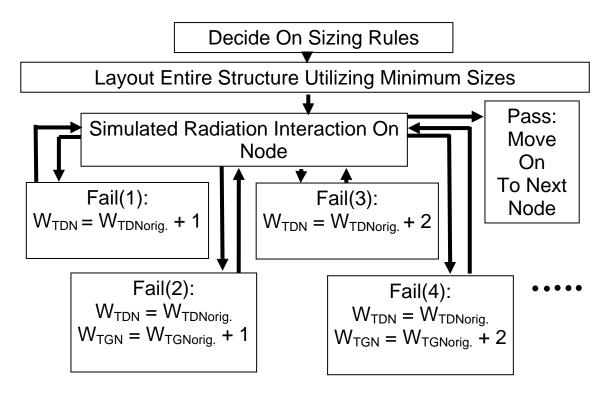

| 3.11.1 | Flow chart of transistor sizing algorithm                                         | 44 |

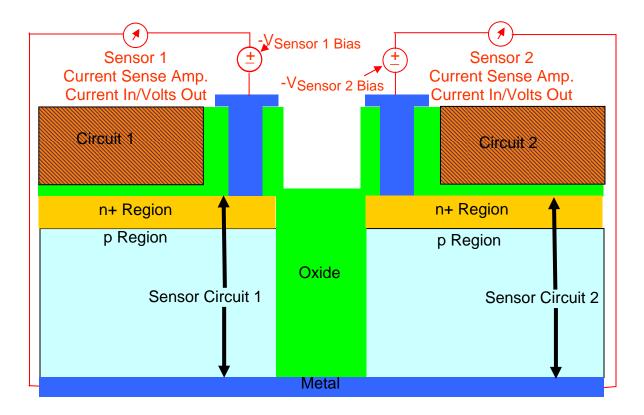

| 5.4.1  | Final S&IC technology formation                                                   | 55 |

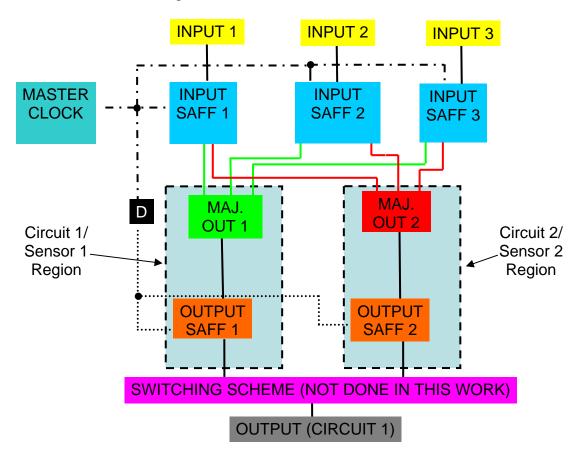

| 5.4.2  | Depiction of S&IC technology with TMRSAFF                                         | 58 |

| 5.4.3  | Depiction of TMRSAFF and S&IC technology after ion interaction                    | 59 |

| 5.4.4  | Self-repairing version of TMRSAFF                                                 | 60 |

## **List of Tables**

| Table |                                                                                                                          | Page |

|-------|--------------------------------------------------------------------------------------------------------------------------|------|

| 2.7.1 | Tabulation of N-modal flip-flop performance parameters                                                                   | 13   |

| 3.3.1 | Tabulation of state of the art flip-flop designs                                                                         | 20   |

| 3.4.1 | Comparison of the Wang and Gong SAFF design to the SAFF design utiliz the ALPHA 21264 space microprocessor               |      |

| 3.4.2 | Comparison of the Wang and Gong SAFF design to basic DICE flip-flop technology                                           | 22   |

| 4.2.1 | Tabulation of TMRSAFF characteristics                                                                                    | 47   |

| 4.3.1 | Tabulation of TMRSAFF design performance as a result of eliminating radhardened majority logic gates                     |      |

| 4.3.2 | Tabulation of TMRSAFF design performance as a result of eliminating radhardened data input lines and data enabling       |      |

| 4.3.3 | Tabulation of TMRSAFF design performance as a result of not using full redundancy                                        | 50   |

| 4.3.4 | Tabulation of TMRSAFF design performance as a result of eliminating ter displacement and clock enabling                  |      |

| 4.3.5 | Tabulation of TMRSAFF design performance as a result of eliminating bo of redundant comparison logics                    |      |

| 4.3.6 | Tabulation of TMRSAFF design performance as a result of eliminating all except for full redundancy and comparison logics |      |

#### List of Acronyms/Abbreviations

AMI American Megatrends Incorporated.

B Boron.

BJT Bipolar Junction Transistor.

C Carbon.

CMOS Complementary Metal Oxide Semiconductor.

Cu Copper.

DICE Dual Interlocked Cell.

DRAM Dynamic Random Access Memory.

E Energy.

EDAC Error Detecting And Correcting.

EHP Electron-Hole Pair.

FDSOI Fully Depleted Silicon on Insulator.

Fe Iron. FF Flip-Flop.

FIT Failures In Time.

GaAs Gallium Arsenide.

Ge Germanium.

He Helium.

High Accuracy Simulation Program with Integrated Circuit

HSPICE Emphasis.

IC Integrated Circuit.

L Length.

LET Linear Energy Transfer.

LSI Large Scale Integration.

Mg Magnesium.

MOSFET Metal Oxide Semiconductor Field Effect Transistor.

NAND not-AND.

Ne Neon.

Ni Nickel.

NMOS N-channel Metal Oxide Semiconductor.

NOR not-OR.

NSREC Nuclear and Space Radiation Effects Conference.

O Oxygen. P Phosphorous.

PDSOI Partially Depleted Silicon on Insulator.

PMOS P-channel Metal Oxide Semiconductor.

RC Resistor-Capacitor.

SAFF Sense Amplifier Flip-Flop.

SEB Single Event Burnout.

SEE Single Event Effects.

SEGR Single Event Gate Rupture.

SEL Single Event Latch-up.

SER Soft Error Rate.

SET Single Event Transient.

SEU Single Event Upset.

Si Silicon.

SiO<sub>2</sub> Silicon Dioxide. SOI Silicon On Insulator.

SPICE Simulation Program with Integrated Circuit Emphasis.

SR Set-Reset.

SRAM Static Random Access Memory.

TID Total Ionizing Dose.

TMR Triple Mode Redundant.

TMRSAFF Triple Mode Redundant Sense Amplifier Flip-Flop.

TSMC Taiwan Semiconductor Manufacturing Company.

$\begin{array}{lll} \alpha\text{-particles} & Alpha\text{-particles}. \\ \beta\text{-particles} & Beta\text{-particles}. \\ \gamma\text{-ray} & Gamma\text{-ray}. \\ \Delta\text{-rays} & Delta\text{-rays}. \\ \rho & Density. \end{array}$

#### DESIGN AND CHARACTERIZATION OF A RADIATION TOLERANT TRIPLE MODE REDUNDANT SENSE AMPLIFIER FLIP-FLOP FOR SPACE APPLICATIONS

#### I. INTRODUCTION

#### 1.1 OVERVIEW

This chapter will go over the following topics:

- 1) Motivation for pursuing the problem to be solved.

- 2) A basic problem statement.

- 3) A basic plan of attack.

- 4) Contributions this work will provide.

- 5) A simple sequence of presentation.

#### 1.2 MOTIVATION

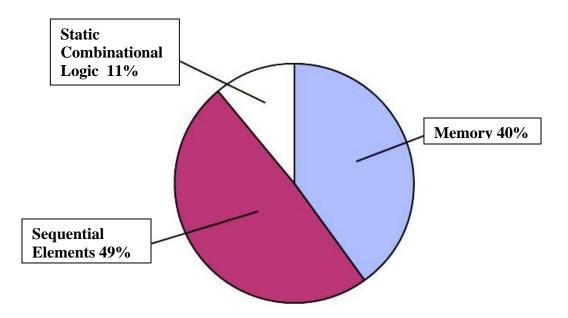

the power consumption, speed and reliability of time driven digital devices and as a result are the most important device type to focus in upon to improve device performance. Figure 1.2.1 illustrates the percentage of error attributable to static combinational logic, sequential elements (latches and flip-flops), and memory. Figure 1.2.1 shows how sequential elements despite being vastly outnumbered by combinational logic and memory is the prime source of error in systems.

Flip-flops are used extensively in time driven digital devices. Flip-flops influence

Focusing in on flip-flops is especially important in space applications because of the need to conserve power and operate in an environment which is inherently detrimental to the reliable operation of semiconductor devices. Indeed, radiation interaction with semiconductor circuits is directly attributable to spacecraft losses every year which could represent a considerable loss of money. For example, from 1998 to

Figure 1.2.1: Pie chart depiction of the amount of soft-error attributable to static combinational logic, sequential elements and memory regardless of environment [1].

2004 twelve satellites were lost due to radiation interaction with the satellites circuitry which represented a total monetary loss of \$500 million [2]. By 2005, there were 967 operating satellites in orbit around the Earth which represented a total of \$190 billion in assets [3]. A sizeable portion of these satellites helped to support a \$350 billion a year telecommunications industry [3]. Forecasts predict the launching of an additional 176 satellites worth \$28.3 billion between 2006 and 2015 [4]. Radiation has been an issue in the past costing millions of dollars in losses and with so much money invested in space applications of all kinds it is imperative that better, more radiation resistant flip-flop designs be developed.

#### 1.3 PROBLEM STATEMENT

The objective of this work will be to design and characterize a radiation tolerant triple mode redundant sense amplifier flip-flop (TMRSAFF) for use in space applications. The design will be created to provide:

1) Radiation tolerance up to the level of a 100MeV Iron (Fe) ion interaction.

- 2) Utilize a modified rail voltage to mitigate total ionizing dose (TID) effects.

- Options to enhance radiation hardness against single event upsets (SEU's) and to provide designers greater flexibility in creating their own version of TMRSAFF.

#### 1.4 PLAN OF ATTACK

The plan of attack for each component of the TMRSAFF design will be initially to assign values to items such as transistor sizes based on the authors initial desire to have a low power, high speed circuit. The plan of attack for the overall design will be to take the basic sense amplifier flip-flop (SAFF) design developed by Wang and Gong [5] and make three copies of the flip-flop. This triple mode redundant (TMR) flip-flop will then be enhanced and modified beyond traditional TMR design by incorporating several valuable options. After the design has been formulated, it will be simulated and tested for basic functionality. With a basically functioning TMRSAFF design, the next step will be to subject the design to simulated levels of cosmic ray ion interactions equivalent to that expected for a 100MeV Fe ion interaction. Adjustments to circuit parameters will be made as a result of empirical results achieved in simulation and simulations repeated until the circuit passes all radiation interaction simulation tests. Given that the circuit basically functions and delivers radiation tolerance results as specified then the circuit will be characterized for performance characteristics such as setup time, hold time, clock to Q delay and so on to establish it as a unique operating device.

#### 1.5 CONTRIBUTIONS

The contributions of this work will include the following:

- 1) The successful design and characterization through simulation of the worlds first version of TMRSAFF.

- 2) Valuable options developed in the TMRSAFF design effort will serve as a list of potential options to incorporate in all TMR flip-flop designs to follow. As such, the options will serve as a precedent for follow on researchers to consider as they develop their own versions of radiation tolerant/hardened flip-flop circuits.

- Development of testing methodologies using a conventional simulation tool for testing whether a given design meets radiation tolerance levels.

#### 1.6 SEQUENCE OF PRESENTATION

This work is divided into five chapters and several supporting appendices.

Chapter 1 provides motivation, a basic problem statement, a plan of attack, and contributions. Chapter 2 provides background information necessary to better understand why certain decisions were made in developing the TMRSAFF design. Chapter 3 will go over the methodology used to design and test the TMRSAFF proposed in this work.

Chapter 4 provides the results of the characterization of the TMRSAFF design and Chapter 5 provides conclusions and some discussion on future work. The supporting appendices contain supporting information considered too lengthy to include in the main body of the text but which provide additional information for those interested parties.

#### II. BACKGROUND INFORMATION

#### 2.1 OVERVIEW

Material that will be discussed in this chapter will be:

- 1) TID Effects on circuits.

- 2) Causes of single event upsets (SEU's) in circuits.

- 3) Choice of radiation tolerant design in the creation of the TMRSAFF design.

- 4) Definition of radiation tolerant design.

- 5) Definition of basic TMR design.

- 6) Justification for use of TMR in flip-flop design.

#### 2.2 TID FFECTS ON CIRCUITS

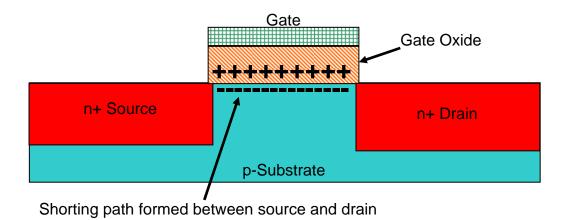

When radiation traverses through a material it produces electron hole pairs (EHP's). When EHP's are generated in oxides a sizable portion of the negative and positive charge recombines but not all of the charge recombines. A certain portion of the generated negative and positive charge remains after a radiation event has occurred. The negative charge is generally drawn out of the oxide rapidly but positive charge is moved less rapidly. Consequently, there is a corresponding increase in the positive charge that exists in the oxide. Over time this positive charge migrates toward the silicon (Si)/silicon dioxide (SiO<sub>2</sub>) interface. The application of positive voltages to conductors (typical in applications) encourages the migration of positive charge to the Si/SiO<sub>2</sub> interface because positive voltage repels positive charge. As charge builds up on the Si/SiO<sub>2</sub> interface of negative metal oxide semiconductor (NMOS) metal oxide semiconductor field effect transistors (MOSFET's), negative charge is drawn up to the Si/SiO<sub>2</sub> interface from within the substrate and shorting paths are formed in circuits. Figure 2.2.1 shows the formation

of a shorting path between the source and drain of an NMOS MOSFET as a result of positive charge build up on the Si/SiO<sub>2</sub> interface.

Figure 2.2.1: Formation of a shorting path between the source and drain of an NMOS device.

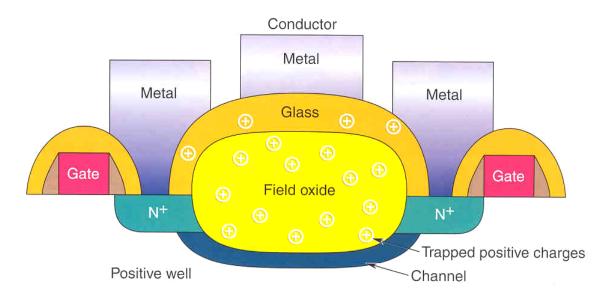

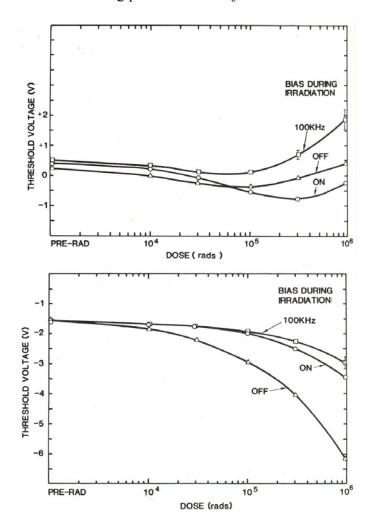

In instances where circuit conductors are routed over oxides which separate adjacent NMOS MOSFET's, a similar phenomenon as seen in the case of NMOS MOSFET gates produces a shorting path between what should be separated devices. This is illustrated in Figure 2.2.2 which shows the formation of a shorting path between the n+ regions of two adjacent NMOS MOSFET's. The accumulation of positive charge in the gate oxides of both NMOS and positive metal oxide semiconductor (PMOS) MOSFET's creates a phenomenon known as negative threshold voltage shift. The accumulation of positive charge and the subsequent attraction of negative charge to the Si/SiO<sub>2</sub> interface corresponds to an equivalent voltage source being applied to the gate of a transistor. The overall effect being that NMOS devices become more difficult to turn off while PMOS devices become more difficult to turn on. Figure 2.2.3 shows the effects of ionizing radiation dose absorbed by both NMOS (top graph) and PMOS (bottom graph) transistors and the corresponding shift of transistor threshold voltage.

Figure 2.2.2: Formation of a shorting path between adjacent NMOS MOSFET's [23].

Figure 2.2.3: NMOS and PMOS transistor threshold voltage shift [6].

#### 2.3 CAUSES OF SEU's IN CIRCUITS

Seu's are caused by one, a combination of two or potential all three of the following occurrences:

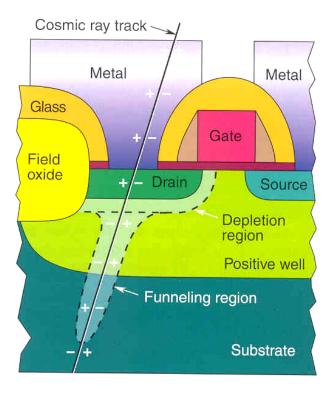

1) When a cosmic ray traverses through Si it generates what is referred to as a funnel which is shown in Figure 2.3.1. When this funnel collapses it collapses back toward the point of entry and as it does so, excess charge generated in the funnel (potentially as high as  $10^{25}$  cm<sup>-3</sup>) is drawn back toward the point of entry. If the point of entry was a node which was storing information, then the introduction of charge on to that node could cause an upset of the information (bit flip).

Figure 2.3.1: Funnel formation in Si [5].

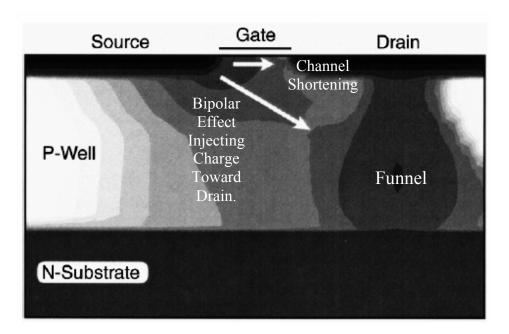

2) If a cosmic ray traverses through the source or drain of a MOSFET, it creates an effect referred to as channel shortening where the physical length of the MOSFET channel is reduced. This reduction in channel length with applied biases encourages the injection of charge across the channel of what should be a turned off transistor. This charge injection can cause upsets in information.

3) If a cosmic ray traverses through the source or drain of a MOSFET, it creates an effect in addition to that outlined in 2). It is referred to as a bipolar effect where charge concentration differences temporarily create a bipolar device which encourages the injection of charge in to the substrate of a MOSFET whereupon it can be collected by a node which is storing information. This also could cause information upsets.

Figure 2.3.2 shows an electron-micrograph of a charged particle going through the drain of an NMOS MOSFET. Dark regions in Figure 2.3.2 are indicative of regions which are predominantly made up of negative charge. Figure 2.3.2 shows the characteristic formation of a funnel, the shortening of the MOSFET channel, and charge injection toward the funnel due to bipolar effects.

Figure 2.3.2: Electron-micrograph of charged particle interaction with NMOS transistor [7].

#### 2.4 CHOICE OF RADIATION TOLERANT DESIGN

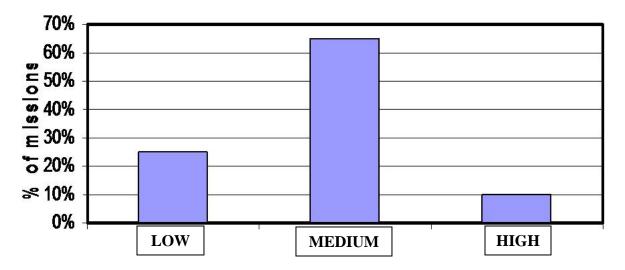

The reasoning behind pursuing radiation tolerant design as opposed to radiation hardened design of the TMRSAFF is mainly due to the fact that NASA currently has greater interest and need for radiation tolerant designs as opposed to radiation hardened designs [8]. This fact is conveyed in Figure 2.4.1 which shows the percentage of missions out of a representative group of 225 recent NASA missions and their requirements in the area of radiation design.

Figure 2.4.1: Bar graph representation of radiation design requirments of 225 recent NASA missions [8].

#### 2.5 DEFINITION OF RADIATION TOLERANT DESIGN

The definition of radiation tolerant design as specified by NASA is as follows [9]:

- 1) Design assures radiation hardness up to a given level.

- 2) Hardness levels required are:

- a) Total Ioniziing Dose: 20-50krad minimum.

- b) SEU Threshold Linear Energy Transfer (LET): 20MeV-cm<sup>2</sup>/mg minimum.

- c) Tested for functional fail only.

The LET of a 100MeV Fe ion in 27-30MeV-cm<sup>2</sup>/mg [10]. It is for this reason and the fact that industry considers a 100MeV Fe ion to represent the upper bound of the typical natural radiation environment [10] that a radiation hardness level resilient up to the level required for a 100MeV Fe ion was chosen in the design of the TMRSAFF.

#### 2.6 DEFINITION OF BASIC TMR DESIGN

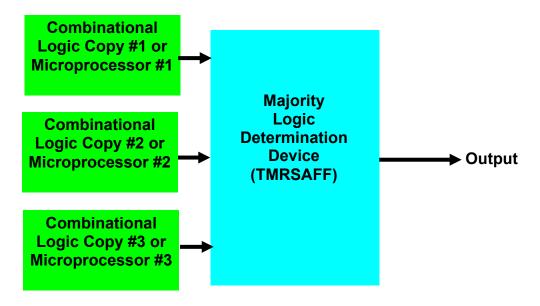

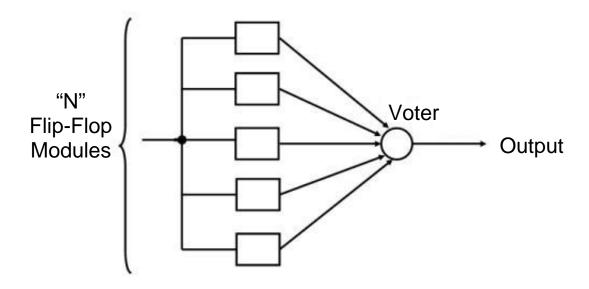

The most fundamental realization of TMR design is shown in Figure 2.6.1. It shows TMR design in its most basic form. In this case, three identical copies of logic are routed into a majority logic gate, also known as a voter, which passes the value found on the majority of its inputs. Results of the majority logic determination then produce a single output.

Figure 2.6.1: Basic TMR block diagram.

In the case of space applications, it is common for three identical copies of microprocessor to be routed to a majority logic gate which then passes the majority value found on its inputs to an overall system output. This arrangement generally requires that each processor be fabricated on its own chip and then be externally wired into a majority

logic chip which then votes on the results.

#### 2.7 JUSTIFICATION FOR USE OF TMR IN FLIP-FLOP DESIGN

The main reason for utilizing TMR design in designing flip-flops is as follows:

- 1) If a single flip-flop is utilized, then the flip-flop has no means by which to either detect or correct for errors by itself.

- 2) If 2N flip-flops (an even number of flip-flops) are utilized then there is no ability to do basic tie breaking determinations. For example, if two flip-flops are utilized and one flip-flop outputs a high while the other flip-flop outputs a low then there is no way of knowing which flip-flop is correct.

- 3) If 2N+1 flip-flops (an odd number of flip-flops) are utilized then there exists the ability to do basic tie breaking. For example, if three flip-flops are utilized and one flip-flop outputs a high while the remaining two flip-flops output a low then routing into a majority logic gate will produce an ultimate low output for the group of three flip-flops.

The main reason for not utilizing more than three copies of any circuit to produce a more reliable device is because there is a point of diminishing return in reliability gained using more than three copies of a circuit while overall circuit performance can be detrimentally affected by utilizing more than three copies of a circuit. Table 2.7.1 lists a tabulation of reliability, transistor count, equivalent power consumption, and equivalent majority logic delay one would incur as a result of utilizing three, five, and seven copies of a sense amplifier flip-flop (SAFF) design [5] in realizing an overall N-modal version of flip-flop as shown in Figure 2.7.1.

Table 2.7.1: Tabulation of N-modal flip-flop performance parameters

| Number of<br>Copies (N) | Reliability | Transistor<br>Count | Equivalent Power<br>Consumption | Equivalent Delay<br>In<br>Majority Logic |

|-------------------------|-------------|---------------------|---------------------------------|------------------------------------------|

| 3                       | 94.3% [12]  | 222                 | 34 units                        | 2 units                                  |

| 5                       | 94.88% [12] | 358                 | 59 units                        | 3 units                                  |

| 7                       | 94.98% [12] | 556                 | 95 units                        | 5 units                                  |

Figure 2.7.1: N-modal flip-flop [12].

The equation used to calculate the reliability of the N-modal flip-flop shown in Figure 2.7.1 was [11]:

$$R_{M-of-N} = R_{voter} \sum_{i=0}^{N-M} \left( \frac{N!}{i! \ (N-i)!} \right) (1-R)^{i} R^{N-i}$$

(Eq. 2.7.1)

where  $R_{M\text{-of-}N}$  is the reliability of an N-modal structure,  $R_{voter}$  is the reliability of the voting circuit, N is the number of identical units, M is the number of modules that must be functional, and R is the reliability of the individual components. For purposes of the

reliability calculations conducted to generate Table 2.7.1, a value for R was chosen to be 0.95 which was deliberately chosen to be unrealistically low in order to slant the calculations in favor of the higher number of copies. The value for M was adjusted to reflect the minimum number of flip-flops required to conducted a rudimentary tie breaking situation. For three copies of flip-flop, the value for M was 3 while for five copies of flip-flop M was 3 and for seven copies of flip-flop M was also 3. To determine the transistor count, a tally of the number of the transistors needed to create a basic SAFF [5] was added to the number of transistors needed to carry out the following majority logic determinations:

3-copies - AB+BC+CA.

5-copies- ABC+ACD+ACE+BCD+BCE+CDE.

7-copies- ABCD+ACDE+ADEF+AEFG+BCDE+BDEF+BEFG+CDEF+CEFG+DEFG.

The majority logic determination on transistor count, power dissipation, and delay was conducted assuming that CMOS was the technology utilized and that logic gates no larger than three inputs would be utilized. The reason for this is because logic gates with more than three inputs is known to be inefficient and induces a large increase in both power dissipation and delay. The power dissipation of both a two and three input logic gate was assumed to have a power dissipation of 1 unit while each level of gates needed to realize a particular majority logic determination was assumed to have a delay of 1 time unit. This would in reality reduce the power dissipation and delay that a majority logic determination would need that utilized three input logic gates as opposed to two input logic gates. Despite advantages given to higher copy versions tabulated in Table 2.7.1 there was not a significant increase in reliability going from three copies up to five or

14

seven copies. In contrast, there was a drastic increase in transistor count which translates into greater Si area to create the circuit and a considerable increase in both power consumption and delay. Therefore, the gist of Table 2.7.1 is to say that using anything more than three copies would be an inefficient implementation and would degrade the resulting circuits performance.

#### III METHODOLOGY

#### 3.1 OVERVIEW

The material that will be covered in this chapter will be:

- 1) Background.

- 2) Choice of basic flip-flop technology in the TMRSAFF design.

- 3) Choice of specific flip-flop technology to use in the design of the TMRSAFF.

- 4) Basic TMRSAFF structure.

- 5) Basic functionality determination.

- 6) Basic timing parameter determination.

- 7) Basic Radiation Simulation.

- 8) How TMRSAFF counters TID Effects.

- 9) Radiation hardening options created in the TMRSAFF design.

- 10) Transistor sizing.

#### 3.2 BACKGROUND

Schematics for the TMRSAFF design created in this work can be found in Appendices 8-15. The software package used to design and test the TMRSAFF design was Design Architect-IC v2005.1\_1.1 software. It is a graphical user interface which allows for the use of either transistor or gate level design of circuits. The actual simulations were carried out using the 2005 release version of ELDO software contained within the Design Architect package. ELDO is a Mentor Graphics specific version of SPICE which has Mentor Graphics operations capability. This package was chosen because of its 100% compatibility with SPICE, accuracy, and its availability to industry and the general education community. The package provides an easy to use graphical

user interface (GUI) by which to create circuits. This was deemed vital for large complex circuits like those proposed in this work. Using ELDO provided calculations on power consumption and the Design Architect package allowed for the generation of varied sets of graphs for viewing circuit performance. In addition, the overall Design Architect package generates a SPICE netlist which allows for quick, less error prone insertion into other software packages like High Accuracy Simulation Program with Integrated Circuit Emphasis (HSPICE) for further validation of results.

The technology family used to design the TMRSAFF was the American Megatrends Incoporated 05 (ami05, 0.6 micron) family whose transistor characteristics are provided in Appendix 7. The decision to use this was based on the fact that this is a long established technology family that is readily accessible to the education community at large and is long since known to be of a reliable functioning nature. The 0.6 micron technology family has been in use for many years and has a comprehensive listing of transistor circuit parameters which many smaller technology families which could have been used at the present time does not. In addition, by starting with a large technology family the speed of the design would be less than that possible for smaller technology families. As a result, downscaling would produce circuits that will run faster and have smaller mechanisms by which failures can occur (smaller diffusions).

The bulk of the work done to produce the TMRSAFF design was decided to be done empirically where initial decisions were made on issues such as transistor sizes.

After initial device sizes were decided upon then tests were summarily conducted where faults which simulate radiation interactions were employed on various nodes to be analyzed and a size increasing algorithm employed to step up the size of devices was

employed to harden the node up to the prescribed level of a 100MeV Fe ion interaction.

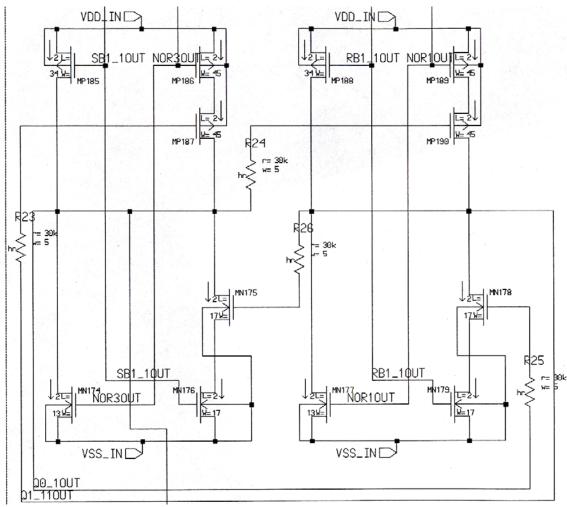

Preliminary work which is not included in this write up was conducted by the author and it was determined that radiation hardening strictly through the brute force method of using larger transistors for larger capacitance would not work even for such a large technology family as the ami05 family. This was because of the fact that in radiation hardening one must manipulate resistor-capacitor (RC) time constants. The faster a circuit is for propagating correct signals then the faster it will be for propagating incorrect signals introduced into the system by radiation interactions. As such, some degree of compromise would have to be made at some point in the opposing performance criteria of speed versus reliability. Given this it really made little difference how large a capacitor like a transistor gate or diffusion was made when the circuit impedance was low. It was from this observation that the decision was made to allow for the use of resistors in the TMRSAFF design in order to achieve desired radiation hardening results

In general, it was decided for the purposes of conserving silicon area that a practical limit would be placed on the width of any transistor in the TMRSAFF design of no more than W = 50 or  $50\lambda$ . This translates into a physical dimension of  $15\mu m$  (0.6 $\mu m$  x 50/2). In practice, most transistor widths proposed in the TMRSAFF design this work is based upon were sized well below the limit of  $50\lambda$  to allow for some room in increasing transistor widths as smaller technology sizes are used to scale the design down. It was also decided early on that for silicon area conservation, ease of design, and the fact that the practice is common that all transistors would be made to have a length (L) of  $2\lambda$ . Thus, every transistor in the TMRSAFF design has L = 2. Another practical designation decision was made on the maximum size of resistors in the circuit. Resistors were

decided not to be larger in size than  $15k\Omega$ . This was done to allow for the potential use if the end user so desires of depletion mode transistors in design as exceedingly large resistances may be difficult to achieve using depletion mode transistors. In fact, the use of transistors to achieve impedance is limited generally to a range of 1-30k $\Omega$ . As such, limiting resistance values to  $15k\Omega$  would leave considerable room for increasing the size of resistors in the event the TMRSAFF design is downscaled to a smaller technology size.

#### 3.3 CHOICE OF BASIC FLIP-FLOP TECHNOLOGY IN THE TMRSAFF DESIGN

Extensive literature review was conducted on basic flip-flop technologies where various types of state of the art flip-flops were considered for use in the development of the TMRSAFF design. Five parameters were focused in upon in order to choose the basic flip-flop technology. These parameters were power consumption, clock to Q delay, setup time, clock loading, and data line loading. The power consumption of the basic flip-flop technology would have to be as low as possible while at the same time providing the shortest clock to Q delay possible in order to have good speed characteristics. In addition since radiation hardening would slow the TMRSAFF design down, setup time would have to be as short as possible in order that the TMRSAFF design would not consume too much time in passing a value and thus leave more time per clock cycle for combinational logic to perform its functions. Because the system clock and its associated loads constitute the largest consumer of power in a system, and the data line constitutes the third largest consumer of power in a system it was decided to choose a flip-flop technology that would reduce these parameters too as low a value as possible in order to further reduce power consumption. The results of the research resulted in the choice of using sense amplifier flip-flop (SAFF) technology in the TMRSAFF design. Table 3.3.1 provides parameters on clock power, data power, total power, delay and setup time for 6 state of the art flip-flop technologies.

Table 3.3.1: Tabulation of state of the art flip-flop designs [18]

| Flip-flop<br>Type | Clock Power (µW) | Data Power (µW) | Total Power (µW) | Delay (ps) | Setup Time (ps) |

|-------------------|------------------|-----------------|------------------|------------|-----------------|

| SAFF              | 18               | 3               | 158              | 272        | -35             |

| K6-ETL            | 15               | 5               | 349              | 200        | -4              |

| SSTC              | 22               | 4               | 160              | 592        | 267             |

| DSTC              | 22               | 4               | 198              | 629        | 263             |

| Hybrid<br>SSTC    | 14               | 1               | 146              | 892        | 476             |

| Hybrid<br>DSTC    | 13               | 1               | 185              | 1060       | 480             |

#### 3.4 CHOICE OF SPECIFIC FLIP-FLOP TO USE IN THE TMRSAFF DESIGN

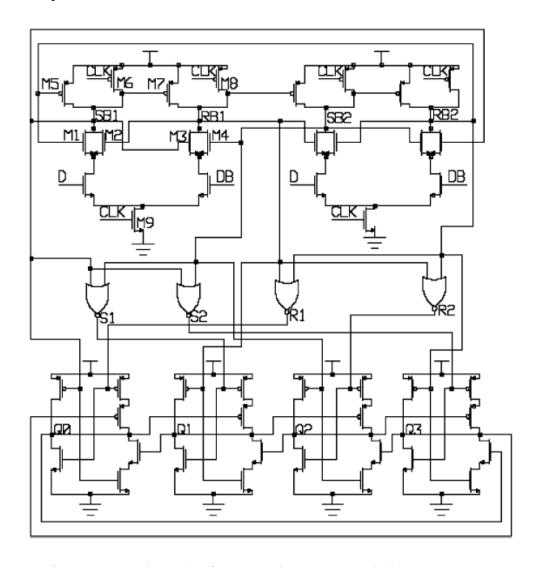

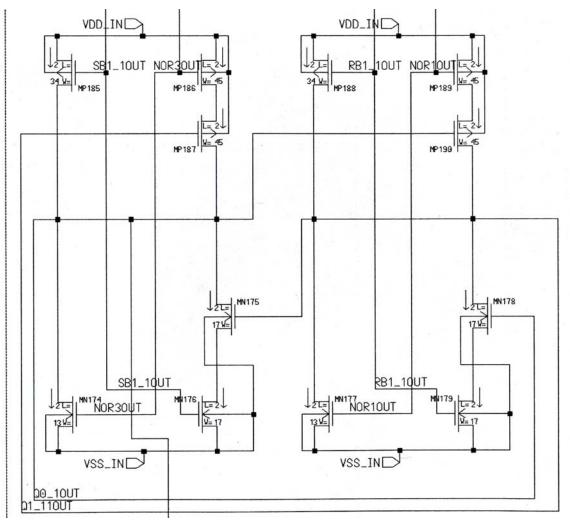

The specific flip-flop design which was selected to create the TMRSAFF design was a design put forth by Weizhong Wang and Haiyan Gong from the University of Wisconsin [5]. The schematic for this design is provided in Figure 3.4.1. The design was chosen for several basic reasons as follows:

- The design eliminated the occurrence of self-locking which has plagued SAFF technology and thus has prevented SAFF technology from be utilized in radiation environments.

- 2) The design generates fully redundant outputs (Q0, Q1 primary and Q2, Q3 redundant in Figure 3.4.1). This would allow for the creation of a redundant output path for the overall TMRSAFF design which would represent an alternative path for passing information to the output of the TMRSAFF design.

3) The design is fully static which translates into nodes which when interacted with by radiation would quickly recover and return to their original quiescent state prior to the interaction event.

Figure 3.4.1: Schematic of Wang and Gong SAFF design [5].

In addition, the Wang and Gong design was compared to two state of the art flip-flop designs currently in use in space applications [5]. The results of these comparisons are provided in table 3.4.1 which compares the Wang and Gong design to the SAFF technology currently in use in the state of the art ALPHA 21264 space microprocessor and in Table 3.4.2 which compares the Wang and Gong design to the most commonly

utilized flip-flop design in space applications, the basic DICE flip-flop. The results of the comparison were that the Wang and Gong design was superior to both the ALPHA 21264 space microprocessor SAFF technology and basic DICE flip-flop technology in the areas of clock to Q delay, data line loading, and clock network loading.

Table 3.4.1: Comparison of the Wang and Gong SAFF design to the SAFF design utilized in the ALPHA 21264 space microprocessor

|                     | WORST CASE<br>CLOCK TO Q<br>DELAY | LOADING TO<br>DATA INPUT<br>LINE | LOADING TO CLOCK<br>NETWORK |

|---------------------|-----------------------------------|----------------------------------|-----------------------------|

| W&GD SAFF           | 367ps                             | 0.186pJ                          | 0.484pJ                     |

| ALPHA 21264<br>SAFF | 412ps                             | 0.212pJ                          | 0.536рЈ                     |

| PERCENT<br>CHANGE   | -10.9%                            | -12.3%                           | -9.7%                       |

Table 3.4.2: Comparison of the Wang and Gong SAFF design to basic DICE flip-flop technology

|                   | WORST CASE<br>CLOCK TO Q<br>DELAY | LOADING TO<br>DATA INPUT<br>LINE | LOADING TO CLOCK<br>NETWORK |

|-------------------|-----------------------------------|----------------------------------|-----------------------------|

| W&GD SAFF         | 367ps                             | 0.186pJ                          | 0.484pJ                     |

| DICE FF           | 476ps                             | 0.245pJ                          | 1.03pJ                      |

| PERCENT<br>CHANGE | -22.9%                            | -24%                             | -53%                        |

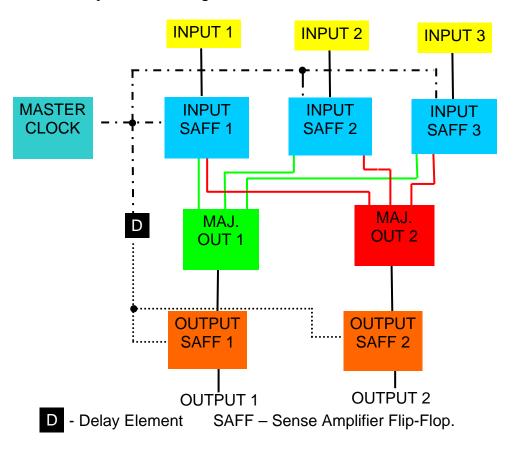

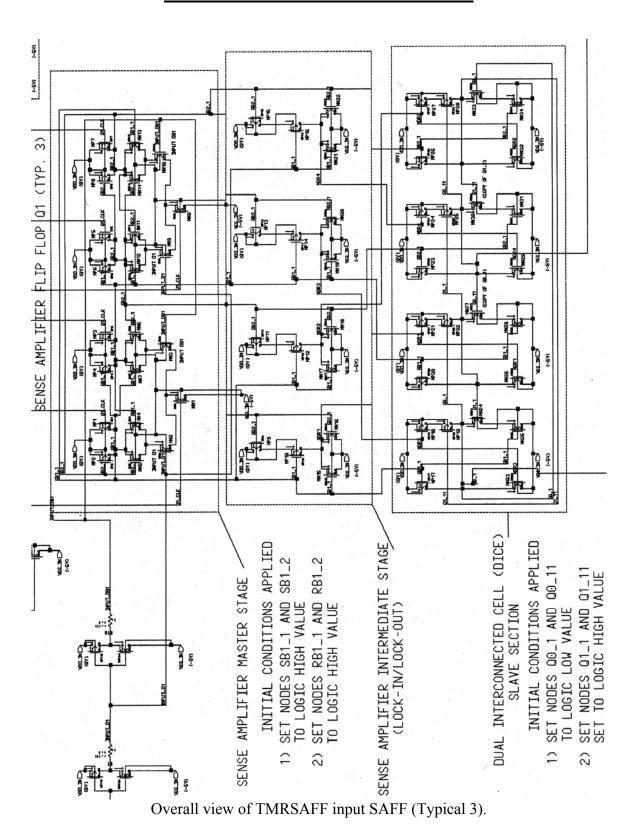

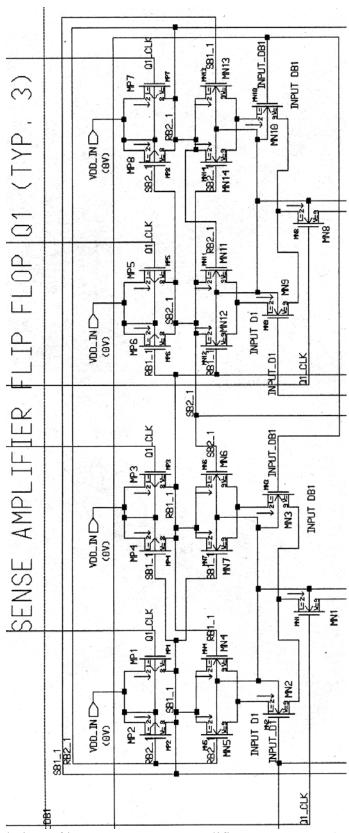

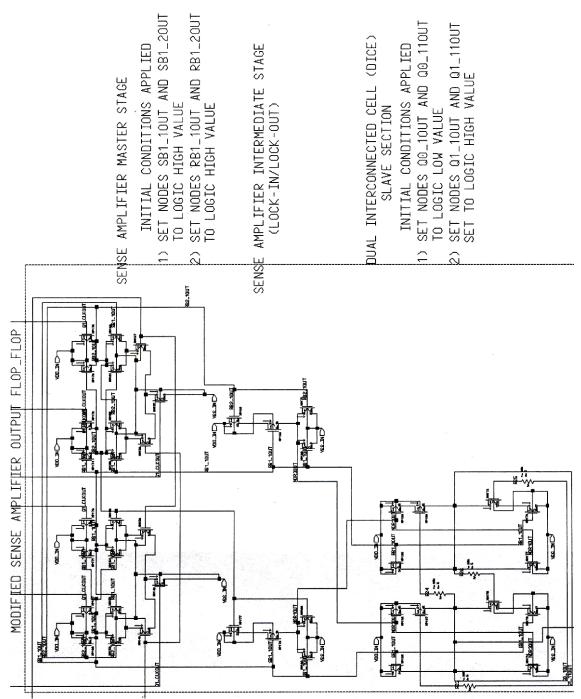

## 3.5 BASIC TMRSAFF STRUCTURE

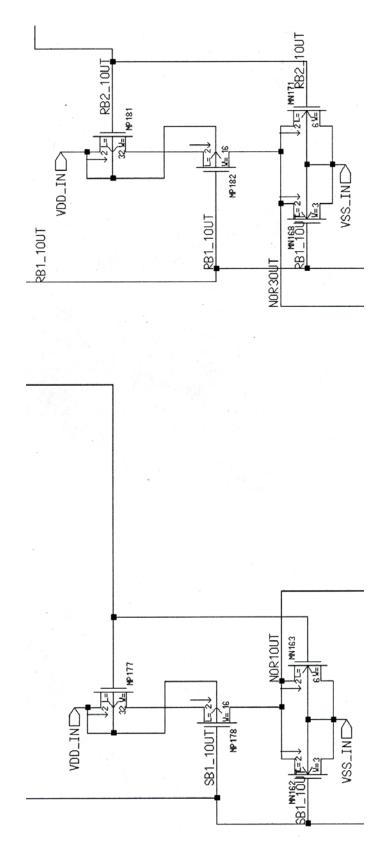

The basic structure of the TMRSAFF design was comprised of three copies of the Wang and Gong SAFF design as the input flip-flops. The primary outputs of each input SAFF were routed to one majority logic gate while the redundant outputs of each input SAFF were routed to a duplicate majority logic gate. Each majority logic gate was then routed into an output SAFF which was made by modifying the Wang and Gong flip-

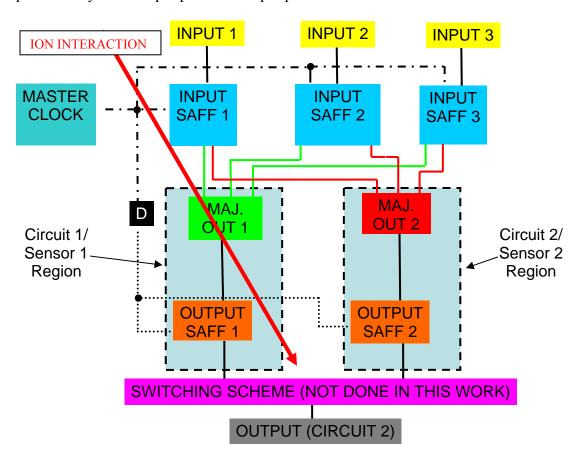

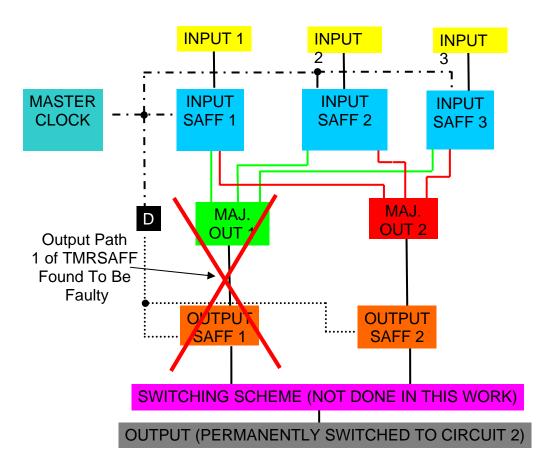

flop design. The modifications employed were to remove the S2 and R2 NOR gates along with the Q2 and Q3 output latches seen in Figure 3.4.1. The master clock was routed into each of the input SAFF's and an appropriate delay of the master clock was used to provide the driving clock signal for each of the output SAFF's. Output SAFF's were employed with the TMRSAFF design in order to prevent the TMRSAFF from being a source of glitches in the system. In addition, the decision was made to derive the driving clock signal of the TMRSAFF output flip-flops local to the flip-flop in order to relieve reliance on outside sources for clocking. In order to ensure basic radiation hardness up to the level of a 100MeV Fe ion interaction, it was decided to harden all of the nodes of the input and output SAFF's up to the level of a 100MeV Fe ion interaction. Figure 3.5.1 shows in simplified block diagram form the basic structure of the TMRSAFF design.

Figure 3.5.1: Basic block diagram of the TMRSAFF design.

## 3.6 BASIC FUNCTIONALITY DETERMINATION

In order to ensure that each individual flip-flop utilized in the TMRSAFF design was functioning properly as a flip-flop, the decision was made to create what is referred to as a basic functionality test vector. This vector is provided in Appendix 1 and is referred to in this text as the basic functionality test vector (D input). Because each individual SAFF, has both a D and DB (D complement) input the test vector provided in Appendix 1 was created to apply to the D input of an individual SAFF while the test vector provided in Appendix 2 was created to apply to the DB input of an individual SAFF.

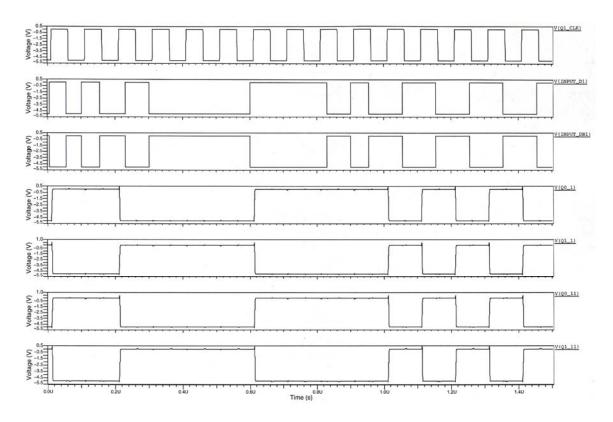

In this way, items such as worst case clock to Q time, setup time, hold time, and power consumption could be determined for singular SAFF's like the SAFF design proposed by Wang and Gong or the modified SAFF design proposed by the author for use as the output stage of the TMRSAFF. A typical set of values for the basic functionality test vector (D Input), the basic functionality test vector (DB Input), and the corresponding correct flip-flop output responses are provided in Figure 3.6.1.

It was decided to test flip-flops for seven distinct events as follows:

- 1) With a high value already clocked into the output of the flip-flop if the data input stays at a high value then the output of the flip-flop should remain at a high value.

- With the flip-flop output already at a high output value then the data input should go low prior to the incoming rising clock edge and the flip-flop should clock in a low value to its output.

- 3) With the flip-flop having clocked in a low value to its output then have what amounts to an out of phase input value corresponding to a high value come in during the

falling transition of the clock but which returns to a low value prior to the next rising edge of the clock. Here the flip-flop output should remain at a low value. This will verify that high data sitting at the input does not affect the output and that the design is a positive edge triggered device.

- 4) With a low value already clocked into the output of the flip-flop if the data input stays at a low value then the output of the flip-flop should remain at a low value.

- 5) With the flip-flop output already at a low output value then the data input should go high prior to the incoming rising clock edge and the flip-flop should clock in a high value to its output.

- 6) With the flip-flop having clocked in a high value to its output then have what amounts to an out of phase input value corresponding to a low value come in during the falling transition of the clock but which returns to a high value prior to the next rising edge of the clock. Here the flip-flop should remain at a high value. This will verify that low data sitting at the input does not affect the output and that the design is a positive edge triggered device.

- 7) Run the flip-flop through several oscillations so that it can be seen that repetitive transitions from high to low can be handled without error.

In Figure 3.6.1, Q1\_CLK is the clock input, D1 is the D input, DB1 is the D complement input, Q0\_1 is the primary output, Q1\_1 is the primary complement output, Q0\_11 is the redundant output, and Q1\_11 is the redundant complement output for the SAFF's used in the design of the TMRSAFF. It should be understood that the Q0\_1 output shown in Figure 3.6.1 is the correct response to all flip-flop primary outputs whether it be for the design proposed by Wang and Gong or the modified SAFF proposed

Figure 3.6.1: Graph of applied inputs and corresponding output results for running the basic functionality test vector/vectors in checking the performance of the individual flip-flops used in this work.

by the author for the TMRSAFF output, or the overall TMRSAFF design itself when running the basic functionality test vector/vectors.

Referring to Figure 3.6.1, one will note that D (and DB) oscillate low to high from t = 0 to t = 180ns. This is the portion of the basic functionality test vector that tests for the input being at a high and the output staying at a high in the face of oscillating input. Time t = 210ns tests the flip-flop input being low and the output transitioning to a low. The step function which occurs at 220ns and ends at 300ns is a test for an out of phase high signal being applied to the input. The period from 300ns to 600ns tests for the input of a flip-flop being at a low value and the output staying at a low. Time t = 610ns tests for the input of a flip-flop being at a high value and the output of the flip-flop transitioning to a high value. The time period from 610ns to 830ns tests for the input of a flip-flop being

high and the output staying at a high. The dip at t = 830ns and lasting to 900ns tests for an out of phase low signal coming in to the flip-flop. Finally, the oscillations which start at 1050ns and last the remainder of the 1500ns of the basic functionality test vector test for correct operation when the flip-flop is subjected to oscillatory input. This short test effectively accomplishes the task of testing a flip-flop's operation for each of the seven items previously listed. It was during basic functionality test runs where current barrages like those which will be described in the next section were applied and the response of the circuit judged for correct operation. It was also during basic functionality tests that power dissipation numbers for a flip-flop were taken.

Once all individual flip-flops to be used in the TMRSAFF design were verified for proper functionality using the basic functionality test vector, then the TMRSAFF shown in Figure 3.5.1 was created and the basic functionality test vector (D input) was applied to the TMRSAFF in order to verify its basic functionality and to acquire basic performance parameters on items such as clock to Q delay, setup time, hold time, and power dissipation.

### 3.7 BASIC TIMING PARAMETER DETERMINATION

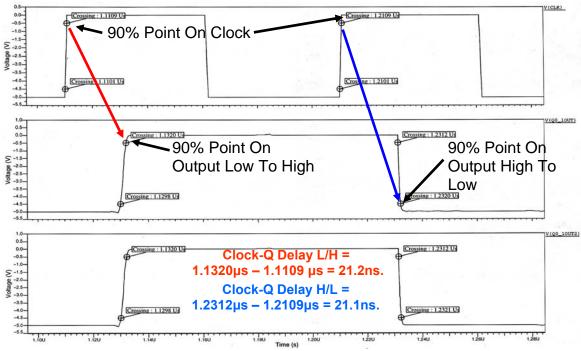

The manner in which the TMRSAFF clock to Q delay was determined is illustrated in Figure 3.7.1. In order to calculate the clock to Q delay of either a high to low or low to high transition, it was decided to use the 90% transition point on the corresponding waveforms (-0.5V going from low to high or -4.5V going from high to low in Figure 3.7.1). This was done because when a transition reaches to within 0.5V of its final value one is assured that only the transistor type (either PMOS or NMOS) which was meant to be turned off downstream of the TMRSAFF would in fact be turned off.

Unfortunately, the threshold voltage of NMOS devices in the ami05 transistor family has a value of 0.7V while that of a PMOS device is -0.9V. So, a value less than 0.7V was required so that timing calculations could be universally conducted.

Figure 3.7.1: Basic determination of TMRSAFF clock to Q delay.

The manner in which setup time was calculated was to apply a regularly oscillating input signal to the TMRSAFF and checking that for both high to low and low to high data transitions that the TMRSAFF correctly produced the appropriate output. If the output was correct then the data input was delayed such that the transition edge of the input data signal was moved 5ps closer to the driving clock edge. This process of advancing the input data towards the driving clock edge was continued until finally the TMRSAFF failed to correctly pass appropriate data to its output. A similar methodology was used to determine TMRSAFF hold time where the incoming data was held steady for a certain period after the incoming driving clock signal. If the data was successfully

passed to the output of the TMRSAFF, then the data transition edge was moved 5ps closer to the clock driving edge until the TMRSAFF no longer correctly passed data to its output.

#### 3.8 BASIC RADITION SIMULATION

To simulate the effects of charged particle interaction with the MOSFET's of the TMRSAFF design, it was decided to use the traditional methodology of applying a current source from the node to be tested to the low circuit rail voltage (NMOS FAULT) or from the high rail voltage to the node to be tested (PMOS FAULT). The reason for this is because NMOS devices are susceptible to "1" to "0" bit flips. This is so because as a particle goes through the n<sup>+</sup>/p diode formed by the drain of an NMOS device into the p-substrate that it is formed in, the p-substrate is grounded to protect against latch-up. This creates a connection from ground to the node. Therefore, a current source from the node to be tested to the low rail voltage was considered adequate for testing the effects of a particle interaction through an n<sup>+</sup>/p diode (NMOS FAULT).

As for PMOS devices, they are susceptible to "0" to "1" bit flips. This is so because as a particle goes through the  $p^+/n$  diode formed by the drain of a PMOS device into the n-well that it is formed in, the n-well is connected to the high rail voltage to protect against latch-up. As a result, a connection is formed from the high rail voltage to the node which creates a means by which charge can be forced on to a node. Given this then a current source from the high rail voltage to the node being tested was deemed adequate to test for a particle interaction through a  $p^+/n$  diode (PMOS FAULT). The issue of determining the shape and form which a 100MeV Fe ion would take as a result of interacting with Si was answered as a result of private communications with Paul Dodd (Project Manager of

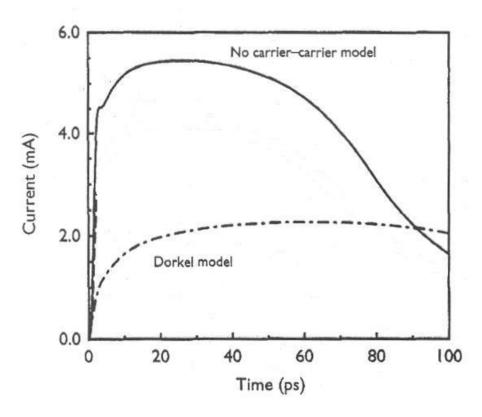

Sandia Laboratories Radiation Effects Testing Division and a world expert in the area of radiation event testing) [13] who recommended the use of the Dorkel mobility model [14]. This model calculates semiconductor mobility and takes into account parameters such as temperature, doping concentration, and carrier injection. Figure 3.8.1 provides the current response of a 100MeV Fe ion interaction with an n+/p diode which is the basic structure one encounters in NMOS MOSFET's. It shows two curves which attempt to predict the amount of current that flows when a 100MeV Fe ion interacts with the n<sup>+</sup>/p diode of an NMOS device. The curve labeled "No carrier-carrier model" is the result one would get as a result of neglecting carrier-carrier scattering in the Dorkel model. The model labeled "Dorkel model" is the result one would get as a result of running the Dorkel model with carrier-carrier scattering taken into account.

Figure 3.8.1: Graph of current response of 100MeV Fe ion interaction with an n+/p Si diode using the Dorkel model [24].

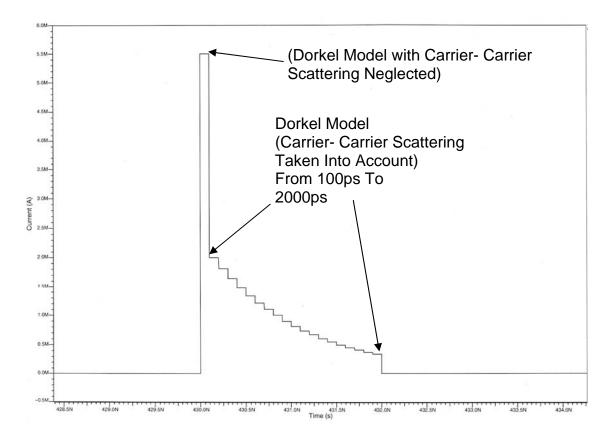

The decision was made to create a step function current source for the testing of faults on the n<sup>+</sup>/p diodes of any NMOS transistors found in the TMRSAFF circuit design by composing it of two different components. The components would be composed of a prompt dose whose magnitude was determined by using the, "No carrier-carier model", peak amplitude in Figure 3.8.1 which can be seen to be 5.5mA. The duration of this prompt component was determined by finding the intersection of the two curves in Figure 3.8.1 and rounding up to the nearest factor of ten which in Figure 3.8.1 can be seen to be 100ps. So, the prompt component of a 100MeV Fe ion interaction would be 5.5mA for 100ps. The remaining component (referred to as a diffusion component) would be determined by using the Dorkel model where carrier-carrier interactions were taken under consideration from 100ps out to 2000ps. The decision to run the Dorkel model out to 2000ps was made on recommendation from Ken Label (NASA Radiation Effects Group. Project Manager) who stated that radiation affects intervals considered by NASA average approximately 2ns in duration [16]. An equation which mimicks the exponential decay from 100ps to 2000ps (2ns) is as follows:

$$I(t) = (0.002) \exp^{-(t-100)/1000} (A)$$

(Eq. 3.8.1)

where the time t is measured in picoseconds and the result is in amps.

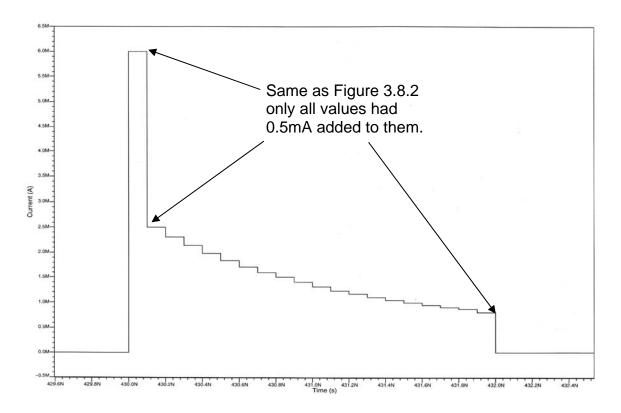

Figure 3.8.2 shows the resulting step function used as the basis for simulating a 100 MeV Fe interaction on the  $n^+/p$  diodes which exist in the NMOS transistors of the TMRSAFF design. This type of current occurrence is referred to in this text as a low current test model. For purposes of pushing the design to a limit beyond that which it was designed, the author created another waveform which simply adds 0.5 mA to all the values shown in Figure 3.8.2. This is referred to in this text as a high current test model

Figure 3.8.2: Low current test model.

For purposes of testing the various nodes in the TMRSAFF design, what were referred to as current barrages were created as test vectors for the circuit. One is provided in Appendix 3 and is known as a low current barrage test vector. It is comprised of current events like those shown in Figure 3.8.2. Along the same lines, something called a high current barrage test vector was created and a copy of one is provided in Appendix 4. It is comprised of current events that are like those shown in Figure 3.8.3 and are made to occur at the same times as those specified for the low current barrage test vector. Figure 3.8.4 shows the time spread for the low current barrage test vector provided in Appendix 3 and the high current barrage test vector provided in Appendix 4 in conjunction with the running of the basic functionality test vector which is shown as the top graph in Figure

Figure 3.8.3: High current test model.

3.8.4. It was during the running of the basic functionality test vector on the TMRSAFF that these barrages were applied to a node and errors observed to occur on the TMRSAFF's output.

The theory behind generating two current barrages, each of a different magnitude was to try and come up with a method that would allow the development of near optimal results in terms of transistor and resistor sizing on circuit nodes. If a node passed the low current barrage test vector, but failed the high current barrage test vector then the node in question would be considered near optimal in terms of device sizing (capacitance and/or resistance applied to a node). As such, a designer would know that the choices for transistor and/or resistor sizing on the node were adequate to harden the circuit up to the prescribed radiation level but at the same time did not add unnecessary capacitance or resistance to a node which would increase power dissipation and increase delay. An

Figure 3.8.4: Timing graph showing the application of one high current barrage test vector and its corresponding low current barrage test vector to a node under radiation simulation testing.

example of how radiation testing was conducted on a node in the Wang and Gong SAFF design can be seen in Figures 3.8.5-3.8.7. Figure 3.8.5 shows the choice of node SB1 in and the propostion of connecting a current source to the node whereupon either a high current barrage test vector or a low current barrage test vector would be applied.

Figure 3.8.6 shows the results of running the low current barrage test vector shown in Figure 3.8.4 on node SB1 of Figure 3.8.5. The results were that several spikes appeared on the output Q0\_1 but no incorrect information was latched into the flip-flop. However, when the high current barrage test vector shown in Figure 3.8.4 was applied to node SB1 in Figure 3.8.5 it resulted in an incorrect value being latched into output Q0\_1 at approximately 0.24µs in Figure 3.8.7.

Figure 3.8.5: Example node to be tested for radiation hardness.

Figure 3.8.6: Results of running a low current barrage test vector on node SB1 in Figure 3.8.5.