Air Force Institute of Technology

# AFIT Scholar

Theses and Dissertations

Student Graduate Works

6-2006

# Active FPGA Security through Decoy Circuits

Bradley D. Christiansen

Follow this and additional works at: https://scholar.afit.edu/etd

Part of the Electrical and Electronics Commons

#### **Recommended Citation**

Christiansen, Bradley D., "Active FPGA Security through Decoy Circuits" (2006). *Theses and Dissertations*. 3316.

https://scholar.afit.edu/etd/3316

This Thesis is brought to you for free and open access by the Student Graduate Works at AFIT Scholar. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of AFIT Scholar. For more information, please contact richard.mansfield@afit.edu.

# ACTIVE FPGA SECURITY THROUGH DECOY CIRCUITS

## THESIS

Bradley D. Christiansen, Major, USAF

AFIT/GE/ENG/06-15

DEPARTMENT OF THE AIR FORCE AIR UNIVERSITY

AIR FORCE INSTITUTE OF TECHNOLOGY

Wright-Patterson Air Force Base, Ohio

APPROVED FOR PUBLIC RELEASE; DISTRIBUTION UNLIMITED

The views expressed in this thesis are those of the author and do not reflect the official policy or position of the United States Air Force, Department of Defense, or the U.S. Government.

# ACTIVE FPGA SECURITY THROUGH DECOY CIRCUITS

## THESIS

Presented to the Faculty

Department of Electrical and Computer Engineering

Graduate School of Engineering and Management

Air Force Institute of Technology

Air University

Air Education and Training Command

In Partial Fulfillment of the Requirements for the

Degree of Master of Science in Electrical Engineering

Bradley D. Christiansen, Bachelor of Science

Major, USAF

March 2006

# APPROVED FOR PUBLIC RELEASE; DISTRIBUTION UNLIMITED

AFIT/GE/ENG/06-15

# ACTIVE FPGA SECURITY THROUGH DECOY CIRCUITS

Bradley D. Christiansen, Bachelor of Science

Major, USAF

Approved: Dr. Yong C. Kim (Chairman)

Dr. Rusty O. Baldwin (Member)

Dr. Barry E. Mullins (Member)

1 MAR '06

Date

1 Mar Ø6 Date

Mar 06 Date

#### Abstract

Field Programmable Gate Arrays (FPGAs) based on Static Random Access Memory (SRAM) are vulnerable to tampering attacks such as readback and cloning attacks. Such attacks enable the reverse engineering of the design programmed into an FPGA. To counter such attacks, measures that protect the design with low performance penalties should be employed.

This research proposes a method which employs the addition of active decoy circuits to protect SRAM FPGAs from reverse engineering. The effects of the protection method on security, execution time, power consumption, and FPGA resource usage are quantified. The method significantly increases the security of the design with only minor increases in execution time, power consumption, and resource usage. For the circuits used to characterize the method, security increased to more than one million times the original values, while execution time increased to at most 1.2 times, dynamic power consumption increased to at most two times, and look-up table usage increased to at most seven times the original values. These are reasonable penalties given the size and security of the modified circuits. The proposed design protection method also extends to FPGAs based on other technologies and to Application-Specific Integrated Circuits (ASICs).

In addition to the design methodology proposed, a new classification of tampering attacks and countermeasures is presented.

iv

#### Acknowledgments

Whoa! What a ride! At times, the terrain was very rugged. However, "My God hath been my support; he hath led me through mine afflictions in the wilderness; and he hath preserved me" (2 Nephi 4:20).

I express my sincere appreciation to my faculty advisor, Dr. Kim. His guidance and encouragement were keys to the creation of this thesis. *Kamsahamnida*.

I thank Dr. Baldwin and Dr. Mullins for their review of, and recommendations for improvement to, this document.

I appreciate the time and effort expended by Mr. Louis Floyd and Mr. Dan Williams to proofread and comment about drafts of the manuscript.

I am very grateful for the care and concern shown for my family by Mr. Mike Bristow, Mr. John Duncan, and Mr. Dan Williams during this difficult period. They and their prayers were a great support to us.

I am eternally grateful to have such a great wife. Her love and belief in me have carried me through these eighteen months. She has endured more than I during this period, and her achievements have been greater, especially in the care and development of our children. She is the primary reason our children greet me with a smile and open arms. I am grateful to have received the love of my wife and children to remind me of the truly important treasures of life.

#### Bradley D. Christiansen

V

# **Table of Contents**

| 1 age                                             |

|---------------------------------------------------|

| Abstractiv                                        |

| Acknowledgmentsv                                  |

| Table of Contents vi                              |

| List of Figuresx                                  |

| List of Tables xii                                |

| 1. Introduction1                                  |

| 1.1 Motivation1                                   |

| 1.2 Problem Statement                             |

| 1.3 Research Scope                                |

| 1.4 Research Contributions                        |

| 1.5 Thesis Preview4                               |

| 2. Background                                     |

| 2.1 Chapter Overview                              |

| 2.2 FPGA Defined                                  |

| 2.3 Definition of Terms9                          |

| 2.4 Reverse Engineering Tutorial11                |

| 2.5 Attacks13                                     |

| 2.6 Protections/Countermeasures                   |

| 2.7 Classification of Attacks and Countermeasures |

| 2.7.1 Introduction                                |

| 2.7.2 Previous Works                              |

| 2.7.3 Classification of Threats                   |

| 2.7.4 Classification of Countermeasure Security Levels |    |

|--------------------------------------------------------|----|

| 2.8 Related Circuit Protection Research                | 31 |

| 2.9 Summary                                            | 32 |

| 3. Methodology                                         |    |

| 3.1 Chapter Overview                                   | 33 |

| 3.2 Problem Definition                                 |    |

| 3.2.1 Goals and Hypotheses                             |    |

| 3.2.2 Approach                                         |    |

| 3.3 System Boundaries                                  |    |

| 3.4 System Services                                    |    |

| 3.5 Workload                                           | 41 |

| 3.6 Performance Metrics                                | 41 |

| 3.7 Parameters                                         | 42 |

| 3.7.1 System                                           |    |

| 3.7.2 Workload                                         |    |

| 3.8 Factors                                            | 43 |

| 3.9 Evaluation Technique                               | 45 |

| 3.10 Experimental Design                               | 46 |

| 3.11 Analyze and Interpret Results                     | 47 |

| 3.12 Summary                                           | 47 |

| 4. Design Algorithm                                    | 49 |

| 4.1 Chapter Overview                                   | 49 |

| 4.2 Combination Lock                                   | 49 |

| 4.3     | Decoy Circuit Generation from Truth and State Tables    | 52   |

|---------|---------------------------------------------------------|------|

|         | 4.3.1 Combinational Circuit                             | 54   |

|         | 4.3.2 Sequential Circuit                                | 63   |

| 4.4     | Decoy Circuit Generation from Boolean Equations         | 66   |

| 4.5     | Decoy Circuit Generation from Gate-level Representation | 69   |

| 4.6     | Decoy Circuit Generation from Existing VHDL             | 72   |

| 4.7     | Decoy Circuit Generation through Partial Scrambling     | 77   |

| 4.8     | Summary                                                 | 84   |

| 5. Resu | lts and Analysis                                        | 87   |

| 5.1     | Chapter Overview                                        | 87   |

| 5.2     | Security                                                | 87   |

|         | 5.2.1 Combination Lock                                  | 91   |

|         | 5.2.2 Combinational Circuit                             | 92   |

|         | 5.2.3 Sequential Circuit                                | 93   |

|         | 5.2.4 VHDL and Partial Scrambling                       | 97   |

| 5.3     | Execution Time                                          | 98   |

|         | 5.3.1 Combination Lock                                  | 98   |

|         | 5.3.2 Combinational Circuit                             | 99   |

|         | 5.3.3 Sequential Circuit                                | 101  |

|         | 5.3.4 VHDL and Partial Scrambling                       | 101  |

| 5.4     | Power Consumption                                       | .102 |

|         | 5.4.1 Combination Lock                                  | 103  |

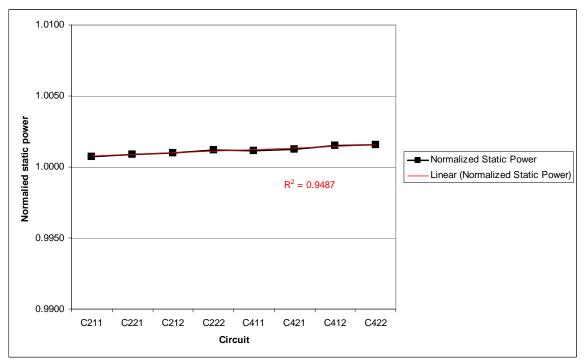

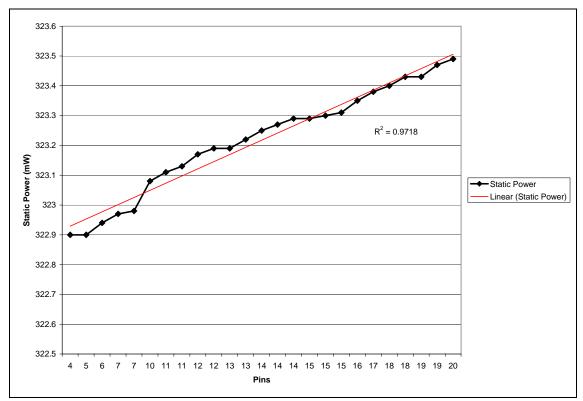

|         | 5.4.2 Combinational Circuit                             | 105  |

|         |                                                         |      |

| 5.4.3 Sequential Circuit 1                               | 107 |

|----------------------------------------------------------|-----|

| 5.4.4 VHDL and Partial Scrambling 1                      | 109 |

| 5.4.5 Observations 1                                     | 109 |

| 5.5 Resource Usage1                                      | 110 |

| 5.5.1 Combination Lock 1                                 | 111 |

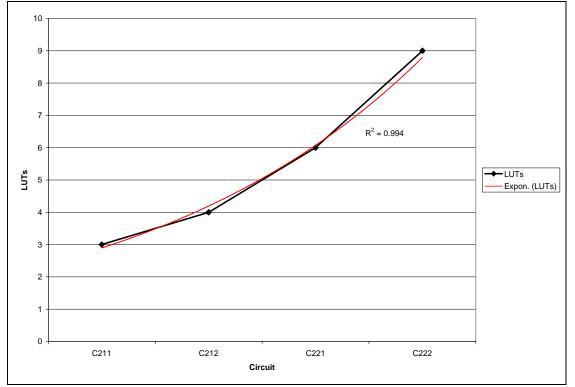

| 5.5.2 Combinational Circuit 1                            | 111 |

| 5.5.3 Sequential Circuit 1                               | 115 |

| 5.5.4 VHDL and Partial Scrambling 1                      | 117 |

| 5.6 Combining a Combination Lock with Modified Circuits1 | 117 |

| 5.7 Summary1                                             | 119 |

| 6. Conclusions and Recommendations1                      | 121 |

| 6.1 Chapter Overview1                                    | 121 |

| 6.2 Conclusions of Research                              | 121 |

| 6.3 Significance of Research                             | 122 |

| 6.4 Recommendations for Action1                          | 122 |

| 6.5 Recommendations for Future Research1                 | 123 |

| 6.6 Summary1                                             | 124 |

| Appendix: Data Analysis Tables1                          | 125 |

| Bibliography1                                            | 136 |

| Vita1                                                    | 141 |

# List of Figures

| Fig | ïgure Page                                              |    |  |

|-----|---------------------------------------------------------|----|--|

| 1.  | Downed F-117A.                                          | 1  |  |

| 2.  | Captured EP-3E.                                         | 2  |  |

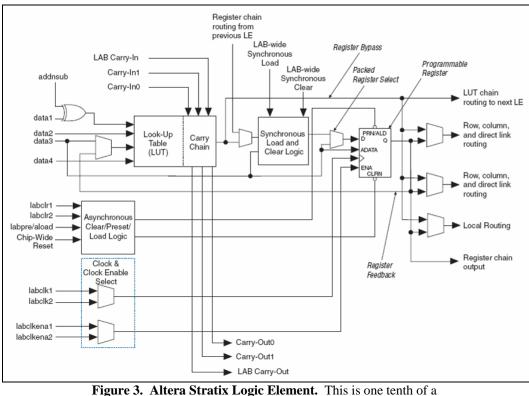

| 3.  | Altera Stratix Logic Element.                           | 7  |  |

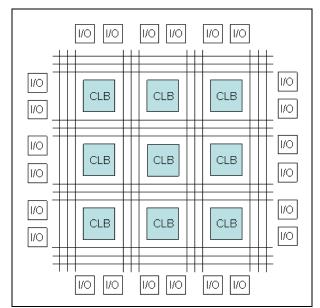

| 4.  | Generalized FPGA interconnect                           | 8  |  |

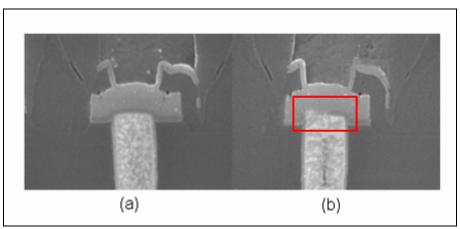

| 5.  | Cross sections of unprogrammed and programmed antifuses | 8  |  |

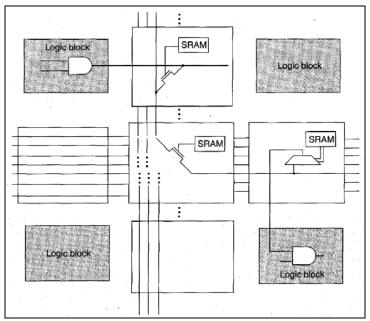

| 6.  | FPGA with SRAM switches.                                | 9  |  |

| 7.  | Black Box attack                                        | 14 |  |

| 8.  | Cloning attack                                          | 14 |  |

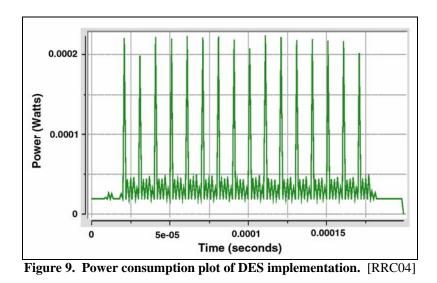

| 9.  | Power consumption plot of DES implementation.           | 15 |  |

| 10. | Reverse engineering an ASIC                             | 16 |  |

| 11. | Use of an encrypted configuration file.                 | 19 |  |

| 12. | On-FPGA PROM                                            | 19 |  |

| 13. | Rearranging design modules                              | 20 |  |

| 14. | Matrix classification.                                  | 27 |  |

| 15. | Methodology design flow                                 | 36 |  |

| 16. | System and component under test.                        | 38 |  |

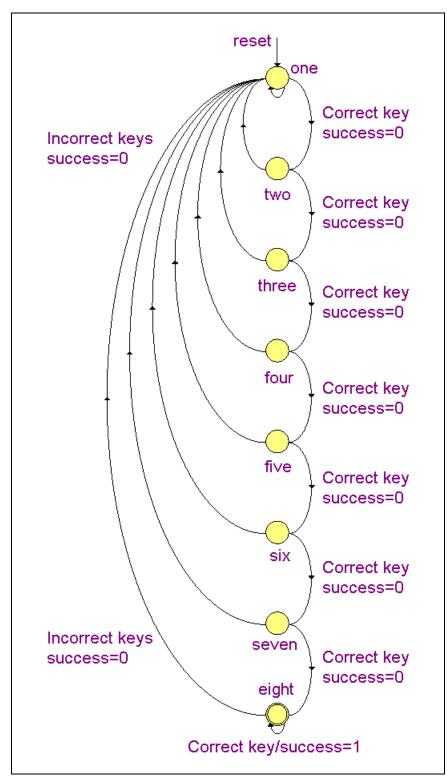

| 17. | Eight-state Combination Lock                            | 53 |  |

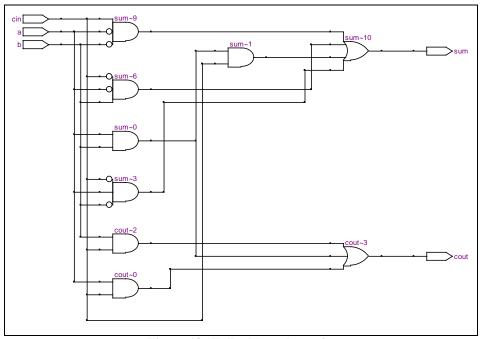

| 18. | Full adder schematic                                    | 55 |  |

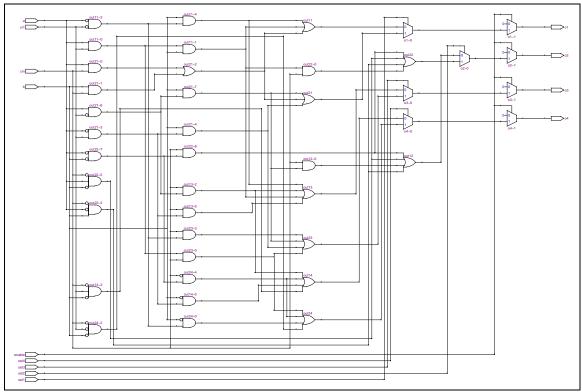

| 19. | Modified full adder schematic                           | 62 |  |

| 20. | Three-bit up counter schematic.                         | 63 |  |

| Fig | Ire Page                                                  |

|-----|-----------------------------------------------------------|

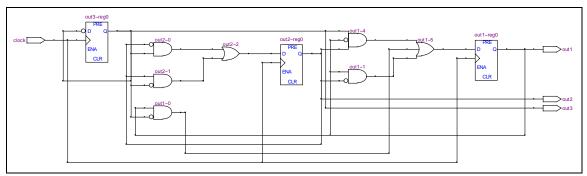

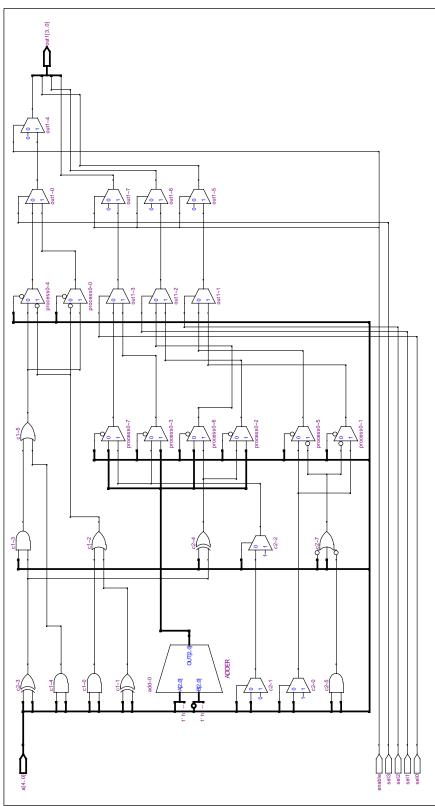

| 21. | Page 3 of 4 of the modified counter schematic             |

| 22. | Original gate-level representation70                      |

| 23. | Modified gate-level representation71                      |

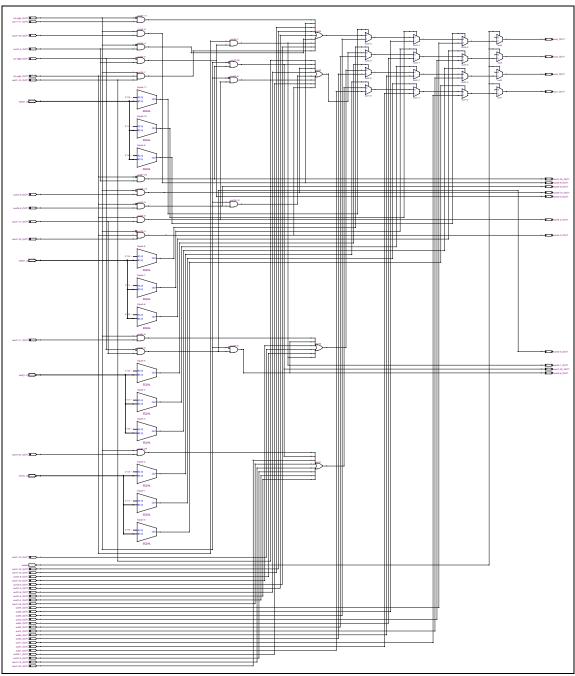

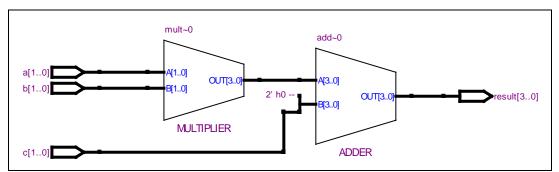

| 24. | Four-bit priority encoder schematic74                     |

| 25. | Modified four-bit priority encoder schematic78            |

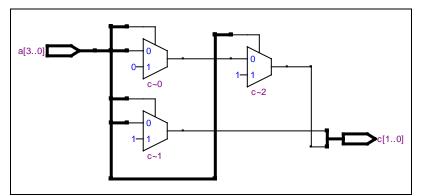

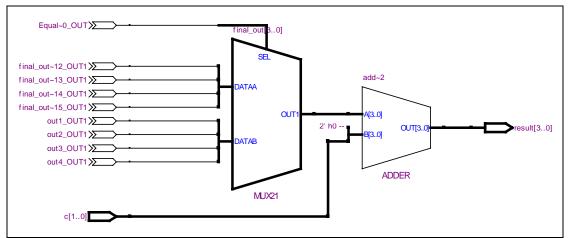

| 26. | Schematic of $result = a*b+c$                             |

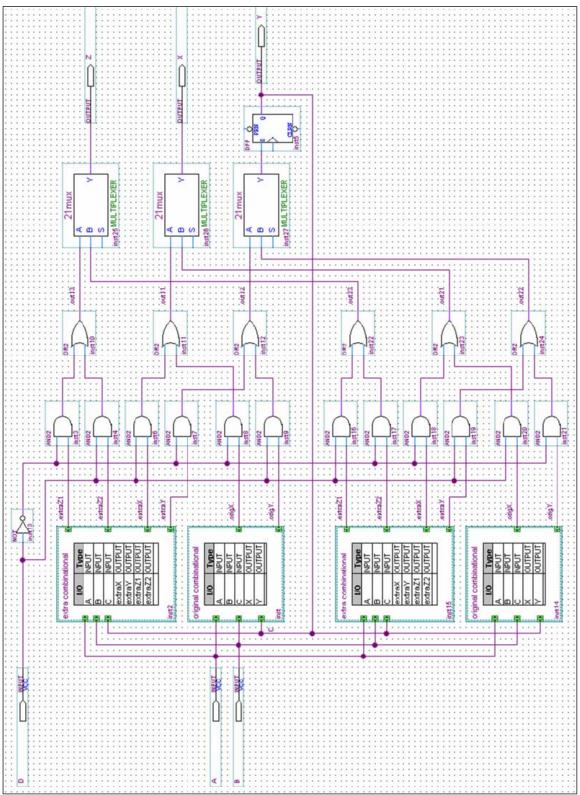

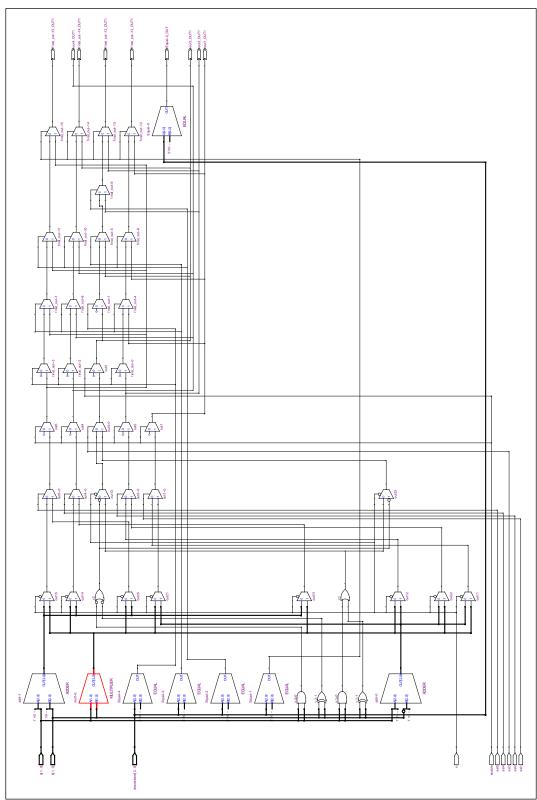

| 27. | Page 1 of partial scrambling schematic                    |

| 28. | Page 2 of partial scrambling schematic                    |

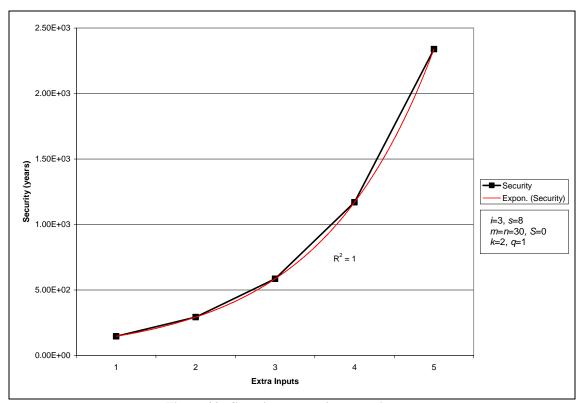

| 29. | Security vs. varying extra inputs                         |

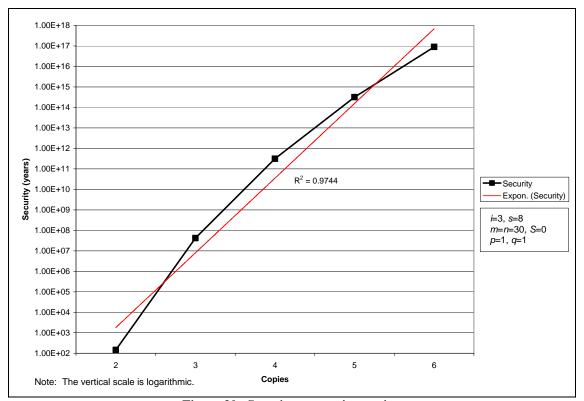

| 30. | Security vs. varying copies                               |

| 31. | Security vs. varying extra outputs                        |

| 32. | Quartus II PowerPlay Power Analyzer Tool 103              |

| 33. | Combinational circuits' static power consumption 106      |

| 34. | Correlation between pin count and static power            |

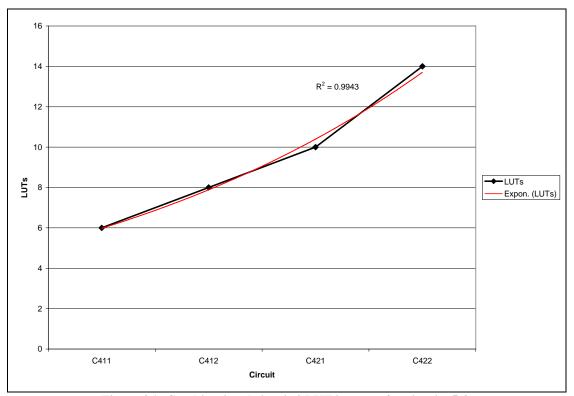

| 35. | Combinational circuits' LUT increase for circuits 1-4 112 |

| 36. | Combinational circuits' LUT increase for circuits 5-8 113 |

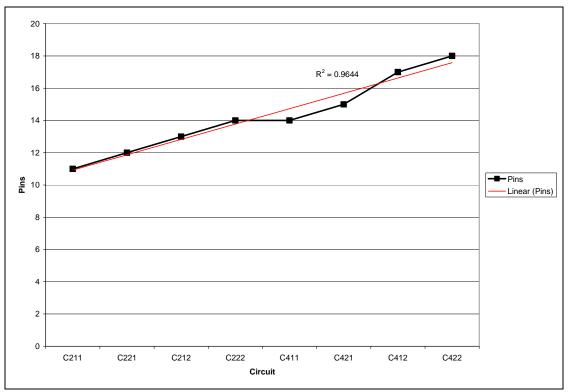

| 37. | Combinational circuits' pin increase                      |

# List of Tables

| Tab | Fable   Page                                                |      |  |  |

|-----|-------------------------------------------------------------|------|--|--|

| 1.  | Attacks and countermeasures.                                | . 21 |  |  |

| 2.  | IBM security level scheme.                                  | . 23 |  |  |

| 3.  | Design steps and attacks they counter.                      | . 38 |  |  |

| 4.  | Failure mode combinations                                   | . 40 |  |  |

| 5.  | Full adder truth table                                      | . 54 |  |  |

| 6.  | Expanded full adder truth table                             | . 55 |  |  |

| 7.  | Expanded full adder truth table with complete top half.     | . 57 |  |  |

| 8.  | Final expanded full adder truth table                       | . 57 |  |  |

| 9.  | Three-bit up counter state table.                           | . 63 |  |  |

| 10. | Copies 1 and 2 of modified counter                          | . 64 |  |  |

| 11. | Copies 3 and 4 of modified counter                          | . 65 |  |  |

| 12. | Resulting truth table from Boolean equation modification.   | . 68 |  |  |

| 13. | Resulting state table from gate-level modification          | . 72 |  |  |

| 14. | Priority encoder truth table                                | . 73 |  |  |

| 15. | Resulting truth table for partial scrambling                | . 80 |  |  |

| 16. | Combinational multiplexer input and output combinations.    | . 80 |  |  |

| 17. | Combination Locks' security contributions                   | . 91 |  |  |

| 18. | Analysis of Combination Locks' security contributions.      | . 92 |  |  |

| 19. | Combinational circuits' security metrics.                   | . 93 |  |  |

| 20. | Analysis of combinational circuits' security contributions. | . 94 |  |  |

| Tab | ble                                                              | Page |

|-----|------------------------------------------------------------------|------|

| 21. | Sequential circuits' security metrics                            | 95   |

| 22. | Analysis of sequential circuits' security contributions          | 96   |

| 23. | Original and scrambled existing VHDL circuits' security.         | 97   |

| 24. | Security metrics of original and partially scrambled circuits.   | 98   |

| 25. | Combination Locks' maximum clock frequencies                     | 98   |

| 26. | Results of Combination Locks' maximum frequency analysis table.  | 99   |

| 27. | Combinational circuits' execution times.                         | 100  |

| 28. | Results of combinational circuits' execution time analysis table | 101  |

| 29. | Existing VHDL designs' execution times.                          | 101  |

| 30. | Partially scrambled and original circuits' execution times       | 102  |

| 31. | Combination Locks' power consumption                             | 103  |

| 32. | Results of Combination Locks' static power analysis table        | 104  |

| 33. | Results of Combination Locks' dynamic power analysis table       | 104  |

| 34. | Combinational circuits' power consumption                        | 105  |

| 35. | Results of combinational circuits' static power analysis table   | 107  |

| 36. | Results of combinational circuits' dynamic power analysis table  | 107  |

| 37. | Sequential circuits' power consumption                           | 108  |

| 38. | Results of sequential circuits' static power analysis table      | 108  |

| 39. | Results of sequential circuits' dynamic power analysis table.    | 108  |

| 40. | VHDL circuits' power consumption.                                | 109  |

| 41. | Partially scrambled circuits' power consumption                  | 109  |

| Tab | Ie                                                             | Page |

|-----|----------------------------------------------------------------|------|

| 42. | Combination Locks' resource usage                              | 111  |

| 43. | Results of Combination Locks' LUT analysis table               | 111  |

| 44. | Combinational circuits' resource usage                         | 112  |

| 45. | Results of combinational circuits' LUT analysis table          | 114  |

| 46. | Results of combinational circuits' pin analysis table.         | 115  |

| 47. | Sequential circuits' resource usage                            | 115  |

| 48. | Results of sequential circuits' LUT analysis table.            | 116  |

| 49. | Results of sequential circuits' pin analysis table.            | 117  |

| 50. | VHDL circuits' resource usage.                                 | 117  |

| 51. | Partially scrambled circuits' resource usage                   | 117  |

| 52. | Combination Lock and modified full adder                       | 118  |

| 53. | Combination Lock and modified counter.                         | 118  |

| 54. | Combination Lock and modified VHDL circuit                     | 118  |

| 55. | Analysis of Combination Locks' maximum frequencies.            | 125  |

| 56. | Analysis of Combination Locks' static power consumptions.      | 125  |

| 57. | Analysis of Combination Locks' dynamic power consumptions      | 126  |

| 58. | Analysis of Combination Locks' LUT usages                      | 126  |

| 59. | Analysis of combinational circuits' execution times            | 127  |

| 60. | Analysis of combinational circuits' static power consumptions  | 128  |

| 61. | Analysis of combinational circuits' dynamic power consumptions | 129  |

| 62. | Analysis of combinational circuits' LUT usages                 | 130  |

| Table                                                           |     |

|-----------------------------------------------------------------|-----|

| 63. Analysis of combinational circuits' pin usages.             | 131 |

| 64. Analysis of sequential circuits' static power consumptions  | 132 |

| 65. Analysis of sequential circuits' dynamic power consumptions | 133 |

| 66. Analysis of sequential circuits' LUT usages.                | 134 |

| 67. Analysis of sequential circuits' pin usages                 | 135 |

## ACTIVE FPGA SECURITY THROUGH DECOY CIRCUITS

#### 1. Introduction

#### 1.1 Motivation

As an F-117A Nighthawk stealth fighter made its way to its target on 27 March 1999 [FAS00], enemy forces pieced together its flight path, from takeoff to the target area. Using knowledge from previous Nighthawk strikes, possible returns from low-frequency radars, and the hint from a dropped bomb, the enemy was able to down the aircraft with a surface-to-air missile (cf., Figure 1). Fortunately, the pilot safely ejected and was rescued before being captured. The decision had to be made whether to destroy the remains of the plane to protect its stealth technology [Lam02] and the specialized circuits used in the flight control system.

**Figure 1. Downed F-117A.** Note the HO designation for Holloman AFB, NM, home of the F-117As. [FAS00]

Almost two years later, as a U.S. Navy EP-3E Aires II surveillance aircraft was conducting a routine mission in international airspace, a Chinese fighter bumped the EP-3E's wing, necessitating an emergency landing in Chinese territory (cf., Figure 2) [New01]. Although the crew was trained to destroy sensitive equipment in the event of capture [DoD01], the equipment may not have been sufficiently destroyed before landing to preclude Chinese exploitation. Among the systems that might have been exploited by the Chinese was the Link-11 secure communications system [Smi01]. It is also possible that classified circuits were also compromised.

**Figure 2. Captured EP-3E.** Note the chipped propeller blade at (2) and the missing radome at (3). [Tri01]

The above examples illustrate the need to protect critical technologies in military systems. The United States Air Force goes to great lengths to maintain technological superiority, avoid technological surprise, and achieve a return on investment from advanced technology development. Protecting integrated circuit designs found in weapons systems helps to achieve those goals [AFR05]. Such protection enables a weapon system to have a long life without compromising its capabilities. Additionally, a protected design can prevent an adversary from increasing his knowledge base and advancing his technology [HuS99].

Field-programmable gate arrays (FPGAs) are increasingly taking the place of application-specific integrated circuits (ASICs) due to their flexibility, increasing densities [Act02], and lower non-recurring engineering costs. Reprogrammable FPGAs are attractive for applications with requirements that change over time, where changes need to be implemented quickly, or for quickly fielding a new product. As more commercial systems are designed with FPGAs rather than ASICs, an increasing number of military systems will also contain FPGAs.

FPGAs have some intrinsic vulnerabilities, including the possibility of extracting the circuit design through reverse engineering [AFR05]. In the corporate arena, protecting a design on an FPGA from reverse engineering helps maintain a competitive edge, market share, and revenues. Securing a design in a military application maintains its technological advantage, prevents the exploitation of a design by an adversary, and consequently can save lives.

#### **1.2 Problem Statement**

The challenge, then, is to devise methods of protecting designs on FPGAs that completely eliminate reverse engineering vulnerabilities or, at a minimum, introduce delays that make reverse engineering impractical. A worthwhile new design protection method balances increased security against increased implementation costs, decreased system performance, and increased operations and maintenance costs [AFR05].

#### 1.3 Research Scope

The purpose of this research is to devise a method to secure integrated circuit designs implemented in FPGAs and then evaluate its effectiveness. A novel process is

proposed to protect designs specified using truth or state tables, with Boolean equations or that are already implemented in VHDL (Very high-speed integrated circuit Hardware Description Language). The proposed design methodology will produce secure application-specific integrated circuits, as well as secure FPGA designs. This procedure is demonstrated using several common circuits. The power consumption, execution times, and resource usage of the original and modified circuits are measured and compared.

### **1.4 Research Contributions**

This research proposes a new attack classification scheme that combines of cost and time. A countermeasure classification system easily correlated to the attack classification is also developed.

In addition, the research contributes an innovative technique that provides significant protection to FPGA and ASIC designs against reverse engineering. The performance penalty to apply this technique to FPGA designs are only minor increases in execution time and power consumption. Increased resource requirements can be accommodated with the generally available excess FPGA resources.

The design methodology is demonstrated using circuits described in various ways from Boolean equations to VHDL. Additionally, the flexibility of the algorithm to modify only a portion of a circuit is illustrated.

#### 1.5 Thesis Preview

Chapter 2 provides background information on FPGAs and reverse engineering, gives definitions, lists and classifies attacks and countermeasures, and presents relevant

existing research. Chapter 3 describes the testing methodology and provides an overview of the proposed circuit modification process. Chapter 4 gives the details of the proposed design methodology by illustrating it with several examples. Chapter 5 presents the test results and analyses. Chapter 6 presents a summary, explains the significance of the research, and makes recommendations for further study.

## 2. Background

#### 2.1 Chapter Overview

The purpose of this chapter is to provide sufficient background for the reader to understand the context of the research. After covering FPGA architectures, the terms *tampering* and *reverse engineering* are defined, followed by a brief tutorial about reverse engineering. Finally, FPGA design threats and possible countermeasures to these threats are presented, as well as a threat and countermeasure classification scheme.

### 2.2 FPGA Defined

A field-programmable gate array (FPGA) is a computer chip that a user can program in the field to accomplish a particular function. For example, a user could program an FPGA to be a general purpose microprocessor or to encrypt or decrypt data. FPGAs are generally divided into cells called configurable logic blocks (CLBs), which may contain the following:

- look-up tables (LUTs) to accomplish logic functions, such as

Y = (B AND D) XOR C,

- arithmetic logic gates to implement other logic functions or to combine outputs from LUTs,

- multiplexers to select particular outputs, and

- storage elements (memory) such as D flip-flops.

Figure 3 shows a portion of a CLB. CLBs are interconnected with wires that can be

**Figure 3.** Altera Stratix Logic Element. This is one tenth of a Logic Array Block (Altera's nomenclature for a CLB). [Alt05]

programmed to provide specific paths between CLBs or to input or output pins as shown in Figure 4 [BrR96, Xil05].

Programmable elements are controlled by switches that determine the function of that building block. The switches are generally either antifuses or SRAM (static random access memory) elements. An antifuse is a 'sandwich' configuration consisting of an insulator between two conductors. The insulator electrically isolates the conductors when the antifuse is not programmed. When the antifuse is programmed by applying a voltage, the insulator provides a low-resistance path between the conductors. Figure 5 shows an unprogrammed antifuse (a) and a programmed antifuse (b). The boxed area of (b) shows where the connection between the two conductors has been made. Antifuse FPGAs are

Figure 4. Generalized FPGA interconnect. Adapted from [BrR96].

Figure 5. Cross sections of unprogrammed and programmed antifuses. [Act06]

one-time-programmable, while SRAM FPGAs are reprogrammable. The appropriate value to either activate or deactivate a particular path or function is stored in an SRAM element. Figure 6 shows SRAM switches configured to connect two logic blocks through two interconnections and a multiplexer. An SRAM element loses its programming (theoretically) when power is disconnected. To program an FPGA, a configuration file (also called a bit stream) is usually created in a software application. This configuration

Figure 6. FPGA with SRAM switches. [BrR96]

file is downloaded directly to the FPGA or to a memory device (flash memory or a PROM – programmable read-only memory). The memory stores the configuration file and programs an SRAM-based FPGA at start-up since the SRAM switches lose their state after a loss of power. The bits in the configuration file dictate the switch settings [BrR96, WGP04].

### 2.3 Definition of Terms

It is important to understand the definitions of the following terms as they are used in this research.

*Tampering* is defined as activities that secretly, dishonestly, or interfere or intrude without consent [Pri05]. Such activities, accomplished through direct physical or remote electronic access, include destruction, modification, observation, and theft of integrated circuits [IEEE93]. The theft could be of the entire chip for use in another system or of

the design for duplication and distribution. The entire circuit, or just a portion thereof, could be destroyed, modified, or observed. The observation of a circuit, possibly in conjunction with modifications, could reveal private information or proprietary algorithms, technologies, or processes.

As the following examples show, tampering has varying levels of difficulty and complexity.

- If physical access is achieved, an entire chip could be stolen, or, with more effort, the circuit design itself could be stolen.

- Modifying an ASIC directly may be more difficult than remotely modifying a reprogrammable FPGA.

- The entire chip could be destroyed or, with more sophisticated tools, a specific area of the chip could be targeted for destruction.

- The leads of a chip could be probed or, at an increased level of complexity, the signals within a circuit could be observed.

*Reverse Engineering*, a subset of tampering, is defined as methods, processes, and analyses used to recreate a design from a final product [Ang06] or other process outputs [Geo05], to create a "representation at a higher level of abstraction" [J-STD95], or to determine the technology that is used [Geo05].

In general, reverse engineering requires more effort and resources than tampering alone. For example, deciphering a secret key in a cryptographic system is tampering, but discovering how the algorithm is implemented would be reverse engineering. Likewise, obtaining an unencrypted FPGA configuration file and using it to program other FPGAs would be tampering, while deciphering the configuration file would be reverse engineering. Tampering to observe an integrated circuit is a prerequisite for analyses that would use the observations to recreate the design.

Being a subset of tampering, reverse engineering also occurs at varying levels. At one level, a cryptographic implementation may be discovered. At another level, the fabrication processes and technology used in that implementation might be determined.

Thus, a secure FPGA design would prevent interference with its operation, intrusion into its functionality, its replication, and the determination of its fundamental technology.

Anti-Tampering and Anti-Reverse Engineering are actions taken to hinder or prevent tampering and reverse engineering.

#### 2.4 Reverse Engineering Tutorial

Since the goal of the proposed design methodology is to produce an FPGA design resistant to reverse engineering, it is appropriate to review the stages of a reverse engineering process. The following list of stages, which apply specifically to ASICs, is excerpted from [CEL99]. Following this list of stages, the application of these stages to FPGAs is discussed.

According to [CEL99], the following stages of the reverse engineering process were identified at the Argonne National Laboratory's 1998 Reverse Engineering Workshop.

1. Sample preparation: An ASIC must be cross-sectioned or chemically etched to reveal its internal construction. Since this step is destructive,

great care must be taken to avoid damaging the components of interest. Several samples may be required, as well as several iterations of slicing or etching subsequent layers and the next stage [AnK96].

- Image acquisition: Once the internal construction is revealed, it must be imaged, section by section. The images of the sections are pieced together for a complete image. A scanning electron microscope may be required, depending on the size of the transistors.

- Geometric description: Geometric data is extracted from the image file and converted to a geometric data stream. Information about the technology employed to realize the circuit is necessary for the conversion of the image to geometric data.

- 4. Transistor netlist: From the geometric data, transistors are identified through design-rule checkers.

- Gate-level netlist: Specific gates are identified from collections of transistors. For example, AND or NOR gates may be identified. Since gates generally have the same geometry, pattern-matching enables the process to be automated.

- Module-level description: With the gates identified, modules such as multiplexers and full adders can be abstracted.

- 7. Register-transfer and behavioral descriptions: Further abstraction generates a register-transfer-level representation and eventually a

behavioral description. (In 1999, the technology to produce these interpretations was not available.)

Reverse engineering an FPGA design uses stages similar to those listed above. If the FPGA is antifuse-based, it has to be cross-sectioned and imaged. For an SRAMbased FPGA, sample preparation and image acquisition determine the contents of the SRAM elements that act as switches. (The process of discovering the state of an SRAM is discussed further in Section 2.5.) The processes of generating a geometric description and a transistor netlist are equivalent to correlating each switch with an FPGA interconnect intersection or CLB element. With that correlation information, gates and modules can be composed.

An FPGA can also be reverse engineered from its unencrypted configuration file. In such a case, obtaining the FPGA bit stream is equivalent to the sample preparation stage for an ASIC. A correlation similar to the one above is done between the bits of the file and entities on the FPGA, and the process continues with the reconstruction of gates and modules.

#### 2.5 Attacks

Partly due to its flexibility and its programming method, an FPGA is vulnerable to reverse engineering (i.e., the determination of the implemented circuit design). Various methods can derive the functionality of a programmed FPGA. These methods include [WGP04]:

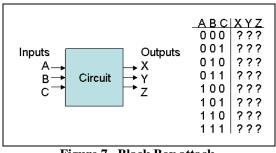

a. Black Box Attacks: All possible inputs are applied and the outputs are observed as illustrated in Figure 7.

Figure 7. Black Box attack.

b. Readback Attacks: The FPGA's configuration data is read directly from the FPGA.

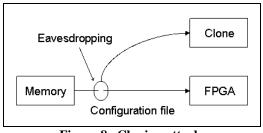

c. Cloning Attacks: An attacker eavesdrops on the transmission of the configuration file from memory to the FPGA and uses the stolen file to program a clone FPGA as shown in Figure 8.

Figure 8. Cloning attack.

d. Reverse-Engineering an unencrypted configuration: This is done after attack (b) or (c) above.

e. Side-Channel Attacks: These attacks include power consumption analysis, timing analysis, electromagnetic (EM) radiation analysis, and injecting faults to reveal functionality. Figure 9 shows the power consumption plot of a Data Encryption Standard implementation, which clearly shows 16 rounds of the algorithm.

f. Physical Attacks: Since SRAM cells are not entirely erased when power is disconnected, physical attacks via accessing them include mechanical probing, accessing the test scan path, removing layers of a chip, and using electron microscopes. However, physical attacks against antifuse FPGAs do not seem practical since much of the chip must be destroyed by cross-sectioning or by removing multiple layers to reveal a single antifuse connection.

The methods for determining the value that is or was in an SRAM element deserve additional discussion. Non-destructive methods include:

- I<sub>DDQ</sub> (quiescent power-supply current) testing measures the supply current to a device after applying a series of test vectors. An abnormal measurement would indicate that the device has been stressed and that its operating characteristics have changed [Gut01].

- Measuring the substrate and gate currents observes the amount of stress a device has experienced [Gut01].

- Using the circuitry intended for device testing, such as JTAG boundary scan [Gut01].

- Voltage contrast imaging detects logic levels and voltages through the examination of the differences in the brightness of the voltage intensity image [SoA93].

One invasive technique uses a focused ion beam (FIB) workstation to drill minute access holes for probing deeply buried entities. The FIB workstation can also inject metal probe points for easier device examination [Gut01]. Although the literature does not describe the use of these methods of attack against SRAM FPGAs, it is conceivable that they could be used to determine the programming of such a device [WGP04].

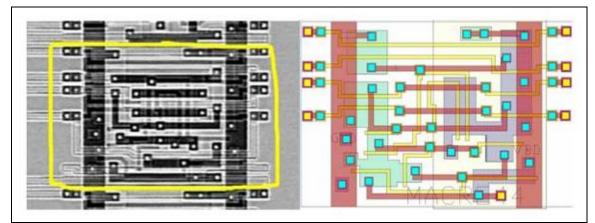

The attacks that could also be used against ASICs include black box, sidechannel, and physical attacks [RRC04]. For example, with the destruction of only six chips, an Intel 80386 was reverse engineered in two weeks using the specific physical attack described in the Reverse Engineering Tutorial section above [AnK96]. Figure 10 illustrates the third stage in the reverse engineering process, where an integrated circuit image is converted to a geometric data format such as Graphic Design Station II (GDSII).

Figure 10. Reverse engineering an ASIC. [ACA02]

#### 2.6 Protections/Countermeasures

There are various approaches to protect a design on an FPGA or to mitigate the effects of its theft and reproduction. Policy and law protections such as patents and copyrights allow private companies to sue an alleged thief for damages. To aid in proving ownership in the event a design is stolen, the original producer might embed a watermark in the design [JYP03]. Export control laws attempt to maintain a nation's technological advantage. Security classifications and laws that prescribe punishments for espionage and treason also attempt to protect a nation's technological capital. If classified knowledge is compromised, a non-disclosure agreement (NDA), which is generally executed to obtain a security clearance, may have been breached. NDAs are also signed before a manufacturer grants access to its FPGA bit stream design [WGP04] or to the mapping between switches and function elements.

If these policy protections are subverted, months or years could elapse before a theft is discovered, by which time significant damage may have already been done. Such was the case with atomic bomb secrets stolen from Los Alamos and given to the Soviet Union [FBI06]. In the corporate arena, by the time such a theft is discovered, a company's market share may have already been lost to a company in a foreign nation that not only refuses to enforce patents but also encourages such piracy. Likewise, a disgruntled former employee of Company X could begin employment with Company Y and describe how a watermark might be removed from a design stolen from Company X.

With these subversions, stronger protections are warranted for high-value assets. Encryption has long been utilized to protect messages. However, even encryption algorithms will eventually be cracked as was the case of the Data Encryption Standard [EFF98]. As described in FIPS 140-2, there are also physical protections such as containers, tamper-evident coatings, and circuitry that detects and responds to unauthorized access [NIS02]. One example of a FIPS 140-2 Security Level 4 device is the IBM 4758 PCI Cryptographic Coprocessor [IBM06]. The circuitry of this device is surrounded by a mesh that detects physical penetrations and abnormal environmental conditions in parameters such as temperature and radiation. The response to such an attack is the erasure of critical secret data.

There are countermeasures stronger than policy that can protect the design of a circuit programmed into an FPGA. These include [WGP04]:

a. The complexity of state-of-the-art FPGAs, which mitigates a black box attack.

b. A security bit can prevent a readback attack. However, it is possible that fault injection may defeat this countermeasure. Applying unusual voltages or voltage transients could reset the security bit [AnK96]. If fault injection is a possibility, the FPGA should be placed in a secure environment.

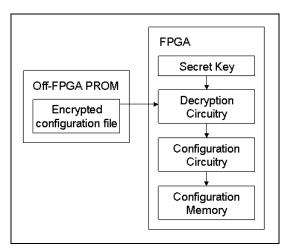

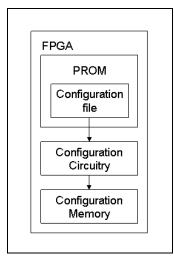

c. Encrypting, as in Figure 11, and/or storing the configuration file in memory resident on the FPGA, as in Figure 12, can prevent cloning attacks. Encryption also prevents reverse engineering a file. (The devices described in [Xil05], however, can decrypt an encrypted configuration file.)

18

Figure 11. Use of an encrypted configuration file. Adapted from [Kea01].

Figure 12. On-FPGA PROM.

d. Techniques to prevent side-channel attacks include inserting random values to mask secret information, smoothing power traces, and changing logic at the transistor level.

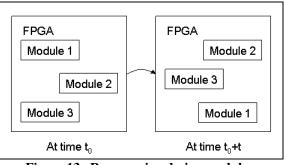

e. To prevent physical attacks on SRAM FPGAs, memory retention should be reduced as much as possible through methods such as periodically inverting the bits, applying an opposite current, inserting dummy cycles, or rearranging the data using dynamically reconfigurable FPGAs as in Figure 13.

Figure 13. Rearranging design modules.

Table 1 summarizes the attacks and countermeasures discussed above Though the attacks and countermeasures listed are not necessarily specific to FPGA designs, some of the methods have been used against or on underlying FPGA technologies, such as SRAM. Attacks and countermeasures with respect to embedded systems have also been examined [RRC04].

# 2.7 Classification of Attacks and Countermeasures

#### 2.7.1 Introduction

An attacker who tampers with an integrated circuit can harm both the developer and the user of the circuit. If the effects of tampering are widespread, the developer is damaged by a reputation for circuit malfunctions. Furthermore, revenue could be lost if the design is copied and distributed, since the developer does not recoup the research and development costs. Likewise, the user may be denied service due to destructive tampering of a circuit or lose information that was supposedly secure due to observation of a circuit. In security and defense applications, lives could be lost due to tampering or reverse engineering. A tampering attack could result in a malfunction that causes a

| Attack                                                                  | Used against<br>FPGAs?              | Countermeasure                                                                                                   | Available in<br>commercial<br>FPGAs?        |  |  |

|-------------------------------------------------------------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------------|--|--|

| Black Box                                                               | Yes                                 | Inherent FPGA size and design complexity                                                                         | Yes                                         |  |  |

| Readback<br>(Security bit<br>possibly overcome<br>with fault injection) | Yes<br>(Not<br>specifically)        | Employ a security bit<br>(Secure environment)<br>See 1 and 2 below                                               | Yes<br>(User-specific)<br>See 1 and 2 below |  |  |

| Cloning<br>Reverse-Engineer<br>the configuration<br>file                | Yes<br>Yes                          | <ol> <li>Encrypt the<br/>configuration file</li> <li>Store the<br/>configuration file in<br/>FPGA</li> </ol>     | 1. Yes<br>2. Varies                         |  |  |

| Physical                                                                | Little<br>specifically<br>published | Reduce the memory-<br>retention effects                                                                          | Not specifically                            |  |  |

| Side-Channel                                                            | Yes                                 | <ul><li>A. Insert random values</li><li>B. Smooth the power</li><li>traces</li><li>C. Change the logic</li></ul> | Not specifically                            |  |  |

Table 1. Attacks and countermeasures. [WGP04]

vehicle to crash or the loss of the designed technological advantage of a weapon or countermeasure.

Countermeasures are employed to thwart such tampering attacks. These methods vary in cost and effectiveness. Thus, an understandable classification is needed to apply appropriate protection mechanisms against perceived threats. However, there are no universally accepted classifications of threats and protection levels for integrated circuits. In fact, there is no IEEE standard that addresses either of these classifications. This section presents a classification of tampering threats and a corresponding classification of protection levels. In [ADD91], Abraham et al. propose a classification of attackers based on the attacker's knowledge and available resources. They also present a security level scheme that appears to be loosely correlated with the attacker classification. Anderson and Kuhn apply the attacker classification to specific attack examples in [AnK96] and [AnK97]. Actel Corporation in [Act02] also references [ADD91] to compare the security offered by their FPGAs to that offered by other manufacturers' devices.

The following subsection explains the IBM classifications and describes the usage of these classifications in other applications. Threats against ASICs and FPGAs are also presented and classified. Examples of countermeasures are given, along with a security level classification correlated to the threat classification. Alternate classifications based on the time required to crack a design are also given.

### 2.7.2 Previous Works

To define the potential physical threats against the Transaction Security System,

attackers are categorized as [ADD91]:

Class I (clever outsiders)—They are often very intelligent but may have insufficient knowledge of the system. They may have access to only moderately sophisticated equipment. They often try to take advantage of an existing weakness in the system, rather than try to create one.

Class II (knowledgeable insiders)—They have substantial specialized technical education and experience. They have varying degrees of understanding of parts of the system but potential access to most of it. They often have access to highly sophisticated tools and instruments for analysis.

Class III (funded organizations)—They are able to assemble teams of specialists with related and complementary skills backed by great funding resources. They are capable of in-depth analysis of the system, designing sophisticated attacks, and using the most sophisticated analysis tools. They may use Class II adversaries as part of the attack team.

Security levels which correlate to the resources (time, money, knowledge) required to conduct an attack on a system are also defined. Table 2 summarizes their security levels.

|                   | Definition                                                     |                                                         |                                    |                                                                 |  |  |  |  |  |

|-------------------|----------------------------------------------------------------|---------------------------------------------------------|------------------------------------|-----------------------------------------------------------------|--|--|--|--|--|

| Security<br>Level | Knowledge/Skills                                               | Tools/Equipment                                         | Tool or<br>Total Cost              | Notes                                                           |  |  |  |  |  |

| ZERO              |                                                                |                                                         |                                    | No special security features                                    |  |  |  |  |  |

| LOW               |                                                                | Common lab or shop tools                                |                                    | Some security features                                          |  |  |  |  |  |

| MODL              | Some specialized knowledge                                     | More expensive                                          | \$500 - \$5,000<br>(tools)         |                                                                 |  |  |  |  |  |

| MOD               | Some special<br>skills and<br>knowledge                        | Special tools and equipment                             | \$5,000 -<br>\$50,000 (tools)      | Attack time-<br>consuming, but<br>successful                    |  |  |  |  |  |

| MODH              | Special skills and<br>knowledge;<br>adversarial team<br>effort | Available, but<br>expensive to buy<br>and operate       | \$50,000 -<br>\$200,000 or<br>more | Attack could be<br>unsuccessful                                 |  |  |  |  |  |

| HIGH              | Team of specialists                                            | Highly<br>specialized,<br>which may have<br>to be built | \$1,000,000 or<br>more             | Known attacks<br>unsuccessful;<br>attack success in<br>question |  |  |  |  |  |

Table 2. IBM security level scheme. Adapted from [ADD91].

Even though both an attacker classification and a protection level scheme are defined, the correlation between the two is not clear. It appears that the LOW security level corresponds to a Class I attacker, the MOD security level could correspond to a Class II attacker, and the HIGH security level corresponds to a Class III attacker. In addition, the security levels MODL and MODH do not clearly fall between the outsiders of Class I and the insiders of Class II and between the insiders of Class II and the funded organizations of Class III, respectively. Thus, how is an outsider classified who is more than clever but less than a funded organization? The IBM attacker categorization has been used to classify several example attacks [Ank96]. The IBM scheme defines Class I as the application of low and high voltages, and power and clock transients, which can be applied non-invasively. For example, directing UV light at the security lock cell of an EPROM, or removing a smartcard chip with a knife, nitric fuming acid, and acetone are Class I attacks. A Class II attack removes each chip layer, imaging it using the Schottky effect and an electron beam, and reconstructing the collection of images with image processing software. Another Class II attack uses a focused ion beam (FIB) workstation to actively attack a chip. Although the use of the FIB workstation is considered Class II, a Class I attacker could rent time on such machines. A Class III attacker is one whose resources are such that "chip contents cannot be kept from" the attacker [AnK96].

Class distinctions do not hold when an attacker can access equipment available predominantly to an attacker of a higher class. For example, a Class I attacker can rent time on a FIB workstation, a tool predominantly available to a Class II attacker. Furthermore, the insider threat is not considered, and Class II is also applied to academics who apparently have no privileged information.

Actel Corporation references [ADD91] in [Act02], but it is not entirely clear whether the reference is to IBM's attacker classification or security level scheme. Actel definitions of security levels are close, though not exact, restatements of IBM's security level definitions. However, Actel uses numbers and + or - for the security levels rather than names as IBM did. In addition, the words "Class" and "Level" are interchanged. With this modification of IBM's attacker classification and/or security level scheme,

Actel claims that conventional SRAM FPGAs are Class or Level 1, SRAM FPGAs with DES encryption are Level 2, and Actel products are Level 2+. A Level 3 example is not given, and the insider threat is not addressed.

[ETS05] applies the IBM classification to attackers of bus encryption hardware. The classification is presented in the context of smartcard memories but was used only sparingly [NPS03]. Others assert the IBM classification should not be used to describe the tamper-proof level of wireless sensor networks, but rather, the level should be defined in terms of network availability [PaS05].

Attacks have also been categorized using privacy, integrity, or availability attacks [RRC04]. Another classification divides attacks among physical, side-channel, and software attacks. Countermeasures are presented and correlated with the second attack classification, but they are not classified with a security level [RRC04].

These previous classifications have obstacles to their understandability and use. Classifying the insider threat, as well as the outsider with moderate resources but no private information, has been a challenge. Also problematic has been the distinction between classes when a member of one class has access to tools of another class. If both attack/attacker classification and countermeasure security level classification are given, the correlation between them is generally absent. The attacker classification is often used to determine a security level. Whatever the obstacles, there are not universally accepted classifications of threats and countermeasure security levels and a correlation between the two.

### **2.7.3** Classification of Threats

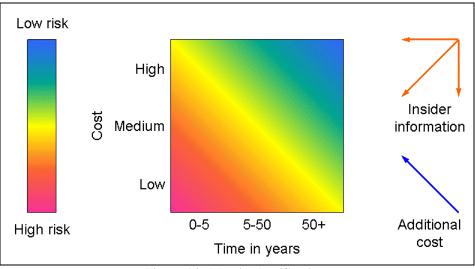

To overcome the shortfalls of the previous classifications, the following matrix categorization is proposed. This categorization uses the attacks, not attackers, based on the resources and time required to successfully accomplish the attack. In this way, the dissolution of classes does not occur when a member of one class uses tools of another. The proposed classification also accounts for the insider threat and the outsider with moderate resources but no inside knowledge. Finally, a correlation can easily be made to protection levels, as discussed in the next subsection.

It is appropriate to classify the attacks and not the attackers. For example, a bullet-proof vest should work whether a gun is fired by a child or a senior citizen. An automatic teller machine should thwart an attack whether perpetrated by a drug addict or by the mafia.

Attacks are classified according to both cost and time, and the classification is depicted graphically in Figure 14. In some respects, cost and time can be considered independent. However, since the application of additional resources (personnel, equipment, etc.) at an additional cost may reduce the time required for a successful attack, this relationship is indicated by the blue arrow in Figure 14 that shows that as the cost increases, time may decrease. Insider knowledge is removed as a class, but this variable is depicted by the three orange arrows in Figure 14, indicating that such information may reduce the cost, time, or both. Insider knowledge may include information about designs and/or processes. The potential for damage from an insider information-enabled attack is increased due to the access available [Ver01]. According

Figure 14. Matrix classification.

to the 2005 CSI/FBI Computer Crime and Security Survey, incidents from the inside occur about as often as incidents from the outside [GLL05].

A qualitative explanation of the cost levels follows.

- Low-cost attack: A successful attack requires limited resources (equipment, knowledge, and personnel). The attack could be executed within an academic laboratory containing only ordinary equipment or possibly at home. Examples of low-cost attacks include black box, faultinjection [AnK96], protocol failure [AnK97], and smartcard physical attacks [AnK96]. Assuming the appropriate access is obtained, perhaps by the end user, reading back and cloning an unencrypted bitstream could also cost very little.

- Medium-cost attack: Moderate resources are required for a successful attack. Specialized academic and corporate laboratories probably contain the required equipment. More people can be applied to the attack, since

the benefits are expected to be greater. Power and timing analyses, determining SRAM contents, and ASIC reverse engineering are examples of medium-cost attacks.

• High-cost attack: These attacks entail vast resources, such as are available to governments and organized crime. Many people, perhaps in multiple locations engage in the attack, since success has implications for years to come. Funds could also be spent to acquire insider knowledge. Examples of these attacks include reverse engineering a bitstream and physically attacking an antifuse FPGA [WGP04].

The time categories are described next.

- 0-5 years: Little time is required or invested for an attack to ensure an appropriate return on the investment. This timeframe provides the highest profit margin if an attack is successful. Reading back and cloning an unencrypted bitstream, given the requisite opportunity, requires little time. For example, an Intel 80386 was reverse engineered in two weeks.

- 5-50 years. Despite the length of time required for success, an attack may

proceed based on the expected payoff. Reverse engineering a bitstream

could take longer than 5 years. Given a large enough design on an FPGA,

more than five years could be expended to determine the values remaining

in the SRAM elements that were programmed.

50+ years. Weapons systems generally have life spans of less than 50 years, so providing protection against a 50-year-long attack provides a comfortable measure of security. A black box attack could last longer than 50 years, if the circuit has a great amount of inputs, has bi-directional inputs and outputs, and is constructed with state machines [WGP04]. Fifty years or more could be required to locate 2-5% of millions of antifuses [Act06].

#### 2.7.4 Classification of Countermeasure Security Levels

From the above categorization of threats, a classification of security levels can be easily made. The security level of an anti-tampering action corresponds to the classification of the attack. For example, a countermeasure that ensures an attack requires more than fifty years for success is a 50-plus-year security measure, and a countermeasure is High-cost if it entails great expense for a successful attack. In this way, the security level of an action correlates to the resources and time required for a successful attack. This meets the goal of Anderson and Kuhn: "the level of tamper resistance offered by any particular product can be measured by the time and cost penalty that the protective mechanisms impose on the attacker" [AnK97].

An example of a Low-cost countermeasure is the use of complex FPGAs and designs to prevent black box attacks. Another example of a Low-cost countermeasure is setting the security bit to prevent readback. If the security bit can be compromised with fault injection and a secure location houses the design, Medium cost or higher could be imposed depending on the location.

Storing the FPGA configuration file in an on-FPGA PROM is another example of a Medium-cost security measure, since attacks similar to SRAM physical attacks would be required to extract the file from the PROM.

One High-cost security measure is bitstream encryption to prevent cloning and reverse engineering. Rearranging design modules to frustrate SRAM physical attacks is another potentially High-cost measure, since more resources would have to be applied to discover the scarce traces of memory contents.

In addition to the higher cost of attacking an SRAM FPGA that uses dynamic reconfiguration, the length of time required could be greater than five years. Another countermeasure that could impose an attack length of greater than five years is configuration file encryption.

Employing on-FPGA PROM for configuration file storage may provide less than a five-year delay. A security bit to prevent readback may also provide protection for less than five years. However, a secure location for placing an FPGA could be designed to repel unauthorized entry for at least five years, if not fifty.

Although the use of complex designs and FPGAs is low-cost, it requires a significant amount of time to perform a black box attack against such a design or FPGA. Due to this time constraint, an attacker would probably consider an attack with a lower time requirement.

Security measures designed to require extensive resources and a considerable amount of time to break include the protection of nuclear weapons [AnK96]. It would be a great benefit to humanity for those security measures to be updated when necessary and to succeed even when faced with an attack from within. This highlights the need for a classification system to ensure designs are adequately secured against perceived threats.

The leak of insider information of appropriate quality and quantity will decrease the security level of a design. A design considered to be of High cost and require ten years to crack could be reduced to medium cost or require only four years to crack, or both, with the proper knowledge. Steps to mitigate the effects of unauthorized disclosure of proprietary information include the compartmentalization of knowledge among developers and restricting of access to the development of products. Expending additional resources for an attack may also reduce the time required for success.

The proposed classification provides a mapping of attacks and countermeasures so that appropriate measures can be employed to counter perceived threats. Efforts to refine the time and cost estimates of particular attacks are still needed. As Anderson and Kuhn state, "Estimating these penalties is clearly an important problem, but is one to which security researchers, evaluators and engineers have paid less attention than perhaps it deserves" [AnK97].

#### 2.8 Related Circuit Protection Research

Current research in circuit protection deals mostly with methods other than modifying the circuit itself, such as encryption and physical access prevention. A review of the literature has not revealed any work in decoy circuits for protection. As far as can be ascertained, this research is the first of its kind dealing with the use of decoy circuits to protect digital circuit designs.

# 2.9 Summary

This chapter contains background information concerning FPGAs, attacks against these devices, and countermeasures that can protect these devices from the attacks. The architecture and programming of FPGAs are described. Definitions of tampering and reverse engineering are presented. Reverse engineering is further explained with a tutorial. Attack examples and countermeasures are listed and illustrated. Finally, a framework for classifying the attacks and countermeasures is offered.

### 3. Methodology

### 3.1 Chapter Overview

This chapter presents the methodology for implementing and testing the proposed anti-reverse engineering scheme. The results of the tests performed characterize the effects of the design modification procedure in terms of security, FPGA resources consumed, execution time, and power usage. An overview of the actual design modification process is given. The details of the process are described in Chapter 4.

#### **3.2 Problem Definition**

#### **3.2.1** Goals and Hypotheses

This research proposes a new scheme of anti-tampering through decoy circuits, and determines the effect of a proposed design modification methodology on the security, execution time, power consumption, and chip area utilization of a given circuit. Multiple circuits are produced using this methodology. The security, execution time, chip area utilization, and power consumption of the resultant circuits are measured and compared with the original circuits' values of these parameters.

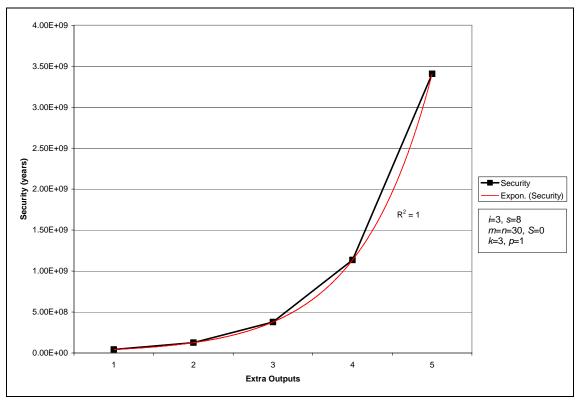

The security of the circuits is defined as the time required to conduct a brute force, black box attack on the FPGAs. This time is calculated by dividing the number of required cycles by a frequency and the appropriate scaling factor to express a value in years. To calculate the number of cycles required for an original circuit, all possible input combinations are considered. Thus, if *m* is the number of original inputs and *S* is the number of sequential elements in the circuit, the number of required cycles for the original circuit is  $2^{m+S}$  (*S*=0 for a combinational circuit). The number of cycles required to conduct a black box attack on a modified design is the sum of half the number of possible input combinations to a Combination Lock (explained later) and the product of half the number of input combinations to the modified circuit and the possible output combinations in length equal to the total number of outputs. That is, the cycles required to conduct a black box attack on a modified design ( $A_{mod}$ ) is

$$A_{\text{mod}} = \frac{1}{2}l + \frac{1}{2}(2^{m+S+p}) \text{(output combinations of length } n+q) \tag{1}$$

where *l* is the number of Combination Lock input combinations, *p* is the number of additional inputs, *n* is the number of original outputs, and *q* is the number of additional outputs. The number of cycles required for a modified combinational circuit is expected to be at least 4 times the cycles required for an original circuit (of 3 total inputs and 2 total outputs), in addition to  $1.68 \times 10^7$  cycles for the smallest combination lock circuit considered. With increases in the numbers of inputs, outputs, and copies added to a circuit, the security is expected to increase exponentially. An increase in the number of possible combination lock input combinations, due to increases in the numbers of inputs and states, is also expected to exponentially increase the security of a modified circuit.

A slight increase is expected in the execution time of the resulting FPGA designs. However, this increase is not expected to be worse than approximately ten gate delays – one or two LUTs. This translates to a minor clock frequency decrease, or only one clock cycle penalty at the original circuit's frequency. This increase is mainly due to a multiplexer introduced into the modified circuit. The execution time is expected to increase by nearly a constant amount over an original circuit's execution time, even with increases in the numbers of added inputs, outputs, and circuit copies.

Both the area and power consumption are expected to increase less than approximately 400% when adding one extra input and one copy. Adding an input would suggest a doubling of the area of the original circuit. Making a copy of the circuit with an extra input would suggest a further doubling, for a total of a 400% increase in area, and thus power consumption. However, logic functions are implemented in FPGA lookup tables (LUTs), and one LUT in the original design may have the capacity to accept the extra input without consuming another resource. As inputs, outputs, and copies are added to a circuit, the area and power are expected to increase linearly.

### 3.2.2 Approach

Various steps are taken in the methodology to ensure a secure FPGA design. These reduce an FPGA design's susceptibility to reverse engineering. However, the increased operation costs are reasonable for the security achieved as a result of the methodology.

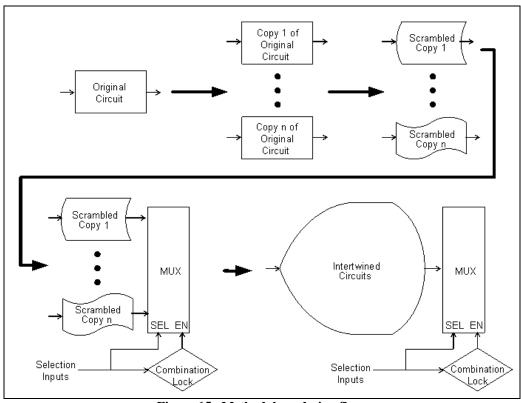

The design flow is illustrated conceptually in Figure 15. An original circuit is copied multiple times and scrambled. (Although the word 'copy' is used, the scrambled circuits are not exact duplicates of each other.) Scrambling adds extraneous inputs and outputs. The scrambled circuit produces correct outputs based on predetermined extraneous inputs. For example, if two extraneous inputs are added, then Scrambled Copy 1 may only produce the correct value for output 2 when the extraneous input is 10<sub>2</sub>, and Scrambled Copy 2 may only produce the correct value for output 2 when the extraneous input is 00<sub>2</sub>, etc. The extraneous output values are chosen to confuse and produce multiple patterns so the original output pattern is hidden among many possible

Figure 15. Methodology design flow.

patterns. The scramblings are such that all original outputs are produced for a given extraneous input combination (for example, 00<sub>2</sub> or 10<sub>2</sub>), although each correct output may be produced by a different copy. To select the correct output, additional Selection Inputs and a multiplexer (MUX) are added. The Selection Inputs determine the copy from which to choose a particular output. The Selection Inputs are synchronized at runtime with the extraneous inputs. For example, when the extra input is 10<sub>2</sub>, the Selection Inputs cause the MUX to select output 2 from Scrambled Copy 1 and output 1 from Scrambled Copy 2. A Combination Lock state machine (inspired by [MIT01]) is added to increase the effort needed in a black box attack. The correct sequence of inputs to the Combination Lock causes the assertion of a signal that enables the MUX. Finally, the Scrambled Copies are intertwined to produce confusion, subject to the constraint that the intertwining does not exceed the expected increase in execution time stated above. Intertwining is achieved by placing elements of one circuit among elements of others and by crossing paths. Explicit intertwining is not investigated in this study. Implicit intertwining may occur as the design software allocates FPGA resources. For example, the design application may assign portions of different circuits to the same CLB.

The proposed methodology is for designs that can be described using truth tables or Boolean equations, designs with gate-level representations, designs already written in VHDL, or designs which require only a portion of the design to be modified.

The various steps of the design flow aid in countering the attacks listed in Chapter 2. Table 3 lists the design steps and the attacks they counter. Although the readback and cloning attacks are not directly countered with the design methodology, understanding a reverse-engineered configuration file obtained with those two attacks is thwarted. Gaining knowledge of the scramblings, the input synchronization, and the correct Combination Lock key is a significant challenge.

Even though significant security for a design is attained with the methodology, the research hypothesis is the performance impacts are reasonable. To determine this, the security, execution time, power consumption, and chip area utilization values of several original circuits are gathered and processed according to the methodology. The parameter values of the resulting circuits are collected and compared with the original circuits' values.

|                     | Attacks   |                                                  |          | •            |                                                                                                                                                            |

|---------------------|-----------|--------------------------------------------------|----------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Design Step         | Black Box | Reverse-<br>engineering<br>configuration<br>file | Physical | Side-channel | Notes                                                                                                                                                      |

| Copying             |           |                                                  | X        | X            | Power and EM analyses<br>and probing more tedious.                                                                                                         |

| Scrambling          | X         | Х                                                | X        | X            | More inputs and outputs increase<br>reverse-engineering time and<br>number of combinations to try.<br>Power and EM analyses and<br>probing more difficult. |

| Selection           | X         | Х                                                |          |              | Sequencing increases complexity of analysis.                                                                                                               |

| Combination<br>Lock | X         |                                                  | Х        |              | Prevents operation. Time-<br>consuming to physically disable.                                                                                              |

| Intertwining        |           |                                                  | X        | X            | Power and EM analyses and probing more difficult.                                                                                                          |

Table 3. Design steps and attacks they counter.

# 3.3 System Boundaries

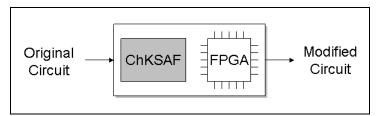

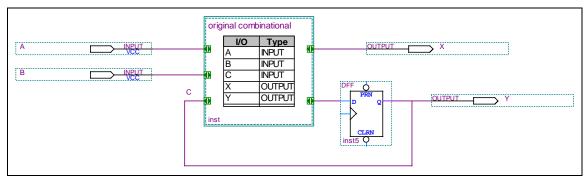

Figure 16 depicts the system under test, which consists of the methodology and an FPGA. The component under test (shaded in Figure 16) is the methodology – the Christiansen-Kim Security Algorithm for FPGAs (ChKSAF, pronounced "check safe"). The input to the system is a circuit, and the output is a circuit modified according to the algorithm.

Figure 16. System and component under test.

The study is limited to SRAM FPGAs, but the methodology easily extends to antifuse FPGAs, and should extend to ASICs as well. Since the goal of this research is to produce a viable design methodology that yields a significant increase in security without major adverse consequences to speed, power, and area usage, small and simple circuits are processed with the algorithm to keep the problem manageable. Although the proposed design modification algorithm can be automated, which study is not herein, the modifications are produced by hand.

#### **3.4 System Services**

The general service provided by the system is a secure FPGA design that functions as the original circuit does. The system either fails or succeeds at producing a design that functions correctly. If the modified circuit does not perform correctly, it is not worth placing in a system since it won't produce the correct output. Only successfully functioning designs are considered in this study.

With a successfully functioning design, the system may succeed or fail at providing acceptable security, execution time, chip area utilization, and power consumption. Table 4 lists the combinations of these outcomes with the metrics listed in order of importance from left to right. The color code indicates the number of successes in the outcome combinations – blue for four success, green for three successes, yellow for two successes, orange for one success, and red for no successes. When there is a failure in any of the four measurements, the designer must decide whether there is sufficient excess from the successful metrics that can be traded to the initially unsuccessful metrics to meet their goals. Alternatively, the designer could implement system changes that

| Security | <b>Execution time</b> | Power   | Area    | Outcome                        |

|----------|-----------------------|---------|---------|--------------------------------|

| Success  | Success               | Success | Success | Ideal                          |

| Success  | Success               | Success | Failure | Trade space or system changes? |

| Success  | Success               | Failure | Success | Trade space or system changes? |

| Success  | Failure               | Success | Success | Trade space or system changes? |

| Failure  | Success               | Success | Success | Trade space or system changes? |

| Success  | Success               | Failure | Failure | Trade space or system changes? |

| Success  | Failure               | Success | Failure | Trade space or system changes? |

| Success  | Failure               | Failure | Success | Trade space or system changes? |

| Failure  | Success               | Success | Failure | Trade space or system changes? |

| Failure  | Success               | Failure | Success | Trade space or system changes? |

| Failure  | Failure               | Success | Success | Trade space or system changes? |