## Air Force Institute of Technology

## **AFIT Scholar**

Theses and Dissertations

Student Graduate Works

3-8-2007

## APHID: Anomaly Processor in Hardware for Intrusion Detection

Samuel A. Hart

Follow this and additional works at: https://scholar.afit.edu/etd

Part of the Hardware Systems Commons

#### **Recommended Citation**

Hart, Samuel A., "APHID: Anomaly Processor in Hardware for Intrusion Detection" (2007). Theses and Dissertations. 3100.

https://scholar.afit.edu/etd/3100

This Thesis is brought to you for free and open access by the Student Graduate Works at AFIT Scholar. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of AFIT Scholar. For more information, please contact richard.mansfield@afit.edu.

### APHID: Anomaly Processor in Hardware for Intrusion Detection

THESIS

Samuel Hart, Captain, USAF  ${\rm AFIT/GCE/ENG/07\text{-}04}$

#### DEPARTMENT OF THE AIR FORCE AIR UNIVERSITY

# AIR FORCE INSTITUTE OF TECHNOLOGY

Wright-Patterson Air Force Base, Ohio

APPROVED FOR PUBLIC RELEASE; DISTRIBUTION UNLIMITED.

| The views expressed in this thesis are those of the author and official policy or position of the United States Air Force, Department the United States Government. |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                                                                     |  |

# APHID: Anomaly Processor in Hardware For Intrusion Detection

#### THESIS

Presented to the Faculty

Department of Electrical and Computer Engineering

Graduate School of Engineering and Management

Air Force Institute of Technology

Air University

Air Education and Training Command

In Partial Fulfillment of the Requirements for the

Degree of Master of Science in Computer Engineering

Samuel Hart, B.S.C.E. Captain, USAF

March 2007

APPROVED FOR PUBLIC RELEASE; DISTRIBUTION UNLIMITED.

# APHID: ANOMALY PROCESSOR IN HARDWARE FOR INTRUSION DETECTION

Samuel Hart, B.S.C.E. Captain, USAF

## Approved:

| $/\mathrm{signed}/$                  | $08~\mathrm{Mar}~2007$ |

|--------------------------------------|------------------------|

| Maj Paul D. Williams, PhD (Chairman) | date                   |

| /signed/                             | 08 Mar 2007            |

| Dr. Barry E. Mullins (Member)        | date                   |

| /signed/                             | 08 Mar 2007            |

| Dr. Yong C. Kim (Member)             | date                   |

#### Abstract

The Anomaly Processor in Hardware for Intrusion Detection (APHID) is a step forward in the field of co-processing intrusion detection mechanism. By using small, fast hardware primitives APHID relieves the production CPU from the burden of security processing. These primitives are tightly coupled to the CPU giving them access to critical state information such as the current instruction(s) in execution, the next instruction, registers, and processor state information. By monitoring these hardware elements, APHID is able to determine when an anomalous action occurs within one clock cycle. Upon detection, APHID can force the processor into a corrective state, or a halted state, depending on the required response. APHID primitives also harden the production system against attacks such as Distribute Denial of Service attack and buffer overflow attacks. APHID is designed to be fast and agile, with the ability to create multiple monitors that switch in and out of monitoring with the context switches of the production processor to highly focused coverage over multiple devices and sections of code.

## Acknowledgements

This thesis is dedicated to my family. I owe you all so much and I am grateful for every sacrifice you have made to allow this accomplishment.

Many thanks go out to all who helped with this thesis. To my advisor, for all of your extra hours dedicated to giving these ideas a sanity check. To our sponsor, AFRL/SNTA Anti Tamper Software Protection Initiative, thank you for the financial support. To my thesis committee, thank you for your time, inputs and suggestions.

Samuel Hart

# $Table\ of\ Contents$

|                                                           | Page |

|-----------------------------------------------------------|------|

| Abstract                                                  | iv   |

| Acknowledgements                                          | V    |

| List of Figures                                           | ix   |

| List of Tables                                            | X    |

| List of Abbreviations                                     | xi   |

| I. Introduction                                           | 1    |

| 1.1 Proposed Solution                                     | 2    |

| 1.1.1 Merits                                              | 2    |

| 1.1.2 Costs                                               | 3    |

| 1.2 Document Organization                                 | 3    |

| II. Related Research and Background Information           | 4    |

| 2.1 Definition of Intrusion                               | 4    |

| 2.2 Classification of Intrusions                          | 4    |

| 2.2.1 Bugs                                                | 4    |

| 2.2.2 Flaws                                               | 5    |

| 2.2.3 Vulnerabilities                                     | 5    |

| 2.2.4 Design Vulnerabilities                              | 5    |

| 2.3 Detection Timeliness                                  | 7    |

| 2.3.1 Measuring Time to Detection                         | 7    |

| 2.4 Attack Surfaces                                       | 8    |

| 2.5 General Classification of Intrusion Detection Systems | 8    |

| 2.5.1 Network IDS                                         | 8    |

| 2.5.2 Host IDS                                            | 9    |

| 2.5.3 Host-based IDS Execution Classes                    | 11   |

| 2.6 Related Research in IDS Co-processing                 | 12   |

| 2.6.1 Cryptographic Co-processing                         | 12   |

| 2.7 CuPIDS                                                | 12   |

| 2.7.1 CuPIDS Goals                                        | 13   |

| 2.7.2 CuPIDS System Architecture                          | 13   |

| 2.7.3 Basic Capabilities                                  | 13   |

| 2.7.4 Strengths and Weaknesses                            | 15   |

| 2.8 Security Enhanced Chip Multiprocessor                 | 16   |

| 2       | 9 CoPilot                                                |

|---------|----------------------------------------------------------|

| 2       | 10 Other Security Systems Using Methods Similar to APHID |

|         | 2.10.1 Techniques for Monitoring Control Flow            |

|         | 2.10.2 ESP: The Embedded Sensor Project                  |

|         | 2.10.3 Protecting the Stack with Hardware                |

| 2       | 11 Classifying the Hardness of a Computing System        |

| 2       | 12 Networking Background                                 |

|         | 2.12.1 The Network Protocol Stack                        |

|         | 2.12.2 Internet Protocol Packets                         |

|         | 2.12.3 Denial of Service                                 |

| 2       | 13 Reconfigurable Hardware                               |

|         | 2.13.1 Useful Hardware Primitives                        |

| 2       | 14 Chapter Summary                                       |

| II. APH | ID Model                                                 |

| 3       | 1 Problem Definition                                     |

|         | 3.1.1 Research Hypothesis                                |

| 3       | 2 Solution Framework                                     |

|         | 3.2.1 Research Goals                                     |

| 3       | 3 Approach                                               |

| 3       | 4 Device Driver Monitor                                  |

|         | 3.4.1 Modular design                                     |

|         | 3.4.2 Anomaly detection                                  |

|         | 3.4.3 Justifications of Sizes                            |

|         | 3.4.4 Monitor Primitives                                 |

|         | 3.4.5 Address Comparator                                 |

|         | 3.4.6 State Machine                                      |

| 3       | 5 Network Stack Monitor                                  |

|         | 3.5.1 Limitation of the Network Stack Monitor            |

|         | 3.5.2 Operation of the Network Stack Monitor             |

|         | 3.5.3 Filter Design                                      |

| 3       | 6 APHID System: Putting it All Together                  |

| 3       | 7 APHID Testing Model                                    |

|         | 3.7.1 System Boundaries                                  |

|         | 3.7.2 System Services                                    |

|         | 3.7.3 Workload                                           |

|         | 3.7.4 Performance Metrics                                |

|         | 3.7.5 Parameters                                         |

|         | 3.7.6 Factors                                            |

|         | 3.7.7 Evaluation Technique                               |

| 3       | 8 Chapter Summary                                        |

|                |                                                        | Page     |

|----------------|--------------------------------------------------------|----------|

| IV. APHID      | Implementation                                         | 50       |

| 4.1            | Hardware and Software Platforms Used                   | 50       |

| 4.2            | APHID Network Stack Monitor Implementation             | 51       |

| 4.3            | Integrating APHID with a Production Processor          | 52       |

|                | 4.3.1 Proposed Architecture                            | 52       |

|                | 4.3.2 Successes                                        | 52       |

|                | 4.3.3 Roadblocks                                       | 54       |

|                | 4.3.4 Fallback Options                                 | 55       |

| 4.4            | Intrusion Attacks on APHID                             | 55       |

| 4.5<br>4.6     | Distributed Denial of Service Attacks on APHID         | 55<br>56 |

| 4.0            | Incomplete Implementation and its Effect on Testing    | 50       |

| V. Results     |                                                        | 58       |

| 5.1            | Results of Tests on APHID Primitives                   | 58       |

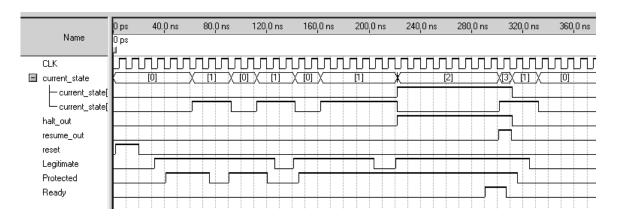

|                | 5.1.1 APHID Finite State Machine Simulation            | 58       |

|                | 5.1.2 APHID Address Comparator Discussion              | 60       |

|                | 5.1.3 Network Filter Simulation Discussion             | 60       |

| 5.2            | The Benefits of Hardware Content Addressable Memory    | 60       |

| 5.3            | Comparison of the APHID Network Filter to Existing Re- | co.      |

| 5.4            | Search                                                 | 63<br>64 |

| 0.4            | Total System Integration                               | 64       |

|                | 5.4.1 In System Performance Estimate                   | 04       |

| VI. Conclud    | ding Remarks and Future Research                       | 66       |

| 6.1            | Concluding Remarks                                     | 66       |

| 6.2            | Contributions                                          | 66       |

| 6.3            | Future Research Opportunities                          | 67       |

| Λ 1: Λ         | ADIIID Deirections in VIIDI                            | co.      |

| Appendix A.    | APHID Primitives in VHDL                               | 68       |

| A.1            | APHID State Machine Primitive                          | 68       |

| Appendix B.    | VHDL MIPS Processor                                    | 72       |

| B.1            | Mips.vhd                                               | 72       |

| B.2            | MIPS_Piped.vhd                                         | 79       |

| B.3            | control.vhd                                            | 89       |

| B.4            | Ifetch.vhd                                             | 91       |

| B.5            | Idecode.vhd                                            | 94       |

| B.6            | Execute.vhd                                            | 97       |

| B.7            | Dmemory.vhd                                            | 100      |

| B.8            | Control.vhd                                            | 102      |

| B.9            | Decode.vhd                                             | 104      |

| Bibliography . |                                                        | 106      |

# List of Figures

| Figure |                                                                           | Page |

|--------|---------------------------------------------------------------------------|------|

| 2.1.   | CuPIDS: Using SMP Architectures for Security Policy Compliance Monitoring | 14   |

| 2.2.   | A Buffer Overflow on the Stack                                            | 19   |

| 2.3.   | Levels of Security                                                        | 21   |

| 2.4.   | The Network Protocol Stack and Packet Encapsulation                       | 22   |

| 2.5.   | A Distributed Denial Of Service Attack                                    | 25   |

| 3.1.   | Monitor Cache                                                             | 33   |

| 3.2.   | APHID Flowchart                                                           | 35   |

| 3.3.   | Device Driver Monitor Architecture                                        | 36   |

| 3.4.   | APHID State Machine                                                       | 38   |

| 3.5.   | Deploying APHID Network Stack Monitor                                     | 41   |

| 3.6.   | Network Stack Monitor Flowchart                                           | 43   |

| 3.7.   | The APHID System                                                          | 44   |

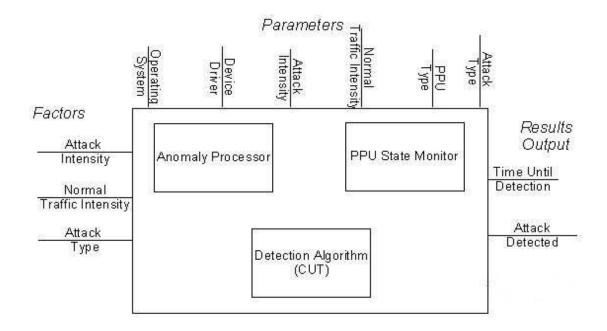

| 3.8.   | The System Under Test                                                     | 45   |

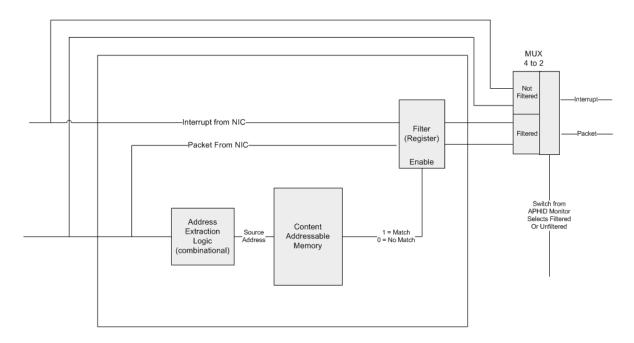

| 4.1.   | The APHID Network Filter                                                  | 52   |

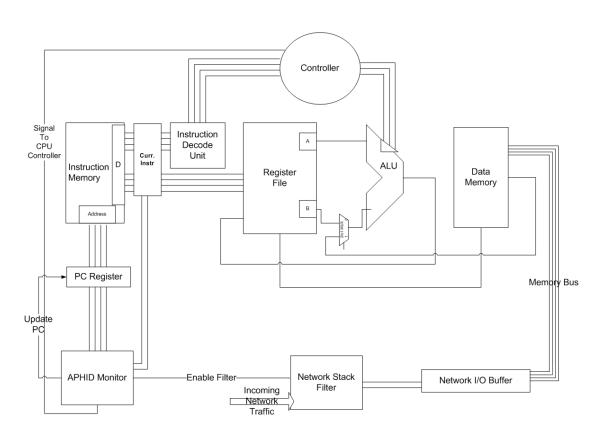

| 4.2.   | The APHID Implementation on a RISC Processor                              | 53   |

| 4.3.   | The APHID Network Filter                                                  | 56   |

| 5.1.   | Results from Simulation of APHID State Machine                            | 60   |

# $List\ of\ Tables$

| Table |             | Page |

|-------|-------------|------|

| 3.1.  | The Factors | 47   |

# List of Abbreviations

| Abbreviation |                                                         | Page |

|--------------|---------------------------------------------------------|------|

| APHID        | Anomaly Processor in Hardware for Intrusion Detection . | 2    |

| PPU          | Production Processing Unit                              | 2    |

| API          | Application Programming Interface                       | 5    |

| IDS          | Intrusion Detection System                              | 8    |

| NIC          | network interface card                                  | 9    |

| VMM          | Virtual Machine Monitor                                 | 11   |

| OS           | Operating System                                        | 11   |

| VM           | Virtual Machine                                         | 11   |

| TPM          | Trusted Platform Module                                 | 12   |

| CuPIDS       | Co-Processing Intrusion Detection System                | 12   |

| SMP          | Symmetric Multiprocessing                               | 12   |

| SPCM         | Security Policy Compliance Monitoring                   | 12   |

| CPP          | CuPIDS Production Process                               | 13   |

| CSP          | CuPIDS Shadow Process                                   | 13   |

| SECM         | Security Enhanced Chip Multiprocessor                   | 16   |

| ESP          | Embedded Sensor Project                                 | 18   |

| SRAS         | Secure Return Address Stack                             | 19   |

| TCP          | Transmission control protocol                           | 23   |

| UDP          | User Datagram Protocol                                  | 23   |

| IP           | Internet Protocol                                       | 23   |

| IPv6         | Internet Protocol version 6                             | 23   |

| DoS          | Denial of Service                                       | 24   |

| DDoS         | Distributed Denial of Service                           | 24   |

| FPGA         | Field Programmable Gate Array                           | 26   |

| LUT          | Look Up Table                                           | 26   |

| Abbreviation |                               | Page |

|--------------|-------------------------------|------|

| HDL          | Hardware Description Language | 26   |

| CAM          | Content Addressable Memory    | 27   |

| KLA          | Known Legitimate Actions      | 32   |

| RTL          | Register Transfer Logic       | 37   |

| FSM          | Finite State Machine          | 37   |

#### APHID:

#### Anomaly Processor in Hardware

#### FOR

#### Intrusion Detection

#### I. Introduction

Todern operating systems are becoming increasingly complex. Studies show ⊥that the average number of bugs per 1000 lines of code is between 1 and 16 [7]. Commodity operating systems (Linux, Unix, and Microsoft Windows XP) contain between 2 and 30 million lines of code, resulting in a conservative estimate of 15 thousand bugs in a typical operating system [42,43]. One author claims that a medium-sized corporation could have as many as 5 million remotely exploitable security vulnerabilities when the problem is compounded over the corporation's network (approximately 30,000 nodes) [23]. Furthermore, device drivers make up a large portion of the operating systems and are often written by third parties. These drivers operate at elevated privilege levels (kernel mode) and have access to critical data structures and memory spaces that the operating system must use [38, 43]. These third party programs may not be developed with the same quality assurance and testing that is afforded by the developers of the operating system kernel. Even efforts in the area of driver certification are not enough because certification does not imply that the program is bug free, only that it meets certain minimum criteria, certified code may still contain software vulnerabilities and exploits [27]!

The spread of broadband to the masses compounds the problem of high bug count. While most users in the fields of computer science and engineering are concerned with security and take at least the minimal security precautions on the systems they use, the masses at large are notoriously bad at securing their systems. Home users have unsecured wireless routers, unpatched operating systems, and disabled firewalls. Often useability trumps security. As a result of the large number of unsecured machines, distributed denial of service attacks become feasible. All an attacker needs to do is gain access to a sufficient number of machines (and turn them into zombies). The average home user would never know of this intrusion and can be an unwitting pawn in the schemes of attackers. Recent bot-net based denial of service attacks against the 13 root domain name servers exemplify the increasing severity and sophistication of the attacks [18].

#### 1.1 Proposed Solution

Thesis Statement: Intrusion Detection through the use of dedicated hardware running anomaly detection schemes at low levels (i.e. in hardware) will result in significant improvements in response time and reliability over software intrusion detection systems. Applying hardware primitives to the problem of denial of service attacks can increase a system's overall resistance to failure.

The Anomaly Processor in Hardware for Intrusion Detection (APHID) is a method for creating a trusted computing environment while maintaining system performance. We accomplish this using hardware primitives and dedicated co-processing rather than a software only solution. The result is increased security with minimal performance impact as compared to a host-based intrusion detection system running as a separate software task on the main system production processing units (PPUs). Furthermore, the detection of intrusions can be accomplished in real-time, as the event occurs, rather than after some passage of time, giving rise to the potential for repair of intrusions (or even stopping the intrusion before damage occurs).

1.1.1 Merits. APHID hardware primitives offer the opportunity to capture bad events as they happen. Doing so can allow one to perform security checks at a very low level (resulting in high fidelity compliance checking) and at hardware speeds. Offloading the security monitoring overhead to dedicated processing allows the production system to operate without interruption when not under attack and to operate with minimal disruption when being actively attacked. Using APHID primitives also allows the administrator to harden the system against various forms

of attacks ranging from buffer overflows on device drivers to denial of service attacks on the network interface.

1.1.2 Costs. The benefits from APHID are not without their costs. APHID requires modification of commodity hardware platforms. Currently this is done with reconfigurable hardware, but for true performance benefits the primitives will need to be placed into the fabric of modern processors. Furthermore, the specific detection algorithms used by APHID are application specific and require the programmer to be intimately familiar with the devices and libraries they are protecting. Improper or naive implementations could result in a substantial performance penalty or an unstable system.

#### 1.2 Document Organization

The remainder of this document is broken into five chapters. Chapter II discusses the past and current work in intrusion detection as well as important background material that the reader may find useful for understanding concepts presented later in the document. Chapter III presents the theoretical APHID architecture and testing models. Where possible, implementation specific details are omitted to keep the model as flexible as possible. Chapter IV presents our implementation of APHID and discusses the process taken to arrive at that implementation. Chapter V presents the results of the APHID implementation. Some of the results are empirical, gathered from simulation, and some are more theoretical, based on some simplifying assumptions that abstract away more complex issues to demonstrate the power of APHID where actual testing has not been possible to date. Chapter VI concludes the document with discussions about APHID and future research opportunities.

## II. Related Research and Background Information

This chapter outlines research in the field of computer system security (specifically intrusion detection) and touches on some necessary background and fundamentals which may assist the reader with understanding topics discussed in later chapters. It is assumed that the reader has a general background in computers and information systems. This section provides a basis for further understanding of what intrusion detection involves and the work that has been done to address the problem.

### 2.1 Definition of Intrusion

This research is in the area of intrusion detection. For the sake of clarity we must define the term intrusion to remove ambiguity. An intrusion can be defined as: "An improper or unauthorized use of computer resources, with or without malicious intent." This definition encompasses the aspects of insider threat, and external attacks [5,24,45]. While we are concerned with insider threat activities, the bulk of this research deals with general protection of code while in execution. We do not address access policies in terms of who is allowed to be on the machine. We are specifically concerned with illegitimate code execution through the exploitation of vulnerabilities in software. Therefore, we can tighten the definition of an intrusion to: "Illegitimate execution of code on a system by exploiting software vulnerabilities." For the remainder of this document, the word *intrusion* is used with the more restricted definition, unless otherwise noted.

#### 2.2 Classification of Intrusions

Intrusions take advantage of system weaknesses. Hoglund and McGraw place use the following categories to classify weaknesses: Bugs, Flaws, Vulnerabilities, and Design Vulnerabilities [23]. This classification is in order of increasing complexity and increasing effort for repair.

2.2.1 Bugs. Bugs are code level issues. Incorrect use of a function call such as strcpy() in C can result in a buffer overflow exploit if array bounds are

not checked. Unfortunately, this type of bug is one of the most common sources of system vulnerabilities. A common exploit can result in arbitrary code running at the privilege level of the process with the buffer overflow bug, compromising the system even to the point of being remotely controlled by an intruder. Most bugs can be resolved using simple scanning of software. Good programming practices reduce or eliminate these.

- 2.2.2 Flaws. Flaws run a deeper risk. A flaw is a problem with the implementation of a section of software, involving a more complex interaction than misuse of a system call or improper bounds checking. Flaws manifest from poor design decisions. A flaw may or may not be exploitable.

- 2.2.3 Vulnerabilities. Vulnerabilities are problems that can be exploited by an attacker. A bug or a flaw can result in a vulnerability. Vulnerabilities have to do with design decisions and access. Particular points of interest are interfaces between software modules (such as device drivers and system libraries). Vulnerabilities can either be directly exploited or used in combinations for gaining access to the system. A buffer overflow is a direct exploit of a bug. By running past the bounds of an array (buffer) the attacker can inject malicious code into the execution path, or can change the control flow of the program resulting in an intrusion. Examples of combination attacks involve exploitation of timing or interface flaws. Some error handling states can leave a system in an insecure state if a exception occurs, or certain application programming interface (API) calls can leave vulnerabilities exposed.

- 2.2.4 Design Vulnerabilities. Detecting a design vulnerability is more of an art than a science. Design vulnerabilities can take the form of improper configurations which expose data channels; improper error handling (as mentioned above), incorrect use of access control mechanisms (weak passwords, or unencrypted password files, for example), or complex interactions among distributed systems that "leak" information through unintended sources (message types and traffic analysis).

It is possible to classify intrusions according to the type of vulnerability exploited, however it is most common to classify them according to the type of activity performed. The following is a list of common classifications of intrusions. It is not exhaustive or complete. The information for this list is gathered from various sources [11, 13, 23].

Virus: A virus is malicious software that attaches itself to other software within the system, lacking the ability to self propagate outside the system.

**Worm:** A worm is software that performs malicious actions and also has the ability to propagate to other systems.

**Trojans:** A trojan is malicious software embedded in an innocuous package that can open security holes to create new vulnerabilities. Trojans can behave as a worm or as a virus.

Rootkit: Rootkits are a more recent addition to the list of vulnerabilities. The design of a malicous rootkit is particularly insidious in that it may become embedded in the operating system in such a manner that it can intercept and change any system messages. The result is that the rootkit maintains root level access for the intruder, but hides all such activities from the operating system. They can operate by several means. A masters thesis research effort by Nerenberg classifies rootkits according to their various strategies and implementations [32].

Timing Attacks: Mentioned above, timing attacks can take advantage of insecure system states achieved by sequences of system or function calls. Additionally, timing based attacks can take advantage of knowledge of scan intervals (by the IDS) or of other similar vulnerabilities in order to avoid detection and compromise a system.

Sequenced Attacks: Sequenced attacks involve using design vulnerabilities to build up an intrusion. These usually require extensive knowledge of the system, or some additional intrusion access through virus, worm, or trojan activities. The sequenced attacks often result from unintended consequences of library calls on the system state.

#### 2.3 Detection Timeliness

One goal of this research is to achieve real-time detection using our IDS. To that end, it is necessary to explicitly define some terms for the remainder of the research. Rather than reinventing the wheel, we refer to definitions from Kuperman's Ph.D. dissertation [24].

**Real-time:** Kuperman defines real-time as: Detection of a bad event,  $\boldsymbol{b}$ , takes place while the system is operating, and before any event dependent upon  $\boldsymbol{b}$  can occur.

**Near Real-time:** Near real-time is defined as: Bad event b is detected within some finite (and small) time  $\delta$  of b's occurrence.

**Periodic:** A scan by the security system at a set interval p. Detection must take place within a worst case maximum of 2 \* p for the detection scheme to qualify for this name. This worst case occurs when b occurs immediately after the previous scan has finished and is not detected by the current scan until immediately before the next scheduled scan. If this were not the case, there would be a bottleneck in the detection system and the system could scan and process enough events to keep up with the incoming event stream.

**Retrospective:** An offline review of events to detect the bad events. This review can be as simple as a person reading the logs, to as complex as a full forensic analysis of a system.

2.3.1 Measuring Time to Detection. For the purposes of this research time is measured as the number of operations (defined as instructions at the assembly code level) executed from the time bad event b begins execution until b is detected. The reasons for this choice are twofold. First, on systems with similar instruction set architectures (such as Power PC and MIPS) one can make an "apples to apples" comparison of detection times, regardless of clocks rate. Likewise, on machines with differing instruction set architectures (such as MIPS and Intel x86), there is generally a

sense of the average ratio of instruction counts acquired from compiling the same code on both machines. Using the instruction counts and average number of instructions executed per clock cycle on each machine allows for a rough comparison between the two machines. The second reason is related to the overall effects of an intrusion. Logically, more instructions executed, from the time b occurs until it is detected, offers an intruder a greater opportunity to cause damage. The metric executed instructions between event occurrence and event detection gives a sense of the extent of damage that can be accomplished. Furthermore, intrusions involving relatively few bytes of executed code (like the SQL Slammer attack with a size of 376 bytes [19]) could execute and remove traces of the intrusion if the time to detection is large.

#### 2.4 Attack Surfaces

Attack surfaces, defined by Manadhata and Wing, is the concept of the size of vulnerability presented to the attacker [28]. For instance, an entire operating system, with all of the services and processes running, presents an extremely large attack surface. It is not reasonable to expect a single monitoring unit to effectively protect this entire surface. By choosing a sufficiently small attack surface it is possible to create an monitor capable of protecting the code section in real time.

#### 2.5 General Classification of Intrusion Detection Systems

An intrusion detection system (IDS) is generally classified as either a network IDS or a host IDS. Our research, while mainly focused on host based systems, has potential applications as a blended approach, incorporating both network and host-based IDS concepts.

2.5.1 Network IDS. A network IDS examines network traffic at the packet level and can be a stand-alone system which monitors all traffic on a specific network segment, or an internetworked set of intrusion detectors that share a private network (either physical, or virtual through a virtual private network) [8]. A network IDS

has visibility only of the traffic on the network. In a typical setup, the network IDS operates its network interface card (NIC) in promiscuous mode, capturing and examining all traffic on the network where it sits. This may require special configuration of the router or switch connected to the network IDS where the switch forwards all traffic to the IDS as well as to the destination. A prime example of a network IDS is the open source, self proclaimed de facto standard for intrusion detection/prevention, Snort [41].

2.5.2 Host IDS. Like the integrated air defense system, a secure enterprise system should not rely on only one layer of defense, rather there should be multiple rings (layers) of protection. A network IDS is one component of such a plan. A Host IDS is a component that can be used to add an additional layer of security. Host IDSs monitor a particular single computing unit (what we would think of as a single server or desktop computer). The host IDS has access to internal information available to only that host, but has limited global awareness. The host IDS is used to monitor the processes and user activities on the single machine and can only monitor network traffic specifically destined for that machine. Dorothy Denning [16] provided the framework for much of the current work in general purpose IDS designs, and most host intrusion detection systems can be classified as derivatives of her work.

In the class of host based ID systems, three main approaches have been taken. The first uses anomaly detection (which we lean toward in our research), the second uses signature based detection, and the third uses specification based detection. We refer the reader to Axelsson's paper [3] for a thorough taxonomy of ID systems and the approaches taken, with the note that he specifies only two IDS classes, anomaly detection and signature detection. The third class, specification based detection, was noted by Williams in [45] as a reflection of the state of the art in intrusion detection.

Anomaly Detection: Anomaly detection works on the principle that a system knows what normal is. This can occur through either self learning, or through programming. Using this sense of normal, the IDS can ascertain when something

outside of those parameters occurs. Anomaly detectors can suffer from higher false positive rates, so a tradeoff must be made by setting thresholds of acceptable deviation from normal. Raising the thresholds can reduce the false positive rates (incorrectly identified intrusions), but can have an inverse effect on the rate of missed detections.

Signature-based Detection: Signature based systems use knowledge of previously encountered attacks to create a signature for a specific attack or class of attacks. This signature allows the IDS to search through events and detection occurs when a signature matches an event. The result is a highly reliable detector for events that have signatures. However, the detector can be easily fooled by even slight changes to the event, and will allow unknown intrusion events, for which there is no signature, unrestricted, undetected access to the system [45].

Specification-based Detection: Growing interest (and concern) in the arena of computer security is resulting in a change of perspective towards specification based systems. The concept of specification based systems is not new (especially in terms of the pace of computing system progress). Once thought to be too expensive (too hard to implement) and too restrictive, the realization of the need for tighter security models is bringing this concept to the forefront [10]. The Bell-Lapadula model [9] is one security model that is commonly applied to these type of systems. A specification-based system explicitly defines a condition of security for the system. Any state that does not match a state in this security specification is flagged or raises an alarm.

Hybrids: There are examples of IDSs that apply more than just one detection approach in an effort to improve reliability and accuracy. As mentioned before, a detection on a signature based system has a high probability of being correct, but it is trivial to manipulate many intrusions so that the signature is rendered invalid, while the attack remains a threat. Applying anomaly detection (or specification-based detection) in concert with a signature-based detector can improve the reliability and accuracy of the system.

2.5.3 Host-based IDS Execution Classes. We can classify host-based intrusion detectors by the manner in which they operate.

Interleaved: This IDS runs as a separate process, interleaved with other processes running on a multitasking machine and it relies on the operating system to schedule the IDS to run frequently enough to capture any intrusions. The best detection timeliness any interleaved IDS can hope for is near real-time, but the more likely case is a periodic detection timeliness (see Section 2.3 for the definition of near real-time).

Interposed: An interposed IDS works by adding a software layer to the system so that all system calls activate the IDS. The result is a finer granularity of detection, with the (potentially high) cost of added overhead to every system call.

Co-processing: A coprocessing based IDS offloads the overhead of running security tasks from the PPU to the security co-processor. This has the added benefit of providing parallel processing with the potential for *real-time* detection (see Section 2.3 for the definition of real-time). One hindrance to this approach is that the co-processor may not have necessary access to the PPU data structures and hardware without modification of the computer system architecture and operating system. This research is focused on defining new hardware primitives to advance co-processing IDS capabilities.

Virtual Machine Monitors: A virtual machine monitor (VMM) based IDS works by running the IDS in a software layer below the operating system (OS. Doing this allows the IDS to have access to virtual machine (VM resources and the IDS can perform detection on each guest OS running on that system. This method appears to have some merit and should prove to be very useful with the increasing emphasis on visualization technology [29].

#### 2.6 Related Research in IDS Co-processing

This research is focused on using co-processing to implement a host-based IDS. The following sections highlight the main points of existing research in IDS co-processing. Co-processing systems stand in contrast to uniprocessor intrusion detection systems in that they are able to process in parallel with the production execution unit, allowing for a finer granularity of detection.

2.6.1 Cryptographic Co-processing. While not a true IDS, a cryptographic co-processor provides the system with services that increase overall system security by encrypting data streams between functional units on the system. The resulting secured busses and channels allow for data integrity checking. Cryptographic co-processors do not necessarily prevent an intrusion, but they do minimize the attack surface presented to that intrusion source by securing the channels. In the event of an intrusion, the attacker is presented with a greater challenge in capturing meaningful data from the system. The trusted platform module used in Intel's LaGrande technology (TPM) is a mainstream example of a cryptographic co-processor [4].

#### 2.7 CuPIDS

The co-processing intrusion detection system (CuPIDS), introduced by Williams, works on symmetric multiprocessing (SMP) systems. Most SMP systems attempt to balance the workload by spreading processes evenly across the processors. CuPIDS differers from this approach by making a conscious tradeoff between security and performance and dedicating one of the processors in the SMP architecture to security related processing tasks. This difference allows CuPIDS to perform parallel monitoring in real time (see Kuperman's definition in Section 2.3) [24,45]. The parallel monitoring performed by CuPIDS supports the broader class of security policy compliance monitoring (SPCM) which includes intrusion detection as well as a number of related areas including error detection and computer forensics [10].

- 2.7.1 CuPIDS Goals. The goals of CuPIDS are:

- Harness the power of SMP systems to perform security monitoring.

- Allocate one processor to perform parallel monitoring at higher fidelity than possible in a uniprocessor intrusion detection system.

- Use the opportunities afforded by parallel monitoring to perform actions not available to a uniprocessor IDS, such as real time monitoring and self healing.

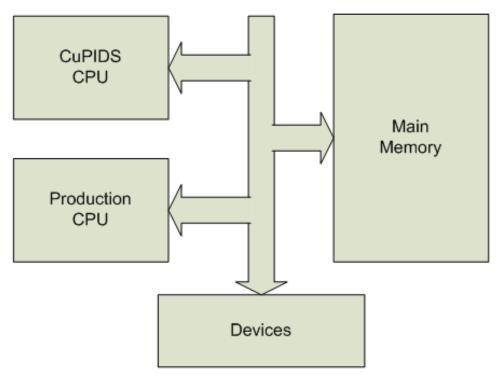

- 2.7.2 CuPIDS System Architecture. The foundation for the CuPIDS architecture is monitoring a production process by running the monitoring process in parallel (on a separate processor) as the production process executes. Designed around a shared resource, general purpose SMP architecture, CuPIDS separates protected processes into two components: A CuPIDS production process (CPP) and a CuPIDS shadow process (CSP). CuPIDS is event driven. The stream of events that CuPIDS operates on is generated by the CPP and used by the CSP. The shared memory resources are not shared symmetrically. The CSP is given insight into the memory space of the CPP but the CPP is not given any access to the memory space of the CSP. This allows the shadow process (CSP) to monitor the production process non-intrusively, while it executes. The CSP is also able to control the activities of the CPP through a control stream.

- 2.7.3 Basic Capabilities. Several characteristics define the capabilities and characteristics of CuPIDS. From Williams' dissertation [45], they are:

- 1. Hardware resources (a processor in this case) are dedicated solely to security tasks (See Figure 2.1).

- 2. All of the state of the monitored process (the CPP) is available to the monitoring process (the CSP).

Figure 2.1: CuPIDS: Using SMP Architectures for Security Policy Compliance Monitoring

- 3. Primary detection tasks are specification-based. That is, explicit knowledge of how the protected application is intended to behave is used to detect incorrect or illegitimate behavior.

- 4. Security monitoring is done in parallel (concurrently) with the execution of the monitored task.

- 5. Attacks may be immediately acted upon because of the parallel monitoring. Any information or analysis gathered by the monitor can be used to halt the attack an keep the system from entering a damaged state, in contrast to an IDS running on the uniprocessor model (interposed or interleaved) where the attack may disable the IDS (or hide from it) before it has a chance to execute.

- The parallel monitoring is not instruction-by-instruction. CuPIDS traces the

execution path in parallel, keeping the appropriate monitor running with its

production code.

- 7. CuPIDS is event based. The execution state of the monitored process is transmitted to the monitoring process via an event stream. The event stream can be automatically generated from some sources, and others require explicit instantiation by the programmer.

- 8. The monitoring unit is synchronized with the protected application by the event flows.

- 9. Monitoring can be performed asynchronously from the protected application, further complicating the task of the attacker.

- 10. CuPIDS resides and operates inside the host OS, giving the monitoring task complete visibility into the state of the OS and full control of a monitored process. This is a much higher level visibility than that provided by other approaches (virtual machine monitors and cryptographic processors).

- 11. CuPIDS can be implemented on commercially available hardware using modified commercially available software.

- 2.7.4 Strengths and Weaknesses. CuPIDS has strengths and weaknesses as pointed out by Williams.

Strengths: CuPIDS can detect intrusions in real time (again using Kuperman's definition). This is the main advantage of CuPIDS. Since it monitors in parallel, CuPIDS can also observe activity internal to the monitored process that a uniprocessor IDS simply cannot observe because it cannot run in parallel. The result is a higher fidelity detection model, using internal control flow events, programmer defined events, and interactions with external entities (e.g., libraries, drivers, system calls). Another strength of CuPIDS is that it removes the burden of security processing tasks from the production process. As security takes a larger role, the cost of security processing will also expand. CuPIDS uses some hardware that could have been used for production processing, but introduces minimal overhead on the production processor(s) it does not use.

Weaknesses: CuPIDS exists inside the production operating system. Because of this, its communications and processes are vulnerable if the host OS is compromised. Messages are passed through the kernel, and a compromised kernel could alter or suppress those messages, resulting in a broken event stream, and rendering CuPIDS inoperative. The tradeoff between visibility of processing state and protection of the security system is the source of this weakness.

#### 2.8 Security Enhanced Chip Multiprocessor

The Security Enhanced Chip Multiprocessor (SECM) is another research effort in the field of parallel co-processing intrusion detection. Like CuPIDS, SECM uses commodity hardware and software (with modifications) to perform the monitoring tasks. SECM differs from CuPIDS in that it uses an asymmetric multiprocessing approach where the production processor uses a full blown kernel, with limited access to "riskier" system calls and the security processor runs a minimal kernel for higher performance and smaller attack surface. The security processor is given higher access to machine state and also access to the production kernel state for monitoring purpose, but the production kernel does not have the same privileges. State information about the production OS is gathered from the memory bus and shared memory resources. SECM, by having elevated privileges over the production OS is able to detect rootkit attacks on that OS (because it has visibility to layers "beneath" the OS where a rootkit would be embedded). Furthermore, given the elevated privileges, the security OS can dump a compromised production OS and reload a clean version of the production kernel in the event that an intrusion is detected. This allows the production OS to maintain some resemblance of robustness to attacks.

#### 2.9 CoPilot

CoPilot approaches the co-processing intrusion detection problem from a different perspective [36]. Rather than dedicate a full CPU to the task of monitoring, the CoPilot system places a co-processor on the PCI bus. Here, the co-processor works

much like a graphics card works for acceleration of graphics libraries. Because the processor sits on the PCI bus, it can only gather system state information through that bus and it cannot directly impose control over the system. Residing on the main memory bus allows co-pilot to do a 1 to 1 mapping of memory addresses to memory space but limits its access to hardwired (non virtualized) kernel pages that do not move. CoPilot works by monitoring these memory locations for changes using anomaly detection. Due to overhead issues, CoPilot monitors on a periodic basis (see Section 2.3 for definition). Because of this, CoPilot cannot achieve real-time or near real-time detection. The idea of using a peripheral card holds promise despite the aforementioned timeliness and memory visibility issues.

#### 2.10 Other Security Systems Using Methods Similar to APHID

This section briefly describes other security systems (not necessarily IDSs) that behave in ways similar to the desired behavior of APHID. These systems are related in that they either contain an idea similar to APHID concepts or use similar methods on different problems.

2.10.1 Techniques for Monitoring Control Flow. Zhang in [49] and Arora in [2] present independent methods for checking control flow at various levels of fidelity. Zhang's method modifies the hardware of a processor to allow for control flow checking at the instruction level. The checking is done by running anomaly detection routines in hardware. The anomaly detector is programmed statically with compile time data regarding branching and then the program is trained in a "sandbox", or a known secure environment. Doing this allows the hardware to record common branching and to gather a sense of normal behavior.

Arora's team presents three methods of integrity checking in an embedded environment. Her work provides: Intra-procedural control flow checking, where branches within a procedure are monitored for illegitimate activity, Inter-procedural control flow checking, where branches from one procedure to another are monitored for cor-

rectness, and finally, instruction stream integrity using hashing algorithms. Procedures are hashed at compile time and the hardware then hashes the procedure at run-time to check against any modifications that may have occurred.

2.10.2 ESP: The Embedded Sensor Project. The Embedded Sensor Project (ESP) is actually a software extension that embeds specific calls in sections of code (it is an interposing IDS in a sense) [48]. However, ESP aims at making the sensors small and fast, and optimized for the task of protecting a specific section of code. Synergistic coupling of the embedded sensors can allow ESP to provide intrusion detection at varying levels from the application level to the operating system level, even to the network level if deployed on several machines and given the ability to communicate with one another.

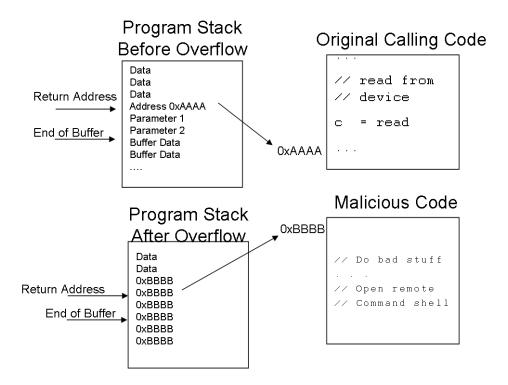

2.10.3 Protecting the Stack with Hardware. Buffer overflows continue to be a steady source of vulnerabilities, even though the solution to the problem is well known. Secure programming practices should eliminate this source of intrusions. Despite this, CERT continues to report vulnerabilities related to the technique of "stack smashing" on a fairly routine basis [13]. The majority of attacks involve the attacker injecting specially crafted code into a buffer with unchecked bounds. The attacker will write the bytecodes corresponding to a NOP (no operation in assembly code) creating what is known as a NOP sled. The attacker then replaces the return address on the stack with an address that is likely to be in the range of the NOP sled and the processor will then execute the NOPs until it reaches the malicious code at the end. If the buffer overflow vulnerability existed in code with elevated privileges the resulting intrusion can grant root level access to the attacker. Figure 2.2 shows a simple example of a buffer overflow in action. In this example, the buffer is in the program stack. The process reads input from the data source (user input, for example), the input exceeds the space allocated to the buffer and important stack data are overwritten. Here we see that the malicious data (from the array overflow) writes over the return address with the calling address of the malicious code. When

Figure 2.2: A Buffer Overflow on the Stack

the process executes the call and returns to what it thinks is the code section that made the original call, it will actually begin execution in the malicious code section where bad things (such as remote root-level access) can occur.

Several methods have been introduced to cope with this epidemic. Lee *et al.* propose a secure return address stack SRAS, which imposes additional hardware checking to stack calls. If SRAS detects a modification to the stack, then a flag is raised [26]. Smashguard employs similar techniques, but handles the problem of deep stack returns more elegantly than Lee [34].

#### 2.11 Classifying the Hardness of a Computing System

It becomes necessary to classify computing systems according to their level of protection, or hardness. The term hardness is chosen to frame the concept in terms of military physical protection. For example, sandbags provide a level of protection

against light munitions, thereby improving the security of anything behind the sand-bags. Further hardening could involve bunkers buried deep underground, with 12 foot thick blast doors. Obviously, there is a tradeoff between the cost of hardening and the level of protection required. It does not make sense to build a subterranean bunker to protect a units meal rations for the day. A truck or small building will provide adequate security. Likewise, it is not prudent to place critical command and control nodes in a canvas tent, that is what the hardened bunkers are for.

We use this analogy to make a point. The act of hardening a system imposes a cost on the system. The cost involves complexity (which can mean higher financial burden for designers) and usability/productivity/performance (which can result in higher financial burden for the users). There is an direct relationship between the cost of the system and the security of the system. This implies that there is a need to harden the system to the appropriate level (as defined by the purpose of the system). In keeping with the thesis statement in Chapter I, we aim to reduce the cost of the security mechanism by pushing the security aspects to a hardware monitor on a system, thereby increasing the security level of the system while minimizing the costs associated with that new security level.

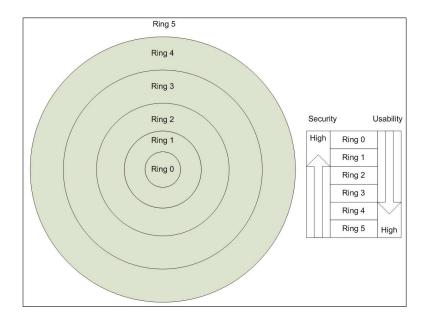

We classify the hardness of a system using a ring topology. Our classification system has six levels numbered 0 to 5 (Figure 2.3).

Ring 0: Perfect Security. A useable system corresponding to this ring does not exist. A system with this level of security is a closed system. No information flows out of the system, nor can it interact with its environment. Unfortunately, this system is useless (notwithstanding its excellent properties as a paper weight).

**Ring 1:** Deeply Hardened. In the military analogy, this is the secure, hardened, underground facility. There is limited direct contact with systems in the outside world. Only trusted entities are allowed access (physical or remote). It can be compromised, but this requires an trusted insider with access to sabotage the system.

Figure 2.3: Levels of Security

This is the type of system you want your bank to have in place for managing deposits and withdrawals from your account.

Ring 2: Hardened. The military analogy is a concrete building with access security and various levels of protection. From the information technology perspective this is like an enterprise server with physical access policies, running behind a firewall, up to date patching, and some type of intrusion detection systems in place.

Ring 3: Heavily Armored. This can be analogous to military heavy armor, like tanks and other vehicles. They are resistant to most attacks from similar platforms. In terms of computing systems we would classify this as a patched, firewalled, small business class network without automated intrusion detection capabilities, but with all appropriate traffic logging and security software (such as virus scanning and strong password login requirements) in place.

Ring 4: Lightly Armored. In the analogy we compare this level to a lightly armored vehicle. It can withstand many attack types, but cannot handle a direct attack from larger munitions and focused attacks by multiple sources. This

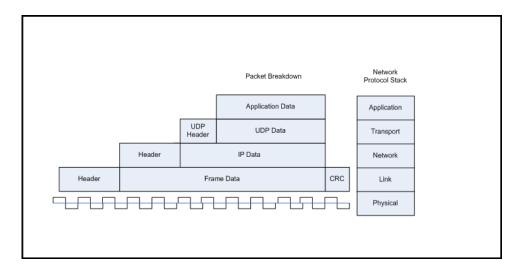

Figure 2.4: The Network Protocol Stack and Packet Encapsulation

would be the equivalent of a home user system, with up to date security patches and perhaps a personal firewall. Here the level of protection is good for very low cost.

Ring 5: Unsecured. Consider this as an unarmed soldier in an enemy camp. This is what you get when you install an operating system and without patching connect to the internet via broadband. Almost immediately, the system can become compromised. Moving from Ring 5 to Ring 4 is easy and has an excellent cost to benefit ratio.

#### 2.12 Networking Background

Figure 2.4 shows both the protocol layering and the datagram packaging concepts discussed in the following sections.

2.12.1 The Network Protocol Stack. The Network Protocol stack is the Internet's layered service protocol stack that facilitates communication over networks. Using protocol layering allows different technologies to communicate by abstracting away complexity of the system. The Internet protocol stack has five layers: Application, Transport, Network, Link and Physical. Each layer provides a service to the layer directly above it in the stack. The following list contains examples of technologies that provide services in each layer, in order from top to bottom [25]:

- Application Layer: End user programs, such as instant messengers, maintain connections at this layer.

- Transport Layer: TCP (transmission control protocol) and UDP (user data-gram protocol) provide datagram services at the transport layer level. TCP provides an end-to-end connection-oriented service with delivery guarantees, while UDP provides a connectionless service with no delivery guarantee. Both modes are used extensively and have merits depending on the particular application.

- Network Layer: The Internet Protocol (IP) provides the source and destination routing services to transport layer packets in the network layer.

- Link Layer: In the link layer, IP packets are provided with the point to point delivery services. Packets at this level are called frames. Ethernet, Wi-Fi, and the point-to-point protocol are examples of link layers.

- Physical Layer: The physical layer delivers bits and provides the mechanism for delivery of frames. This is where the hardware resides. We can think of this layers as the wires, or the radios involved in transmission and receipt of data.

- 2.12.2 Internet Protocol Packets. IP packets are the workhorses of the Internet. An IP Packet is wrapped in a frame and sent across links. Upon arriving at a host, the IP Packet is extracted from the frame and examined for destination address. If the host doing the examination is the destination, then the packet continues up to the transport layer. Otherwise the packet is ignored or forwarded, depending on the role of the receiving host. This research is primarily concerned with IPv6 (IP version 6) packets because they are (slowly) replacing IP version 4 packets as the new standard [25]. This choice provides several advantages. First, the amount of work that must be done to parse the packets is reduced because the specification removes variability of the header length. This was a problem in IPv4 where the header could have optional data resulting in more complex parsing algorithms [14]. Beyond that, the IPv6 packets also do not allow fragmented packets, which simplifies design choices in this research. As a result, the hardware that works with the IP

packets must handle larger addresses (128 bit versus 32 bit), and address ranges, than it would have handled with IPv4 packet specifications [15].

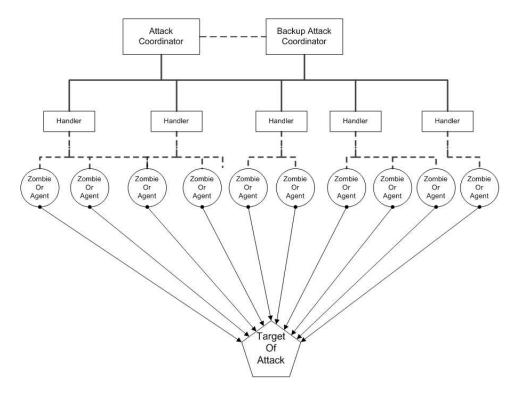

2.12.3 Denial of Service. Denial of Service (DoS) attacks are of particular importance to this research. Current events illustrate that this form of attack is still very much a threat [37]. A DoS may either originate from a single source or from many distributed sources. The attack from distributed sources is known as a distributed denial of service (DDoS) [25]. A system being attacked by a single source DoS needs only to block traffic from that source. A DDoS requires a more sophisticated approach, and there may not be any perfect solutions, depending on the intensity and spread of the attack. When a system comes under a DDoS, it may receive modest traffic from hundreds to thousands of unique nodes. The synergistic effect of this traffic can easily overwhelm most enterprise level servers [35]. Figure 2.5 shows a generic example of how a DDoS is initiated by the attackers. The zombies (or agents in some literature) generally participate unknowingly in the attack. The attack coordinators are far enough removed from the actual attack execution that it is difficult to prove their involvement in many cases. Handlers may also participate in the attacks, but typically this is avoided to keep the trail of evidence from being too strong.

Source address spoofing gives rise to on particular kind of DDoS attack that is particularly difficult to deal with. Legitimate sites are tricked into playing part in a DDoS by group of zombies. Rather than using the zombies to directly flood the target system, the zombies spoof their source address to that of the target and then send a TCP packet to a number of legitimate web sites. Because of TCP's three way handshake connection protocol, those sites respond with an acknowledgement. Unfortunately, the target system is suddenly inundated by the acknowledgements from these various sources. TCP's automatic retransmission further increases the problem.

Another interesting class of DDoS is the flash crowd. This DDoS is not a coordinated attack with malicious intent, but has serious consequences nonetheless.

Figure 2.5: A Distributed Denial Of Service Attack

Flash crowds (also known as the slashdot effect [44]) occur when a particular web site becomes overwhelmed by legitimate requests for data because of a sudden increase in popularity or visibility stemming from being linked to by one of many popular article posting sites like Slashdot [39], digg [17], or Fark [20].

Much research has been in the area of protection against DDoS attacks using signature methods and or dropping specific types of traffic when under attack, using flow monitoring. For example, if the attack appears to be UDP based, then the firewall is directed to drop all UDP packets regardless of source. The problem with this 'solution' is that it gives the desired effect of a DoS for any legitimate sources communicating via UDP protocols.

One interesting direction of research is using history based IP filtering on edge routers of a particular network [35]. This research was discovered after the APHID proposal for doing a similar task in hardware, and it appears to have merit. Peng states that in a code red (a well known worm) attack the source IP address is spoofed

using a randomly generated IP address [35]. Only 0.06% to 14% of those spoofed IP addresses corresponded to addresses previously seen by the system. The authors describe a system of DDoS Protection where the edge routers of the network build up a history of IP addresses that have recently accessed the system [35]. They use two rules to define what a trusted IP address is. First the frequency of visits by an IP address, and second, the packet count generated by that IP address. Attack statistics show that most attacking IP sources generate a relatively low traffic volume compared to active users. Using this knowledge they build a system using the two rules to allow access (via a tuneable metric) to specific IP sources when an attack is taking place.

In Section 3.5 we discuss how APHID builds upon this concept and Section 5.3 shows how the hardware primitives improve the situation through increased speed of filtering and decreased operating system load.

### 2.13 Reconfigurable Hardware

Field programmable gate arrays (FPGAs) are devices that allow for rapid prototyping of digital designs [40]. Often described as a "sea of gates", an FPGA contains thousands of look up tables (LUTs) which can be used to implement arbitrary logic. Current generation FPGAs often contain embedded, optimized, hard wired, devices that are common fixtures in many designs. Examples of the hardwired blocks are multipliers, memories, and even processor cores. FPGAs are generally programmed using a hardware description language (HDL) which is compiled and translated to bitstreams by vendor specific software. Other approaches to programming involve writing code in a specialized C dialect that allows translation to the hardware. FPGA designs generally have limited clock speeds compared to integrated circuits. Applications where FPGAs are useful generally involve applications where using the parallel execution nature of hardware gives an advantage over serial execution of software commands. Pattern matching, vector operations, and memory to memory operations are examples of applications that see performance gains from FPGA implementations [47].

2.13.1 Useful Hardware Primitives. Using FPGA technology allows a designer to have access to (or to create) hardware primitives that have constant time performance, with low overhead, for problems that require multiple iterations or even polynomial time algorithms in software. By pushing the algorithm to hardware and exploiting parallelism, the designer can see huge performance improvements. One example of such a hardware primitive is the look up table (not the same as the tiny LUTs that make up FPGA fabric). Look up tables have the same basic function as a hash table does in software. A key is associated with a memory location. The benefit that a hardware look up table has over a hash table is that the "hash" function in hardware requires very little time, whereas in software it can require significant overhead. Furthermore, access times for a look up table are often in the range of 1 to 2 clock cycles, depending on implementation. Of particular interest is the look up table known as a Content Addressable Memory (CAM). CAMs have the feature that the data to be stored is the key. This scheme is particularly useful in determining whether a piece of data is a member of a particular set. This research will make heavy use of CAM technology.

## 2.14 Chapter Summary

This chapter covered various topics including the concept of intrusions and intrusion detection. Other topics discussed include various methods and classifications of intrusion detection systems and current IDS implementations. A brief overview of the basics of network protocol stacks and network vulnerabilities is included. A short description of technologies used in this research closes out the chapter.

## III. APHID Model

This chapter defines the APHID architectural model. The discussion includes a description of the generic architectural primitives as well as a proposed proof of concept application model. Finally, the chapter outlines the testing model that is used to examine the potential benefits of the hardware monitor enhancements.

# 3.1 Problem Definition

The current security climate is changing. Security was once an afterthought and performance was king, but we are now seeing a shift in priorities. Security is coming to the forefront as performance from current hardware exceeds the requirements of most systems. Attacks of increasing intensity, severity, and frequency on commercial operating systems with common vulnerabilities are forcing the community, at large, to examine other ways to combat the problems. APHID is one solution among many that should be part of a layered defense approach.

3.1.1 Research Hypothesis. Hypothesis: Intrusion Detection through the use of dedicated hardware running anomaly detection schemes at low levels (i.e., in hardware) will result in significant improvements in response time and reliability over software intrusion detection systems. Applying hardware primitives to the problem of denial of service attacks can increase a system's overall resistance to failure.

Software ID systems, running as a concurrent task on a multitasking operating system are forced to make a tradeoff between system overhead and detection granularity. In other words, a software IDS must be scheduled by the operating system to run. More frequent IDS scheduling by the OS results in a finer grained detection. That is, the chances of detecting an intrusion are greatly increased. The tradeoff is in terms of performance overhead. Every time the IDS gets scheduled, the system resources are being used for security processing rather than working on production processes.

By moving this overhead into hardware, we make the tradeoff at a different level. We sacrifice potential processing power (transistors, memory, etc...) to implement a hardware level detection mechanism that runs in parallel with the production process. The parallel monitoring frees the production processor from some of the burden of running IDS tasks, and therefore frees more resources for the actual production processes. Because we choose to protect a small attack surface at any given time, we are able to increase the reliability of results from anomaly detection.

### 3.2 Solution Framework

APHID builds off of the CuPIDS [45] model of using hardware to exploit parallelism and achieve faster detection and response to attacks on a system. CuPIDS uses a symmetric multiprocessor system where one processor (the security processing unit, SPU) monitors the operation of the other (production processing unit, PPU) processor. Special messages (execution traces) are passed through memory resulting in detection times orders of magnitude faster than a standard uniprocessor intrusion detection system [45]. This research extends and modifies the CuPIDS concept by further separating the SPU, departing from a symmetric multiprocessor to an asymmetric multiprocessor system with the SPU dedicated to the task of monitoring specific parts of the system. In the general case, any part of the system may be monitored. This application of APHID monitors the network protocols to include the OSI stack and system calls related to network operations. This scheme will provide general protection of device drivers as well as user processes.

3.2.1 Research Goals. This goal of this effort is to achieve significant reductions in response time to intrusions by asymmetric coprocessing to perform IDS functions. Response time, for the purposes of this paper, is defined as the time it takes the IDS to detect the attack and take some form of action, initially in the form of a simple notification.

To achieve the goals above, we define new hardware primitives and connect them to the PPU in ways that allow for novel detection schemes. We strive to answer the following questions:

- 1. Can a device driver be monitored by hardware to determine if malicious actions are occurring?

- 2. How fast can detection occur using the APHID scheme and how does this compare with existing methods?

- 3. What is the performance benefit gained by pushing the monitoring work into parallel hardware?

These questions can be summarized with the following goals.

- 1. Determine feasibility of detection through the use of hardware to monitor and protect device drivers.

- 2. Determine response time (time to detection in terms of instructions executed) of the APHID protected system and compare that to the software protected response times.

- 3. Develop an understanding of how APHID increased hardness on a system versus software only methods.

# 3.3 Approach

APHID is an asymmetric security co-processor that monitors device drivers and OS kernel code for anomalous behavior. Anomaly detection is facilitated by gathering statistics of normal behavior in a trusted environment. Then, when operating in an untrusted environment, APHID compares the current system state (or small portions thereof) with what it is given as normal activity.

The ideas behind APHID emphasize using hardware co-processing to enhance security instead of enhancing performance alone. In practice, the potential for performance enhancement exists because APHID is designed to reduce the burden of security on the production processing unit (PPU). In general, this design allows the PPU (which may consist of multiple processors) to operate as normal, without having to run a separate security task as overhead. The security task is offloaded to dedicated hardware where we take advantage of hardware parallelism to perform real-time security compliance checking. In our research we define real-time to mean monitoring

the PPU(s) as they operate without interrupting them to perform the checks. Only when a security event triggers APHID to take action will the PPU be affected by the existence of APHID. In contrast, a security process running on the PPU will always require system resources (memory, processor time, CPU cycles) regardless of attacks. Refer to Kuperman's definition of real-time in Section 2.3.

APHID is made up of hardware primitives, which are tightly coupled with the existing hardware platform. From the perspective of the OS, APHID does not exist. There is no need for OS support or connection to APHID. In fact, modifying the OS to be aware of APHID, and to have some control over it, would remove most of the security benefit in the event of many rootkit type of intrusions [23].

In the following sections we describe a notional system, composed of APHID primitives and their interfaces with the existing hardware.

### 3.4 Device Driver Monitor

The initial purpose for APHID is to monitor device drivers as they interact with the system. We have chosen device drivers because of their elevated privileges and generally limited interface with the operating system, that is, the attack surface is small (See Section 2.4). Because of this, we can create small and fast monitors to quickly detect intrusions. The same principles can be applied to system calls with some modification.

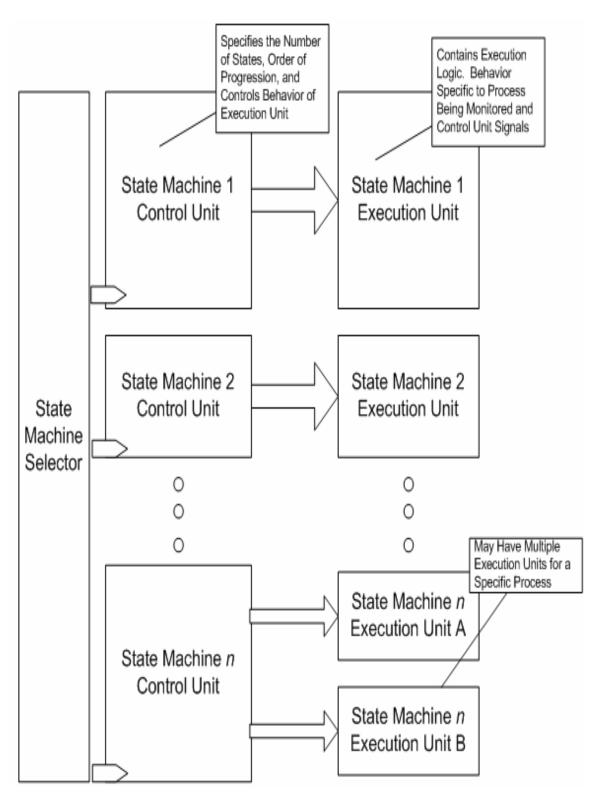

3.4.1 Modular design. APHID is designed to be modular, enabling the ability to monitor many types of devices. Additionally, APHID is designed to be useful for protecting other types of code. To facilitate these we propose the possibility of a Monitor Cache. The address comparator mentioned in Section 3.4.5 is used as a selector to a specific monitor based on which protected section of code (if any) is being executed.

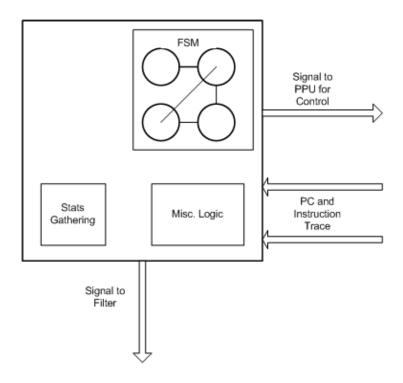

Monitor Cache. A key function of the modular design is to allow for monitoring of many different devices and code types. These monitors are small enough to

reside in a reconfigurable memory cache. Figure 3.1 shows a monitor cache. Using the address comparator (shown as "state machine selector" in Figure 3.1), a specific monitor can be enabled when the section of code that it is designed to monitor enters execution on the PPU. The monitors execute custom state machines, tuned to the specific application. Enabling monitors in this way allows the monitors to be traded in and out in the same time it takes to to a process swap on the CPU, and the safety coverage can be seamless.

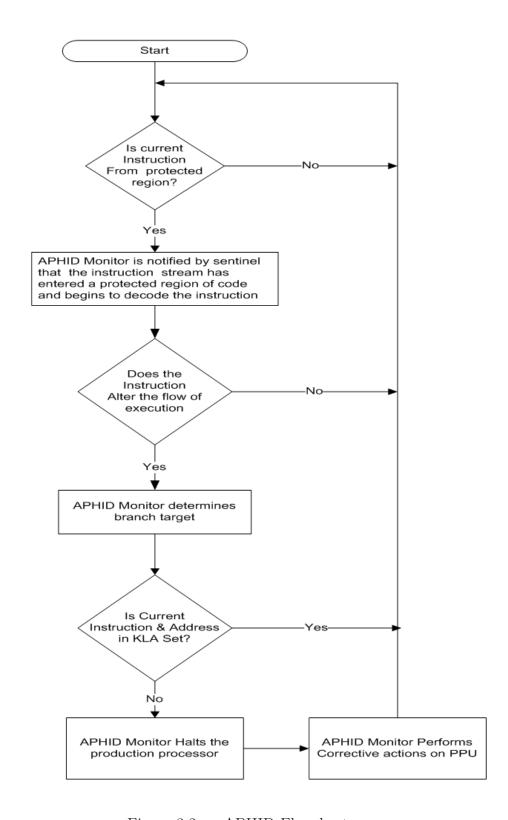

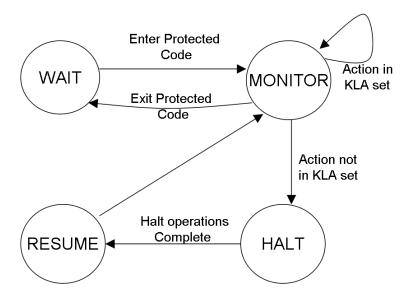

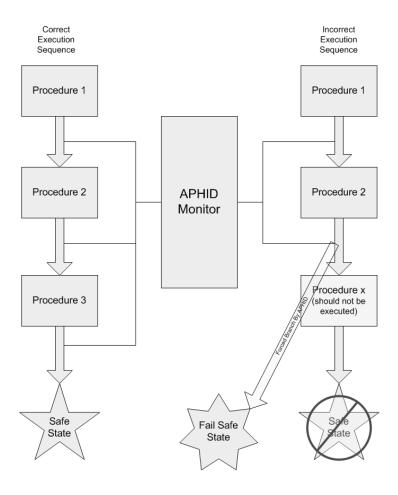

- 3.4.2 Anomaly detection. APHID uses anomaly detection to perform the monitoring tasks. To facilitate the anomaly detection, we use fast hardware look up tables to store a set of known legitimate actions (KLA). APHID monitors the behavior of a specific device driver and compares the actions it performs (jump to address x, return to address y, etc...) to the KLA set. If an action occurs that is not in the KLA set, the detector triggers and a flag is raised. The monitor then uses that information to perform corrective actions when possible. The KLA set is currently static and created ahead of time. Further enhancements to APHID can implement a dynamic reinforcement scheme where APHID is "trained" in safe mode, where intrusions are not allowed to occur. Then, using the dynamically collected KLA set, APHID can reinforce the static set and, additionally, learn from false positives and true positives through a feedback mechanism.

- 3.4.3 Justifications of Sizes. Several assumptions have been made that are important to note at this point. APHID monitors use control flow changes (branches, jumps, returns and calls) to generate the KLA set. Hennesey and Patterson [22] present profiles of several benchmarks, in Appendix B of their book. From these profiles we gather that 17% of all instructions in these benchmarks affect control flow. We will assume that most device drivers are comparable in instruction profile to these benchmarks. Ball et al have done a static analysis of Windows device drivers for the sake of error detection [6]. In their paper they list the lines of code for the twenty-six device drivers included in the Windows device driver kit. The sizes range from 24536

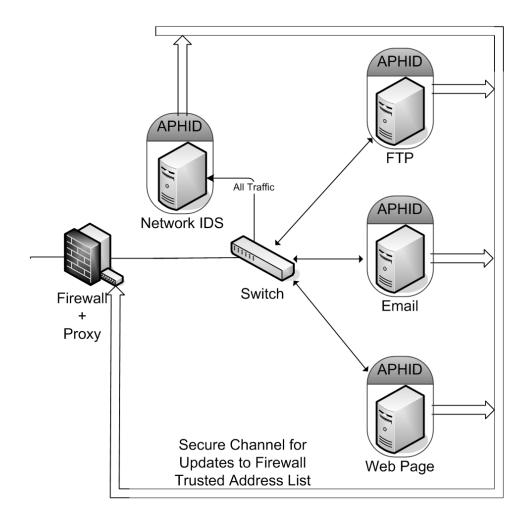

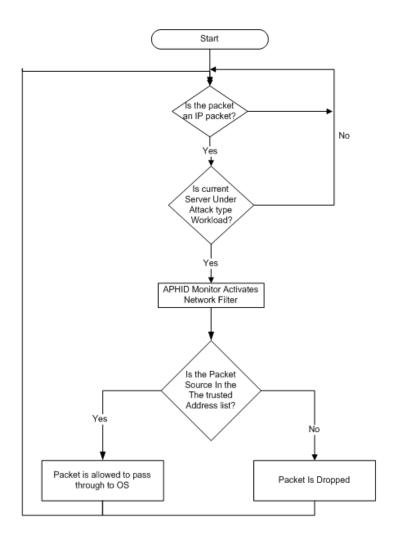

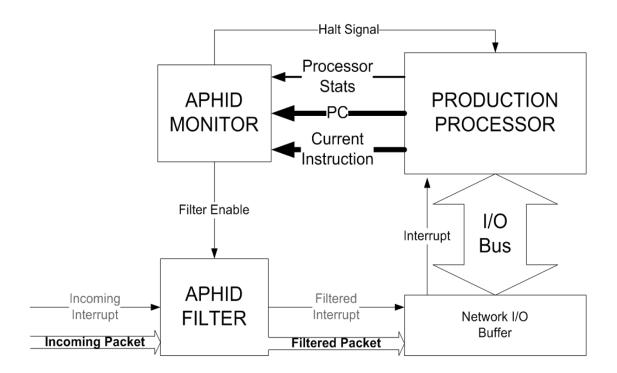

Figure 3.1: Monitor Cache