Electronic Theses and Dissertations, 2020-

2020

# **Enabling Recovery of Secure Non-Volatile Memories**

Mao Ye University of Central Florida

Part of the Computer Engineering Commons

Find similar works at: https://stars.library.ucf.edu/etd2020 University of Central Florida Libraries http://library.ucf.edu

This Doctoral Dissertation (Open Access) is brought to you for free and open access by STARS. It has been accepted for inclusion in Electronic Theses and Dissertations, 2020- by an authorized administrator of STARS. For more information, please contact STARS@ucf.edu.

### **STARS Citation**

Ye, Mao, "Enabling Recovery of Secure Non-Volatile Memories" (2020). *Electronic Theses and Dissertations, 2020-.* 154.

https://stars.library.ucf.edu/etd2020/154

### ENABLING RECOVERY OF SECURE NON-VOLATILE MEMORIES

by

# MAO YE B.S. Zhejiang University, 2004 M.S. University of Central Florida, 2017

A dissertation submitted in partial fulfilment of the requirements for the degree of Doctor of Philosophy in the Department of Electrical and Computer Engineering in the College of Engineering and Computer Science at the University of Central Florida

Orlando, Florida

Spring Term 2020

Major Professor: Amro Awad

© 2020 Mao Ye

### **ABSTRACT**

Emerging non-volatile memories (NVMs), such as phase change memory (PCM), spin-transfer torque RAM (STT-RAM) and resistive RAM (ReRAM), have dual memory-storage characteristics and, therefore, are strong candidates to replace or augment current DRAM and secondary storage devices. The newly released Intel 3D XPoint persistent memory and Optane SSD series have shown promising features. However, when these new devices are exposed to events such as power loss, many issues arise when data recovery is expected. In this dissertation, I devised multiple schemes to enable secure data recovery for emerging NVM technologies when memory encryption is used. With the data-remanence feature of NVMs, physical attacks become easier; hence, emerging NVMs are typically paired with encryption. In particular, counter-mode encryption is commonly used due to its performance and security advantages over other schemes (e.g., electronic codebook encryption). However, enabling data recovery in power failure events requires the recovery of security metadata associated with data blocks. Naively writing security metadata updates along with data for each operation can further exacerbate the write endurance problem of NVMs as they have limited write endurance and very slow write operations. Therefore, it is necessary to enable the recovery of data and security metadata (encryption counters) but without incurring a significant number of writes.

The first work of this dissertation presents an explanation of Osiris, a novel mechanism that repurposes error correcting code (ECC) co-located with data to enable recovery of encryption counters by additionally serving as a sanity-check for encryption counters used. Thus, by using a stop-loss mechanism with a limited number of trials, ECC can be used to identify which encryption counter that was used most recently to encrypt the data and, hence, allow correct decryption and recovery. The first work of this dissertation explores how different stop-loss parameters along with optimizations of Osiris can potentially reduce the number of writes. Overall, Osiris enables

the recovery of encryption counters while achieving better performance and fewer writes than a conventional write-back caching scheme of encryption counters, which lacks the ability to recover encryption counters. Later, in the second work, Osiris implementation is expanded to work with different counter-mode memory encryption schemes, where we use an epoch-based approach to periodically persist updated counters. Later, when a crash occurs, we can recover counters through test-and-verification to identify the correct counter within the size of an epoch for counter recovery. Our proposed scheme, Osiris-Global, incurs minimal performance overheads and write overheads in enabling the recovery of encryption counters.

In summary, the findings of the present PhD work enable the recovery of secure NVM systems and, hence, allows persistent applications to leverage the persistency features of NVMs. Meanwhile, it also minimizes the number of writes required in meeting this crash consistency requirement of secure NVM systems.

| This dissertation is dedicated to my parents, Weiyin Ye and Lining Wu, the kindest persons in my life who have given me unconditional support for my dreams. |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                              |

|                                                                                                                                                              |

|                                                                                                                                                              |

|                                                                                                                                                              |

### **ACKNOWLEDGMENTS**

I would like to express my gratitude to my adviser, Prof. Amro Awad, for his patience and guidance on my research work, his instructions on my writing and presentation and his tremendous efforts on my summer internship search. Without his help, It would have been impossible for me to publish at top-tier conferences, meet many smart and interesting students and scholars in computer architecture research community and finish this dissertation.

Additionally, Dr. Mingjie Lin and Dr. Shaojie Zhang provide valuable suggestions to me on many occasions. Dr. Rickard Ewetz always gives me frank and sharp opinions and the discussion with Dr. Fan Yao during joint seminar is informative. Further, Dr. John Seel gives me incredible encouragement and support. I am very glad to have them as my committee members and herein thank them sincerely. Moreover, I want to thank Dr. Kalpathy Sundaram, Dr. Yan Solihin, Dr. Aziz Mohaisen and Dr. Clayton Hughes respectively, for either giving me personal suggestions or instructions on publications. My appreciation also goes to Diana Poulalion for her kindness and honesty.

Furthermore, I would like to express my appreciation to my labmates: Vamsee Reddy, Mazen AlWadi, Kazi Zubair, John McFarland, Ghadeer Al-Musaddar and Abdullahal Arafat. We shared short but precious good times together that I will remember forever. My special thanks go to Nicholas Omusi, who has given me his emotional support from beginning to end.

In addition, I would like to thank some of my friends in academia and life. Beginning with my friends in academia first, they are Youwei Zhuo, Sihang Liu, Linghao Song, Pengfei Zuo, Xin Hu, Haiyu Mao, Tianqi Tang, Yifan Sun and Mengjia Yan. I met them during conferences, have had interesting and useful discussion with them and have received their valuable support. From my personal life, I would sincerely like to thank, Jie Xiong, who treated me to her delicious Sichuan

cuisine many times when I was too busy with deadlines and provided me valuable personal advice during my down time. I also owe a lot to Xinyan Zha, my life-long friend, who keeps calling me every week for months to help me get through the difficult times, and to Huihui Li, who offered me several referrals and, sent me preparation materials and useful information. I would also like to deeply thank Yu Bi and Kate Wang. With their sincere help, I received my current job. Besides, I would like to thank Xuhong Zhang, Jun Ye, Jiangling Yin, Dan Huang, Hao Hu, Bin Huang, Yuyan Bao, Sudharsan Vaidhun, Dean Sullivan, Dr. Zakhia Abichar, Dr. Suboh Suboh, Dr. Deliang Fan, Professor Su-I Hou, Paster Chen, Luo Yu, Biquan Wang, Lin He, Xin Liu, Tia Law and many others for their kindness. Again, I want to thank Prof. Hongwei Yang for his encouragement and help.

Lastly, I would like to thank my extended family in China and in US for their support before and during the pandemic and through the whole PhD journey.

## TABLE OF CONTENTS

| LIST OF FIGURES                                   | . xi   |

|---------------------------------------------------|--------|

| LIST OF TABLES                                    | . xiii |

| CHAPTER 1: INTRODUCTION AND BACKGROUND            | . 1    |

| Memory Encryption                                 | . 1    |

| Non Volatile Memories                             | . 2    |

| Recovery for Secure Non-volatile Memory           | . 7    |

| CHAPTER 2: OSIRIS                                 | . 11   |

| Background and Motivation                         | . 12   |

| Background                                        | . 12   |

| Emerging NVMs                                     | . 12   |

| Memory Encryption and Data Integrity Verification | . 13   |

| Encryption Metadata Crash Consistency             | . 16   |

| Design                                            | . 18   |

| Threat Model                                      | . 18   |

| Design Assumption                                                   | 19 |

|---------------------------------------------------------------------|----|

| Design Options                                                      | 19 |

| Design                                                              | 22 |

| Reliability and Recovery from Crash                                 | 29 |

| Different ECC Schemes                                               | 32 |

| Systems without ECC                                                 | 34 |

| System with both ECC and MAC                                        | 35 |

| Security of Osiris and Osiris-Plus                                  | 35 |

| Evaluation                                                          | 36 |

| Methodology                                                         | 36 |

| Analysis                                                            | 37 |

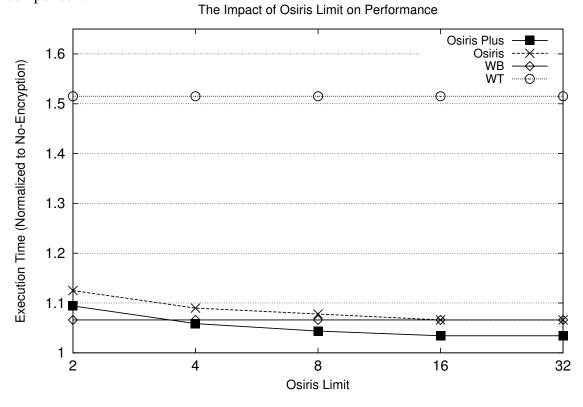

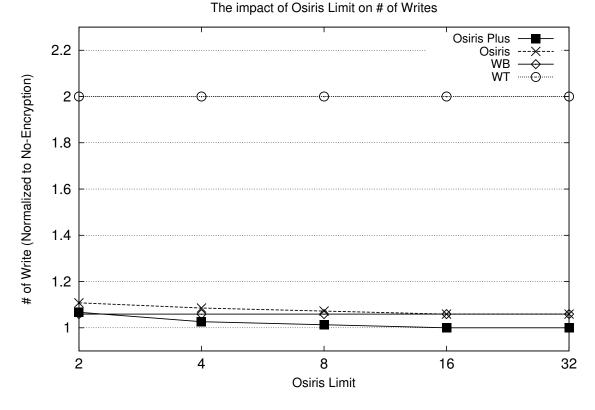

| Impact of Osiris Limit                                              | 38 |

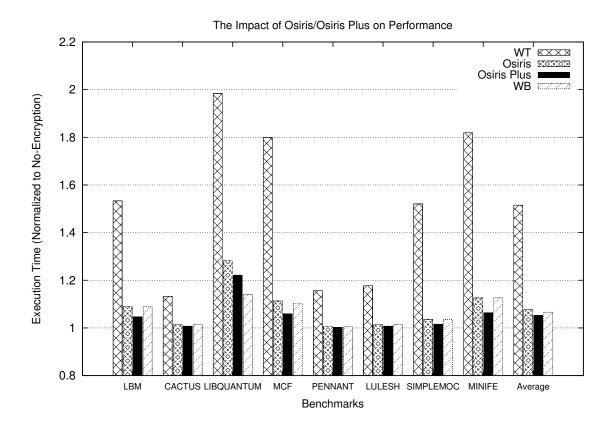

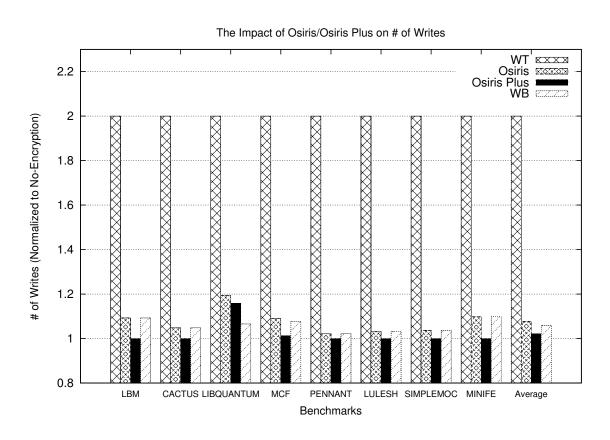

| Impact of Osiris and Osiris Plus persistency on multiple benchmarks | 40 |

| CHAPTER 3: OSIRIS GLOBAL                                            | 43 |

| Background                                                          | 43 |

| Design                                                              | 44 |

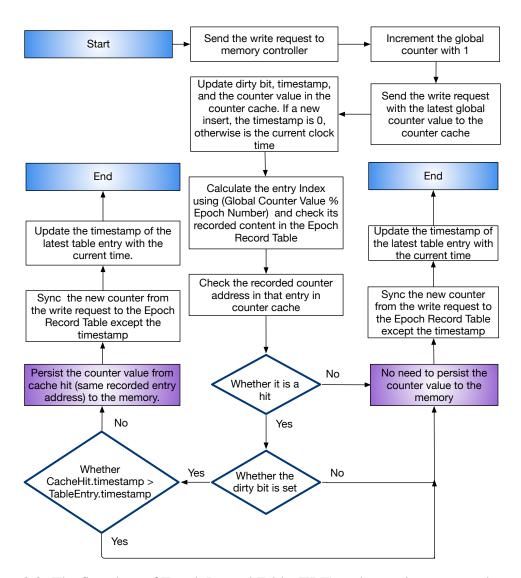

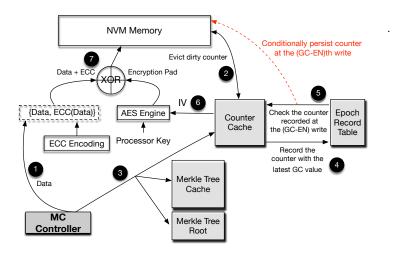

| Write Operation of Osiris-global                                    | 47 |

| Hardware Overhead for Osiris-global              | 49 |

|--------------------------------------------------|----|

| Evaluation                                       | 50 |

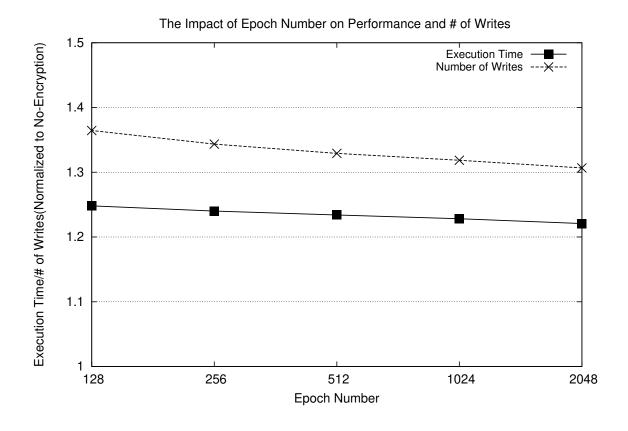

| The impact of Epoch Number                       | 50 |

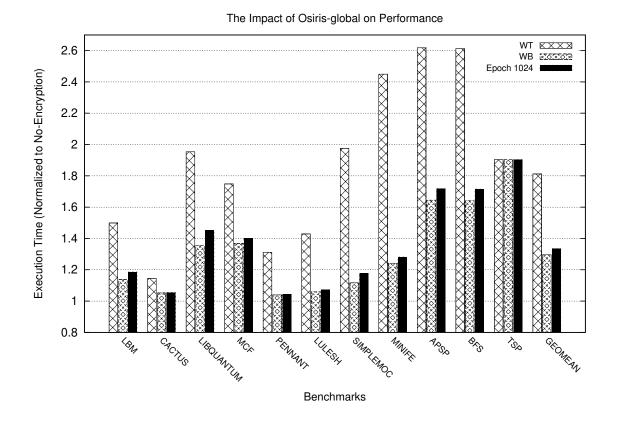

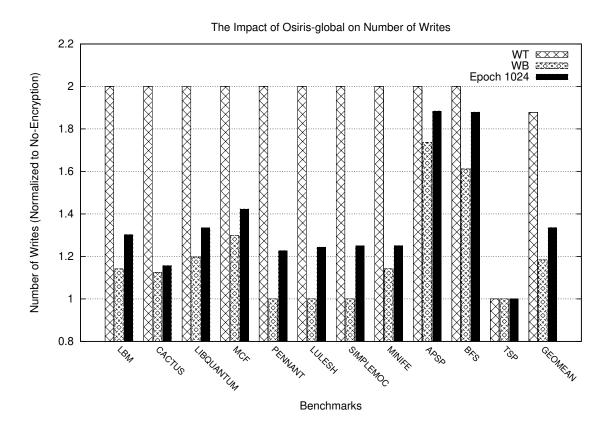

| Osiris-global persistency on multiple benchmarks | 51 |

| Recovery Time                                    | 53 |

| CHAPTER 4: SUMMARY                               | 55 |

| LIST OF REFERENCES                               | 57 |

# LIST OF FIGURES

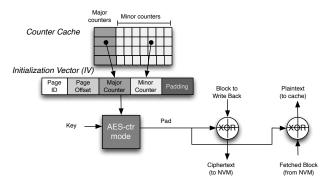

| 1.1  | Counter-mode encryption in memory                                                                      | 8  |

|------|--------------------------------------------------------------------------------------------------------|----|

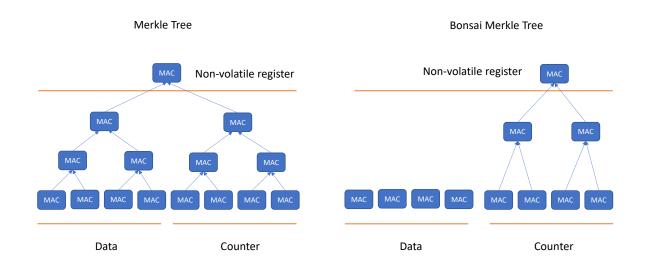

| 1.2  | Demo construction of Merkle Tree and Bonsai Merkle Tree                                                | ç  |

| 2.1  | State-of-the-art counter mode encryption. AES is shown but other cryptographic algorithms are possible | 13 |

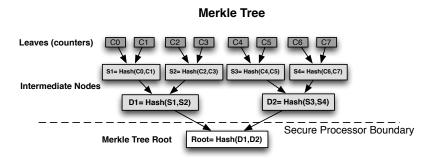

| 2.2  | An example Merkle Tree for integrity verification                                                      | 14 |

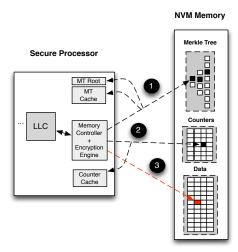

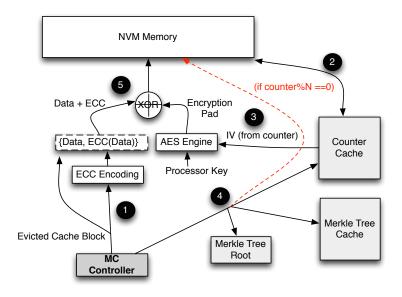

| 2.3  | Steps for write operations to ensure crash consistency                                                 | 16 |

| 2.4  | Osiris write operation                                                                                 | 27 |

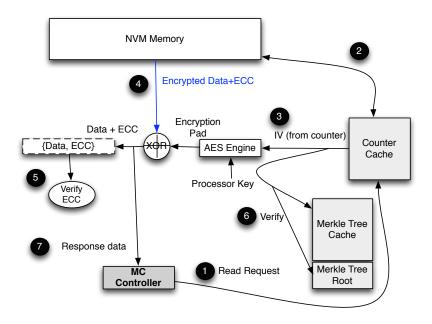

| 2.5  | Osiris read operation                                                                                  | 27 |

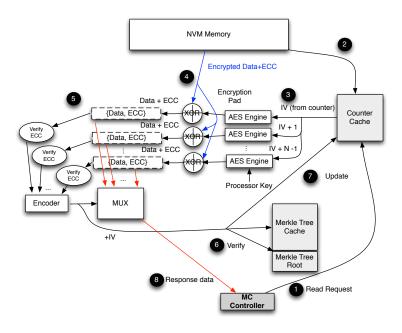

| 2.6  | Osiris-Plus read operation                                                                             | 29 |

| 2.7  | The impact of Osiris limit on performance                                                              | 38 |

| 2.8  | The impact of Osiris limit on number of writes                                                         | 39 |

| 2.9  | The impact of Osiris and Osiris Plus persistence on performance                                        | 41 |

| 2.10 | The impact of Osiris and Osiris Plus persistence on number of writes                                   | 42 |

| 3.1  | The structure of the Epoch Record Table (ERT) and the counter cache                                    | 46 |

| 3.2  | The flowchart of Epoch Record Table (ERT) update and counter cache update                              | 49 |

| 3.3 | Osiris-global write operation                                | 50 |

|-----|--------------------------------------------------------------|----|

| 3.4 | The impact of Epoch Number on performance (Number of writes) | 51 |

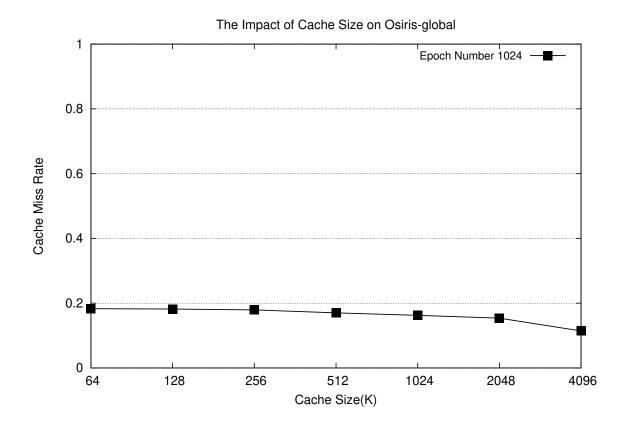

| 3.5 | The sensitivity studies of cache size for Osiris-global      | 52 |

| 3.6 | The impact of Osiris-global on performance                   | 53 |

| 3.7 | The impact of Osiris-global on number of writes              | 54 |

## LIST OF TABLES

| 2.1 | Common sources of ECC mismatch        | 24 |

|-----|---------------------------------------|----|

| 2.2 | Configuration of the simulated system | 36 |

| 3.1 | Counter Types Used in Encryption Mode | 44 |

### **CHAPTER 1: INTRODUCTION AND BACKGROUND**

This chapter provides the general information regarding the current progress of emerging non-volatile memory(NVM) technologies with an emphasis on memory encryption and secure metadata restoration.

### Memory Encryption

Memory encryption is an important measure to protect memory content from being modified or leaked out intentionally or unintentionally. Following the lead on storage and network device encryption, memory encryption that started as a feature for specific products has now become a common feature for general products. Memory encryption has drawn attention and is widely employed because memory can be attacked easily when industries rapidly move their business and critical data to cloud platforms where computation and storage resource is shared. Recent years, more and more hardware vulnerabilities are probed and revealed from security research community to the public[1]. The most frequently seen attacks include but are not limited to bus-snooping attack, memory scan attack(i.e. cold boot) and, memory content tampering attacks (i.e. memory spoofing, splicing and packet/data replay)[2]. At the front line of the battle for guaranteeing security, AMD proposes secure memory encryption (SME) to provide full memory encryption for their products. With SME, each memory controller is equipped with a standard AES engine for data encryption/decryption. The AES engine uses a key that is generated on each reset and stored on a system-on-chip register only visible to hardware to guarantee its security[1]. Intel, on the other hand, proposes a technology called Software Guard Extension to mitigate security risks that arise from using shared resources and untrusted operating system or untrusted DRAM[3, 4]. The core component of this technology is Memory Encryption Engine (MEE). While the system is booting

up, it reserves a fixed portion of memory as a data protection region where all the data will be encrypted. Therefore, if an application requires high-level of security during run-time, it will be only mapped to the encrypted memory. Additionally, data integrity is supported as a part of MEE unit[3]. SGX, although powerful, cannot guarantee the security for the whole memory. Therefore, Intel still expects to implement full-memory encryption in the future, similar to current AMD's SME technology[5].

While encrypted DRAM has become more developed, encrypted non-volatile memory (NVM) is new to the market[6, 7]. Due to its non-volatility NVM is more vulnerable than DRAM for data leakage attack. Despite removal from the device or under power shortage, NVM keeps its data intact. Moreover, all the aforementioned memory attacks apply to NVM as well. In particular, data replay attack is a threat model of the interests of this dissertation. Hence, encryption is required for NVM in concern of security risk. To make NVM feasible for current heterogeneous environment and shared cloud platform, NVM encryption and its consequence(i.e. performance, trade off, consistency) need open discussion and careful examination.

### Non Volatile Memories

Emerging NVMs, as the latest products to enter the memory market, demonstrate promising characteristics for users. NVMs such as phase change memory (PCM)[8], resistive RAM (ReRAM)[9], spin-transfer torque RAM (STT-RAM)[10] show better scalability, higher density and cheaper perbit costs[11].

The major difference between these NVMs stems from the materials and the structures on which they are built[8, 9, 10]. PCM is temperature-dependent technology to make chalchogenide alloy change between amorphous and crystalline phases. The amorphous phase results from a low

temperature and shows a high resistance whereas crystalline phase arrives only when the temperature is above the crystallization point. The different resistance level marks the different stored value[12]. A cell of ReRAM has a sandwich structure made of metal/oxide insular/metal layers. Similarly, it can also have two distinguished resistance levels due to the filament formation to enable conductive path in the insular layer[13]. By adjusting the voltage through an external source, the low-resistance and high-resistance statuses can be efficiently switched, representing logical 0 and 1[9]. STT-RAM cells are also built with a sandwich structure as well, with two ferromagnetic layers and one tunnel barrier layer in between. When the magnetic directions of two ferromagnetic layers are the same, it represents logical 0 and, vice versa, it represents logical 1[14, 10]. Therefore, it is the physical characteristics of the materials that determine the performance pattern of NVMs. Even within the same category, the variance can be huge [15, 8]. This dissertation focuses on phase-change memory, which is considered the core technology for both the Intel Optane Persistent Memory and Intel Optane SSD Series[7]. Phase-change memory has clear advantages, such as DRAM-comparable processing speed (read only), high capacity, byte addressability and nonvolatility[8]. Overall, NVM exhibits both memory and storage characteristics. Since 2009, NVM technology has been commonly seen in NAND flash and SSD[16], and, more recently, in hybrid or unified filesystems as the main storage powered by advanced 3D XPoint technology, especially in data centers[17, 6]. With PCM serving as the main storage of the file system, new applications can unleash their performance by taking advantage of the byte addressability of PCM through direct load/store operations[18, 19]. Hence, using PCM can yield tremendous performance gains, but it requires changes for most legacy applications[20, 21].

On the other hand, PCM has drawbacks. It is known for limited write endurance, slow writes compared to DRAM, power-consuming writes, and, finally the non-volatility, which appears as a weak point in some scenarios due to the data-remanence vulnerability. To address these drawbacks, prior studies have intensively researched in these challenges [22, 23, 24, 25, 26, 27, 28, 29, 30].

Their major results and solutions are summarized below.

It is shown that the write limit of PCM is around  $10^7$  to  $10^8$  with current technology[23]. This is because write operations require frequent heating and cooling to memory cells and, to a threshold, a cell ends up permanently losing its programmability[31]. While it is not plausible to limit the number of writes that each application needs to complete its task, it is useful to reduce unnecessary writes or distribute writes evenly to the cells on the memory. As such, multiple methods are addressed. In flip-and-write, the authors propose a simple read-modify-write solution to avoid unnecessary bit programming by only modifying changed bits. In addition, they introduce a flip bit which is set when the read comparison finds more than half of the bits between the old data and new data are different. Then, the old data chunk flips all of its bits to the opposite value before writing the modified part of the new data to the memory [32]. These two mechanisms can reduce write programming by half. To balance writes onto different locations of the memory, the write count for each memory line has to be tracked and the relocated line needs to be calculated. The Start-Gap wear-leveling algorithm periodically moves the content of a memory line to the line next to it, regardless of the write traffic[23]. To achieve this goal, it requires two registers named Gap and Start respectively and, one extra line to facilitate data movement. Then, for every N writes, starting from the line adjacent to the gap line, its content is copied to the gap line, making itself become the next gap line. Gap register always points to the gap line and, when Gap reaches 0, the memory works like a circular buffer to copy the content of the gap line at the beginning to the line that the Start register points to. To start a new data movement cycle, the Gap register again is set to N+1, pointing to the gap line and Start register increments to record the write cycle number. However, this method does not help with the cases where writes are frequently positioned to adjacent memory lines. To optimize this algorithm, a randomness generation function is used to enhance the location randomness of the gap line. Overall, the Start-Gap method can achieve up to 97% of the ideal device lifetime [23] after the optimization. Similarly, Security Refresh proposes to use a randomized address mapping mechanism to hide the memory locations from users and software [25]. In this study, physical locations of the data are constantly migrated within the memory. They can elongate the lifetime of PCM for another six years when confronted with the worst adversary attack described in their paper to exacerbate the write endurance to a specific set of cells[25]. The type of adversary attack to wear out cells by repeated writes is also addressed in the Start-Gap paper[23]. Their solution is to partition the memory into different sections and apply Start-Gap wear-leveling to each section. This is to reduce the number of writes to finish a cycle of data swapping for each partition. With this region-based Start-Gap, they can increase PCM's life by months to even years under the described attacks in their paper [23].

For PCM that is paired with counter-mode encryption, a number of studies have proposed different solutions to enhance device endurance, reduce write power and increase write bandwidth[22, 24]. Before discussing these works in details, one needs to understand that data remanence vulnerability of PCM is obvious and lasts much longer than DRAM. Needless to say, it has no temperature constrains like DRAM if one attempts to retrieve data from memory devices with no power supplies.

In DEUCE, it shows that with current counter-mode encryption, when the actual number of different bits between a chunk of old and new plaintext is small, the encrypted text written to the PCM could end up with around a 50% bit difference. Considering the fact that most written-back data only has a difference of few words from what is present in the memory, this work proposes to only re-encrypt the part that has been changed on each cacheline. In order to do so, this paper tracks the cacheline difference, and provides a two-counter system to reduce unnecessary bit flip. The two line counters are based on the physical cacheline counter. One is the same as the physical counter and the other masks the unchanged part of the cacheline bounded by an Epoch Interval. Using this scheme, the line-level redundant write have reduced the bit-flip caused by encryption to 24%. In accompany of a horizontal wear-leveling algorithm based on Start-Gap paper, they can achieve a

uniform line level write[22].

The paper Silent Shredder studies data shredding for operating system, an action to zero out physical pages before mapping them to a new process. It is a common practice in DRAM to secure the data but is highly undesirable for PCM where writes are expensive and life-costing. Therefore, for encrypted PCM, Silent Shredder repurposes the initialization vector to eliminate the writes for data shredding by resetting the associated counters before remapping and, by making the remaining data meaningless to processes that reuse them[24]. Not only does it reduce the writes by 48%, it also significantly speeds up read speed. This paper together with the DEUCE paper show different angles of how to take advantage of secure metadata to improve the lifespan of encrypted PCM[24].

Apart from improving the performance of encrypted PCM, significant efforts have been paid to improve slow writes and reduce power-consuming writes in regular PCM[26, 27, 28, 29, 30]. For the slow write problem, most studies fall in two categories. Either they focus on how to cancel, pause or truncate writes or they attempt to compress the write content[26, 27, 28, 33]. Power budget aware write scheduling and read-before-write comparison both want to reduce the expensive power consumption for write operation[29, 30]. All of these are very smart solutions. However, the problems they intend to conquer are not the foci of this dissertation.

Lastly, the difference between PCM and DRAM is summarized. In terms of structure, each DRAM cell is build on a capacitor and a transistor whereas PCM is based on phase change materials that show a huge resistance contrast between the amorphous phase and crystallized phases. PCM write speed depends on how fast its material can convert to and from amorphous to crystalline stages, where the high-resistance amorphous status is called RESET stage and the low-resistance crystalline stage is called SET stage. PCM read is performed when the material is under a small current pulse which would not change its status[34]. Experiments conducted by the research laboratories in industry show that, from the major metrics in performance evaluation, currently PCM is

still 4 to 100-fold slower than DRAM in terms of read speed[35]. The read bandwidth of PCM is also 4 to 10-fold smaller than that of DRAM. The minimum write latency and bandwidth of PCM is about 100-fold slower than its DRAM counterpart. However, the density of PCM is around four times higher than DRAM and its per-byte price is lower than DRAM[35]. DRAM needs to be repeatedly charged to maintain the status of its data while PCM does not. As such, PCM saves more power. Again, PCM shows a much higher risk of data leakage due to its non-volatility. Given the many difference between these two memory technologies, any well-suited designs and solutions for DRAM may not be relevant for PCM and may even bring interesting and practical problems.

### Recovery for Secure Non-volatile Memory

In Chapter 2, we mainly discuss our approach to solve the data recovery problem for encrypted NVM. To be clear, when without notification, in the following chapters NVM only refers to PCM. As a feature of security concern, we pair the NVM with counter-mode encryption. Using counter-mode encryption has shown shortened latency in comparison to other methods, such as direct encryption[36]. To implement the counter-mode encryption, a specific area of memory is reserved for counters. Any data stored on secure NVM is encrypted with its own counter, or more accurately, a derived form of its counter called an initialization vector (IV). The memory controller is usually equipped with an AES or a type of cryptographic engine, which is used to generate an one-time pad (OTP) with an IV and a processor-specific key as the parameters. For plain text data, XORing with an OTP makes it encrypted and, therefore, could be stored on the PCM memory. On the other hand, to reverse back to the plain text, encrypted data from the memory has to be XORed again using the same OTP derived from same IV and the key. Note that only plain text is passed to last level cache for further processing in the processor. This scheme with its core components is shown in Figure 1.1.

# NVMM | Decrypted | Data | Decrypted | Data | Data

Figure 1.1: Counter-mode encryption in memory

Importantly, secure NVM relies on integrity trees, such as the Merkle Tree for data integrity verification[37]. Briefly, a Merkle Tree is a hashed tree with data and counters as its leaf nodes and with the hashed value of the leaves as its intermediate nodes all the way up to the root. The root is saved in a register that is kept safe in the processor, the trust-based zone for all of the hardware[37, 38]. Therefore, the intermediate hash nodes are also considered a part of the secure metadata that need to be reserved. Bonsai Merkle Tree significantly reduces the level and storage overhead of the original Merkle Tree by being built on hash values(MAC value) of only counters. Note that Merkle Tree is used to detect replay attack and counters actually work as a version of its associated data. MAC value itself can detect splicing and spoofing attacks. Therefore, it can be proved that data does not need Merkle Tree protection as long as it satisfies three conditions together: 1) A data chunk is protected by a MAC value. 2) A MAC value is calculated over the counter and the data address. 3) The counter values are under integrity protection[37]. A figure provides a more detailed illustration of how the Merkle Tree and Bonsai Merkle Tree are

constructed (Figure 1.2). In this dissertation, we acknowledge the importance of the presence of Merkle Tree and describe its role in data recovery.

Figure 1.2: Demo construction of Merkle Tree and Bonsai Merkle Tree

In a previous research, it was discovered that in secure NVM after a crash, the counters and data that are persisted in the memory are not always matched with each other due to the incapability to flush all of the latest counter values to the memory[39]. Consequently, some of the data in the memory will forever lose their encryption counter values even if the power is switched on again. Data decryption failure makes data restoration meaningless. In that work, the authors provided a solution that uses an additional ready bit for both the counter and data to guarantee that they can track each other in an atomic way in write queues. The write queues blocks all the inconsistent data and counter pairs (ready bit not set) from being persisted. When a crash happens, write queues only drain the counter and data that both have arrived in the queues and have ready bit set. Moreover, to prevent performance degradation, the authors provide a recovery scheme only selectively persists data determined by programmers[39]. Research from another work utilized a

write-through counter cache for the same problem and it proposed to reduce counter writes through cancelling earlier write requests in the write queue if a recent request shares the same physical address with the pending requests[40]. Considering the write-endurance limitation of PCM and with the concerns of unavailable battery support, in Chapter 2, we discuss how to re-purpose ECC bits at a low cost to enable full memory data recovery without exacerbating the writes.

In secure NVM, multiple counter schemes are employed. Although the state-of-art counter scheme is proposed as a split counter, local and global counters are still discussed and employed in many studies[37, 3, 41]. Different types of counter scheme bring new challenges for counter persistence and recovery. Therefore, in Chapter 3, for a counter type not discussed in Chapter 2, we devised an epoch-based scheme for its persistence which only incurs a small number of extra write[42]. For data recovery, this newly devised scheme still relies on re-purposed ECC bits for stale counter identification.

### **CHAPTER 2: OSIRIS**

As discussed in the Chapter 1, the representative type of NVM for this dissertation, phase change memory, demonstrates promising characteristics, such as low latency, high densities, high scalability and byte addressibility. Hence, it is considered a strong candidate to replace DRAM. Recently Intel announced an NVM product using 3D-XPoint technology, further confirming the market's interests in this emerging memory device. However, it has several drawbacks, i.e. limited write endurance, power-consuming writes and the data remanence problem due to the non-volatility. These drawbacks render it vulnerable to a variety of attacks, including bus snooping attacks, cold-boot attacks, and others. Therefore, NVM is usually paired with encryption to defend against the threats listed above.

Despite the use of the encryption mode, the persistence of security metadata triggers a problem when a crash happens. It is always guaranteed that the data in the cache is flushed to the main memory. However, the metadata(encryption counters) in the cache is not always persisted to the main memory in time; hence, some up-to-date metadata is lost during the crash. This leads to the failure to recover their matched encrypted data stored in the memory because the metadata remaining in the memory for these data chunks are stale.

Previous research solves this problem by strict and relaxed persistence of the security metadata. Although strict persistence guarantees the data recovery, the expense is huge as it either requires a write-through scheme that introduces double writes, or through a battery-supported write-back scheme which is not always affordable. Since write endurance is already a problem for NVM and the encryption exacerbates it, double writes is not desirable for persisting NVM. Relaxed persistence, despite reducing the number of writes significantly, requires efforts from programmers and may invite plain-text replay attacks.

In this work, we propose a hardware solution that can effectively persist the security metadata to

the main memory with fewer writes than a write-back scheme and does not need external power supply.

### Background and Motivation

In this section, we discuss the main concepts that are relevant to our proposed solution, followed by motivation for our work.

### **Background**

In this part of the chapter, we will discuss emerging NVMs and state-of-the-art memory encryption implementations.

### Emerging NVMs

Emerging NVM technologies, such as Phase-Change Memory (PCM) and Memristor, are promising candidates to be the main building blocks of future memory systems. Vendors are already commercializing these technologies due to their many benefits. NVMs' read latencies are comparable to DRAM while promising high densities and potential for scaling better than DRAM. Furthermore, they enable persistent applications. On the other hand, emerging NVMs have limited, slow and power consuming writes. NVMs also have limited write endurance. For example, PCM's write endurance is between 10-100 million writes[23]. Moreover, emerging NVMs suffer from a serious security vulnerability: they keep their content even when the system is powered off. Accordingly, NVM devices are often paired with memory encryption.

### Memory Encryption and Data Integrity Verification

There are different encryption modes that can be used to encrypt the main memory. The first one is the *direct encryption* (a.k.a ECB mode), where an encryption algorithm, such as AES or DES, is used to encrypt each cache block when it is written back to memory and decrypt it when it enters the processor chip again. The main drawback of direct encryption is system performance degradation due to adding the encryption latency to the memory access latency (the encryption algorithm takes the memory data as its input). The second mode, which is commonly used in secure processors, is *counter mode* encryption. In counter-mode encryption, the encryption algorithm (AES or DES) uses an *initialization vector* (IV) as its input to generate a one-time pad (OTP) as depicted in Figure 2.1. Once the data arrives, a simple bitwise XOR with the pad is needed to complete the decryption. Thus, the decryption latency is overlapped with the memory access latency. Countermode encryption have different design schemes. In state-of-the-art designs [38],each IV consists of a unique ID of a page (to distinguish between swap space and main memory space), page offset (to guarantee different blocks in a page will get different IVs), a per-block *minor* counter (to make the same value encrypted differently when written again to the same address), and a per-page *major* counter (to guarantee uniqueness of IV when minor counters overflow).

Figure 2.1: State-of-the-art counter mode encryption. AES is shown but other cryptographic algorithms are possible.

Similar to prior work [24, 39, 37, 38, 22], we assume counter mode processor-side encryption. In addition to hiding the encryption latency when used for memory encryption, it also provides strong security defenses against a wide range of attacks. Specifically, counter-mode encryption prevents snooping attacks, dictionary-based attacks, known-plaintext attacks and replay attacks. Typically, the encryption counters are organized as major counters (shared between cache blocks of the same page) and minor counters that are specific for each cache block [38]. This organization of counters can fit 64 cache blocks' counters in a 64B block; 7-bit minor counters and a 64-bit major counter. The major counter is only incremented when one of its relevant minor counters overflows, in which the minor counters will be reset and the whole page will be re-encrypted using the new major counter for building the IV of each cache block of the page[38]. When the major counter of a page overflows (64-bit counter), the key must be changed and the whole memory will be re-encrypted with the new key. This scheme provides a significant reduction of memory re-encryption rate and minimizes the storage overhead of encryption counters when compared to other schemes such as monolithic counter scheme or independent counter for each cache block. Additionally, a split-counter scheme allows for better exploitation of spatial locality of encryption counters, achieving a higher counter cache hit rate. Similar to state-of-the-art work [24, 43, 44, 38], we use a split-counter scheme to organize the encryption counters.

Figure 2.2: An example Merkle Tree for integrity verification.

Data integrity is typically verified through a Merkle Tree — a tree of hash values with the root maintained in a secure region. Actually, not only data but also encryption counter integrity needs to be maintained. As such, state-of-the-art designs combine both data integrity and encryption counters integrity through a single Merkle Tree (Bonsai Merkle Tree [37]). As shown in Figure 2.2, Bonsai Merkle tree is built around the encryption counters. Data blocks are protected by a MAC value that is calculated over the counter and the data itself. Note that only the root of the tree needs to be kept in the secure region, other parts of the Merkle Tree are cached on-chip to improve performance.

MAC are indispensable to detect spoofing and splicing attacks towards memory data[37]. MAC value is originally calculated for data and counters respectively in the context of secure memory. But later MAC is calculated only over data as long as its counter integrity is guaranteed via a Merkle Tree. This is because a MAC value is calculated over the input consisting of a counter and its cipher-text [37]. Despite sharing some similarity, the algorithms for commonly used hash and MAC are different. SHA-1 and SHA-256 are widely used hash functions and both take 80 rounds to process a 512-bit block[45]. For MAC computation, some schemes are based on hash function, such as HMAC, while others are not[46, 47]. HMAC literally means has-based message authentication code, which employs two passes of hash computation (e.g, any of the SHA algorithms) on the data size defined by the selected algorithm and its security strength solely relies on the length of secret key[46]. Used widely in network protocols, HMAC value can be truncated in practical[46]. GMAC is the NIST recommended authentication method that simply uses the Advanced Encryption Standard by default on 128-bit block and a secret key to encrypt the input data. The encryption itself is initialization vector based that is made of a 32-bit counter appending to a 96-bit initialization vector for randomness[47].

### Encryption Metadata Crash Consistency

While crash consistency of encryption metadata has been overlooked in most memory encryption work, it becomes essential in persistent memory systems. If a crash happens, the system is expected to recover and restore its encrypted memory data. The steps needed to ensure crash consistency are depicted in Figure 2.3.

Figure 2.3: Steps for write operations to ensure crash consistency.

As shown in the Figure 2.3, when there is a write operation to NVM, first we need to update the root of the Merkle tree (as shown in step ①) and any cached intermediate nodes inside the processor. Note that only the *root* of the Merkle Tree needs to be kept in the secure region. In fact, maintaining intermediate nodes of the Merkle Tree can speed up the integrity verification. Persisting updates of intermediate nodes into memory is optional as it is feasible to reconstruct them from leaf nodes (counters) and then generate the root and verify it through comparison with that kept inside the processor. We stress that the root of the Merkle Tree must persist safely across system failures, e.g., through internal processor NVM registers. Persisting updates to intermediate nodes of the Merkle Tree after each access might speed up recovery time by reducing the time of

rebuilding the whole Merkle Tree after crash. However, the overheads of such a scheme and the infrequency of crashes make rebuilding the tree a more reasonable option.

In step (2) (Figure 2.3), the updated counter block will be written back to memory as it gets updated in the counter cache. Unlike Merkle Tree intermediate nodes, counters are critical to keep and persist, otherwise the security of the counter-mode encryption is compromised. Moreover, losing the counter values can result in the inability to restore encrypted memory data. As noted by Liu et al. [39], it is possible to just persist counters of persistent data structures (or a subset of them) to enable consistent recovery. However, this is not sufficient from a security point of view; losing counters' values, even for non-persistent memory locations, can cause reuse of an encryption counter with the same key, which can compromise the security of the counter-mode encryption. Furthermore, legacy applications may rely on OS-level or periodic application-oblivious checkpointing, making it challenging to expose their persistent ranges to the memory controller. Accordingly, a secure scheme that persists counter updates and does not require software alteration is needed. Note that even for non-persistent applications, counters must be persisted on each update or the encryption key must be changed and all of the memory must be re-encrypted with a new key. Moreover, if the persistent region in memory is large, which is likely in future NVM-based systems, most memory writes will naturally be accompanied by an operation to persist the corresponding encryption counters, making step (2) a common event.

Finally, the written block will be sent to the NVM as shown in step ③. Some portions of step ① and step ② are crucial for correct and secure restoration of secure NVMs. Also note that when updating the root of the Merkle Tree on the chip, updating the counter and writing the data are assumed to happen atomically, either using three internal NVM registers to save them before trying to update them persistently or using hold-up power that is sufficient to complete three writes. To avoid incurring high latency to update NVM registers for each memory write, a hybrid approach can be used where three volatile registers can be backed with hold-up power enough to write them

to the slower NVM registers inside processor. Ensuring such write atomicity is beyond the scope of this chapter; our focus is to avoid frequent persistence of updates to counter values in memory and using the fast volatile counter cache while ensuring safe and secure recover-ability.

### Design

We first discuss our threat model, followed by the design of Osiris and the possible design options and trade-offs.

#### Threat Model

Our assumed threat model is similar to state-of-the-art work on secure processors [22, 24, 39, 44]. The trust base includes the processor and all its internal structures. Our threat model assumes that an attacker can snoop the memory bus, scan the memory content, try to tamper with the memory content and replay old packets. Differential power and electromagnetic inference attacks, as well as attacks that try to exploit processor bugs in speculative execution, such as Meltdown and Spectre, are beyond the scope of this chapter. Such attacks can be mitigated through more aggressive memory fencing around critical code to prevent speculative execution. Finally, our proposed solution does not preclude secure enclaves and hence can operate in untrusted Operating System (OS) environments.

Attack on Reusing Counter Values for Non-Persistent Data: While state-of-the-art [39] work relaxes persisting counters for non-persistent data, it introduces serious security vulnerabilities. Specifically, assume an attacker application uses known-plaintext and write it to memory, however, if the memory location is non-persistent the encrypted data will be written to memory but probably not the counter. Thus, by observing the memory bus, the attacker can find out the encryption pad by XORing the observed ciphertext,  $(E_{key}(IV_{new}) \oplus Plaintext)$ , with the Plaintext. Note that

it is also easy to predict the plaintext for some accesses, for instance, zeroing at first access. By now, the attacker knows the value of  $E_{key}(IV_{new})$ . After a crash, however, the memory controller will read  $IV_{old}$  and increment it, which generates  $IV_{new}$  and then encrypt the new application data written to that location to become  $E_{key}(IV_{new}) \oplus Plaintext2$ . Knowing Plaintext2 only needs XORing the ciphertext with the previously observed  $E_{key}(IV_{new})$ . Note that the stale counter could have been already incremented multiple times before the crash, hence multiple writes of the new application can reuse counters with known encryption pads. Note that such an attack only needs a malicious application to run (or just predictable initial plaintext of an application) and having a physical attacker or bus snooper.

### Design Assumption

Counter and MAC are the major secure metadata in current secure memory system. They each serve different purpose. Counters are used for preventing data replay attacks, while MAC values can detect data splicing and spoofing attacks[38]. While there is no argument about where to place counters, MAC values can either be co-located with data on ECC chips, or they are located on the data chips just like counters are[38]. Although MAC is frequently discussed in research community, in commercial products, only ECC chips are normally paired with data chips on memory. Therefore, in this work, we assume MAC will be co-located with data with an extra burst. That requires the change of bus-width.

### Design Options

Before delving deep into the details of Osiris, let's first discuss the challenges of securely recovering the encryption counters after a crash happens. Without a mechanism to persist encryption counters, once a crash occurs, you are only guaranteed that the root (kept in processor) of the

Merkle Tree is updated and reflects the most recent counter values written to memory; any write operation before being sent to NVM will update the affected parts/branches of the Merkle Tree up to the root. Note that most likely the affected branches of the Merkle Tree will be cached on the processor and there is no need to persist them as long as the processor can maintain the value of the root after crash. Later, once the power is back and we want to restore the system, we may have stale counter values in the NVM and stale intermediate values of the Merkle Tree.

Once the system is powered back, any access to a memory location needs two main steps: (1) Obtaining the corresponding most-recent encryption counter from memory. (2) Verifying the integrity of data through MAC and the integrity of the used counter value through Merkle Tree. As it is possible that Step (1) results in a stale counter, Step (2) will fail due to Merkle Tree mismatch. Remember that the root of the Merkle Tree has been updated before crash, thus using any stale counter will be detected. As soon as the error is detected, the recovery process stops. One naïve approach would be to try all possible counter values and use Merkle Tree to verify each value. Unfortunately, such a brute-force approach is impractical due to several reasons. First, finding out the actual value requires trying all possible values for a counter paired with calculating the corresponding hash values to verify integrity, which is impractical for typical encryption counter schemes where there could be  $2^{64}$  possible values for each counter. Second, it is very unlikely that only one counter value is stale; many updated counters in the counter cache will be lost. Thus, reconstructing the Merkle Tree will be almost impractical if there are multiple stale counters. Let's say counters of blocks X and Y are lost, then we need to reconstruct Merkle Tree with all possible combinations/values of X and Y and then compare the resulting root with the one safely stored in processor. While for simplicity we only mention losing two counters, in actual crash where a counter cache is hundreds of kilobytes, we will likely have thousands of stale blocks.

Losing encryption counter values renders reconstructing Merkle Tree nearly impossible. Approaches such as brute-force trial of possibly lost counter values to reconstruct Merkle Tree will

likely take impractical time especially when multiple counter values have been lost. Hence, verifying the integrity/correctness of the counters stored in NVM is challenging.

One possible way to reduce reconstruction time is through employing *stop-loss* mechanisms to limit the number of possible counter values to verify for each counter after recovery. Unfortunately, since there is no way to pinpoint exactly which counters have lost their values, an aggressive searching mechanism is still needed. If we limit the number of writes to each counter block before persisting it to only N, then we need to try up to  $N^S$  combinations for reconstruction where S is the number of data blocks. For instance, let's assume we have a 128GB NVM memory and 64B cache blocks, then we have 2G blocks. If we only set N to 2, then we need up to  $2^{2^{31}} = 2^{2147483648}$  trials. Accordingly, stop-loss mechanism could reduce the time to reconstruct the Merkle Tree, however, still is impractical.

Obviously, a more explicit confirmation is needed before proceeding with an arbitrary counter value to reconstruct the Merkle Tree. In other words, we need a hint on what was the most recent counter value for each counter block. For instance, if the previously discussed stop-loss mechanism is used along with an approach to bookkeep the *phase* within the N trials before writing the whole counter block, then we can start with a more educated guess. Specifically, each time we update a counter block N times in the counter-cache, we need to persist its Nth update in the memory, which means that we need  $log_2N$  bits (i.e., phase) for each counter block be written atomically with the data block. Later, the system starts recovery, it knows the exact difference between the most recent counter value and one used to encrypt the data through the phase value. Co-locating the data blocks with a few bits that reflect most-recent counter value used for encryption can enable fast-recovery of the counter-value used for encryption. Note that if an attacker tries to replay old data along with their phase bits, then the Merkle Tree verification will detect the tampering due to mismatch in the resulting root of the Merkle Tree. Although stop-loss along with phase storage can make the recovery time practical, adding more bits in memory for each cache line is tricky for

several reasons. First, as discussed in [39], increasing the bus-width requires adding more pins to the processor. Even avoiding extra pins by adding extra burst in addition to the 8 bursts of 64-bit bus width for each 64B block is expensive and requires support from DIMMs in addition to under utilization of data bus (only few bits are written in the 64-bit wide memory bus in the last burst). Second, major memory organization changes are needed, e.g., row-buffer size, memory controller timing and DIMM support. Additionally, cache blocks are no longer 64B aligned, which can cause complexity in addressing. Finally, extra bit writes are needed for each cache line to reflect the counter phase, which can map to a different memory bank, hence additional occupation of bank for write latency.

To retain the advantages of stop-loss paired with phase bookkeeping but without extra bits, Osiris re-purposes already existing ECC bits as a fast counter recovery mechanism. The following subsection will discuss in details how Osiris can elegantly employ ECC bits of data to find out the counter used for encryption.

### Design

Osiris mainly relies on inferring the correctness of an encryption counter from calculating the ECC associated with the decrypted text and compares it with that encrypted and stored along with the encrypted cache line. In conventional (not encrypted) systems, when the memory controller writes a cache block to the memory, it also calculates its ECC, e.g., hamming code, and stores it along with the cache line. In other words, the tuple will be written to the memory when writing cache block X to memory is  $\{X, ECC(X)\}$ . In contrast, in encrypted memory systems, there are two options to calculate ECC: ① Using the plaintext, then encrypt it with the cache line before writing both to memory. ② The second option is to encrypt the plaintext, then calculate the ECC over the encrypted block before both are written to the memory. Although approach ② allows overlapping decryption and ECC verification, most ECC implementations used in memory controllers,

e.g., SEC-DED Hsiao Code [48], take less than a nanosecond to complete [49, 50, 51], which is negligible compared to cache or memory access latencies [52]. Additionally, pipelining the arrival of bursts with decryption and ECC bits decoding will completely hide the latency. However, we observe that calculating ECC bits over the plaintext and encrypting it along with the cacheline can provide low-cost and fast way of verifying the correctness of the encryption/decryption operation. Specifically, in the counter-mode encryption, the data is decrypted using the following:  $\{X,Z\}=E_{key}(IV_X)\oplus Y$ , where Y is potentially the encryption of X along with its ECC and Z is potentially equal to ECC(X). In conventional systems, if  $ECC(X) \neq Z$ , then the reason is definitely an error (or tampering) occurred on X or Z. However, when the counter-mode encryption is used, the reason could be an error (or tampering) occurred on X or Z, or wrong IV is used to do the encryption, i.e., decryption is not successful. When the ECC function is applied over the plaintext and the resulting ECC bits are encrypted along with the data, ECC bits can provide a sanity-check for the used encryption counter. Any tampering with the counter value will be detected by a clear mismatch of the ECC bits result from that invalid (wrong/stale counter) decryption; results of  $E_{key}(IV_{old})$  and  $E_{key}(IV_{new})$  are very different and independent. Note that in Bonsai Merkle Tree, data-integrity is protected through MAC values that are calculated over each data and its corresponding counter. While relying on ECC for sanity-checking the used counter can be used, the ECC bits can fail to provide guarantees as strong as cryptographic MAC values. Accordingly, we adopt Bonsai Merkle to additionally protect data integrity. However, ECC bits when combined with counter-verification mechanisms, can provide tamper-resistance as strong as the error detection of the used ECC algorithm. Important Note: Stream ciphers, e.g., CTR and OFP modes, do not propagate errors, i.e., an error in the ith encrypted data bit will result in an error in ith bit of decrypted data, hence the reliability is not affected. In encryption modes where an error in encrypted data results in completely unrelated decrypted text, e.g., block cipher modes, careful consideration is required as encrypting ECC bits can render them useless when there is an error. For our scheme, we focus on state-of-the-art memory encryption, which uses CTR-mode for security and performance reasons.

The question is how to proceed when there is an error detected due to a mismatch between the expected and stored ECC. As the reader would expect, the first step is to find if the error is correctable using the ECC code. If the error is un-correctable, before giving up, we take the odds that the IV used is incorrect, i.e., the decryption was not successful. Our goal is to find out if the error is due to using a wrong IV. Below is a summary of the common reasons for such a mismatch between the expected ECC and the stored ECC after decryption:

Table 2.1: Common sources of ECC mismatch

| Error Type      | Typical Fix                                     |  |

|-----------------|-------------------------------------------------|--|

| Error on stored | can be fixed if the error is correctable, e.g., |  |

| data            | single bit failure                              |  |

| Error on ECC    | typically unrecoverable                         |  |

| Stale/Wrong IV  | Speculate the correct IV and verify it          |  |

As shown in Table 2.1, one reason for such a mismatch is using an old IV value. To better understand how this can happen, we recall the counter cache persistence issue. If a cache block is updated in memory, it is necessary to also update and persist its encryption counter, for both security and correctness reasons. Given the ability to detect the use of stale counter/IV, we can *implicitly* reason about the likelihood of losing the most-recent counter value due to a sudden power loss. To that extent, in theory, we can try to decrypt the data with all possible IVs and stop when an IV successfully decrypts the block, i.e., the resulting ECC matches the expected one (ECC(X) = Z). At that point, there is a high chance that such an IV was actually the one used to encrypt the block, but was either lost due to inability to persist the new counter value after persisting the data, or due to a *relaxed scheme*. Osiris builds upon the later possibility using a relaxed counter persistence scheme employing ECC bits to verify the correctness of the counter used for encryption. As discussed earlier, it is impractical to try all the possible IVs to infer the one used to encrypt the block. Thus, Osiris deploys the stop-loss mechanism to limit such possibility to only N counter updates;

i.e., the correct IV should be within [IV+1,IV+N], where IV is the most recent IV that was stored/persisted in memory. Note that once the speculated/chosen IV passes the first check through ECC sanity-check it also needs to be verified through Merkle Tree.

We propose two flavors for Osiris, baseline *Osiris* and *Osiris-Plus*. In the baseline, all counters being read from memory reflect their most-recent values during normal operation, and the most-recent value is either updated in cache or evicted/written-back to memory. Thus, inconsistency between counters in memory and counters in cache can happen due to crash or tampering with counters in memory. In contrast, Osiris-Plus strives to even outperform Battery-Backed Write-Back counter-cache scheme through purposely skipping counter updates and recovering their most-recent values when reading them back, hence inconsistency can happen during normal operation. Below is a further discussion on both baseline Osiris and Osiris-Plus.

Normal Operation Stage: During normal operation, Osiris adopts write-back mechanism by updating memory counters when evicted from the counter cache. Thus, Osiris can always find the most-recent counter value either in cache or by fetching it from memory in case of miss. Accordingly, Osiris operation in normal operation is similar to conventional memory encryption except that a counter is additionally persisted once each Nth update, hence acting like a write-through for the Nth update of each counter. In contrast, Osiris-Plus allows occasional dropping of most-recent values of encryption counters through relying on run-time recovery mechanism of the most-recent values of counters. In simple words, Osiris-Plus relies on trying multiple possible values on each counter miss to recover the most-recent one before verifying it through Merkle Tree, whereas baseline Osiris would do that only at system recovery time.

**System Recovery Stage:** During system recovery time, both Osiris and Osiris-Plus need to reconstruct Merkle Tree at the time of restoration. Furthermore, both need to use most-recent values of counters to reconstruct a Merkle Tree that eventually has a root that matches the root stored in the

secure processor. In both Osiris and Osiris-Plus, the system recovery will start with traversing all memory locations (cache lines) in integrity verified region (all memory in secure NVM). For each cache line location, i.e., 64B address, the memory controller uses ECC value after decryption as a sanity check of the counter retrieved from memory, however, if the counter value fails the check, all possible N values will be checked to find the most-recently used counter value. Later, the correct value will overwrite the current (stale value) counter in memory. After all memory locations are vetted, Merkle Tree will be reconstructed with the recovered counter values and eventually build up all intermediate nodes and the root. In the final step, the resulting root will be compared with that saved and kept in the processor. If a mismatch occurs, the data integrity of the memory cannot be verified and it is very likely that an attacker has replayed both counter and corresponding encrypted data+ECC blocks.

In the next parts, we will discuss the design of Osiris and Osiris+Plus by guiding the reader through the steps of read/write operations in both schemes.

### Osiris Read and Write Operations

During a write operation, once there is a cache block evicted from LLC, the memory controller will calculate the ECC of the data in the block, as shown in Step ① (Figure 2.4). Note that write operations happen in the background and typically are buffered for a while in the write-pending queue. Later, in Step ②, the memory controller obtains the corresponding counter in case of miss and evict/write-back the evicted counter block, if dirty. The counter value obtained from Step ② will be used to proactively generate the encryption pad, as shown in Step ③. Later, in Step ④, the obtained counter value will be verified (in case of miss) and then the counter and affected Merkle Tree (including root) are updated in Merkle Tree cache. Additionally, unlike typical write-back counter-cache, if the new counter value is a multiple of N or 0, then the new counter value is also persisted before proceeding. Finally, in Step ⑤, the data+ECC is encrypted using the encryption pad and written to memory.

Figure 2.4: Osiris write operation

Figure 2.5: Osiris read operation

During read operation, the memory controller will obtain the corresponding counter value from counter cache (with hit) or memory (with miss) and evict the victim block, if dirty, as shown in Steps ① and ② (Figure 2.5). Later, the obtained counter value will be used to generate the encryption pad as shown in Step ③. In Step ④, the actual data block is read from memory and decrypted using the pad generated in Step ③. Later, in Step ⑤, traditional ECC checking occurs to the decrypted data. Finally, before proceeding, if the counter block is fetched from memory (miss), the integrity of the counter value is verified, as shown in Step ⑥. Finally, as shown in Step ⑦, the memory controller receives the decrypted data which is then forwarded to the cache hierarchy by the memory controller. Note that many of the steps can be overlapped with any conflicts, for instance, Step ⑥ and steps ④ and ⑤.

## Osiris-Plus Read and Write Operations

The write operation in Osiris-Plus is very similar to the write-operation in baseline Osiris except that it does not write back evicted dirty blocks from counter cache (as could happen in Step ② of Figure 2.4); Osiris-Plus recovers the most-recent value of counter each-time it is read from memory and only updates it in memory each Nth update. The read operation of Osiris-Plus is demonstrated in Figure 2.6.

The main difference between Osiris and Osiris-Plus are Steps (5) and (6) in Figure 2.6. Osiris-Plus utilizes additional encryption engines and ECC units to allow fast recovery of the most-recent counter value. Note that given the fact that most AES encryption engines are pipelined and the candidate counter values are sequential, using a single encryption engine instead of N engines can only add N extra cycles. Later, once a counter value is detected, through post-decryption ECC verification, to be the most-recent one, it will be verified through Merkle Tree similar to baseline Osiris. Later, once counter is verified, the data resulting from decrypting the ciphertext with the most-recent counter value will be returned to the memory controller. Note that the recovered

Figure 2.6: Osiris-Plus read operation

counter value is updated in the counter-cache with the recovered value, as shown in Step  $\bigcirc$ .

## Reliability and Recovery from Crash

As mentioned earlier, to recover from crash, Osiris and Osiris-Plus need to first recover the most-recent counter values through utilizing post-decryption ECC bits to find the correct counters. Later, the Merkle Tree will be constructed and the root will be verified and compared with that kept in the root. While the process seems reasonably simple without errors, the recovery process can get complicated in the presence of errors. Specifically, uncorrectable errors in the data or encryption counters render generating a matching Merkle Tree root nearly impossible, and hence the inability to verify the integrity of memory. Note that such uncorrectable errors will have the same effect on integrity-verified memories even without deploying Osiris.

Uncorrectable errors in encryption counters protected by Merkle Tree can potentially fail the whole

recovery process. Specifically, when the system attempts to reconstruct the Merkle Tree, it will fail to generate a matching root. Furthermore, it is also infeasible to know which part of the Merkle Tree causes the problem; only the root is maintained and all other parts of Merkle Tree should work perfectly and generate the same root or none is trusted. One way to mitigate such single-point of failure is to keep other parts of the Merkle Tree in the processor and guarantee they are never lost from the secure processor chip. For instance, for an 8-ary Merkle Tree, the immediate 8 children of the root are also saved all the time in the processor. In a more capable system, the root, its immediate 8 children and their immediate children are kept, which is a total of 73 MAC values. In case recovery fails to produce the root of the Merkle Tree, we can look at which children are mismatching, and then declare that part of the tree as un-verifiable and probably warn the user/OS. While we provide such insights to solve this problem, we assume the system architects choose to only save the root, however, having more NVM registers inside the processors to save more levels of Merkle Tree can be implemented in case of high error systems. In fact, Triad-NVM addressed the importance and the performance overhead for persisting Merkle Tree. Persisting the lower levels of the Merkle Tree can significantly shorten the Merkle Tree recovery after the crash and, speed up the recovery process by 3 orders of magnitude[53]. Anubis, on the other hand, optimizes the Osiris by recording the addresses of updated counters in a reserved table [54]. Moreover, it further discusses how to recover a SGX-style integrity tree [54]. Both papers point out that when integrity tree is used for memory integrity purpose, rebuilding the tree is the most critical task and the time-bound job to guarantee the later recovery of secure metadata and actual data.

To formally describe our recovery process success rate, we can look at two cases. In the first case, when no errors occur in the data, since each 64B memory block has 8B ECC bits, the probability that a wrong counter results in correct (indicate no errors) ECC bits for the whole block is only  $\frac{1}{2^{64}}$ , i.e., similar probability to guessing a 64-bit key correctly, which is next to impossible. Note that each 64B block is practically divided into 8 64-bit words [55], each has its own 8-bit ECC, i.e.,

each bus burst will have 64-bit data and 8-bit ECC (total of 72 bits). This is why most ECC-enabled memory systems will have 9 chips per rank instead of 8, where each chip provides 8 bits. The 9th chip provides the ECC 8-bits for the burst/word. Also note that the 64B block will be read/written as 8 bursts on a 72-bit memory bus.

Bearing in mind the organization of ECC codewords for each 64B memory block, let's now discuss the case where there is actually an error in data.

For an incorrect counter, the probability that an 8-bit ECC codeword indicates that there is no error is  $P_{no-error}=\frac{1}{2^8}$  and the probability of not indicating that there is no-error, i.e., that there is an error, is  $P_{error} = 1 - \frac{1}{2^8}$ . The probability that k codewords of the 8 ECC codewords indicate an error can be represented by a Bernoulli Trial as  $P_k = \binom{8}{k} \times (1 - \frac{1}{2^8})^K \times (\frac{1}{2^8})^{8-K}$ . For example,  $P_2$  represents the probability of having 2 of the 8 ECC codewords flagging an error for a wrongly decrypted data and ECC (semi-randomly generated). Accordingly, if we use our metric to filter out encryption counters that have 4 or more ECC codewords indicating an error, then the probability of our success in detecting wrong counters can be given by  $P_{k\geq 4}=1-(P_0+P_1+P_2+P_3)$ . We find that  $P_{k\geq 4}$  is nearly 100%. Even  $P_{k\geq 7}$  is 99.95%. Note that the probability all 8 codewords indicate an error is 96.91%, which is still very high. In other words, Osiris can successfully identify wrong counters with a success rate of almost 100% by filtering out any counter has 7 or more ECC codewords indicating errors. Thus, except for the pathological case where a cache block has actual errors on each of its words, Osiris can reliably distinguish wrong counters with a success rate of almost 100%. In that extremely pathological case, where each word of the memory block has at least one error, all counter values will be filtered out, and then Osiris can verify all the counters values (e.g., 8 values) through Merkle Tree to recover the correct one. Note that the probability a bit error occurs is very small, however, the described pathological case occurrence requires at least an error to occur on each of the 8 memory words in the block at the same time, which is extremely rare. Note that the words and ECC are typically interleaved and spread in the row and thus nearly

independent[55]. It is also important to note that all of our discussion here about detecting a wrong encryption counter in the presence of errors is relevant to the case of having an error.

In summary, Osiris can detect wrong counter reliably in all cases except the pathological case where there is at least an error *on each word* of the block corresponds to the counter being recovered, which will require an additional step of verification through Merkle Tree. Thus, Osiris does not affect how many errors an ECC can detect/correct per word but limits the number of faulty words within a 64B to not exceed 7 words to avoid additional step (Merkle Tree) before detection/correction. We believe that having errors on each word of a block is an extreme case and will not affect the adoption of Osiris. Note that some PCM prototypes use similar ECC organization but with larger number of ECC bits per 64-bit words, e.g., 16-bit ECC for each 64-bit word[56], which even makes our detection success rate even closer to perfect.

## Different ECC Schemes

The ECC scheme that we employ is the SEC-DEC algorithm[48], one of the widely implemented encoding schemes for memory reliability that corrects 1-bit error. DEC-TEC code that handles multiple-bit(2-bit) error correction is another commonly seen scheme[45]. DEC-TEC codes requires 15 bits for each 64-byte data block. To incorporate DEC-TEC with Osiris, the memory bus width needs to increase another eight bits.

A tiered ECC system is an active direction of research. LOT-ECC, Virtualized ECC, Multi-ECC, Clean-ECC are the representative works in this area that not only provide reliability but concern memory access granularity[57, 58, 59, 60]. All these schemes use additional storage to provide redundant error protection. The similarity among these schemes is that they divide their ECC codes into different tiers that are respectively based on their functions, namely, error detection, error localization and error correction. Multi-ECC uses Reed-Solomon codes(16 bits) for error

detection and erasure correction, using complement checksum for error localization[59]. LOT-ECC was one of the earliest tiered ECC protection schemes. To eliminate a dedicated ECC chip, the error detection code is co-localized with data. Error reconstructions codes comprise the other three tiers. Virtualized ECC, in particular, after error detection, mitigates hardware errors in a software-visible memory pool[58]. Clean-ECC needs a regular 64-bit dbus plus eight bits redundancy. Apart from data chips, two redundant chips serve to store detection codes and correction codes, respectively[60]. Virtualized ECC and Clean-ECC are compatible with Osiris schemes, but due to different per-data vs ECC code length, the minor counter length might need to change. Multi-ECC may be compatible with Osiris, but more knowledge is required for checksum algorithm. Moreover due to the error correction codes, the use of encrypted or non-encrypted error detection codes is to be closely considered.

Other commonly used reliability schemes include but are not limited to parity and Chipkill correction codes[61, 45]. Parity is simple for error detection but lacks the capacity to correct errors. On the other hand, Chipkill-correction code can significantly reduce the uncorrectable error rate by up to more than tenfold (36x or 42x) in comparison to the SECDEC scheme from DRAM[62, 63, 64]

The Chipkill-correction code can guarantee that errors caused by a chip failure are corrected by ECC codes, and it can detect the errors on two different chips, but at the expense of activating four ranks with 18 chips per bank[65].

The assumption that Chipkill is based on is that multiple-bit error(up to four adjacent bits) has a large probability of taking place on one chip[65]. To be capable of fixing four adjacent bits, one implementation of Chipkill is that every four bits will be mapped to four different ECC words. To achieve this, the simplest solution is to interleave four SEC-DEC algorithms[65, 66]. However, this is incompatible with Osiris. The presumption in Osiris is that, every 64-byte data block with its encoded ECC is encrypted with the same counter. However, when 4 SEC-DEC algorithms

are interleaved, per 64-byte data is encoded by 4 different ECCs and therefore is difficult to be encrypted by a single counter. However, we do not rule out other implementations of Chipkill are not compatiable with Osiris. In commercialized chipkill-level products, not only can two failed devices be detected, but also one (SCCDCD) or two(Double Chip Sparing) failed devices can be corrected[67].

When NVM is used as storage, the most commonly used ECC schemes are BCH and LDPC[68]. However, counter-mode encryption is not used in SSD or flash disks and, therefore, is not discussed here.

### Systems without ECC

Some systems do not employ ECC bits, but rather rely on MAC values that can be co-located with data instead of ECC bits [44]. For instance, the ECC chips in the DIMM can be utilized to store the MAC values of the Bonsai Merkle Tree to allow obtaining data integrity verification MACs along with the data. While our description of Osiris and Osiris-Plus was focused on using ECC, MAC values can also be used to achieve the exact same purpose; a sanity-check for the decryption counter used. The only difference is that if there is an error, when ECC bits are used, we can use the number of mismatched ECC bits as a way to guess the counter value, whereas MAC values tend to differ significantly when there is any error in data. Accordingly, to mitigate this problem, MAC values that are aggregations of multiple MACs per word, e.g., 64 bits that are made of eight bits for each 64 data bits, can be used; in this way, the difference between the generated MACs and the stored MACs for different counter values can be used as a selection criteria for the candidate counter value. Note that our proposed schemes also work with ECC and MAC co-designs such as Synergy(parity+MAC)[44].

## System with both ECC and MAC