# Scholars' Mine

**Doctoral Dissertations**

Student Theses and Dissertations

Spring 2020

# Novel approaches for reliable and efficient circuit design

Prashanthi Metku

Follow this and additional works at: https://scholarsmine.mst.edu/doctoral\_dissertations

Part of the Computer Engineering Commons Department: Electrical and Computer Engineering

### **Recommended Citation**

Metku, Prashanthi, "Novel approaches for reliable and efficient circuit design" (2020). *Doctoral Dissertations*. 2871. https://scholarsmine.mst.edu/doctoral\_dissertations/2871

This thesis is brought to you by Scholars' Mine, a service of the Missouri S&T Library and Learning Resources. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

# NOVEL APPROACHES FOR RELIABLE AND EFFICIENT CIRCUIT DESIGN

by

# PRASHANTHI METKU

## A DISSERTATION

Presented to the Graduate Faculty of the

### MISSOURI UNIVERSITY OF SCIENCE AND TECHNOLOGY

In Partial Fulfillment of the Requirements for the Degree

## DOCTOR OF PHILOSOPHY

in

# COMPUTER ENGINEERING

2020

Approved by:

Dr. Minsu Choi, Advisor Dr. Daryl Beetner Dr. Sahra Sedigh Sarvestani Dr. Joe Stanley Dr Abusayeed Saifullah

© 2020

# Prashanthi Metku

All Rights Reserved

### PUBLICATION DISSERTATION OPTION

This dissertation consists of the following four articles, formatted in the style used by the Missouri University of Science and Technology:

Paper I, found on pages 6–32, Adaptive Multi-path BCH Decoder to Alleviate Hotspot-induced DRAM Bit Error Variation in 3D Heterogeneous Processor published in Journal of Semiconductor Technology and Science.

Paper II, found on pages 33–51, Novel Area-Efficient Null Convention Logic based on CMOS and Gate Diffusion Input (GDI) Hybrid Methodology accepted in Journal of Semiconductor Technology and Science.

Paper III, found on pages 52–80, A Low Power Design Technique for the Asynchronous Null-Convention Logic Circuits is intended for submission to IEEE Transactions on Very Large Scale Integration (VLSI) Systems.

Paper IV, found on pages 81–103, Energy-Performance Scalability Analysis of a Novel Quasi-Stochastic Computing Approach published in Journal of Low Power Electronics and Applications.

#### ABSTRACT

In this research work, a suite of approaches are presented to improve reliability of 3D heterogeneous processors (3DHP) and to reduce the area overhead of asynchronous designs. This work is primarily divided into two parts. In the first part, we present an approach for improving reliability in 3DHP. Typically, in 3DHP, thermal hotspots introduce spatial and temporal variability that results in wide bit error variation in DRAM dies. To address this issue multi- path BCH decoder is introduced. Based on the thermal gradient data generated by on-chip temperature sensors, the proposed methodology specializes in adaptively estimating the number of errors in the incoming word and also selecting the fast decoding path to correct these errors. Thus, provides DRAM error protection with minimal decoding latency. In the next part of this work, we focus on reducing the area overhead of asynchronous paradigm-driven null convention logic (NCL) design using Gate Diffusion Input (GDI). We first develop technique for realizing NCL gates. In the process, we demonstrate that there is a voltage swing at the output that may introduces errors. To address this limitation, a HYBRID approach is introduced where conventional complementary metal oxide semiconductor (CMOS) technology is integrated with GDI methodology. With this approach, we demonstrate that we can reduce the transistor count (TC) of the NCL designs while addressing the limitations due to voltage drop. To further reduce the TC of the NCL designs, GNCL is developed. This approach utilizes the regenerative buffers to overcome the performance degradation and also reduce the area overhead. Overall in this dissertation, we demonstrate reductions in area and power overheads for asynchronous designs.

### ACKNOWLEDGMENTS

I want to extend my sincere gratitude to my advisor, Dr. Minsu Choi for allowing me to work and learn under his tutelage and helping me acquire invaluable insights to make this work possible. Dr. Choi's constant support and patience has helped me develop the skills at my own pace and time. All these years working under him will go down as some of the most valuable and productive years of my student life.

I profoundly thank Dr. Daryl Beetner, Dr. Sahra Sedigh Sarvestani, Dr. Joe Stanley and Dr Abusayeed Saifullah for being my committee members and for their valuable inputs. I would also like to thank my lab partners and friends from Missouri University of Science and Technology especially Krishnan Raghavan and Vikram Chowdhury, for providing help and support during the course of my doctoral studies at Missouri S&T.

I am immensely grateful and owe my utmost gratitude towards my parents Venkateshwar Metku and Kalpana Metku for giving me the chance to be who I am today. Thank you both for believing in me and giving me strength to chase my dreams. Finally, special thanks to my brothers Virjanand Sagar, Vivekanand Sagar amd Sandeep Nallagula for constant understanding and encouragement.

# **TABLE OF CONTENTS**

| Page                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------|

| PUBLICATION DISSERTATION OPTIONiii                                                                                           |

| ABSTRACTiv                                                                                                                   |

| ACKNOWLEDGMENTSv                                                                                                             |

| LIST OF ILLUSTRATIONS                                                                                                        |

| LIST OF TABLES                                                                                                               |

| SECTION                                                                                                                      |

| 1. INTRODUCTION                                                                                                              |

| PAPER                                                                                                                        |

| I. ADAPTIVE MULTI-PATH BCH DECODER TO ALLEVIATE HOTSPOT<br>INDUCED DRAM BIT ERROR VARIATION IN 3D HETEROGENEOUS<br>PROCESSOR |

| ABSTRACT 6                                                                                                                   |

| 1. INTRODUCTION                                                                                                              |

| 2. ARCHITECTURE                                                                                                              |

| 3. ADAPTIVE MULTI-PATH DECODER DESIGN                                                                                        |

| 3.1. SYNDROME BLOCK DESIGN FOR MULTI-PATH BCH DECODER 14                                                                     |

| 3.2. EEROR LOCATOR POLYNOMIAL CALCULATOR DESIGN                                                                              |

| 3.3. CHIEN SEARCH BLOCK DESIGN 18                                                                                            |

| 3.4. PARALLEL ADAPTIVE BCH DECODING FOR REDUCED<br>DECODING                                                                  |

| 4. PERFORMANCE EVALUATION                                                                                                    |

| 4.1. SERIAL DECODING PERFORMANCE EVALUATION                                                                 | 23 |

|-------------------------------------------------------------------------------------------------------------|----|

| 4.1.1. Average Decoding Latency for Various Bit Error Probabilities                                         | 25 |

| 4.1.2. Cumulative Error Coverage                                                                            | 27 |

| 4.2. PARALLEL DECODING PERFORMANCE                                                                          | 27 |

| 5. CONCLUSION                                                                                               | 29 |

| BIBLOGRAPHY                                                                                                 | 30 |

| II. NOVEL AREA-EFFICIENT NULL CONVENTION LOGIC ON CMOS AND<br>GATE DIFFUSION INPUT (GDI) HYRBID METHODOLOGY | 33 |

| ABSTRACT                                                                                                    | 33 |

| 1. INTRODUCTION                                                                                             | 33 |

| 2. PRELIMINARIES AND REVIEW                                                                                 | 36 |

| 2.1. NULL CONVENTION LOGIC                                                                                  | 36 |

| 2.2. GATE DIFFUSION INPUT                                                                                   | 40 |

| 3. THE PROPOSED HYBRID METHODOLOGY                                                                          | 41 |

| 3.1. REALIZATION OF NCL USING FNCL APPROACH (BASED ON F1<br>AND F2 FUNCTIONS OF GDI GATE)                   | 41 |

| 3.2. PERFORMANCE DEGRADATION OF FNCL APPROACH                                                               | 43 |

| 3.3. CMOS-GDI HYBRID APPROACH                                                                               | 45 |

| 4. PERFORMANCE EVALUATION                                                                                   | 47 |

| 4.1. NCL GATES UTILIZED FOR REALIZING NUI CIRCUITS                                                          | 48 |

| 4.2. TRANSISTOR COUNT FOR VARIOUS NUI IMPLEMENTATIONS                                                       | 48 |

| 5. CONCLUSION                                                                                               | 50 |

| BIBLOGRAPHY                                                                                                 | 50 |

| III. | A LOW POWER DESIGN TECHNIQUE FOR THE ASYNCHRONOUS NULL-CONVENTION LOGIC CIRCUITS       | 52  |

|------|----------------------------------------------------------------------------------------|-----|

|      | ABSTRACT                                                                               | 52  |

|      | 1. INTRODUCTION                                                                        | 53  |

|      | 2. PRELIMINARIES AND REVIEW                                                            | 56  |

|      | 3. LIMITATION OF NCL                                                                   | 59  |

|      | 4. PROPOSED APPROACH FOR DESIGNING NCL CIRCUITS                                        | 61  |

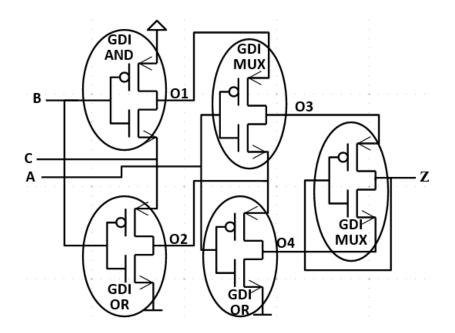

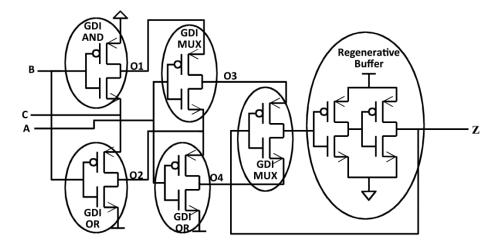

|      | 4.1. BASIC IMPLEMENTATION OF NCL GATES USING GDI<br>TECHNIQUE (GDI-NCL TECHNIQUE)      | 61  |

|      | 4.2. GENERALIZED APPROACH (GNCL) FOR REALIZING NCL GATES                               | 68  |

|      | 5. SIMULATION RESULTS                                                                  | 69  |

|      | 5.1. 27 FUNDAMENTAL NCL GATES                                                          | 71  |

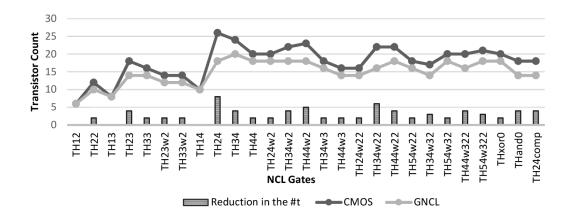

|      | 5.1.1. Transistor Count                                                                | 71  |

|      | 5.1.2. Power Consumption                                                               | 72  |

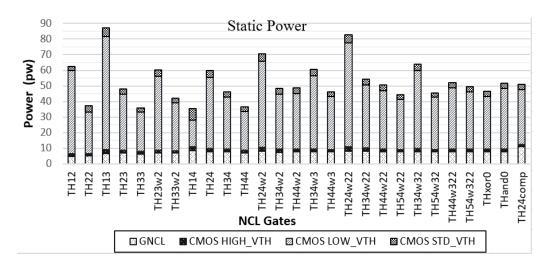

|      | 5.1.2.1. Static power                                                                  | .72 |

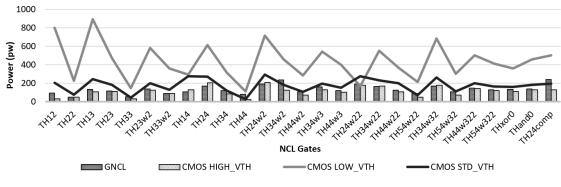

|      | 5.1.2.2. Dynamic power.                                                                | .72 |

|      | 5.2. COMBINATIONAL CIRCUITS                                                            | 73  |

|      | 5.2.1. Transistor Count                                                                | 74  |

|      | 5.2.2. Power Consumption                                                               | 74  |

|      | 5.2.2.1. Static power                                                                  | .75 |

|      | 5.2.2.2. Dynamic power.                                                                | .76 |

|      | 6. CONCLUSION                                                                          | 76  |

|      | BIBLOGRAPHY                                                                            | 77  |

| IV.  | ENERGY-PERFORMANCE SCALABILITY ANALYSIS OF A NOVEL QUASI-STOCHASTIC COMPUTING APPROACH | 81  |

|      | ABSTRACT                                                                               | 81  |

| 1. INTRODUCTION                                                                    | 82  |

|------------------------------------------------------------------------------------|-----|

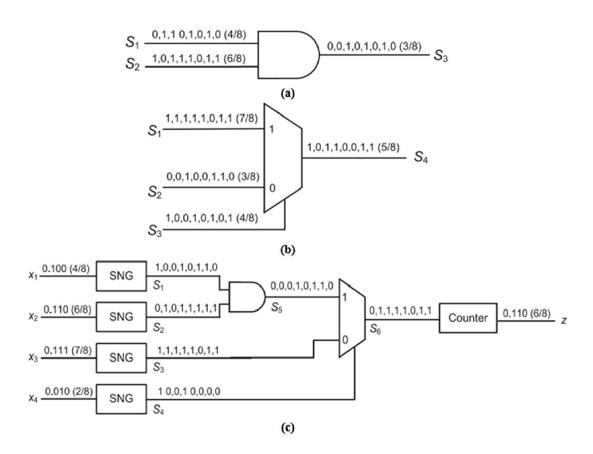

| 2. BACKGROUND                                                                      | 83  |

| 2.1. STOCHASTIC COMPUTING                                                          | 83  |

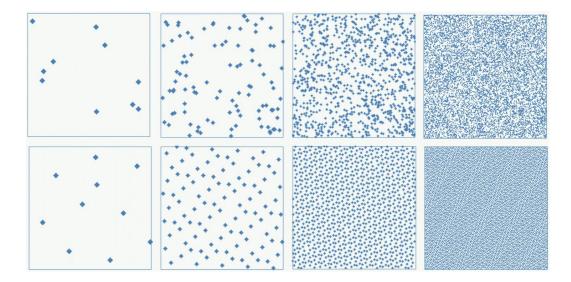

| 2.2. QUASI-STOCHASTIC BIT SEQUENCE GENERATION                                      | 85  |

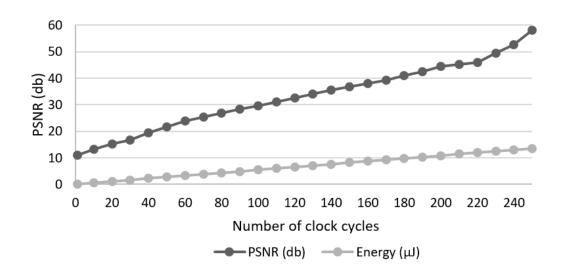

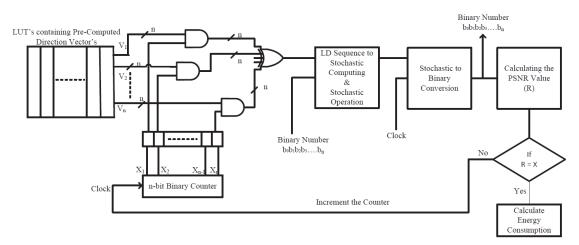

| 3. ENERGY PERFORMANCE SCALABILITY OF NOVEL QUASI-<br>STOCHASTIC COMPUTING APPROACH | 88  |

| 4. SIMULATION-BASED ENERGY-PERFORMANCE SCALABILITY<br>ANALYSIS                     | 93  |

| 5. CONCLUSION                                                                      | 101 |

| BIBLOGRAPH                                                                         | 102 |

| SECTION                                                                            |     |

| 2. CONCLUSION                                                                      | 104 |

| BIBLIOGRAPHY                                                                       | 105 |

| VITA                                                                               | 108 |

# LIST OF ILLUSTRATIONS

| PAPER I Page                                                                                    |

|-------------------------------------------------------------------------------------------------|

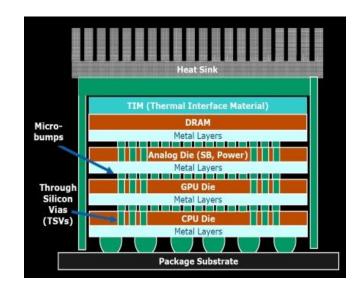

| Figure 1. 3D stacking of CPU, GPU, analog and DRAM dies using TSVs 8                            |

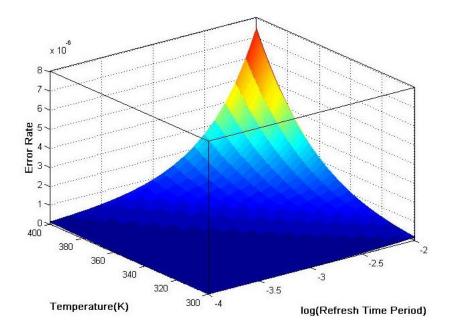

| Figure 2. DRAM error rate as a function of temperature and refresh period reported in [4]       |

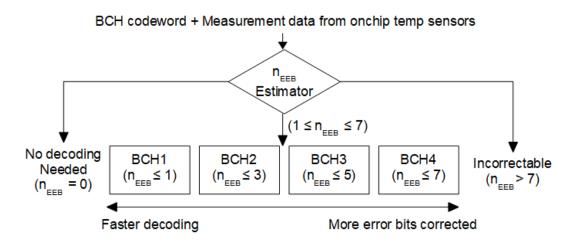

| Figure 3. The proposed multi-path BCH Decoder                                                   |

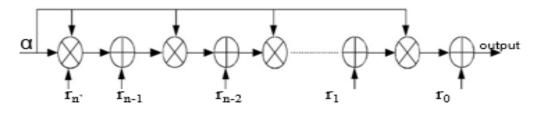

| Figure 4. Syndrome block diagram                                                                |

| Figure 5. Chien Search block diagram for t = 5 case                                             |

| Figure 6. An example of the proposed parallel decoding                                          |

| Figure 7. Distribution of error probabilities for variable $p_{BE}$ values                      |

| PAPER II                                                                                        |

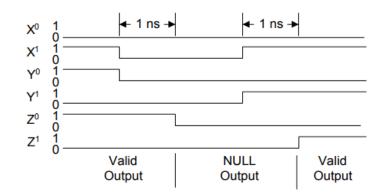

| Figure 1. Dual-rail representation of NCL AND function                                          |

| Figure 2. NCL system framework                                                                  |

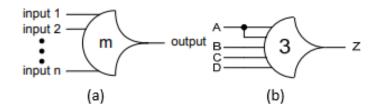

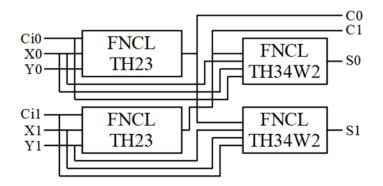

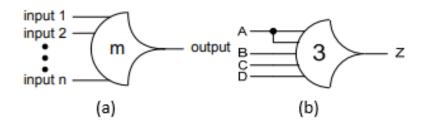

| Figure 3. (a) THmn threshold gate (b) TH34w2 threshold gate                                     |

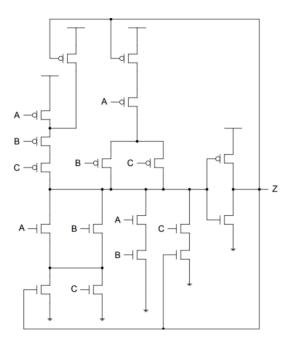

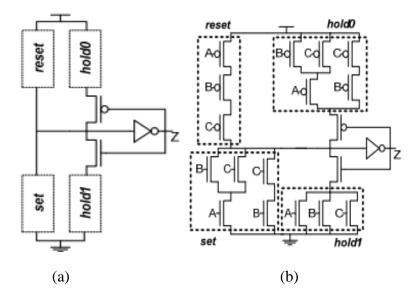

| Figure 4. Transistor level realization of TH23 gate using Static CMOS methodology 39            |

| Figure 5. Transistor level implementation of TH23 gate using semi-static methodology 39         |

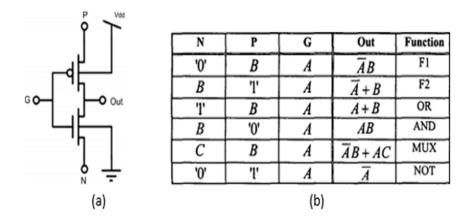

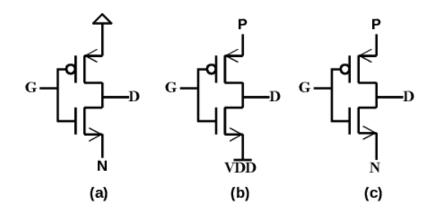

| Figure 6. (a) Basic GDI cell structure (b) Different functions input configurations 40          |

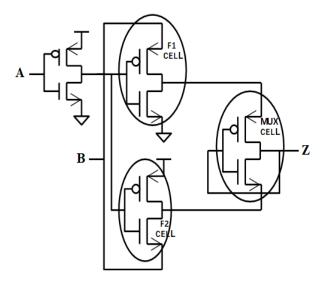

| Figure 7. FNCL implementation of TH22 gate                                                      |

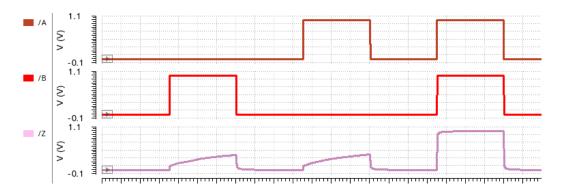

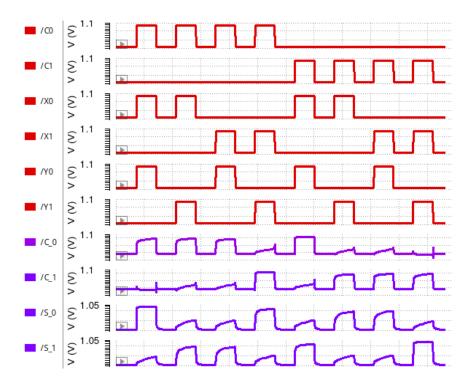

| Figure 8. Simulation results demonstrating voltage drop of FNC TH22 gate                        |

| Figure 9. Structure of FNCL FA                                                                  |

| Figure 10. Simulation results of FA validating the volatge drop at sum is greater than carryout |

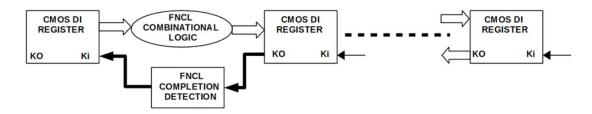

| Figure 11. The proposed HYBRID framework                                                        |

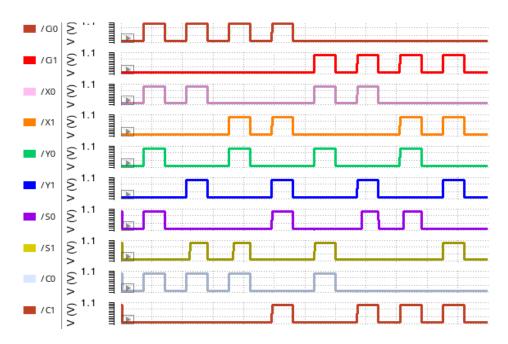

| Figure 12. Simulation results of a 1-bit full adder using HYBRID approach                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------|

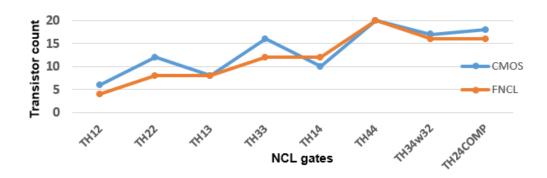

| Figure 13. Number of transistors utilized by CMOS and FNCL                                                                             |

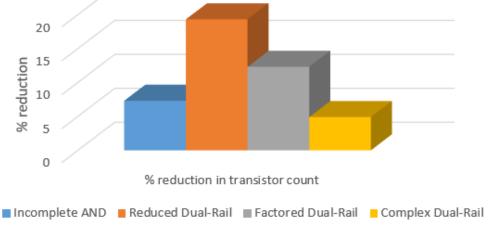

| Figure 14. Percentage reduction in the transistor count                                                                                |

| PAPER III                                                                                                                              |

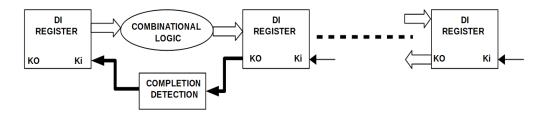

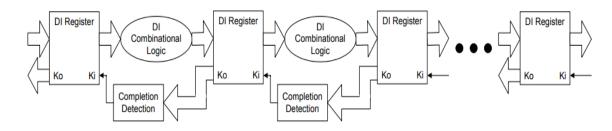

| Figure 1. NCL framework                                                                                                                |

| Figure 2. (a) THmn threshold gate (b) TH34w2 threshold gate                                                                            |

| Figure 3. (a) Structure of static CMOS implementation of NCL gates (b) Static<br>CMOS transistor level implementation of TH23 NCL gate |

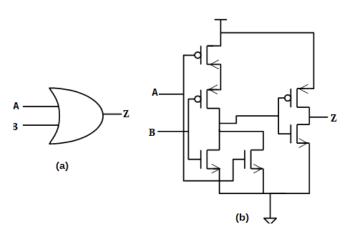

| Figure 4. Conventional Boolean OR gate (a) symbol (b) Static CMOS implementation. 59                                                   |

| Figure 5. (a) NCL input-complete OR function: Z=X+Y (b) Static CMOS implementation of TH22 NCL gate                                    |

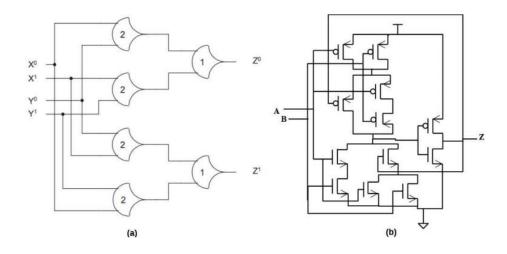

| Figure 6. Structures of different GDI functionality cells                                                                              |

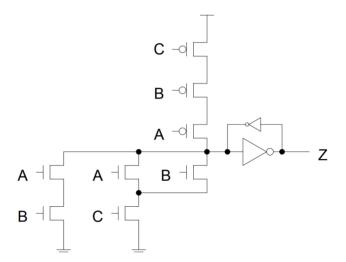

| Figure 7. GDI implementation of TH23 NCL gate                                                                                          |

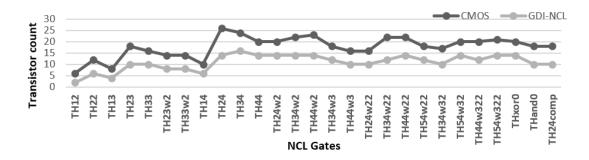

| Figure 8. Number of transistors required for implemetung NCL gates using CMOS<br>and GDI-NCL methodology                               |

| Figure 9. GDI-NCL implementation of few NCL gates                                                                                      |

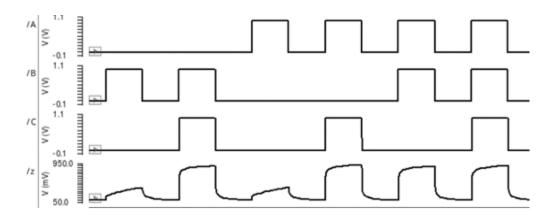

| Figure 10. Voltage drop at the output of GDI-NCL TH23 gate                                                                             |

| Figure 11. Voltage drop at the output of GDI-NCL TH23 gate for different input combinations                                            |

| Figure 12. Addition of regnerative buffer at the output of GDI-NCL TH23                                                                |

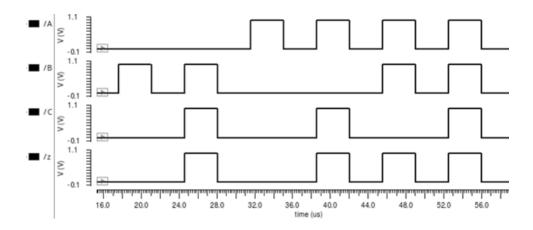

| Figure 13. Output wavefprm of GDI-NCL TH23 gate after the use of renerative buffers                                                    |

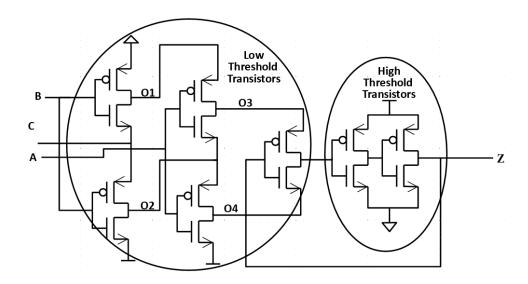

| Figure 14. GNCL implementation of TH23 gate                                                                                            |

| Figure 15. Transistor counts for 27 NCL gates using CMOS and GNCL techniques 71                                                        |

| Figure 16. Static power consumption of 27 NCL gates                                                                                    |

| Figure 17. Dynamic power consumption of 27 NCL gates                                                                | 73  |

|---------------------------------------------------------------------------------------------------------------------|-----|

| PAPER IV                                                                                                            |     |

| Figure 1. Basic circuits used in stochastic computation.                                                            | 84  |

| Figure 2. Distribution of pseudo-random points (top) and LD points (bottom) in the unit square                      | 86  |

| Figure 3. Accuracy and energy consumption during edge detection of clock test image                                 | .90 |

| Figure 4. Structure of EQSNG                                                                                        | 91  |

| Figure 5. Open source test images used for edge detection                                                           | 94  |

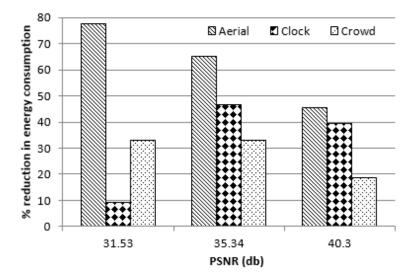

| Figure 6. Reduction in energy consumption for various PSNR values using EQSNG methodology compared to LFSR approach | 96  |

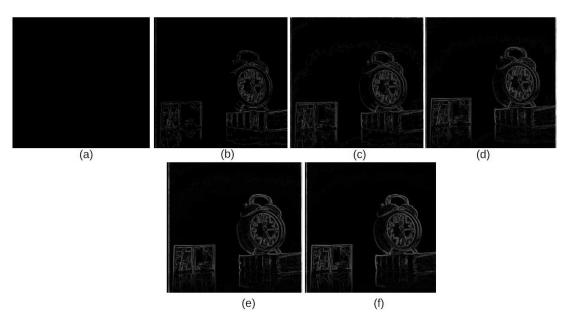

| Figure 7. Edge detection on the clock test image using the proposed EQSNG SC apporach                               | 98  |

| Figure 8. Edge detection on the clock test image using conventional LFSR-based SC apporach.                         | 98  |

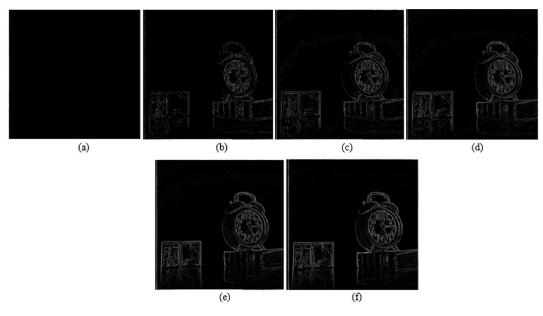

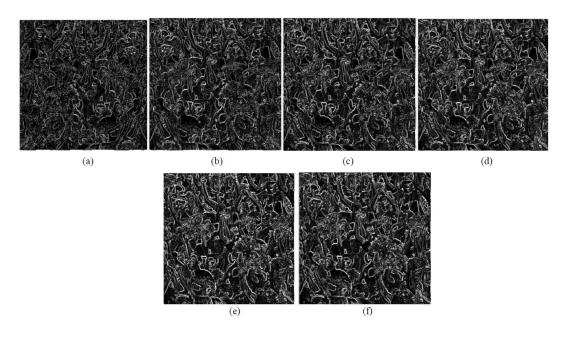

| Figure 9. Edge detection on the crowd test image using the proposed EQSNG SC apporach                               | 99  |

| Figure 10. Edge detection on the crowd test image using conventional LFSR-based SC apporach.                        |     |

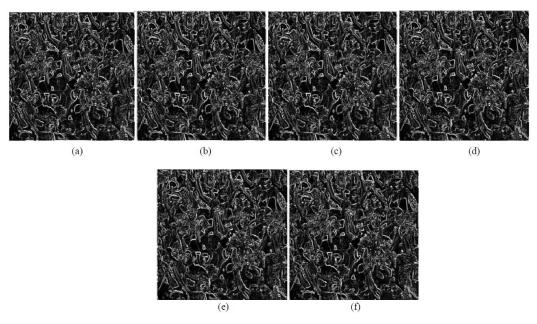

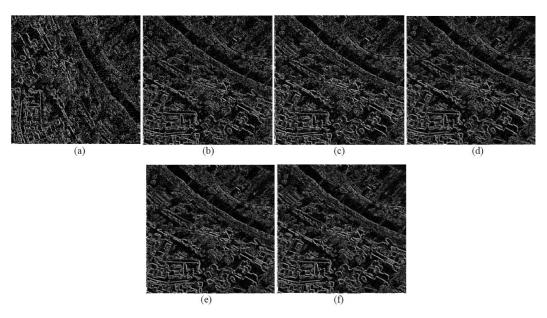

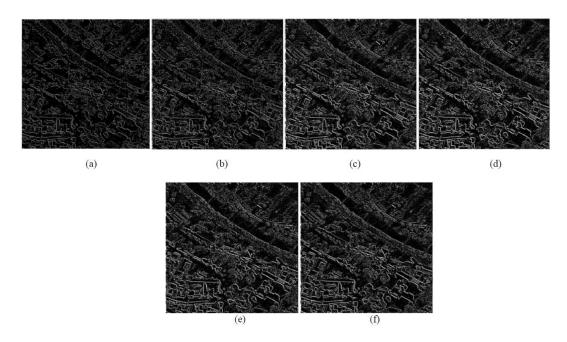

| Figure 11. Edge detection on the aerial test image using the proposed EQSNG SC apporach                             | .00 |

| Figure 12. Edge detection on the aerial test image using conventional LFSR-based SC apporach                        | .00 |

# LIST OF TABLES

| PAPER I Page                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 1. FPGA resource utilization and decoding latency of four decoding paths in the proposed adaptive multi-path BCH decoder                        |

| Table 2. Average decoding latency (ADL) for different p <sub>BE</sub> values                                                                          |

| Table 3. Cumulative error coverage for various pBE values    26                                                                                       |

| Table 4. Parallel decoding simulation results showing the average decoding latency by varying $pBE_{H}'pBE_{C}$ , $f_{hot}'f_{cold}$ and $size_{buf}$ |

| PAPER II                                                                                                                                              |

| Table 1. Comparison of static CMOS and HYBRID methodologies       49                                                                                  |

| PAPER III                                                                                                                                             |

| Table 1. GDI-NCL TH23 gate results for different input combinations                                                                                   |

| Table 2. Total number of transistor used for implemententing various NCL circuit 74                                                                   |

| Table 3. Static power consumption for different NCL circuits       75                                                                                 |

| Table 4. Dynamic power consumption for different NCL circuits       75                                                                                |

| PAPER IV                                                                                                                                              |

| Table 1. Table showing the no of clock cycles and energy consumption for various         PNSR                                                         |

### **SECTION**

#### **1. INTRODUCTION**

For the past few decades, scientists have been scaling devices to increasingly smaller feature sizes for enhanced performance of complementary metal-oxide semiconductor (CMOS) technology, thereby increasing the functionality of integrated circuits and systems [1, 2, 3]. However, with the exponential growth of transistor densities, power efficiency has become primary determinant of performance in todays' semiconductor industry [4]. In addition to power concerns, off-chip bandwidth trends are also expected to have a major impact on the scalability of the future designs [5]. In particular, the demand for high computing performance has increased in accordance with the requirements for smaller and more energy efficient devices. One way to obtain high computation performance is by increasing the robustness of a single processor [7]. This can be achieved by increasing its clock frequency and mounting more transistors such that more calculations could be executed. However, with the physical limits of such processors being fully exploited and an advanced version of computing strategy, heterogeneous computing i.e. using heterogeneous or hybrid platform containing more than one type of processor was introduced such that different types of tasks can be executed by processors that are specialized in them [7].

Recently, many of highly-ranked Performance computing systems include discrete Graphics Processing Unit accelerators (GPU) [8]. Systems where discrete GPUs are connected to CPUs over PCI-E bus, however, frequently suffer from a significant data copy overhead between two processors. To address this limitation, researchers in industry and academia are trying to seek a solution in a single-chip heterogeneous processors where CPU and GPU share a unified memory hierarchy [9]. However, parallelism and scalability of such heterogeneous processors are still severely constrained by limited bandwidth, high latency, and energy consumption of offchip DRAM [10, 11]. To address these bottlenecks, the processor architecture is evolving toward a 3D heterogeneous integration (commonly termed as 3DIC) [12]. In 3DIC four heterogeneous dies (i.e., CPU, GPU, analog and DRAM) are vertically interconnected by a massive number of through-Silicon Vias (TSVs). Compared with the traditional off-chip interconnects, TSVs enable a massive number of vertical channels among CPU, GPU and DRAM dies while providing much shorter distance of data travel [12, 13]. Therefore, 3DHP technology is anticipated to inherently provide much higher bandwidth, low latency and power consumption. Despite numerous unprecedented benefits, however, there is a big challenge which is a thermal reliability issue [13].

A significantly higher power density, thinned substrate, and low thermal conductivity of inter-layer material all make heat dissipation a serious problem that threatens circuit reliability and performance in 3DIC [13]. Various design-time solutions are available to tackle hotspots in 3DIC designs but the transient nature of thermal hotspots cause the design time solutions less effective. The increase in power density of 3D stacking causes an elevation in the temperature, which nominally results in an exponential rise in charge leakage of DRAM cells [13]. Therefore, requires significant increase in refresh frequency to retain data at the expense of additional power and performance overhead. Also, the spatial and temporal variability in temperature (i.e., hotspots) further complicates

the DRAM reliability issues thereby requiring error detection and correction (EDAC) techniques.

The conventional 2D EDA assume a near constant bit error rate (BER) over time. Hence, EDAC engine does not need to be designed to adapt to a varying BER over time. For instance, state-of-the-art SECDED (Single Error Correction, Double Error Detection) code [14] and buses with CRC (Cyclic Redundancy Check) code [15] cannot be directly applied to the proposed 3DHP, since it is anticipated to have a varying BER and TSV failure rate over time caused by the thermally-induced reliability issues. Therefore, a novel approach to tackle this limitation is presented in the first part i.e. paper I of this dissertation.

The second and third part of this dissertation discuss about the asynchronous paradigm, null convention logic (NCL). The advantages, limitations and a methodology to address these challenges have also been part of the dissertation. Conventional synchronous logic with clocked structures have been dominating semiconductor industry over the past decades [16]. However, the continuous decreasing in the feature size and increasing operating frequency of integrated circuits (IC), clock-related issues such as clock skews, increased power at the clock edges, extra area, and layout complexity for clock distribution networks, and glitches are emerging as the dominant factor hindering increased performance [17]. These limitations have caused renewed interest asynchronous digital design. Asynchronous, clockless circuits require less power, generate less noise, and produce less electro-magnetic interference (EMI), compared to their synchronous counterparts, without degrading performance. Furthermore, delay-insensitive (DI) asynchronous paradigms have a number of additional advantages, especially when designing complex circuits, like Systems-on-a-Chip (SoCs), including substantially

reduced crosstalk between analog and digital circuits, ease of integrating multi-rate circuits, and facilitation of component reuse [18, 19].

Null Convention Logic (NCL) is a delay-insensitive (DI) asynchronous. NCL was first proposed by Karl Fant and Scott Brandt in 1994 [20, 21], and further developed by Dr. Scott Smith's research group [22]. NCL initially aimed at designing Application Specific Integrated Circuit (ASIC) and Very-large-scale Integration (VLSI) circuits with lower power, lower noise, and lower electromagnetic interference (EMI). Various NCL based circuits have shown these characteristics. An NCL based Motorola STAR08 processor [23] shows the power and noise reduction up to 40% and 10dB, respectively, comparing to its synchronous counterpart. In [24], an 8-operation NCL ALUs was designed as a benchmark. The simulation result shows that the dual-rail NCL circuit consumes less power and other designs like NCL divider [25] and NCL multiply-and-accumulate unit [26] have shown the benefits of speed improvement and reduction in power consumption, noise, and EMI. However, the major drawback of NCL designs is that it requires a larger area compared with the conventional Boolean logic version. The area overhead is approximately 1.5-2 times as much as an equivalent synchronous design when using static CMOS gates, but less for semi-static CMOS gates [27].

This dissertation proposes and demonstrates two novel approaches to address this limitation of NCL. These approaches when compared with the conventional static CMOS methodology show a significant reduction in the transistor count which in turn helps in reducing the area overhead. However, power and delay analysis in the first approach was not fully studied. Similarly, latency analysis of the second approach will be the part of the future work. In additional to these work, additional research has conducted in the area of stochastic computing (SC) which is discussed in the fourth part of the dissertation. Traditionally, SC's accuracy heavily depends on the stochastic bitstream length. Therefore, generating acceptable approximate results while minimizing the bitstream length is challenging, as energy consumption tends to linearly increase with bitstream length. To address this issue, a novel energy-performance scalable approach based on quasi-stochastic number generators is proposed and validated in this work.

### PAPER

### I. ADAPTIVE MULTI-PATH BCH DECODER TO ALLEVIATE HOTSPOT-INDUCED DRAM BIT ERROR VARIATION IN 3D HETEROGENEOUS PROCESSOR

### ABSTRACT

A 3D heterogeneous processor (commonly termed as 3DHP) integrates multiple processor (such as CPU/GPU) and DRAM dies, interconnected vertically by a massive number of Through-Silicon Vias (TSVs). The 3DHP is expected to address the limited bandwidth, high latency and energy consumption of off-chip DRAM. However, spatial and temporal variability due to hotspots in on-chip thermal gradient may result in wide bit error variation in DRAM dies. This work proposes a novel adaptive multi-path BCH decoder to efficiently address this issue. Instead of having a static BCH decoder designed from the worst-case bit error probability analysis, the proposed adaptive multi-path BCH decoder offers multiple decoding paths with varying target number of error bits to correct, which is estimated from the thermal gradient data generated by on-chip temperature sensors. Thus minimizes the overall decoding latency adaptively. The proposed approach has been verified by implementing an adaptive 4-path BCH decoder in FPGA hardware. A series of decoding performance evaluation data has been generated to demonstrate the efficiency of the proposed design.

### **1. INTRODUCTION**

Processors are evolving toward a 3D heterogeneous integration (3DIC) of CPU, GPU and DRAM dies vertically interconnected by TSVs (Through-Silicon Vias) to alleviate power, bandwidth and latency bottlenecks. Figure. 1 shows an example where four heterogeneous dies (i.e., CPU, GPU, analog and DRAM) are stacked and interconnected by TSVs. When compared with the traditional off-chip interconnects, TSVs enable a massive number of vertical channels along CPU, GPU and DRAM dies while proving a much shorter distance of data travel. Therefore, 3DHP technology is anticipated to inherently provide higher bandwidth, low latency and low power consumption. Despite the numerous unprecedented benefits, 3DHP face a big challenge which is thermal reliability issues.

The conventional 2D integration/packaging technology is mature enough to assume a near constant bit error probability (BEP) over time in DRAM. Hence, the Error Detection and Correction (EDAC) engine does not need to be designed to adapt to a varying BEP over time. However, the same EDAC strategy cannot be directly applied to 3DHP, since it is anticipated to have a varying BEP caused by hotspots (i.e., spatial/temporal variation in temperature). Various design-time solutions are available to tackle hotspots in 3DIC designs but the transient nature of thermal hotspots cause the design time solutions to be less effective. It is thus important to monitor the chip temperature during runtime using distributed temperature sensors to avoid potential temperature-induced failures. The main objective of this work is to propose and validate a novel adaptive multi-path BCH error correction decoder that provides just-enough DRAM error protection to minimize the overall decoding latency. The proposed decoder can be coupled with on-chip distributed temperature sensor network to analyze the thermal gradient to adaptively tolerate spatial/temporal bit error variance in a 3DHP.

Figure 1. 3D stacking of CPU, GPU, analog and DRAM dies using TSVs [1]

This article is organized as follows. Preliminaries and review are given in Section 2. Then, the proposed adaptive multi-path BCH decoder design is extensively discussed in Section 3. Design and performance evaluation data including the area and latency are included in Section 4. Finally, concluding remarks are made in Section 5.

### **2. ARCHITECTURE**

In 3DHP, the increase in power density of 3D stacking causes an elevation in the temperature, which nominally results in an exponential rise in charge leakage of DRAM cells. Therefore, requires significant increase in refresh frequency to retain data at the

expense of additional power and performance overhead. Also, the spatial and temporal variability in temperature (i.e., hotspots) further complicates the DRAM reliability issues.

The Leakage power of DRAM cell is modeled to exponentially increase with temperature, T, as  $P_{\text{leakage}} = P^0 \cdot \exp(-A / A - B)$  where  $P^0$  is the room-temperature leakage power and parameters A and B are empirical constants [2], [3]. The number of discharged cells in DRAM is proportional to the dissipation of the leakage power of cells. In [4], the relation between the error rate (i.e., the number of discharged cells divided by the total number of cells) and temperature is modeled as  $E_{DRAM} \propto P_{leakage}$  where  $E_{DRAM}$ is the error rate and P<sub>leakage</sub> is a function of T. The retention time distribution of cells is known to be divided into two regions: 1) tail distribution, and 2) main distribution [5]. For thermally-stable operation condition, the retention time of almost all the memory cells belong to "Main Distribution". However, there are a few memory cells whose retention time does not belong to "Main Distribution." This shorter retention time distribution is defined as "Tail Distribution." The refresh characteristics of DRAM are dominated by "Tail Distribution". Further, because leakage power is exponentially increased as temperature rises, which means more and more cells fail to retain charge and become a part of the "Tail distribution". To compensate this reduction in retention time, refresh period should be shorten to refresh more frequently. Yun et al has used the data reported in [6], [7] to fit the parameters and the resulting plot is shown in Figure 2. This figure shows how DRAM error rate is related to temperature and refresh period.

In 3DHP, high temperature exponentially increases the charge leakage in DRAM memory. High refresh rates can address this issue, but reduces the performance and increases power consumption [4] [7]. The temporal and spatial change in temperature,

known as hotspots further complicates the reliability issue in 3DHPs [8]. Error Correction Code (ECC) is used to address this issue in 3DIC. There are different ways the ECC can be employed depending on the number of errors detected and corrected. For example single error correction and double error detection [9] (SECDED) method can detect up to two errors but can only correct a single error.

Figure 2. DRAM error rate as a function of temperature and refresh period reported in [4]

For multi-bit burst error correction, strong BCH cyclic codes can be used to provide better error correction performance [10, 11]. However, the hardware complexity of ECC circuit exponentially increases as the number of error bits to correct increases. Therefore, a novel the ECC solution with a lower area-latency product is needed to address the bit error variability caused by hotspots in 3DHP.

### **3. ADPATIVE MULTI-PATH DECODER DESIGN**

A DRAM die consists of multiple memory cells, where each data bit is stored as a charge in the storage capacitor. The charging and discharging actions of the storage capacitor are directly related to temperature. Due to hotspots, leakage current increase which thusly discharges the charge stored by the capacitor and increases the probability of the memory errors [2].

To ensure thermal reliability and better performance of DRAM dies in 3DHP, a temperature-based adaptive ECC is proposed. Bose-Chaudhuri-Hocquenghem (BCH) codes are strong efficient error-correcting codes used to detect and correct enormous errors that have occurred in memory [11]. In 3DHP, hotspots show spatial/temporal localities as they are mainly caused by aggressive switching activities in CPU and GPU processor dies. To ensure thermal integrity among 3D-stacked dies, on-chip temperature sensors are placed to detect hotspots. When the proposed adaptive BCH decoder reads a word to decode, temperature measurement data from the distributed on-chip temperature sensor network is also read and used to calculate  $n_{EEB}$ , which is the estimated number of Error Bits for the incoming word. Then, the fastest decoding path which can be used to correct  $n_{EEB}$  number of error bits gets adaptively selected to decode the incoming codeword with the minimum decoding latency. The main advantage of the proposed adaptive multi-stage BCH decoder to single stage BCH decoder is the reduced decoding latency with area overhead.

For any integer  $m \ge 3$  and  $t < 2^{m-1}$ , there exists a binary t-error-correcting (n, k) BCH code, which satisfies the following conditions: (1)  $n = 2^{m-1}$ , (2)  $n - k \le mt$ , and (3)  $d_{min} \ge 2t + 1$ , where n is the total number of bits per codeword, k is the number

of information bits, n - k is the number of check bits, t is the maximum number of error bits corrected per codeword, and  $d_{min}$  is the minimum Hamming distance.

The proposed multi-path BCH decoder has multiple decoding paths with variable target t and decoding latency. As a concrete demonstration of the proposed multi-path BCH decoding approach, a 7-error correcting (511, 448) BCH decoder (i.e., m = 9) with p = 4 decoding paths with target t = 1, 3, 5 and 7 has been designed and verified in this work. ECC word size is normally chosen to match the size of the last level cache block, which is 64B for most current processors. Current ECC DRAMs come with  $1/8_{th}$  of the capacity for storing ECC check bits, thus a 64B memory block already has 64 bits reserved for ECC. Hence, the closest n and k values (i.e., n = 511 and k = 63) are chosen for the proposed design. Figure 3 shows a block diagram of the proposed adaptive multi-path BCH decoder with p = 4.

The proposed adaptive multi-path BCH decoder has three main advantages over the static BCH decoder designed for a fixed t (e.g., static BCH decoders for t = 1 for faster decoding and t = 7 for higher error correction coverage). First, it can reduce the overall decoding latency, when compared to a static BCH decoder with higher t (e.g., t = 7). Second, it can provide better error correction coverage, when compared to a static BCH decoder multiple words depending on n<sub>EEB</sub> for further reduction in decoding latency, as it has multiple independent decoding paths.

The proposed BCH decoder design consists of four decoding paths, each designed to correct a specified number errors. The temporal and spatial changes in the temperature are recorded by the distributed onchip temperature sensors, from which Bit Error Probability ( $p_{BE}$ ) is calculated.  $p_{BE}$  is used to determine  $n_{EEB}$ .

Figure 3. The proposed multi-path BCH Decoder. The estimated number of error bits for the incoming BCH codeword is calculated from the measurement data from onchip temperature sensors and is denoted as n<sub>EEB</sub> [12]

To ensure accuracy, there is a provision for calculating  $n_{EEB}$  depending on confidence level. The confidence level is interpreted as the likehood that a particular confidence interval contains the actual  $n_{EEB}$ . For the proposed  $n_{EEB}$  estimator, a one-sided upper-bounded confidence interval is appropriate since estimation error only happens when the actual number of erroneous bits is greater than  $n_{EEB}$ . The confidence interval can be selected to calculate  $n_{EEB}$  depending on the desired accuracy. This calculation is based on  $p_{BE}$ . There exists a trade-off between  $n_{EEB}$  and the confidence level. For the higher confidence level,  $n_{EEB}$  calculation is more precise, resulting in a higher number of expected error bits. As the number of error correcting bits increases the decoding latency increases slowing down the decoding.

The first decoding algorithm for binary BCH codes was devised by Peterson in 1960 [13]. Since then, the Petersons algorithm has been refined by Berlekamp [14], Massey [15], Chien [16], Forney [17], and many others. The BCH decoder follows the sequence of decoding steps which are Syndrome Calculator [18], Error Locator Polynomial [19] and Chien Search [19]. These algorithms are interrelated, i.e. the syndrome calculator calculates the syndrome according to the received data. Error locator polynomial is generated from syndrome value, and the error location is calculated using Chien search and the transmitter can be achieved.

### **3.1. SYNDROME BLOCK DESIGN FOR MULTI-PATH BCH DECODER**

BCH code can be implemented in hardware and software. There have been numerous efficient decoding algorithms reported in the literature. Two recent examples are [18, 20]. For a BCH code with  $n = 2^{m-1}$  and generator polynomial g(x), a code polynomial  $c(x) = c_0 + c_1x + c_2x^2 + \dots + c_{n-1}x^{n-1}$  is generated from the encoder and its binary representation is stored as a word in the DRAM. When this word is read from DRAM, a received polynomial (i.e., polynomial representation of the received word) is created as  $r(x) = r_0 + r_1x + r_2x^2 + \dots + r_{n-1}x^{n-1}$ . Note this received word is expected to contain  $n_{EEB}$  number of error bits and should be decoded for error correction, if  $1 \le n_{EEB} \le 7$ . In the BCH code, r(x) = c(x) + e(x), where  $e(x) = e_0 + e_1x + e_2x^2 + \dots + e_{n-1}x^{n-1}$  is the error polynomial.

The initial step in BCH decoder is the syndrome calculator. It provides information to later decoding stages for error detection and correction. The received codeword is error free when the syndrome outputs are zeros. Consider a t-error-correcting BCH code of length  $n = 2^{m-1}$  with generator polynomial g(x), where g(x) has  $\alpha, \alpha^2, ..., \alpha^{2t}$  roots, as  $g(\alpha^i) = 0$  for  $1 \le i \le 2t$ . To check whether r(x) is a code polynomial or not, one can simply test whether  $r(\alpha^i) = 0$  for  $1 \le i \le 2t$ . If yes, then r(x) is a code polynomial, otherwise r(x) is not a code polynomial and error correction decoding is needed.

Syndrome calculation in BCH decoding directly deals with the errors present. For the target t, 2t syndrome components are calculated for  $1 \le j \le 2t$ ,

$$S = \sum_{i=0}^{n-1} r_i \alpha^{ij} \tag{1}$$

where  $\alpha$  is the primitive element. The polynomials which are not factorable (i.e., divisible by one and itself) are called irreducible polynomials. The root of this polynomial is called primitive polynomial [21] and it generates all non-zero field elements. These non-zero fields are used in the generation of *GF* (2<sup>*m*</sup>) and  $\alpha$  is its primitive element. Thus, s<sub>i</sub> is

calculated as

$$s_j = (((((r_{n-1}\alpha^j + r_{n-2})\alpha^j + r_{n-3})\alpha^j \dots + r_1)\alpha^j + r_0))$$

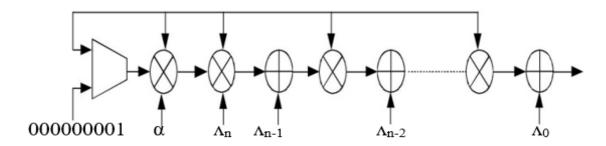

Figure 4 shows the procedure followed for syndrome calculation. From the n bit received data the (n - 1) bit is first multiplied by the primitive element  $\alpha^{j}$  then the resultant is XORed with the (n - 2) bit. The obtained result is again multiplied with  $\alpha^{j}$  and the resultant is XORed with (n - 3) bit. This process is continued untill bit position 0 and the final result is s<sub>j</sub>. The calculation of odd syndrome components from even syndrome components leads to area efficient hardware design with reduced latency [18], as the relation between them is

$$s_{2t} = s_t^2 \tag{2}$$

For the proposed adaptive BCH decoder with 4 decoding paths (i.e., BCH1, BCH2, BCH3 and BCH4), four individual syndrome sets are needed to be calculated. Then, from

Equation 2,  $s_2$  is easily calculated from  $s_1$ by squaring it (i.e.  $s_1^2$ ). Similarly, for BCH2 is designed to correct up to t = 3 error bits, j ranging from one to six (i.e., 2t = 6). So, the numbers of syndrome components calculated are six (i.e.  $s_1$  to  $s_6$ ). BCH3 can correct up to five error bits, so j varies from one to ten. Hence the syndrome calculations are done from  $s_1$  to  $s_{10}$ . For BCH4 the calculated syndromes are from  $s_1$  to  $s_{14}$ , since the j ranges from one to fourteen. In all cases, odd syndrome components are first calculated. Then, even components are found by squaring them and the transmitter can be achieved.

Figure 4. Syndrome block diagram [22]

### **3.2. ERROR LOCATOR POLYNOMIAL CALCULATOR DESIGN**

The secondary stage of the BCH decoder is to determine the error locator polynomial. The syndrome calculator outputs are used to generate this polynomial [18]. The relation the between syndrome calculator and error locator is expressed as:

$$\sum_{j=0}^{t} s_{t+i-j} \Lambda_j = 0 \tag{3}$$

where s is the syndrome and Ais the error locator coefficient. Then, the error locator polynomial can be expressed as  $\Lambda(x) = \Lambda_0 + \Lambda_1 x + \Lambda_2 x^2 + \dots + \Lambda_t x^t$ [19]. To deduce the error locator polynomial Peterson, Berlekamp and Euclidean are the most prominently used decoding algorithms in hardware the BCH decoder [23]. The Peterson algorithm is known to be the best choice, when the error correcting capability is less than or equal to three, since its computation is simple and less costly, especially in hardware [24]. Euclidean algorithm is advantageous in terms of speed and can be used in design where speed is the major objective [19]. Berlekamp algorithm has less hardware complexity in calculating the error locator polynomial and is used in the design where area is a limiting factor [24]. In designing BCH1 and BCH2 the Peterson error locator computation algorithm [19] has been used, since the number of errors to be corrected (i.e., target t) for these designs are less than or equal to three. As the Peterson error locator polynomial computation is complex for more than three errors Simplified Truncated Inverse Berlekamp Massey algorithm (SiBM) [25] is used for designing BCH3 and BCH4 as it provides better speed with less area overhead for determine error location polynomial coefficient.

According to the Peterson algorithm [19],  $\Lambda(x)$  is computed directly and the degree of  $\Lambda(x)$  is equal to the number of error bits occurred. For t = 3 as an example,  $\Lambda$  (i.e., coefficients of the error locator polynomial) is represented as follows:

$$\begin{bmatrix} 1 & 0 & 0 \\ s_2 & s_1 & 1 \\ s_4 & s_3 & s_2 \end{bmatrix} * \begin{bmatrix} \Lambda_1 \\ \Lambda_2 \\ \Lambda_3 \end{bmatrix} = \begin{bmatrix} s_1 \\ s_2 \\ s_3 \end{bmatrix}$$

(4)

For BCH1,  $\Lambda_0 = 1$  and  $\Lambda_1 = s_1$ . For BCH2, deleting the two rightmost columns and two bottom rows of matrix leads to a singular matrix, and solving the corresponding equation yields:  $\Lambda 0 = 1$ ,  $\Lambda 1 = s_1$ ,  $\Lambda_2 = (s_2s_3 + s_5)/(s_1^3 + s_3)$ , and  $\Lambda_3 = (s_1^3 + s_3) + (s_1\Lambda_2)$  [26]. The proposed decoding paths BCH3 and BCH4 have t = 5 and t = 7, respectively. Therefore, Peterson algorithm is inappropriate due to its poor hardware scalability. Therefore, the Simplified truncated inverse Berlekamp Massey algorithm (SiBM) has been used to find the coefficients of the error polynomial. SiBM [25] is known to provide higher decoding speed with less area overhead to determine the error locator polynomial coefficients. Its efficiency comes from two factors including: 1) for binary BCH codes, the Berlekamp-Massey algorithms' odd iterations can be skipped, and 2) since the error value is always binary, one error evaluator polynomial is not required. SIBM consists of an error locator polynomial and discrepancy polynomial block. Appending the error locator polynomial to the discrepancy polynomial will result in the disappearance of the error evaluator polynomial after the iteration is completed.

The SiBM processing element (PE) is capable of updating the coefficients of both error locator polynomial and discrepancy polynomial simultaneously. The odd coefficient of the extended polynomial is not capable to interact with the even coefficients. Therefore, PEs is placed as nearly two independent layers. The upper layer affects the lower layer through dependency, while the lower layer has no effect on the upper layer. The lower layer variables have little effect on the final error locator polynomial and can be simply shifted out. This further reduces the computational time and optimize SiBM algorithm.

### **3.3. CHIEN SEARCH BLOCK DESIGN**

The final step of BCH decoder is to find the error location(s) through the Chien search method. Error location is obtained by finding the roots of the error locator polynomial [19]. The roots are searched as follows:

- 1. For each power of  $\alpha$  (i.e., primitive element) for i = 0 to n 1,  $\alpha^{i}$  is taken as the test root

- 2. Calculate the polynomial coefficients of the current root using coefficients of the past iteration using  $\alpha^{j} = \alpha^{j-1} \cdot \alpha^{1}$  during the j<sub>th</sub> iteration.

- 3. Calculate the sum of the polynomial coefficients.

- 4. When the sum is zero, an error bit is present at that location.

The factorization method [27] is used to reduce the complexity of the conventional method. It allows designing another form of the circuit of the Chien search that minimizes a large number of the used logic gates in the circuit. This block finds the error location depending on the error locator polynomial. Figure 5 shows a Chien search block diagram for t = 5 case as an example. In this figure, one is multiplied with  $\alpha^t$  and then the resultant is multiplied with the  $\Lambda_t$ . The obtained result is XORed with  $\Lambda_{t-1}$ , again this resultant is multiplied  $\alpha^t$ , and then XORed with  $\Lambda_{t-2}$  and the process repeats until  $\Lambda_0$ . The above said process iterates until  $\alpha^0$ . In this way, the roots of the error location determine the error location.

Figure 5. Chien Search block diagram for t = 5 case [19]

### 3.4. PARALLEL ADAPTIVE BCH DECODING FOR REDUCED DECODING

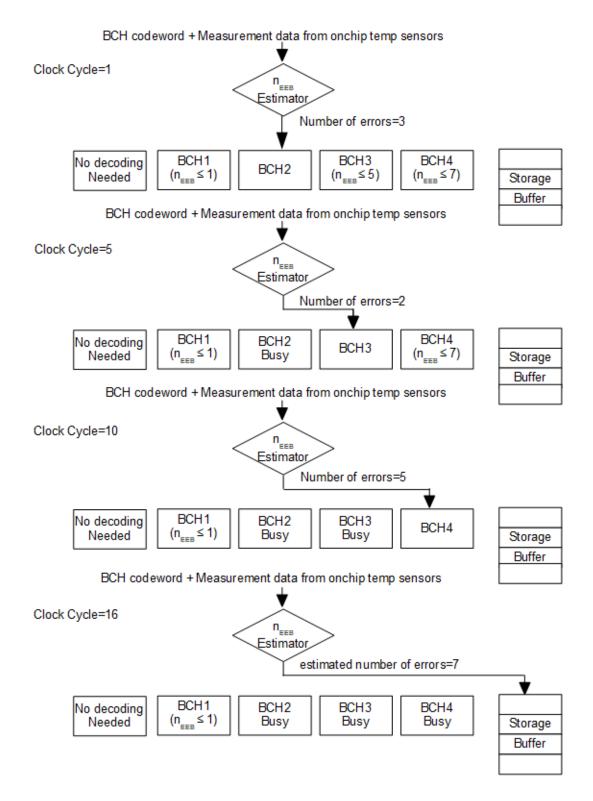

In addition to the serial decoding (i.e., decoding one codeword at a time), the proposed adaptive multi-stage BCH decoder can be utilized to correct multiple words in parallel provided incoming codewords have different  $n_{EEB}$ . Even though one or more decoding paths are occupied, if there is an unoccupied path with minimum  $t \ge n_{EEB}$  of the incoming codeword, that path can start decoding it in parallel for further reduction in decoding latency. If there is no idle decoding path that can be used to decode the incoming codeword, it is temporarily stored in the storage buffer until an appropriate vacant decoding path becomes available.

Figure 6 illustrates an example of the proposed parallel decoding process. As seen in the first clock cycle ( $\varphi = 1$ ), the n<sub>EEB</sub> of the incoming codeword is 3 and the decoding path with the minimum  $t \ge n_{EEB}$  is BCH2 (i.e., t = 3). So, BCH2's availability is checked and it is currently idle. Therefore, the word is given to BCH2 to be decoded. In  $\varphi = 5$ , another word is read from the memory, which is estimated to contain two error bits. It is given to BCH3 to be decoded, because BCH2 is currently decoding the first word and the next higher error correcting decoder path available is BCH3. Similarly, the next incoming codeword is estimated to have five error bits and is read from the memory in  $\varphi = 10$ .

This codeword is read from the memory in  $\varphi = 10$ . This codeword is given to BCH4, since BCH3 is busy decoding the second word. As seen from the figure for  $\varphi = 16$  when the codeword with  $n_{EEB} = 7$  is coming for decoding, it is stored in the storage buffer instead, since BCH4 is currently busy decoding another word. When the respective decoder becomes available the word stored in storage buffer is fetched to be decoded.

Figure 6. An example of the proposed parallel decoding

### 4. PERFORMANCE EVALUATION

To quantitatively demonstrate and verify the decoding performance of the proposed adaptive multi-path BCH decoder approach, the presented 7-error-correcting (511, 448) adaptive BCH decoder (i.e., m = 9) with p = 4 decoding paths with target t = 1, 3, 5 and 7 has been designed in Verilog HDL (Hardware Description Language) and verified. Simulation and synthesis have been carried out using Xilinx ISE tool on a Virtex5 FPGA (target device: XC5VLX30). Resource utilization and decoding latency results of the FPGA prototype are summarized in Table 1.

In FPGA, reconfigurable resources are grouped into slices which contain a set of LUTs (Look-Up Tables), flip-flops and multiplexers. These LUTs represent a group of logic gates that are hard-wired on the FPGA and stores the output depending on the input. Thus, these LUTs provide the fastest way to retrieve the output when needed. A flip-flop circuit is used for change of state and stores a single bit of data. A slice register is the group of flip-flops used to store a data word. A register has a clock, enable pin, input and output data ports. For every clock cycle depending on the input, the output is updated and stored. It should be noticed that as the error correcting capability of the decoder increases the hardware resources utilized also increases leading to a large area overhead. As in this Table 1, hardware implementations of different BCH decoder paths show poor scalability as t increased.

Therefore, a decoding path with minimum  $t \ge n_{EEB}$  should be used to decode. This would adaptively minimize the overall decoding time. The area overhead of the proposed adaptive 4-path BCH decoder compared to the static BCH decoder designed to tolerate

maximum t = 7 is calculated using the number of occupied slices used in both designs. The static decoder which has only one decoding path of BCH4 utilizes 1, 776 FPGA slices and the proposed adaptive 4-path BCH decoder design utilizes 2, 628 slices. Therefore, the area overhead of the proposed adaptive 4-path BCH decoder is *only* 47.97%, even though it has 4 physically separate decoding paths. This area overhead is relatively small, since decoding paths with smaller t (i.e., BCH1, BCH2 and BCH3) have considerably lower hardware complexities and require only 852 (i.e., 47.97% of BCH4's 1,776) additional slices to be realized.

|                      | BCH1<br>(t = 1) | BCH2<br>(t = 3) | BCH3<br>(t = 5) | BCH4<br>(t = 7) |

|----------------------|-----------------|-----------------|-----------------|-----------------|

| # of Slice Registers | 49              | 93              | 220             | 444             |

| # of Slices LUT      | 107             | 586             | 1817            | 2536            |

| # of LUT FF used     | 44              | 98              | 203             | 397             |

| # of Occupied Slices | 44              | 220             | 558             | 1776            |

| Decoding Latency     | 7.21 ns         | 12.73 ns        | 28.59s          | 39.33s          |

Table 1. FPGA resource utilization and decoding latency of four decoding paths in the proposed adaptive multi-path BCH decoder

# 4.1. SERIAL DECODING PERFORMANCE EVALUTION

In this section, serial decoding performance of the prototype adaptive errorcorrecting (511, 448) BCH decoder (i.e., m = 9) with p = 4 decoding paths with target t =1, 3, 5 and 7 (adaptive 4-path BCH decoder, in short) will be evaluated. In the proposed adaptive multi-path BCH decoding approach, distributed onchip temperature sensors in 3DHP provide temerature measurement data for DRAM die to the  $n_{EEB}$  estimator as shown in Figure 3. Then, the  $n_{EEB}$  estimator calculates the  $p_{BE}$  of the codeword that is being read from DRAM with a certain user-provided confidence level as previously discussed in Section 3.

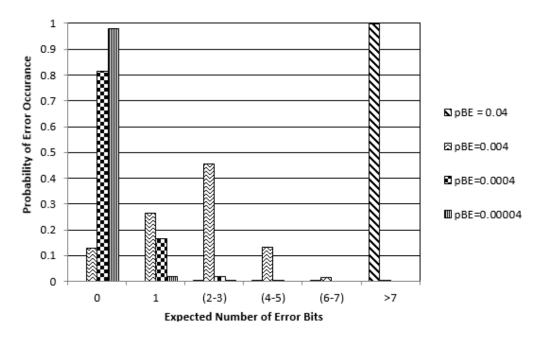

For variable  $p_{BE}$ , the probability of having k number of error bits occurred in n-bit BCH codeword can be calculated using binomial equation,  $p(k) = n_k k_{BE} (1 - p_{BE})^{nk}$ . For the prototype adaptive 4-path BCH decoder, the distribution of six different error probabilities can be calculated as follows:

1) P(0), where no decoding is necessary, since  $n_{EEB}=0$ ;

2) P(1), where BCH1 decoding path is used to correct single bit error;

3)  $P(2 \land 3)$ , where BCH2 decoding path is used to correct 2 to 3 error bits;

4) P (4  $\wedge$  5), where BCH3 decoding path is used to correct 4 to 5 error bits;

5) P ( $6 \land 7$ ), where BCH4 decoding path is used to correct 6 to 7 error bits.

6)  $P(>7) = 1 - P_{i=1} P(i)$ , which means uncorrectable.

Figure 7 depicts the distribution of error probabilities for various  $p_{BE}$  values, which are arbitrarily chosen as 0.04, 0.004, 0.0004 and 0.0004. This graph illustrates implications of  $p_{BE}$  on the utilization of 4 decoding paths. For example, when  $p_{BE} = 0.04$ , the probability of codeword having more than seven error bits per codeword is dominant; thereby, almost all codewords are uncorrectable. On the other hand,  $p_{BE} = 0.00004$  yields codewords with no error bits (i.e., codewords with no decoding is necessary) almost 98% of the time. Therefore, no useful error correction decoding happens in both of these extreme cases and the utilization of decoding paths is extremely low. The  $p_{BE} = 0.0004$  case gives higher utilization of 4 decoding paths as P (0)  $\approx 13\%$  (i.e., no error - no decoding needed) and P  $(>7) \approx 0\%$  (i.e., almost no uncorrectable codewords). In this case, BCH2 with t = 3 shows the highest utilization of 45% among 4 decoding paths.

**4.1.1.** Average Decoding Latency for Various Bit Error Probabilities. Table 2 shows the average decoding latency of the proposed adaptive 4-path BCH decoder for variable  $p_{BE}$ . From Figure 7, for  $p_{BE} = 0.04$  case, the excepted number of error bits is mostly more than seven. Therefore, codewords containing more than seven errors are not correctable by the proposed design. Hence, its average decoding latency is near zero as almost no decoding occurs. The other extreme case of  $p_{BE} = 0.00004$  is similar, as the decoding paths are under-utilized as the most of codewords are error-free requiring no decoding. Notably, the other two intermediate cases (i.e.,  $p_{BE} = 0.004$  and 0.0004) can be used to represent the error distribution of 3DHP with hotspot induced  $p_{BE}$  variation. The  $p_{BE} = 0.004$  case has an order of magnitude higher  $p_{BE}$  when compared with  $p_{BE} = 0.0004$  case, so it can be used an exemplary  $p_{BE}$  for hotspots in 3DHP. Also, the other has 10 times lower  $p_{BE}$ , so it can be used an exemplary  $p_{BE}$  for the other area not affected by the hotspots.

Table 2. Average decoding latency (ADL) for different  $p_{BE}$  values. For  $p_{BE} = 0.04$ , P (>7)  $\approx 100\%$ , which means almost all codewords are uncorrectable and not decoded. For the other extreme,  $p_{BE} = 0.00004$ , 98% of codewords are error-free and do not need decoding

| рве       | 0.04              | 0.004                 | 0.0004           | 0.00004        |

|-----------|-------------------|-----------------------|------------------|----------------|

| nEEB      | Highest           | Mid-high              | Mid-low          | Lowest         |

| max P (t) | P (> 7)<br>≈ 100% | $P(2 \land 3) = 46\%$ | P (0)<br>= 81.5% | P (0)<br>= 98% |

| ADL       | pprox 0           | 11.50 ns              | 1.44 ns          | 0.15 ns        |

Figure 7. Distribution of error probabilities for variable pBE values

| рве     | P (0)   | <b>P</b> (1) | P (2 ∧ 3) | P (4 ∧ 5) | P (6 A 7) | <b>P</b> (> 7) |

|---------|---------|--------------|-----------|-----------|-----------|----------------|

| 0.04    | 8.7e-10 | 1.9e-08      | 1.6e-06   | 4.01e-05  | 0.00047   | 1              |

| 0.004   | 0.1289  | 0.3936       | 0.84945   | 0.9820    | 0.99878   | 1              |

| 0.0004  | 0.8151  | 0.9817       | 0.999938  | 0.99999   | 0.99999   | 1              |

| 0.00004 | 0.9797  | 0.9997       | 0.999997  | 0.999998  | 0.99999   | 1              |

Table 3. Cumulative error coverage for various  $p_{BE}$  values

As clearly shown in Figure 7, the average decoding latency for codewords read from the area not affected by hotspots (i.e.,  $p_{BE} = 0.0004$ ) is 1.14 ns, which is considerably lower than 11.50 ns decoding latency of the hotspot-affected codewords. Notably, even this slowest 11.50 ns decoding latency is significantly lower than the worst-case (i.e., t = 7) static BCH decoding latency of 39.33 ns reported in Table 1.

**4.1.2. Cumulative Error Coverage.** The proposed adaptive 4-path BCH decoder can correct up to 7 error bits per word. Table 3 shows the cumulative error coverage for variable  $p_{BE}$ . As per the results shown in the table maximum error coverage is found near more than seven errors for high  $p_{BE}$  value. As the  $p_{BE}$  value decreases error coverage is maximum for small number of errors.

There is tradeoff between error coverage and latency. The staged BCH decoder for any input irrespective of varying  $p_{BE}$  offer maximum error coverage with maximum latency overhead. Whereas the adaptive multi-stage BCH decoder relies on  $p_{BE}$  and offers required error coverage with the reduced latency. Therefore the proposed model can provide efficient error coverage with less delay for varying temporal and spatial changes.

# 4.2. PARALLEL DECODING PERFORMANCE

As discussed in Section 3.4, multiple independent decoding paths given in the proposed adaptive multi-path BCH decoder can be utilized to decode multiple codewords from DRAM in parallel. The performance of the proposed parallel decoding technique will be extensively evaluated using the adaptive 4-path BCH decoder design as an example in this section. A cycle-accurate simulator has been implemented in Matlab to generate simulation results for the proposed parallel decoding technique. Bit error variations caused by hotspots are simulated by introducing the following user-provided simulation parameters:

- 1. p<sub>BEH</sub> : the increased bit error probability due to hotspots.

- 2. p<sub>BEC</sub> : the baseline bit error probability unaffected by hotspots.

- 3. fhot: the relative frequency of codewords subject to pBEH.

4.  $f_{cold}$ : the relative frequency of codewords subject to  $p_{BEC}$ , where  $f_{hot} + f_{cold} = 100\%$ . size<sub>buf</sub>: the storage buffer size

Accordingly, each respective decoder's status is checked for its availability. If the decoder is not available then the next available higher error correcting decoder (i.e., the decoder which can correct more number of errors when compared to the required no of error correction) is selected for decoding. When there is no available decoder with  $t \ge m_{EEB}$ , then the respective word is stored in the storage buffer. If the storage buffer is completely occupied then the word is not read from the memory. Table 4 shows the average decoding latency for various  $p_{BEH} / p_{BEC}$ ,  $f_{hot}/f_{cold}$  and  $size_{buf}$  values chosen arbitrarily. It can be noticed that decoding latencies differ with  $size_{buf}$  and  $f_{hot}/f_{cold}$  ratio. Decoding latency increases with the increases in the number of words read from hotspot region.

| pBE <sub>H</sub> /pBE <sub>C</sub> | size <sub>BUF</sub> | fhot/fcold | fhot/fcold | f <sub>HOT</sub> /f <sub>COLD</sub> |

|------------------------------------|---------------------|------------|------------|-------------------------------------|

|                                    |                     | 40/60      | 60/40      | 80/20                               |

| 0.003/0.002                        | 4                   | 15.7 ns    | 15.8 ns    | 16.8 ns                             |

|                                    | 8                   | 15.6 ns    | 15.69 ns   | 16.4 ns                             |

|                                    | 16                  | 15.8 ns    | 15.8 ns    | 16.2 ns                             |

| 0.009/0.002                        | 4                   | 17.1 ns    | 20 ns      | 23.3 ns                             |

|                                    | 8                   | 16.8 ns    | 19.7 ns    | 23.1 ns                             |

|                                    | 16                  | 16.6 ns    | 19.63 ns   | 22.8 ns                             |

| 0.011/0.005                        | 4                   | 23.2 ns    | 26.9 ns    | 30.2 ns                             |

|                                    | 8                   | 22.9 ns    | 26.7 ns    | 29.8 ns                             |

|                                    | 16                  | 22.5 ns    | 26.5 ns    | 29.6 ns                             |

Table 4. Parallel decoding simulation results showing the average decoding latency by varying  $pBE_{\rm H}$  ' $pBE_{\rm C}$ ,  $f_{hot}$ ' $f_{cold}$  and  $size_{buf}$

The obtained results also indicate that the average decoding latency for the proposed adaptive multi-path BCH decoder leveraging the parallel decoding technique has less decoding latency when compared to the static BCH decoder with fixed t = 7, which has a constant 39.33 ns decoding latency. Thus, it can be concluded that the proposed adaptive 4-path BCH decoder can achieve significantly lower decoding latency ranging from 15.7 ns to 29.6 ns for  $p_{BEH}/p_{BEC}$ ,  $f_{hot}/f_{cold}$  and size<sub>buf</sub> values chosen with are a overhead of 47.97%.

### 5. CONCLUSION

In this paper, a novel adaptive multi-path BCH decoder design approach is proposed and validated to address the bit error variation issue caused by hotspots in 3DHP. The proposed design has multiple decoding paths with variable decoding latency and area trade-off. For each word read from DRAM, thermal gradient data from the on-chip temperature sensors is utilized to estimate the expected number of error bits. Then, the fastest possible decoding path which is able to correct the expected number of error bits is adaptively selected to reduce the overall decoding time. Also, a parallel decoding approach leveraging the multiple independent decoding paths of the proposed decoder design is also proposed and validated in this work. To clearly evaluate the latency reduction performance and area overhead of the proposed approach, an adaptive 4-path BCH decoder has been implemented in FPGA hardware. Then, its serial and parallel decoding performances along with area overhead have been extensively evaluated. The proposed adaptive 4-path BCH decoder can achieve significantly reduced average decoding latency ranging from 15.7 ns to 29.6 ns for variable  $p_{BEH}/p_{BEC}$ ,  $f_{hot}/f_{cold}$  and  $size_{buf}$  value sets chosen with area overhead of 47.97%.

### **BIBLOGRAPHY**

- S. Naffziger, "Technology impacts from the new wave of archi-tectures for mediarich workloads," in VLSI Technology (VLSIT), 2011 Symposium on, 2011, pp. 6– 10.

- [2] W. Liao, F. Li, and L. He, "Microarchitecture level power and thermal simulation considering temperature dependent leakage model," in Low Power Electronics and Design, 2003. ISLPED '03. Proceedings of the 2003 International Symposium on, 2003, pp. 211–216.

- [3] J.-H. Ahn, B.-H. Jeong, S.-H. Kim, S.-H. Chu, S.-K. Cho, H.-J. Lee, M.-H. Kim, S.-I. Park, S.-W. Shin, J.-H. Lee et al., "Adaptive self-refresh scheme for battery operated high-density mobile DRAM applications," in Solid-State Circuits Conference, 2006. ASSCC 2006. IEEE Asian. IEEE, 2006, pp. 319–322.

- [4] W. Yun, K. Kang, and C.-M. Kyung, "Thermal-aware energy minimization of 3Dstacked L3 cache with error rate limitation," in Circuits and Systems (ISCAS), 2011 IEEE International Sym-posium on, 2011, pp. 1672–1675.

- [5] T. Hamamoto, S. Sugiura, and S. Sawada, "On the retention time distribution of dynamic random access memory (DRAM)," Electron Devices, IEEE Transactions on, vol. 45, no. 6, pp. 1300–1309, 1998.

- [6] M. Cho, Y. Kim, D. Woo, S. Kim, M. Shim, Y. Park, W. Lee, and B.-I. Ryu, "Analysis of Thermal Variation of DRAM Retention Time," in Reliability Physics Symposium Proceedings, 2006. 44th Annual, IEEE International. IEEE, 2006, pp. 433–436.

- [7] M. Hashimoto and R. Baumann, "Investigation of cell leakage and data retention in eDRAM," in Solid-State Circuits Conference, 2000. ESSCIRC'00Proceedings of the 26rd European, 2000, pp. 356–359.

- [8] M. Guan and L. Wang, "Temperature aware refresh for DRAM performance improvement in 3D ICs," in Quality Electronic Design (ISQED), 2015 16th International Symposium on, 2015, pp. 207–211.

- [9] M. Richter, K. Oberlaender, and M. Goessel, "New Linear SEC-DED Codes with Reduced Triple Bit Error Miscorrection Probability," in On-Line Testing Symposium, 2008. IOLTS'08. 14th IEEE International, 2008, pp. 37–42.

- [10] P.-Y. Chen, C.-L. Su, C.-H. Chen, and C.-W. Wu, "Generalization of an Enhanced ECC Methodology for Low Power PSRAM," IEEE Trans. Comput., vol. 62, no. 7, pp. 1318–1331, 2013.

- Z. Chishti, A. Alameldeen, C. Wilkerson, W. Wu, and S.-L. Lu, "Improving cache lifetime reliability at ultra-low voltages," in Microarchitecture, 2009. MICRO-42. 42nd Annual IEEE/ACM International Symposium on, 2009, pp. 89–99.

- [12] K. K. Prashanthi Metku, Ramu Seva and M. Choi, "Multi-Stage BCH Decoder to Mitigate Hotspot-Induced Bit Error Variation," in 2015 International SoC Design Conference, pp. 89–90.

- [13] W. Peterson, "Encoding and error-correction procedures for the Bose-Chaudhuri codes," IRE Transactions on Information Theory, vol. 6, no. 4, pp. 459–470, 1960.

- [14] E. Berlekamp, "On decoding binary Bose-Chadhuri Hocquenghem codes," IEEE Trans. Inf. Theory, vol. 11, no. 4, pp. 577–579, 1965.

- [15] J. Massey, "Step-by-step decoding of the Bose-Chaudhuri- Hocquenghemcodes," IEEE Trans. Inf. Theory, vol. 11, no. 4, pp.580–585, 1965.

- [16] R. Chien, "Cyclic decoding procedures for Bose- Chaudhuri-Hocquenghem codes," IEEE Trans. Inf. Theory, vol. 10, no. 4, pp. 357–363, 1964.

- [17] G. Forney, "On decoding BCH codes," IEEE Trans. Inf. Theory, vol. 11, no. 4, pp. 549–557, 1965.

- [18] H. Kristian, H. Wahyono, K. Rizki, and T. Adiono, "Ultrafast scalable BCH decoder with efficient-Extended Fast Chien Search," in Computer Science and Information Technology (ICCSIT), 2010 3rd IEEE International Conference on, vol. 4, 2010, pp. 338–343.

- [19] X. Zhang and Z. Wang, "A Low-Complexity Three-Error Correcting BCH Decoder for Optical Transport Network," IEEE Trans. Circuits Syst. II, vol. 59, no. 10, pp. 663–667, 2012.

- [20] Y.-M. Lin, H.-C. Chang, and C.-Y. Lee, "Improved High Code Rate Soft BCH Decoder Architectures With One Extra Error Compensation," IEEE Trans. VLSI Syst., vol. 21, no. 11, pp. 2160–2164, 2013.

- [21] Lempel, "Analysis and synthesis of polynomials and sequences over," IEEE Trans. Inf. Theory, vol. 17, no. 3, pp. 297–03, 1971.

- [22] N. Ahmadi, M. Sirojuddiin, A. Nandaviri, and T. Adiono, "An optimal architecture of BCH decoder," in Application of Information and Communication Technologies (AICT), 2010 4th International Conference on, 2010, pp. 1–5.

- [23] Y. Liu, "Channel Coding," Henan Science and Technology Press, 1992.

- [24] X. Qi, X. Ma, D. Li, and Y. Zhao, "Implementation of accelerated BCH decoders on GPU," in Wireless Communications & Signal Processing (WCSP), 2013 International Conference on, 2013, pp. 1–6.

- [25] M. Yin, M. Xie, and B. Yi, "Optimized algorithms for binary BCH codes," in Circuits and Systems (ISCAS), 2013 IEEE International Symposium on, 2013, pp. 1552– 1555.

- [26] X. Zhi-yuan, L. Na, and L. Le-le, "New decoder for triple error correcting binary BCH codes," in Industrial Electronics and Applications, 2008. ICIEA 2008. 3rd IEEE Conference on, 2008, pp. 1426–1429.

- [27] E.-H. El Idrissi Anas, E. Rachid, and H. Lamari, "A low power error detection in the Chien Search Block for Reed Solomon code," in Complex Systems (ICCS), 2012 International Conference on, 2012, pp. 1–3.

# II. NOVEL AREA-EFFICIENT NULL CONVENTION LOGIC ON CMOS AND GATE DIFFUSION INPUT (GDI) HYBRID METHODOLOGY

## ABSTRACT

A Null convention logic (NCL) is a promising delay insensitive paradigm for constructing asynchronous circuits. Traditionally, NCL circuits are implemented utilizing complementary metal oxide semiconductor (CMOS) technology that has large area overhead. To address this issue, a HYBRID methodology is introduced for realizing NCL circuits in this paper. The proposed approach utilizes both CMOS and gate diffusion input (GDI) techniques to significantly reduce the area. Compared with the conventional static CMOS NCL counterpart, the HYBRID implementation of an NCL up counter demonstrate an average of 10% reduction in the transistor count.

## **1. INTRODUCTION**

The clocked synchronous paradigm currently dominates the semiconductor design industry [1]. However, there are major drawbacks of this synchronous approach, including critical timing analysis and clock skew issues [2]. Typically, a precise clock distribution network is used to address these limitations, which is a tedious and complex task. Moreover, with the decreasing feature size, power consumption of clock distribution network is found to be rapidly increasing, which is a major limiting factor for emerging low power semiconductor industry [3]. Since asynchronous designs consumes less power, produce less noise and electromagnetic interference (EMI) than their synchronous counterparts, there is renewed interest in this field [4].

Asynchronous circuits are characterized into two classifications: bounded-delay and delay-insensitive (DI) models [3]. Bounded-delay models consider that the both gate and wire delays are bounded and therefore, require extensive timing analysis to determine the delay [1]. On the other hand, DI circuits assume both interconnects and logic elements delay are unbounded and wire forks within the components are isochronic [5]. However, wires connecting the components do not adhere to this isochronic fork assumption, ensuring the correct operation regardless on the input availability. Hence, DI circuits require little timing analysis and yield average case performance rather than the worstcase performance of bounded-delay and traditional synchronous paradigms [6].