Imperial College of Science, Technology and Medicine Department of Electrical and Electronic Engineering

# Acceleration of ListNet for Ranking Using Reconfigurable Architecture

Qiang Li

Supervised by Dr David B. Thomas and Prof Peter Y.K. Cheung

Submitted in part fulfilment of the requirements for the degree of Doctor of Philosophy in Electrical and Electronic Engineering of Imperial College London and the Diploma of Imperial College, October 2019

#### Abstract

Document ranking is used to order query results by relevance with ranking models. ListNet is a well-known ranking approach for constructing and training learning-to-rank models. Compared with traditional learning approaches, ListNet delivers better accuracy, but is computationally too expensive to learn models with large data sets due to the large number of permutations and documents involved in computing the gradients. Currently, the long training time limits the practicality of ListNet in ranking applications such as breaking news search and stock prediction, and this situation is getting worse with the increase in data-set size. In order to tackle the challenge of long training time, this thesis optimises the ListNet algorithm, and designs hardware accelerators for learning the ListNet algorithm using Field Programmable Gate Arrays (FPGAs), making the algorithm more practical for real-world application.

The contributions of this thesis include: 1) A novel computation method of the ListNet algorithm for ranking. The proposed computation method exposes more fine-grained parallelism for FPGA implementation. 2) A weighted sampling method that takes into account the ranking positions, along with an effective quantisation method based on FPGA devices. The proposed design achieves a 4.42x improvement over GPU implementation speed, while still guaranteeing the accuracy. 3) A full reconfigurable architecture for the ListNet training using multiple bitstream kernels. The proposed method achieves a higher model accuracy than pure fixed point training, and a better throughput than pure floating point training. This thesis has resulted in the acceleration of the ListNet algorithm for ranking using FPGAs by applying the above techniques. Significant improvements in speed have been achieved in this work against CPU and GPU implementations.

#### Acknowledgements

I would like to thank my supervisor, Prof. Peter Cheung, without whom this thesis would not have been possible. He actively encouraged me to explore my own research interests. He also advised me to improve on my English language skills and helped me build my self-confidence. In addition, he provided funding for my research. I truly appreciate his support.

Thank you to my co-supervisor, Dr. David Thomas, for his guidance during our weekly meetings. Through our fruitful discussions, I gained a deeper understanding on how to conduct research. It is a skill I will treasure forever.

I would also like to thank Shane Fleming, who helped me immensely in my research and publications. To Erwei Wang, He Li, Ben Chua, and Jianyi Cheng, it has been an enjoyable journey together. To the rest of the CAS group, thank you for the fun and laughter.

Most importantly, I also thank my family for their continuous support in my life - my parents, who spent their precious time and energy to nurture me, and my siblings, who have been there for me through my ups and downs. I love you three thousand times.

## Declarations

#### **Declaration of Originality**

I herewith certify that the work presented in this thesis is my own. All other related work are appropriately referenced.

#### **Declaration of Copyright**

The copyright of this thesis rests with the author. Unless otherwise indicated, its contents are licensed under a Creative Commons Attribution-Non Commercial 4.0 International Licence (CC BY-NC).

Under this licence, you may copy and redistribute the material in any medium or format. You may also create and distribute modified versions of the work. This is on the condition that: you credit the author and do not use it, or any derivative works, for a commercial purpose.

When reusing or sharing this work, ensure you make the licence terms clear to others by naming the licence and linking to the licence text. Where a work has been adapted, you should indicate that the work has been changed and describe those changes.

Please seek permission from the copyright holder for uses of this work that are not included in this licence or permitted under UK Copyright Law.

# Contents

| A        | bstra | nct                              | i   |

|----------|-------|----------------------------------|-----|

| A        | cknov | wledgements                      | iii |

| 1        | Intr  | roduction                        | 1   |

|          | 1.1   | Motivation                       | 1   |

|          | 1.2   | Challenges                       | 3   |

|          | 1.3   | Contributions                    | 5   |

|          | 1.4   | Thesis Outline                   | 7   |

|          | 1.5   | Publications                     | 8   |

| <b>2</b> | Bac   | kground                          | 9   |

|          | 2.1   | Introduction of Learning to Rank | 9   |

|          | 2.2   | Major Ranking Approaches         | 13  |

|          |       | 2.2.1 The Pointwise Approach     | 13  |

|          |       | 2.2.2 The Pairwise Approach      | 15  |

|          |       | 2.2.3 The Listwise Approach      | 16  |

|   |     | 2.2.4 Ranking Approach Overview                            | 18 |

|---|-----|------------------------------------------------------------|----|

|   | 2.3 | Evaluation Measures                                        | 19 |

|   | 2.4 | Review of Top- $k$ ListNet                                 | 21 |

|   | 2.5 | Related Work                                               | 26 |

|   |     | 2.5.1 Algorithm Optimisation                               | 26 |

|   |     | 2.5.2 Hardware Acceleration                                | 28 |

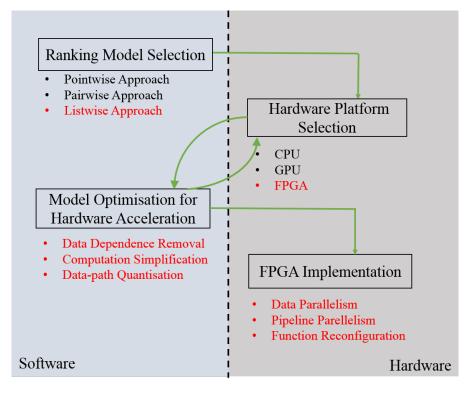

|   | 2.6 | Design Flow of Hardware-Based Accelerator                  | 32 |

|   | 2.7 | Summary                                                    | 33 |

| 3 | Acc | elerating Top- $k$ ListNet Training for Ranking Using FPGA | 34 |

|   | 3.1 | Introduction                                               | 34 |

|   | 3.2 | Analysis of Top-k ListNet                                  | 36 |

|   |     | 3.2.1 Challenge of Top- $k$ ListNet                        | 36 |

|   |     | 3.2.2 Redesign of Top- $k$ ListNet Computation             | 37 |

|   |     | 3.2.3 Benefit of Precomputation for Top- $k$ ListNet       | 40 |

|   | 3.3 | Hardware Mapping                                           | 41 |

|   |     | 3.3.1 HW/SW Partitioning and Communication                 | 41 |

|   |     | 3.3.2 Data Parallelism                                     | 45 |

|   |     | 3.3.3 Fine-grain Pipeline Parallelism                      | 46 |

|   | 3.4 | Experiments and Analysis                                   | 47 |

|   |     | 3.4.1 Analysis of the Speedup                              | 48 |

|   |     | 3.4.2 Ranking Accuracy                                     | 50 |

|   |     | 3.4.3 Scalability of Speedup                                          | 50 |

|---|-----|-----------------------------------------------------------------------|----|

|   | 3.5 | Expectation                                                           | 51 |

|   | 3.6 | Summary                                                               | 53 |

| 4 | Acc | elerating Position-Aware Top-k ListNet under Custom Precision Regimes | 54 |

|   | 4.1 | Introduction                                                          | 54 |

|   | 4.2 | Position-Aware Sampling Approach                                      | 56 |

|   |     | 4.2.1 Optimisation of Top- $k$ ListNet Scheduling                     | 56 |

|   |     | 4.2.2 Position-Aware Sampling Scheme                                  | 57 |

|   | 4.3 | Mixed Precision Fixed Point Implementation                            | 60 |

|   |     | 4.3.1 Organisation of Computation Tasks                               | 60 |

|   |     | 4.3.2 Limitation of Traditional Fixed Point Implementation            | 63 |

|   |     | 4.3.3 Batch Fixed Point Implementation                                | 64 |

|   |     | 4.3.4 Case Study                                                      | 66 |

|   | 4.4 | Experiment Results and Analysis                                       | 68 |

|   |     | 4.4.1 Analysis of the Performance                                     | 68 |

|   | 4.5 | Expectation                                                           | 69 |

|   | 4.6 | Summary                                                               | 70 |

| 5 | Nov | The relation of Top- $k$ ListNet on FPGA                              | 71 |

|   | 5.1 | Introduction                                                          | 71 |

|   | 5.2 | Training with Multi-Kernels under Different Data Representations      | 73 |

|    | 5.3   | Experiment Results and Analysis                                                | 74 |

|----|-------|--------------------------------------------------------------------------------|----|

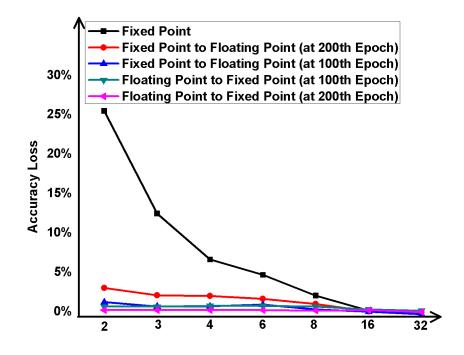

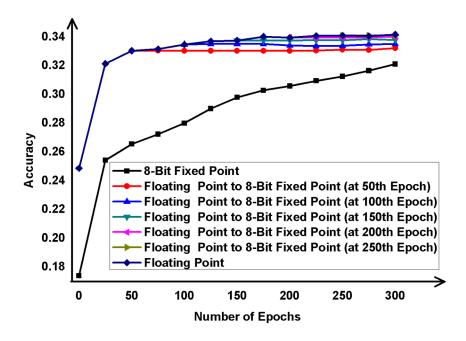

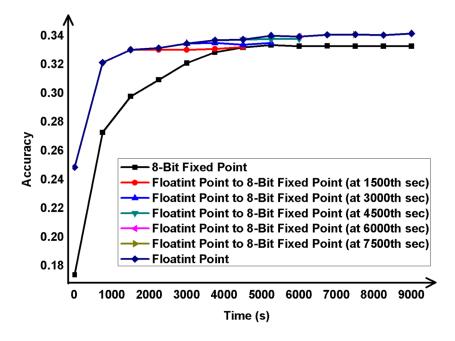

|    |       | 5.3.1 Performance of Swapping from Floating Point Kernel to Fixed Point Kernel | 75 |

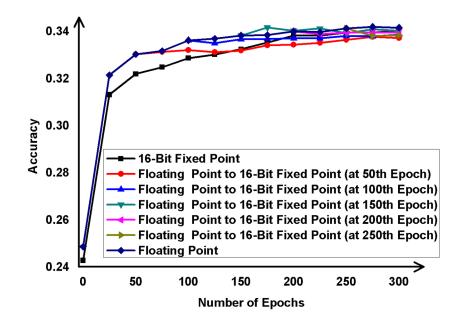

|    |       | 5.3.2 Performance of Swapping from Fixed Point Kernel to Floating Point Kernel | 79 |

|    | 5.4   | Performance Comparison                                                         | 82 |

|    | 5.5   | Expectation                                                                    | 83 |

|    | 5.6   | Summary                                                                        | 84 |

| 6  | Con   | clusion                                                                        | 85 |

|    | 6.1   | Summary of Thesis Achievements                                                 | 85 |

|    | 6.2   | Future Work                                                                    | 89 |

| Bi | bliog | raphy                                                                          | 90 |

# List of Tables

| 2.1 | The process of pointwise approach. The technology of pointwise approach is                                             |    |

|-----|------------------------------------------------------------------------------------------------------------------------|----|

|     | regression                                                                                                             | 14 |

| 2.2 | The process of pairwise approach. The technology of pairwise approach is clas-                                         |    |

|     | sification                                                                                                             | 16 |

| 2.3 | The process of listwise approach. The output space of listwise approach is exactly                                     |    |

|     | the same as that of the task $\ldots$ | 17 |

| 2.4 | Summary of ranking approaches                                                                                          | 18 |

| 3.1 | Size of communication data between software and hardware of one-task hardware                                          |    |

|     | implementation for Top-2 ListNet                                                                                       | 44 |

| 3.2 | Size of communication data between software and hardware of two-task hardware                                          |    |

|     | implementation for Top-2 ListNet                                                                                       | 45 |

| 3.3 | Utilization of hardware resource for Top-2 ListNet on Xilinx ZCU102 develop-                                           |    |

|     | ment board                                                                                                             | 49 |

| 3.4 | Time consumption of different tasks on CPU VS FPGA in one epoch $\ . \ . \ . \ .$                                      | 49 |

| 3.5 | The contribution of data parallelism with unrolling factor $U = 150$ (under fanout                                     |    |

|     | limitation) and pipeline with initiation interval $II = 11$ to speedup. Metric of                                      |    |

|     | computational efficiency is FLOP/s/DSP                                                                                 | 50 |

| 4.1 | Consumption of hardware resource and speedup over GPU implementation for                                             |    |

|-----|----------------------------------------------------------------------------------------------------------------------|----|

|     | different data types                                                                                                 | 66 |

| 4.2 | Consumption of hardware resource under different numbers of bits for batch                                           |    |

|     | quantisation implementation                                                                                          | 67 |

| 4.3 | The performance comparison of different data types implemented on FPGA. The                                          |    |

|     | standard time consumption on CPU is 420.05s per epoch, GPU is 45.8s $\ldots$ .                                       | 69 |

| 4.4 | The resource required and computation efficiency for different data types imple-                                     |    |

|     | mented on FPGA. Metric of computational efficiency is $OP/s/DSP$                                                     | 69 |

| 4.5 | The contribution of data parallelism with unrolling factor $U = 150$ (under fanout                                   |    |

|     | limitation) and pipeline with initiation interval $II = 11$ to speedup. Metric of                                    |    |

|     | computational efficiency is Gop/s/DSP $\hfill \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 69 |

| 4.6 | The consumption of hardware resource under different strategies for 8-bit batch                                      |    |

|     | quantsation                                                                                                          | 70 |

# List of Figures

| 2.1 | Searching result for query "learning to rank" [1]                                                  | 10 |

|-----|----------------------------------------------------------------------------------------------------|----|

| 2.2 | Framework of learning to rank                                                                      | 12 |

| 2.3 | Machine-learning-based search engine overview                                                      | 13 |

| 2.4 | Computation process of Top- $k$ ListNet                                                            | 22 |

| 2.5 | FPGA-based Accelerator Design Flow for Listwise Approach                                           | 32 |

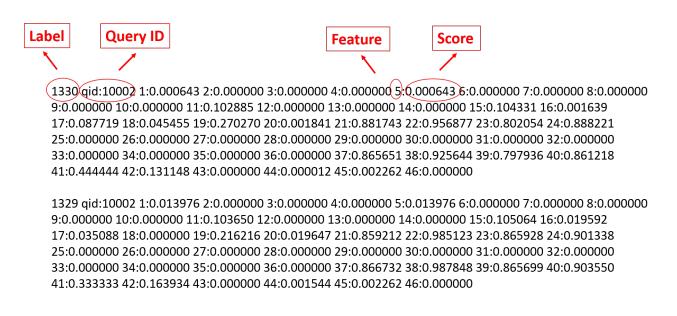

| 3.1 | An example of document representation in benchmark data set LETOR 4.0 $$                           | 36 |

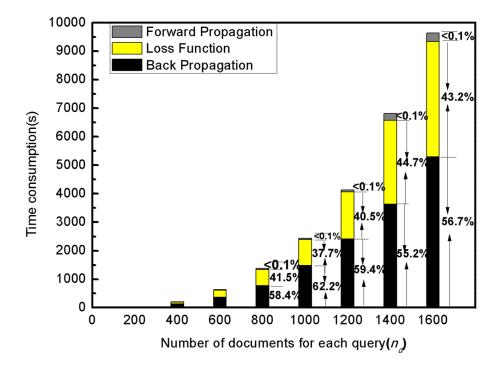

| 3.2 | Time consumption on our Intel Xeon CPU for different tasks in Top-2 ListNet                        |    |

|     | using the source code of RankLib                                                                   | 38 |

| 3.3 | Time consumption on our Intel Xeon CPU for different probability computation                       |    |

|     | methods                                                                                            | 39 |

| 3.4 | Communication data among different tasks in computation per training epoch $% \mathcal{L}^{(n)}$ . | 41 |

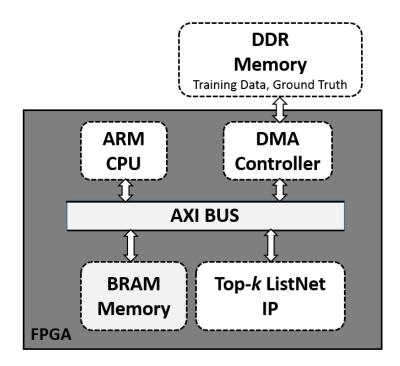

| 3.5 | The architecture of FPGA system integrated with Top- $k$ ListNet IP $\ . \ . \ . \ .$              | 44 |

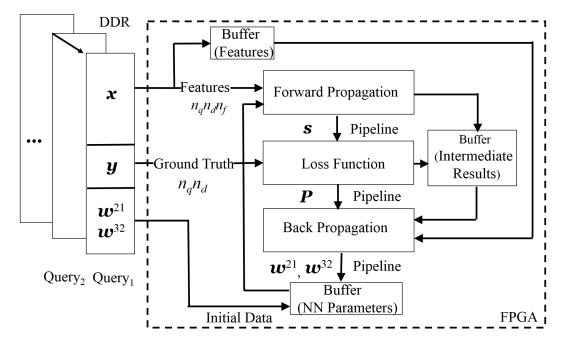

| 3.6 | Data flow between different tasks on FPGA                                                          | 46 |

| 3.7 | Structure of 2-layer neural network ranking model                                                  | 47 |

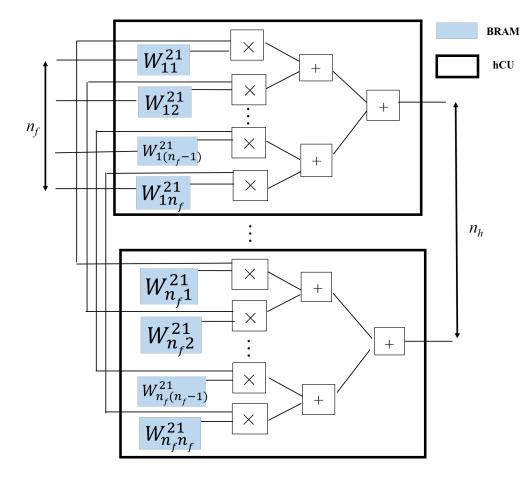

| 3.8 | The organisation of Computation Unit for hidden layer (hCU) $\ \ldots \ \ldots \ \ldots$           | 48 |

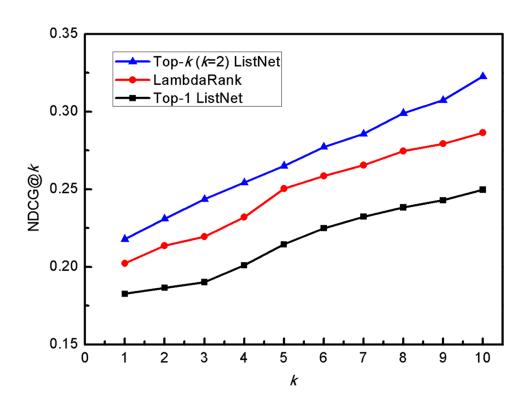

| 3.9  | Accuracy comparison among different algorithms, NDCG@ $k$ means it calculated                                                                                                                                                                              |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | at the first $k$ positions                                                                                                                                                                                                                                 | 51 |

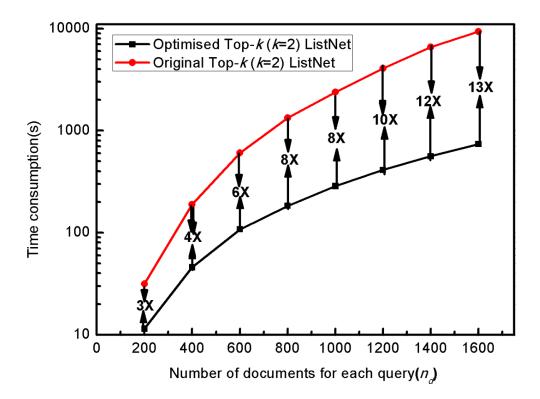

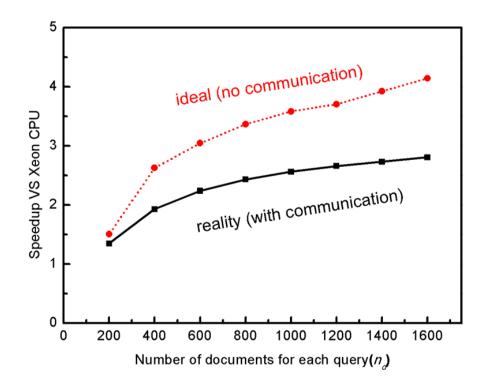

| 3.10 | The complete execution speedup of Top-k (k=2) ListNet with different $n_d$                                                                                                                                                                                 | 52 |

| 4.1  | Stochastic Top-3 ListNet. Each box represents a selected permutation, which is selected randomly                                                                                                                                                           | 56 |

| 4.2  | Position-aware Top-3 ListNet. Each box is one position, the number of samples in each box decreases from top to bottom                                                                                                                                     | 58 |

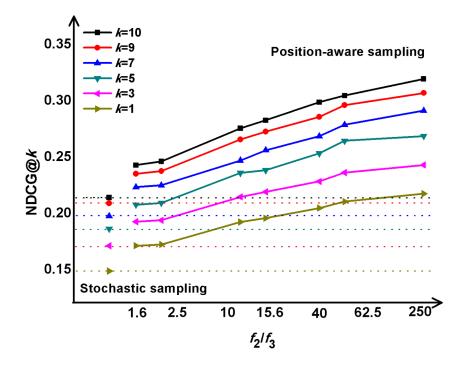

| 4.3  | NDCG@ $k$ comparison among different sampling factor sets, NDCG@ $k$ means it calculated at the first $k$ positions $\ldots \ldots \ldots$ | 60 |

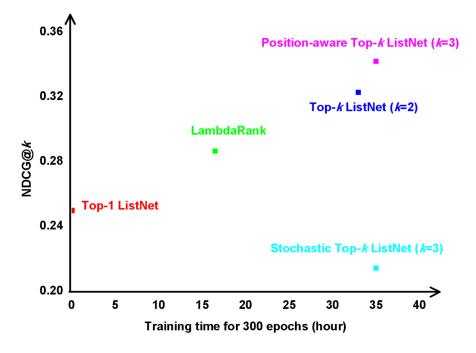

| 4.4  | Performance comparison among different ranking algorithms using CPU platform over 300 epochs                                                                                                                                                               | 61 |

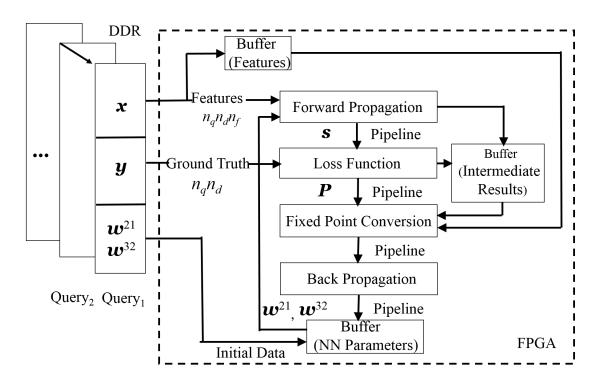

| 4.5  | The organisation of computation tasks on FPGA                                                                                                                                                                                                              | 62 |

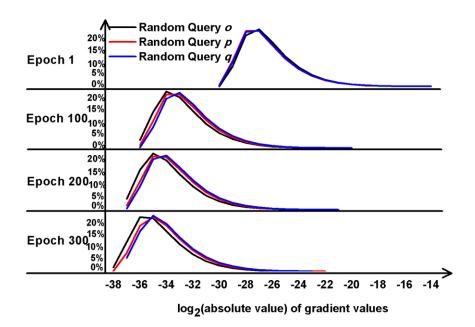

| 4.6  | Distribution of gradient values of loss function over 300 epochs                                                                                                                                                                                           | 63 |

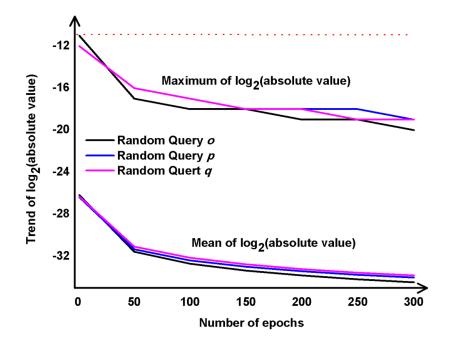

| 4.7  | The trend of mean and maximum gradient value of loss function over 300 epochs                                                                                                                                                                              | 64 |

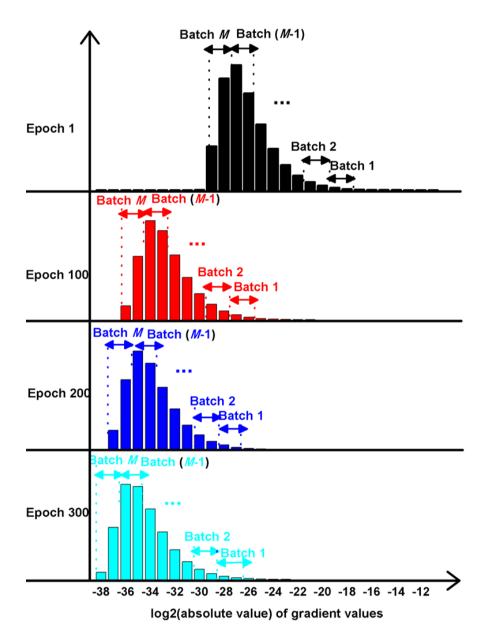

| 4.8  | The theory of batch implementation                                                                                                                                                                                                                         | 65 |

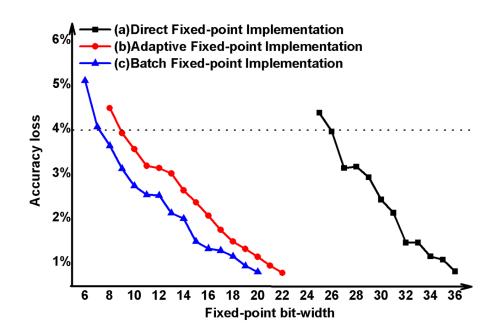

| 4.9  | Accuracy loss with different fixed point bit-widths $bw_1$ compared to floating point implementation                                                                                                                                                       | 67 |

| 5.1  | Accuracy loss for different representation types over 300 epochs compared to single floating point                                                                                                                                                         | 74 |

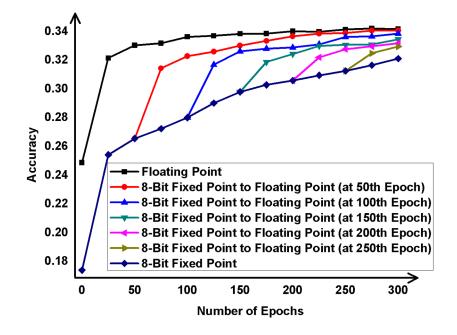

| 5.2  | Accuracy for swapping once from floating point kernel to 8-bit fixed point kernel at different epochs                                                                                                                                                      | 76 |

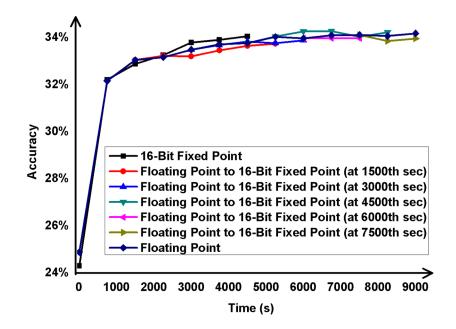

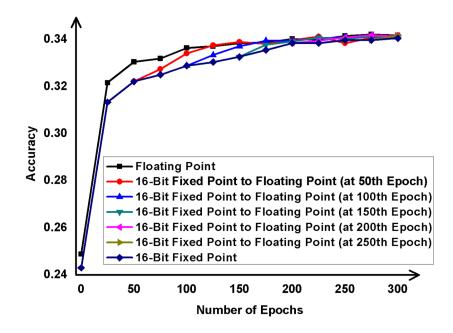

| 5.3  | Accuracy for swapping once from floating point kernel to 16-bit fixed point kernel at different epochs                                                                                                                                                     | 77 |

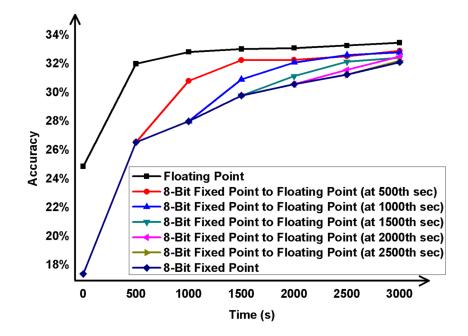

| 5.4 | Accuracy with swapping once from floating point kernel to 8-bit fixed point        |    |

|-----|------------------------------------------------------------------------------------|----|

|     | kernel at different time                                                           | 78 |

| 5.5 | Accuracy with swapping once from floating point kernel to 16-bit fixed point       |    |

|     | kernel at different time                                                           | 78 |

| 5.6 | Accuracy for swapping once from 8-bit fixed point kernel to floating point kernel  |    |

|     | at different epochs                                                                | 80 |

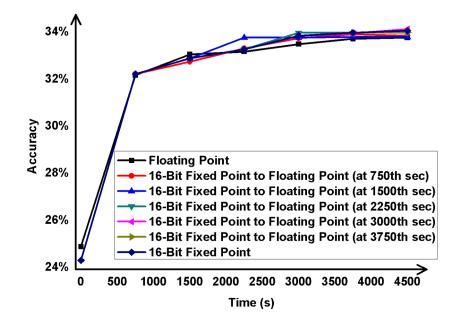

| 5.7 | Accuracy for swapping once from 16-bit fixed point kernel to floating point kernel |    |

|     | at different epochs                                                                | 81 |

| 5.8 | Accuracy for swapping from once 8-bit fixed point kernel to floating point kernel  |    |

|     | at different time                                                                  | 81 |

| 5.9 | Accuracy for swapping once from 16-bit fixed point kernel to floating point kernel |    |

|     | at different time                                                                  | 82 |

# Chapter 1

# Introduction

In recent years, with the increase of data-set size for document ranking, high-quality ranking models are required. It is promising to learn ranking models by leveraging machine learning technologies. However, when applying machine learning, it faces challenges in computational complexity for modern ranking algorithms. In this chapter, we display the difficulties to accelerate state-of-the-art ranking algorithms, and present several effective techniques to address the difficulties. These techniques will be explained in following chapters in details.

## 1.1 Motivation

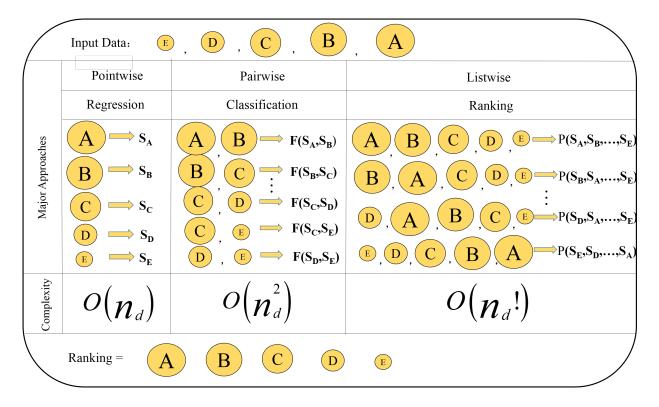

Ranking is the process of ordering a set of documents according to relevance to a query [2, 3, 4]. A well-known example is in the ordering of links returned from a search engine such as Google: links near the top of the page should be those which are most likely to satisfy the user's query. Ranking relies on the definition and training of a ranking model f(q, d) which accepts a query qand a set of documents d, and returns a ranked list of documents. To improve ranking the use of machine-learning techniques has been explored to automatically construct and tune the ranking model, which has led to a general field called learning to rank, with three main approaches:

• pointwise approach;

- pairwise approach;

- listwise approach.

Pointwise and pairwise learning approaches are currently used in practice, as they have relatively low compute requirements. In the pointwise approach a ranking function is applied independently to each individual document to determine individual scores. These scores are then sorted to determine the overall ranking [5, 6]. In the pairwise approach pairs of documents are considered at a time and their relative rankings are determined [7, 8, 9]. The advantage of both these approaches is that existing methods, such as regression techniques for pointwise and classification techniques for pairwise, can be directly applied. However, because ranking is about learning a complete ordering on documents, it is difficult to accurately derive the relative position of the documents in the final ranked list using these two approaches [10].

The listwise approach is a newer method which addresses the issue of relative ranking accuracy by constructing the ranking function using lists of documents, rather than considering single document or pairs of documents [11, 12]. While this improves the accuracy of the ranking, it scales poorly: if the number of documents is  $n_d$ , then the naive listwise approach takes  $O(n_d!)$  time. To address this scaling problem, Top-k ListNet was proposed where instead of all permutations being considered, they are only clustered by the first k documents [13, 14, 15].

Top-k ListNet reduces the number of permutations that need to be considered from  $n_d!$  to  $\frac{n_d!}{(n_d-k)!}$ . However, as the number of documents being ranked is usually large  $(n_d > 1000)$ , k is generally limited to 1, as for k > 1 the time complexity is still quite high. For many applications, the high time complexity can be a problem, for example, searching breaking news, where the ranking model needs to be updated and retrained frequently so that it can reflect the freshness of more recent documents [16, 17, 18, 19]. Wang et al, give a good example for the importance of freshness [20]: a user types the query "Apple Company" into a search engine, with the goal of finding breaking news relevant to this company. The documents which cover the release of iPhone 4S were quite relevant on October 4, 2011; however, one day later these documents became less relevant as the Apple founder Steve Jobs had just passed away. So a document

which was quite relevant to a certain query may become less relevant than newer documents. If we want to exploit the potential gains in accuracy from Top-k ListNet approach, then we need to find a way to decrease its training time.

In this research, we investigate the training process of Top-k ListNet by setting up a randomly initialised network, to reveal the bottleneck in computation. Then we offer local optimal solutions by redesigning the Top-k ListNet algorithm and applying hardware acceleration to tackle the challenge of high training time. We hope to improve the training speed of Top-k ListNet and maintain the model accuracy at the same time, so as to bring an alternative for commercial applications.

### 1.2 Challenges

As listwise approach, Top-k LisNet is quite effective in the application of ranking, but the intensive computation restrains it in real applications. Like other neural network algorithms, the Top-k ListNet algorithm consists of three basic steps: forward propagation, loss function and back propagation. Forward propagation is not expensive in computation, which just calculates the score for each candidate document. The loss function and back propagation are the computationally intensive steps because of the large number of permutations involved in computing the gradients. The loss function and back propagation necessarily need to access all of the possible permutations at each epoch in order to evaluate the distance between each possible permutation and ground truth permutation. As mentioned in Section 1.1, the number of possible permutations is  $\frac{n_d!}{(n_d-k)!}$ , where  $n_d$  is the number of the documents. This makes the Top-k ListNet algorithms time-consuming, especially when large data sets are targeted. One possible solution is parallel implementations of Top-k ListNet, however, it is not straightforward. There are several challenges in the acceleration of Top-k ListNet using hardware:

(1) The first challenge of accelerating the Top-k ListNet algorithms in parallel computing devices is the computational dependence between different permutations. The evaluation of the divergence loss which needs to access every possible permutation is the dominant computational

bottleneck. Therefore, accelerating the permutation computation is a crucial task in order to allow the listwise approach to learn ranking models with large-scale training data sets. However, the probability of next permutation is calculated by changing the document order of last permutation, that means the permutation probability is calculated sequentially and there is dependence between different permutations. In order to achieve useful speedup using parallel computing platforms, we need to expose the parallelism first.

(2) The second challenge is how to select high-weighted samples from the whole data set which has a large population. As mentioned in Section 1.1, the full set of the permutation class is  $\frac{n_d!}{(n_d-k)!}$ , which is intractable in practice. Thus it is necessary to using sampling approaches to reduce the scale of computation in the model training. However, it is difficult to select highweighted samples using traditional sampling methods since there are many more low-weighted samples.

(3) The third challenge of accelerating the Top-k ListNet algorithms in parallel computing devices is how to maintain the model accuracy using low precision training. The quantisation implementation has already become an important technique in the acceleration of the Top-k ListNet algorithm, as the low precision representation is able to achieve high computation speed. However, the quantisation method would strongly influence the model accuracy if the number of bits is not enough to represent the whole range of the variable faithfully. Thus it is quite necessary to explore effective quantisation methods on listwise algorithms in ranking applications, as Top-k ListNet has variables with a large range.

(4) The fourth challenge is how to deal with the trade-off between model accuracy and training time. As we know, the fixed point operation consumes less resource and leads to a higher parallelism compared to floating point data paths. That means the fixed point computation can minimise training latency. However, apparently the fixed point computation sacrifices the model accuracy. Floating point training can guarantee the model accuracy, but it requires a high computation time. Therefore it is necessary to develop new methodologies to improve the trade-off.

In order to improve the practicality of information retrieval, multi-core computational plat-

forms, such as Central Processing Units (CPUs) and Graphics Processing Units (GPUs), have been widely used to accelerate ranking algorithms [21, 22, 23]. However, for current computational capability of CPUs and GPUs, it is difficult to keep up with the pace at which data is increasing dramatically. Thus we turn to the reconfigurable device: Field Programmable Gate Arrays (FPGAs) in this work. FPGAs can be used as customized computing engines for accelerating many machine learning algorithms due to its bit-level parallelism. By properly optimising the computation task so that it can be operated in parallel, and mapping the task into an FPGA, a competitive acceleration can be achieved compared to the respective CPU and GPU implementations [24, 25, 26]. Furthermore, FPGAs make it possible to explore the potential of any custom precision format for neural network parameters. Comparing to implementations with full precision (floating point) which is the default approach in the ranking algorithm, low precision (fixed point) operators consume less resource, and thus allow for more parallelism. Last but not least, reconfiguration is basically a feature in modern FPGAs that enables users to change their functions at running time according to the application requirement. This capability can be utilised to improve the training speed of floating point implementation and model accuracy of fixed point implementation. In this research, the FPGA platform used is Xilinx UltraScale+ ZCU 102 board, and the RTL code is transcompiled from high-level language C++.

### **1.3** Contributions

This research aims to accelerate the training process of the Top-k ListNet algorithm on FPGAs by proposing new computation methods for algorithms and novel customized precision method, in order to largely utilize the advantages and characteristics of FPGAs. The new computation method of the Top-k ListNet training exposes more fine-grained parallelisms, as such, parallel computation can be realized from node to node by applying loop unrolling directive using high-level synthesis, and pipelining computation can be implemented from permutation to permutation by applying pipelining directive using high-level synthesis. The novel customized precision method improves the training speed of Top-k ListNet by implementing the back propagation arithmetic operators in fixed point on FPGAs, but within acceptable accuracy loss. As such, more parallel operators can be instantiated for a given resource budget, and thus improving the computation speed. The thesis also investigates how to utilise the differentiating reconfiguration capability of FPGAs for applications with large data sets, in order to tackle the trade-off between long training time under floating point implementation and low model accuracy under fixed point implementation. This is achieved by switching between floating point kernel and fixed point kernel automatically. The results presented in the thesis denotes that significant improvements in speed can be attained with the proposed FPGA implementation techniques compared to the respective CPU and GPU implementations.

This research achieves several contributions on developing the hardware-based acceleration of the Top-k ListNet algorithm for ranking. These contributions are summarized as follows (the details are given in each chapter):

- A new computation method, which exposes more parallelism, allowing the computation in parallel to address challenge (1). It is the first work that presents parallel FPGA architectures for the Top-k ListNet algorithm, and shows a 3.21x speedup compared to that of the CPU implementation.

- A novel biased sampling method, which takes the importance of positions into account to address challenge (2). This method has a higher probability to select high-weighted samples, leading to significant accuracy gains.

- A novel quantisation method based on FPGA devices for variables with a large range to address challenge (3). This method organises the whole range of the variable to several batches, and associates each batch with a different fractional precision. It needs fewer bits to represent the whole range, fewer bits consume less resource and delivers a higher degree of parallelism for a fixed hardware resource. FPGA implementation based on the quantisation method shows a 4.42x speedup over the GPU implementation.

- A methodology that allows switching between floating point and fixed point kernels automatically via full reconfiguration, which improves the trade-off between model accuracy

and training time, to address challenge (4).

### 1.4 Thesis Outline

This thesis contains six chapters. In this chapter, the motivation, challenges and contributions of this work are presented.

Chapter 2 gives an introduction to the theory of ranking algorithms (the pointwise, pairwise, and listwise approaches) in details. It contains the concrete training process of these algorithms to follow the remaining chapters. Furthermore, the main advantages and shortcomings of ranking algorithms focusing on the model accuracy and the training complexity are analysed and concluded in details. Then the main evaluation measures for ranking model are provided. After that, the Top-k ListNet approach is reviewed, and the main bottleneck of Top-k ListNet is identified, especially for big data applications. Finally, a complete literature review is presented as a separate section, together with the acceleration of ranking algorithms using multi-CUPs, GPUs, and FPGAs in previous works.

Chapter 3 meets challenge (1), it investigates the acceleration of ListNet training using FPGAs, and improves the training speed by using hardware-oriented algorithmic optimisations, and by transforming algorithmic structures to expose parallelisms. The parallelism is ready to be exploited by implementing a randomly initialised the ListNet algorithm on FPGA devices. The performance is compared to existing ranking approaches, and also to the respective CPU implementation. Analysis on the results is also provided.

Chapter 4 meets challenges (2) and (3), an FPGA-based accelerator for Top-k ListNet under custom precision regimes is proposed. This position-aware sampling approach takes the importance of ranking positions into account, and shows a better accuracy than previous sampling methods. An effective quantisation method based on FPGA devices for a randomly initialised the ListNet algorithm is proposed, which organises the gradient values to several batches, and associates each batch with a different fractional precision. We implemented our approach on a Xilinx UltraScale+ board and applied it to the benchmark data set for ranking. The experiment results show a significant improvement in the training speed, and also computation efficiency (OP/s/DSP).

Chapter 5 meets challenge (4), an multiple kernel training method is proposed which is based on the differentiating reconfigurable feature of FPGAs. This new method deploys multiple functions, which are the fixed point function and floating point function. The function on board can be interchanged during runtime, which is decided according to the model accuracy and training time requirements. We implemented the methodology for randomly initialised position-aware Top-k ListNet on FPGAs, the performance is compared to pure floating point training and fixed point training, great balance is attained.

Finally, Chapter 6 summarizes the current state of our work and discusses future research directions.

## 1.5 Publications

This thesis has led to the following published conference papers:

- Qiang Li, Shane T. Fleming, David B. Thomas, Peter Y. K. Cheung. Accelerating Topk ListNet Training for Ranking Using FPGA. IEEE International Conference on Field Programmable Technology (FPT), December, 2018.

- Qiang Li, Erwei Wang, Shane T. Fleming, David B. Thomas, Peter Y. K. Cheung. Accelerating Position-Aware Top-k ListNet for Ranking under Custom Precision Regimes. International Conference on Field Programmable Logic and Applications (FPL), September, 2019.

# Chapter 2

# Background

With the fast development of learning to rank, different ranking approaches have been proposed. However, different approaches have their own advantages and shortcomings. In order to obtain high-quality ranking models with low training latency, existing ranking approaches and acceleration work are briefly depicted in this chapter.

## 2.1 Introduction of Learning to Rank

In order to improve the efficiency of information retrieval on FPGAs, we need to know how to order the relevant documents which match the queries first, and then consider how to utilize FPGAs to implement ranking algorithms. A typical application of ranking algorithms is search engine.

A search engine architecture generally contains six major components: crawler, parser, indexer, link analyzer, query processor, and ranker. When a user submits queries to a document retrieval system, the crawler collects the relevant documents from the data set, according to some prioritization strategies. The parser generates index terms and a hyperlink graph for these documents after analyzing them. The indexer creates the indexes or data structures which enable fast search of the documents. The link analyzer determines the importance of each document

| Query=learning to rank                             |             |

|----------------------------------------------------|-------------|

| a. http://web.mit.edu/shivani/www/Ranking-NIPS-05/ | 1 (Good)    |

| b. http://www.learn-in-china.com/rank.htm          | 0 (Bad)     |

| c. http://research.Microsoft.com/~letor/           | 3 (Perfect) |

|                                                    |             |

Figure 2.1: Searching result for query "learning to rank" [1]

on the basis of the document graph. The query processor is the interface between users and search engines, which transforms the input queries to index terms which can be understood by search engines. The ranker is the central component which is responsible to rank indexed documents using ranking models [1]. For example, when a user types query "learning to rank" in the search engine as Figure 2.1, the engine system processes the query as followings:

1) The indexer generates the indexes for documents to enable efficient document retrieval;

2) The link analyzer finds the candidate documents (a, b, c...) that satisfy the input query – "learning to rank";

3) The ranker calculates scores for the documents (a, b, c...) with the ranking model, which is usually the combination of many information retrieval features, such as frequency of the term (noted as TF), the length (noted as LEN), etc.. Then all these documents are sorted in descending order of their scores.

Due to its importance, machine learning technologies have been leveraged to build innovative and effective ranking models, which is named learning to rank. In machine learning, there are four key components, which are *input space*, *output space*, *hypothesis space*, and *loss function* [1].

(1) The *input space*, which contains the relevant documents for ranking. The input, or socalled training set, is structured with queries that are issued. As mentioned before, a data set has lots of queries, and every query has  $n_d$  relevant documents. These documents are usually represented by feature vectors which are chosen based on the application. Each document feature is real-valued data.

(2) The *output space*, which contains the learning results in regard to relevant documents. In machine learning, the *output space* is usually decided by the application. The *output space* is the set of real numbers in regression; the *output space* is discrete categories in classification, which is not associated with positions; while in ranking, it should be a permutation, which is position based.

(3) The hypothesis space, which defines the function mapping the input to the output. That is, the function takes the relevant documents as input, and generates predictions for each document.

(4) The *loss function*, which measures the compatibility between the prediction of the model and the ground truth. It is clear that *loss function* plays a key role in machine learning, because it reflects the distance between the prediction and the target. With the *loss function*, the differences between the predictions and the ground truths are collected, and the parameters of ranking model are optimised by minimising the differences.

In ranking, the ranking model takes documents as inputs and assigns a score to each document; then the documents are sorted in descending order of the scores, and a ranked list is returned back to user. The order of the ranked list should reflect how relevant each document is to the query, with the most relevant coming first.

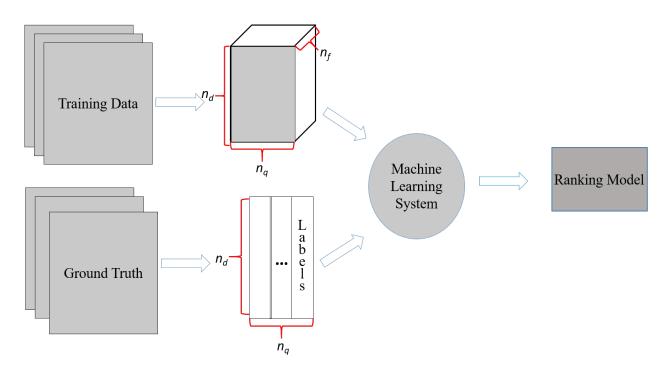

In learning, there is a training set consisting of  $n_q$  queries, where each query has  $n_d$  relevant documents and each document is represented by  $n_f$  features. This results in an input data set  $\boldsymbol{x}$  of size  $n_q n_d n_f$ . The ground truth labels  $\boldsymbol{y}$  are given as a reference ordering of the documents, where an ordering is a permutation of  $n_d$  documents for each query, and the size of  $\boldsymbol{y}$  is  $n_q n_d$ . The goal of learning is to train the ranking model so that the output of the ranking model is as close to the ground truth as possible, as displayed in Figure 2.2. The learning process tunes the ranking model by three steps: first, applying the training data to the model; second, comparing the model output to the ground truth using a *loss function*; and finally updating the parameters of the model to minimise the error [1]. The overall structure of machine-learning-based search

Figure 2.2: Framework of learning to rank

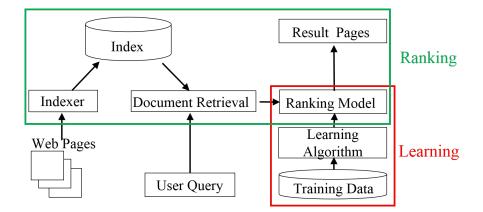

engine is shown in Figure 2.3.

In order to improve the accuracy of ranking model, a more sophisticated technique for hyper parameter tuning is widely used, which is called cross-validation. In cross-validation, a learningto-rank algorithm is adopted to train ranking models, and then the model is adjusted using the validation fold. For example, in five-fold cross validation, each training set is split into five equal folds, which means the number of queries among folds is equal. Four training folds are used for learning the ranking model, the remaining validation fold is used for tuning the hyper parameters of the ranking algorithm. We would then iterate over which fold is the validation fold, the average performance across the different folds is used to measure the overall accuracy of a learning-to-rank algorithm.

Besides the model accuracy, the performance of learning-to-rank algorithms is also evaluated by training time. For the model accuracy, we prefer employing the standard metric "Normalized Discounted Cumulative Gain" to evaluate, which will be explained below. For the training time, the results are compared with that of implementation on general computing platforms, such as CPU and GPU. Normally we run 300 epochs on the benchmark data set. 300 epochs is a typical length of training to obtain a ranking model with good accuracy [27].

Figure 2.3: Machine-learning-based search engine overview

In order to obtain a deeper understanding of learning-to-rank algorithms, a categorization is performed on these algorithms. Based on the four components of machine learning, we categorise the algorithms and models for learning-to-rank into three groups: the pointwise, pairwise, and listwise approaches.

## 2.2 Major Ranking Approaches

As mentioned above, the major ranking approaches can be divided to three categories. In order to better understand learning to rank, we will explain the advantages and disadvantages of each category in the following subsections.

#### 2.2.1 The Pointwise Approach

The pointwise approach assigns a score to each single document, and then the *loss function* examines the accurate prediction of the ground truth label for each document. The *input space* of pointwise approach is each single document, which is represented by a feature vector. The *output space* contains the accurate prediction for each document, which indicates the relevance degree to the query. The *hypothesis space* contains a function called scoring function s [1], which takes the feature vector as input and produces the accurate prediction for the document. Based on s, we can sort all the documents and generate the predicted ranking list. When using the pointwise approach to do ranking, the *loss function* examines the accurate difference between

| Training Data Input: | A | В | C        | D | E |

|----------------------|---|---|----------|---|---|

|                      |   |   | $s_A$    |   |   |

|                      |   |   | $s_B$    |   |   |

| Regression           |   |   | $s_C$    |   |   |

|                      |   |   | $s_D$    |   |   |

|                      |   |   | $s_E$    |   |   |

| Complexity           |   |   | $O(n_d)$ |   |   |

Table 2.1: The process of pointwise approach. The technology of pointwise approach is regression

the predicted result and the ground truth label over each single document. So the computational complexity of training process is proportional to the number of associated documents, which is  $n_d$ .

Note that the pointwise approach is deployed for tasks of predicting real-valued quantities. In ranking, pointwise approach predicts the accurate relevance degree for each document, the position information of each document is not considered over the training process. Besides, the pointwise approach does not take into account that some documents are related to the same query. Because information retrieval is query level and position based, the pointwise approach has its limitations:

(1) In pointwise algorithms, the fact that the numbers of relevant documents for different queries are quite different is ignored. That means, when the number of relevant documents varies largely for different queries, the queries with a large number of documents will decide the final result of *loss function*.

(2) The pointwise approach calculates the accurate relevance degree of each document, so the position information of each document in the ranked list is not reflected. Therefore, the pointwise approach will be unconsciously dominated by those unimportant documents (the number of unimportant documents is much larger than that of important documents).

From above, we can see the pointwise approach is not the perfect approach to do ranking. In order to overcome the shortcomings of pointwise approach, people turn to take document pairs or a set of documents as the input rather than a single document. The approach which regards document pairs as input is called the pairwise approach, while the approach which takes the whole set of documents as input is called the listwise approach. Using the pairwise approach, the relative relevance degree between documents can be visible. Using the listwise approach, the position of every document with the same query can be reflected.

#### 2.2.2 The Pairwise Approach

The pairwise approach assigns a score to each relevant document using the current ranking model parameters, applies a pairwise differentiable *loss function* to the scores, and finally applies gradient descent to update the model parameters. The *input space* of the pairwise approach is pairs of documents, which are represented by feature vectors. The *output space* is the relative order between each pair of documents, which can be the value of -1 and +1. The *hypothesis space* takes a pair of documents as input and predicts the pairwise preference between them. In the pairwise approach, ranking is modeled as a pairwise classification, and the corresponding classification loss on a pair of documents is used as the *loss function*. When the scoring function s is used, the *loss function* measures the difference between  $F(s_A, s_B)$  and the ground truth label  $G(y_A, y_B)$ .

Note that the *loss function* used in the pairwise approach only considers the relative order of document pairs. So the computational complexity of the training process is proportional to the number of document pairs, which is  $n_d^2$ . When only taking into account pairs of documents, however, it is difficult to derive the positions of the documents in the final permutation. Besides, pairwise approach does not leverage the fact that some pairs are related to the same query. Considering that ranking is query level and position based, we can predict a gap between this approach and ranking:

(1) When the relevance judgments are given in terms of multiple levels, however, it will lead to the loss of the finer granularity in relevant judgments as we assign the pairwise preference. For instance, there are two document pairs whose relevance degrees are different, the relevance judgments of one pair are GOOD and BAD, while the relevance judgments of the other pair are GOOD and FAIR, we can see these two pairs have different magnitudes of pairwise preferences.

| Training Data Input: | A             | В | $\overline{C}$ | D | E             |

|----------------------|---------------|---|----------------|---|---------------|

|                      |               |   |                |   |               |

|                      | $F(s_A, s_B)$ |   | $F(s_A, s_C)$  |   | $F(s_A, s_D)$ |

|                      | $F(s_A, s_E)$ |   | $F(s_B, s_A)$  |   | $F(s_B, s_C)$ |

| Classification       | $F(s_B, s_D)$ |   | $F(s_B, s_E)$  |   | $F(s_C, s_A)$ |

|                      | $F(s_C, s_B)$ |   | $F(s_C, s_D)$  |   | $F(s_C, s_E)$ |

|                      | $F(s_D, s_A)$ |   | $F(s_D, s_B)$  |   | $F(s_D, s_C)$ |

|                      | $F(s_D, s_E)$ |   | $F(s_E, s_A)$  |   | $F(s_E, s_B)$ |

|                      | $F(s_E, s_C)$ |   | $F(s_E, s_D)$  |   |               |

| Complexity           |               |   | $O(n_d^2)$     |   |               |

Table 2.2: The process of pairwise approach. The technology of pairwise approach is classification

However, in the *loss function* calculation of the pair approach, the ground truth labels of these two pairs are the same, which is not reasonable.

(2) For the pairwise approach, the number of pairs is in a quadratic order of the number of documents, that makes the imbalanced distribution across queries more serious than the pointwise approach.

(3) The position of documents in the final results is invisible from pairwise ranking algorithms, because the input of *loss functions* is document pairs. This means it only considers the relative order between two documents, the position of the documents in the final ranked list can hardly be derived. This approach is still not perfect for ranking.

From above analysis, we can see the pairwise approach has its advantages over the pointwise approach. It gives a relative order between two documents instead of the precise relevant value of single document. However, the problems mentioned above limits the effectiveness of the pairwise approach. To address the problems, new algorithms have been proposed.

#### 2.2.3 The Listwise Approach

The listwise approach gives a score to each document and then these documents are sorted to produce permutations. Different from the pointwise and pairwise approaches, the *input space* of the listwise approach is the entire set of documents associated with a query, which are all represented by feature vectors. The *output space* of the listwise approach is a predicted

| Training Data Input: | A                         | B C                       | D E                       |

|----------------------|---------------------------|---------------------------|---------------------------|

| Classification       | $P(s_A, s_B, \dots, s_E)$ | $P(s_A, s_B, \dots, s_D)$ | $P(s_A, s_B, \dots, s_C)$ |

|                      | $P(s_B, s_A, \dots, s_E)$ | $P(s_B, s_A, \dots, s_D)$ | $P(s_B, s_A,, s_C)$       |

|                      | $P(s_C, s_A, \dots, s_E)$ | $P(s_C, s_A,, s_D)$       | $P(s_C, s_A,, s_B)$       |

|                      | $P(s_D, s_A,, s_E)$       | $F(s_D, s_A, \dots, s_C)$ | $P(s_D, s_A,, s_B)$       |

|                      | $P(s_E, s_A, \dots, s_D)$ | $P(s_E, s_A, \dots, s_C)$ | $P(s_E, s_A,, s_B)$       |

| Complexity           |                           | $\frac{\dots}{O(n_d!)}$   |                           |

Table 2.3: The process of listwise approach. The output space of listwise approach is exactly the same as that of the task

permutation of the relevant documents, which is consistent with the task. The hypothesis space operates on the entire set of documents and outputs the predicted permutation, which is usually realised with the scoring function s in real implementations. s assigns a score to each document first, and then these documents are sorted in descending order to generate the ranked list based on the scores. The listwise *loss function* measures the inconsistency between the predicted permutations and the ground truth permutation.

Note that for the listwise approach, the *output space* that facilitates the learning process is exactly the same as the *output space* of the task. In this regard, the listwise approach models the raking problem in a more natural way than the other approaches where there are mismatches between the *output space* that facilitates learning and the real *output space* of the task. However, the computational complexity of training process of listwise approach is  $O(n_d!)$ , which is much higher than pointwise and pairwise approaches.

While the listwise approach improves the accuracy, the training complexity unfortunately scales quadraticaly with the number of documents,  $n_d$ . Comparatively speaking, the training complexity of pointwise and pairwise approaches is more acceptable. In particular, the complexity of listwise approach might be too high for real applications when  $n_d$  is large. This situation would be changed by parallel computing, since there is a potential to execute the *loss function* of listwise approach in parallel, as will be shown later.

Table 2.4: Summary of ranking approaches

#### 2.2.4 Ranking Approach Overview

In the previous three subsections, we gave a comprehensive review on the pointwise, pairwise, and listwise approaches for learning to rank. We presented the basic framework, and discussed the advantages and disadvantages of each approach from the perspective of model accuracy and computational complexity. The key components for each approach are listed in Table 2.4. In the case of Figure 2.1, after calculating a score for each document, the pointwise approach compares the score with the ground truth label for each document (a, b, c...) directly; the pairwise approach measures the difference for relative order of each pair (ab, ac, bc...); the listwise approach evaluates the inconsistency with the ground truth permutation (c, a, b...). We can see that the major differences between these approaches lie in their *loss functions*, which guide the learning process. However, the evaluation of the learned ranking models is based on the evaluation measures, which will be discussed next.

## 2.3 Evaluation Measures

A standard evaluation mechanism plays an important role in selecting the most effective model. Because information retrieval is based on shareable document collections, queries, and relevance assessments, the corresponding evaluation process to proposed ranking models can be described as follows:

1) Collect queries submitted by surfers to form a test set.

2) For each query,

(a) Collect relevant documents of the query from the data set.

(b) Get the ground truth label for each document.

(c) Generate the desired permutation by sorting the relevant documents using a proposed model.

(d) Measure the difference between the permutation predicted by the proposed model and the permutation generated by the ground truth labels.

3) Calculate the average difference over all queries to evaluate the performance of the proposed model.

There are two most popular evaluation measures, one is called Mean Average Precision (MAP), the other is Normalized Discounted Cumulative Gain (NDCG). Usually the evaluation measures are defined query level and position based, as a function of the ordered documents given by the proposed model and the ground truth labels. The measured results are averaged over all the queries in the test set.

For MAP, the precision at position k is defined as (P@k). Suppose the binary judgment is used for the documents, 1 for relevant documents, while 0 for irrelevant documents. Then P@k is defined by

$$P@k(\boldsymbol{y}, \boldsymbol{\pi}) = \frac{\sum_{j < =k} I_{\{y_{\pi(k)=1}\}}}{k}$$

(2.1)

Here  $I_{\{\}}$  is the indicator function, and  $\pi(k)$  means the document at position k in the permutation  $\pi$ . Finally the Average Precision (AP) can be calculated as:

$$AP@k(\boldsymbol{y}, \boldsymbol{\pi}) = \frac{\sum_{j < =k}^{n_d} P@k \cdot I_{\{y_{\pi(k)=1}\}}}{n_d^1}$$

(2.2)

Here  $n_d$  is the total number of documents relevant with query q, and  $n_d^1$  is the total number of documents whose judgments are 1. The mean value of AP over all queries is mean average precision (MAP).

For NDCG, the precision at position k is defined as (NDCG@k). This evaluation measure is special for multiple relevance judgments, and takes documents' explicit position into account. The DCG can be calculated by:

$$DCG@k(\boldsymbol{y}, \boldsymbol{\pi}) = \sum_{j=1}^{k} G(y_{\pi(j)})\eta(j)$$

(2.3)

Here G() is the rating of a document, which usually sets  $G(z) = (2^z - 1)$ .  $\eta(j)$  is a position discount factor, which is  $\eta(j) = 1/\log(j+1)$ . By normalizing DCG@k with its maximum possible value (denoted as  $Z_k$ ), another measure called Normalized DCG (NDCG) is got as,

$$NDCG@k(\boldsymbol{y}, \boldsymbol{\pi}) = \frac{1}{Z_k} \sum_{j=1}^k G(y_{\pi(j)}) \eta(j)$$

(2.4)

We can see that upper bound of NDCG is 1, while the bottom bound is 0. There are some similarities between these two evaluation measures:

1. Both MAP and NDCG are calculated at the query level. That means, we calculate the measure for each query first, and then average the results over all queries. Because the measure result is decided by the averaged value over all queries, and each query contributes similarly to the final result, a particular query will not dominate the evaluation process.

2. Both MAP and NDCG are position based. That is, rank position is explicitly considered in

computation. If and only if the score of one document passes another, the rank positions will change. And small changes in the scores will not influence the positions of documents. Note that both of the measures are usually position-based, that means they are discontinuous and non-differentiable with regards to the continuous scores.

MAP is assumed that there are two ground truth labels: relevant and irrelevant. So it is mainly used for the pointwise and pairwise approaches. While NDCG is mainly used to measure the ranking accuracy when there are more than two distinct ground truth levels. Using NDCG to compare the listwise with the other two approaches, the listwise approach delivers a better accuracy in general, because it emphasizes the concept of a ranked list and the position of the documents in the final ranking result are visible [1].

## 2.4 Review of Top-k ListNet

ListNet, proposed by Cao [13], is the current state-of-the-art listwise approach receiving much attention. This method implements the ranking model as a fully-connected neural network (NN). For each query, the ranking model takes the feature vector of each relevant document as input and predicts the relevance degree for each document, the relevance degree is represented by the real-valued output; Then the divergence is collected between the permutation based on the outputs of ranking model and permutation based on ground truth; Finally a method called gradient descent is used to update the ranking model, so that the divergence loss diminishes.

Based on the fact that the calculation is intractable in practice, an alternative approach was proposed that only ranked the Top-k elements in a listwise fashion. Given the scores of all documents, Top-k ListNet clusters the permutations by the first k documents.

The value of k determines the computational complexity of loss function directly, as the metric between the corresponding Top-k probability distributions is defined as the listwise loss function. For Top-k ListNet, although the number of distinct probabilities reduces from  $n_d!$ to  $\frac{n_d!}{(n_d-k)!}$ , the complexity is still a problem as it scales poorly as k is increase, as it needs to calculate the probability of every permutation.

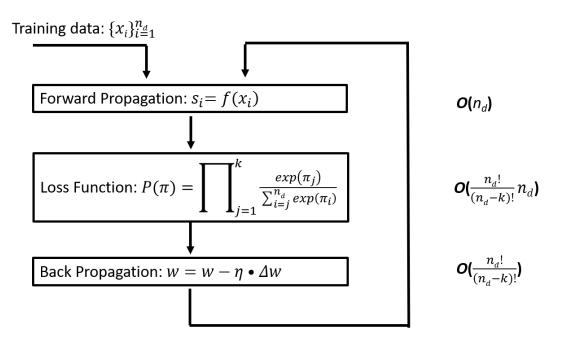

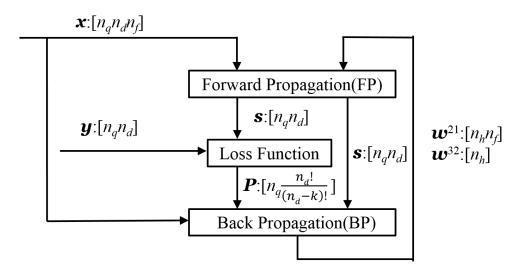

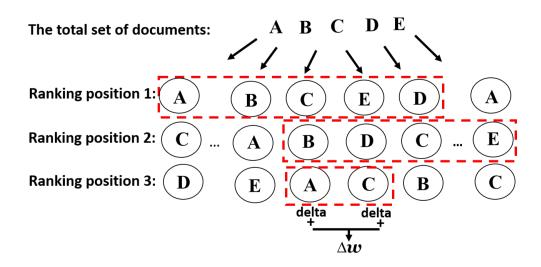

Figure 2.4: Computation process of Top-k ListNet

In order to deal with the high computational complexity, k = 1 was selected in [13]. Choosing k = 1 reduces the amount of computation dramatically, but it largely restricts the capability of ListNet. In fact, setting k = 1 converts the probabilities distributed over document permutations to the probabilities over individual documents. As explained in Section 2.3, the evaluation measure NDCG contains a position discount factor. Therefore, it is quite important to learn the position information conveyed by the scores of other documents in the permutation. However, Top-1 ListNet places distributions over documents, and ignores the rank information of sequences, which will lead to lose the information about permutations. Thus the effective-ness of the ListNet algorithm cannot be guaranteed. We therefore seek to extend the Top-1 approximation to Top-k ( $k \ge 2$ ) with an acceleration of computation.

We will introduce the Top-k ListNet algorithm in detail below, which will be the focus of the acceleration work in this thesis. In the training process of Top-k ListNet there are three steps:

- (1) Forward Propagation;

- (2) Loss Function;

- (3) Back Propagation.

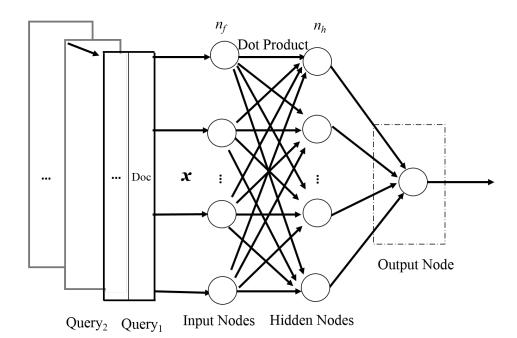

The first step is Forward Propagation (FP), as seen in Figure 2.4. In FP our ranking model uses a fully-connected 2-layer NN from [28], which has  $n_f$  inputs,  $n_h$  hidden units, and one output unit. The model parameters include the weights  $\boldsymbol{w}^{21}$  between the input layer and the hidden layer, the weights  $\boldsymbol{w}^{32}$  between hidden layer and output layer. For each query, the FP calculates the score  $s_i$ ,  $i = 1, ... n_d$  of each relevant document:

$$s_i = \text{Sigmoid}(\sum_{h=1}^{n_h} w_h \text{Sigmoid}(\sum_{f=1}^{n_f} w_{hf}^{21} x_{qif}))$$

(2.5)

Sigmoid function is historically deployed as the activation function, which takes a single number and squashes it into range between 0 and 1. Crucially, negative numbers saturate at 0 and positive numbers saturate at 1. Rectified Linear Unit (ReLU) is another option which drew wide attention recently as its linear computation, and it is cheap to implement on hardware. In order to keep consistent with previous ranking algorithms, we decide to choose Sigmoid function as the activation function.

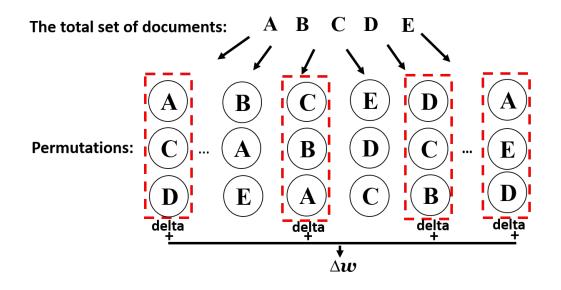

The second step is the Loss Function calculation, as seen in Figure 2.4. The set of all possible permutations of  $n_d$  documents for each query is denoted as  $G_{n_d}$ , the number of permutations in  $G_{n_d}$  is  $n_d$ !. A permutation  $\pi$  of  $G_{n_d}$  on the  $n_d$  documents is a bijection from  $\{1, 2, ..., n_d\}$  to itself, which is written as  $\pi = \langle \pi(1), \pi(2), ..., \pi(n_d) \rangle$ , where  $\pi(j)$  denotes the document assigned to position j. Top-k ListNet elaborates the permutations with k documents, so the number of permutations decreases to  $\frac{n_d!}{(n_d-k)!}$ ; we call the set of Top-k permutations  $G_{n_d}^k$ . The probability of permutation  $\pi$  is defined using the Top-k Plackett-Luce model [29]:

$$P(s, \pi) = \prod_{j=1}^{k} \frac{e^{s_{\pi(j)}}}{\sum_{i=j}^{n_d} e^{s_{\pi(i)}}}$$

(2.6)

where  $s_{\pi(j)}$  is the score of the document at position j (j = 1, 2, ..., k) in permutation  $\pi$ . In Equation (2.6), exponentiating the scores produces the probabilities, and the division performs the normalization so that the summation of all permutation probabilities equals to 1. Based on the probability Equation (2.6), given a list of scores, we can calculate the probability of each possible permutation. In order to make the Loss Function differentiable cross entropy is taken as the metric between two probability distributions over the document permutations, one derived from the ground truth permutation and the other derived from the model prediction, which means the Loss Function is calculated as:

$$L(\boldsymbol{y}, \boldsymbol{s}) = -\sum_{\forall \boldsymbol{\pi} \in \boldsymbol{G}_{\boldsymbol{n}_{\boldsymbol{d}}}^{\boldsymbol{k}}} P(\boldsymbol{y}, \boldsymbol{\pi}) \log(P(\boldsymbol{s}, \boldsymbol{\pi}))$$

(2.7)

The final step is Back Propagation (BP), as seen in Figure 2.4. We get the gradient of L with respect to the parameters  $\boldsymbol{w}^{21}$  and  $\boldsymbol{w}^{32}$  as:

$$\Delta w = \frac{\partial L(\boldsymbol{y}, \boldsymbol{s})}{\partial w} = -\sum_{\forall \boldsymbol{\pi} \in \boldsymbol{G}_{\boldsymbol{n_d}}^k} \frac{\partial P(\boldsymbol{s}, \boldsymbol{\pi})}{\partial w} \frac{P(\boldsymbol{y}, \boldsymbol{\pi})}{P(\boldsymbol{s}, \boldsymbol{\pi})}$$

(2.8)

Then we update the parameters of the ranking model over epochs using gradient descent under learning rate  $\eta$  [30]:

$$w' = w - \eta \Delta w \tag{2.9}$$

Note that learning rate  $\eta$  is the most important hyperparameter setting in the training process of NN algorithms. A small  $\eta$  makes very tiny progress and is not efficient. Conversely, a large  $\eta$  may not pay off. In practice, the learning rate is commonly decayed over time to improve the performance of NN training.

As mentioned earlier,  $n_d$  is above 1000 in general, so the computation of Loss Function and BP might be intractable with a large k due to the large number of permutations. For example, when k = 2, the scale of computation is order of  $10^9$ , and when k = 3, the scale becomes order of  $10^{12}$ , thus the training time of Top-k ListNet is rather slow when k > 1. For Top-k (k = 2) ListNet, it normally takes about 24 hours or more to get acceptable results. For Top-k (k = 3) ListNet, the calculation becomes intractable in practice. However, as the calculation is dominated by a summation over many permutations there is a potential for parallelism if we are able to restructure the algorithm correctly.

#### **Algorithm 1** Top-*k* ListNet

| 1:  | Input: number of epochs $n_{epoch}$ , number of hidden nodes $n_h$ , document features $\boldsymbol{x}$ , learning                                                                     |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | rate $\eta$                                                                                                                                                                            |

|     | Output: $\boldsymbol{w}^{21}, \boldsymbol{w}^{32}$                                                                                                                                     |

|     | Initialization: $\boldsymbol{w}^{21} = random(n_h, n_f), \ \boldsymbol{w}^{32} = random(n_h)$                                                                                          |

| 4:  | for $e = 1$ to $n_{epoch}$ do                                                                                                                                                          |

| 5:  | for $q = 1$ to $n_q$ do                                                                                                                                                                |

| 6:  | ▷ Forward Propagation                                                                                                                                                                  |

| 7:  | Initialization: $s^{32} = 0$ , $s = 0$                                                                                                                                                 |

| 8:  | for $i = 1$ to $n_d$ do                                                                                                                                                                |

| 9:  | for $h = 1$ to $n_h$ do                                                                                                                                                                |

| 10: | $\mathbf{for}_{f} f = 1 \text{ to } n_f \mathbf{do}$                                                                                                                                   |

| 11: | $m{s}_{ih}^{32} = m{s}_{ih}^{32} + m{w}_{hf}^{21} m{x}_{qif}$                                                                                                                          |

| 12: | end for                                                                                                                                                                                |

| 13: | $oldsymbol{s}_{ih}^{32} = \operatorname{Sigmoid}_{ih}(oldsymbol{s}_{ih}^{32})$                                                                                                         |

| 14: | $oldsymbol{s}_i = oldsymbol{s}_i + oldsymbol{w}_h^{32} oldsymbol{s}_{ih}^{32}$                                                                                                         |

| 15: | end for                                                                                                                                                                                |

| 16: | $oldsymbol{s}_i = \operatorname{Sigmoid}(oldsymbol{s}_i)$                                                                                                                              |

| 17: | end for $\mathbf{c}^{k}$                                                                                                                                                               |

| 18: | $\mathbf{while} \; oldsymbol{\pi} \in oldsymbol{G}_{n_d}^k \; \mathbf{do}$                                                                                                             |

| 19: | $\triangleright$ Loss Function                                                                                                                                                         |

| 20: | $P(\boldsymbol{y}, \boldsymbol{\pi}) = \prod_{j=1}^{k} rac{\exp(\boldsymbol{y}_{\pi(j)})}{\sum_{i=j}^{n_d} \exp(\boldsymbol{y}_{\pi(i)})}$                                            |

| 21: | $P(oldsymbol{s},oldsymbol{\pi}) = \prod_{j=1}^k rac{\exp(oldsymbol{s}_{\pi(j)})}{\sum_{i=j}^{n_d} \exp(oldsymbol{s}_{\pi(i)})}$                                                       |

| 22: | ▷ Back Propagation and Update Parameters                                                                                                                                               |

| 23: | for $h = 1$ to $n_h do$                                                                                                                                                                |

| 24: | $\Deltaoldsymbol{w}_h^{32}=-rac{\widetilde{\partial}P(oldsymbol{s},oldsymbol{\pi})}{\partialoldsymbol{w}_h^{32}}rac{P(oldsymbol{y},oldsymbol{\pi})}{P(oldsymbol{s},oldsymbol{\pi})}$ |

| 25: | $oldsymbol{w}_h^{32} = oldsymbol{w}_h^{32} - \eta \dot{\Delta} oldsymbol{w}_h^{32}$                                                                                                    |

| 26: | for $f = 1$ to $n_f$ do                                                                                                                                                                |

| 27: | $\Deltaoldsymbol{w}_{hf}^{21}=-rac{\partial P(oldsymbol{s},oldsymbol{\pi})}{\partialoldsymbol{w}_{hf}^{21}}rac{P(oldsymbol{y},oldsymbol{\pi})}{P(oldsymbol{s},oldsymbol{\pi})}$      |

| 28: | $oldsymbol{w}_{hf}^{21}=oldsymbol{w}_{hf}^{21}-\eta\Deltaoldsymbol{w}_{hf}^{21}$                                                                                                       |

| 29: | end for                                                                                                                                                                                |

| 30: | end for                                                                                                                                                                                |

| 31: | end while                                                                                                                                                                              |

| 32: | end for                                                                                                                                                                                |

| 33: | end for                                                                                                                                                                                |

|     |                                                                                                                                                                                        |

In this research, we use a single benchmark data set – LETOR 4.0. This is because LETOR 4.0 is the only training set where the ground truth is labeled as a permutation for a query. As the Loss Function of listwise approach is based the permutation probabilities, LETOR 4.0 allows to apply listwise algorithms directly. In addition, our target is developing techniques to accelerate the learning process rather than improving the model accuracy. One data set is enough to verify the effectiveness of proposed techniques, so our experiments are developed on

LETOR 4.0.

## 2.5 Related Work

From the analysis above, we can see the calculation of Top-k ListNet algorithm is quite different from that of the pointwise and pairwise approaches. While considering just singles or pairs has much lower cost, it is difficult to derive the positions of documents in the final ranked list. Ultimately, ranking is about learning a complete ordering on documents, so we can expect a large accuracy gap between traditional approaches and the listwise approach. Top-k ListNet uses permutations of documents as instances in learning, and the positions of documents in the final ranking result are visible. This makes the listwise approach more accordance with the ranking task than other two approaches. Note that there are in total  $\frac{n_d!}{(n_d-k)!}$  elements in the permutation class for each query. In addition, the computational complexity of permutation probability for Top-k ListNet is  $O(n_d)$ , which is much more complex than regressing one singe document into a concrete value in the pointwise approach or classifying document pairs into two categories in the pairwise approach. In order to address the high computational complexity of the Top-k ListNet algorithm, we investigate optimisations on both software (reducing computational complexity) and hardware (accelerating computation speed).

#### 2.5.1 Algorithm Optimisation