#### Imperial College London Department of Computing

# Dynamic Analysis for Concurrent Modern C/C++ Applications

Christopher David Lidbury

May 2019

Submitted in part fulfilment of the requirements for the degree of Doctor of Philosophy in Computing of Imperial College London and the Diploma of Imperial College London

## Declaration

This thesis and the work it presents are my own except where otherwise acknowledged.

Christopher David Lidbury

The copyright of this thesis rests with the author and is made available under a Creative Commons Attribution Non-Commercial No Derivatives licence. Researchers are free to copy, distribute or transmit the thesis on the condition that they attribute it, that they do not use it for commercial purposes and that they do not alter, transform or build upon it. For any reuse or redistribution, researchers must make clear to others the licence terms of this work.

### Abstract

Concurrent programs are executed by multiple threads that run simultaneously. While this allows programs to run more efficiently by utilising multiple processors, it brings with it numerous complications. For example, a program may behave unpredictably or erroneously when multiple threads modify the same memory location in an uncoordinated manner. Issues such as this are difficult to avoid, and when introduced, can break the program in unpredictable ways. Programmers will therefore often turn towards automated tools to aide in the detection of concurrency bugs.

The work presented in this thesis aims to provide methods to aid in the creation of tools for the purpose of finding and explaining concurrency bugs. In particular, the following studies have been conducted:

Dynamic Race Detection for C/C++11 With the introduction of a weak memory model in C++, many tools that provide dynamic race detection have become outdated, and are unable to adequately identify data races. This work updates an existing data race detection algorithm such that it can identify data races according to this new definition. A method for allowing programs to explore many of the weak behaviours that this new memory model permits is also provided.

Record and Replay Much work has gone into record and replay, however, most of this work is focussed on *whole system* replay, whereby a tool will aim to record as much of the program execution as possible. Contrasting this, the work presented here aims to record as *little as* possible. This *sparse* approach has many interesting implications: some programs that were previously out of reach for record and reply become tractable, and vice versa. To back this up, controlled scheduling is introduced that is capable of applying different scheduling strategies, which combined with the record and replay is beneficial for helping to root out bugs.

**Tool Support** Both of the above techniques have been implemented in a tool, tsan11rec, that builds on the tsan dynamic race detection tool. A large experimental evaluation is presented investigating the effectiveness of the enhanced data race detection algorithm when applied to the Firefox and Chromium web browsers, and of the novel approach to record and replay when applied to a diverse set of concurrent applications.

## Contents

| 1 | Intr | roduction                                     | 12        |

|---|------|-----------------------------------------------|-----------|

|   | 1.1  | Current Issues                                | 13        |

|   | 1.2  | Contributions                                 | 13        |

|   | 1.3  | Publications                                  | 14        |

|   | 1.4  | Acknowledgements                              | 14        |

| 2 | Bac  | kground                                       | <b>15</b> |

|   | 2.1  | Multi-Threaded Programs                       | 15        |

|   | 2.2  | Memory Models                                 | 17        |

|   | 2.3  | Program Analysis                              | 20        |

| 3 | Dyr  | namic Race Detection for C/C++11              | 24        |

|   | 3.1  | C/C++11 Memory Model                          | 26        |

|   | 3.2  | Dynamic Race Detection                        | 34        |

|   | 3.3  | Data Race Detection for C++11                 | 36        |

|   |      | 3.3.1 Release Sequences                       | 36        |

|   |      | 3.3.2 Fences                                  | 40        |

|   |      | 3.3.3 Algorithm                               | 41        |

|   | 3.4  | Exploring Weak Behaviours                     | 43        |

|   |      | 3.4.1 Post-Store Buffering                    | 44        |

|   |      | 3.4.2 Consistent Modification Order (§PR6.17) | 45        |

|   |      | 3.4.3 Consistent SC Order (§PR6.16)           | 45        |

|   |      | 3.4.4 Consistent Reads From Mapping (§PR6.19) | 46        |

|   | 3.5  | Operational Model                             | 51        |

|   |      | 3.5.1 Programming Language Syntax             | 51        |

|   |      | 3.5.2 Operational Model Formalised            | 52        |

|   |      | 3.5.3 Operational Semantics                   | 53        |

|   | 3.6  | Characterising The Model Axiomatically        | 55        |

|   |      | 3.6.1 Lifting Traces                          | 58        |

|   |      | 3.6.2 Restricted Axiomatic Model              | 59        |

|   |     | 3.6.3 Equivalence of Operational and Axiomatic Models 6          | 0 |

|---|-----|------------------------------------------------------------------|---|

|   | 3.7 | Related Work                                                     | 1 |

|   | 3.8 | Summary                                                          | 3 |

| 4 | Spa | rse Record and Replay with Controlled Scheduling 6               | 4 |

|   | 4.1 | Controlled Scheduling                                            | 6 |

|   | 4.2 | Record and Replay                                                | 7 |

|   | 4.3 | Scheduling Protocol                                              | 9 |

|   |     | 4.3.1 Protocol Details                                           | 0 |

|   |     | 4.3.2 Special Cases                                              | 1 |

|   |     | 4.3.3 Liveness                                                   | 5 |

|   | 4.4 | Sparse Record and Replay                                         | 6 |

|   |     | 4.4.1 Motivating Example                                         | 7 |

|   |     | 4.4.2 Interleaving                                               | 8 |

|   |     | 4.4.3 Signals                                                    | 9 |

|   |     | 4.4.4 System Calls                                               | 9 |

|   |     | 4.4.5 Asynchronous Events                                        | 3 |

|   | 4.5 | Related Work                                                     | 4 |

|   | 4.6 | Summary                                                          | 7 |

| 5 | Ext | ending ThreadSanitizer 8                                         | 8 |

|   | 5.1 | ThreadSanitizer                                                  | 8 |

|   | 5.2 | Implementation of C++11 Data Race Detection                      | 0 |

|   |     | 5.2.1 The tsan11 Tool                                            | 1 |

|   |     | 5.2.2 Evaluation Using Benchmark Programs                        | 2 |

|   |     | 5.2.3 Evaluation Using Large Applications                        | 6 |

|   | 5.3 | Implementation of Controlled Scheduling With Record and Replay 9 | 9 |

|   |     | 5.3.1 The tsan11rec Tool                                         | 9 |

|   |     | 5.3.2 Experimental Overview                                      | 0 |

|   |     | 5.3.3 CDSchecker Litmus Tests                                    | 1 |

|   |     | 5.3.4 httpd                                                      | 4 |

|   |     | 5.3.5 PARSEC and pbzip                                           | 5 |

|   |     | 5.3.6 SDL-based Games                                            | 8 |

|   |     | 5.3.7 Limitations: SQLite and SpiderMonkey                       | 0 |

|   | 5.4 | Summary                                                          | 0 |

| 6  | Con   | clusion 1          | 12  |

|----|-------|--------------------|-----|

|    | 6.1   | Thesis Reflections | .12 |

|    | 6.2   | Future Work        | .13 |

|    | 6.3   | Summary            | .14 |

| Bi | bliog | raphy 1            | 14  |

# List of Tables

| 2.1 | Differences between static and dynamic analysis                                   | 21  |

|-----|-----------------------------------------------------------------------------------|-----|

| 5.1 | Comparison of CDSChecker, tsan11 and tsan03; all times reported are in ms.        | 95  |

| 5.2 | Memory usage, runtime and number of races reported for the browser con-           |     |

|     | figurations running on JSBench                                                    | 97  |

| 5.3 | The number of atomic operations executed by the browsers during a com-            |     |

|     | plete JSBench run, with a breakdown according to operation type and memory order. | 98  |

| 5.4 | Comparison over CDSchecker benchmarks between tsan + rr, tsan11 and               | 30  |

| 0.4 | tsan11rec with controlled random and queue scheduling. Each benchmark             |     |

|     |                                                                                   |     |

|     | was executed 1000 times in each mode. The "Time" columns shows the                |     |

|     | mean execution time (ms) and standard deviation (in parentheses). The             |     |

|     | "Rate" column shows the proportion of runs that exhibited data races              | 103 |

| 5.5 | Comparison of throughput and race rate between native, tsan11, rr and             |     |

|     | tsan11rec for Apache's httpd. Results are averaged over 10 runs. "Through-        |     |

|     | put" shows mean throughput in queries per second, "Rate" is the number            |     |

|     | of races detected per run (where relevant). Standard deviations are shown         |     |

|     | (in parentheses). Overhead is computed relative top native throughput 1           | 106 |

| 5.6 | Execution times (s) for tool configurations across the pbzip and PARSEC           |     |

| 0.0 | benchmarks, averaged across 10 runs. Standard deviation is shown (in              |     |

|     | •                                                                                 |     |

|     | parentheses)                                                                      | ٠07 |

| 5.7 | Overhead compared with native execution for tool configurations across the        |     |

|     | pbzip and PARSEC benchmarks, computed from the results of Table 5.6 1             | 107 |

# List of Figures

| 2.1 | Multiple threads perform a summation over disjoint sets of data concur-                   |    |

|-----|-------------------------------------------------------------------------------------------|----|

|     | rently, providing a linear speed-up over a single-threaded approach                       | 16 |

| 2.2 | The audio playback has a dedicated thread. The main thread does not need                  |    |

|     | to think about it, and the audio will be responsive                                       | 16 |

| 2.3 | Simple parallel program, showing one of the possible ways in which it can                 |    |

|     | run on hardware                                                                           | 18 |

| 2.4 | The diagram on the right shows how a barrier prevents memory operations                   |    |

|     | from shifting over it                                                                     | 19 |

| 2.5 | Barrier synchronisation. The operations before the barrier on CPU1 become                 |    |

|     | visible to those after the barrier on CPU2                                                | 19 |

| 2.6 | Finding the nth number in an unordered sequence of numbers                                | 21 |

| 2.7 | Knowledge about the program is gradually built up while processing the                    |    |

|     | lines of the program. When nums is accessed, the possible range of indexes                |    |

|     | is out of the range of the array                                                          | 22 |

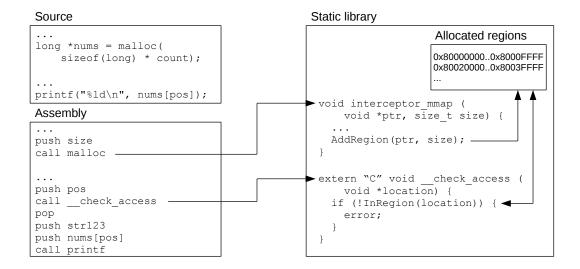

| 2.8 | A static library is bundled with the executable, which is called into at                  |    |

|     | certain points in the program. This library keeps track of all valid memory               |    |

|     | regions and ensures all memory accesses are valid                                         | 22 |

| 3.1 | Simple racy C++11 program                                                                 | 29 |

| 3.2 | Pre-execution, witness and derived relations for the program in Listing 2.1.              | 30 |

| 3.3 | A candidate execution for the pre-execution of Figure 3.2a. The modifica-                 |    |

|     | tion order will prevent this from being allowed by the $C/C++11$ memory                   |    |

|     | model                                                                                     | 31 |

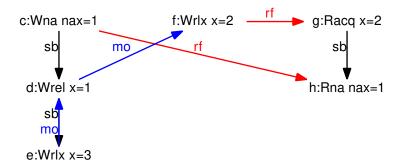

| 3.4 | The release sequence headed by $d$ is blocked by event $f$ , causing a data race          |    |

|     | between $c$ , the non-atomic write to $\mathbf{nax}$ , and $h$ , the non-atomic read from |    |

|     | $\mathbf{nax}$ ; if the blocking event $f$ is removed, there is no race                   | 32 |

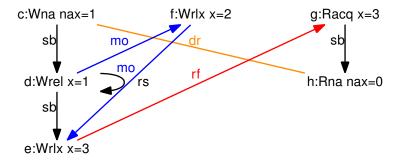

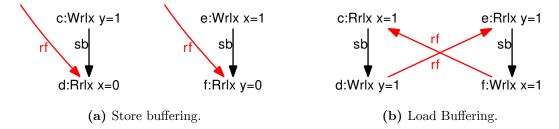

| 3.5 | Example executions showing some of the common weak behaviours allowed                     |    |

|     | by the $C/C++11$ memory model                                                             | 34 |

| 3.6  | The write from T2 can cause T1 to fail to synchronise with T3, resulting in a data race on nax; tsan cannot detect the race | 35  |

|------|-----------------------------------------------------------------------------------------------------------------------------|-----|

| 97   | ,                                                                                                                           | Je  |

| 3.7  | Trace of the program in Figure 3.6, showing the value of the VCs after each                                                 |     |

|      | statement. Only updated values are shown, and those where race detection                                                    | 26  |

| 9.0  | checks are performed.                                                                                                       | 36  |

| 3.8  | Trace of the program in Figure 3.6, showing the value of the VCs after each                                                 |     |

|      | statement. Only updated values are shown, and those where race detection                                                    |     |

|      | checks are performed. Blue updates show those that differ from the sketch                                                   | 0.5 |

| 0.0  | of Fig.3.7                                                                                                                  | 37  |

| 3.9  | The release sequence started by $d$ and continued by $e$ is blocked by $f$ ; thus                                           | 0.0 |

| 2.40 | d does not synchronise with $g$ , so $c$ races with $h$                                                                     | 38  |

| 3.10 | Trace of the program in Figure 3.9, showing the value of the VCs after each                                                 |     |

|      | statement. Only updated values are shown, and those where race detection                                                    |     |

|      | checks are performed                                                                                                        | 39  |

|      | Synchronisation caused by fences                                                                                            | 40  |

| 3.12 | Semantics for tracking the happens-before relation with loads, stores, RMWs                                                 |     |

|      | and fences                                                                                                                  | 42  |

|      | Construction of a program execution                                                                                         | 46  |

| 3.14 | Inconsistent execution fragment caused by lack of CoRR                                                                      | 48  |

| 3.15 | Consistency of $sc$ -reads only forbids $d$ reading from $b$                                                                | 49  |

| 3.16 | Visible side effects and visible sequence of side effects                                                                   | 50  |

|      | Syntax for the core language                                                                                                |     |

| 3.18 | Operational State                                                                                                           | 54  |

| 3.19 | Semantics for atomic statements                                                                                             | 56  |

| 3.20 | Semantics for sequentially consistent fence functions                                                                       | 57  |

| 3.21 | Interface from operational model to VC algorithm of Figure 3.12. The                                                        |     |

|      | [LOAD] operation is slightly different, as $a$ is a store element. For the                                                  |     |

|      | [FENCE] operation, the $\Sigma$ and $a$ parameters are omitted, and $\mathbb{C}$ , $\mathbb{L}$ and $\mathbb{V}$            |     |

|      | will be empty                                                                                                               | 58  |

| 3.22 | Construction of the reads-from set $\dots \dots \dots \dots \dots \dots$                                                    | 58  |

| 3.23 | Visual representation of the proof of equivalence between program traces                                                    |     |

|      | and executions                                                                                                              | 61  |

| 4.1  | A racy C++11 program using atomic operations                                                                                | 67  |

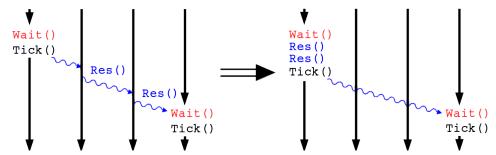

| 4.2  | Generic client for processing and returning requests sent from some server.                                                 | 68  |

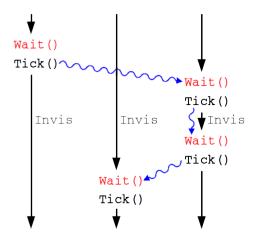

| 4.3  | Sequentialised critical sections and parallel invisible operations. Blue wavy |

|------|-------------------------------------------------------------------------------|

|      | arrows represent scheduler-imposed ordering; black arrows represent pro-      |

|      | gram order                                                                    |

| 4.4  | Instrumented mutex lock. The real lock function is called inside a trylock    |

|      | loop, where each lock attempt is a separate critical section                  |

| 4.5  | Instrumented conditional wait. When the thread has released the mutex         |

|      | and entered the intercepted mutex lock function, it will block waiting to be  |

|      | signalled and reacquire the lock                                              |

| 4.6  | Printing nax is semantically possible, and therefore the program contains a   |

|      | data race. But by preserving the liveness of the program, the racy execution  |

|      | will be very unlikely to occur                                                |

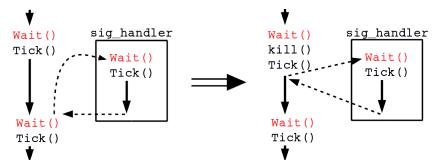

| 4.7  | Signals are replayed immediately after the preceding tick                     |

| 4.8  | Record and replay setup for bind                                              |

| 4.9  | Record and replay setup for poll                                              |

| 4.10 | Right diagram shows how reschedules on the left are floated above the         |

|      | preceding Tick()                                                              |

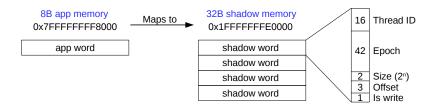

| 5.1  | Each 8 bytes of application memory maps to 32 bytes of shadow memory,         |

|      | which contains 4 shadow words. Each shadow word stores information on         |

|      | a single access. The information stored in the shadow word is enough to       |

|      | determine if two accesses form a data race                                    |

| 5.2  | Interception for syscall recv. The user call to recv will instead callin-     |

|      | terceptor_recv, which in turn will call the scheduler function for recv       |

|      | after the real syscall                                                        |

### 1 Introduction

Linux introduced the notion of threads in C with *pthreads* [NBF96] 1996. But it wasn't until fifteen years later in 2011 that C formally adopted threads with C11 [ISO11b]. Most modern languages provide some form of support for multi-threading, including Java [GPB+06] and Go [go]. Hardware has also become very accommodating of threads, with many multi-core processors providing low level caches shared between threads, through which data can be shared, and hardware barriers to communicate. Multi-threading has therefore become commonplace, with many programs utilising it in some form, even indirectly through the use of a library.

The introduction of multi-threading has provided many benefits to programmers with regards to program speed, structure and many others aspects; however, it also introduces a number of pitfalls, which ultimately makes multi-threaded programming very difficult to do correctly. For a single-threaded program, program bugs will depend on the program code and how the program interacts with the environment, such as the file system or network. With multiple threads, the order in which they execute becomes a major source of nondeterminism, and so one must also consider how they communicate and modify parts of the program state. If two threads modify, for example, the same data structure, it may end up in an undefined state. Attempting to debug such programs is also more difficult. Running the same program twice and ensuring the relevant program environment and inputs are the same on both runs will not ensure that the program will follow the same sequence of states. In these cases, traditional debugging methods such as pausing a program with a debugger will not be enough, as there will be no clear indication as to how the program became in such a state.

Perhaps the most defining type of bug that arises with multi-threading is the *data race*, typically defined as follows: A data race occurs between two threads when both access the same location, at least one is a write, at least one is *non-atomic*, and neither happens before the other [Lam78]. But without any formalisation, what are "atomic accesses" and "happens-before"? Before C11, happens-before was assumed to occur primarily between the lock and unlock operations on mutexes, between a parent and child thread upon thread creation and joining, and between operations in the same thread according to program

order. It was also assumed that lock operations were atomic. From this grew the lock-based approach to multi-threading, where everything that could be accessed by multiple threads was guarded by some form of lock. Atomics were introduced with C11 that can be accessed by multiple threads without the need for locks, but are also more difficult to use, as there is no longer a region of code that is mutually exclusive.

To help fix these issues, programmers may use a *program analyser*. An analyser will capture and infer properties of the program in an attempt to inform the user of particular deficiencies in the program. There are many different kinds of analysers, that focus on different deficiencies and use different methods of approach. For example, the Address-Sanitizer [HH12] tool will analyse a program, while it is running, and inform the user of any address violations detected. This of course means that it will only detect address violations, and only if they occur during that particular execution.

#### 1.1 Current Issues

The current state of concurrent programming has become unclear. While program analysers, libraries, research and understanding on the pitfalls of concurrent programming have come a long way, it has become muddled by the introduction of complicated memory models and the plethora of different models that different hardware and languages specify.

In the particular case of program analysers, while research continues to be performed on improving the efficiency and their ability to detect data races according to some arbitrary and simple definition of a data race, none of this research addresses the issue of the increased complexity of the memory models embedded in the languages, or helping the user to understand what is wrong with their program.

#### 1.2 Contributions

In light of the issues raised above, this work focuses on three important issues:

Dynamic race detection for C11/C++11 (§3) focuses on the detection of data races in the presence of a weak memory model, specifically, C11/C++11. It does so by updating the traditional vector clock algorithm [FF09] to be aware of the nuances of the C11/C++11 memory model. It also allows the exploration of some of the weak behaviours permitted by C11/C++11, something that was previously restricted to static analysers due to the perceived difficulties.

Controlled scheduling with sparse record and replay (§4) attempts to solve the issue of both finding and reproducing difficult to find data races. It does so by introducing a method of controlled scheduling that works in tandem with a record and replay system. This takes a sparse approach to record and replay, where instead of recording as much as possible, it tries to record as little as possible.

ThreadSanitizer §5 details the implementation of the two previous contributions as an extension of ThreadSanitizer (tsan), a state of the art dynamic race detection tool. An extensive evaluation of the tool is provided, showing that it can scale to large applications and can both find and reproduce bugs. These applications range from small litmus tests, to large programs such as popular web browsers, and real-time applications such as videogames.

#### 1.3 Publications

The material presented in this thesis has been published as follows:

Dynamic race detection for C++11 The dynamic race detection work of §3, and its implementation and evaluation in §5.2, have been published in the 2017 ACM SIGPLAN conference on Principles of Programming Language (POPL 2017) [LD17b]. This work has an approved artifact and a companion website which can be found online [LD17a].

Sparse Record and Replay With Controlled Scheduling The controlled scheduling and record and replay work of §4, and its implementation and evaluation in §5.3, have been accepted and is to appear in the 2019 ACM SIGPLAN conference on Programming Language Design and Implementation (PLDI 2019). A reference to a draft is provided [LD].

#### 1.4 Acknowledgements

The author acknowledges and is grateful to the collaborators throughout this PhD. In particular Alastair Donaldson, who co-authored and contributed to the prose in all of the work presented in this thesis. Additional acknowledgements are given to John Wickerson and Mark Batty for help on understanding the technical aspects of the C++11 memory model, and on the presentation of the paper "Dynamic race detection for C++11" [LD17b].

## 2 Background

#### 2.1 Multi-Threaded Programs

Multi-threaded programming allows programs to be executed with multiple threads of execution. In C++11, threads are created explicitly with the std::thread class, by passing in a function pointer. This function becomes the main function for the thread. An example program is shown in Figure 2.1, whereby the main thread constructs two threads t1 and t2, passing in the Summation function as the entry point and a pointer to the data that needs summing. The join operation will cause the thread invoking it to block until the specified child thread has finished. Each thread may run on two separate processors concurrently, in theory doubling the speed over using a single thread. In practice, the overhead of thread creation and completion will result in diminishing returns for fixed-size data with the increase in thread count [Rod85].

Another example program is shown in Figure 2.2. The audio subsystem has been given its own dedicated thread, tasked with consolidating all sound samples being played, mixing them together and then sending the mixed sample to the audio device. Other threads do not need to be concerned with playing back the audio with the correct timing, simplifying them. The responsiveness of the audio will be improved, as the audio thread cannot be busy working on other parts of the program.

In both examples, certain steps are taken to ensure correctness in how the threads interact. In the audio example, access to samples\_pending is guarded by a mutex. Mutexes ensure mutually exclusive access to parts of the process memory space. In this case, if a thread is in PlaySample and has acquired the mutex, the audio thread must wait until the mutex is freed before it can acquire it and move past the mutex acquire. Mutual exclusion is a common tool used in concurrent programs, but has the drawback that only one thread may be running inside a mutex-protected region at a time.

The summation example uses an atomic variable instead. Under most circumstances, variables are *not* safe to access concurrently. Atomics, however, are safe to use without the guarantee of mutual exclusion, so in this case, there is no issue with total. The benefit of this is that there is no need for mutual exclusion, and therefore threads are left to run

```

const size_t kDataCount = 1024;

int data[kDataCount];

std::atomic<int> total(0);

void Summation(const int *data, size_t count) {

int total = 0;

for (size_t idx = 0; idx < count; ++idx) {</pre>

total += data[idx];

::total += total;

int main(int argc, char **arv) {

FillData():

std::thread t1(Summation, &data[0 * kDataCount / 2], kDataCount / 2);

std::thread t2(Summation, &data[1 * kDataCount / 2], kDataCount / 2);

t1.join();

t2.join();

std::cout << "Total: " << total << std::endl;</pre>

return 0;

```

**Figure 2.1:** Multiple threads perform a summation over disjoint sets of data concurrently, providing a linear speed-up over a single-threaded approach.

```

std::list<const SoundSample&> samples_pending;

std::list<const SoundSample&> samples_active;

std::mutex audio_mtx;

void RunAudio() {

InitAudio();

while (!shutdown) {

SoundSample mixed_sample = MixSamples(samples_active);

SendAudio(mixed_sample);

std::this_thread::sleep_for(std::chrono::milliseconds(10));

std::unique_lock<std::mutex> lck(audio_mtx);

samples_active.splice(samples_active.end(), samples_pending);

}

void PlaySample(const SoundSample& sample) {

std::unique_lock<std::mutex> lck(audio_mtx);

samples_pending.push_back(sample);

int main(int argc, char **arv) {

std::thread audio_thread(RunAudio);

if (weapon_fired) {

PlaySample(weapon_sample);

audio_thread.join();

return 0;

```

**Figure 2.2:** The audio playback has a dedicated thread. The main thread does not need to think about it, and the audio will be responsive.

in parallel.

In these examples, the programmer has taken the necessary precautions to ensure that there are no adverse effects caused by the multi-threaded approach. Sometimes these precautions are not enough, and the program can fail in strange ways. Consider the Summation function in Figure 2.1, specifically the line ::total += total;. For atomic locations, the += is an atomic read-modify-write, it performs the load, addition and store as a single, irreducible operation. If this line is instead ::total = ::total + total;, the load, addition and store will be three separate operations. Two threads could then load the original value of total in parallel, without seeing the updated value from the other thread. The resulting value would then be incorrect.

Now consider the audio example of Figure 2.2, and imagine someone has added functionality for stopping samples that are currently being played, that looks as follows:

```

void StopSample(const SoundSample& sample) {

samples_active.remove(sample);

}

```

Said person has clearly forgotten to acquire the mutex first. The effects of this error is not clear, for example, the list may become corrupt and the program may crash as a result, the function may fail to stop the sample from playing, or, most likely, the program will appear to continue as expected. One of the major problems with concurrency bugs is their tendency to appear rarely and unpredictably, and so they are often colloquially known as heisenbugs [MQB<sup>+</sup>08].

Concurrent programming has undergone much work, with many programming constructs being created specifically for use in multi-threaded programs, such as condition variables, monitors, and even data structures specifically designed to be safely accessed by multiple threads. But even with these constructs, the extra complications that come with inter-thread interactions will still result in subtle bugs [ND13, BAM07].

#### 2.2 Memory Models

The examples shown in Figures 2.1 and 2.2 provide two distinct methods of multi-threaded interaction: the well established method of using mutual exclusion and the more modern approach of using atomics. While the atomic approach avoids the need to block threads, it has many nuances that must be formalised through the use of a *memory model*. To see why this is necessary, a closer look at the hardware is required.

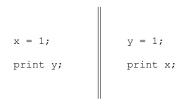

Consider the simple abstract program fragment shown in Figure 2.3a. Each thread writes to one of x and y before reading the other in parallel. Assume that all accesses

- (a) Two threads write to and read from x and y. The vertical bars represent separate threads running in parallel.

- (b) The CPUs do not communicate directly with memory, and may read older values from the cache or leave stores in the cache.

**Figure 2.3:** Simple parallel program, showing one of the possible ways in which it can run on hardware.

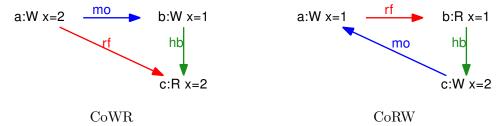

are atomic, and therefore safe. A common assumption will be that there is a sequentially consistent ordering over all of the operations. For example, one execution may be x=1; y=1; print x; print y;, and so the program will output 1 1. Under sequential consistency, the program should never output 0 0. These assumptions do not hold in reality though, and it is possible for the program to output 0 0, depending on the hardware and compiler. One such way is shown in Figure 2.3b, whereby each store is kept in the CPU's cache causing each load to see the initial value in memory. Given the typical hardware setup of Figure 2.3b, enforcing sequential consistency over all threads will in fact be more tricky and expensive than going without. Other ways in which this can happen include the compiler reordering operations, or the CPU executing operations out-of-order, a common feature in modern CPUs.

Under a single processor, how memory operations interact is mostly unambiguous. With multiple processors, the state of the system can become unspecified, particularly if the memory operations are non-atomic. The role of a hardware memory model is to specify the behaviour of memory operations, such as how they interact and how they are ordered.

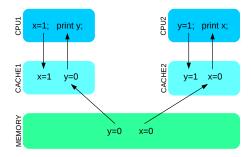

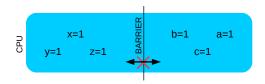

From Figure 2.3, it is clear that without some way to order memory operations, the values a load can read will be mostly unconstrained, which is particularly problematic when considering the locking example of Figure 2.2. One common solution is to use *memory barriers* (also known as memory fences), to prevent the memory operations from being reordered beyond certain points. An example of how memory barriers prevent reorderings is shown in Figure 2.4. This barrier will not prevent the operations on either side of the barrier from being reordered amongst themselves however. Different types of hardware

```

x=1; y=1; z=1;

__sync_synchronize();

a=1; b=1; c=1;

```

- (a) Memory stores separated by a GCC builtin barrier, which will compile into a hardware barrier.

- (b) Barrier prevents memory operations from shifting across it, but does not prevent other reorderings.

**Figure 2.4:** The diagram on the right shows how a barrier prevents memory operations from shifting over it.

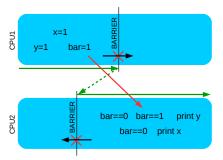

- (a) Synchronisation between release and acquire barriers.

- (b) The green arrow represents visibility, or happens before. It crosses the thread boundary thanks to barrier synchronisation.

Figure 2.5: Barrier synchronisation. The operations before the barrier on CPU1 become visible to those after the barrier on CPU2.

will have their own variations of barriers, which will be defined by the underlying memory model.

For interthread ordering, which is crucial for the locking example in Figure 2.2 to work, barriers must connect across threads. Most hardware will provide two kinds of barriers: a release barrier, which will prevent reordering past it, and an acquire barrier, which will prevent reordering before it. A barrier can also be both, such as the one shown in Figure 2.4b. Release barriers synchronise with acquire barriers, causing everything ordered before the release barrier to become visible to everything ordered after the acquire barrier. For this to work, the barrier is usually coupled with a memory access, and requires one memory access to read from another. An example is shown in Figure 2.5. When the load on bar reads from the store by CPU1, represented by the red arrow, the barriers synchronise, and so CPU2 can safely access x and y.

While most hardware memory models share the same basic principles, trying to cater for all of them in a high level programming language such as C++ or Java would be difficult. These languages that provide support for concurrency will therefore also provide their own software memory model, to bridge the gap between the program and the hardware, and to provide a single unified memory model which the programmer can program against. It is the responsibility of the compiler, that implements a language specification, to ensure that whatever code gets generated to run on hardware respects the underlying software memory model of the language.

#### 2.3 Program Analysis

With the complexity of programs increasing over time, so too does the complexity of the bugs they exhibit. Many programs will have bugs that are too contrived to detect manually and too difficult to fix by hand. The process of finding and explaining bugs autonomously through the use of program analysis can therefore be beneficial.

Broadly speaking, program analysers come in two forms, static and dynamic, as depicted in Table 2.1. A static analyser will work on the source program, while a dynamic analyser runs alongside the program, collecting information while it is running. Both kinds of analysis have a precision-scalability trade-off. Some cheap static analysers will scale really well, but only check simple properties (e.g. C Lint [Dar96]) or have a high false positive rate (e.g. FindBugs [HP07]), while others are much more detailed but do not scale (e.g. CDSChecker [ND13]). Dynamic analysers typically incur a linear increase in execution time, but the slowdown varies depending on the nature of the analysis. Dynamic analysis can almost never be used to prove absence of bugs, as they will typically only explore single executions, but bug reports will usually be accurate. Static analysers can be complete, but can also produce bug reports that are imprecise or are not even an issue, or if they are, it might not be clear how to reproduce them.

To demonstrate how these analyses work in practise, and the practical differences between the two, consider a static and dynamic analyser that can detect invalid memory accesses, that will be applied to the program of Figure 2.6. This program reads in a vector of numbers, sorts them, and then prints the nth number, specified by the first user argument. Assume that the parse\_numbers function will correctly parse each number and exit the program if there is an invalid number provided.

An example run of a static analyser is shown in Figure 2.7. This particular analyser aims to construct a knowledge base of the program in question, using it to identify semantic errors such as memory access violations. The knowledge base of the program starts off

| Static analysis                              | Dynamic analysis                            |

|----------------------------------------------|---------------------------------------------|

| Analyses the codebase, without execution.    | Collects and analyses as the program is ex- |

|                                              | ecuting.                                    |

| Collects information on all possible execu-  | Only collects information on a single exe-  |

| tions.                                       | cution.                                     |

| Generally works on small programs (<200      | Scales up to very large programs.           |

| LOC), but can scale very well (e.g. for type |                                             |

| checkers, linters).                          |                                             |

| Runs as its own executable, applied to the   | Requires instrumentation of the original    |

| source or executable for the codebase of     | program, with a static library bundled      |

| interest                                     | with the executable.                        |

Table 2.1: Differences between static and dynamic analysis.

```

int main(int argc, char **argv) {

if (argc < 3) {

return 1;

}

size_t count = argc - 2;

long pos = strtol(argv[1], NULL, 10);

long *nums = malloc(sizeof(long) * count);

parse_numbers(&argv[2], count, nums);

qsort(nums, count, sizeof(long), compare);

if (pos < 0 || pos > count) {

return 1;

}

printf("%ld\n", nums[pos]);

return 0;

}

```

**Figure 2.6:** Finding the nth number in an unordered sequence of numbers.

empty, and is gradually added to upon processing each line. When the print statement is reached, it deduces that the range of potential indexes into nums can be invalid, as the program permits the index to equal count. This knowledge base can become complex when loops and functions are also included.

An example of a dynamic analysis is shown in Figure 2.8. Here the program is instrumented by calling into a library at certain points in the program execution, which keeps track of certain parts of the program's state. These library calls can be added to the relevant lines in the program by the compiler automatically, removing the need for the user to modify the program manually. In this case, only events that occur during a particular execution can be analysed.

```

argc >= 3

if (argc < 3) {-

count = argc - 2, count >= 1

return 1:

pos >= LONG_MIN, pos <= LONG_MAX

size t count = argc - 2;-

long pos = strtol(argv[1], NULL, 10);-

nums.length = count, nums.length = argc - 2

long *nums = malloc(

nums.length >= 1

sizeof(long) * count);-

nums.range = [0..count - 1]

if (pos < 0 || pos > count) {-

pos >= 0, pos <= count

return 1;

nums.access[pos]

printf("%ld\n", nums[pos]);—

nums.access[0..count]

```

**Figure 2.7:** Knowledge about the program is gradually built up while processing the lines of the program. When nums is accessed, the possible range of indexes is out of the range of the array.

**Figure 2.8:** A static library is bundled with the executable, which is called into at certain points in the program. This library keeps track of all valid memory regions and ensures all memory accesses are valid.

Many tools exist that can perform program analysis to detect memory violations. A couple of the most widely used analysers are AddressSanitizer [SBPV12] and MemorySanitizer [SS15], two dynamic analysers built into LLVM.

## 3 Dynamic Race Detection for C/C++11

With the introduction of threads of execution as a first-class language construct, the C/C++11 standards give a detailed memory model for concurrent programs [ISO11b, ISO11a]. A principal feature of this memory model is the notion of a data race, and that a program exhibiting a data race has undefined semantics. As a result, it is important for programmers writing multi-threaded programs to take care to avoid data races.

Prior to the introduction of this memory model, the provision of threads was system and compiler dependent, and the definition of a data race was informal but commonly agreed upon. This lead to much work being created on the detection of data races in C/C++ programs, and other languages such as Java.

Despite the introduction of a formal definition of a data race, much of the work on data race detection for C/C++11 programs is still created with the old informal definition in mind. The most significant reason for this is that the definition of a data race in C++11 is far from trivial, due to the complex rules for when synchronisation occurs between the various atomic operations provided by the language, and the memory orders with which atomic operations are annotated.

Another subtlety of this new memory model is the reads-from relation, which specifies the values that can be observed by an atomic load. This relation can lead to nonsequentially consistent (SC) behaviours; such weak behaviours can be counter-intuitive for programmers. The definition of reads-from is detailed and fragmented over several sections of the standards, and the weak behaviours it allows complicate data race analysis, because a race may be dependent upon a weak behaviour having occurred.

Because of these factors, working out by hand whether a program is race-free, even for small litmus tests, is difficult.

The aim of this chapter is to investigate the provision of automated tool support for race analysis of C++11 programs, with the goal of helping C++11 programmers write race-free programs. The current state-of-the-art in dynamic race analysis for C++11 is ThreadSanitizer [SI09] (tsan). Although tsan can be applied to programs that use C++11 concurrency, the tool does not understand the specifics of the C++11 memory model: it can miss both data races and errors, and report false alarms.

The main research questions considered are: (1) Can synchronisation properties of a C++11 program be efficiently tracked during dynamic analysis? (2) How large a fragment of the C++11 memory model can be modelled efficiently during dynamic analysis? (3) Following from (1) and (2), can a memory model-aware dynamic race analysis tool scale to large concurrent applications, such as the Firefox and Chromium web browsers? These applications can already be analysed using tsan, without the full extent of the C++11 memory model; by modifying tsan to be fully aware of the memory model, can applications such as these be explored?

Sections 3.1 and 3.2 detail existing work. The rest of the section is original work that builds on these two sections. The original work presented in this chapter is structured as follows:

Extending the vector clock algorithm for C++11 §3.3 The vector clock-based dynamic race detection algorithm [FF09] is extended to handle C++11 synchronisation accurately, requiring awareness of release sequences and fence semantics.

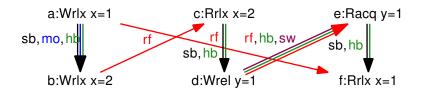

Exploring weak behaviours §3.4 Many C++11 weak behaviours are due to the readsfrom relation, which allows a load to read from one of several stores. This section presents the design of an instrumentation library that enables dynamic exploration of this relation, capturing a large fragment of the C++11 memory model.

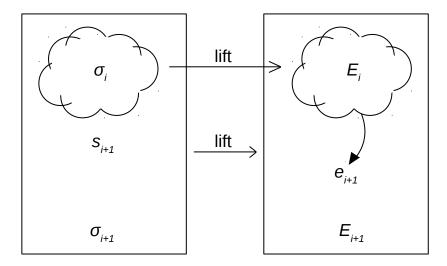

Operational model §3.5 This section formalises the instrumentation of §3.4 as an operational semantics for a core language. Unlike related works on operational semantics for C/C++11 that aim to capture the full memory model, the semantics presented here is intended as a basis for dynamic analysis of real-world applications, thus trades coverage for feasibility of implementation.

Characterising the operational model axiomatically §3.6 The practically-focussed design of the operational model in §3.6 means that not all memory model behaviours can be observed. To make this precise, the behaviours that are unobservable have been characterised via a single additional axiom to those of an existing axiomatic formalisation of C++11, and an argument that this strengthened memory model is in correspondence with the operational model is provided.

A detailed implementation and evaluation of the instrumentation described in this chapter is provided in §5.2. The implementation is provided as an extension to ThreadSanitizer.

#### 3.1 C/C++11 Memory Model

The C/C++11 specification provides a unified memory model that abstracts away the memory model of the underlying hardware, allowing programmers to target a single platform [ISO11b, ISO11a]. The C/C++11 memory model has been designed such that it avoids excluding behaviours that a potential underlying hardware memory model could exhibit, as doing so would reduce the usability of C/C++11 for programmers who wish to make full use of such hardware. As a result, the C/C++11 memory model is very permissive in the behaviours that it will allow. In some case, this can lead to some confusing and unintuitive executions.

Four basic low level atomic operations are provided: stores, loads, read-modify-writes (RMWs) and fences. Stores and loads will write to and read from an atomic location respectively. RMWs will modify (e.g. increment) the existing value of an atomic location, storing the new value and returning the previous value atomically. Fences apply memory order constraints on the program. Atomic operations on the same location are safe to use across multiple threads in a racy manner, and are expected to race, as this allows communication between threads without the use of locks. These races are not regarded as data races according to the C++11 memory model however.

While atomics allow safe access to atomic locations, on their own they do not help memory accesses that are non-atomic. As shown in §2.2, the general hardware-based solution is to use memory barriers. To briefly recap, the release barrier prevents memory operations ordered before the barrier from being shifted after it, while also releasing, or publishing, the side effects for other threads to see. The acquire barrier prevents memory operations ordered after it from being shifted before it. A barrier is implicitly attached to certain atomic operations. When an atomic load with an acquire barrier reads the value stored by an atomic store, the side effects published by any release barrier on that store, and only that store, are guaranteed to become visible to any memory operation ordered after the acquire barrier. This is the most common method of inter-thread communication, called synchronisation.

In C/C++11, atomic operations are annotated with a memory ordering. There are six types of ordering: relaxed, consume, acquire, release, acquire-release and sequentially consistent. Release and acquire resemble the release and acquire barriers discussed in §2.2. Relaxed applies no barrier semantics, but does have other ordering implications. Sequentially consistent applies release and acquire semantics, and also enforces a strict total order over all operation marked as such, provided the program is race-free. Consume has a special meaning, and in line with many previous works, is not considered in this

work [ND13, BDW16, VBC<sup>+</sup>15]. The consume ordering is rarely considered due to its unusual semantics and lack of implementation in most compilers.

While these orderings order non-atomic operations, the question now is: what value should an atomic load read? Or rather, what orders the orderings? Because it is not feasible to specify precisely what value should be read, or the order in which atomic operations are executed, the C/C++11 memory model instead specifies what can and cannot happen. This means the model is axiomatic, and as such is defined as a set of axioms. An execution of a C/C++11 program is only considered valid if it abides by the axioms of the C/C++11 memory model.

The set of executions that a program can exhibit is often referred to as the behaviours. A behaviour that cannot be exhibited under strict sequential consistency is called a weak behaviour. The release orderings can be ordered by strength as relaxed > release > release-acquire > sequentially-consistent, with a similar ordering for the acquire orders. A weaker ordering here means that it will allow more program behaviours than a stronger ordering. If a particular hardware setup cannot handle a given ordering, it can be strengthened by going up the chain, with the guarantee that a stronger ordering will not introduce new behaviours, but may restrict them; this guarantee has been shown to be false in some circumstances however [BDW16]. By providing this guarantee, a program written to be able to exploit weak behaviours can still be run on hardware that cannot exhibit them, by strengthening the orderings, as long as the hardware is at least capable of strict sequential consistency. Any hardware that can enforce strict sequential consistency can satisfy the C/C++11 memory model.

The rest of this section is dedicated to formalising the C/C++11 memory model. This follows the *Post-Rapperswil* formalisation of Batty et al. [BOS<sup>+</sup>10]. Although recent works have condensed the formalisation [BDW16, VBC<sup>+</sup>15], the descriptive presentation of [BOS<sup>+</sup>10] provides a greater degree of intuition, especially for designing the instrumentation framework in §3.4.

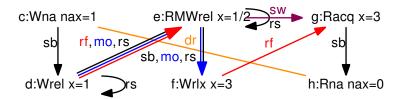

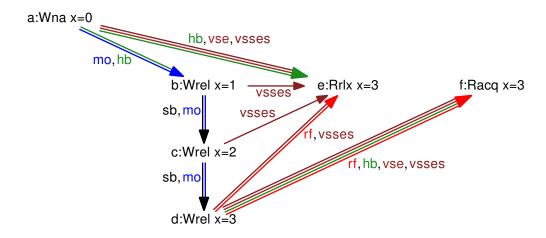

**Pre-executions** A program execution represents the behaviour of a single run of the program. These are shown as execution graphs (e.g. Figure 3.2c), where nodes represent memory events. For example, **a**:**W**<sub>rel</sub>**x**=**1** is a memory event that corresponds to a release write of 1 to memory location **x**; **a** is a unique identifier for the event. The event types **W**, **R**, **RMW** and **F** represent read, write, RMW and fence events, respectively. Memory orderings are shortened to **rlx**, **rel**, **acq**, **ra**, **sc** and **na** for relaxed, release, acquire, release-acquire, sequentially-consistent and non-atomic, respectively. An RMW has two associated values, representing both the value read and the value written. For example,

b:RMW<sub>ra</sub> $\mathbf{x}=1/2$  shows event b reading value 1 from and writing value 2 to  $\mathbf{x}$  atomically. Fences have no associated values or atomic location; an example release fence event is  $\mathbf{c}$ : $\mathbf{F}_{rel}$ .

Execution graphs are used throughout this work to provide a clear representation of specific executions. These graphs are best viewed in colour. In each graph, events in the same column are issued by the same thread.

Sequenced-before (sb) is an intra-thread relation that orders events by the order they appear in the program. The sb relation is not total within a thread, as operations within an expression are not ordered. For example, ++i + ++i will result in two unsequenced loads of i.

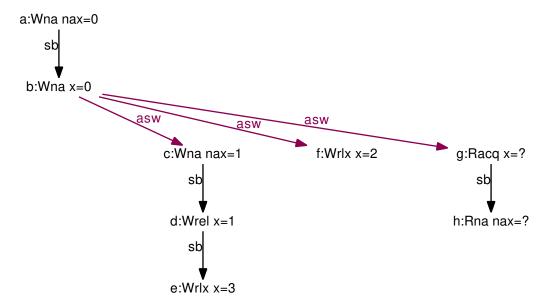

Additional-synchronises-with (asw) causes synchronisation on thread launch, between the parent thread and the newly created child thread. Let a be the last event performed by a thread before it creates a new thread, and b be the first event in the created thread. Then  $(a,b) \in asw$ . Similarly, an asw edge is also created between the last event in the child thread and the event immediately following the child-parent join operation in the parent thread.

The events, sb edges and asw edges form a pre-execution. This represents one possible flow of the program according to the control flow of the program, with arbitrary values for the memory loads. Due to the presence of branches, there can be many, possibly infinitely many, pre-executions. A pre-execution represents a possibility, and may or may not be able to be extended to an actual execution.

Figure 3.2a shows an execution graph for a pre-execution of the program in Listing 3.1. Because there is no information on what store the loads have read from, the values of the loads are ambiguous. Unnecessary information is often omitted from these graphs to prevent them from becoming cluttered. Most notably, the initialisation of variables and the additional-synchronises-with edges will usually be omitted.

Candidate Executions Each pre-execution can be extended with a set of witness relations, to give a candidate execution. These relations represent the runtime observations of the execution. Not all pre-executions can be extended to a candidate execution, e.g. when a load cannot be matched with any store. Consider the pre-execution of Figure 3.2a in which event g reads the value 4, there will be no store that can be matched to g, and thus no candidate executions.

Reads-from (rf) shows which store each load reads from. For a store a and load b,  $(a,b) \in rf$  indicates that the value read by b was written by a. Each load must have exactly one rf edge incident on it.

```

int nax = 0;

std::atomic<int> x(0);

void T1() {

nax = 1;

x.store(1, std::memory_order_release);

x.store(3, std::memory_order_relaxed);

}

void T2() {

x.store(2, std::memory_order_relaxed);

}

void T3() {

x.load(std::memory_order_acquire);

nax; // read from 'nax'

}

```

**Figure 3.1:** Simple racy C++11 program.

Modification-order (mo) is a total order over all of the stores to a single atomic location. Each location has its own total order.

Sequentially-consistent (sc) order is a total order over all atomic operations in the execution marked with sequentially-consistent ordering. It is expected that the other relations, sb, rf and mo, do not conflict with sc, thus restricting many of the behaviours that would otherwise be allowed.

The set of all candidate executions for a given program is called the *candidate set*. Figure 3.2b shows one possible candidate execution for the pre-execution of Figure 3.2a. The number of ways in which a pre-execution can be extended grows very quickly with the number of memory events, due to the many ways in which the relations may be arranged. For example, the modification order over the 4 writes to x in Figure 3.2a can be arranged in 24 different ways. When combined with the 4 possible stores the load in g can read from and the 2 stores for h, gives 192 candidate executions.

A candidate execution does not have to be viable according to the C/C++11 memory model, as checking for consistency comes at a later step. Many of these candidates will therefore have seemingly bizarre behaviours. For example, Figure 3.3 shows another candidate execution for the pre-execution of Figure 3.2a, with mo going backwards in program order.

**Derived Relations** A candidate execution must still be checked against the C/C++11 memory model for consistency. To simplify the consistency rules, the candidate execution can be extended with a set of *derived relations*.

A release-sequence (rs) represents a continuous subset of the modification order. An rs is headed by a release store, and continues along each store to the same location. The rs

(a) A pre-execution of the program in Listing 3.1, the only possible pre-execution for this program.

(b) The pre-execution in Figure 3.2a has been extended with a set of possible witness relations to give a candidate execution. The initialisations of the main thread have been excluded.

(c) Given the candidate execution of Figure 3.2b, you can derive the derived relations. The hypothetical release sequence and some happens-before relations have been excluded for clarity.

Figure 3.2: Pre-execution, witness and derived relations for the program in Listing 2.1.

Figure 3.3: A candidate execution for the pre-execution of Figure 3.2a. The modification order will prevent this from being allowed by the C/C++11 memory model.

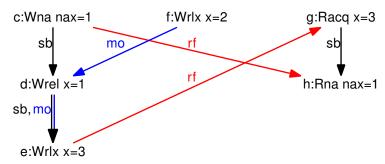

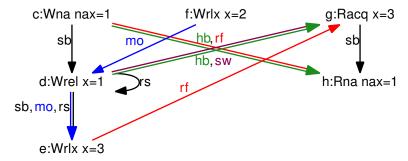

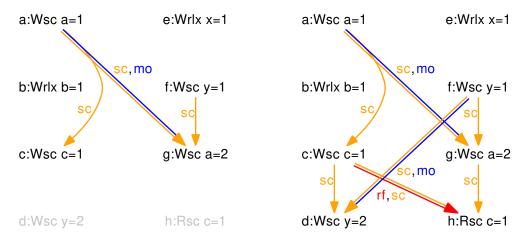

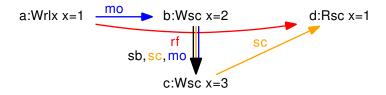

is blocked when another thread performs a store to the location. An RMW from another thread will however continue the rs. An example of this is shown in Figure 3.2c, whereby an rs headed by d extends down to e. Another example is shown in Figure 3.4, where instead the rs headed by d is blocked by the store in another thread labelled f.

A hypothetical-release-sequence (hrs) works in the same way as a release sequence, but is headed by both release stores and non-release stores. The rules for extending and blocking are the same as for release sequences. The hrs is used for fence synchronisation.

Synchronises-with (sw) defines the points in an execution where one thread has synchronised with another. When a thread performs an acquire load, and reads from a store that is part of a release sequence, the head of the release sequence synchronises with the acquire load. This means that release sequences are necessary for synchronisation, and so the aforementioned release sequence blocking behaviour can be detrimental if synchronisation is required. An asw edge is also an sw edge.

Happens-before (hb) is simply  $(sb \cup sw)^+$  (where + denotes transitive closure), representing Lamport's partial ordering over the events in a system [Lam78]. Because an sw edge is also an hb edge, when event a in thread A synchronises with event b in thread B, every side effect sequenced before a in A will become visible to every event sequenced after b in B.

Figure 3.2c shows the candidate execution of Figure 3.2b that has been extended with the derived relations. The release store of d heads a release sequence, that then extends down to e. When the acquire load of g reads from e, the event that headed the release sequence synchronises with g. Due to synchronisation, the non-atomic write of e happens before the non-atomic read of e.

Figure 3.4 shows another candidate execution. The release sequence is blocked by the

**Figure 3.4:** The release sequence headed by d is blocked by event f, causing a data race between c, the non-atomic write to  $\mathbf{nax}$ , and h, the non-atomic read from  $\mathbf{nax}$ ; if the blocking event f is removed, there is no race.

store of f. As e is not a part of the release sequence, there is no synchronisation, and so the non-atomic accesses are not ordered.

Data Races A further relation can now be defined that will identify data races. To reiterate, a data race occurs between two memory accesses when both operate on the same location, at least one is non-atomic, at least one is a store, and neither happens before the other. The hb relation defined above suitably fits this notion of happens before. Figure 3.4 shows an execution with a data race, as there is no sw edge between the release store d and acquire load g, and therefore no hb edge between the non-atomic accesses c and h.

The C/C++11 standards state that data races are undefined behaviour. It does not matter if a particular execution does not have a data race; if any of the consistent executions have a data race the behaviour of the program is undefined.

The negative consequences of data races are well known from a research perspective [Adv10a, Adv10b], but to a regular programmer, they can seem inconsequential. The obvious assumption is that the physical representation of the bits in memory may become mangled after two concurrent stores. In practise, this is not an issue for most systems, especially with the introduction of transactional memory [CSW18]. The bigger issue lies with the compiler. Consider a C++11 compiler that takes as input a well formed C++11 program. The compiler will assume that any program given to it is well formed, and thus race free. A programmer can still give it a racy program, but the compiler will transform it under the assumption that it is race free. For example, consider a thread that performs a series of non-atomic stores, but does not follow up with a release atomic operation. From the compiler's perspective, no other thread is going to try to access the locations of these

stores, as doing so would constitute a data race. The compiler may therefore simply omit the stores for efficiency, leaving them invisible to other threads.

Consistent Executions A consistent execution is a candidate execution that abides by the C/C++11 memory model. The consistent set is a candidate set filtered by consistency. The rules for consistency are presented as a set of axioms. For an execution to be consistent it must satisfy all of the axioms. The set of executions that are allowable is the consistent set, with the caveat that if any consistent execution contains a data race, the set of allowed executions is empty and the program is undefined.

There are seven axioms that determine consistency [BOS<sup>+</sup>10]. Some of these axioms will be simplified, as consume ordering and locks are not being considered. A brief overview of each axiom is given in this section, but will be covered in more detail where appropriate when describing the exploration of weak behaviours in §3.4.

The well-formed-threads axiom restricts the formation of memory events, sb, and asw. This will prevent considering pre-executions that will only lead to inconsistent executions. The well-formed-rf-mapping axiom similarly restricts rf, such as not allowing a load specified at one location reading from a store to another location, or a load reading from multiple stores. This will prevent considering candidate executions that will trivially be inconsistent. The consistent-locks axiom is not considered, as locks have not been affected by this work.

The three axioms, consistent-sc-order, consistent-mo and consistent-rf-mapping, correspond with the formation of the sc, mo and rf relations. These are non-trivial, and are covered in more detail in §3.4. The last axiom is consistent-ithb axiom which, without consume, simply requires hb to be irreflexive.

As long as an execution follows these axioms, it is deemed a valid execution of a well formed C/C++11 program. This leads to some interesting behaviours. A weak behaviour is one that would not appear under any interleaving of the threads using sequentially consistent semantics. To illustrate this, Figure 3.5 shows two such executions that arise from well-known litmus tests [AMT14, BOS+11, BWB+11, ND13]. In the load and store buffering examples, at least one of the reads will not read from the most recent write in mo, no matter how the threads are interleaved. In the load buffering example, one of the reads will read from a write that could not have occurred yet at that point in the execution. While these behaviours are allowed by the memory model, whether they are observed in practice will depend on practical issues such as the effect of compiler reorderings and properties of the hardware on which a program is executed.

Figure 3.5: Example executions showing some of the common weak behaviours allowed by the C/C++11 memory model.

#### 3.2 Dynamic Race Detection

A dynamic race detector aims to catch data races while a program executes. This requires inferring various properties of the program after specific instructions have been carried out.

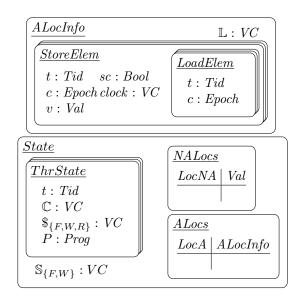

The vector clock (VC) algorithm is a prominent method for race detection that can be applied to multiple languages, including C++ with pthreads, and Java [FF09, Mat88, PS03, PS07, ISZ99]. It aims to compute the happens-before relation. Each thread in the program has an *epoch* representing its current logical time. A VC holds an epoch for each thread, and each thread has its own VC, denoted  $\mathbb{C}_t$  for thread t. The epoch for thread t'in  $\mathbb{C}_t$  represents the logical time of the last instruction executed by t' that happens before any instruction thread t will execute in the future. The local epoch for thread t,  $\mathbb{C}_t(t)$ , is denoted c@t.

VCs have an *initial value*,  $\perp_V$ , a *join* operator,  $\cup$ , a *comparison* operator,  $\leq$ , and a per-thread increment operator,  $inc_t$ . These are defined as follows:

Upon creation of thread t,  $\mathbb{C}_t$  is initialised to  $inc_t(\bot_V)$ , possibly joined with the clock of the parent thread, depending on the synchronisation semantics of the associated programming language. Each atomic location m has its own VC,  $\mathbb{L}_m$ , which is updated as follows: when thread t performs a release operation on m, it releases  $\mathbb{C}_t$  to m:  $\mathbb{L}_m := \mathbb{C}_t$ . When thread t performs an acquire operation on m, it acquires  $\mathbb{L}_m$  using the join operator:  $\mathbb{C}_t := \mathbb{C}_t \cup \mathbb{L}_m$ . Thread t releasing to location t and the subsequent acquire of t by thread t simulates

Figure 3.6: The write from T2 can cause T1 to fail to synchronise with T3, resulting in a data race on nax; tsan cannot detect the race.

synchronisation between t and u. On performing a release operation, thread t's vector clock is incremented:  $\mathbb{C}_t := inc_t(\mathbb{C}_t)$ .

To detect data races, specific checks are performed to ensure that certain accesses to each location are ordered by hb, the happens-before relation. As all writes must be totally ordered, only the epoch of the last write to a location x, denoted  $W_x$ , needs to be known at any point. As data races do not occur between reads, the reads do not need to be totally ordered, and so the epoch of the last read by each thread may need to be known. A full VC must therefore be used to track reads for each memory location, denoted  $\mathbb{R}_x$  for location x;  $\mathbb{R}_x(t)$  gets set to the epoch  $\mathbb{C}_t(t)$  when t reads from x.

To check for data races, a different check must be performed depending on the type of the current and previous accesses. These are outlined as follows, where thread u is accessing location x, c@t is the epoch of the last write to x and  $\mathbb{R}_x$  represents the latest read for x by each thread; if any check fails then there is a data race:

```

write-write: c \leq \mathbb{C}_u(t) write-read: c \leq \mathbb{C}_u(t) read-write: c \leq \mathbb{C}_u(t) \wedge \mathbb{R}_x \leq \mathbb{C}_u

```

**Example** An illustration of the VC-based race detection algorithm is provided using the example of Figure 3.6, for the thread schedule in which the statements are executed in the order A-F. Initially, the thread VCs are  $\mathbb{C}_{T1} = (1,0,0)$ ,  $\mathbb{C}_{T2} = (0,1,0)$ ,  $\mathbb{C}_{T3} = (0,0,1)$ , and  $\mathbb{R}_{nax} = \mathbb{L}_x = \bot_V$ . Because nax has not been written to,  $W_{nax}$  has initial value 0@T1, where the choice of T1 is arbitrary: epoch 0 for any thread would suffice [FF09].

Statement A writes to nax, which has not been accessed previously, no race check is required. After A,  $W_{\text{nax}} := 1@\text{T1}$ , because T1's epoch is 1. After T1's release store at B,  $\mathbb{L}_{\mathbf{x}} := \mathbb{L}_{\mathbf{x}} \cup \mathbb{C}_{\text{T1}} = (1,0,0)$ , and  $\mathbb{C}_{\text{T1}} := inc_{\text{T1}}(\mathbb{C}_{\text{T1}}) = (2,0,0)$ . After T2's acquire load C,

| Statement    | $\mathbb{C}_{\mathtt{T1}}$ | $\mathbb{C}_{\mathtt{T2}}$ | $\mathbb{C}_{	exttt{T3}}$ | $\mathbb{L}_{\mathtt{x}}$ | $\mathbb{R}_{\mathtt{nax}}$ | $\mathbb{W}_{\mathtt{nax}}$ |

|--------------|----------------------------|----------------------------|---------------------------|---------------------------|-----------------------------|-----------------------------|

| -            | (1,0,0)                    | (0, 1, 0)                  | (0,0,1)                   | $\perp_V$                 | $\perp_V$                   | -                           |

| A            |                            |                            |                           |                           |                             | $1@{\bf T1}$                |

| В            | (2,0,0)                    |                            |                           | (1,0,0)                   |                             |                             |

| $\mathbf{C}$ |                            | (1, 1, 0)                  |                           |                           |                             |                             |

| D            |                            |                            |                           |                           |                             |                             |

| $\mathbf{E}$ |                            |                            | (1, 0, 1)                 |                           |                             |                             |

| $\mathbf{F}$ |                            |                            | (1, 0, 1)                 |                           |                             | 1@T1                        |

**Figure 3.7:** Trace of the program in Figure 3.6, showing the value of the VCs after each statement. Only updated values are shown, and those where race detection checks are performed.

$\mathbb{C}_{T2} := \mathbb{C}_{T2} \cup \mathbb{L}_x = (1,1,0)$ . The race analysis state is not updated by T2's store at D since relaxed ordering is used.

After T3's acquire load at E,  $\mathbb{C}_{T3} := \mathbb{C}_{T3} \cup \mathbb{L}_{x} = (1,0,1)$ . Thread T3 then reads from nax at statement F, thus a race check is required between this read and the write issued at A. A write-read check is required, to show that  $c \leq \mathbb{C}_{T3}(t)$ , where  $W_{\text{nax}} = c@t$ . Because  $W_{\text{nax}} = 1@T1$ , this simplifies to  $1 \leq \mathbb{C}_{T3}(T1)$ , which can be seen to hold. The execution is thus deemed race-free.

A sketch of this execution is shown in Figure 3.7. Only updates are shown, except where a race condition check is performed, which is coloured red. A check is performed during statement F, which shows that  $1 \leq \mathbb{C}_{T3}(T1)$  and so there is no race.

#### 3.3 Data Race Detection for C++11

The rest of this section describes original work, that build upon the pre-existing work outline in sections 3.1 an 3.2.

The traditional VC algorithm outlined in  $\S 3.2$ , and implemented in tsan, is defined over simple release and acquire operations. It is unaware of the more complicated synchronisation patterns of C/C++11. This section describes an updated VC algorithm that properly handles C/C++11 synchronisation, by showing where the original VC algorithm falls short and how the updated algorithm fixes these shortcomings. The algorithm is summarised as a set of inference rules in  $\S 3.3.3$ .

#### 3.3.1 Release Sequences

As described in §3.1, release sequences are key to synchronisation in C++11. Event a will synchronise with event b if a is a release store, b is an acquire load, and b reads from a

| Statement    | $\mathbb{C}_{\mathtt{T1}}$ | $\mathbb{C}_{\texttt{T2}}$ | $\mathbb{C}_{\mathtt{T3}}$ | $\mathbb{L}_{x}$ | $\mathbb{R}_{\mathtt{nax}}$ | $\mathbb{W}_{\mathtt{nax}}$ |

|--------------|----------------------------|----------------------------|----------------------------|------------------|-----------------------------|-----------------------------|

| -            | (1,0,0)                    | (0, 1, 0)                  | (0,0,1)                    | $\perp_V$        | $\perp_V$                   | -                           |

| A            |                            |                            |                            |                  |                             | $1@{\tt T1}$                |

| В            | (2,0,0)                    |                            |                            | (1,0,0)          |                             |                             |

| $\mathbf{C}$ |                            | (1, 1, 0)                  |                            |                  |                             |                             |

| D            |                            |                            |                            | $\perp_V$        |                             |                             |

| ${f E}$      |                            |                            | (0, 0, 1)                  |                  |                             |                             |

| $\mathbf{F}$ |                            |                            | (0, 0, 1)                  |                  |                             | $1@{\bf T1}$                |

**Figure 3.8:** Trace of the program in Figure 3.6, showing the value of the VCs after each statement. Only updated values are shown, and those where race detection checks are performed. Blue updates show those that differ from the sketch of Fig.3.7.

store in the release sequence headed by a. This subsection explains why the existing VC algorithm does not accurately capture release sequence semantics, and how the new VC algorithm will fix these shortcomings.