UNICAMP

UNIVERSIDADE ESTADUAL DE CAMPINAS FACULDADE DE ENGENHARIA ELÉTRICA E DE COMPUTAÇÃO

LUCAS STUCCHI-ZUCCHI

# SILICON WET ETCHING IN NH4OH SOLUTION AS CHANNEL THINNING MECHANISM FOR JUNCTIONLESS-FET DEVICES

# CORROSÃO DE SILÍCIO EM SOLUÇÃO DE NH₄OH COMO FORMA DE AFINAMENTO DO CANAL PARA DISPOSITIVOS JUNCTIONLESS-FET

CAMPINAS 2019

UNICAMP

UNIVERSIDADE ESTADUAL DE CAMPINAS FACULDADE DE ENGENHARIA ELÉTRICA E DE COMPUTAÇÃO

# Lucas Stucchi-Zucchi

Silicon wet etching in NH<sub>4</sub>OH solution as channel thinning mechanism for Junctionless-FET devices

Corrosão de silício em solução de NH4OH como forma de afinamento do canal para dispositivos Junctionless-FET

Dissertation presented to the Graduate Program in Electrical Engineering of the School of Electrical and Computer Engineering of the State University of Campinas as a requirement for the title of Master of Science in the area of Electronics, Microelectronics and Optoelectronics

Dissertação apresentada ao Programa de Pós-Graduação em Engenharia Elétrica da Faculdade de Engenharia Elétrica e de Computação da Universidade Estadual de Campinas para obtenção do título de Mestre em Engenharia Elétrica, na área de Eletrônica, Microeletrônica e Optoeletrônica.

### Orientador: Prof. Dr. José Alexandre Diniz

Este exemplar corresponde à versão final da tese defendida pelo aluno Lucas Stucchi-Zucchi, e orientada pelo Prof. Dr. José Alexandre Diniz

#### Ficha catalográfica Universidade Estadual de Campinas Biblioteca da Área de Engenharia e Arquitetura Luciana Pietrosanto Milla - CRB 8/8129

Stucchi-Zucchi, Lucas, 1993 St93c

St93c

Corrosão de silício em solução de NH4OH como forma de afinamento do canal para dispositivos Junctionless-FET / Lucas Stucchi-Zucchi. – Campinas, SP : [s.n.], 2019.

Orientador: José Alexandre Diniz.

Dissertação (mestrado) – Universidade Estadual de Campinas, Faculdade de Engenharia Elétrica e de Computação.

1. Silício. 2. Nanoeletrônica. 3. Microeletrônica. 4. Transistor. I. Diniz, José Alexandre, 1964-. II. Universidade Estadual de Campinas. Faculdade de Engenharia Elétrica e de Computação. III. Título.

#### Informações para Biblioteca Digital

Título em outro idioma: Silicon wet etching in NH4OH solution as channel thinning mechanism for Junctionless-FET devices Palavras-chave em inglês: Silicon Nanoeletronics Microeletronics Transistor Área de concentração: Eletrônica, Microeletrônica e Optoeletrônica Titulação: Mestre em Engenharia Elétrica Banca examinadora: José Alexandre Diniz [Orientador] Leandro Tiago Manera Ricardo Cotrin Teixeira Data de defesa: 27-09-2019 Programa de Pós-Graduação: Engenharia Elétrica

Identificação e informações acadêmicas do(a) aluno(a) - ORCID do autor: https://orcid.org/0000-0001-7900-0000

- Currículo Lattes do autor: http://lattes.cnpq.br/5594099085421052

# COMISSÃO JULGADORA – DISSERTAÇÃO DE MESTRADO

Candidato: Lucas Stucchi-Zucchi RA: 122975

Data da Defesa: 27 de setembro de 2019

**Título da Tese:** "Corrosão de silício em solução de NH4OH como forma de afinamento do canal para dispositivos Junctionless-FET".

Prof. Dr. José Alexandre Diniz (Presidente) Prof. Dr. Leandro Tiago Manera Dr. Ricardo Cotrin Teixeira

A ata de defesa, com as respectivas assinaturas dos membros da Comissão Julgadora, encontra-se no SIGA (Sistema de Fluxo de Dissertação/Tese) e na Secretaria de Pós-Graduação da Faculdade de Engenharia Elétrica e de Computação.

#### AGRADECIMENTOS

Agradeço a todos que contribuíram direta ou indiretamente para a execução desse trabalho. Especialmente aos colegas que pude fazer nessa caminhada que ajudaram algum conselho, solução ou apoio. Gostaria de agradecer:

• A meus pais, minha madrasta Silvia, e meu padrasto Rodolfo, que sempre me apoiaram nas minhas escolhas e aventuras, mesmo quando escolhi seguir um caminho pouco trilhado, e muitas vezes a partir de escolhas duvidosas. Ao seu entusiasmo e exemplo devo todas as minhas conquistas.

• A minha madrasta Silvia, pelo apoio e incentivo ao atravessar as dificuldades durante a minha graduação e pesquisa.

• Aos meus amigos Natalia, Levi, Camila, Paula e Paula Fernandes, pelo carinho e companhia que me auxiliaram nos momentos de dificuldade e nos inúmeros bloqueios criativos.

• Ao Prof. José Alexandre Diniz pelo incentivo, disponibilidade, confiança e pelas palavras que me motivaram sempre que duvidei de minha capacidade.

• Aos amigos Rodrigo, Hugo e Fernando, pelas conversas e pelo auxílio nos processos de caracterização usando o sistema FIB-SEM, nas inúmeras deposições e na interpretação e apresentação dos resultados obtidos.

• Aos funcionários do CCS que sempre se dispuseram a colaborar com esse trabalho.

• Aos funcionários do DFA-IFGW/UNICAMP. Em especial a Marcos Vinicios Puydinger dos Santos, pelas conversas, apoio e ajuda ao navegar os trâmites burocráticos e sociais do projeto.

• Aos amigos Rodrigo, Hugo, Débora, Paula, Fernando, Lucas, Sérgio e Lucas Spejo, com os quais compartilhei momentos de trabalho, de alegria e de comunidade no laboratório e também fora dele.

• Ao meu amigo Rocky, com quem compartilhei noites em claro e dias chuvosos.

• O presente trabalho foi realizado com apoio da Coordenação de Aperfeiçoamento de Pessoal de Nível Superior - Brasil (CAPES) - Código de Financiamento 001.

### Abstract

The industry of nanoeletronics is a symbol of technological innovations and one of the cores of modern-day information systems. After decades of innovations in miniaturizing and improving the traditional inversion-type MOSFET device, its once thought to be unbound potential seems to be arriving at its limits. Among the new devices proposed to sustain the historical increase in computing power and efficiency, the Junctionless-Field-Effect-Transistor (JL-FET) stands out as an alternative that can lower the cost and complexity of fabrication, while at the same time improving key figures such as on and off current, switching delay and subthreshold slope. To achieve JL-FET devices that are compatible with state of the art switching applications, the device channel must be thin enough to enable full charge carrier depletion for null gate voltage, usually a few dozen nanometers.

In this work, the silicon anisotropic etching in NH<sub>4</sub>OH solution was developed as means to thin structures to the required thicknesses for JL-FET fabrication. Initially, the devices were simulated numerically on SILVACO Atlas and Athena environments, so as to generate a numerical model that could help on planning and implementing the proposed processes. Every test was carried out in 340 nm silicon (100) over 400 nm Silicon Dioxide Silicon-On-Insulator (SOI) wafers. Building on previous works that measured minimum etch rate at 2.5 nm/s for the specific structures, JL-FET devices were fabricated by two distinct processes. In the original process the silicon etching in NH<sub>4</sub>OH solution took place after the active region is already defined and etched and after ion implantation (<sup>31</sup>P<sup>+</sup> ion, dose of 6.10<sup>15</sup> atoms.cm<sup>-2</sup>, and energy of 50 keV) was carried out to achieve the channel doping. An updated process was proposes, in which the NH<sub>4</sub>OH solution silicon etching takes place before any other process, among the advantages of this process flow, the structures can be characterized optically midway through the fabrication and the etching rate becomes even for both pMOS and nMOS devices.

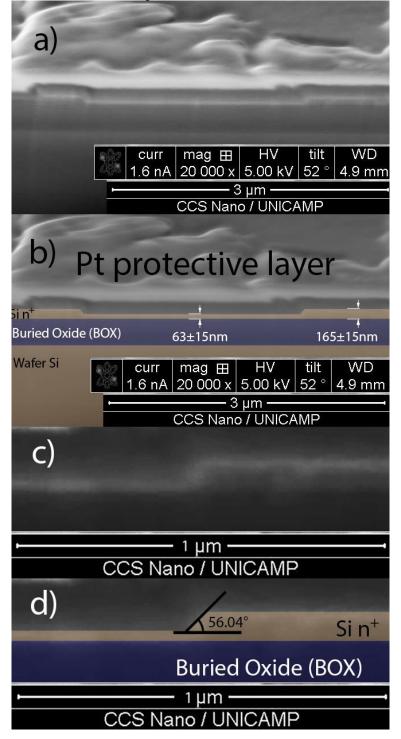

Devices with channel thickness of 63 nm were fabricated using the original process, thinned from 165-nm-thick SOI layers. The dopant concentration on the channel region was estimated at approximately 10<sup>17</sup> atoms/cm<sup>3</sup>, obtained by the Pseudo-MOS characterization technique. The device presented Schottky electrical contacts with potential barriers of approximately 1 V and also presented a negative threshold voltage, due to the dopant concentration and thickness of the channel. These results were confirmed by feeding the obtained data back in the numeric simulation models.

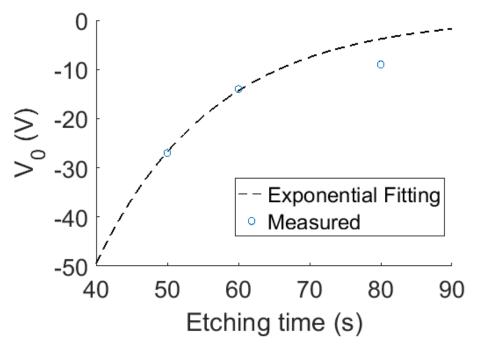

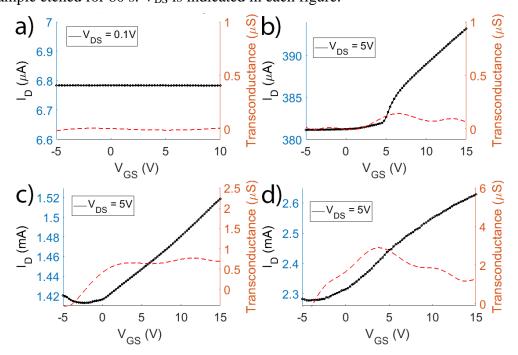

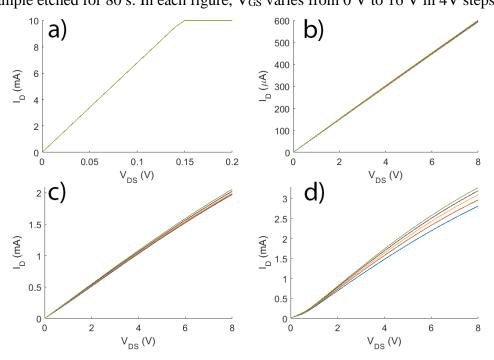

Samples with etching times between 50 s to 80 s were fabricated using the updated process, alongside unetched samples. Without the doping effect, this process presents an improved control over the etching rates, enables the fabrication of pMOS devices and an overall larger dopant concentration on the devices. The voltage necessary to deplete every charge carrier in the channel,  $V_0$ , were estimated (between -27 V and -10 V) using the Pseudo-MOS measurements for all the samples fabricated using the updated process. Using this data, a fitting was performed to obtain a  $V_0$  versus etching time plot. As  $V_0$  is closely related to the ability of the transistor to achieve cut-off, this figure will be used to guide future fabrication efforts.  $I_D x V_{GS}$  measurements also showed increased  $I_{on}/I_{off}$  ratios as the etching time increases, from 1 in the unetched sample, to approximately 1.13 in the sample etched for 80 seconds.

In conclusion, we developed the anisotropic etching of silicon in an ammonium hydroxide (NH<sub>4</sub>OH) solution as a way to allow the fabrication of JL-FET devices, with channel thickness up to 63 nm, because these devices require dimensions thinner than 100 nm. This kind of etching is accessible and cheap, presents almost negligible etching rate to the oxide hardmask used to define the etched regions and does not cause the introduction of contaminating ions and materials on silicon substrate.

### Resumo

A indústria da nanoeletrônica é símbolo da inovação tecnológica e está no cerne dos sistemas de informações modernos. Após décadas de inovações em miniaturização e melhoramentos na configuração tradicional dos dispositivos MOSFET (*Metal-Oxide-Semiconductor Field-Effect-Transistor*), novos dispositivos precisam ser estudados. Em meio a esses novos dispositivos, o Transistor de Efeito de Campo Sem Junções (*Junctionless-Field-Effect-Transistors*, ou JL-FET) se destaca devido ao seu menor custo e complexidade de fabricação, ao mesmo tempo que apresenta melhorias em características centrais ao funcionamento do dispositivo, como a corrente quando ligado e quando desligado, menor atraso de chaveamento e menor *subthreshold slope*. Para obter dispositivos JL-FET compatíveis com aplicações digitais, o canal do dispositivo deve ser fino o suficiente para que todos os portadores de carga estejam depletados para uma tensão de porta nula, isto ocorre quando a espessura é menor do que 100 nm.

Neste trabalho, foi estudada a corrosão anisotrópica de silício em solução de NH<sub>4</sub>OH como forma de afinar estruturas a níveis nanométricos, com foco na fabricação de JL-FETs. Inicialmente, os dispositivos fabricados com o processo foram simulados numericamente nos ambientes SILVACO Athena e Atlas, para gerar um modelo que auxiliasse no planejamento dos processos propostos. Todos os testes foram feitos em lâminas de silício-sobreisolante (*silicon-on-insulator*, ou SOI), inicialmente com 340 nm de silício monocristalino (100) sobre 400 nm de óxido de silício. Primeiro, a corrosão foi caracterizada através de testes já com os padrões necessários para a fabricação dos dispositivos, visto que a taxa de corrosão da solução de NH<sub>4</sub>OH varia conforme as estruturas expostas. Dispositivos JL-FET foram fabricados utilizando duas maneiras distintas: em uma delas a corrosão de silício em solução de NH<sub>4</sub>OH ocorre após a definição da região ativa e implantação de dopantes (<sup>31</sup>P<sup>+</sup> ion, dose de 6.10<sup>15</sup> atoms.cm<sup>-2</sup>, e energia de 50 keV), na outra a corrosão de silício em solução de NH<sub>4</sub>OH ocorre antes de todos os outros processos.

Foram obtidos dispositivos com canais com espessuras de 63 nm para o primeiro processo, afinados a partir de estruturas que inicialmente apresentavam 165 nm de espessura. A dopagem do canal nesses dispositivos foi estimada na ordem de 10<sup>17</sup>atomos/cm<sup>3</sup>, determinada a partir do método de caracterização Pseudo-MOS, O comportamento observado foi adequado às características medidas: o dispositivo apresentou contatos Schottky com barreiras de potencial da ordem de 1 V, condizente com a dopagem obtida, e uma tensão de limiar

negativa, que também condiz com a dopagem e espessura medidas. Esses resultados foram confirmados pela realimentação dos dados obtidos nos modelos de simulação numérica.

Foram fabricadas amostras com tempos de corrosão variando entre 50 s e 80 s, utilizando a nova sequência de processos. Sem o efeito da dopagem, este processo apresenta um maior controle sobre as taxas de corrosão, permite que sejam fabricados dispositivos pMOS e de maneira geral aumenta a máxima dopagem possível nos dispositivos. Os valores de tensão de corpo que seriam necessários para depletar todos os portadores de carga do canal, V<sub>0</sub>, foram estimados (entre -27 V e -10 V) a partir das medições Pseudo-MOS para todas as amostras fabricadas com o novo processo. Usando estes dados, um fitting foi obtido que representa V<sub>0</sub> e sua variação com o tempo de corrosão. Como o V<sub>0</sub> indica o quão próximo um dispositivo está de atingir a região de corte, esta curva será usada para guiar os próximos processos de fabricação. Medições I<sub>D</sub> x V<sub>GS</sub> mostraram uma melhoria na razão I<sub>on</sub>/I<sub>off</sub> conforme o tempo de corrosão aumenta, de 1 nas amostras sem corrosão até aproximadamente 1.13 na amostra corroída por 80 segundos. A transcondutância também apresentou evolução similar, de valores nulos nas amostras sem corrosão a 3.5  $\mu$ S na amostra corroída por 80 segundos.

Concluindo, a corrosão anisotrópica de silicio em solução de hidróxido de amônio (NH<sub>4</sub>OH) foi desenvolvida para a fabricação de dispositivos JL-FET com espessura de 63 nm na região de canal, esse processo é necessário pois os dispositivos necessitam dimensões menores do que 100 nm. Este tipo de corrosão é acessível e barato, apresenta uma taxa de corrosão desprezível para o óxido de mascaramento e não causa contaminação com íons ou outros materiais no substrato de silício.

## LIST OF FIGURES

| Figure 1    | Scaling of key ground rules, according to IRDS 2018 report                                  |

|-------------|---------------------------------------------------------------------------------------------|

| Figure 2    | Transistor roadmap from IRDS 2018 report                                                    |

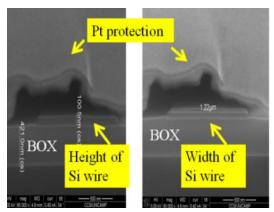

| Figure 3    | Cross-Section SEM images of the 3-nm-long transistor using TMAH etching                     |

| fabricated  | by (MIGITA et al., 2014, adapted)                                                           |

| Figure 4    | Cross-Section SEM images of the devices thinned laterally with trapezoid-                   |

| shaped cha  | nnels fabricated by (SOARES et al., 2018)                                                   |

| Figure 5    | The MOS Capacitor                                                                           |

| Figure 6    | Charge and potential distribution in a MOS capacitor biased with $V_{\text{GB}}$            |

| (TSIVIDIS   | ; MCANDREW, 2011)                                                                           |

| Figure 7    | <i>QC</i> ' $x \psi s$ plot of the example MOS capacitor                                    |

| Figure 8    | <i>VGB x</i> $\psi$ <i>s</i> plot of the example MOS capacitor                              |

| Figure 9    | <i>QC</i> ′ <i>x VGB</i> plot of the example MOS capacitor                                  |

| Figure 10   | Complete band diagram and charge concentration plot for the example MOS                     |

| capacitor.  | 31                                                                                          |

| Figure 11   | Band diagram of the example MOS capacitor for different biasing                             |

| conditions. | 32                                                                                          |

| Figure 12   | Schematic of a standard planar MOSFET device (SEDRA; SMITH, 2015) 33                        |

| Figure 13   | Representation of the charge carrier density in a JL-FET device.(COLINGE et                 |

| al., 2010)  | 34                                                                                          |

| Figure 14   | $Log(I_D) \ge V_{GS}$ plots of MOSFET and JL-FET devices(COLINGE et al., 2010)              |

|             | 35                                                                                          |

| Figure 15   | Comparison of charge carrier and dopant concentrations in JL-FET and                        |

| inversion-r | node MOSFETs                                                                                |

| Figure 16   | Sidecut view of a structure etched in NH4OH solution                                        |

| Figure 17   | SEM image of a structure etched in NH4OH solution                                           |

| Figure 18   | TEM images of the devices fabricated by (COLINGE et al., 2010)                              |

| Figure 19   | $I_{\rm D}~x~V_{GS}$ measurements of the devices fabricated by (COLINGE et al.,             |

| 2010)       | 42                                                                                          |

| Figure 20   | $I_{\text{D}}\x$ $V_{\text{DS}}$ measurements of the devices fabricated by (COLINGE et al., |

| 2010)       | 42                                                                                          |

| Figure 21   | Process flow outline of (MIGITA et al., 2014)                                               |

| Figure 22     | TEM images and $I_D \times V_{GS}$ measurements of (MIGITA et al., 2014) 3.2 nm                      |

|---------------|------------------------------------------------------------------------------------------------------|

| EOT devices   | 3 44                                                                                                 |

| Figure 23     | Cross-Section TEM images of the devices fabricated in(MIGITA et al.,                                 |

| 2014)         | 45                                                                                                   |

| Figure 24     | $I_D \times V_{GS}$ and $I_D \times V_{GS}$ plots of the devices fabricated in (MIGITA et al., 2014) |

|               | 45                                                                                                   |

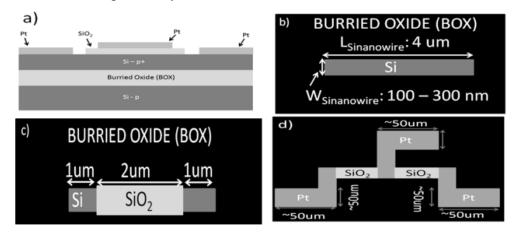

| Figure 25     | Schematics of the devices fabricated by (LIMA et al., 2012)                                          |

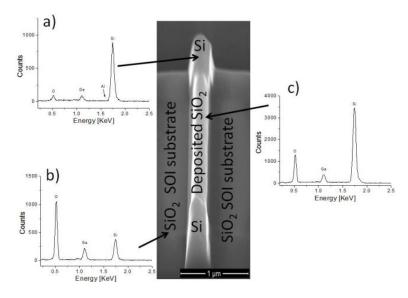

| Figure 26     | SEM image and EDS measurements of a device fabricated by (LIMA et al.,                               |

| 2012).        | 47                                                                                                   |

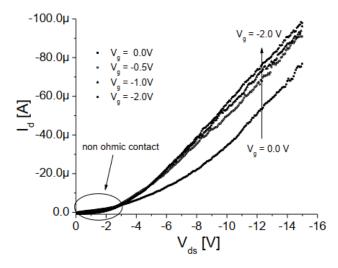

| Figure 27     | $I_D x V_{DS}$ measurements of the devices fabricated by (LIMA et al., 2012)47                       |

| Figure 28     | Schematics of the process performed by (PUYDINGER DOS SANTOS et al.,                                 |

| 2013)         | 49                                                                                                   |

| Figure 29     | SEM images of the structures fabricated by (PUYDINGER DOS SANTOS et                                  |

| al., 2013)    | 50                                                                                                   |

| Figure 30     | Side-view representation and electrical measurements of the Pseudo-MOS                               |

| device fabric | cated (PUYDINGER DOS SANTOS et al., 2013)                                                            |

| Figure 31     | Side-view representation and electrical measurements of the Junctionless-FET                         |

| device fabric | cated (PUYDINGER DOS SANTOS et al., 2013)                                                            |

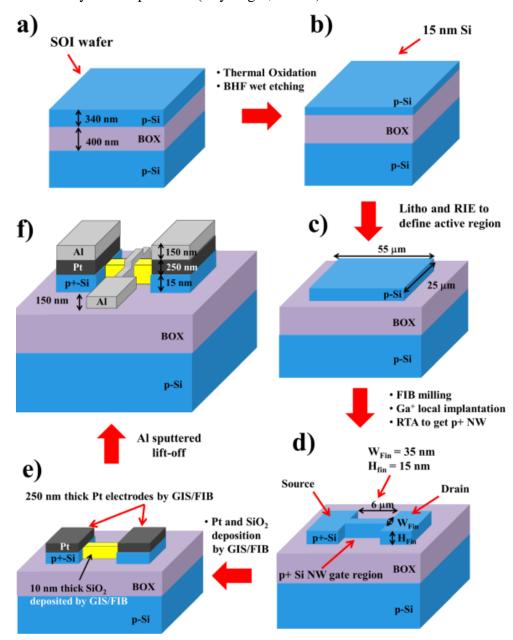

| Figure 32     | Schematics of the process steps followed by (SOARES et al., 2018)                                    |

| Figure 33     | SEM images and measurements of the structures fabricated by (SOARES et                               |

| al., 2018)    | 53                                                                                                   |

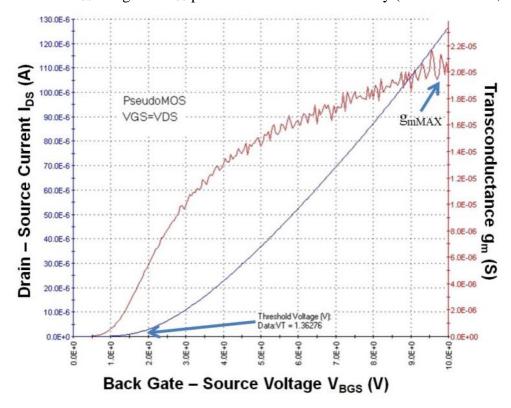

| Figure 34     | $I_D x V_{BGS}$ and $g_m x V_{BGS}$ plot of the device fabricated by (SOARES et al., 2018)           |

|               | 54                                                                                                   |

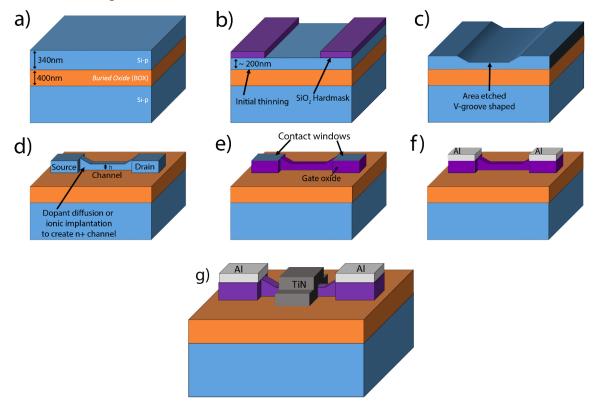

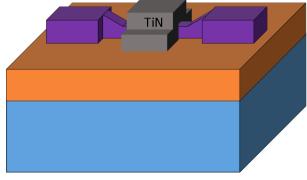

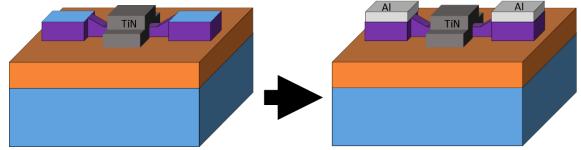

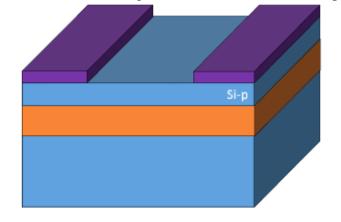

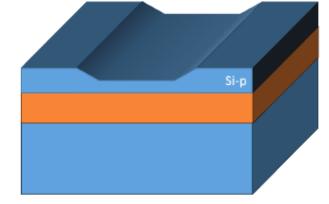

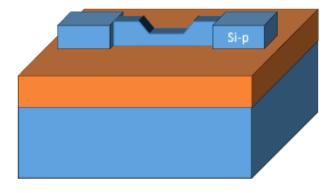

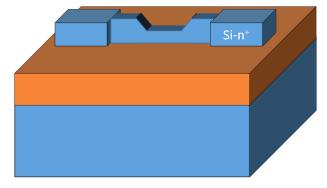

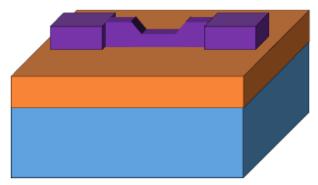

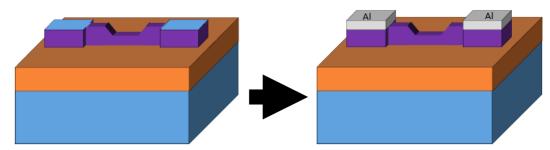

| Figure 35     | Simplified process steps of the devices fabricated in this project                                   |

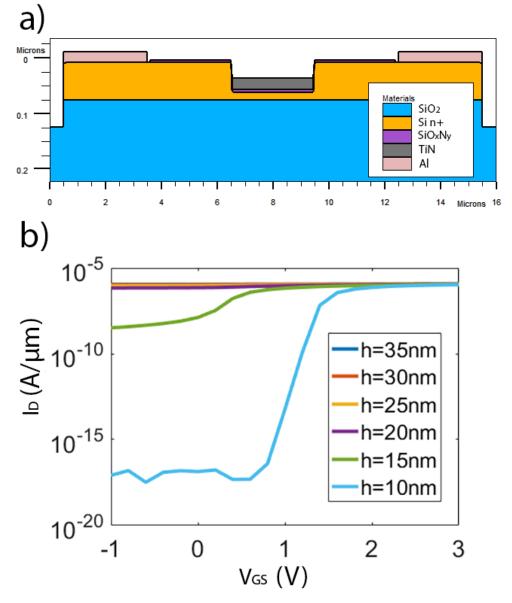

| Figure 36     | Simulation results of the JL-FET device                                                              |

| Figure 37     | $I_D \ge V_{DS}$ plot of the simulated device with a channel thickness of 10 nm 59                   |

| Figure 38     | SEM image showing the area etched in NH <sub>4</sub> OH solution                                     |

| Figure 39     | SEM images detailing the sidewall profiles of the etching in NH <sub>4</sub> OH solution.            |

|               | 61                                                                                                   |

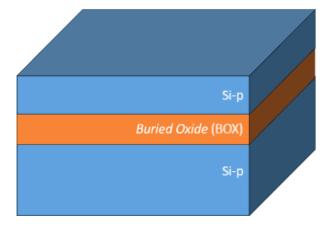

| Figure 40     | Initial wafer configuration                                                                          |

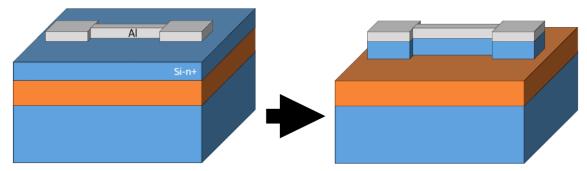

| Figure 41     | Silicon wafer after initial thinning                                                                 |

| Figure 42     | Silicon wafer after oxide barrier growth                                                             |

| Figure 43     | Silicon wafer after ionic implantation and oxide etching                                             |

| Figure 44     | Silicon wafer after dopant activation step                                                           |

| Figure 45      | Silicon wafer after hardmask definition and after active region etching in ICP-    |

|----------------|------------------------------------------------------------------------------------|

| RIE            | 65                                                                                 |

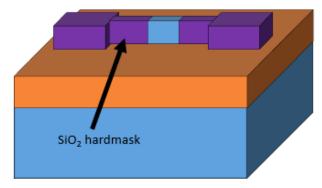

| Figure 46      | Silicon wafer after oxide hardmask deposition and definition                       |

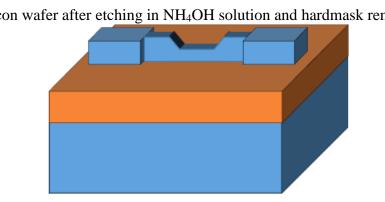

| Figure 47      | Silicon wafer after etching in $NH_4OH$ solution and hardmask removal 66           |

| Figure 48      | Silicon wafer after gate metal deposition                                          |

| Figure 49      | Silicon wafer after HF solution oxide etching to open electric contact area and    |

| after the elec | tric contact fabrication                                                           |

| Figure 50      | Silicon wafer after hardmask growth and definition for the updated process $68$    |

| Figure 51      | Silicon wafer after etching and hardmask removal for the updated process . $69$    |

| Figure 52      | Silicon wafer active region definition for the updated process                     |

| Figure 53      | Silicon wafer after dopant diffusion for the updated process                       |

| Figure 54      | Silicon wafer after gate dielectric growth for the updated process                 |

| Figure 55      | Silicon wafer after HF solution oxide etching to open electric contact area and    |

| after the elec | tric contact fabrication for the updated process                                   |

| Figure 56      | Silicon wafer gate metal fabrication for the updated process                       |

| Figure 57      | JL-FET and Pseudo-MOS biasing schematics                                           |

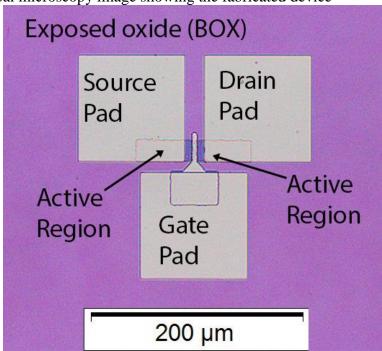

| Figure 58      | Optical microscopy image showing the fabricated device                             |

| Figure 59      | Cross-section SEM images of the device fabricated using the original               |

| process        | 76                                                                                 |

| Figure 60      | $I_DxV_{BGS}plots$ for the pseudo-MOS device fabricated using the original process |

|                | 77                                                                                 |

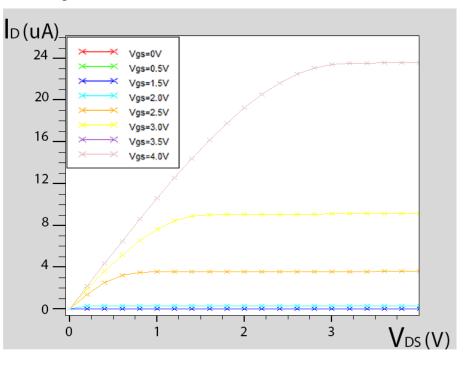

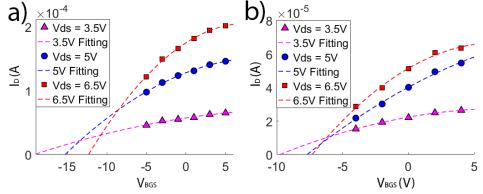

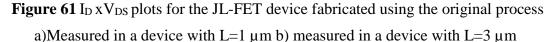

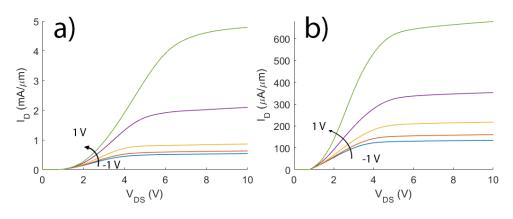

| Figure 61      | $I_DxV_{DS}plots$ for the JL-FET device fabricated using the original process 78   |

| Figure 62      | $I_DxV_{GS}plots$ for the JL-FET device fabricated using the original process 78   |

| Figure 63      | $I_D x V_{DS}$ plots for the JL-FET device simulated                               |

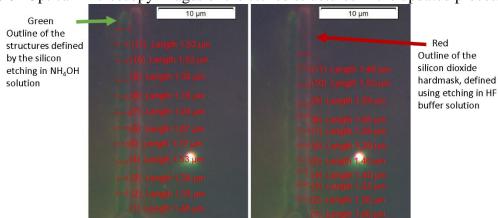

| Figure 64      | Optical Microscopy images of the etched structures in the updated process 80       |

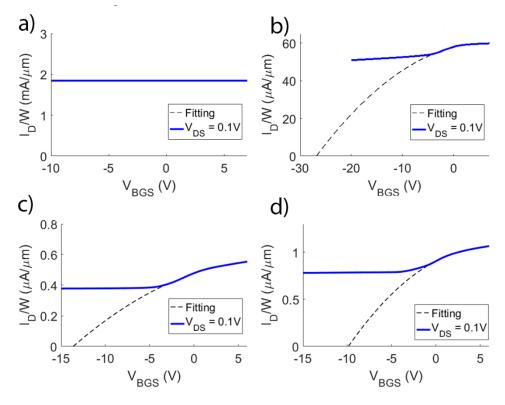

| Figure 65      | $I_DxV_{BGS}$ pseudo-MOS measurements for each sample prior to gate fabrication    |

|                | 81                                                                                 |

| Figure 66      | $V_{0}x$ etching time measurements and fitting for the fabricated samples 82       |

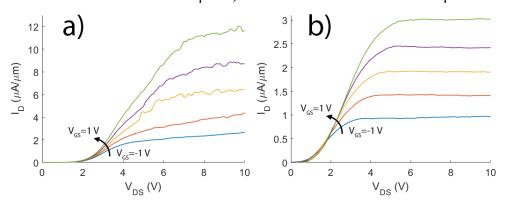

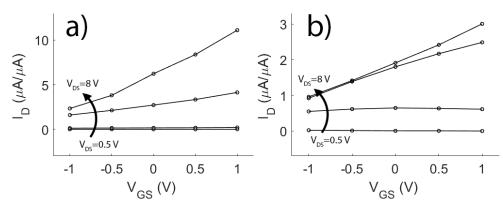

| Figure 67      | $I_DxV_{GS}$ JL-FET measurements for each sample after complete fabrication $83$   |

| Figure 68      | $I_DxV_{DS}$ JL-FET measurements for each sample after complete fabrication $84$   |

| Figure 69      | Schematics of a typical implanter (FRANSSILA, 2010)                                |

| Figure 70      | Photolithography masks used in the fabrication process. (LEONHARDT,                |

| 2016)          | 97                                                                                 |

| Figure 71      | Lift-off process flow (RUFINO, 2019, adapted)                                      |

|                |                                                                                    |

### LIST OF TABLES

| Table 1 | Steps of the Standard RCA cleaning. (PUYDINGER DOS SANTOS, 2013)               | 37 |

|---------|--------------------------------------------------------------------------------|----|

| Table 2 | Characteristics of the simulated transistor according to the channel thickness | 58 |

| Table 3 | Ion and Ioff characteristics for the fabricated devices                        | 79 |

| Table 4 | Ion and Ioff characteristics for the simulated devices                         | 79 |

| Table 5 | Sum of the square of the residuals for each fitting curve                      | 82 |

| Table 6 | Process for patterning structures with active region and gate region masks     | 98 |

| Table 7 | Process for patterning structures with the metallic pads mask                  | 99 |

## TABLE OF CONTENTS

| 1 INTRODUCTION                                                       |    |

|----------------------------------------------------------------------|----|

| 1.1 HISTORY OF MICRO AND NANOELECTRONICS                             | 18 |

| 1.2 MOTIVATION: JL-FET FABRICATION CHALLENGES                        | 21 |

| 1.3 OBJECTIVES                                                       | 24 |

| 1.4 DISSERTATION OUTLINE                                             | 24 |

| 2 FET THEORY AND PROCESSING TECHNIQUES OF JUNCTIONLE<br>FET          |    |

| 2.1 MOSFET FUNCTIONING PRINCIPLE: THE MOS CAPACITOR                  | 26 |

| 2.1.1 Charge sheet model                                             |    |

| 2.1.2 Band diagram                                                   |    |

| 2.2 TRADITIONAL ENHANCEMENT-TYPE MOSFET DEVICE                       | 32 |

| 2.3 THE JUNCTIONLESS-FET DEVICE                                      | 33 |

| 2.4 PHOTOLITHOGRAPHIC PATTERNING TECHNIQUES                          | 36 |

| 2.5 CONTAMINANTS CONTROL                                             | 36 |

| 2.5.1 Deionized water                                                |    |

| 2.5.2 Stantard cleaning                                              |    |

| 2.5.3 Organic cleaning                                               |    |

| 2.6 ANISOTROPIC SILICON ETCHING IN NH4OH SOLUTION                    |    |

| 2.7 PREVIOUS RESEARCH                                                | 41 |

| 2.7.1 The original JL-FET                                            | 41 |

| 2.7.2 Using silicon anisotropic etching in TMAH                      |    |

| 2.8 RESEARCH DEVELOPED AT CCS/UNICAMP                                | 46 |

| 2.8.1 Ga <sup>+</sup> Focused Ion Beam milling and Al diffusion      | 46 |

| 2.8.2 Ga <sup>+</sup> Focused Ion Beam milling with Ga incorporation | 48 |

| 2.8.3 Lateral etching in NH4OH solution                              | 52 |

| 2.9 IN THIS PROJECT                                                  | 54 |

| 3 SIMULATION AND EXPERIMENTAL PROCEDURES                             | 56 |

| 3.1 SIMULATION                                                       |    |

| 3.2 FABRICATION: ETCHING CALIBRATION                                 |    |

| 3.3 FABRICATION: FIRST BATCH OF JL-FET DEVICES                       | 61 |

| 3.3.1 Initial wafer configuration                                    | 61 |

| 3.3.2 Standard cleaning                                              |    |

| 3.3.3 Initial thinning                                                 | 62    |

|------------------------------------------------------------------------|-------|

| 3.3.4 Oxide barrier for ionic implantation and ionic implantation      | 63    |

| 3.3.5 Standard Cleaning and oxide etching                              | 64    |

| 3.3.6 Dopant activation and crystal structure reconstruction           | 64    |

| 3.3.7 Active Region definition                                         | 65    |

| 3.3.8 Oxide hardmask deposition and definition                         | 65    |

| 3.3.9 Silicon etching in NH4OH solution                                | 66    |

| 3.3.10 Gate oxide deposition and gate metal deposition and definition  | ı66   |

| 3.3.11 Electric contacts metallization and definition and final anneal | ing66 |

| 3.4 FABRICATION: SECOND BATCH OF JL-FET DEVICES                        | 67    |

| 3.4.1 Oxide hardmask growth and definition                             | 68    |

| 3.4.2 Silicon etching in NH4OH solution                                | 68    |

| 3.4.3 Active Regionde finition                                         | 69    |

| 3.4.4 Dopant diffusion                                                 | 69    |

| 3.4.5 Gate dielectric growth                                           | 70    |

| 3.4.6 Metal contacts patterning, fabrication and initial annealing     | 70    |

| 3.4.7 Pseudo-MOS channel characterization                              | 71    |

| 3.4.8 Gate metal patterning, fabrication and final annealing           | 71    |

| 3.5 CHARACTERIZATION                                                   | 72    |

| 4 RESULTS AND DISCUSSION                                               | 74    |

| 4.1 ORIGINAL PROCESS                                                   | 74    |

| 4.2 UPDATED PROCESS                                                    | 80    |

| 4.2.1 Optical Microscopy process confirmation                          | 80    |

| 4.2.2 Pseudo-MOS measurements prior to gate fabrication                | 80    |

| 4.2.3 JL-FET biasing measurements in the completed devices             | 83    |

| 5 SUMMARY AND CONCLUSIONS                                              | 85    |

| 5.1 PROJECT SUMMARY                                                    | 85    |

| 5.2 CONCLUSIONS                                                        | 86    |

| 5.3 FUTURE WORKS                                                       | 87    |

| 5.4 SCIENTIFIC CONTRIBUTION: PUBLICATIONS AND AWARDS                   | 88    |

| REFERENCES                                                             | 90    |

| APPENDIX A: SILICON DOPING PROCESS DESCRIPTION                         | 94    |

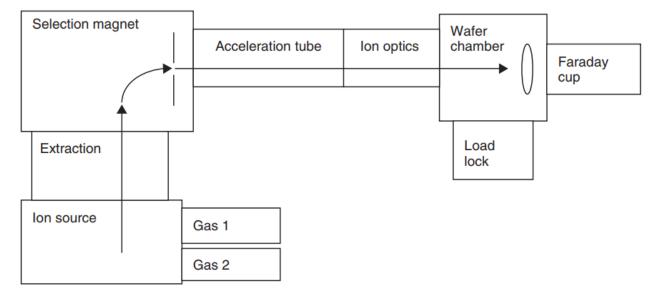

| ION IMPLANTATION                                                       | 95    |

| DOPANT DIFFUSION                                                       | 95    |

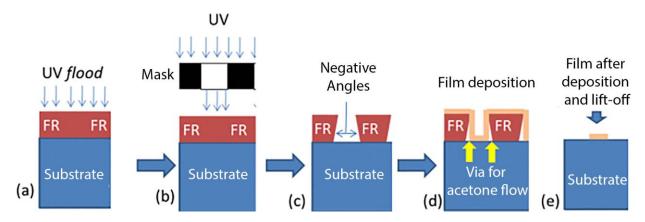

| APPENDIX B: OPTICAL PHOTOLITHOGRAPY PATTERNING | PROCESS97 |

|------------------------------------------------|-----------|

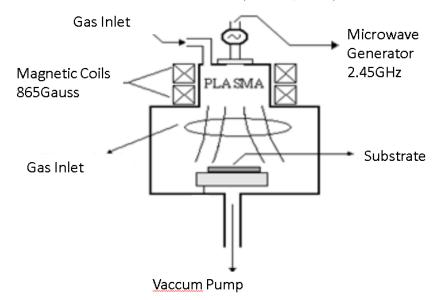

| APPENDIX C: DC SPUTTERING                      | 101       |

| APPENDIX D: ECR-CVD                            | 102       |

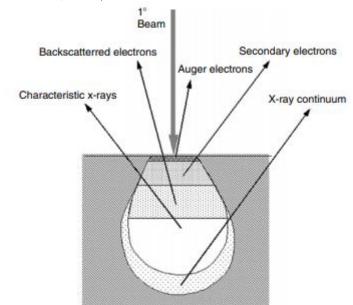

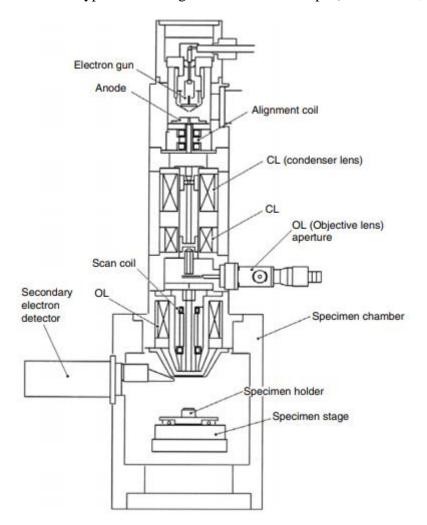

| APPENDIX E: SCANNING ELECTRON MICROSCOPY       | 103       |

# CHAPTER 1

# INTRODUCTION

#### **1.1 HISTORY OF MICRO AND NANOELECTRONICS**

To estabilish the novelty of a Junctionless-Field-Effect-Transistor (JL-FET) device, we must first understand how the inversion-type transistor became the forefront of the nanoeletronics industry. The first ever transistor patent, filed by Lilienfeld, described a depletiontype field-effect-transistor, where a thin layer of semiconductor was stacked on top of an insulator and a metal to modulate the current flow (LILIENFELD, 1930). A functional device was never showed by Lilienfeld, but soon John Bardeen and Walter Brattain obtained the first-ever functional transistor in 1947, which was called the Point-Contact Transistor (BARDEEN, 1956). The Bipolar Junction Transistor (BJT) was demonstrated by the same research group an year later (SHOCKLEY, 1984). It was only by the 1950s that the first Metal-Oxide-Semiconductor Field-Effect-Transistor (MOSFET) devices were achieved (PUERS et al., 2017), and these devices would soon take over the industry. The enhancement-type MOSFET had a lower loff that was perfect for digital applications, as when the Gate Voltage (VG) is lower than the Threshold Voltage (VTH), the device behaves as two opposing p-n diodes, blocking the current flow (SEDRA; SMITH, 2015). Also, the enhancement-type transistor was producible in a fast, cheap and reliable manner using the planar process. There is yet another configuration of MOSFETs, the depletion-type transistor. Its main issue arises when fabricated with a planar process in a bulk wafer, this results in a device with a very negative VTH, which makes it unsuitable to digital technologies (SEDRA; SMITH, 2015).

With all these characteristics, and allied to the flexibility of silicon-based materials, the planar process of enhancement-type MOSFETs drove the industry for decades. The scaling of the planar MOSFETs and evolution in processing techniques and materials culminated in an Information Technology Revolution. The speed with which the technology evolved was put into words by Gordon Moore, at the time the director of R&D in Fairchild Semiconductors and that would later become co-founder of Intel. Moore stated, in an iconic piece in 1965, that the area density of microfabricated devices would roughly double every 18 months, without any increase in production costs (MOORE, 2006). The time frame was then updated to doubling every two years in the following decades, and similar trends can still be observed today. Amidst such prolific era of technological advancements in the MOSFET devices, little to no drive to develop new devices was present.

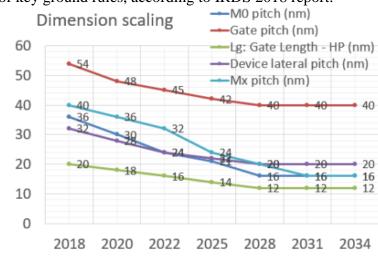

This era of rapidly advancing technology is coming to a steeping halt. As devices were scaled for decades, their dimensions are now so small that a few dozens of doping atoms are responsible for the dopant concentration in the entire device. This makes even small random dopant fluctuations (RDF) a big concern (SUZUKI et al., 2014) and faster and faster annealing techniques are needed so that de dopant diffusion during annealing steps will not compromise the steep gradient of dopant concentration required in state-of-the-art transistors. Short Channel Effects such as Drain Induced Barrier Lowering (DIBL) and Hot-Carriers injection, and Quantum Effects such as tunneling and confinement are also responsible for degradation on smaller transistors characteristics as the devices draw dangerously close to the tunneling distance (IWAI, 2016). This tendency is notable in 0, where some key ground rules of device scaling are plotted for the predicted values in the near future. MO symbolizes the distance between two interconnectors on the first metal level, the gate pitch is the distance between the channels of two devices, Lg is the effective gate length, the lateral pitch is the distance between two devices, and Mx pitch is the distance between two interconnectors of the topmost metal level. Taking the gate pitch as an example, which is a ground rule that if historically one of the main goals of scaling, it faced a steep decline in scaling speed in recent years, and is projected to stop scaling altogether as soon as 2028.

Figure 1 Scaling of key ground rules, according to IRDS 2018 report.

This sets the stage for the research and development of novel devices and structures that are capable of mitigating such effects, and continue driving the technological advancements in micro and nanofabrication. So far, the industry has been exploring new device geometries and dispositions that can increase the area density or current of each device. For instance, the finFET device is a multi-gate device that can increase the current of the device by using the sidewalls as current paths (FERAIN; COLINGE; COLINGE, 2011). Newer technologies such as the lateral Gate-All-Around (LGAA) and vertical Gate-All-Around (VGAA) are also in implementation for future technological nodes. This trend is seen in Figure 2.

| YEAR OF PRODUCTION                        | 2018   | 2020          | 2022             | 2025    | 2028         | 2031            | 2034            |

|-------------------------------------------|--------|---------------|------------------|---------|--------------|-----------------|-----------------|

|                                           | G54M36 | G48M30        | G45M24           | G42M21  | G40M16       | G40M16T2        | G40M16T4        |

| Logic industry "Node Range" Labeling (nm) | "7"    | "5"           | "3"              | "2.1"   | "1.5"        | "1.0 eq"        | "0.7 eq"        |

| IDM-Foundry node labeling                 | i10-f7 | i7-f5         | i5-f3            | i3-f2.1 | i2.1-f1.5    | i1.5e-f1.0e     | i1.0e-f0.7e     |

| Logic device structure options            | FinFET | finFET        | finFET<br>LGAA   | LGAA    | LGAA<br>VGAA | LGAA-3D<br>VGAA | LGAA-3D<br>VGAA |

| Mainstream device for logic               | finFET | finFET        | finFET           | LGAA    | LGAA         | LGAA-3D         | LGAA-3D         |

|                                           | Oxide  | S Contraction | <b>B</b><br>Oxee | Oxide   |              |                 |                 |

Figure 2 Transistor roadmap from IRDS 2018 report.<sup>1</sup>

<sup>&</sup>lt;sup>1</sup> Note from the source: "GxxMxxTx notation refers to Gxx: gate pitch, Mxx: tightest metal pitch in nm, Tx: number of tiers. This notation illustrates the technology capability. On top of pitch scaling there are other elements such as cell height, fin depopulation, DTCO constructs, 3D integration, etc. that define the target area scaling (gates/mm2)." (IRDS report, 2018)

This context made the need for newer devices and materials reemerge. Devices with higher current drives or with steeper subthreshold swings are steadily becoming more ubiquitous (CRISTOLOVEANU; WAN; ZASLAVSKY, 2016). The interest in different switching mechanisms as in tunnel-FETs were reignited (QUINN; KAWAMOTO; MCCOMBE, 1978; IONESCU; RIEL, 2011; NARIMANI et al., 2017), and research in materials became a promising topic for future technological nodes, especially in graphene-based devices and III-V materials such as GaAs.

Jean-Pierre Colinge first proposed the Junctionless-FET device (COLINGE et al., 2010) as a possible device in the next technological nodes, as impurities diffusion, surface scattering of the charge carriers and short-channel effects become increasingly hard to manage (COLINGE et al., 2010). When compared to the traditional enhancement-mode field-effect transistors, the JL-FET devices present clear advantages, such as not requiring expensive junction engineering techniques, as costly Ultra Rapid Thermal Annealing, now required to maintain the sharp dopant concentration gradients needed in inversion-mode transistors and an important focus in scaling research (KIKUCHI et al., 2019; WANG et al., 2016). It also presents a higher current, due to the higher charge carrier mobility when operating in flatband conditions and by distributing the current through the entire channel, as opposed to only superficial conduction in the inversion-type FETs (COLINGE et al., 2010). One of the advantages of the JL-FET device is full compatibility with current and planned cMOS technologies, as these devices can be implemented with the same materials and structures in every quasi-planar or 3D SOI configurations used in state-of-the-art cMOS applications (CO-LINGE et al., 2010).

#### **1.2 MOTIVATION: JL-FET FABRICATION CHALLENGES**

Despite all the advantages, the JL-FET device also brings a big technological challenge, as these are inherently nanometer-scaled devices that require state-of-the-art patterning processes. This is because the phenomena responsible for modulating the current that flows through the device is the depletion region induced and controlled by the Metal-Oxide-Semiconductor contact of the gate stack and the biasing voltage applied to it. This depletion region width is in the order of a few nanometers for highly doped silicon, which imposes a critical dimension of the same magnitude. JL-FETs were fabricated using electron-beam lithography patterning (CHUNG et al., 2018; COLINGE et al., 2010; DORIA et al., 2011; MILLAR et al., 2018; THIRUNAVUK-KARASU et al., 2017) and focused ion beam milling (LIMA et al., 2012; PUYDINGER DOS SANTOS et al., 2013); as well as being studied by simulation (GUPTA; KRANTI, 2017; RIOS et al., 2011; SAHAY; KUMAR, 2017). Besides silicon-based devices, high mobility materials such as germanium (GUPTA; KRANTI, 2017) and III-V materials (MIL-LAR et al., 2018) were also reported on the literature.

High precision processes such as electron-beal lithography and focused ion beam milling are ideal for prototyping and conceptual demonstrations, but are lacking on productivity and present high costs. This work proposes an accessible way to fabricate these structures with industrial throughputs, improving the competitivity of the JL-FET and other nanometer-scaled devices, and opening up the research possibilities to fabrication facilities that do not have access to advanced junction and patterning processes.

Replacing the traditional inversion-type MOSFET is argued to be the next step on nanoelectronics, since most scaling strategies are now encountering critical challenges that could impair further miniaturization on the coming years (IRDS 2018 UPDATE, 2018a). Multiple new devices have been proposed, and continue to be tested and studied all across the world, and once such device is the Junctionless-FET. In his report on the intricacies of nanowire transistors without junctions (COLINGE et al., 2010) proposes that the JL-FET might be the new flagship device for the next technological nodes. Before this switch can happen, new techniques to fabricate these devices in a reliable and economically viable way must be researched, as must be the intricate effects of devices with small dimensions on the functioning and stability of single and integrated systems. Therefore, the ability to fabricate nanometer-scale structures is paramount not only in achieving functional JL-FET devices, but also for a number of other devices, such as finFETs, monolithic GAA devices and tunnelFETs. The ability to evaluate the wafer-wide behavior of integrated logic devices is one of the main challenges to reduce fabrication and implementation costs of new technologies and devices (IRDS 2018 UPDATE, 2018b).

The ability to fabricate short and thin structures using the anisotropic etching of silicon was shown by laterally etching structures in the <100> direction using an Ion-Bombardment-Retarded-Etching (IBRE) process (MASAHARA et al., 2004), and by vertically etching silicon to the meeting point of the (111) planes (MIGITA et al., 2014). Structures as short as 3-nm can be seen in Figure 3, with the possibility to fabricate atomically sharp structures. The etching reagent used was Tetramethylammonium Hydroxide (TMAH). (BAN et al., 2015) also showed how the intrinsic characteristics of the anisotropic silicon etching can be used in novel and interesting ways, such as capturing nanostructured particles that can alter the device functioning.

SOARES et al. (2018) also showed that the anisotropic etching can be used as a lateral thinning technique in the <111> direction. When used to thin the wire laterally, the silicon anisotropic etching generates trapezoid-shaped channels with the (111) crystallographic planes exposed, as seen in Figure 4. The etching reagent used was NH<sub>4</sub>OH.

These research projects indicate that a vertical thinning of the silicon layer could be a viable alternative to fabricate devices with gates thin enough to achieve JL-FET functioning, with gates long enough to minimize short channel effects by stopping the etching process before the sharp v-groove profile can form.

#### **1.3 OBJECTIVES**

As a way to allow the fabrication of JL-FET devices, and therefore of other devices which require dimensions thinner than 100 nm, we propose the usage of the anisotropic etching of silicon in an ammonium hydroxide (NH<sub>4</sub>OH) solution. This kind of etching is accessible and cheap, presents almost negligible etching rate to the oxide hardmask used to define the etched regions and does not cause the introduction of contaminating ions and materials on silicon substrate.

This project intends on develop and demonstrate the fabrication of structures thinned using silicon etching in NH<sub>4</sub>OH solution. A comprehensive study of the process will be described, with numerical models in SILVACO Athenas and Atlas, evaluation of the device parameters according to etching time and processing techniques.

Another set of novelties established by this project is the fabrication of sub-100-nm devices using dopant diffusion. Dopant diffusion sees little use in semiconductor fabrication due to poor controllability of dopant concentration and junction depth, which is incompatible with the shallow junction and steep dopant concentration gradients needed for traditional enhancement-type MOSFET. When fabricating JL-FETs, on the other hand, these characteristics are not as problematic, and diffusion becomes a powerful technique as it does not introduce as many defects in the silicon crystal as the high-energy ions introduced by ion implantation.

The JL-FET device fabrication and characterization was chosen as an evaluating technique for the proposed process. Chapter two starts by presenting the charge distribution in MOS structures as basis to analyze the intricacies and particularities of JL-FET device functioning when compared to the traditional devices.

#### 1.4 DISSERTATION OUTLINE

In chapter one, the history of the nano and micro electronics industry was layed out to better contextualize the junctionless-FET device and its place in technological innovation. The challenges for the fabrication of these devices and some the techniques that other research works used to achieve working devices were also presented. In the end, the main objective was presented, to achieve a competitive new process for the fabrication of nanometer-scaled JL-FET devices.

In chapter two, the general field-effect-transistor theory and fabrication techniques are presented.

The MOSFET usage in circuit design and its representations show how these devices work as a component. The MOS capacitor theory is then presented to elaborate on how these devices work physically, enabling further distinction between the two categories of devices presented: the enhancement-type MOSFET device, that dominates the landscape of state-ofthe-art nanoelectronics, and the JL-FET, which is the device proposed to take on the next technological nodes.

The techniques used in MOSFET fabrication are described in a broader sense, with patterning techniques, physical and chemical processes and procedures for contaminants control.

The techniques used for traditional fabrication of JL-devices are also presented, as are alternative techniques that were established to achieve functioning devices and techniques previously used by the nanoelectronics group at CCS/UNICAMP. At the end of chapter two, the processes investigated in this work are presented in their context.

In chapter three, the process flow is outlined step-by-step. The necessary cleaning and patterning are listed, as described in chapter two. The numerical simulation and etching rate studies are described, as the results were used in planning the methods. The first process is explained in detail, while the second process is defined by its differences and improvements upon the first.

In chapter four, the results from both of the fabrications are presented. The devices were characterized both structurally, using Scanning Electron Microscopy (SEM) imaging and optical microscopy, and electrically, using Pseudo-MOS and Junctionless biasing techniques.

In chapter five, the conclusions are presented, along the publications and accolades received during this research work.

In the appendices, succinct explanations of the processes and equipments utilized are presented.

# CHAPTER 2

# FET THEORY AND PROCESSING TECHNIQUES OF JUNCTIONLESS-FET

#### 2.1 MOSFET FUNCTIONING PRINCIPLE: THE MOS CAPACITOR

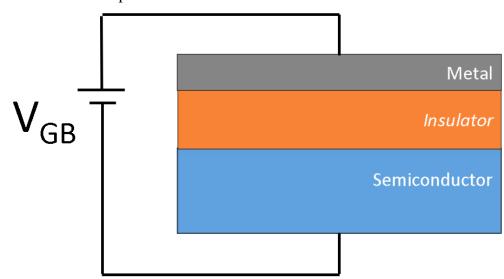

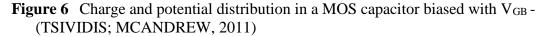

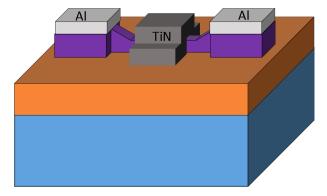

The main structure responsible for the current control in the traditional MOSFETs fabricated with the planar process to 3D MOSFETs and in JL-FET devices is the MOS capacitor. The MOS capacitor is defined by the stack of a metal film, an insulator film and a semiconductor film, as seen in Figure 5 with the external biasing voltage,  $V_{GB}$ .

Figure 5 The MOS Capacitor

This configuration means that, as any other capacitor, variations on the biasing voltage incurs in variations on the superficial charges. There is a layer of charge in the metal, called  $Q_G$ , a layer of charge trapped in the insulator-semiconductor interface, called  $Q_0$ , and a layer of charge in the semiconductor,  $Q_C$ . Understanding  $Q_C$  is the objective of studying the MOS capacitor, as it is responsible to modulate the current flow in MOSFET devices.

#### 2.1.1 Charge sheet model

The surface charge method involves calculating the surface potential and the charge density for each biasing voltage. It is a powerful tool to understand the charges involved and their behavior according to the capacitor functioning conditions.

Using the charge sheet approximation, where it is assumed that the charge is confined to a very thin layer on the semiconductor surface, it is possible to write Poisson's equation (equation 1), as equation 2, and derive an expression for the surface charge  $Q'_c$ , presented in equation  $3.\Psi_s$  is the surface potential of the charge sheet model,  $\Psi(y)$  is the potential in the point y,  $\rho(y)$  is the charge density in the point y,  $\varepsilon_s$  is the absolute permittivity of the semiconductor, q is the elementary charge,  $\Phi_t$  is the thermal voltage,  $p_0$  is the surface density of holes,  $n_0$  is the surface density of electrons,  $N_D$  is the concentration of donor atoms,  $Q'_c$  is the surface density of capacitor charges and  $n_i$  is the intrinsic concentration of charge carriers in the semiconductor.

$$\frac{d^2\psi(y)}{dy^2} = -\frac{\rho(y)}{\varepsilon_s}$$

Eq. 1

$$\frac{d^2\psi_s}{dy^2} = \frac{-q}{\varepsilon_s} (p_0 e^{-\psi(y)} / \phi_t - n_0 e^{\psi(y)} / \phi_t + N_D)$$

Eq. 2

$$Q_C' = \pm \sqrt{2q\varepsilon_s} \sqrt{\Phi_t \frac{n_t^2}{N_D} \left( e^{-\psi_s/\phi_t} - 1 \right) + N_D \Phi_t \left( e^{\Phi_s/\phi_t} - 1 \right) + N_D \psi_s} \qquad \text{Eq. 3}$$

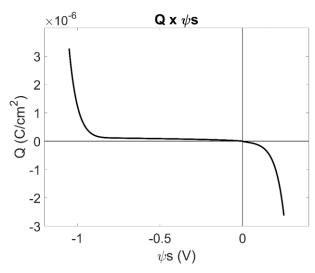

By solving equation 3 numerically, it is possible to plot the  $Q'_C x \psi_s$  behavior of the MOS capacitor, as seen in Figure 7. The parameters used are for an-type substrate, with initial doping concentration of 5.10<sup>16</sup> phosphorus atoms/cm<sup>3</sup>, a 10-nm-thick hafnium dioxide (HfO<sub>2</sub>) oxide layer, and a TiN metal layer.

**Figure 7**  $Q'_{c} x \psi_{s}$  plot of the example MOS capacitor

The relation of the surface potential to the external voltage is written in equation 4, where  $\Psi_{ox}$  is the voltage drop across the oxide and  $\Phi_{MS}$  is the metal-semiconductor potential.

$$V_{GB} = \Psi_{ox} + \Psi_S + \Phi_{MS}$$

Eq. 4

The voltage drop in the oxide is given in equation 5, where  $Q'_o$  is the area density of charges in the oxide-semiconductor interface and  $C'_{ox}$  is the capacitance per area of the MOS capacitor.

$$\Psi_{ox} = -\frac{Q'_o}{c'_{ox}}$$

Eq. 5

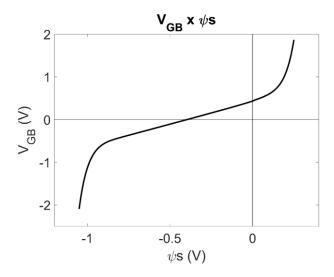

By solving equations 4 and 5, it is possible to plot a  $V_{GB} x \psi_s$  curve for the MOS capacitor, in 0. In this figure it is possible to notice the  $\psi_s$  saturation, when V<sub>GB</sub> exceeds the range of approximately 0.55V around the opposite of the flatband voltage, increasing V<sub>GB</sub> further has little effect on  $\psi_s$ . The saturation effect is the main limit on increasing inversion and accumulation regions by increasing or decreasing the external biasing.

**Figure 8**  $V_{GB} x \psi_s$  plot of the example MOS capacitor

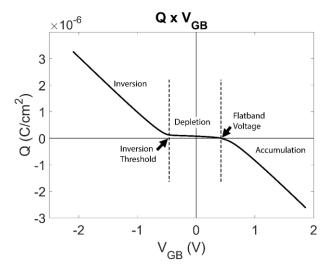

By combining the results plotted in both Figure 7 and 0, it is possible to achieve the final behavior of the surface charges according to external bias,  $Q'_C \times V_{GB}$ , plotted in0. In the  $Q'_C \times V_{GB}$  plot, there are three regions indicated: Accumulation, Depletion and Inversion. These conditions are of utmost importance for the functioning of MOSFET devices. By shifting the charge density and polarity on the semiconductor surface through the gate bias, the current can be modulated.

**Figure 9**  $Q'_{C} \times V_{GB}$  plot of the example MOS capacitor

In accumulation, the majority charge carriers, those with the same charge type of the semiconductor doping, start to accumulate on the semiconductor-oxide surface, increasing the superficial density of charges.

In depletion, the only charges present are those of the ionized doping atoms. Because those atoms are in a substitutional position in the silicon crystallographic structure, these are not charge carriers due to having no mobility, and no current can flow through this configuration.

In inversion, in addition to the doping atoms, opposite charge type carriers of the semiconductor charges are generated in the surface, giving this region its name. There are two main thresholds, the weak inversion threshold voltage, where the minority charges start to appear, and the strong inversion threshold voltage where the inversion charges become dominant.

In the flatband voltage, no charges resulting from the capacitor operation are present, only those extrinsically introduced charges from the semiconductor doping. In this configuration, the outside biasing is equal, but opposite, to the metal-semiconductor and the oxide voltage drops, thus making every perpendicular electric field to be cancelled. The net zero electrical field also implicates lesser surface scattering of the charge carriers, and then the semiconductor behaves as a resistor with a resistivity dependent on dopant concentration. In these conditions, (COLINGE et al., 2010) argues that it can be said that the semiconductor presents "bulk mobility".

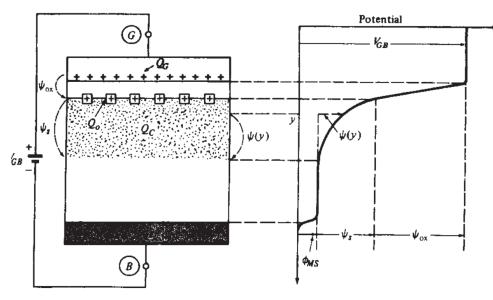

#### 2.1.2 Band diagram

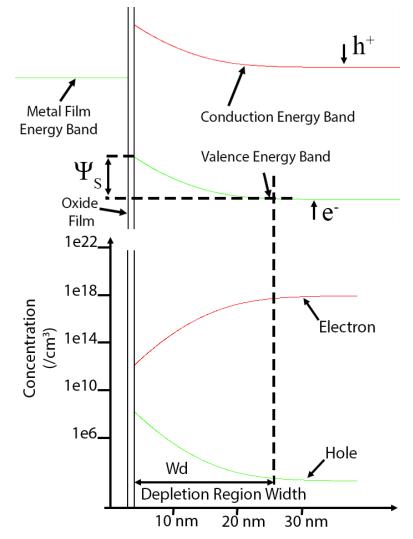

The charge sheet model is most useful when used to define the charge carriers polarity and superficial density in a MOS capacitor. When there is a need to evaluate these charge carriers according to depth in the semiconductor, another tool is used, the Band Diagram. The band diagram is an approximation that consists of plotting the energy levels of the materials used in the y-axis, and the depth in the x-axis. The energy level for holes increased downwards, while the energy level for electrons increases upwards. Known parameters such as the electron affinity, work function and Fermi level are used to situate the bands of different materials in regard to one another. Junctions are then drawn by following current flow or charge carrier accumulations in the materials involved. It is used as a way to visualize the energy levels and the effects of the MOS capacitor on electric field, charge carrier concentration and potential barriers. Due to being an approximation, exact energy levels are usually omitted and are characterized by their relation to one another, although calculated energy and depth values can be added to illustrate junctions and biasing. In a band diagram, the effects of the MOS capacitor construction and the external biasing are readily visible, and other parameters such as electric potential and voltage barriers can be easily estimated. 0(a) shows the band diagram of a common MOS capacitor compromised of a TiN metal layer, with a work function of around 4.7 eV, a 2 nm thick silicon oxide layer and a semiconductor substrate of n-type silicon with a dopant concentration of approximately 10<sup>18</sup> atoms.cm<sup>-3</sup>. In 0(b) it is possible to see the decrease in electron concentration and increase in hole concentration according to the depth, since the hole concentration is not higher than the electron concentration, the surface is in depletion. This image is aligned to the band diagram to show the correlation between charge density, most easily calculated in the charge sheet model, and the energy bands of the band diagram.

Figure 10 Complete band diagram and charge concentration plot for the example MOS capacitor.

The electron energy level axis and the holes energy level axis are represented by arrows labeled  $e^{-}$  and  $h^{+}$ , respectively. The surface potential, $\psi_{S}$ , and the depletion region width,  $W_d$ , are represented.

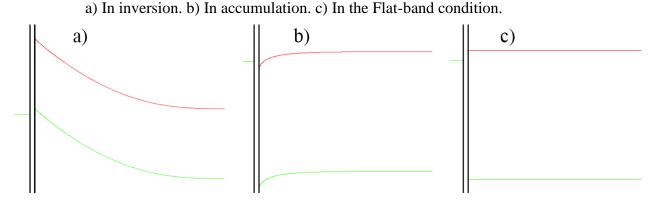

By introducing the external voltage  $V_{GB}$  the bands can be shifted up and down in relation to one another. In Figure 11 the MOS capacitor represented above is biased to achieve the superficial state of inversion, accumulation and in the flatband voltage.

Figure 11 Band diagram of the example MOS capacitor for different biasing conditions.

2.2 TRADITIONAL ENHANCEMENT-TYPE MOSFET DEVICE

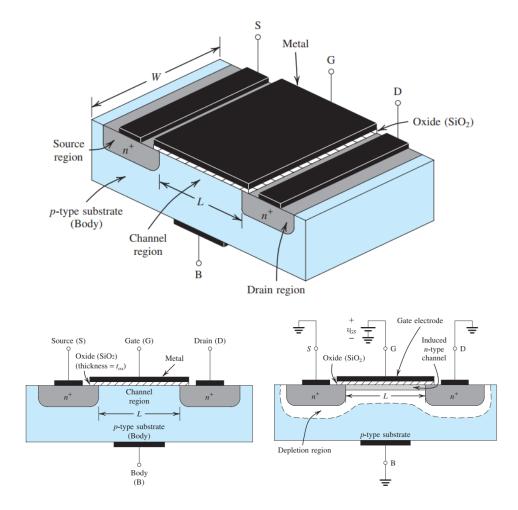

Enhancement-type MOSFETs are the standard device in the micro and nanoelectronics industry. Their market penetration is well-explained: they are easy to manufacture, present a good  $I_{on}$  /  $I_{off}$  ratio and very good parameter control. They have been miniaturized and improved upon since their inception in the 1950s.

The functioning principle of the enhancement-type MOSFETs is simple: initially, two opposing p-n junctions act as a very efficient barrier for the electric current, driving down I<sub>off</sub> figures. In the material that is closer to the gate oxide, the effects of gate bias is able to drive the semiconductor into inversion as soon as the gate voltage surpasses the threshold voltage. In this configuration, there is a continuous conduction path from source to drain made up entirely of electron-rich silicon. Since the semiconductor must be driven into inversion for the current to flow, NMOS devices are fabricated on p-type wafers by implanting the drain and source regions, and PMOS devices are fabricated on n-type wafers by the same technique. Usually a polycrystalline silicon gate is deposited and defined before the source-drain implantation, in what is called a "self-aligned" process. When this polycrystalline gate is removed and another metal gate is fabricated, it is a process named "dummy gate". The depletion-type MOSFET has the same principles, but a channel is implanted in the substrate, allowing current flow event at 0 V gate bias.

#### 2.3 THE JUNCTIONLESS-FET DEVICE

The main difference between the JL-FET and the traditional inversion-type MOSFETs is the flat dopant concentration across the device, and therefore an absence of pn junctions. Normally, this structure would act as a gated-resistor, since the electrostatic control that stems from the MOS gate-stack does not have a very good control on the charge carriers present on the devices channel.

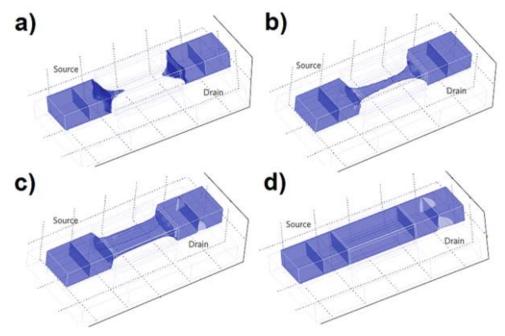

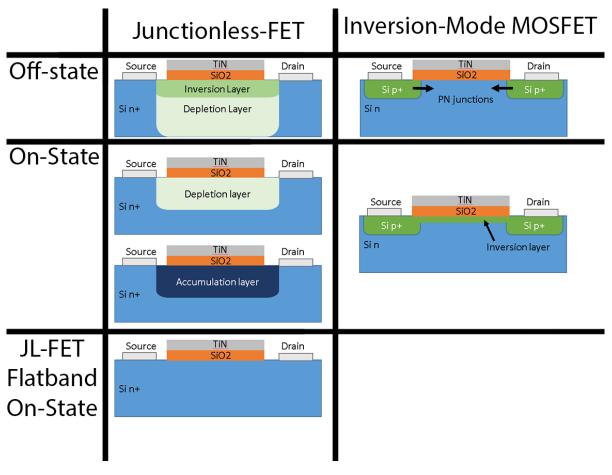

To operate this device as a transistor, the gate dimensions, or at least one of them, must be equal or thinner than the depletion region width when the gate voltage is 0V. In these conditions, the gate-stack will be able to deplete every charge carrier, thus creating the cut-off region of the transistor operation. When a bias voltage is applied to the gate-stack, the surface potential diminishes, and the depletion region gets narrower, thus permitting the current flow. As more charge carriers are available to participate in the current flow, the magnitude raises. The charge carrier concentration is represented in Figure 13.

**Figure 13** Representation of the charge carrier density in a JL-FET device.(COLINGE et al., 2010)

a) when  $V_{GS} < V_{TH}$ , the channel is completely depleted. b) when  $V_{GS}$  is near  $V_{TH}$ , the sub-threshold region, the channel begins to form. c) when  $V_{GS} >> V_{TH}$  the channel is completely formed. d) when  $V_{GS} = V_{FB}$  the device is in flatband condition, the net perpendicular electric field is null and the device is a doped-silicon resistor.

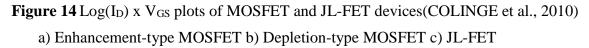

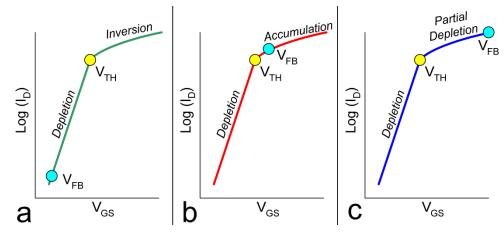

The current response for the gate voltage in JL-FET devices in comparison with enhancement and depletion type MOSFETs is plotted in 0, while the charge carrier layers and physical comparison of JL-FET and inversion-mode transistors is presented in Figure 15. While comparing the physical structure of both devices side by side, one of the main differences between inversion-mode and JL-FET devices is evident: in inversion devices, the current flow is mainly comprised of minority charge carriers, introduced by the inversion-layer, while in JL-FET devices the majority carriers are the main components of current.

Figure 15 Comparison of charge carrier and dopant concentrations in JL-FET and inversion-mode MOSFETs

#### 2.4 PHOTOLITHOGRAPHIC PATTERNING TECHNIQUES

The patterning process used throughout the fabrication was the optical photolithography, which consists of using light to transfer the patterns from a prefabricated mask onto the samples, through photosensitive reactions in a polymer called photoresist. This process is well established and is used in high-end industrial fabrication plants due to its high throughput, as a flood exposition process capable of patterning thousands of dies with each exposure, and good precision and minimum line length built over decades of technological advancements. Such as the projection lithography, where an array of lenses can improve the patterned structures, and immersion lithography.

#### 2.5 CONTAMINANTS CONTROL

In nanoelectronics, even the smallest contaminants can have destructive effects. Therefore, all device processing must be performed in clean room environment, and precise cleaning techniques must be used. This section is dedicated to explaining the optimal conditions and how to achieve them.

#### 2.5.1 Deionized water

In semiconductor processing, metallic ions such as  $K^+$  and  $Na^+$  must be eliminated, since they present high mobility inside silicon oxide and monocrystalline silicon, and could damage the solid structure of the materials. Therefore, water used in semiconductor processing must be purified and deionized by filtering and ionic exchange with especially engineered membranes. To be adequate for semiconductor processing, deionized water must present a resistivity of 18 M $\Omega$ .cm.

# 2.5.2 Stantard cleaning

The standard cleaning, or RCA cleaning, is used as a first cleaning technique in new wafers and every front-end-of-line cleaning process thereafter. In back-end-of-line processes this cleaning gives place to the organic cleaning, since the alkaline and acidic solutions used are metal etchants. It is responsible to remove organic and metallic contaminants and is performed in a 4-step system, with rinsing in deionized water after each step, as seen in table 2.

| Table 1 Steps of the Standard RCA cleaning | g. (PUYDINGER DOS SANTOS, 2013) |

|--------------------------------------------|---------------------------------|

|--------------------------------------------|---------------------------------|

| Reagents                                                                             | Ratio | T (°C)              | Time   | Comments                                                                                                                                                                                                |  |

|--------------------------------------------------------------------------------------|-------|---------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| H <sub>2</sub> SO <sub>4</sub> /H <sub>2</sub> O <sub>2</sub>                        | 4:1   | 80                  | 10 min | This step removes organic com-<br>pounds from the surface of the sil-<br>icon wafer. As a result of this reac-<br>tion, silicone dioxide is formed in<br>the surface.                                   |  |

| HF/H <sub>2</sub> O                                                                  | 1:10  | Room<br>temperature | 10 s   | The hydrofluoric acid removes<br>the silicon dioxide formed in the<br>first step.                                                                                                                       |  |

| H <sub>2</sub> O                                                                     | -     | Room<br>temperature | -      | Rinsing in deionized water with resistivity of 18 MΩ.cm                                                                                                                                                 |  |

| NH4OH/H2O2/H2O<br>(RCA standard<br>cleaning #1)                                      | 1:1:5 | 80                  | 10 min | This step removes organic com-<br>pounds and metals from the 1B<br>and IIIB groups of the periodic ta-<br>ble. This step also causes an in-<br>crease in the superficial roughness<br>of the substrate. |  |

| H <sub>2</sub> O                                                                     | -     | Room<br>temperature | -      | Rinsing in deionized water with<br>resistivity of 18 MΩ.cm                                                                                                                                              |  |

| HCl/H <sub>2</sub> O <sub>2</sub> /H <sub>2</sub> O<br>(RCA standard<br>cleaning #2) | 1:1:5 | 80                  | 10 min | This step removes alkaline ions<br>and Fe, Al, and Mg hydroxides.<br>Also polishes chemically the sur-                                                                                                  |  |

37

|                     |      |                     |      | face of the wafer, which had be-<br>come rough after the<br>NH4OH/H2O2/H2O step.      |

|---------------------|------|---------------------|------|---------------------------------------------------------------------------------------|

| H <sub>2</sub> O    | -    | Room<br>temperature | -    | Rinsing in deionized water with resistivity of 18 MΩ.cm                               |

| HF/H <sub>2</sub> O | 1:10 | Room<br>temperature | 10 s | The hydrofluoric acid removes<br>the silicon dioxide formed by the<br>last two steps. |

| H <sub>2</sub> O    | -    | Room<br>temperature | -    | Rinsing in deionized water with resistivity of 18 MΩ.cm                               |

# 2.5.3 Organic cleaning

Organic cleaning is used in back-end-of-line processing, where metallic films are already present in the structures and alkaline and acid solutions cannot be used. It is also widely used to remove photorresists and other polymeric films where the full RCA cleaning is not needed.

The organic cleaning, consists of a quick rinse in cold acetone, followed by a 10 minutes bath in acetone heated to its boiling point in a hotplate, and a 10 minutes bath in isopropyl alcohol also at its boiling point in a hotplate. Rinse in deionized water and isopropyl alcohol with drying in a 110°C hotplate.

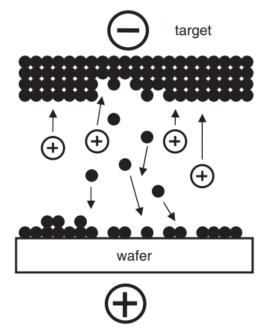

# 2.6 ANISOTROPIC SILICON ETCHING IN NH4OH SOLUTION

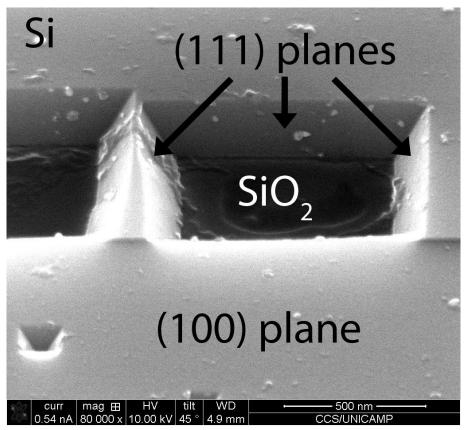

The anisotropic silicon etching is a process in which the silicon is etched in an alkaline solution. This kind of etching reacts about ten times faster with the (100) family of crystallographic planes in silicon than it does with the (111) family of planes, giving the etched structures a distinct V shapes most commonly known as V-Groove(SHIKIDA et al., 2002). In (100) wafers, the sidewalls present a constant angle of 54.74° to the surface of the wafer. These structures can therefore be manipulated to fit a number of etched thicknesses, transferred patterns and effective etched patterns. Other works showed device fabrication by using the atomically sharp edge of the V-groove to fabricate 3 nm-long devices with TMAH (MIGITA et al., 2012, 2014), and using NH4OH to thin structures sideways using the more controlled (111) etching rate (SILVA et al., 2014).

The anisotropic silicon etching etching can be achieved in a number of alkaline solutions, such as KOH, hydrazine, Tetramethylammonium Hidroxide (TMAH) and NH4OH. KOH solutons are commonly used in Micro Eletromechanichal Systems (MEMS), and although it is a cheap and well-understood process for silicon anisotropic etching, it causes K<sup>+</sup> ions incorporation in silicon and silicon dioxide, making it unsuitable for nanoeletronics fabrication. TMAH is another alternative, commonly found in most fabrication plants in photoresist developers as it presents a controlled, slow etching rate, and does not introduce metal ions such as K<sup>+</sup>. In this work, the NH4OH solution was chosen to perform the silicon anisotropic etching. This solution can be about 10 times cheaper than TMAH solutions, has a higher etching rate and has then same ion-free properties, making it a perfect choice for accessible nanoeletronics fabrication.

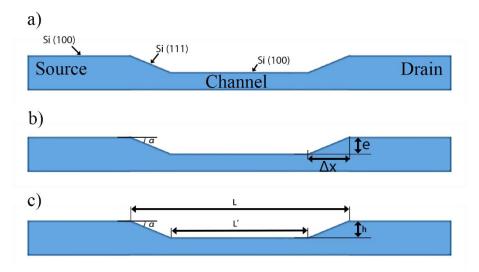

The anisotropic etching rate of alkaline solutions can be seen represented in in greater detail in Figure 16. In Figure 16 (a), the exposed crystallographic planes of the silicon are shown. The angle of the sidewall can be calculated by taking the angle between (100) planes and (111) planes. It is approximately 54.74° as shown in Figure 16 (b).

In Figure 16 (b), the sidewall angle can be used to correlate the etched thickness and the gate length variation, and an effective gate length L<sup>'</sup> can be calculated using equation 8, as seen in Figure 16 (c).

$$L' = L - \frac{2h}{\tan(a)}$$

Eq. 6

$$L' = L - \frac{2h}{\tan(54.74)}$$

Eq. 7

$$L' \cong L - 1.41h \qquad \qquad \text{Eq. 8}$$

Figure 16 Sidecut view of a structure etched in NH<sub>4</sub>OH solution.

Figure 17 SEM image of a structure etched in NH<sub>4</sub>OH solution.

The etching times chosen were calibrated according to previous tests, as described in Chapter 4. As a general rule, it is better to design a longer etching time since this process takes a few seconds to achieve thermal equilibrium, making the etching rate chaotic during the first seconds. Large quantities of Ammonia gas are also a byproduct, causing the formation of gas bubbles on the etched surface and impairing the etchant circulation. In longer processes, the unpredictable effects of both these phenomena are statistically smoothed, creating a better etch rate function.

# 2.7 PREVIOUS RESEARCH

# 2.7.1 The original JL-FET

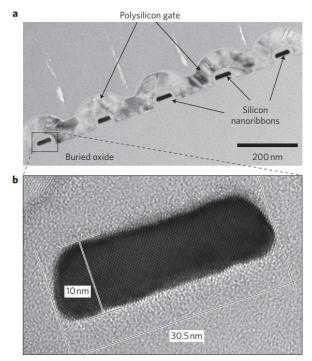

First proposed in 2010, the JL-FET devices in (COLINGE et al., 2010) were fabricated using 10-nm-thick and a few tens of nanometers wide silicon channels, called "silicon nanoribbons", defined using electron beam lithography. The channel doping was performed by ionic implantation of arsenic to yield an uniform doping concentration of  $2x10^{19}$ to  $5x10^{19}$ atoms/cm<sup>3</sup>. The gate oxide was a 10-nm-thick grown silicon oxide and the gate was fabricated using polycrystalline silicon. The Transmission Electron Microscopy (TEM) images of the fabricated devices are shown in Figure 18.

Figure 18 TEM images of the devices fabricated by (COLINGE et al., 2010).

"a) Five parallel devices with a common polysilicon gate electrode. b) Magnification of a single nanoribbon device. Individual atomic rows can be seen in the silicon"(COLINGE et al., 2010).

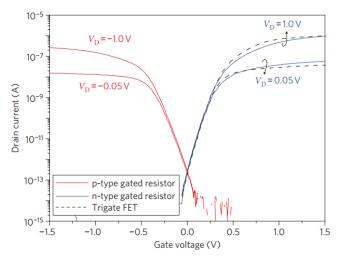

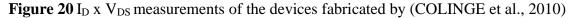

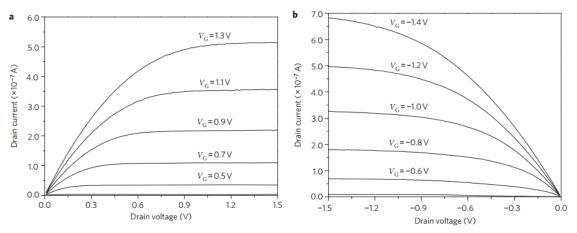

The electric characteristics of the devices shown were parallel to those of the stateof-the-art MOSFETs. In the  $I_D \ge V_{GS}$  plots, shown in 0, the on/off current ratio was larger than  $1 \ge 10^6$ , and the substhreshold swing was of 64 mV/dec, close to the theoretical minimum of 60mV/dec. The curve for a trigate FET is also shown for comparison. In the  $I_D \ge V_{DS}$ plots, shown in Figure 20, the typical transistor behavior is seen, with clear cut-off, triode and saturation regions.

Figure 19 I<sub>D</sub> x V<sub>GS</sub> measurements of the devices fabricated by (COLINGE et al., 2010)

"Drain current versus gate voltage for drain voltages of +50 mV and +1 V. The off current is below the detection limit of the measurement system  $(1x10^{-15} \text{ A})$ , and the on/off current ratio for between V<sub>G</sub>=0 and V<sub>G</sub>=+1 V is larger than  $1x10^6$ . The width of the device is 30 nm. The curve for a classical trigate FET is shown for comparison." (COLINGE et al., 2010)

"a,b, Drain current versus drain voltage for different values of gate voltage for an nchannel gated resistor (a) and a p-channel gated resistor (b). The width of the nanowires, W, is 20 nm and the gate length, L, is 1 mm, such that W/L=0.02." (COLINGE et al., 2010)

#### 2.7.2 Using silicon anisotropic etching in TMAH

Devices fabricated using silicon etching in TMAH solution were shown by (MIGITA et al., 2012, 2014). In (MIGITA et al., 2014), the surface of a 88-nm-thick silicon over 144-nm-thick silicon dioxide SOI substrate was used. The surface orientation was (100) and the initial dopant concentration was  $10^{15}$  atoms/cm<sup>3</sup> of boron. The surface was covered with a thin film of SiO<sub>2</sub> and slit patterns were drawn using electron lithography, the oxide film in these slit patterns were then etched using HF solution. The silicon wafers were then dipped into a 25 wt% solution of TMAH at room temperature. A 3-nm-thick HfO<sub>2</sub> film was then deposited by atomic layer deposition for the gate dielectric film. A 10-nm-thick TaN film and a 100-nm-thick polycrystalline Si film were then deposited as gate metal by dc sputtering and chemical vapor deposition. The gate was then patterned using electron-beam lithography and reactive ion etching. The wafers were then implanted for both p-type (BF<sup>2</sup> at 15keV and dose of  $2*10^{15}$  atoms/cm<sup>2</sup>) and for n-type (P at 15keV and dose of  $2*10^{15}$  atoms/cm<sup>2</sup>). The electric contacts metallization and final annealing in H<sub>2</sub> gas at 400C for 30 minutes were performed.

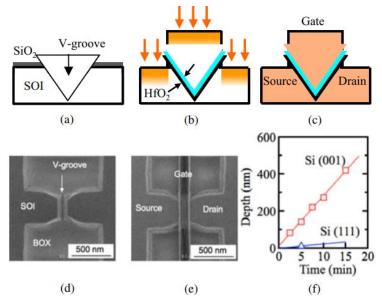

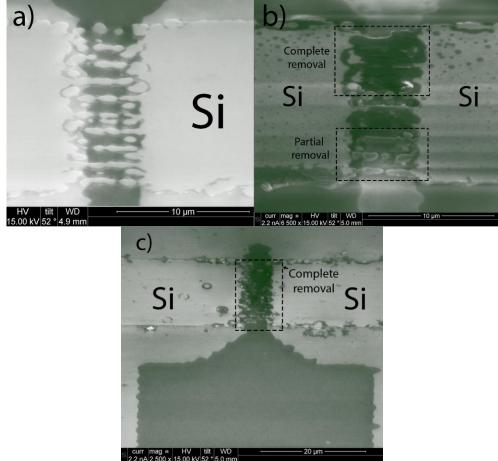

Figure 21 Process flow outline of (MIGITA et al., 2014).

"(a) Partial removalof SiO2 mask and anisotropic wet etching of SOI substrate using TMAH solution. (b) Deposition of gate stack films, gate electrode patterning, and ionimplantation. (c) Long-period annealing for diffusion and activation of dopants( $1000 \circ C 10 \text{ min}$ ). (d) SEM image of the V-groove formed on SOI. (e) SEMimage after the gate patterning. (f) Anisotropic wet etching nature of Si substrate" (MIGITA et al., 2014)

In the first attempt of this study, the devices showed partial oxidation of the device channel during dopant activation, as seen in Figure 22, and degradation on the electrical characteristics. The device is normally-on, due to the 3.2-nm effective oxide thickness (EOT).

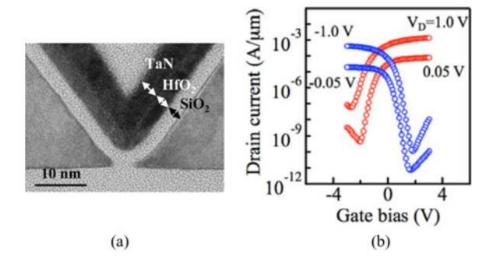

Figure 22 TEM images and I<sub>D</sub> x V<sub>GS</sub> measurements of (MIGITA et al., 2014) 3.2 nm EOT devices

"(a) Cross-sectional TEM image of the V-groove MOSFET with 3.2-nm EOT. (b) Measured ID -VG characteristics (VD = 0.05 and 1.0 V) of n-type and p-type V-groove MOSFETs with 3.2-nm EOT, 1-nm channel thickness, and 1-mm channel width." (MIGITA et al., 2014)

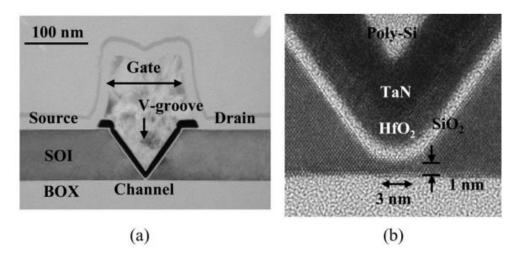

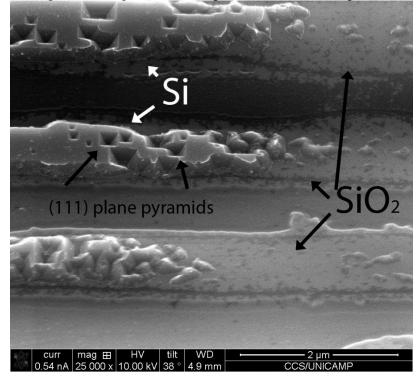

After reducing the EOT to 1.5 nm, and adding a SiN film deposited before the  $HfO_2$  deposition to prevent oxygen diffusion towards the silicon substrate, the devices showed much better electrical characteristics. In 0, the TEM images of the device fabricated with this method is shown, the 1-nm-thick and 3-nm-long device channel is visible with clear distinction of the (100) and (111) planes in silicon. The curving of the sidewalls nearing the channel is argued to be caused by the formation of meta-stable (311) planes in the interface (SHIKIDA et al., 2002).

Figure 23 Cross-Section TEM images of the devices fabricated in(MIGITA et al., 2014)

"(a) Cross-sectional TEM image of the V-groove junctionless FET. The V-groove was formed by anisotropic wet etching of SOI substrate. Source, channel, and drain regions are uniformly doped with high concentration. (b) Magnified image of the channel region. The channel length and the thickness are scaled to 3 and 1 nm, respectively. The gate stack consists of poly-Si/ TaN/ HfO2 /SiO2 layers. The EOT is 1.5 nm and the effective work function is 4.46 eV that were evaluated by C–V measurements MOS capacitors fabricated by the same process flow." (MIGITA et al., 2014)

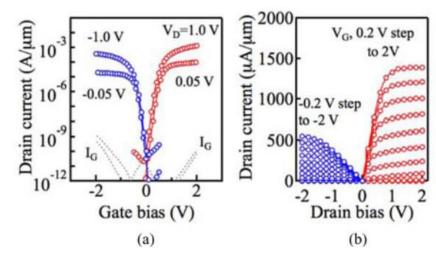

In 0, the  $I_D \times V_{DS}$  and  $I_D \times V_{GS}$  characteristics are shown. The devices presented good  $I_{on}/I_{Off}$  ratio, excellent substhreshold swing and telltale transistor behavior on the  $I_D \times V_{DS}$  curve.

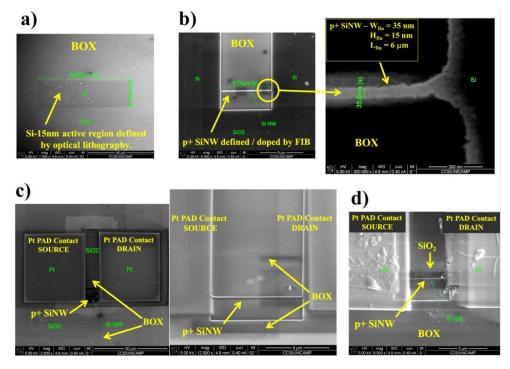

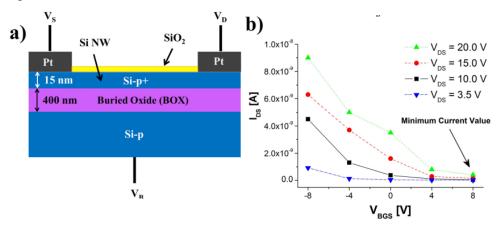

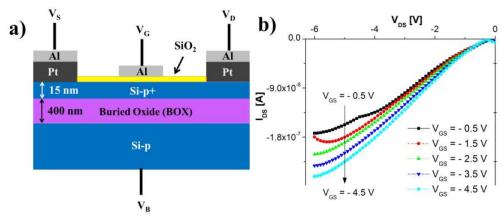

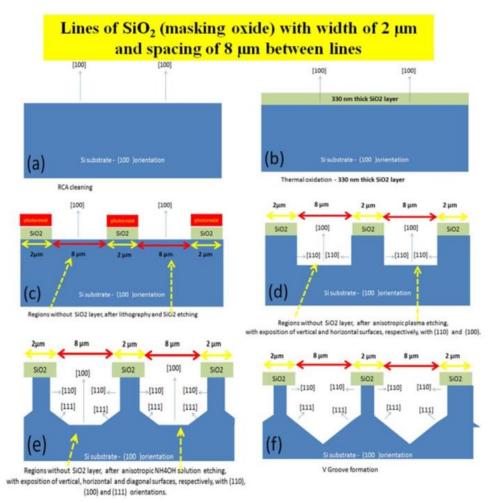

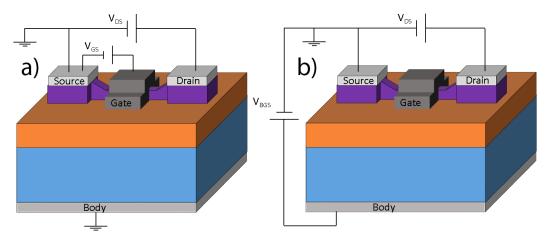

Figure 24 I<sub>D</sub> x V<sub>GS</sub> and I<sub>D</sub> x V<sub>GS</sub> plots of the devices fabricated in (MIGITA et al., 2014)