#### THESIS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

# High Performance Hybrid Memory Systems with 3D-stacked DRAM

**EVANGELOS VASILAKIS**

Division of Computer Engineering Department of Computer Science & Engineering Chalmers University of Technology Gothenburg, Sweden, 2020

#### High Performance Hybrid Memory Systems with 3D-stacked DRAM

EVANGELOS VASILAKIS

**Advisor:** Ioannis Sourdis, Professor at Chalmers University of Technology **Co-Advisor:** Vassilios Papaefstathiou, Researcher at FORTH-ICS, Greece **Co-Advisor:** Pedro Trancoso, Professor at Chalmers University of Technology

**Examiner:** Ulf Assarsson, Professor at Chalmers University of Technology

Thesis Opponent: Babak Falsafi, Professor at EPFL, Switzerland

#### **Grading Committee:**

- Erik Hagersten, Professor at Uppsala University, Sweden

- Bruce Jacob, Professor at University of Maryland, USA

- André Seznec, Senior research director at IRISA/INRIA, France

Copyright ©2020 Evangelos Vasilakis except where otherwise stated. All rights reserved.

ISBN: 978-91-7905-311-6

Doktorsavhandlingar vid Chalmers tekniska högskola.

Series number: 4778 ISSN 0346-718X

Department of Computer Science & Engineering Division of Computer Engineering Chalmers University of Technology Gothenburg, Sweden

This thesis has been prepared using LATEX. Printed by Chalmers Reproservice, Gothenburg, Sweden 2020.

#### **Abstract**

The bandwidth of traditional DRAM is pin limited and so does not scale well with the increasing demand of data intensive workloads. 3D-stacked DRAM can alleviate this problem providing substantially higher bandwidth to a processor chip. However, the capacity of 3D-stacked DRAM is not enough to replace the bulk of the memory and therefore it is used together with off-chip DRAM in a hybrid memory system, either as a DRAM cache or as part of a flat address space with support for data migration. The performance of both above alternative designs is limited by their particular overheads. This thesis proposes new designs that improve the performance of hybrid memory systems. It does so first by alleviating the overheads of current approaches and second, by proposing a new design that combines the best attributes of DRAM caching and data migration while addressing their respective weaknesses. The first part of this thesis focuses on improving the performance of DRAM caches. Besides the unavoidable DRAM access to fetch the requested data, tag access is in the critical path adding significant latency and energy costs. Existing approaches are not able to remove these overheads and in some cases limit DRAM cache design options. To alleviate the tag access overheads of DRAM caches this thesis proposes *Decoupled* Fused Cache (DFC), a DRAM cache design that fuses DRAM cache tags with the tags of the on-chip Last Level Cache (LLC) to access the DRAM cache data directly on LLC misses. Compared to current state-of-the-art DRAM caches, DFC improves system performance by 11% on average. Finally, DFC reduces DRAM cache traffic by 25% and DRAM cache energy consumption by 24.5%. The second part of this thesis focuses on improving the performance of data migration. Data migration has significant performance potential, but also entails overheads which may diminish its benefits or even degrade performance. These overheads are mainly due to the high cost of swapping data between memories which also makes selecting which data to migrate critical to performance. To address these challenges of data migration this thesis proposes LLC guided Data Migration (LGM). LGM uses the LLC to predict future reuse and select memory segments for migration. Furthermore, LGM reduces the data migration traffic overheads by not migrating the cache lines of memory segments which are present in the LLC. LGM outperforms current state-of-the art data migration, improving system performance by 12.1% and reducing memory system dynamic energy by 13.2%. DRAM caches and data migration offer different tradeoffs for the utilization of 3D-stacked DRAM but also share some similar challenges. The third part of this thesis aims to provide an alternative approach to the utilization of 3D-stacked DRAM combining the strengths of both DRAM caches and data migration while eliminating their weaknesses. To that end, this thesis proposes  $Hybrid^2$ , a hybrid memory system design which uses only a small fraction of the 3D-stacked DRAM as a cache and thus does not deny valuable capacity from the memory system. It further leverages the DRAM cache as a staging area to select the data most suitable for migration. Finally, Hybrid<sup>2</sup> alleviates the metadata overheads of both DRAM caches and migration using a common mechanism. Depending on the system configuration,  $Hybrid^2$  on average outperforms state-of-the-art migration schemes by 6.4% to 9.1%, compared to DRAM caches Hybrid<sup>2</sup> gives away on average only 0.3%, to 5.3% of performance offering up to 24.6% more main memory capacity.

#### **Keywords:**

Hybrid memory systems, 3D-stacked DRAM, DRAM caches, Data migration

## Acknowledgments

I always believed that a PhD is a personal endeavour where the student has to show their capabilities and struggle to contribute to their field while also improving themselves through hard work. That said, it would not be possible to walk this path alone without the support of all the people around me.

First of all, a big thanks to my advisor Yiannis for putting up with me for all this time and for guiding me from the beginning of this endeavour. Although we probably disagreed more often than not, we both know that it was always for the best. I will always think of Yiannis not only as a good advisor but also as a good friend. A big thanks also to my co-advisors, Vassilis and Pedro for their valuable help throughout my studies. Without all of you this work would not have been possible.

Also thanks to all the excellent people at Chalmers for making Chalmers a wonderful work environment. A special note for my colleagues and office mates, Alirad, Stavros, Prajith, Ahsen, Albin and Stefano for being there with me through the trenches. Outside Chalmers, my friends, Dimitris, Stella, Giorgos, Anastasia, Giorgos, Anna, Lea, and Despoina who were always there for me when I needed them. Finally, I would like to thank my mother for making me what I am today and my sister for being a close confidant I can always trust.

This work was supported by the European Commission under the Horizon 2020 Program through the ECOSCALE (grant agreement 671632) and SHARCS (grant agreement 644571) projects as well as by the European Research Council (ERC) under the MECCA project (Contract No. 340328).

### **List of Publications**

This thesis is based on the following publications:

- [A] Evangelos Vasilakis, Vassilis Papaefstathiou, Pedro Trancoso, Ioannis Sourdis "FusionCache: using LLC Tags for DRAM Cache" 2018 Design, Automation & Test in Europe Conference & Exhibition, DATE 2018, Dresden, Germany, March 19-23, 2018, pp. 593–596.

- [B] Evangelos Vasilakis, Vassilis Papaefstathiou, Pedro Trancoso, Ioannis Sourdis "Decoupled Fused Cache: Fusing a Decoupled LLC with a DRAM Cache" *ACM Transactions on Architecture and Code Optimization (TACO), vol. 15, no.* 4, pp. 65:1–65:23, Jan. 2019.

- [C] Evangelos Vasilakis, Vassilis Papaefstathiou, Pedro Trancoso, Ioannis Sourdis "LLC-guided Data Migration in Hybrid Memory Systems" 2019 IEEE International Parallel and Distributed Processing Symposium, IPDPS 2019, Rio de Janeiro, Brazil, May 20-24, 2019, pp. 932–942.

- [D] Evangelos Vasilakis, Vassilis Papaefstathiou, Pedro Trancoso, Ioannis Sourdis "Hybrid<sup>2</sup>: Combining Caching and Migration in Hybrid Memory Systems" 26th IEEE International Symposium on High Performance Computer Architecture, HPCA 2020, San Diego, California, USA, February 22–26, 2020.

#### Other publications

The following publications were also published during my PhD studies. However, they are not included to this thesis because their contents are overlapping or not related to the thesis.

- [a] Alirad Malek, Evangelos Vasilakis, Vassilis Papaefstathiou, Pedro Trancoso, Ioannis Sourdis

- "Odd-ECC: On-demand DRAM Error Correcting Codes" Proceedings of the International Symposium on Memory Systems, MEMSYS 2017, Alexandria, VA, USA, October 02 - 05, 2017, pp. 96-111.

- [b] Evangelos Vasilakis, Ioannis Sourdis, Vassilis Papaefstathiou, Antonis Psathakis and Manolis Katevenis

- "Modeling Energy-Performance Tradeoffs in ARM big.LITTLE Architectures" 27th International Symposium on Power and Timing Modeling, Optimization and Simulation, PATMOS 2017, Thessaloniki, Greece, September 25-27, 2017, pp. 1–8.

## **Contents**

| Al | ostrac  | et e e e e e e e e e e e e e e e e e e                            | iii |

|----|---------|-------------------------------------------------------------------|-----|

| Ac | know    | vledgement                                                        | v   |

| Li | st of I | Publications                                                      | vii |

| 1  | Intr    | oduction                                                          | 1   |

|    | 1.1     | Problem Statement                                                 | 2   |

|    |         | 1.1.1 Tag Lookups in DRAM Caches                                  | 2   |

|    |         | 1.1.2 Data Migration Overheads and Inefficiencies                 | 3   |

|    |         | 1.1.3 Copying Costs Capacity, Swapping Costs Traffic              | 3   |

|    | 1.2     | Thesis Objectives and Contributions                               | 3   |

|    |         | 1.2.1 Minimizing the Tag lookup Overheads in DRAM Caches          | 3   |

|    |         | 1.2.2 Minimizing Migration Overheads and Improving Data Selection | 5   |

|    |         | 1.2.3 Combining Caching and Data Migration                        | 7   |

|    | 1.3     | Thesis Outline                                                    | 9   |

| 2  | Dece    | oupled Fused Cache: Fusing a Decoupled LLC with a DRAM Cache      | 11  |

|    | 2.1     | Background and Motivation                                         | 13  |

|    | 2.2     | Decoupled Fused Cache design                                      | 16  |

|    |         | 2.2.1 DFC tag arrays:                                             | 17  |

|    |         | 2.2.2 DFC Indexing:                                               | 18  |

|    |         | 2.2.3 DFC tag matching:                                           | 19  |

|    |         | 2.2.4 DFC Tag Evictions:                                          | 21  |

|    |         | 2.2.5 Configurable DC-cacheline size                              | 22  |

|    |         | 2.2.6 DFC Hardware Overhead:                                      | 22  |

|    | 2.3     | Evaluation                                                        | 23  |

|    |         | 2.3.1 Experimental Setup                                          | 24  |

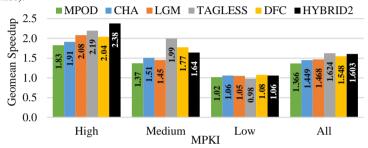

|    |         | 2.3.2 Performance                                                 | 25  |

|    |         | 2.3.3 Energy efficiency                                           | 29  |

|    | 2.4     | Related Work                                                      | 31  |

|    | 2.5     | Conclusions                                                       | 32  |

| 3  | LLC     | C-guided Data Migration in Hybrid Memory Systems                  | 35  |

|    | 3.1     | Background and Motivation                                         | 36  |

|    |         | 3.1.1 Related Work                                                | 37  |

|    |         | 3.1.2 Motivation                                                  | 39  |

|    | 3.2     | LLC-guided Migration                                              | 40  |

X CONTENTS

|    |        | 3.2.1    | Segment selection for migration          |   |    |     |     |     | 41       |

|----|--------|----------|------------------------------------------|---|----|-----|-----|-----|----------|

|    |        |          | Reducing Migration Traffic               |   |    |     |     |     | 43       |

|    |        |          | Architecture                             |   |    |     |     |     | 43       |

|    | 3.3    |          | nental Setup                             |   |    |     |     |     | 48       |

|    | 3.4    | Evaluati | ion                                      |   |    |     |     |     | 50       |

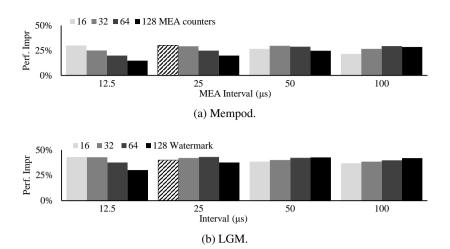

|    |        |          | Design space exploration                 |   |    |     |     |     | 50       |

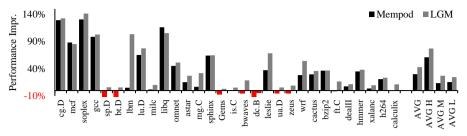

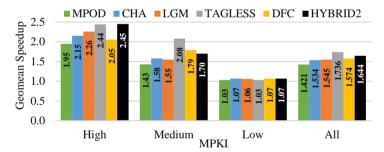

|    |        |          | Performance                              |   |    |     |     |     | 51       |

|    |        | 3.4.3    | Traffic                                  |   |    |     |     |     | 53       |

|    |        |          | Energy Consumption                       |   |    |     |     |     | 55       |

|    | 3.5    |          | sions                                    |   |    |     |     |     | 56       |

|    |        | 2        |                                          |   |    |     |     |     |          |

| 4  | -      |          | ombining Caching and Migration in Hybrid | M | em | ory | y S | ys- | 57       |

|    | tems   |          | Wada and Matination                      |   |    |     |     |     |          |

|    | 4.1    |          | Work and Motivation                      |   |    |     |     |     | 58<br>59 |

|    |        |          | Related work on DRAM caches              |   |    |     |     |     |          |

|    |        |          | Related work on data migration           |   |    |     |     |     | 60       |

|    | 4.0    |          | Motivation                               |   |    |     |     |     | 60       |

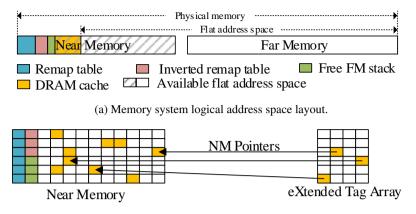

|    | 4.2    |          | Caching and Migration                    |   |    |     |     |     | 62       |

|    |        |          | Hybrid <sup>2</sup> System Overview      |   |    |     |     |     | 62       |

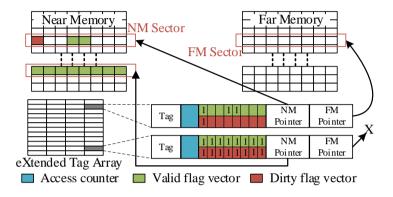

|    |        |          | eXtended Tag Array                       |   |    |     |     |     | 64       |

|    |        |          | Memory space layout and metadata         |   |    |     |     |     | 65       |

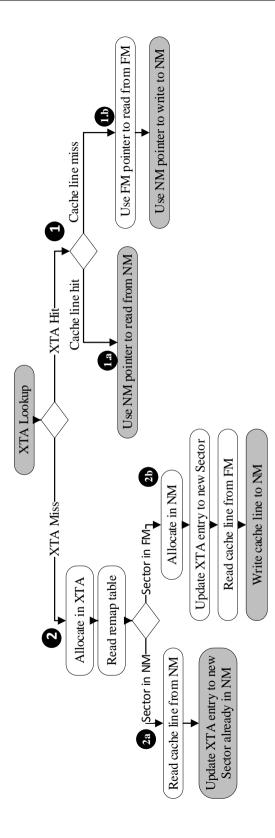

|    |        |          | Memory access path                       |   |    |     |     |     | 66       |

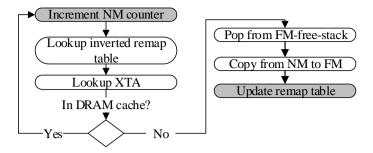

|    |        |          | Allocating NM                            |   |    |     |     |     | 68       |

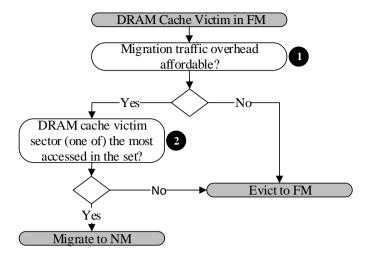

|    |        |          | DRAM cache evictions                     |   |    |     |     |     | 69       |

|    |        |          | Migration Decision                       |   |    |     |     |     | 70       |

|    |        |          | Using more free space                    |   |    |     |     |     | 72       |

|    | 4.3    |          | nental Setup                             |   |    |     |     |     | 73       |

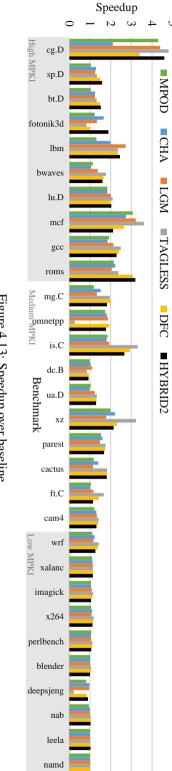

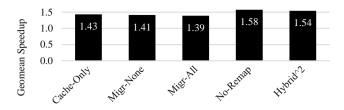

|    | 4.4    |          | ion                                      |   |    |     |     |     | 73       |

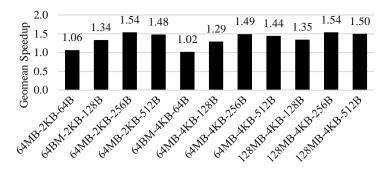

|    |        |          | Design space exploration                 |   |    |     |     |     | 74       |

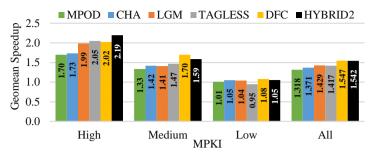

|    |        |          | Performance                              |   |    |     |     |     | 74       |

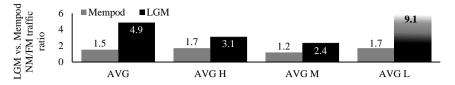

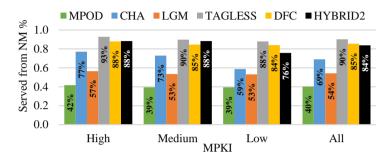

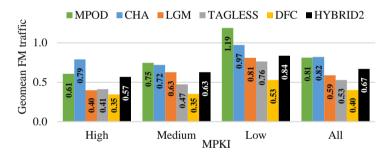

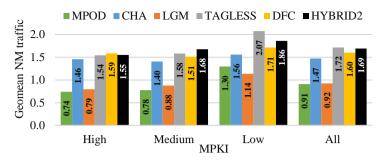

|    |        |          | Traffic                                  |   |    |     |     |     | 80       |

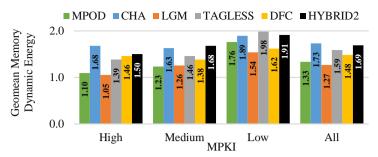

|    |        |          | Energy consumption                       |   |    |     |     |     | 80       |

|    | 4.5    | Conclus  | sions                                    |   |    |     |     |     | 81       |

| 5  | Con    | clusions |                                          |   |    |     |     |     | 83       |

|    | 5.1    |          | ry                                       |   |    |     |     |     | 84       |

|    | 5.2    |          | utions                                   |   |    |     |     |     | 85       |

|    | 5.3    |          | Work                                     |   |    |     |     |     | 86       |

| Ri | hling  | aphy     |                                          |   |    |     |     |     | 87       |

|    | ~11081 | ~P'''J   |                                          |   |    |     |     |     | 07       |

## Chapter 1

### Introduction

The performance of computer systems is largely dominated by their memory hierarchy [1]. Besides latency, memory bandwidth can be a limiting factor for many workloads [2–5]. On one hand, data intensive applications as well as the large number of cores and specialized accelerators integrated on a chip increase the demand for higher data rates. On the other hand, memory bandwidth is pin limited [2, 6] and is therefore more difficult to scale [5].

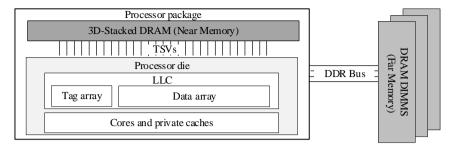

3D-stacked DRAM can be placed near the processor die offering substantially higher bandwidth than off-chip DRAM. 3D-stacked DRAM though has limited capacity and often needs to be complemented with a larger off-chip DRAM that has however lower bandwidth. Currently, there are two approaches to integrate both 3D-stacked DRAM and off-chip DRAM to form a hybrid memory system: the first one is a flat address-space memory system supporting migration between the two types of DRAM [7–11]; the second one is to use 3D-stacked DRAM as a cache [12–26].

DRAM caches have shown excellent potential in capturing the spatial and temporal data locality of applications. By copying the most recently accessed data to the 3D-stacked DRAM, they faithfully follow the working set of applications. Due to the size of DRAM caches, traditional (on-chip) cache architectures are sub-optimal for organizing DRAM caches, making their performance far from ideal.

As opposed to DRAM caches, data migration keeps 3D-stacked DRAM capacity available to the system. This means that data cannot be just copied to 3D-stacked DRAM as in caches, but instead has to be swapped which incurs double the overhead of copying. To amortize the overheads of swapping, it is important to select for migration only a subset of the accessed data; preferably the ones with the highest potential for future reuse. Reducing the swapping overheads as well as selecting the most promising data to migrate are critical factors for the performance of systems that support data migration.

This thesis addresses the overheads and limitations of hybrid memory systems by proposing more efficient designs for systems that utilize 3D-stacked DRAM in addition to conventional off-chip DRAM.

The rest of this introductory Chapter is organized as follows: The problem statement is presented in Section 1.1 followed by a discussion of the objectives and contributions of this thesis in Chapter 1.2.

2 CHAPTER 1. INTRODUCTION

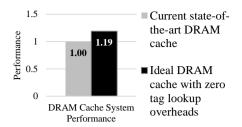

(a) Performance of a system with current state-of-the-art DRAM cache [19] and with an ideal DRAM cache with zero tag lookup overheads.

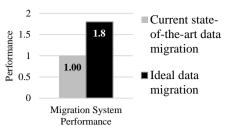

(b) Performance of a system with current state-of-the-art data migration scheme [9] and ideal system where all data are in 3D-stacked DRAM without any overheads.

Figure 1.1: Potential performance of DRAM caches and Data migration.

#### 1.1 Problem Statement

Existing hybrid memory systems have significant overheads that limit their performance. DRAM caches suffer mainly from the tag lookup overheads while data migration suffers most performance losses because of the more expensive data movement it requires. Tag management of DRAM caches and data movement overheads in data migration are the first two problems addressed in the thesis as they are the leading causes of inefficiencies in these approaches.

Furthermore, both DRAM caches and data migration offer fixed tradeoffs in the design of hybrid memory systems. DRAM caches waste the 3D-stacked DRAM capacity to allow data replication, which in turn reduces the bandwidth overhead of transferring data. Migration does not waste capacity, but this forces data swapping between the memories wasting bandwidth. The third problem addressed in this thesis is the lack of an alternative design that combines the benefits of DRAM caches and data migration and reduces their overheads.

More details about each problem addressed in this thesis are provided bellow.

#### 1.1.1 Tag Lookups in DRAM Caches

The DRAM cache tag access latency affects performance and depends on the tag organization and management. Different design choices come with different tradeoffs that are tightly related to the DRAM cache line size. Smaller DRAM cache lines offer more flexibility and more efficient use of the cache bandwidth and capacity when the application is characterized by low spatial locality. Larger DRAM cache lines offer better prefetching and overall better performance when the workloads exhibit spatial locality. On the other hand, smaller DRAM cache lines require more tag storage than larger ones for the same cache size making it infeasible to store them on chip. Even for larger DRAM cache lines, the cost of storing the tags on chip is not negligible and it could otherwise be utilized for a larger on-chip Last Level Cache (LLC). Storing the DRAM cache tags in DRAM is more space efficient and also allows for smaller DRAM cache lines but results in substantially higher tag access latency as well as increased 3D-stacked DRAM traffic.

Figure 1.1a shows the performance overhead of tag lookups in ATCache, a current state-of-the-art DRAM cache design [19]. An ideal DRAM cache that performs tag lookups with zero latency would have 19% better performance. This performance gap presents an opportunity for improving existing DRAM cache designs.

#### 1.1.2 Data Migration Overheads and Inefficiencies

Data migration differs from caching in that it does not waste the capacity of the 3D-stacked DRAM from the memory system. To achieve that, data migration schemes need to swap data from off-chip to 3D-stacked DRAM instead of just copying as caches. Swapping however, requires double the memory traffic of copying. Migration traffic competes directly with processor memory requests for bandwidth and increases the queuing latency, especially in off-chip DRAM, which is the memory system bottleneck. To increase the performance of data migration it is important to reduce the migration traffic overheads as well as to select data with good potential for future reuse.

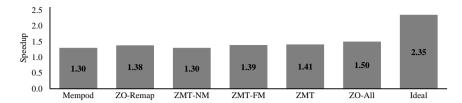

Figure 1.1b shows that an ideal system where all data are always found (with zero overheads) in the high bandwidth 3D-stacked DRAM could achieve  $1.8\times$  better performance than a current state-of-the-art data migration scheme, MemPod [9]. This significant gap in performance is due to the migration overheads as well as due to sub-optimal data selection of existing data migration schemes. This thesis aims to bridge this gap by improving these aspects of data migration.

#### 1.1.3 Copying Costs Capacity, Swapping Costs Traffic

On one hand, DRAM caches achieve high performance because they react fast to changes in the working set, but need to waste 3D-stacked DRAM capacity to copy data. On the other hand, migration schemes allow 3D-stacked DRAM space to be part of the main memory, but suffer more expensive data transfers as they need to swap data between the two parts of the hybrid memory system. As a consequence, migration schemes need to be more selective in transferring data and become less reactive giving away performance.

This thesis aims to propose a memory system design that reacts to working set changes like DRAM caches while at the same time does not deny much capacity.

#### 1.2 Thesis Objectives and Contributions

The primary objective of this thesis is to improve the performance of a hybrid memory system that consists of 3D-stacked and off-chip DRAM. We first aim to improve DRAM cache designs, subsequently we try to improve data migration and finally we attempt to combine the advantages of both approaches.

#### 1.2.1 Minimizing the Tag lookup Overheads in DRAM Caches

The first thesis objective is to improve the performance of systems that use 3D-stacked DRAM as a cache by minimizing their tag lookup overheads. The main idea behind this is to:

4 CHAPTER 1. INTRODUCTION

Store information about the location of DRAM cache lines in the tag array of the on-chip Last Level Cache (LLC) so as to access the data in the DRAM cache directly after LLC misses.

**Related Work:** Several designs have been proposed aiming to reduce the DRAM cache tag access latency, however they are not able to nullify it and some of them introduce significant constraints to the system. One such design employs an on-chip SRAM cache of the DRAM cache tags [19]. This reduces the average DRAM cache tag lookup latency however it adds a constant delay to every DRAM cache access for accessing the tag-cache and more on-chip resources are occupied for caching the DRAM cache tags. Another technique places the DRAM cache data addresses directly in the TLB entries [21]. Every TLB entry would then have information about the location of the respective page in the DRAM cache. However, this requires fixing the DRAM cache line size to the Operating System (OS) page size, which can be inefficient for applications with low spatial locality and wasteful in terms of off-chip bandwidth and DRAM cache space. The inefficiencies of this approach would be even more evident in systems that use super-pages/huge-pages [27–29]. Other techniques such as Alloy Cache and Compound Access Scheduling collocate DRAM cache data and tags in the same DRAM row to allow faster accesses [13,24]. These designs either require a direct mapped cache organization or customizing the cache associativity and cacheline size to the DRAM row size. Such restrictions can impact the hit rate or waste DRAM cache capacity.

In summary, although existing DRAM cache designs reduce the tag lookup latency, they do so by either introducing a constant latency to all accesses, as in the case of tag-caches, or by severely limiting critical DRAM cache parameters such as cache line size and associativity, ultimately limiting the performance of DRAM caches.

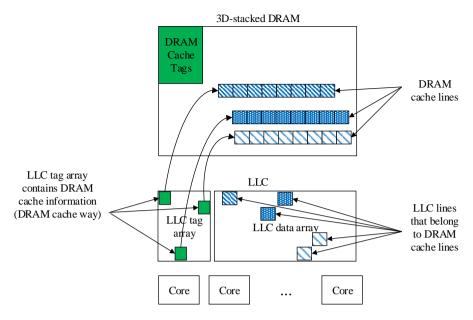

**Thesis Approach:** To minimize the tag lookup overheads for DRAM caches this thesis proposes Decoupled Fused Cache (DFC), described in Chapter 2 of this thesis. DFC is a new DRAM cache architecture that mitigates the cost of accessing the DRAM cache tags while enforcing minimal design restrictions. Figure 1.2 provides a conceptual overview of our proposal. DFC takes advantage of the redundancy in the tags within the LLC as well as across the LLC and DRAM cache tag arrays and uses the LLC tag-array to store information about the location of data in the DRAM cache. In the common case, this allows DFC to access the DRAM cache data array without looking up its tags which are stored in 3D-stacked DRAM. DFC decouples the location of LLC tags from the location of the LLC lines in the LLC data array in a way that resembles Decoupled Sector Caches [30]. In a nutshell, an LLC tag is associated with a DRAM cache line, which consists of several LLC lines, while the LLC management (validity, dirty, etc.) is performed (and related information is stored) at LLC line granularity. DFC can support a configurable (at boot time) DRAM cache line size, which is a power-of-two multiple of the LLC line size. In essence the only limitation of DFC is that the DRAM cache lines needs to be at least twice as large as an LLC line.

Contrary to existing work, DFC mitigates the DRAM cache tag access overheads without imposing significant design restrictions. More precisely, DFC does not require any OS support, it does not limit DRAM cache associativity, it does not impose additional overheads in every access, and does not affect LLC performance. Still, DFC offers zero tag access overhead in the common case, and can dynamically (at boot time) support variable DRAM cache line sizes.

Figure 1.2: Decoupled Fused Cache (DFC) overview.

**Contributions:** For DRAM caches this thesis proposes Decoupled Fused Cache [31], a new cache hierarchy which:

- Stores information about the contents of the DRAM cache in the LLC to avoid DRAM cache tag lookups for most LLC misses.

- Supports any DRAM cache line size power-of-two multiple of a LLC cache line (up to 4KB in our experiments), which is configurable at boot time.

- Improves performance by an average of 11% compared to a state-of-the-art DRAM cache [19].

- Reduces DRAM cache traffic by 25% and DRAM cache energy by 24.5% versus the current state-of-the-art.

## 1.2.2 Minimizing Migration Overheads and Improving Data Selection

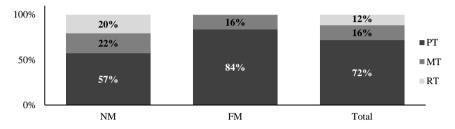

The second objective of this thesis is to improve the performance of systems that use 3D-stacked DRAM as part of a flat address space with data migration. It does so by reducing the migration traffic overheads and improving the selection of data that are migrated. The ideas behind this objective are to:

Use the on-chip LLC to guide data selection for migration based on the observed spatial locality.

Reduce migration traffic by not migrating cache lines already present in the LLC, as they can be written to their new location upon eviction.

6 CHAPTER 1. INTRODUCTION

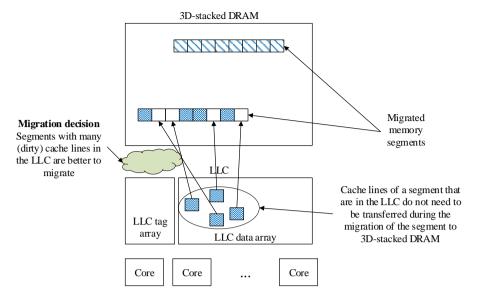

Figure 1.3: LLC-guided data migration (LGM) overview.

**Related Work:** There exists a large body of prior work on data migration for hybrid memory systems. The core component of every data migration strategy, is the way a memory segment is selected for migration. Most approaches use counters to keep track of accesses to memory segments [32] or counters for every segment within a group [7, 10]. So far, the most promising approach has been the activity tracking mechanism proposed by Mempod [9], which uses the *Majority Element Algorithm* (MEA) [33]. MEA has been shown to predict the hottest pages within an interval with high accuracy and at minimal hardware cost.

Different approaches trigger migrations in different ways. Many of them do it on time intervals [9,32], while others do it on an event, e.g. CAMEO migrates at every memory access that is not in the 3D-stacked DRAM [34]. Some approaches trigger migrations when the values of selection counters go beyond some threshold [7,10].

Another aspect that characterizes the different approaches is whether the migration mechanism is based on software or hardware, or a combination of the two. Some migration mechanisms rely on the Operating System (OS) with some hardware support to identify the working set and orchestrate the migration [32], others only involve the hardware and are transparent to the OS [7,9,10,34].

Overall, current approaches to data migration are far from their ideal performance. Their performance is limited partly due to the increased overheads of data migration and also because of the difficulty to select data to migrate with good potential for future reuse.

**Thesis Approach:** For data migration between off-chip and 3D-stacked DRAM, this thesis proposes LLC-guided Migration (LGM), a novel scheme for data migration in hybrid memory systems aiming both at improving the selection of migrated data as well as at reducing their traffic overheads. Figure 1.3 provides a conceptual overview of our proposed design, described in Chapter 3 of this thesis. Improving the selection of migrated data is achieved by using the LLC to guide the selection of memory segments to be migrated by detecting high spatial and temporal locality. More precisely, the

LLC is used to identify memory segments that have a large number of cachelines on-chip. This is an indication for potential future reuse, which gets stronger when these cachelines are dirty. Employing the LLC to select segments for migration ensures that these segments are at that moment –at least partly– present in LLC. This can be used for reducing migration traffic. This is because when a fraction of a memory segment is located in the LLC, it can be omitted from the migration to reduce the migration traffic, as long as the LLC writes it back to memory when evicted.

The main novelty of our approach is the following: Firstly, the migration overheads are reduced by avoiding traffic for cache lines already present in the LLC. Secondly, the quality of selecting of data for migration is improved. Even more important is that segments are selected for migrations when a large fraction of them resides in the LLC, this timing further reduces the migration traffic.

**Contributions:** For data migration this thesis proposes LLC-guided Data Migration (LGM) [35], a data migration scheme which:

- Employs the LLC to detect locality and leverages it for selecting data with higher potential for reuse to migrate.

- Reduces the migration traffic overhead by avoiding to migrate data that already reside in the LLC.

- Increases the benefits of the above migration traffic reduction because the selected data are more likely to be in the LLC when migrated.

- Reduces migration traffic to almost half and enables more data to be migrated therefore increasing the ratio of memory requests serviced by the 3D-stacked DRAM.

- Improves performance by 12.1% and reduces memory system dynamic energy by 13.2% compared to the current state-of-the-art [9].

#### 1.2.3 Combining Caching and Data Migration

The third objective of this thesis is to define a new memory system design that combines the strengths of DRAM caches and data migration while reducing their respective weaknesses. The main idea behind this objective is to:

Use a small part of the 3D-stacked DRAM as a cache to retain the reactiveness of caches with minimal capacity waste and use the rest of the 3D-stacked DRAM for data migration.

Design a unified mechanism that seamlessly manages both DRAM cache and data migration metadata and reduces their respective overheads.

**Related Work:** DRAM caches, as described above, present one solution to the utilization of 3D-stacked DRAM which trades capacity for less wasted bandwidth [13,19,21,24]. Data migration designs present a different tradeoff, preserving capacity for more expensive swapping operations between the conventional and 3D-stacked DRAM [7,9,10,32,34]. Furthermore, there are two designs that strike a different balance. Chameleon is based on PoM with the added option to economize on migration bandwidth when the software does not use some memory space [7] [8]. Chameleon

8 CHAPTER 1. INTRODUCTION

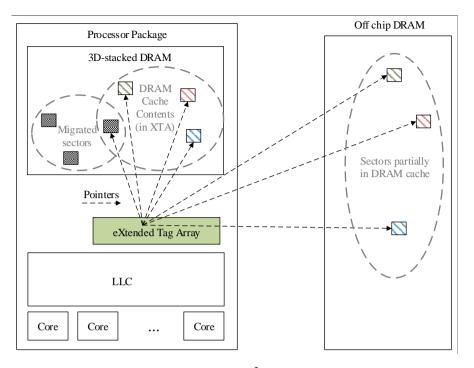

Figure 1.4: *Hybrid*<sup>2</sup> Overview.

does so by involving the Operating System and adding new instructions to the instruction set, this enables the underlying PoM migration mechanism to safely overwrite memory that is not in use, therefore alleviating some of the migration traffic overheads. Intel's Knights Landing provides the option to split the *MCDRAM* between DRAM cache and flat address space, however, it does not support transparent data migration in hardware. Instead it moves the burden to the software to explicitly allocate data to the 3D-stacked DRAM through the *hbw\_malloc()* function [36, 37].

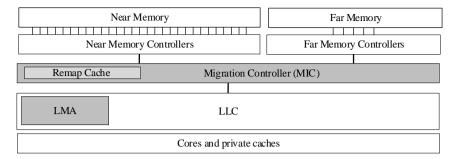

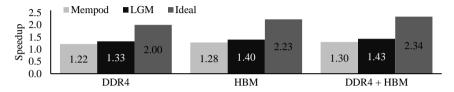

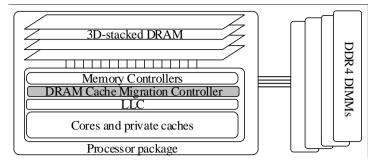

**Thesis Approach:** In order to combine caching and migration in the same memory system this thesis proposes  $Hybrid^2$ .  $Hybrid^2$  aims to preserve the advantages of both caching and migration as well as to minimize their overheads. A conceptual overview of this design is presented in Figure 1.4. Hybrid<sup>2</sup> employs a small portion of the 3D-stacked DRAM to implement a DRAM cache and offers the rest of its capacity to main memory. The DRAM cache quickly adjusts to the working set of the workload by fetching to the 3D-stacked DRAM all the data that is requested by the processor. Besides preserving most of the 3D-stacked DRAM capacity, the small DRAM cache size allows its tag array to fit entirely on-chip, thereby reducing access latency. The on-chip tag array is additionally extended to act as a cache for the remapping metadata required for data migration. Migrations are decided upon eviction from the DRAM cache which allows observing the access patterns in the DRAM cache and make informed migration decisions. Finally, the data of the DRAM cache can be located anywhere in the 3D-stacked DRAM through the use of indirection, therefore, data selected to be kept after eviction from the cache do not require relocation within the 3D-stacked DRAM, this avoids unnecessary traffic.

1.3. THESIS OUTLINE 9

**Contributions:** To combine the benefits of DRAM caches and data migration this thesis proposes [38], a memory system design which:

- Uses a small part of the 3D-stacked DRAM as a cache and utilizes the rest for data migration.

- Employs a small on-chip tag array which eliminates DRAM cache tag lookup overheads and also to alleviate the data migration remapping metadata overheads.

- Utilizes the DRAM cache as a staging area to select the data with most potential for future reuse and selectively migrates data when evicted from the DRAM cache.

- Avoids unnecessary data movement in the 3D-stacked DRAM by employing indirection in the DRAM cache tag array.

- Improves performance on average by 6.4-9.1% compared to migration mechanisms.

- Offers 5.9-24.6% more main memory capacity than caches while giving away only 0.3-5.1% of performance on average.

#### 1.3 Thesis Outline

The remainder of this thesis is organized as follows. Chapter 2 presents the design and evaluation of *Decoupled Fused Cache*, A DRAM cache design that uses the LLC tag array to store information about the contents of the DRAM cache. Chapter 3 presents the design and evaluation of *LLC-guided Data Migration in Hybrid Memory Systems*, a data migration scheme that uses the LLC to select memory segments to migrate based on their observed spatial locality and to reduce the migration traffic overheads. Chapter 4 presents the design and evaluation of *Hybrid*<sup>2</sup>: *Combining Caching and Migration in Hybrid Memory Systems*, a memory system design that combines the benefits of caching and migration in the same memory system while tackling their respective overheads. Finally, The conclusions of this thesis are presented in Chapter 5.

10 CHAPTER 1. INTRODUCTION

### Chapter 2

## Decoupled Fused Cache: Fusing a Decoupled LLC with a DRAM Cache

As 3D-stacking technology becomes more widely used, DRAM and processor can be integrated in the same package sustaining higher memory bandwidth and substantially lower energy per transferred bit [39]. Compared to the narrower-channels of traditional off-chip DRAM, 3D-stacked DRAM achieves 2-4 times higher bandwidth [40]. This in turn alleviates the queuing latency and contention effects that traditional DRAM channels suffer from leading to lower average memory access time. Currently, 3D-stacked DRAM falls short in meeting the main memory capacity requirements of high-end systems, but it is orders of magnitude larger than on-chip SRAM caches. Their capacity and high bandwidth makes 3D-stacked DRAMs a suitable building block for an off-chip (off the processor die) cache. DRAM caches (DC) exploit the coarse grain spatial locality of applications and reduce the number of accesses to main memory, however they are still far from their ideal access latency [16]. This, in turn, may negatively impact system performance as it adds delay to all memory requests that miss in the on-chip caches.

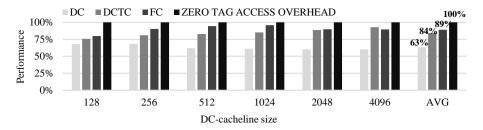

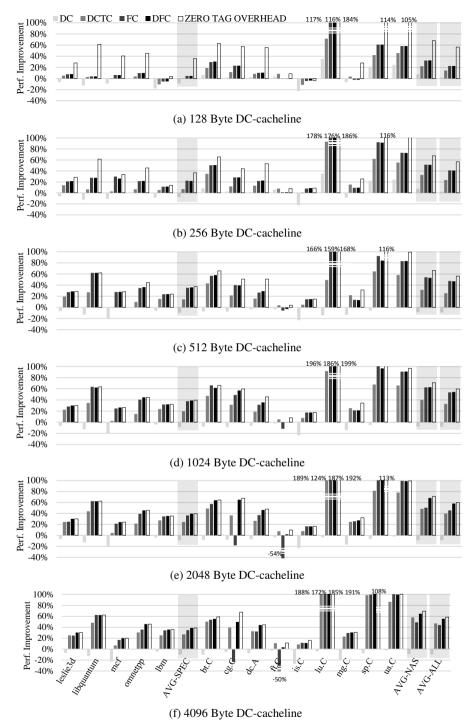

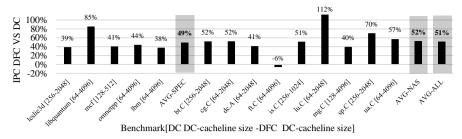

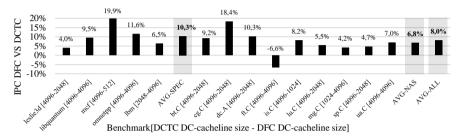

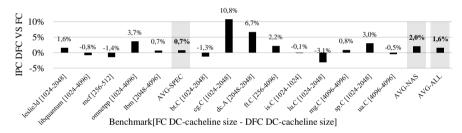

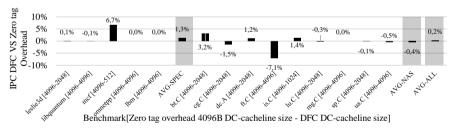

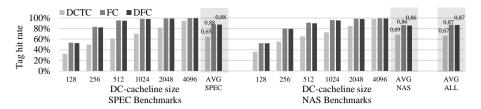

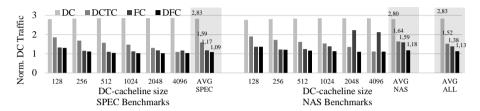

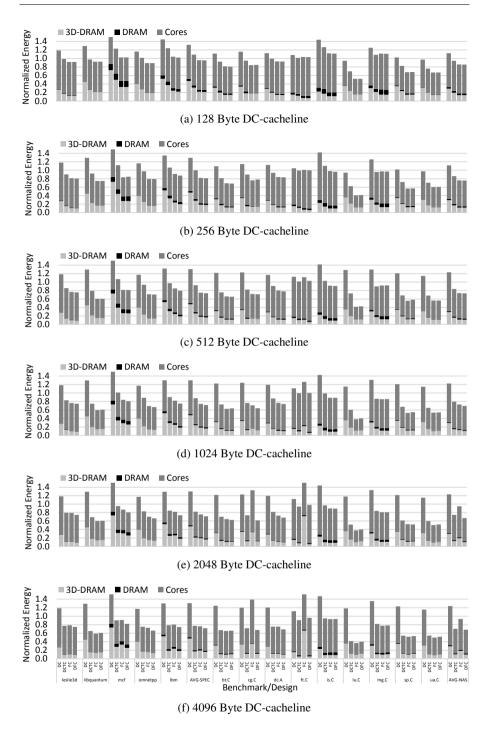

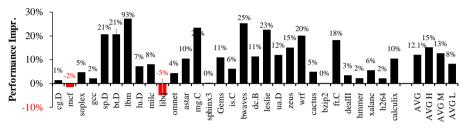

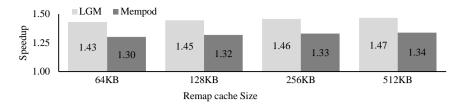

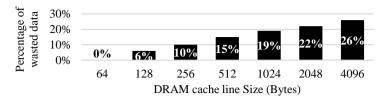

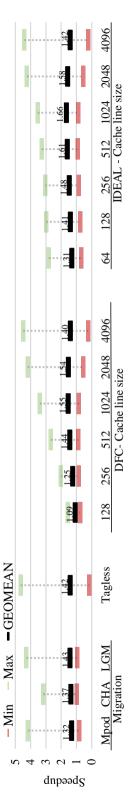

A significant factor of DC latency, as in any cache, is the tag lookup time, which is added to the memory access time for both hits and misses and can be as costly as the data access. As shown in Figure 2.1, a simple DRAM cache (DC) gives away an average 37% of system performance compared to using an ideal DC with zero tag access latency. Designs that try to mitigate the tag access overhead, such as *Fusioncache* (FC) [41], which uses the LLC tags to access the DRAM cache, and *ATCache*, which is a DRAM Cache with an on-chip Tag-Cache (DCTC) [19] bridge that performance gap significantly, however there is still ample room for improvement, 16% for the DCTC and 11% for the FC on average.

The DC tag access latency depends on the tag management. Each design choice comes with tradeoffs that are tightly related to the DC-cacheline size. Since DCs are in the order of hundreds of MB in size, the options for the DC-cacheline size range from the conventional cacheline size of on-chip caches (often 64 Bytes) to a full Operating System (OS) page (4KB). Various designs have been proposed advocating particular DC-cacheline sizes and as also shown in our evaluation there is no single size that

Figure 2.1: Performance normalized to DRAM cache without tag access overhead. The depicted results are the average performance results retrieved for the SPEC and NAS benchmarks used in our evaluation section.

fits all applications [12, 21, 24]. Smaller DC-cachelines offer more flexibility and more efficient use of the cache bandwidth when the application is characterized by low spatial locality. Larger DC-cacheline offer better prefetching and overall better performance when the workloads exhibit spatial locality [20, 23]. On the other hand, smaller DC-cachelines require more tag storage than larger ones for the same cache size making it infeasible to store them on chip. Even for larger cachelines, the cost of storing the tags on chip is not negligible and it could otherwise be utilized for a larger on-chip Last Level Cache (LLC). Storing the DRAM cache tags in DRAM is more space efficient and as such allows for smaller DC-cachelines but it results in substantially higher tag access latency as well as increased DRAM cache traffic [22].

Several designs have been proposed aiming to reduce the DC tag access latency, however they are not able to nullify it and some of them introduce significant constraints to the system. One such design employs an on-chip SRAM cache of the DC tags [19]. This reduces the average DC tag lookup latency however it adds a constant delay to every DC access for accessing the tag-cache and more on-chip resources are occupied for caching the DC-tags. Another technique places the DC addresses directly in the TLB entries [21]. Every TLB entry would then have information about the location of the respective page in the DRAM cache. However, this requires fixing the DC-cacheline size to the OS page size, which can be inefficient for applications with low spatial locality and wasteful in terms of off-chip bandwidth and DC space. The inefficiencies of this approach would be even more evident in systems that use superpages/huge-pages [27-29]. Other techniques such as Alloy Cache and Compound Access Scheduling collocate DC data and tags in the same DRAM row to allow faster accesses [13,24]. These designs either require a direct mapped cache organization or customizing the cache associativity and cacheline size to the DRAM row size. Such restrictions can impact the hit rate or waste DC capacity. In summary, although existing DC designs reduce the DC tag lookup latency, they do so by either introducing a constant latency to all accesses, as in the case of Tag-cache, or by severely limiting critical DRAM cache parameters such as DC-cacheline size and associativity. As a consequence, minimizing the tag lookup latency remains an open challenge in the design of a DC.

In this thesis we propose *Decoupled Fused Cache* (DFC). DFC is a new DRAM cache architecture that mitigates the cost of accessing the DRAM cache tags while enforcing minimal design restrictions. Our design achieves zero tag access latency in the common case by storing information about the location of DC cachelines in the tag array of the on-chip LLC. DFC can support a configurable (at boot time) DC cacheline

size, which is a power-of-two multiple of the LLC-cachelines. In essence the only limitation of our proposal is that the DC-cachelines needs to be at least twice as large as an LLC-cacheline. Then, considering an inclusive cache model, each cacheline stored in the LLC is always part of a DC-cacheline stored in the DC. Our work builds upon our initial work on DRAM caches, *Fusioncache*, which used the LLC tags to access the DC reducing its latency [41]. Our previous design required LLC cachelines that belong to the same DC-cacheline to be placed on the same LLC set. *Decoupled Fused Cache* overcomes this limitation by decoupling the LLC tag in a way that resembles *Decoupled Sectored Caches* [30] yielding significant performance improvements – up to 100% for particular benchmarks and design points. In a nutshell, an LLC tag is associated with a DC-cacheline, which consists of several LLC cachelines, while the LLC management (validity, dirty, etc.) is performed (and related information is stored) at LLC cacheline granularity.

Concisely, the contributions of Decoupled Fused Cache are the following:

- A new cache hierarchy is proposed that fuses the on-chip LLC and DRAM cache tags to achieve zero-latency DC access without affecting LLC performance;

- The proposed solution supports any DC-cacheline size power of two multiple of the LLC-cachelines;

- An evaluation and comparison against related approaches showing that Decoupled Fused Cache achieves better performance and energy efficiency.

The remainder of this Chapter is structured as follows: Section 2.1 uses a motivating example to introduce background information and highlight the challenges addressed in this work. In Section 2.2 the proposed *Decoupled Fused Cache* design is presented. Section 2.3 offers the evaluation and comparison of our work. Section 2.4 discusses in more detail related work on DRAM caches and in particular on designs that aim at reducing DC tag lookup latency. Finally, Section 2.5 summarizes our conclusions.

#### 2.1 Background and Motivation

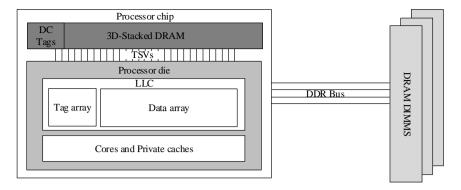

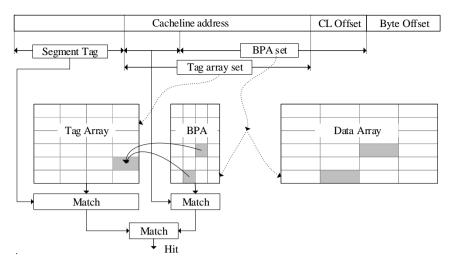

Considering a system as the one illustrated in Figure 2.2 with an inclusive DRAM cache (DC) placed between the on-chip Last Level Cache (LLC) and main memory, we present a motivating example highlighting the challenges addressed in this work. We discuss first the functionality of a DC and LLC when organized in a conventional way and subsequently contrast it with our previous *Fusioncache* (FC) design pointing to its advantages and drawbacks addressed by *Decoupled Fused Cache* (DFC).

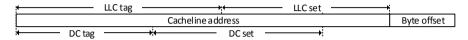

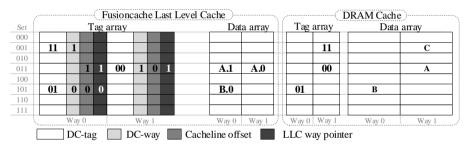

A conventional system with a DRAM cache (DC) would function as illustrated in the example of Figure 2.3a. Both the LLC and the DC use the upper part of an address as a tag and the remaining bits before the byte-offset for selecting a set as shown in Figure 2.3b (Figure 2.5 shows the addresses and fields of the LLC- and DC- cachelines used for the examples in Figures 2.3, 2.4 and 2.6).

Let us consider that the DC uses for its tags equal or fewer address bits than the LLC assuming it has equal or larger cachelines and number of sets. Then, in an inclusive cache hierarchy, a cacheline stored in the LLC will be also stored in the DC as part of a DC-cacheline. As a consequence, (part of) an LLC tag would identify a DC-cacheline and would be stored in the DC tag-array, too. For example,

Figure 2.2: System Overview.

in Figure 2.3a, we can observe that the upper part of the tag of an LLC-cacheline (i.e., 011 for LLC-cacheline *B.0*) is the same with the DC-tag of the respective DC-cacheline (i.e.,01 for DC-cacheline *B*). Moreover, considering some spatial locality, it is reasonable for a cache to host consecutive cachelines which would have the same tag. Then, the tag of such cachelines would be repeated in multiple (consecutive) sets of the tag array as shown in the LLC of Figure 2.3a. For instance, consecutive LLC-cachelines *A.0* and *A.1*, which belong to the same DC-cacheline (*A*), store their identical LLC-tag (000) twice in the LLC tag array in different sets. In summary, we can observe that: firstly, (parts of) the LLC tags are also stored in the DC tag-array, and secondly, the LLC tags for consecutive LLC-cachelines are duplicated in multiple sets of the LLC tag array.

Fusioncache is based on the first above observation to reduce the DC tag access latency. It appends LLC tag array entries with information for accessing their respective DC-cacheline. Thereby, LLC accesses that would miss in the LLC, i.e., B.1 in the above example, but their tags are stored in the LLC tag-array would need no further DC-tag access. However, an LLC access that falls to a particular DC-cacheline may hit one of several LLC sets as observed in Figure 2.3a. In this example, an access to DC-cacheline A may go through the LLC set that stores either A.0 or A.1. In order to ensure that a single LLC access can provide a definite answer about the DC tags, Fusioncache restricts all LLC-cachelines that belong to the same DC-cacheline to be placed in the same LLC set as shown in Figure 2.4a. Our second above observation, that the LLC tags for consecutive LLC-cachelines are duplicated in multiple sets of the LLC tag array, also comes to Fusioncache's advantage, as the tag for these LLC-cachelines is then stored only once saving space in the LLC tag array and increasing the number of DC tags that can be stored in the LLC. For example, the tag of DC-cacheline C is stored in the LLC of Fusioncache of Figure 2.4a without a corresponding LLC-cacheline and can be used for accessing the DC. In order to enforce this LLC-cacheline placement Fusioncache uses higher order address bits for indexing LLC as depicted in Figures 2.4b and 2.5. As explained in our previous work, this design choice restricts the effective LLC associativity and limits performance for particular memory access patterns especially in large DC-cacheline sizes [41].

Taking a closer look to the *Fusioncache* example of Figure 2.4a, an LLC-tag array entry stores the DC-tag and, besides the standard fields needed for the management of the two caches (validity, dirty, etc), it also stores the DC-way of the corresponding DC-cacheline, the offset of the stored LLC cacheline, and a pointer to the way of the

| ,       | Last Level Cache |       |  |       |         |   | DRAM Cache |       |  |       |       |  |

|---------|------------------|-------|--|-------|---------|---|------------|-------|--|-------|-------|--|

| Set     | Tag              | array |  | Data  | a array |   | Tag        |       |  |       | array |  |

| Set 000 |                  |       |  |       |         |   |            |       |  |       |       |  |

| 001     |                  |       |  |       |         |   |            | 11    |  |       | C     |  |

| 010     | 011              |       |  | B.0   |         |   |            |       |  |       |       |  |

| 011     |                  |       |  |       |         |   |            | 00    |  |       | A     |  |

| 100     |                  |       |  |       |         |   |            |       |  |       |       |  |

| 101     |                  |       |  |       |         |   | 01         |       |  | В     |       |  |

| 110     |                  | 000   |  |       | A.0     |   |            |       |  |       |       |  |

| 111     | 000              |       |  | A.1   |         |   |            |       |  |       |       |  |

| 1       | . Way 0          | Way 1 |  | Way 0 | Way 1   | Д | Way 0      | Way 1 |  | Way 0 | Way 1 |  |

(a) Location of LLC-cachelines and tags in conventional cache.

(b) Conventional cache address breakdown

Figure 2.3: Conventional cache example and address breakdown.

(a) Location of LLC-cachelines and tags in Fusioncache (FC)

(b) Fusioncache address breakdown

Figure 2.4: Fusioncache example and address breakdown.

| Conventio             | nal LLC address fields:                             | •    | — Tag — | <del>,</del>   | +                  | Set     | <del></del> |

|-----------------------|-----------------------------------------------------|------|---------|----------------|--------------------|---------|-------------|

| Fusioncac             | Fusioncache LLC ad dress fields: Tag Set Set CL off |      |         |                |                    |         |             |

| Decoupled Fused Cad   | the LLC address fields:                             | ← т  | ag      | ← Tag suffix → | Tag array set<br>← |         | <b></b>     |

| DC-cacheline          | LLC-ca cheline                                      | •    |         | LLC cach el    | ne address —       |         |             |

| Α                     | A.0                                                 | 0    | 0       | 0              | 1                  | 1       | 0           |

| ^                     | A.1                                                 | 0    | 0       | 0              | 1                  | 1       | 1           |

| В                     | B.0                                                 | 0    | 1       | 1              | 0                  | 1       | 0           |

| ь                     | B.1                                                 | 0    | 1       | 1              | 0                  | 1       | 1           |

| _                     | C.0                                                 | 1    | 1       | 0              | 0                  | 1       | 0           |

|                       | C.1                                                 | 1    | 1       | 0              | 0                  | 1       | 1           |

| DC cacheline add ress |                                                     |      |         |                |                    |         |             |

| DRAM                  | 1 cache address fields:                             | ← та | ag      | ·              | Set                | <b></b> |             |

Figure 2.5: Address fields for indexing and tag matching for conventional LLC, *Fusioncache* LLC, *Decoupled Fused Cache* LLC, and DRAM cache.

LLC tag-array that stores the corresponding LLC-tag. In our example, LLC cachelines A.0 and A.1 have their tag stored in only one entry of the LLC-tag array (way-1 of the corresponding set). The same tag (00) is used for accessing the DC in way 1 as indicated by the DC-way field. The LLC cacheline offset is 1 and 0 for the LLC-cachelines A.1 and A.0, respectively. Finally, the field pointing to the way that stores the tag for these two LLC-cachelines is 1 for both entries as their tag (00) is stored in way-1 of the LLC-tag array. Accessing the LLC requires matching each tag, as indicated by the LLC-way pointer, and each LLC-cacheline offset. When a DC-tag is matched but the requested LLC-cacheline is not present in the LLC, the DC data array can be accessed directly by use of the DC-way information, otherwise a DRAM access for the DC-tag is required before accessing the DC data array.

Effectively, *Fusioncache* indexes the LLC as if it was a cache with a DC-cacheline size and uses an offset to identify the particular LLC-cacheline. Thereby, the LLC tag array acts like a cache of DC-tags storing DC-tags used in previous LLC accesses, even if all corresponding LLC-cachelines have been evicted. However, the modified indexing of the LLC and the placement restriction of all LLC-cachelines that belong to the same DC-cacheline to reside on the same LLC set affects performance. When the number of LLC-cachelines per DC-cacheline is higher than the LLC associativity, sequential accesses to the same DC-cacheline would exhaust the LLC set and result in unwanted evictions. On the contrary, in a conventional LLC, the LLC-cachelines of the same DC-cacheline map to different LLC sets.

As explained in the next section, *Decoupled Fused Cache* addresses this problem allowing the LLC of a fused cache to operate as in the conventional way, using lower order address bits for indexing and still storing DC-tags in the LLC-tag array.

#### 2.2 Decoupled Fused Cache design

The *Decoupled Fused Cache* (DFC) is based on the same two observations exploited by the *Fusioncache*. It takes advantage of the redundancy in the tags within the LLC as well as across the LLC and DC tag arrays and uses the LLC tag-array to store information about the location of data in the DRAM cache (DC). In the common case, this allows DFC to access the DC data array without looking up its tag array. As opposed to *Fusioncache*, DFC does not restrict LLC-cachelines of the same DC-cacheline to sit on the same LLC set. This is achieved by decoupling the location of LLC tags from the location of the LLC-cachelines in the LLC data array in a way that resembles Decoupled Sector Caches [30].

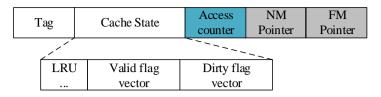

In DFC, tags in the LLC are stored in a *tag-array*, which is indexed as if it were a DC-tag array. Then, a second, *Back Pointer Array* (BPA), which follows the indexing of the LLC data array, is used to store the information for the LLC management (valid, dirty, LRU bits of the corresponding LLC data entry). In addition, each entry of the BPA points to the tag array entry, which stores the tag of the corresponding LLC cacheline. As explained below, pointing from the BPA to the tag-array requires information about the correct way of the tag-array as well as the LLC tag suffix<sup>1</sup>. Note that both the tag and back pointer arrays have equal number of sets and ways as the LLC data-array.

Using the above indirection, DFC decouples the location of tags and data in the LLC. In doing so, it allows the LLC-cachelines to be placed as in a conventional LLC

<sup>&</sup>lt;sup>1</sup>That is the address bits that need to be appended to the DC-tag in order to form the LLC-tag.

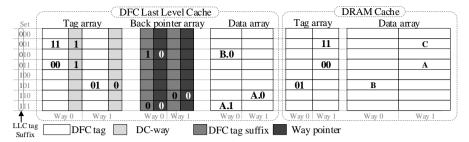

(a) Location of LLC-cachelines and tags in Decoupled Fused Cache (DFC).

Figure 2.6: Decoupled Fused Cache example and address breakdown.

and its tags to be organized as in a DC tag array. Then, each entry of the tag array can store information for the DC-cacheline associated with the stored tag. In particular, the location of the corresponding DC-cacheline and some DC management fields. As a consequence, the DFC avoids DC-tag accesses for all the tags stored in the LLC without restricting LLC-cacheline placement and hence without affecting the LLC performance.

Figure 2.6a illustrates the DFC functionality for the same example used in the previous section to demonstrate the FC and conventional cache. Figure 2.5 shows the addresses as well as the respective address fields used for indexing and tag-matching for the LLC- and DC-cachelines used in the examples in Figures 2.3a, 2.4a, and 2.6a for a conventional cache, *Fusioncache*, and *Decoupled Fused Cache*, respectively. Notice that DFC keeps the same data placement in the LLC as in the conventional cache of Figure 2.3a. As opposed to FC, LLC-cachelines that belong to the same DC-cacheline are placed in different sets in DFC (e.g *A.0* and *A.1*). At the same time, DFC keeps only one tag for all cachelines that belong to the same DC-cacheline in the LLC, economizing space and ensuring that DRAM cache information is retrieved with a single LLC lookup.

Next, the details of DFC are discussed, explaining first the organization of the tag arrays, then, the indexing and tag matching mechanism and finally analyzing the hardware cost of the DFC design.

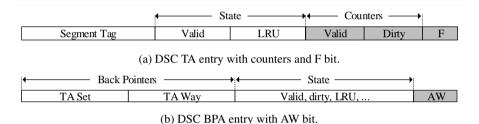

#### 2.2.1 DFC tag arrays:

DFC splits the tag array of the LLC in two parts which are indexed by different parts of the cacheline address, the resulting two arrays are:

- The *Tag Array* which holds the tags for the DC-cachelines.

- The Back Pointer Array (BPA) which holds pointers that associate every LLC-cacheline with a tag by specifying the set and way in the tag array in which it is located.

- (a) A DFC Tag Array entry.

- (b) A DFC back pointer array entry.

Figure 2.7: DFC Tag array and BPA entries, shaded fields indicate additions for DFC.

DFC introduces some extra fields in the tag arrays beyond those in a conventional cache. These extra fields facilitate locating the LLC-cachelines using DC-cacheline granularity tags and additionally they store the information needed to access the DRAM cache (DC). These extra fields are shaded in Figures 2.7a and 2.7b for the *tag array* and the *Back Pointer Array* (BPA), respectively. These fields are:

#### • Tag Array:

- Tag valid, Tag LRU: Additional valid and replacement policy fields for the tags, since each tag can be associated with several LLC-cachelines, the tag array must handle validity and replacement independently of the LLC data array.

- DC way: The way in the DRAM cache set in which the DC-cacheline identified by this tag resides.

- DC dirty: Dirty bit for the DC-cacheline in the DRAM cache, since LLC-cacheline evictions are directly forwarded to the DRAM cache, a dirty bit is needed to keep track of written blocks locally in the LLC tag array. This also allows to update the DRAM cache tags (in DRAM) only when a tag is evicted from the LLC tag array.

- count: A counter to keep track of the number of LLC-cachelines that reference a tag. This field is optional as DFC can operate correctly without it, however, as we explain later in our evaluation in Section 2.3, it helps avoid unnecessary BPA lookups when a tag has to be evicted from the tag array.

#### Back Pointer Array:

- Tag suffix: Since each tag can be associated with multiple LLC-cachelines, each cacheline can potentially belong to any tag in a subset of the sets of the tag array. That subset is identified by the tag-suffix part of the address (Figure 2.6b) and must be stored in the back pointer array for every LLC-cacheline.

- **Tag way:** To fully identify the correct tag for an LLC-cacheline in the tag array the way in the set must also be stored in the BPA.

#### 2.2.2 DFC Indexing:

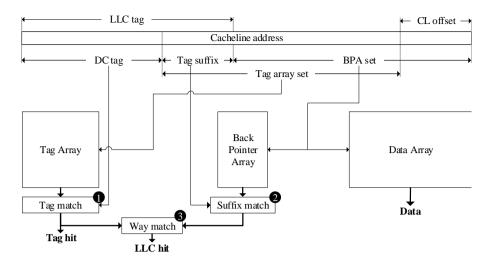

Figure 2.6b shows the breakdown of an address and the bit fields used to index the tag array and the Back Pointer Array (BPA) in the *Decoupled Fused Cache* LLC.

BPA Set: The BPA is indexed using the same indexing bits as conventional caches, these are the Least Significant (LS) bits after the byte offset of the address. • Tag array set: The tag array is indexed by the same bits of the address that would index a cache with a cacheline size equal to the DC-cacheline size. These are the LS bits right after the byte offset and LLC-cacheline offset (CL Offset) parts of the address. The CL Offset depends on the ratio of LLC-cachelines per DC-cacheline and can be 2 to 6 bits for 128 Byte to 4KB DC-cacheline sizes, respectively.

With this indexing, the LLC-cachelines are placed in the LLC data array in the same sets as they would be placed in a conventional LLC. Just like conventional caches, consecutive LLC-cachelines that are parts of the same DC-cacheline will be placed in consecutive sets. In contrast to FC, the LLC-cachelines of the same DC-cacheline are not forced into the same set and thus the set conflicts introduced by FC are avoided.

The tag that identifies an LLC-cacheline can only reside in a subset of the sets in the tag array, the size of this subset depends on the ratio of LLC-cachelines per DC-cacheline. For 64-Byte LLC-cachelines and 4KB DC-cachelines the DC-tag for an LLC-cacheline can reside 64 different sets, for 128-Byte DC-cachelines it can reside in two different sets. As demonstrated by Figure 2.6b, the *tag array set* is comprised of the Most Significant (MS) bits of the *BPA Set* and the *LLC tag suffix* parts of the address. In the DFC example in Figure 2.6a, the tag for a cacheline located in set 110 can only be located in sets 011 and 111 depending on the LLC tag suffix. For cacheline *A.0* the LLC tag suffix is 0 (as shown in Figure 2.5) and so the tag is located in set 011 of the tag array. This indexing allows DFC to decouple the tags from the LLC-cachelines that reference them in order to (a) save space in the tag array of the LLC to store additional information about the location of DC-cachelines in the DRAM cache and (b) to access that information with a single lookup.

#### 2.2.3 DFC tag matching:

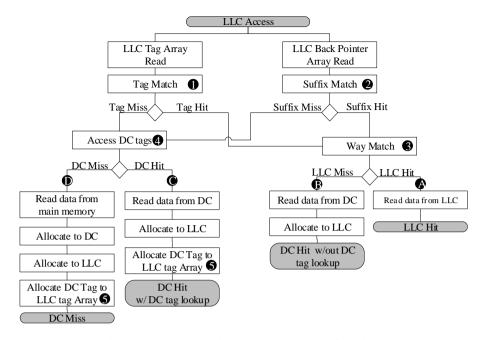

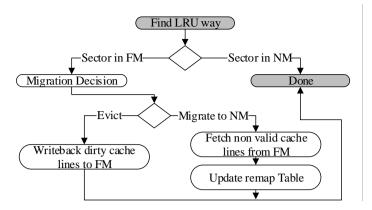

Figure 2.8 depicts the block diagram of the DFC LLC showing the address parts used for indexing the individual arrays as well as for matching the tag-array and BPA. In addition, Figure 2.9 offers a flowchart showing the steps of a DFC access for every possible case: LLC hit (ⓐ), DC hit without tag lookup (⑥), DC hit with tag lookup (⑥), and DC miss (⑥). When a request is made to the LLC, particular parts of the address are used separately as shown in Figure 2.6b. The *Tag array set* part of the address is used to index the tag array and at the same time, the BPA is indexed with the *BPA Set* field of the address. After both arrays have been indexed and the respective sets have been read, their contents must be matched to determine a cache hit or miss.

The matching consists of three steps:

- Tag match: The tags in the tag array set are compared against the *tag* field of the address for a match (Figures 2.8 and 2.9 **1**).

- Suffix Match: The *tag suffix* field of the set of the BPA are compared with the corresponding part of the address (*tag suffix*) for a match (Figures 2.8 and 2.9 2).

- Way Match: The way of the matching tag in the Tag array is compared with the *Tag way* field of each matching suffix in the BPA (Figures 2.8 and 2.9 ③). In case of a match at this stage then this is an LLC hit ④, otherwise an LLC miss (Figure 2.9 ⑤,⑥,⑥).

Figure 2.8: DFC address breakdown, indexing and tag matching process.

The Tag match ① and Suffix Match ② can be performed in parallel as they are independent of each other. The Way Match ③ step however can start only when the previous two steps have completed. If the requested LLC-cacheline is located in the LLC then there is a LLC hit as shown in Figure 2.9 ④. Otherwise, an LLC miss will be handled in one of the following two ways depending on whether the tag of the requested address is in the tag array of the LLC:

- [a] In case the tag is located in the tag array (there was a match at the *Tag match* stage) but there were no LLC-cachelines pointing to that tag (*Suffix match* or *Way match* stailed), then the DC data array can be accessed directly (s) using the *DC-way* field of the tag array entry that matched in the *Tag Match* stage. The physical address of the LLC-cacheline in the DC data array can be calculated from the set and way of the DC-cacheline in the DC. The set can be directly inferred from the physical address of the DC-cacheline and the DC-way is stored in the LLC tag array. The new LLC-cacheline read from the DC is subsequently stored in the LLC data array and its corresponding BPA entry is updated to point to the tag in the LLC tag array. Additionally, the respective fields of the tag entry are updated, in this case, only the replacement (LRU) and *count* bits. The *LRU* of the tag is updated to show that this was the most recently accessed tag in the set. The *count* field is incremented to show that one additional LLC-cacheline is now associated with this tag.

- [b] In case the tag is not located in the LLC tag array (no match in the *Tag match* stage), then the DC tag-array stored in DRAM needs to be accessed (Figure 2.9 **4**). Thereby, it is determined whether the DC-cacheline is located in the DC (**6**) or there is a DC miss and the requested cacheline should be read from the main memory (**b**). In case of a DC miss, a suitable victim DC-cacheline is selected from the DC set using LRU replacement policy and written back to main memory if dirty. The DC-way of the DC-cacheline is then stored in the LLC tag array along with its tag (Figure 2.9 **5**). All subsequent misses of LLC-cachelines that belong to this DC-cacheline can be fetched from the DC directly without accessing the DC tags in DRAM (Figure 2.9 **B**).

Figure 2.9: Decoupled Fused Cache access flowchart.

#### **2.2.4 DFC Tag Evictions:**

When a tag is evicted from the DFC tag array any LLC-cachelines that reference that tag must be evicted from the LLC as well, otherwise they will be orphaned and their *Tag-suffix* and *tag-way* fields in the BPA will point to a stale tag in the tag array. Considering a ratio of *N* LLC-cachelines per DC-cacheline, in the worst case there might be as many as *N* LLC-cachelines that must be evicted in *N* different LLC data array sets. To avoid looking up all the sets that could potentially hold an LLC-cacheline that is associated with a tag, we introduce a counter for every tag to account for the number of these LLC-cachelines, this counter is updated whenever an LLC-cacheline is fetched to or evicted from the LLC. Introducing this counter makes evictions more efficient and, as shown in our experiments, more than 99.5% of the time, with LRU replacement policy for the tags, the counter for the victim tag is zero. A counter equal to zero means that no LLC-cachelines need to be evicted from the LLC because of a tag eviction but also that the corresponding sets in the BPA need not be searched for such LLC-cachelines at all.

Furthermore, when a tag is evicted from the DFC tag array the DC tag array must be updated. The dirty status of the DC-cacheline that corresponds to the evicted tag is copied and the LRU of the DC set is updated. This is necessary since by design all LLC-cacheline writebacks from the LLC to the DC do not need to access the DC tags. Subsequently, the dirty state of the DC-cacheline is stored along with the tag in the tag array (*DC dirty* in Figure 2.7a) and the DC tags are updated only when a tag is evicted from the DFC tag array.

#### 2.2.5 Configurable DC-cacheline size

As shown in our evaluation (Section 2.3) different workloads achieve their best performance with different DC-cacheline sizes. DFC can be configured (at boot time) to accommodate different DC-cacheline sizes ranging from 128 Bytes (two times the LLC-cacheline size) to 4KB (OS page size)<sup>2</sup>. This requires the additional DFC related fields on the LLC tag array and BPA to be provisioned for the worst case size, as shown in the next paragraph. Supporting variable DC-cacheline sizes allows DFC to better fit the needs of a particular workload and maximize performance.

#### 2.2.6 DFC Hardware Overhead:

DFC re-organizes the LLC tag array and changes the indexing and tag matching mechanisms of the LLC. Furthermore, DFC requires the addition of some extra fields in the LLC tag array and splitting it into two separate arrays, these are the *tag array* and the BPA. In this Section we discuss the hardware cost of DFC and in particular its overhead in the LLC tag array.

When calculating the overhead of DFC we must take into account the characteristics of the DC and also the ratio of LLC-cachelines per DC-cacheline. Let the ratio of LLC-cachelines per DC-cacheline be  $R \in [2-64]$ , the LLC associativity be A, and the DC-associativity be B for the rest of our analysis.

The extra fields needed in the LLC tag arrays are:

#### • DC-Tag Array:

- **DC dirty:** One bit for the dirty state of the DC-cacheline.

- DC way: Log<sub>2</sub>B bits for the DC way where the DC-cacheline is located.

- **count:**  $Log_2R + 1$  bits for the counter of LLC-cachelines that reference this tag (from 0 to R LLC-cachelines).

- Tag valid: Valid bit for the tag.

- Tag LRU: Log<sub>2</sub>A LRU bits for Tag replacement.

#### Back Pointer Array:

- Tag suffix: Log<sub>2</sub>R bits that identify the set in which the tag of the LLC-cacheline is located.

- Tag way: Log<sub>2</sub>A bits to identify the way in which the tag of the LLC-cacheline is located in its set.

The above listed fields account for an total of  $2 \times \log_2 R + 2 \times \log_2 A + Log_2 B + 3$  bits per LLC-cacheline. However we can further reduce the cost by one bit per LLC-cacheline by using the valid bit as a part of the counter and offsetting the count by one. Additionally, the tag in a DFC is  $\log_2 R$  bits smaller than a conventional LLC tag. Thus, the additional space overhead of DFC is:  $\log_2 R + 2 \times \log_2 A + Log_2 B + 2$ . To support different DC-cacheline sizes, we must account for the worst case overhead of the fields in the Tag Array and the BPA, this is the overhead for the 4KB DC-cacheline.

To quantitatively present the hardware cost in the LLC we use a realistic example that matches our experimental setup configuration. Lets consider a system with 48

<sup>&</sup>lt;sup>2</sup>Larger DC-cacheline sizes can be supported at little additional cost but we consider up to 4KB DC-cacheline size to keep within the granularities considered in competing designs.

2.3. EVALUATION 23

| DC-cacheline size | DC-cacheline /      | Added Bits per | LLC extra cost |

|-------------------|---------------------|----------------|----------------|

|                   | LLC-cacheline ratio | Entry          | %              |

| 128 Byte          | 2                   | 15             | 224KB (2.5%)   |

| 256 Byte          | 4                   | 16             | 240KB (2.9%)   |

| 512 Byte          | 8                   | 17             | 256KB (3.1%)   |

| 1024 Byte         | 16                  | 18             | 272KB (3.3%)   |

| 2048 Byte         | 32                  | 19             | 288KB (3.5%)   |

| 4096 Byte         | 64                  | 20             | 320KB (3.7%)   |

| configurable (128 | 2-64                | 20             | 320KB (3.7%)   |

| Byte-4KB)         |                     |                |                |

Table 2.1: DFC SRAM overhead.

bit physical addresses, 64-Byte LLC-cachelines and a 16-way LLC with 8192 sets (total LLC capacity of 8MB). The 6 Least Significant (LS) bits are the byte offset in an LLC-cacheline and are not used for accessing the cache since it operates at LLC-cacheline granularity. The next 13 bits are used to index the 8192 sets of the cache (2<sup>13</sup> sets). This means that each tag in the tag array is 29 bits long. For a 16 way LLC we also need 4 bits for LRU replacement policy and 2 more bits for valid and dirty flags. The total size for an entry in a tag array of a 8MB 16-way cache is thus 35 bits and the total size of the tag array is 560KB. We also assume a 512MB, 16-way set associative DC as in our evaluation.

Table 2.1 Shows the overhead of DFC in terms of additional storage required in the DFC tag array for every different supported DC-cacheline size. The worst case overhead of the DFC design is 320KB for a 8MB LLC which accounts for a 3.7% area overhead.

The hardware overhead of DFCs indexing and tag-matching mechanisms is very small compared to a conventional LLC in terms of additional space required in the LLC tag array. As far as lookup latency is concerned, the modified indexing and tag-matching mechanisms do not impose extra latency to the cache access compared to a conventional LLC. Steps ① and ② in Figure 2.8 are faster than a traditional LLC tag lookup because the number of compared bits is smaller. Step ③, which adds to the latency of steps ① and ② in practice adds a 32-bit product of sums logic delay. This delay does not add a cycle to the LLC access time as it is within the available slack estimated by *Cacti* [42] after accounting for its logic latency in the same technology node.

#### 2.3 Evaluation

In this section we present the evaluation of the proposed *Decoupled Fused Cache* and compare with state-of-the-art designs that target the tag access cost for DRAM caches. We first present our experimental setup followed by the results of our evaluation in terms of performance and energy consumption for a series of single- and multi-threaded benchmarks for different DC-cacheline sizes.

| Cores      | 4 cores, out-of-order, 4-way issue/commit 3.2 GHz       |

|------------|---------------------------------------------------------|

| L1 Cache   | Private, 64 KB, 4-way, 1 cycle access latency           |

| L2 Cache   | Private, 256 KB, 8-way, 9 cycles access latency         |

| L3 Cache   | Shared 8MB, 16-way, 14 cycles access latency            |

| DRAM Cache | 512 MB, 16-way, 2 128-bit channels, 8ns tRCD, 10ns      |

|            | tCAS, 1.6 GHz (DDR 3.2GHz)                              |

| Tag cache  | 256 KB (272KB including its tag array), 8-way, 5 cycles |

|            | access latency                                          |

| Main DRAM  | 8 GB, 2 channels, 64 bit bus, 14ns tRCD, 14ns tCAS, 800 |

|            | MHz (DDR 1.6GHz)                                        |

Table 2.2: System configuration.

Table 2.3: Main DRAM and 3D-DRAM energy consumption.

| Parameter          | 3D-DRAM   | Main Memory DRAM |

|--------------------|-----------|------------------|

| RD/WR + I/O energy | 6.4pJ/bit | 33pJ/bit         |

| ACT/PRE DRAM Row   | 15nJ      | 15nJ             |

#### 2.3.1 Experimental Setup

Our evaluation is performed using an in-house simulator based on *Pin* [43] following the interval-based simulation methodology [44] for the processor and cycle-accurate modelling of the cache and memory system. We simulate a four core processor with private L1 and L2 caches, a shared on-chip last level cache (LLC) and a DRAM cache (DC). Table 2.2 presents the configuration of our system<sup>3</sup>. We use *Cacti v6.5* to determine the access times for the caches and tag arrays [42]. For the main DRAM and 3D-DRAM timing and energy consumption we use the parameters provided by [21]. The DRAM energy parameters are shown in Table 2.3. To estimate the energy consumption of the processor cores we use McPAT [45].

We evaluate our design with both single- and multi-threaded workloads. For single-threaded workloads, we selected a representative subset of the SPEC2006 [46] benchmarks following the guidelines of Phansalkar et al. [47]. For multi-threaded workloads we used the *OpenMP* version of the *NAS Parallel Benchmark* suite [48,49].

We simulate one billion instructions for every thread after a warmup period of 100 million instructions. For the NAS benchmarks we select the simulated portion immediately after the initialization phase of each benchmark, while for the SPEC benchmarks we use *simpoints* to select a representative slice of one billion instructions [50]. The benchmarks used and their memory footprint are shown in Table 2.4.

Finally, our evaluation considers the following design points:

- Baseline: A system with no DRAM cache.

- **DRAM Cache (DC):** A system with a DRAM cache and tags-in-DRAM.

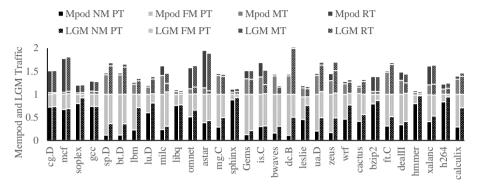

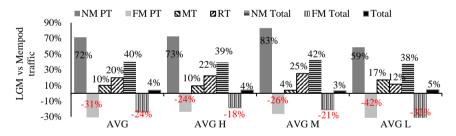

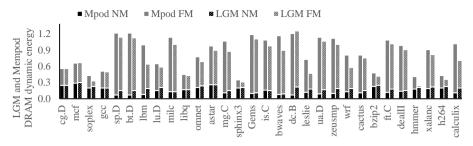

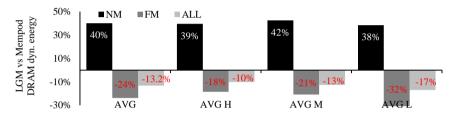

- DRAM Cache with Tag-Cache (DCTC): a DRAM cache system with tags in DRAM and an on-chip SRAM cache of the DC-tags similar to *ATCache* [19]. The size of the DCTC SRAM tag cache is equal to the size of the SRAM overhead incurred by DFC.