## CMOS DATA CONVERTERS FOR CLOSED-LOOP MMWAVE TRANSMITTERS

Victor Åberg

Department of Computer Science and Engineering Chalmers University of Technology Göteborg, Sweden, 2020 CMOS DATA CONVERTERS FOR CLOSED-LOOP MMWAVE TRANSMITTERS

Victor Åberg

©Victor Åberg, 2020

Technical report 212L ISSN 1652-876X

Department of Computer Science and Engineering Chalmers University of Technology SE-412 96 Göteborg Sweden Telephone:  $+46-(0)31-772\,10\,00$

Cover: Chip photo of the  $2{\times}6\,\mathrm{bit}$  RF IQ modulator presented in chapter 3.

Printed by Chalmers digitaltryck Chalmers Tekniska Högskola Göteborg, Sweden, 2020 CMOS DATA CONVERTERS FOR CLOSED-LOOP MMWAVE TRANSMITTERS Victor Åberg Department of Computer Science and Engineering Chalmers University of Technology

#### Abstract

With the increased amount of data consumed in mobile communication systems, new solutions for the infrastructure are needed. Massive multiple input multiple output (MIMO) is seen as a key enabler for providing this increased capacity. With the use of a large number of transmitters, the cost of each transmitter must be low. Closed-loop transmitters, featuring high-speed data converters is a promising option for achieving this reduced unit cost.

In this thesis, both digital-to-analog (D/A) and analog-to-digital (A/D) converters suitable for wideband operation in millimeter wave (mmWave) massive MIMO transmitters are demonstrated. A 2×6 bit radio frequency digital-to-analog converter (RF-DAC)-based in-phase quadrature (IQ) modulator is demonstrated as a compact building block, that to a large extent realizes the transmit path in a closed-loop mmWave transmitter. The evaluation of an successive-approximation register (SAR) analog-to-digital converter (ADC) is also presented in this thesis. Methods for connecting simulated and measured performance has been studied in order to achieve a better understanding about the alternating comparator topology.

These contributions show great potential for enabling closed-loop mmWave transmitters for massive MIMO transmitter realizations.

**Keywords:** CMOS, Data converter, IQ-modulator, mmWave, RF-DAC, SAR ADC

## **Publications**

This thesis is based on the work contained in the following papers:

- [A] V. Åberg, C. Fager, and L. Svensson, "Design Considerations and Evaluation of a High-Speed SAR ADC", in *IEEE Nordic Circuits and Systems Conference (NORCAS): NORCHIP and International Symposium of System-on-Chip (SoC)*, 2018, pp. 1-6.

- [B] V. Åberg, C. Fager, and L. Svensson, "A 2×6b 8GS/s 17-24GHz I/Q RF-DAC Transmitter in 22nm FDSOI CMOS", submitted to *IEEE Solid-State Circuits Letters*, 2020, pp. 1-4.

## Contents

| Abstract |                   |         |                                            |      |  |  |  |  |  |

|----------|-------------------|---------|--------------------------------------------|------|--|--|--|--|--|

| Pι       | Publications      |         |                                            |      |  |  |  |  |  |

| A        | f Acknowledgement |         |                                            |      |  |  |  |  |  |

| A        | crony             | yms     |                                            | xiv  |  |  |  |  |  |

| 1        | Inti              | roducti | ion                                        | 1    |  |  |  |  |  |

|          | 1.1               | Closed  | d-loop mmWave transmitter                  | . 2  |  |  |  |  |  |

|          | 1.2               | CMOS    | S integration                              | . 3  |  |  |  |  |  |

|          | 1.3               | Goal    |                                            | . 3  |  |  |  |  |  |

|          | 1.4               | Thesis  | s outline                                  | . 3  |  |  |  |  |  |

| <b>2</b> | Bac               | kgrou   | nd on RF digital-to-analog conversion      | 5    |  |  |  |  |  |

|          | 2.1               | Modu    | lation theory                              | . 5  |  |  |  |  |  |

|          |                   | 2.1.1   | Mathematical definition of modulation      | . 6  |  |  |  |  |  |

|          |                   | 2.1.2   | Modulation principle in time and frequency | . 6  |  |  |  |  |  |

|          |                   | 2.1.3   | Modulation formats                         | . 8  |  |  |  |  |  |

|          |                   | 2.1.4   | Pulse-shaping                              | . 11 |  |  |  |  |  |

|          | 2.2               | Figure  | es of merit                                | . 12 |  |  |  |  |  |

|          |                   | 2.2.1   | Error vector magnitude                     | . 13 |  |  |  |  |  |

|          |                   | 2.2.2   | Efficiency metrics                         |      |  |  |  |  |  |

|          |                   | 2.2.3   | Energy consumption per bit                 |      |  |  |  |  |  |

|          | 2.3               | Topole  | ogical alternatives                        | . 17 |  |  |  |  |  |

|          |                   | 2.3.1   | The classical transmitter approach         |      |  |  |  |  |  |

|          |                   | 2.3.2   | Cartesian RF-DAC                           |      |  |  |  |  |  |

|          |                   | 2.3.3   | Polar RF-DAC                               |      |  |  |  |  |  |

|          |                   | 2.3.4   | Outphasing transmitter                     |      |  |  |  |  |  |

|          |                   | 2.3.5   | Topology comparison                        | . 21 |  |  |  |  |  |

|   | 2.4           | Code dependent efficiency                  |

|---|---------------|--------------------------------------------|

|   | 2.5           | Non-overlapping LO                         |

| 3 | $\mathbf{RF}$ | IQ modulator design and evaluation 27      |

|   | 3.1           | Proof of concept                           |

|   | 3.2           | Unit cell                                  |

|   | 3.3           | RF IQ modulator core topology              |

|   | 3.4           | LO generation                              |

|   | 3.5           | Testability                                |

|   | 3.6           | Manufactured chip                          |

|   | 3.7           | Measurements                               |

|   |               | 3.7.1 Static measurements                  |

|   |               | 3.7.2 Modulated measurements               |

|   | 3.8           | Performance                                |

|   |               | 3.8.1 Static performance                   |

|   |               | 3.8.2 Modulated performance 42             |

| 4 | Boo           | kground on analog-to-digital conversion 49 |

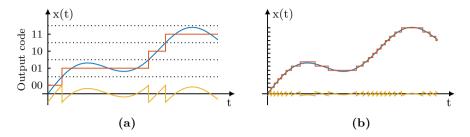

| 4 | 4.1           | Conversion theory                          |

|   | 4.1           | 4.1.1 Sampling                             |

|   |               | 4.1.2 Quantization                         |

|   |               | 4.1.3 Combining sampling and quantization  |

|   | 4.2           | Theoretical and practical limits           |

|   | 7.2           | 4.2.1 Quantization noise                   |

|   |               | 4.2.2 Thermal noise                        |

|   |               | 4.2.3 Jitter                               |

|   |               | 4.2.4 Matching                             |

|   | 4.3           | Figures of merit                           |

|   | 1.0           | 4.3.1 Dynamic metrics                      |

|   |               | 4.3.2 Static metrics                       |

|   |               | 4.3.3 Comparison metrics                   |

|   | 4.4           | High-speed converter topologies            |

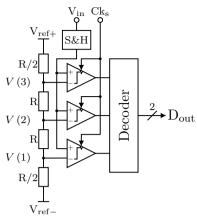

|   | 1.1           | 4.4.1 Flash                                |

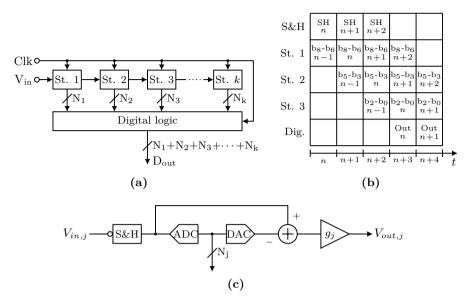

|   |               | 4.4.2 Pipeline                             |

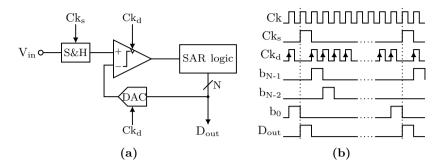

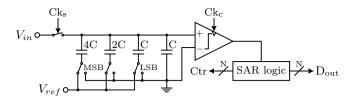

|   |               | 4.4.3 Successive-approximation register 63 |

|   |               | 4.4.4 Topological trends                   |

|   | 4.5           | Charge-redistribution                      |

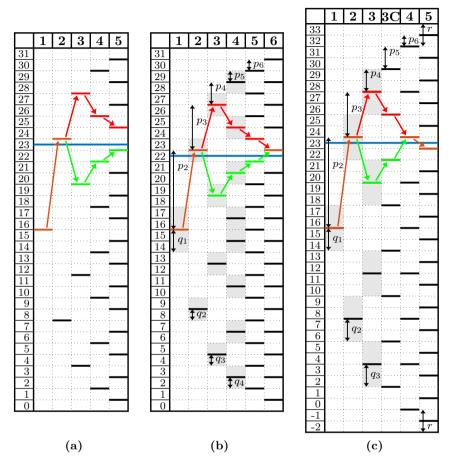

|   | 4.6           | Redundant scaling                          |

|   |               |                                            |

| <b>5</b> | $\mathbf{AD}$ | $\operatorname{sign}$ and evaluation        |  |  | 71 |    |

|----------|---------------|---------------------------------------------|--|--|----|----|

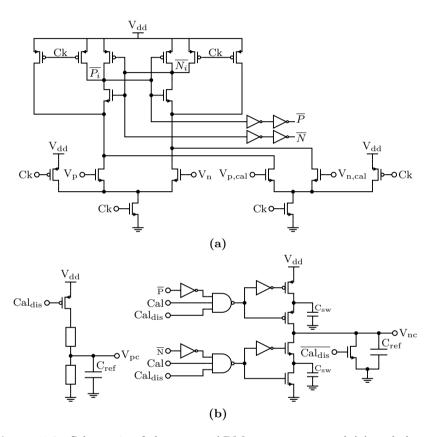

|          | 5.1           | Alternating comparator topology             |  |  |    | 73 |

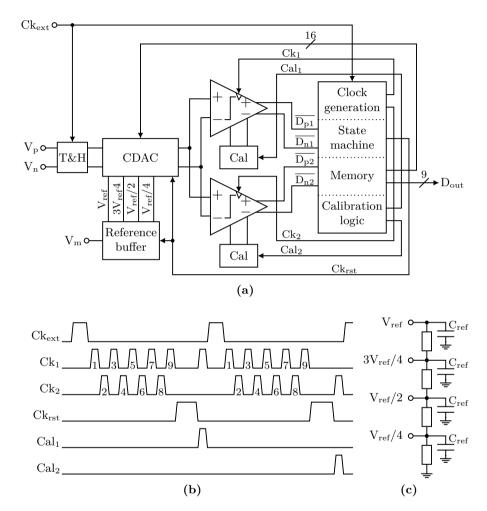

|          | 5.2           | Capacitive DAC                              |  |  |    | 76 |

|          | 5.3           | Asynchronous logic                          |  |  |    | 79 |

|          | 5.4           | Testability                                 |  |  |    |    |

|          | 5.5           | Manufactured chip                           |  |  |    | 80 |

|          | 5.6           | Measurements                                |  |  |    |    |

|          |               | 5.6.1 Measured performance                  |  |  |    |    |

|          | 5.7           | Evaluation and performance analysis         |  |  |    | 84 |

|          |               | 5.7.1 Output clock and data feedthrough     |  |  |    |    |

|          |               | 5.7.2 Excess noise around the signal        |  |  |    |    |

|          |               | 5.7.3 Comparator offset voltage             |  |  |    |    |

| 6        | Cor           | nclusions                                   |  |  |    | 93 |

|          | 6.1           | Future work                                 |  |  |    | 94 |

|          |               | 6.1.1 Increased RF-DAC resolution           |  |  |    | 94 |

|          |               | 6.1.2 Quadrature LO generation              |  |  |    |    |

|          |               | 6.1.3 Co-integration with PA                |  |  |    |    |

|          |               | 6.1.4 Closed-loop transmitter demonstration |  |  |    |    |

| R        | efere         | nces                                        |  |  |    | 97 |

## Acknowledgement

First and foremost, I want to express my deepest gratitude to my main supervisor, Dr. Lars Svensson, for his immense support, deep understanding, and for the perspectives to all the unexpected events that has taken place during this journey. Also, thanks for always being there, guiding me around this uncharted territory.

I want to thank my co-supervisor, prof. Christian Fager, for his immense support, for sharing his deep knowledge about modelling and measurements, and most importantly, for always being there to help.

I want to thank my examiner, Prof. Per Larsson-Edefors, for his support, input, and ideas.

I want to thank my office mates: Dr. Christoffer Fougstedt, Dr. Kevin Cushon, Erik Börjeson, Dr. Erik Ryman, Dr. Mohammed Abdulaziz, and Han Zhou for all the interesting discussion, fun times, and for the help with mastering the CAD tools.

I want to thank Dr. Lena Perterson, Prof. Jan Jonsson, and Alexandra Angerd for your support and understanding when I, at times, was tied up with completing my designs for tape-out, thus not being able to fully help out with teaching.

I also want to thank MEL for their support in the measurement lab. I want to thank Globalfoundries for sponsoring the manufacturing of the 22 nm chips. I want to thank Johan, Thomas, and Jean-Pierre at Keysight for rapidly sourcing measurement equipment and software at times when my measurements were in limbo, caused by unforeseen events. I want to thank my co-workers at the Computer Engineering division for all interesting discussions. I want thank the GHz center at Chalmers, Vinnova, and the industry partners in the ELEMENT project for their financial support and for interesting discussions and input during the project meetings.

In addition, I also want to thank my fellow guiders and board members in Varbergs NSF Scoutkår for their support and understanding when I, at times, have been too busy to help out with the activities.

Finally, I would like to express my deepest gratitude to my parents Eva and Jan and my sister Anna for their fantastic support throughout this journey.

> Victor Åberg Göteborg, 2020

## Acronyms

$\begin{array}{ll} \text{2D} & \text{2 dimensional} \\ \text{5G} & \text{fifth generation} \\ \text{A/D} & \text{analog-to-digital} \end{array}$

ADC analog-to-digital converter AM amplitude modulation

AWG arbitrary waveform generator

BB baseband BER bit-error rate

CDAC capacitive digital-to-analog converter

CMOS complementary metal oxide semiconductor

CW continuous wave D/A digital-to-analog

DAC digital-to-analog converter

DC direct current

DE drain efficiency

DNL differential non-linearity DPD digital pre-distortion DR dynamic range

DSP digital signal processing ENOB effective number of bits EVM error vector magnitude

FDSOI fully-depleted silicon-on-insulator

FF flip-flop

FFT Fast Fourier transform

FoM figure of merit

FoMS Schreier figure of merit FoMW Walden figure of merit

FPGA field-programmable gate array

GaAs gallium arsenide

HD harmonic distortion

I in-phase

IF intermediate frequency

INL integral non-linearity

IQ in-phase quadrature

ISI intersymbol interference

LO local oscillator LSB least significant bit

MIMO multiple input multiple output

mmWave millimeter wave MSB most significant bit

NR new radio

OSR oversampling ratio PA power amplifier

PAE power added efficiency

PAPR peak-to-average power ratio

PCB printed circuit board PPF polyphase filter

PPG pulse pattern generator

PRBS pseudorandom binary sequence

PSD power spectral density Q quadrature-phase

QAM quadrature amplitude modulation

QFN quad flat no-lead RF radio frequency

RF-DAC radio frequency digital-to-analog converter

RMS root mean square RRC root raised cosine

SAR successive-approximation register SFDR spurious free dynamic range

SiGe silicon germanium

SNDR spurious free dynamic range

SNR signal-to-noise ratio

SRAM static random-access memory

TI time interleave

VHDL very high speed integrated circuit hardware

description language

ZOH zero-order hold

## Chapter 1

### Introduction

We continuously consume more and more data as we spend more time online: working, communicating with friends and family, and entertaining ourselves. For the last couple of years, a yearly 60% increase in global mobile traffic has been observed [1]. This trend is expected to continue for the coming years. To support this increased demand, new technologies are needed.

Traditionally, frequencies in the sub-6 GHz band has been used for mobile communication [2]. However, these frequency bands are highly crowded, supporting not only mobile communication but also satellite communication, defence systems, and aeronautical systems just to mention a few [2]. Allocating additional frequency resources for mobile communication in order to support the increased demands is therefore hard. In the newly-introduced fifth generation (5G) new radio (NR) mobile communication standard, millimeter wave (mmWave) bands in frequency range 2 (24.5–40 GHz) are allocated for multi-Gb/s communication [3].

An important component in the realisation of 5G NR mmWave transmitters is the use of beamforming and massive multiple input multiple output (MIMO) [4]. Arranging tens or hundreds of antennas in arrays enables multi-beam operation, allowing for multiple parallel channels using the same spectral resources [5]. The high power consumption resulting from assigning a transceiver to each antenna element in the array is seen one of the major challenges that needs to be solved before the deployment of mmWave massive MIMO systems [6].

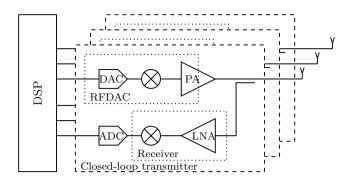

Figure 1.1: Illustration of generic closed-loop transmitter in a MIMO setting.

#### 1.1 Closed-loop mmWave transmitter

Realizing a mmWave massive MIMO transmitter where each antenna element is individually driven, is a major challenge. This not only due to the power consumption, but also due to the small wavelength of mmWave signals, resulting in small antenna separation, thus limiting the allowable size of each individual transceiver.

Using higher-complexity digital techniques to compensate for analog impairments is seen as a key enabler for relaxed hardware requirements, allowing for reduced size and increased efficiency [7]. To train the digital pre-distortion (DPD) algorithms, they need to know the behaviour of the transmitted signal, thus requiring a feedback path [8]. A generic closed-loop array transmitter is shown in figure 1.1. It shows how the transmitted signal is tapped and feed back into the digital signal processing (DSP), adapting the transmitted signal to reduce the effect of the analog impairments. This feedback path can either be in constant operation, or be used during shorter training sequences. In any case the feedback path must handle the entire transmitted bandwidth, thus requiring analog-to-digital converters (ADCs) with both high sample rate and high bandwidth.

To further reduce the transmitter cost, alternative architectures are needed, combining multiple analog functionalities into a single building block [6]. Radio frequency digital-to-analog converters (RF-DACs) are seen as a promising option, combining the digital-to-analog converter (DAC), mixer, and to some extent the power amplifier (PA) into a single building block, bringing a significantly reduced transmitter cost [9, 10].

#### 1.2 CMOS integration

Integration of mmWave circuits have for long been done in compound semiconductors, such as silicon germanium (SiGe) and gallium arsenide (GaAs), as these provide excellent analog performance [11, Ch. 11]. GaAs is often chosen for its higher output power [12] while SiGe enables tighter integration [11, Ch. 11].

Thanks to its aggressive scaling, tight integration, and power efficient operation, there is no technology that can compete with complementary metal oxide semiconductor (CMOS) when it comes to the realization of digital circuits.

In massive MIMO, a tight integration between analog and digital components is needed to achieve a low transmitter cost, making CMOS the only viable option. This forces analog building blocks, operating at mmWave frequencies to also be implemented in CMOS [13].

#### 1.3 Goal

The work reported in this thesis addresses fully-depleted silicon-oninsulator (FDSOI) CMOS implementations of both the data converters shown in figure 1.1. The goal is to explore the design space for circuits at the required performance level, using state-of-the-art silicon processes; and also to provide contributions in the testing and characterization of the experimental circuits.

#### 1.4 Thesis outline

The continuation of the thesis is outlined as follows: Theoretical framework and fundamental concepts for designing and evaluating RF-DACs are presented in chapter 2. The design and evaluation of an radio frequency (RF) in-phase quadrature (IQ) modulator is then presented in chapter 3. These two chapters focuses on the design and evaluation of RF-DAC based IQ modulators. The two following chapters will focus on the design and evaluation of an ADC, starting with the theoretical framework, fundamental concepts and topological alternatives in chapter 4. The design and evaluation of a successive-approximation register (SAR) ADC will then follow in chapter 5. The thesis will then be concluded in chapter 6, summarizing the contributions and looking at future work.

## Chapter 2

# Background on RF digital-to-analog conversion

This chapter will present the theoretical framework needed to understand the principles behind a modulator. The chapter will also cover different topological options for RF-DAC based IQ modulators and metrics for evaluating them.

#### 2.1 Modulation theory

The modulator is an essential part of a transmitter; it is responsible for placing the information that is to be transmitted onto the carrier. A continuous wave (CW) signal cannot transmit any information since its behaviour is static over time, although it is alternating within a period. The amount of information that can be transmitted on a white Gaussian noise channel is given by the Shannon theorem, equation (2.1) [14]. This equation gives the total channel capacity C, given the channel bandwidth B and signal-to-noise ratio (SNR).

$$C = B \log_{10} (1 + SNR)$$

[b/s] (2.1)

Below, the theory behind modulation will be studied in more detail, starting with the mathematical definition. The principle behind modulation will then be described, followed by the principles behind pulse shaping.

#### 2.1.1 Mathematical definition of modulation

The mathematical definition of modulation is a multiplication between a time-varying signal  $v_m(t)$  and the CW carrier  $v_c(t)$ , given by equation (2.2). Let us first study amplitude modulation (AM), using a sine wave as the modulating signal  $v_m$ , equation (2.3). Multiplying the CW carrier, equation (2.2), with the modulation, equation (2.3), gives the modulated signal in equation (2.4).

$$V_c = v_c \sin\left(2\pi f_c t\right) \tag{2.2}$$

$$v_m(t) = v_a \sin(2\pi f_s t) \tag{2.3}$$

$$v(t) = v_a \sin(2\pi f_s t) \cdot v_c \sin(2\pi f_c t) = v_a v_c \sin(2\pi (f_c \pm f_s) t) \qquad (2.4)$$

Finally, let us now consider a time-varying amplitude and phase signal  $v_m$ , given by equation (2.5). Multiplying this signal to the carrier, equation (2.2), then gives equation (2.6).

$$v_m(t) = v_a(t)\sin(\varphi(t)) \tag{2.5}$$

$$v\left(t\right) = v_{a}\left(t\right)\sin\left(\varphi\left(t\right)\right) \cdot v_{c}\sin\left(2\pi f_{c}t\right) = v_{c}v_{a}\left(t\right)\sin\left(2\pi f_{c}t \pm \varphi\left(t\right)\right) \tag{2.6}$$

In a communication system, the time-varying signals,  $v_a(t)$  and  $\varphi(t)$ , represents the movement between discrete points, so called constellation points, located in the complex plane. All the constellation points for a given modulation format forms a constellation diagram, representing all the values that  $v_a(t)$  and  $\varphi(t)$  can take.

#### 2.1.2 Modulation principle in time and frequency

Based on the mathematical definition above, we can now study the waveforms used to form modulated signals, both in time and frequency domain.

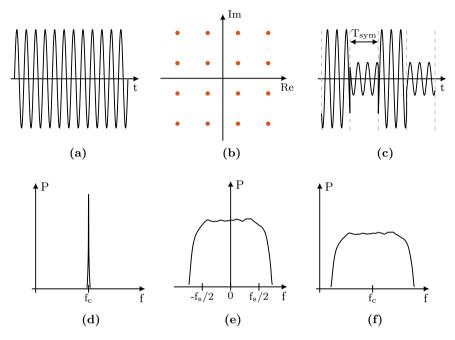

In the time domain, we have the CW signal shown in figure 2.1a. The data to be transmitted is represented by a sequence of symbols, each having a unique combination of amplitude and phase defined by its

**Figure 2.1:** Illustration of the modulation principle in both time (a)-(c) and frequency (d)-(f) domain.

location in the constellation diagram, as shown in figure 2.1b. This time-varying amplitude and phase signal is multiplied with the CW signal, forming the modulated signal shown in figure 2.1c. In this figure we can observe how the amplitude and phase change at uniformly separated instances in time, with a spacing equal to the symbol duration  $T_{\rm sym}$ .

Now, let us look at the principle behind modulation in the frequency domain. The CW signal is represented by a narrow pulse in figure 2.1d, ideally consisting of a single frequency, although noise causes it to spread out. From equation (2.6), we know that the frequency domain baseband (BB) data will appear at both sides of the carrier. The BB frequency domain spectrum presented in figure 2.1e, uses a oversampled pulse-shaping filter to provide a band-limited signal (the signal in figure 2.1c does not use such a filter). Here, two samples per symbol are used, thus relating the sample rate to the symbol duration as follows:  $T_{sym} = 2/f_s$ . The spectral behaviour is the same, both for fully random signals and random sequences with finite length, given that the latter is long enough

to appear random. In the time domain, the modulation was applied through a multiplication. The corresponding operation in the frequency domain is an addition between the BB signal and the carrier, thus, only shifting the center frequency of the BB signal, locating it around the carrier  $f_c$  as shown in figure 2.1f.

From figure 2.1e, it appears like the BB signal bandwidth is doubled, as the signal covers the band  $[-f_s/2, f_s/2]$ . For real signals, such as those used in AM, the spectrum is symmetrical around the carrier, thus, only a single side-band needs to be transmitted. For complex signals, such as those used in quadrature amplitude modulation (QAM), the spectrum is asymmetrical around the carrier, making both side-bands important. The asymmetrical spectrum is a result of combining the two orthogonal signals which make up the complex QAM signals. As one DAC is needed on the transmit-side and one ADC is needed on the receive-side, for each orthogonal component, the effective sample rate is doubled as the orthogonal signals are processed in parallel, thus resulting in the increased bandwidth.

#### 2.1.3 Modulation formats

Above we presented how data is modulated on to the carrier. The chosen modulation format will not only affect the complexity of the modulator implementation. It will also set the amount of data that can be transmitted for a given bandwidth. The spectral efficiency S is a metric of the number of bits that can be transmitted per spectral resource. Equation (2.7) gives the spectral efficiency for a bit-rate  $R_b$  and a bandwidth BW.

$$S = \frac{R_b}{\text{BW}} \quad [b/(\text{Hz s})] \tag{2.7}$$

With limited spectral resources, a high spectral efficiency is important in order to achieve a high bandwidth. The spectral efficiency is listed in table 2.1 for a few different modulation formats with varying complexity.

Each symbol in a modulated signal is represented by a unique amplitude, or by a unique phase, or by a unique combination of these two. A constellation diagram shows all the symbols that can be transmitted, for a given modulation format, arranging them after their amplitude and phase. The constellation diagrams for a few different modulation

| Modulation | Spectral efficiency |

|------------|---------------------|

| Iomat      | [b/(Hzs)]           |

| OOK        | 1                   |

| PAM-4      | 2                   |

| QPSK       | 2                   |

| 16-QAM     | 4                   |

| 32-QAM     | 5                   |

| 64-QAM     | 6                   |

| 256-QAM    | 8                   |

| 1024-QAM   | 10                  |

Table 2.1: Spectral efficiency for different modulation formats.

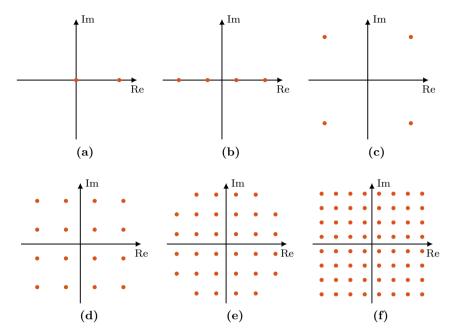

formats of varying complexity are shown in figure 2.2. The principle behind a few of them will be described below.

The simplest AM format is OOK, shown in figure 2.2a, which builds on toggling the carrier on and off according to the bit-stream. This is however not a very effective modulation format as can be seen in table 2.1. The principle behind OOK can be extended further with the introduction of additional amplitude levels and sign. A constellation diagram for a PAM with four levels is shown in figure 2.2b. The spectral efficiency is given as  $\log_2$  of the number of levels used. Clearly, it can be seen that the number of levels needed rapidly increase with demands for higher spectral efficiency.

PAM4 introduces the phase as a means to transfer information. By further using the phase it becomes possible to construct 2 dimensional (2D) constellations, giving higher spectral efficiency while requiring fewer levels along each direction. The simplest 2D modulation format is QPSK, shown in figure 2.2c, which modulates only the phase of the carrier (the amplitude is constant regardless of the transmitted data). By introducing additional amplitude levels to the 2D modulation formats, we introduce QAM. This set of modulation formats was first introduced in 1960 [15], and few years later, the square QAM typically seen today was introduced [16]. A few different QAM formats are show in figures 2.2d to 2.2f, containing 16, 32, and 64 constellation points respectively. For these modulation formats, the number of levels needed along each orthogonal direction is the square-root (rounded up) of the

**Figure 2.2:** Illustration of a few commonly used modulation formats, ranging from simple formats, such as OOK (a), PAM (b), and QPSK (c), to more complex QAM formats (d)-(f).

number of constellation points for the given modulation format, clearly showing a large gain compared to using PAM. If the grid contains more locations than the number of constellation points provided by the modulation format, the locations in the corners are not used, as can be seen in figure 2.2e. The reason is that these locations suffers more from non-linearities in the transmitter as these locations have the highest signal power, thus making them more suitable to exclude.

The mapping of digital data onto the constellation points is typically done using Gray encoding [17, Ch. 3]. The benefit with this encoding is that the bit sequence mapped to each constellation point only differs by one bit for the closest located constellation points. Thereby the bit-error rate (BER) is minimized when detecting the received data as the constellation points most likely to be erroneously detected are the ones located closest to the intended value. Mapping principles can be used to reduce the peak-to-average power ratio (PAPR), where scrambling methods, such as block level codes are popular [18].

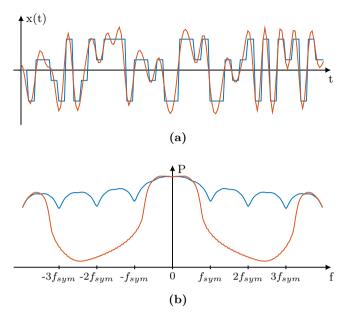

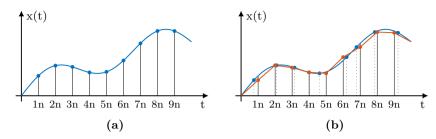

Figure 2.3: Time domain behaviour is shown in (a) for an AM signal outputted by a DAC modelled by a ZOH function (blue) and the corresponding pulse-shaped signal (orange). The frequency domain behaviour is shown in figure 2.3b.

#### 2.1.4 Pulse-shaping

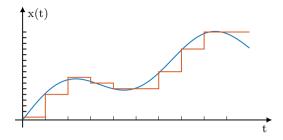

The DAC output can be modelled by a block that connects a digital code to an analog value and a block that keeps this value constant for the entire sample duration. The time domain output signal for a DAC modelled by a zero-order hold (ZOH) function is shown in figure 2.3a together with the corresponding signal fed through a pulse shaping filter. In the figure it can been seen how the ZOH gives a box-shaped signal. The signal passing through the pulse-shaping filter is smother, at the cost of overshooting the range. The frequency domain behaviour is shown in figure 2.3b for the two signals. The ZOH function here translates into a sinc function with zeros at every multiple of the symbol frequency  $f_{sym}$ . The oversampled and pulse-shaped signal suppresses the signal further outside the transmitted band but the images around  $f_s$  cannot be compensated for.

In modern communication systems, requirements are not only tough on the signal quality within the transmitted band, but also in the neighbouring bands, making it important to suppress the out-of-band emissions, such as the ones caused by the ZOH. In addition, non-linear distortion in the channel introduces intersymbol interference (ISI), making symbols dependent on each other. By properly selecting a filter, the signal can both be band-limited and ISI can be prevented at the sampling instances [19, Ch. 8]. The root raised cosine (RRC) filter is popular in communication systems as the same filter can implemented both in the transmitter and in the receiver for an overall ISI-free channel.

Combining the pulse-shaping filter with oversampling introduces additional points along the path from one constellation point to the next, bringing a smoother signal [17, Ch. 4]. The oversampling ratio (OSR) is defined as the ratio between the sample rate and the symbol rate in the system. Oversampling also simplifies the requirements on the analog filter needed to suppress images, as they are further separated by the increased sample rate [17, Ch. 4]. While oversampling mainly affects the out-of-band properties, it can also improve the in-band performance. As the transition rates when moving from one constellation point to another is reduced, smother transitions are allowed, stressing the circuit less. To fully benefit from oversampling, an increased DAC resolution is needed in order to provide additional levels in between the constellations points, used to smoothen the transition from one symbol to the next.

A drawback with using oversampling is that it increases the required sample rate for the DAC for a given symbol rate, or it reduces the symbol rate for a given sample rate. Achieving both high bandwidth and high OSR is hard as circuit technology limits the achievable sample rate for DACs.

#### 2.2 Figures of merit

To fairly compare different designs, fair comparison measures that does not favour a single topology are needed. While there exist several generally accepted figures of merit (FoMs) for ADCs, as described in section 4.3, this is not the case for RF-DACs. One reason is that there is no fixed output interface for RF-DACs, as output power and load impedance are part of the specifications. Another reason is that RF-DACs can be used to generate modulated signals, making it highly beneficial to co-integrate large portions of a modulator into a single block, further complicating the comparison of different designs. In addition, they can be designed for different output power levels, operate

at different frequency bands and be optimized for different modulation formats, making a fair comparison even tougher.

There are several traditional DAC measures which in theory could be of interest also for RF-DACs, such as linearity and spurious free dynamic range (SNDR). However, the linearity is a static measure, not giving any insight about the performance for wideband signals. It might also be complex to accurately measure the steady-state linearity for a RF-DAC due to a potentially high carrier frequency. The narrow-band signals needed for SNDR measurements would also not mimic the actual wideband performance. Below, a few different FoMs commonly used for evaluating RF-DACs will be presented.

#### 2.2.1 Error vector magnitude

The error vector magnitude (EVM) is a measure of how accurate the transmitted constellation is compared to the intended one. EVM is typically measured as the root mean square (RMS) error normalized to either the average constellation power  $EVM_{rms}$ , or to the highest power for any constellation point  $EVM_{rms,peak}$ .

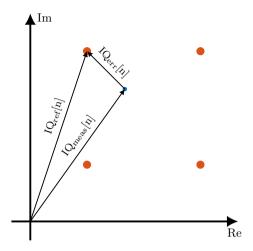

An illustration of the error vector for a single point is shown in figure 2.4. From this figure, the EVM for a single point can be calculated as in equation (2.9), where equation (2.8) shows the definition of the error vector. This equation can then be extended into the average metrics commonly used for performance comparison. Equation (2.10) shows the expression for  $EVM_{rms}$  while equation (2.11) shows the expression for the  $EVM_{rms,peak}$ . The metric normalized to the RMS power makes it possible to compare the performance for different modulation formats [20, Ch. 5] while the one normalized to the peak constellation point is commonly adopted in instruments [21,22].

$$IQ_{err} = IQ_{meas} - IQ_{ref}$$

(2.8)

$$EVM[n] = \frac{|IQ_{err}[n]|}{|IQ_{ref}[n]|}$$

(2.9)

$$EVM_{rms} = \frac{rms(|IQ_{err}|)}{rms(|IQ_{ref}|)}$$

(2.10)

$$EVM_{rms,peak} = \frac{rms(|IQ_{err}|)}{max(|IQ_{ref}|)}$$

(2.11)

Figure 2.4: Illustration of EVM calculation for a single point.

In a real communication system, the received constellation diagram will be affected by noise coming from three sources: the transmitter, the channel, and the receiver. This noise will introduce errors in the transmitted data stream. The BER is a measure of how many erroneous bits that are received in relation to the total number of received bits. The BER is also tightly connected to the error in the received constellation diagram. By connecting the BER to the EVM through the SNR, it becomes possible to study the relationship between BER and EVM in a Gaussian channel. For QAM, the bit error probability can be calculated using equation (2.12), by inserting equation (2.13), assuming Gaussian noise [20, Ch. 2]. In the following equations, M is the number of constellation points in the modulation format, BW is the bandwidth of the system, and BR is the bit rate. Q(x) is the Q-function, often used in error-probability expressions [20, Ch. 2].

$$P_b(M) = \frac{2P_{e\sqrt{M}}}{\log_2 M} \left(1 - \frac{1}{2}P_{e\sqrt{M}}\right)$$

(2.12)

$$P_{e\sqrt{M}} \cong \frac{2\left(\sqrt{M} - 1\right)}{\sqrt{M}} Q\left(\sqrt{3\frac{\log_2 M}{M - 1}} \frac{\text{BW}}{\text{BR}} \text{SNR}\right)$$

(2.13)

For a channel where bit errors are caused by additive white Gaussian noise [23], the SNR will correspond to the average signal power over the

average error. The relationship between  $EVM_{rms}$  and SNR is given by equation (2.14).

$$EVM_{rms} = \frac{1}{\sqrt{SNR}}$$

(2.14)

In order to relate the average power to the peak constellation point a scale factor is needed. The crest factor c, relates the magnitude of the maximum constellation point to the average constellation magnitude, while PAPR relates the corresponding power ratio. Equation (2.15) shows the expression commonly used to describe this modulation format dependent ratio [24–26]. Here, M is the number constellation points for a given modulation format. As EVM is inversely proportional to the signal power, EVM<sub>rms,peak</sub> will therefore be related to EVM<sub>rms</sub> as in equation (2.16).

$$c = \sqrt{\text{PAPR}} = \sqrt{3\frac{\sqrt{M} - 1}{\sqrt{M} + 1}} \tag{2.15}$$

$$EVM_{rms,peak} = \frac{1}{c}EVM_{rms}$$

(2.16)

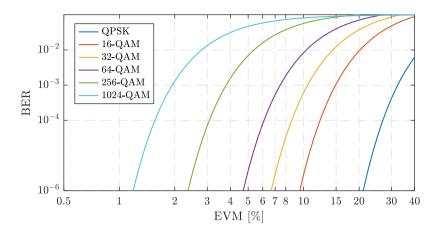

The relationship between EVM and BER is shown in figure 2.5 for several different modulation formats of different complexity. The EVM is normalized to the average constellation for these curves. In high-capacity communication systems, an input BER of 10<sup>-3</sup> is typically considered as the DSP typically includes error correcting capabilities, thereby further reducing the BER [23].

From the diagram in figure 2.5 we can observe several things. We can see that as the number of constellation points is quadrupled, the required EVM must be halved for a constant BER. It can also be observed that the slope is larger for a BER of  $1\times 10^{-6}$  than for a BER of  $1\times 10^{-3}$ , making the system more sensitive to noise when BER requirements are tougher.

Although EVM gives a good measure on the accuracy of the transmitted constellation, the measure still comes with its limitations when it comes to comparing different designs. As it does not account for the DAC resolution, it is important to keep this in mind when comparing figures. As the modulator resolution is connected to the complexity of the intended modulation format, the ratio between the number of required levels and the number of levels available must also be considered. In theory, a high resolution modulator should be able to provide

**Figure 2.5:** BER plotted versus EVM for different modulation formats with EVM normalized to average power.

a better EVM than a modulator with lower resolution given the same sample rate and modulation format. It also is important to account for the transmitted data rate as the non-linear behaviour of the modulator might be further stressed by wideband signals.

#### 2.2.2 Efficiency metrics

Efficiency measures are often of interest when comparing highly integrated components. For PAs, both drain efficiency (DE) and power added efficiency (PAE) are common measures used to compare the efficiency of the implementation.

$$DE = \frac{P_{RF,out}}{P_{DC}} \tag{2.17}$$

$$PAE = \frac{P_{RF,out} - P_{RF,in}}{P_{DC}}$$

(2.18)

While DE only accounts for the efficiency at the output the PA equation (2.17), PAE also accounts for the input power and the power consumed in potential pre-amplifier stages as in equation (2.18). This makes PAE a much more usable metric. However, for RF-DACs, all the power consumption will not be located in the analog path as some functionality needs to be implemented as digital circuits. It is not clear

if this consumption should be included in the PAE or not, making the measure hard to use.

Another complication is the vast span of topologies used for implementing RF-DACs. To some extent, the principles for achieving a high output power are the same both for RF-DACs and for PAs. Again, comparing with PAs, a large span of different PA topologies exist. When comparing PA implementations, one tries to keep the topology as similar as possible, as the topology might have significant impact on the efficiency. For RF-DACs on the other hand, the relatively low number of publications makes this kind of categorization impossible as other things not related to the output power also need to be considered, such as the data rate.

#### 2.2.3 Energy consumption per bit

The energy consumed per transmitted bit is a comparison metric used when comparing the performance both in entire communication systems and in individual subsystems [9]. This is a good method as it makes it possible to study effects on a system level even though focus might be on a significantly smaller block. There are however subsystems which are less suitable for this kind of comparison, such as RF-DACs, as the output power level is not compensated for. Subtracting the output power will not be sufficient as the power consumption is highly dependent on the intended output power. Other parts of the RF-DAC must also be designed for the intended output power, thus connecting the power consumption for the rest of the RF-DAC to the output power level.

#### 2.3 Topological alternatives

Transmitters can be highly customized depending on their intended operation. Two transmitter topologies, the direct conversion and the superheterodyne, have traditionally been adopted in communication systems [27, Ch. 14]. This however changed with the introduction of wideband RF-DAC-based transmitters [28–30]. Since their introduction in 2004, there has been an increased interest for RF-DAC-based transmitters, driven by increased demands of tighter system integration. Both Cartesian [9,10,31–37] and polar [38–42] transmitters has been demonstrated, operating over a large range of frequencies ranging from a few GHz [28–30,40–42] to 60 GHz and above [32–39].

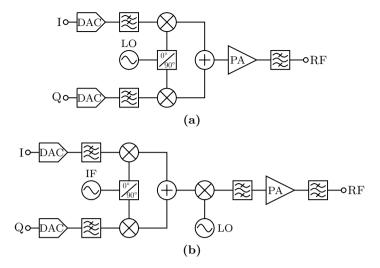

**Figure 2.6:** Illustrations of the direct converting transmitter (a) and the superheterodyne transmitter (b).

#### 2.3.1 The classical transmitter approach

The two transmitter topologies traditionally used are both based on similar principles, up-converting the BB data using mixers [27, Ch. 14]. Generic block diagrams for the direct-converting and the superheterodyne transmitter are shown in figures 2.6a and 2.6b respectively. The direct-converting transmitter is compact as it only requires a single up-conversion. However, as only a single up-conversion is used, potential local oscillator (LO) leakage will end up in the center of the transmitted band, making it impossible to filter out. The superheterodyne transmitter solves this problem by introducing an intermediate frequency (IF). Carefully selecting the IF and LO frequencies makes it possible to filter out any LO leakage as the IF provides an offset between the transmitted band and the LO. This however comes at the cost of additional hardware.

Although both topologies in principle are fairly simple, many different versions are presented in literature, addressing different weaknesses with these topologies. These will however not be studied here.

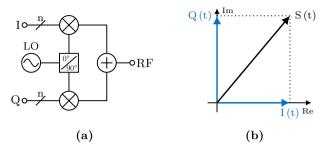

Figure 2.7: Illustration of the RF-DAC based Cartesian modulator (a) and the vector combining (b).

#### 2.3.2 Cartesian RF-DAC

The Cartesian RF-DAC based modulator is to a large extent based on the direct-converting transmitter topology presented above. However, there is one significant difference; rather than providing analog BB data to the mixer using DACs, digital control signals are used to control the operation of the mixer. To allow this control of the mixer, it is divided into several smaller cells that are individually controlled. Through this individual control, it becomes possible to combine the up-conversion with the digital-to-analog (D/A) conversion. The similarities between the two topologies can clearly be seen when comparing the RF-DAC-based topology in figure 2.7a with the direct-converting topology in figure 2.6a. In figure 2.7b the vector combining of the in-phase (I) and quadrature-phase (Q) signals is shown.

#### 2.3.3 Polar RF-DAC

The idea behind the polar RF-DAC-based topology is very similar to the Cartesian topology. However, rather than using two RF-DACs to realize the orthogonal signals in the Cartesian coordinate system, the polar topology operates based on a polar coordinate system, thus only requiring a single RF-DAC for the amplitude modulation [39]. The phase modulation is applied to the LO signal at an earlier stage. A block diagram for a generic RF-DAC-based polar transmitter is shown in figure 2.8a. The vector summation of the phase  $\varphi$  and amplitude A is shown in figure 2.8b.

Figure 2.8: Illustration of the RF-DAC based polar modulator (a) and the vector summation (b).

**Figure 2.9:** Illustration of the RF-DAC based outphasing modulator (a) and the vector summation of the outphasing signals (b).

#### 2.3.4 Outphasing transmitter

The principle behind outphasing differs a bit from the two approaches presented above. It focuses on keeping a constant amplitude level, eliminating the need for an amplitude modulator. Rather the phase modulation is used to generate the amplitude levels needed, making it possible to use highly efficient amplifiers rather than RF-DACs [43].

The modulation is applied using two parallel phase modulators, one having a positive phase offset and the other a negative one. Each modulator has a fixed magnitude of half the desired maximum output level. The amplitude modulation is achieved by adjusting the outphasing angle  $\theta$  and then combine the two channels. A block diagram for the outphasing transmitter is shown in figure 2.9a. The vector summation of the outphasing signals is shown in figure 2.9b.

#### 2.3.5 Topology comparison

The Cartesian topology has the advantage that it operates in the same coordinate system as the complex modulation formats commonly used. The square grid making up a M-QAM constellation, see figure 2.2, closely matches the grid formed by the Cartesian modulator. However, a weakness with the topology is when it is desired to adjust the phase of the transmitted signal, such as in beam-forming MIMO systems [44–46]. Rotating the constellation would result in a mismatch between the grid generated by the modulator and the constellation to be transmitted, reducing the modulation accuracy. However, as phase adjustments for beam movements are occurring at a less frequent rate than the transmitted data is updated, it becomes possible to use an external phase modulator located either before or after the Cartesian modulator.

The polar topology on the other hand with its circular grid, is more suitable for systems requiring phase rotation. However, when a static phase is needed, the polar topology becomes less suitable for squareshaped constellations as a large set of the available points will not be used. Fitting a square into a circle will always result in areas of the circle not being covered by the square. Another drawback with the polar topology is the complexity of implementing phase modulators. RF-DACs have been demonstrated to operate at high speed with moderate resolution [9, 39]. The same cannot be said about phase modulators. In some cases, Cartesian based modulators have been used as phase modulators [39,40], although this in not their primary function as they simultaneously provide both amplitude and phase modulation. Transmissionline-based phase modulators have been demonstrated [47–49], but these were intended for beam-forming applications and cannot provide the sample rate required for polar modulation. The phase modulation waveform also needs to be synced to the amplitude signal with sub-sample precision for good performance [39], which further complicates the implementation of a high-bandwidth polar modulator.

The outphasing modulator is very similar to using two parallel polar transmitters, although no amplitude modulation is needed. As no amplitude modulation is needed, highly efficient amplifiers could be used, thereby in principle result in a high efficiency [43, 50]. However, high-speed phase modulation is a problem that the outphasing topology shares with the polar topology. Another problem with the phase modulation is the non-linear signal processing [51], resulting in a large bandwidth expansion, thus requiring a large OSR which is problematic

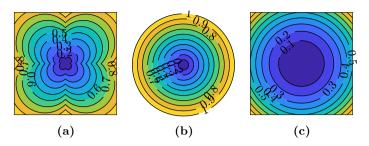

Figure 2.10: Contour plots of the normalized DE for the different modulator topologies, comparing the code dependency for Cartesian (a), polar (b), and outphasing (c).

for wideband modulators. A rule of thumb is that polar transmitters require roughly an oversampling of ten times the signal bandwidth to account for the bandwidth expansion [52]. However, polar transmitter realizations requiring a lower OSR have been demonstrated [39].

#### 2.4 Code dependent efficiency

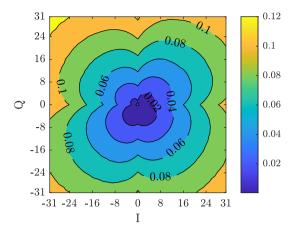

For RF-DAC-based modulators, not only the peak efficiency is of interest; also the code-dependent efficiency is important, especially for modulated signals with a large PAPR. On average, the output power for modulated signals is significantly lower than the peak output power, thus resulting in a significant efficiency reduction [10]. Figure 2.10 shows contour plots of the code dependent DE for, Cartesian, polar and outphasing modulators normalized to the peak DE achieved by each topology.

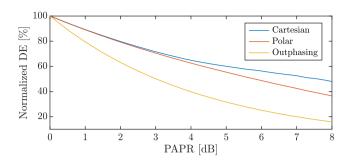

From figure 2.10 it might be hard to see how the PAPR caused by the modulation will affect the efficiency. The relative modulated DE is plotted versus PAPR in figure 2.11 for the three transmitter topologies. It can here be seen how the outphasing transmitter achieves the lowest efficiency while the Cartesian and polar are fairly similar.

#### 2.5 Non-overlapping LO

In most analog systems, the duty cycle is not considered as pure sine wave signals are more desired than pulse-shaped signals. For pulse-

**Figure 2.11:** Modulation dependent DE as a function of PAPR, plotted for Cartesian, polar and outphasing transmitters. The DE is normalized to the peak for each individual transmitter topology.

shaped signals, the duty cycle is defined as the ratio between the duration of the pulse and the signal period at half the pulse magnitude. As pulse-based signals have a high harmonic content, they might cause undesired interference. Mixers are however the exception, where strong LO signals are desired for more idealized operation [11, Ch. 13]. Here it is typically not a problem to use 50 % duty cycle signals, making it possible to use clipped sine wave signals to drive the LO port on the mixer. Since RF-DACs can be seen as a group of parallel mixers, one might think that 50 % duty cycle would be fine for them as well. This is however only true for polar transmitters, which only use a single RF-DAC, thus not having any summation on the output. For other RF-DAC-based topologies, the outputs from several parallel RF-DACs are summed to form the desired signal.

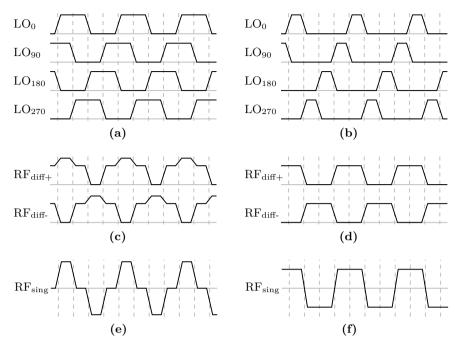

The different waveforms shown in figure 2.12 are calculated based on the four LO signals, to generate the top right point in figure 2.4. The two differential signal are defined as in equation (2.19) where  $RF_{diff+}$  is generated by LO<sub>0</sub> and LO<sub>20</sub>. The same also goes for  $RF_{diff-}$ , which is generated by LO<sub>180</sub> and LO<sub>270</sub>. The resulting single-ended signal is then given by equation (2.20). The 50% and 25% duty cycle cases will be presented in more detail below.

$$RF_{diff+} = LO_0 + LO_{90} \tag{2.19}$$

$$RF_{sing} = RF_{diff+} - RF_{diff-}$$

(2.20)

The Cartesian topology relies on the summation of the orthogonal

**Figure 2.12:** Quadrature LO signals with 50% duty cycle (a) and 25% duty cycle (b). LO<sub>0</sub> and LO<sub>90</sub> are then combined to form RF<sub>diff+</sub> (c) and (d). The resulting RF signal is shown for the 50% and 25% cases in (e) and (f) respectively.

signals generated by the parallel RF-DACs. However, complete orthogonality can only be achieved if there is no interaction between the RF-DACs [33]. Interaction-free operation will however not be fulfilled for 50 % duty cycle LO signals [33]. As can be seen in figure 2.12a, the four LO signals needed in a fully differential quadrature modulator overlap with each other, thus causing intermodulation [33]. The extreme cases when both RF-DACs are fully on become most troublesome as the largest interference occurs here, although the problem is present for all output combinations.

In figure 2.12c,  $RF_{diff+}$  is generated from  $LO_0$  and  $LO_{90}$  to form the top right most point in figure 2.4. Combining the 50% duty cycle LO signals to form the differential components results in a large duty cycle expansion as illustrated in figure 2.12c. To mimic the effects of saturation in the transistors when both LO signals are combined, a smaller

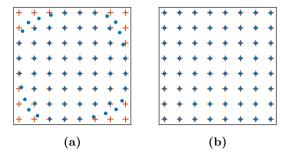

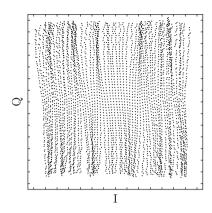

**Figure 2.13:** Effects on output constellation when directly combining the RF signals at the RF-DAC outputs, using 50 % duty cycle LO signals (a) and 25 % duty cycle (b) LOs signals. The reference grid is shown in orange.

than ideal increase is shown. Combining the differential signals in figure 2.12c into a single-ended signal, shown in figure 2.12e, results in large portions of the differential signals cancel each other with a reduced efficiency as the result. The resulting waveform, with a small duty cycle, will have a high harmonic content that needs to be filtered out.

With the  $25\,\%$  duty cycle LO signals shown in figure 2.12b, it can be seen that the LO signals do not overlap, thereby ideally combine into the differential signals shown in figure 2.12d. This results in fully differential signals, not overlapping each other at any time, bringing a nice  $50\,\%$  duty cycle RF signal when combined into the single-ended signal shown in figure 2.12f.

Constellation diagrams for modulated signals using 50% and 25% duty cycle LO signal are shown in figure 2.13. With 50% duty cycle LO signals, a significant compression can be seen for the corner points, significantly reducing the EVM. This effect cannot be seen for 25% duty cycle LO signals as they are non-overlapping.

The principle of  $25\,\%$  duty cycle LO signals has been demonstrated both in mixer applications [53–55] and in RF-DAC based transmitters [33], although at low frequency. Wideband LO generators for  $25\,\%$  duty cycle operating at DC–62 GHz [56] have also been demonstrated, albeit in SiGe process.

The RF-DAC efficiency is tightly connected to the duty cycle, although this might not be fully intuitive. Consider the differential outputs for the RF-DAC in the 50 % duty cycle case shown in figure 2.12c.

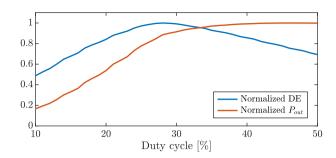

**Figure 2.14:** Normalized DE and output power as a function of the duty cycle.

Here it can be seen that the RF-DACs are active  $75\,\%$  of the time, resulting in a conduction angle of  $75\,\%$ , which translates into an amplifier operating in class-AB. Ideally, it would be desired to have class-B operation, which corresponds to a conduction angle of  $50\,\%$ . As  $25\,\%$  duty cycle LO signals are fully isolated, a conduction angle of  $50\,\%$  is achieved, as can be seen in figure 2.12d.

In figure 2.14, the normalized DE and output power is plotted as a function of duty cycle. Depending on for which duty cycle a saturated output power is desired, the peak seen for the DE will move. It will however not be possible to get a maximum efficiency at a duty cycle of 50%.

# Chapter 3

# RF IQ modulator design and evaluation

RF IQ modulators have been presented to operate at a large set of frequency bands, ranging from a few GHz up to 60 GHz and beyond [9, 10, 23, 31–34, 36, 37, 39, 57, 58]. In [9], a RF-DAC based IQ modulator is described, having a resolution of 2×6 bit, operating at 20–32 GHz with a sample rate of 5 GS/s, although simulations indicate a sample rate approaching 16 GS/s. A 2×10 bit RF-DAC based IQ modulator operating at 20–32 GHz with a sample rate of 2 GS/s is demonstrated in [10]. A polar modulator having a 4 bit resolution, operating at 60 GHz is demonstrated in [39]. In this design, the amplitude modulator is clocked at 10 GHz. The phase modulation is implemented using a Cartesian upconverting mixer where analog BB data is fed onto the chip, generating the phase modulated LO signal. A 2×9 bit RF-DAC based IQ modulator is demonstrated with an operating range of 85–95 GHz and a clock rate of 15 GHz [34]. This IQ modulator has however only been verified using OOK, by toggling the most significant bit (MSB). A RF-DAC based IQ modulator with a  $2\times2$  bit resolution, operating at 94 GHz with a sample rate of 20 GHz is demonstrated in [23].

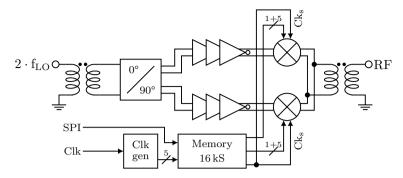

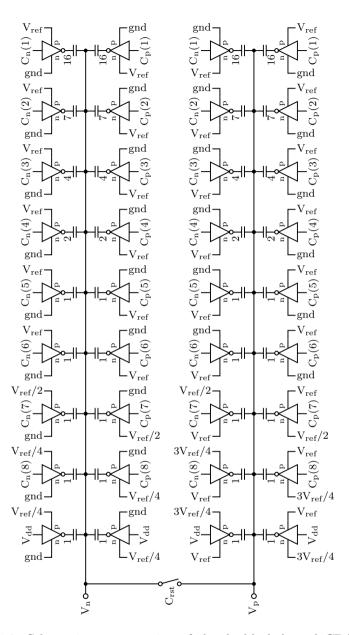

I will below describe the realization of a 17–24 GHz, 2×6 bit RF IQ modulator, operating at 10 GS/s. A block diagram of the modulator is shown in figure 3.1. A LO at two times the desired carrier frequency is fed into the divider which generates the quadrature LO signals. These are then fed through inverter buffers to boost the drive-strength. Two RF-DACs are used to generate the I- and Q-components before being combined at the output. An on-chip memory is used to provide the data

**Figure 3.1:** Block diagram showing the implementation of the RF IQ modulator.

streams that are fed into the RF-DACs.

# 3.1 Proof of concept

Before implementing the entire RF IQ modulator, a simpler RF-DAC was implemented as a proof of concept, testing the principle. This RF-DAC used a 5 bit resolution and only supported magnitude modulation. In this proof of concept, data was externally fed onto the chip together with a sample clock using an field-programmable gate array (FPGA), providing a quick evaluation of the principles.

This evaluation highlighted the complexity of having multiple differential high-speed signals connected to the chip, not only significantly impacting the layout of the chip but also the testability. Providing six parallel data streams while simultaneously probing the RF signals proved too complex, highlighting the limitations with this test-setup.

## 3.2 Unit cell

The unit cell is the lowest level building block in RF-DACs. It can be used to form thermometer based implementations where each cell has its own control signal. Also, it can be used to form hierarchical blocks, where several unit cells are grouped together, for example into bit-cells. This flexibility makes the unit cell usable in many types of implementations. The basic principle behind a mixing unit cell is a set

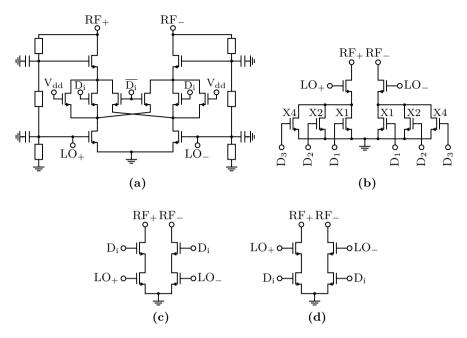

Figure 3.2: Examples of different unit cell arrangements seen in literature. In (a) an arrangement for constant bias current is shown. The shared LO principle is shown in (b). The individually paired configurations with the data switch on top (c) and below (d) the LO-switch.

of stacked transistors, one pair for LO signals and another pair for data signals.

Implementations described in literature sometimes directly go for binary weighted structures and do not rely on unit cells [9]. There are many different considerations behind the realization of a RF-DAC; the topology is one of them. The important point is however that all implementations require some sort of scaled structure for realizing the output levels (with thermometer based implementation being the exception). Many different topologies for arranging the LO- and data-switches are presented in literature; three alternatives will be presented below.

In stacked topologies where cascodes are used to increase the output power, a cancelling unit cell topology is commonly used. In this topology, the data-switches are placed on top of the LO-switches, and three parallel data-switches are used in each differential leg. Two of these data-switches are connected to one of the LO signals and the third one is connected to the LO signal having opposite polarity [9,37], as shown in figure 3.2a. One transistor controls the bias level, while the others control the output level through RF summation or cancellation. As two transistors constantly are active, a constant bias current is achieved for all digital control signals. This constant bias condition is important in cascodes as the supply voltage must be evenly distributed over all the stacked transistors making up the cascode.

Another approach, that shares some principles with the stacked topology, uses multiple parallel data switches, all sharing a common LO-switch. The data-switches are placed in the bottom, controlling the bias current through the LO switch [23,31], as shown in figure 3.2b. While only a single set of LO-switches are needed, the topology suffers from a large parasitic capacitance in the node connecting the data-switches to the LO-switches.

The third principle builds on combining a data-switch and a LO-switch, either placing the data-switch on the top as in figure 3.2c [10,36] or by placing the data-switch in the bottom as in figure 3.2d [39]. These arrangements brings a reduced parasitic capacitance between the LO-and data-switch compared to the case when the LO-switch was shared. The topologies presented in figures 3.2b to 3.2d all have in common that the total bias current for the RF-DAC is dependent on the number of active unit cells, thus improving the efficiency when bot all unit cells are active.

Although all the topologies presented above are very different, they all only realize the magnitude part of the modulation. The sign, that is the ability to turn the phase 180°, is typically implemented in between the quadrature LO generation and the RF-DACs [9,10,36,37,39]. This sign generation is based on swapping the polarity of the LO signals connected to the RF-DACs This method however requires the sign generation to be synced to the amplitude generation. An alternative approach for the sign generation is to implement it into the unit cells. This can be done by duplicating the magnitude generation while swapping the LO connections, thus doubling the footprint of the unit cell.

The LO leakage cancellation brought by arrangement of the LOand data-switches greatly impacts the overall RF-DAC performance. Since none of the topologies presented above have sign generation, they all suffer form potentially large LO leakage. Although the cancellation approach builds on suppressing the signal when no output is desired, leakage will still occur due to transistor mismatch. For the case when

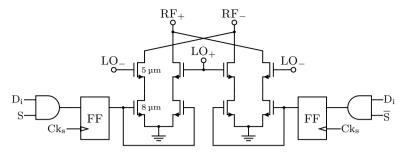

**Figure 3.3:** A schematic of the unit cell implementation showing both RF path with LO and data switches as well as the FFs that are used to align the data.

the data-switch is placed on top of the LO-switch, cancellation is brought by the blocking provided by the deactivated data-switch [10,36]. Further LO leakage cancellation is claimed to be achieved by also gating the LO signal reaching the LO-switch [10]. This would however add additional delays for activation of the cell, making it less suitable for wideband operation.

The unit-cell topology presented in figure 3.3 seeks to mitigate these drawbacks. The unit cell uses top placed LO transistors and slightly larger data switches placed below. The size of the LO-switches are set by the desired output power, while slightly larger data-switches are used to improve the efficiency. For the RF-DAC to be able to handle wideband signals and high OSR, it is important that the data-switches can operate at high speed. To reduce effects of jitter in the data switching, flip-flops (FFs) have been placed in the unit cells in order to align all the data switching events to a single signal, the sample clock. The sign generation has also been moved into the unit cell, using two parallel mixers with the LO signals swapped, as seen in figure 3.3. Placing the sign generation within the unit cell also brings inherent LO leakage cancellation at unit-cell level.

The largest contribution to LO leakage is the capacitive coupling between the gate and drain terminals of the LO-switches. Through the introduction of an additional mixer, a leakage-path with opposite polarity is introduced, thus significantly reducing the LO leakage.

The LO leakage has been simulated for the two topologies presented in figures 3.2c and 3.2d, for the case when additional disabling of the LO switches is used [10], and for the unit cell topology presented in

figure 3.3. Schematic level simulations has been performed on the four topologies mentioned above to estimate their LO leakage, using the sizes for the LO- and data-switch in figure 3.3. For an implemented circuit, additional leakage caused by the routing is expected, further degrading the LO leakage performance. As the topology in figure 3.2d suffers from the highest LO leakage, this topology will be used as the reference. The topology presented in figure 3.2c brings a LO leakage reduction of 25 dB. Deactivating the LO signal when the cell is not used brings an additional 20 dB LO leakage reduction compared to the topology in figure 3.2c which this principle is used for. The unit cell presented in figure 3.3 shows excellent LO leakage cancellation, showing a 90 dB leakage reduction compared to figure 3.2d. However, as this principle builds on cancellation of the leakage paths, mismatch is the transistor sizes will significantly increase the leakage. In the case of a  $\pm 1\%$  transistor size mismatch, the LO leakage performance closely matches the performance achieved by disabling the LO signal driving the switch when it is not in use.

In principle, it is possible to use a single data switch shared by the two LO switches in the mixer, as long as the total size is maintained. However, with the introduction of the sign generation, one signal needs to be crossed in the unit cell layout, as can be understood from figure 3.3, further increasing the complexity. The dual data switches give more freedom for the implementation, allowing the LO signals to be crossed rather than the RF signals.

In modern CMOS processes, the metal routing in the bottom metal layers is very narrow and thin, severely limiting ability to transfer current, especially direct current (DC). With the total power consumed by RF-DACs mainly being consumed in the unit cells, a good ground is required to handle this total current. This is currently the limiting factor for the unit cell size. The intense routing of LO and RF signals above the mixers limits the available area for ground routing.

# 3.3 RF IQ modulator core topology

The RF IQ modulator core arranges the unit cells in a hierarchy to form the different output levels. Two different hierarchies are often used: the binary topology, where unit cells are combined into binary weighted groups, or the thermometer topology, where the unit cells are individually activated depending on the input code. These topologies are most

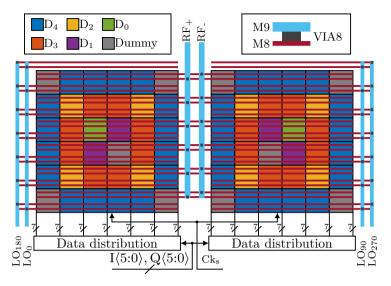

**Figure 3.4:** Illustration of the unit cell placement for the binary scheme together with the routing of the LO and RF signals. The data distribution blocks contains the binary to thermometer encoder.

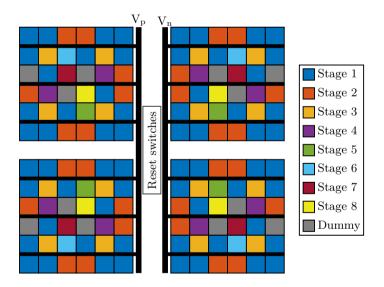

commonly used for low and medium resolution RF-DACs. At higher resolutions, a combination of these topologies can often be found, where the MSBs are thermometer encoded and the least significant bits (LSBs) are binary encoded. The RF IQ modulator presented here features the possibility to choose between binary and thermometer encoding.

For the binary encoding scheme, the unit cells are distributed in a common-centroid fashion, as can be seen in figure 3.4. For the thermometer-encoded mode, the cells are activated in a chain starting at the corner where the LO signals are fed in, moving up and down columnwise until reaching the corner where the RF signal is outputted. The Q-block is a mirrored replica of the I-block to further improve matching.

The FFs located in the unit cells, see figure 3.3, reduce skew caused by the data routing by isolating the data switches from the data routing. Instead, the control signals for the data switches are derived by the sample clock. This makes the clock signal Ck<sub>s</sub> the only signal that needs to be carefully aligned at the input of all unit cells. The clock signal is routed to the center of the RF-DAC before being distributed through a H-tree in order to reduce the switching skew at the unit cells. Dummy loads are placed at the locations in the H-tree where no cells

are connected, further balancing the clock distribution.

The unit cells are distributed over a fairly large area, which makes it important to consider delays in the routing of the LO and RF signals for optimum combining of the unit cell outputs. The routing is implemented as mirrored F-shaped structures in the top metal layers, as shown in figure 3.4. This routing is designed to give equal delay from the LO input to the RF output through any unit cell.

In addition to the LO leakage, phase inversion is something that can be done either inside the unit cell or before it. Generating the sign before the RF-DAC reduces the complexity of the unit cell it self. However, for good performance using wideband signals, the sign generation needs to be precisely synced to the amplitude switching in the unit cells. The exact propagation delay from the phase generation to the unit cell will not be a multiple of the clock period, which makes this alignment complex. An alternative is to move the sign generation into the unit cell, eliminating the need for critical alignment of the sign and data. The sign generation is implemented by duplicating parts of the unit cell or the entire structure, at an obvious cost in cell area.

# 3.4 LO generation

Circuits for delivering quadrature LO signals can be divided into three categories: 90° hybrids [10,23,31,32], polyphase filters (PPFs) [59], and divider-based topologies [9]. The hybrid-based quadrature LO generators are often implemented using transmission-lines, although a lumped realization is an option. A quarter wavelength transmission-line will realize a 90° phase shift. With increased frequency, the absolute length decreases, making the hybrid approach most suitable for high frequency implementations. In air, the wavelength for a 30 GHz signal is 1 cm and on chip, it is roughly a quarter of this, making a  $\lambda/4$  transmission-line roughly 700 µm long. Although there are methods for reducing the size of 90° hybrids [60], their size will still be substantial below 30 GHz. Another limitation with 90° hybrids is that they can only generate 50 % duty cycle LO signals.

High frequency PPFs are typically implemented as passive structures, using resistors and capacitors. This topology features significant loss, requiring amplifiers to boost the signal level. Another limitation with the PPF topology is that it can, just like the  $90^{\circ}$  hybrid, only generate 50% duty cycle LO signals.

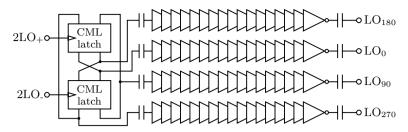

**Figure 3.5:** Schematic of the quadrature LO generation including the divider and DC-block capacitors.

The divider-based topology can in theory operate over the largest relative frequency band. It builds on using two cross-coupled latches, clocked with opposite sign. The two latches will output signals at half the clock frequency having 90° phase difference. In principle, divider-based quadrature LO generators have no lower frequency limit for their operation. However, due to the double input frequency required, there is an upper frequency limit for which the topology will work. Divider based quadrature LO generators have been demonstrated to generate upto 32 GHz LO signals in CMOS [9] and 62 GHz in SiGe [56]. With the limited driving capability of the divider, significant buffering is needed. However, thanks to the switching behaviour of the divider it is possible to use inverter-based buffers, thus making it suitable for CMOS integration.

The divider-based topology allows for a tunable duty cycle as the bias level can be adjusted at the buffer input. This is good as transistors often have a threshold voltage smaller than half the supply voltage, effectively increasing the duty cycle. The  $50\,\%$  duty cycle signals generated by the hybrid and PPF can also be used to generate non-overlapping LO signals using AND-gates [56], however, this results in a fixed duty cycle.

A schematic of the implemented LO generator is shown in figure 3.5. Due to its potential for high operational bandwidth and ability to provide non-overlapping LO signals, the divider based quadrature LO generation was chosen. Two cross-coupled dividers are used to generate the non-overlapping LO signals. These signals are then fed through four parallel 17 inverter buffers to increase the drive strength. The final two inverters in the buffer chain have the same size in order to sharpen the output transitions.

## 3.5 Testability

The testing and evaluating of a design is just as important as the design it-self. Already when designing the circuit, it is important to make sure that it can be evaluated in a good way. The test infrastructure must be flexible in order to support several different test cases. The data streams used to control the RF-DACs can be generated using several different sources, each featuring its own set of challenges. The data streams can be externally provided to the chip, using either a FPGA or a waveform generator. An alternative is to use generators implemented on the chip, either pseudorandom binary sequence (PRBS) generators or memories.

Most RF-DACs presented in literature use externally fed data for controlling the functionality [10, 31, 34–37, 39]. This method simplifies the on-chip design, as the data stream can be directly fed to the RF-DAC. By serializing the data stream, fewer parallel interfaces are needed. This is at the cost of demultiplexers needed to parallelize the data. The problem here is the complexity of providing and aligning a large number of high-speed control signals without electrically and practically affecting the RF measurements. There are cases where limitations in the external test equipment have limited the possibilities to fully test the chip [34].

Externally-fed data streams can either be provided by an arbitrary waveform generator (AWG) or a pulse pattern generator (PPG), however, these typically come with a limited number of ports, limiting the number of parallel channels that can be used. An alternative here would be to use an FPGA, as the number of parallel channels here can be increased. It will however be more complex to fine-tune the delays on a FPGA and a significant design effort is needed for the implementing the test system on the FPGA.

An alternative to externally feeding the data onto the chip is to use an on-chip memory that stores a record of data points [9,33]. This record is then used to control the RF-DACs during the measurements, giving almost the same flexibility as the external option. There are however two limitations with the on-chip memory solution; the record length is limited by the amount of memory that can fit onto the chip, and the transmitter cannot be used in a real link, as the record length would be too short. While the on-chip solution brings a simpler measurement set-up, it comes at the cost of a larger design effort for the chip as the memory also needs to be integrated together with the rest of the design. An important factor with the memory is that it should not limit

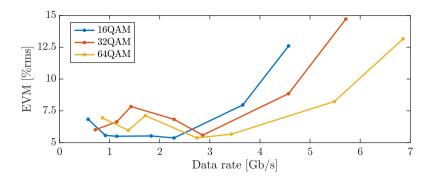

the testability of the circuit, either in terms of data rate or in terms of record length. A too-short memory will significantly limit the testability of the chip [9]. It should be noticed that when an oversampled pulse-shaping filter is used for spectral shaping, the number of transmitted symbols becomes the record length divided by the OSR. To achieve a good statistics for the EVM calculation, the record length will depend on the modulation format used. High complexity QAM formats have a larger number of unique symbols resulting in the need of a longer record and thereby a larger memory.

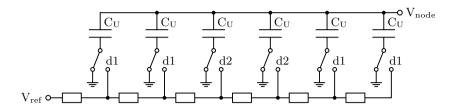

The method chosen for providing the digital data to the RF-DACs is an on-chip static random-access memory (SRAM) memory. With the 2×6 bit configuration, a total of 12 bits will be needed for each symbol, resulting in a digital bandwidth of 120 Gb/s between the memory and the RF-DACs at a sample rate of 10 GS/s. A 16 kS memory has been chosen, as it provides a good balance between footprint and record length. It consists of two blocks, a memory array and a serializer. The memory array is configured as 1024 words each containing 16 samples. These 16 samples are then serialized through a pipelined multiplexer tree, allowing the memory array to operate at 1/16 of the output clock rate. Programming is performed through a simple serial interface implemented in the memory block. The block has been designed in VHDL, using a SRAM memory array generated by a memory compiler. The design has then been synthesized and placed-and-routed with a target output clock rate of 10 GHz, using a standard digital design flow, providing a standard-cell based implementation of the memory block.

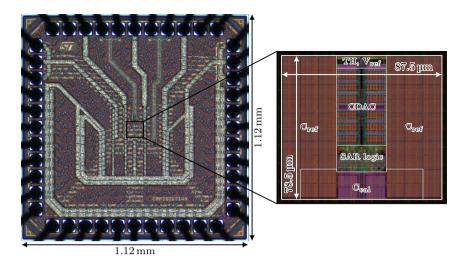

# 3.6 Manufactured chip

In order to measure the implemented RF IQ modulator it needs to be accessed externally. During the design, all signals that needs to be accessed externally must be connected to a pad. Although the RF-DAC is a differential circuit, measuring differential signals is complex; thus a circuit element, a so called balun, is needed for converting the input signal from single-ended to differential. On the output a balun will also be needed for converting the differential signal into a single-ended one.

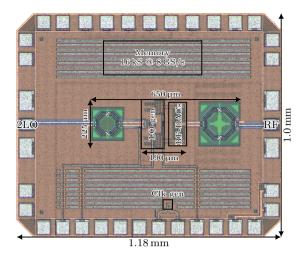

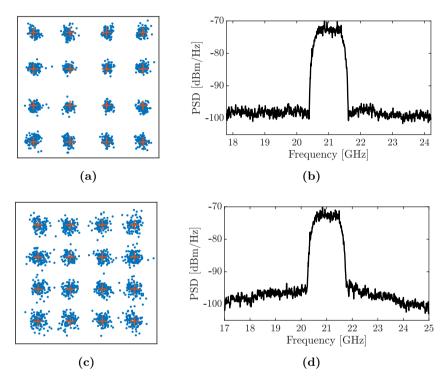

The RF IQ modulator has be fabricated in Global foundries 22 nm FDSOI CMOS process. The entire design measures 1 mm by  $1.18\,\rm mm$ . The modulator core including baluns occupy  $225\,\mu\rm m$  by  $650\,\mu\rm m$  out of which the core itself occupy  $225\,\mu\rm m$  by  $190\,\mu\rm m$ . A chip photo is shown

**Figure 3.6:** Chip photo highlighting the placement of the different building blocks and some key dimensions.

in figure 3.6, highlighting all the essential blocks in the IQ modulator.

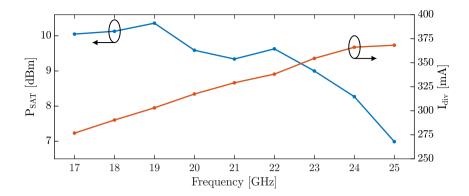

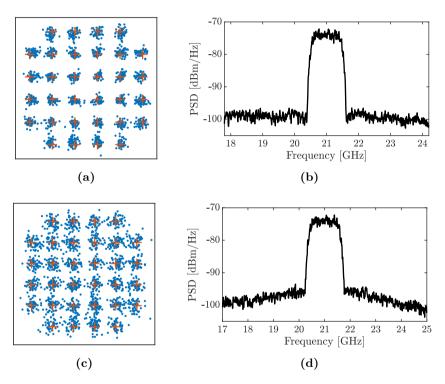

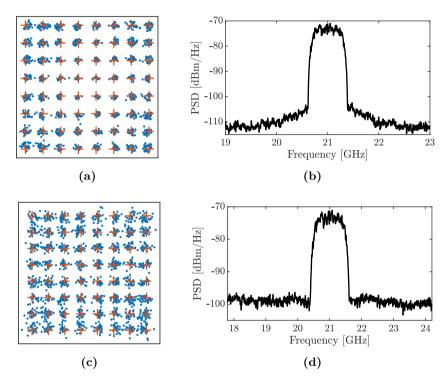

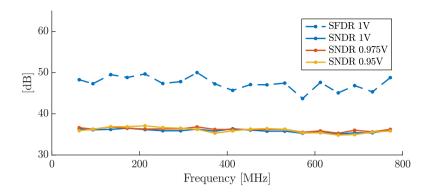

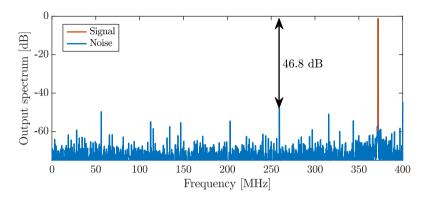

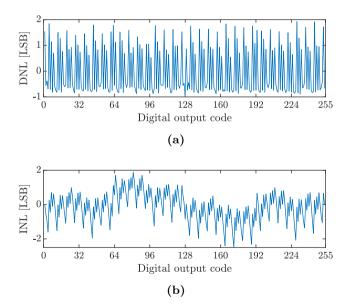

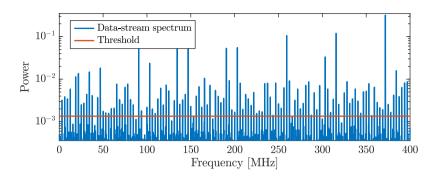

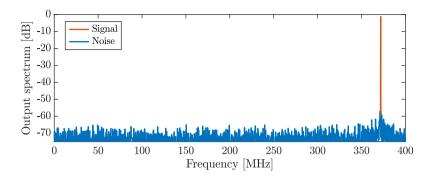

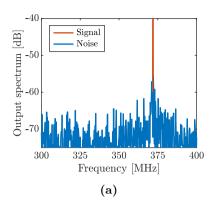

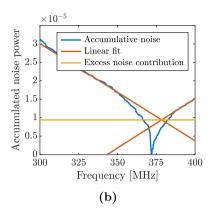

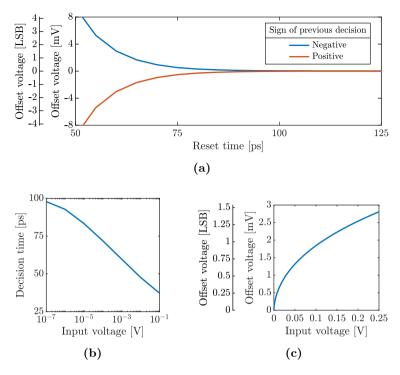

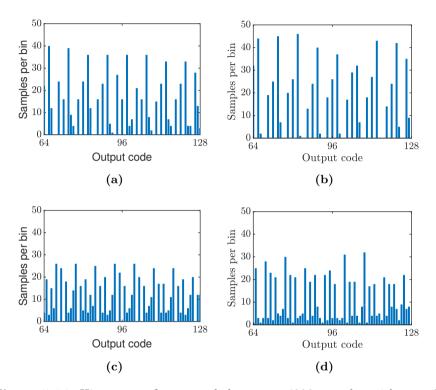

### 3.7 Measurements