# Model-Architecture Co-design of Deep Neural Networks for Embedded Systems

# Partha Prasun Maji

Department of Computer Science and Technology University of Cambridge

This dissertation is submitted for the degree of Doctor of Philosophy

Clare Hall

June 2020

# Declaration

This dissertation is the result of my own work and includes nothing which is the outcome of work done in collaboration except as declared in the Preface and specified in the text. It is not substantially the same as any that I have submitted, or am concurrently submitting, for a degree or diploma or other qualification at the University of Cambridge or any other University or similar institution except as declared in the Preface and specified in the text. I further state that no substantial part of my dissertation has already been submitted, or is being concurrently submitted, for any such degree, diploma or other qualification at the University of Cambridge or any other University or similar institution except as declared in the reflect and specified in the Preface and specified in the text. I further state that no substantial part of my dissertation has already been submitted, or is being concurrently submitted, for any such degree, diploma or other qualification at the University of Cambridge or any other University or similar institution except as declared in the Preface and specified in the text. This dissertation does not exceed the prescribed limit of 60 000 words.

Partha Prasun Maji June 2020

### Abstract

In deep learning, a convolutional neural network (ConvNet or CNN) is a powerful tool for building interesting embedded applications that use data to make predictions. An application running on an embedded system typically has limited access to memory resources, processing power, and storage. Implementing deep convolutional neural network based inference on resource constrained devices can be very challenging, as these environments cannot usually make use of the massive compute power and storage that are present in cloud server environments. Furthermore, the constantly evolving nature of modern deep network architecture aggravates the problem by making it necessary to balance flexibility against specialisation to avoid the inability to adapt. However, much of the baseline architecture of a deep convolutional neural network stayed the same. With careful optimisation of the most commonly and widely occurring layer architectures, it is typically possible to accelerate these emerging workloads for resource-constrained embedded systems.

This thesis makes four contributions. I first developed a lossy three-stage low-rank approximation scheme that can reduce the computational complexity of a pre-trained model by  $3-5\times$  and up to  $8-9\times$  for individual convolutional layers. This scheme requires restructuring of the convolutional layers and generally suits the scenario where both the training data and trained model are available.

In many scenarios, the training data is not available for fine-tuning any loss in prediction accuracy if structural changes are made to a model as a post-processing step. Besides the lack of availability of training data, there are other situations where the architecture of a model cannot be changed after training. My second contribution handles this scenario by using a low-level optimisation scheme that requires no changes to the model architecture, unlike the low-rank approximation scheme. This novel scheme uses a modified version of the Cook-Toom algorithm to reduce the computational intensity of commonly occurring dense and spatial convolutional layers and speedup inference time by  $2-4\times$ .

My third contribution is an efficient implementation of the Cook-Toom class of algorithms on ubiquitous Arm's low-power Cortex processor. Unlike the direct convolution, computing convolutions using the modified Cook-Toom algorithm requires a different data processing pipeline as it involves pre- and post-transformations of the intermediate activations. I introduced a multi-channel multi-region (MCMR) scheme to enable an efficient implementation of the fast Cook-Toom algorithm. I demonstrate that by effectively using SIMD instructions and the MCMR scheme an average  $2-3\times$  and a peak  $4\times$  per layer speedup is easily achievable.

My final contribution is the Cook-Toom accelerator, a custom hardware architecture for modern convolutional neural network. This accelerator architecture is designed from the ground up to address some of the limitations of a resource constrained SIMD processor. I also illustrate how new emerging layer types can be mapped efficiently to the same flexible architecture without any modification.

## Acknowledgements

I'd like to start by thanking Robert Mullins, who has been an incredibly encouraging and active supervisor throughout this entire experience. His guidance through ideas of experiments and discussions has been crucial. I'd also like to thank my secondary advisor Simon Moore, for his pragmatic suggestions, and Sean Holden from the AI research group, for helping me through the process of finding the right research question. I'd like to thank a few other members of the Computer Laboratory, especially, Alex Chadwick, Yousun Ko and Daniel Bates for always being there to brainstorm novel ideas. I'd like to thank the Engineering and Physical Sciences Research Council (EPSRC) for funding my research and the opportunity they gave me to travel to conferences around Europe.

A lot of interesting research questions and ideas I learned during my short stint in Arm Ltd., for which I am incredibly grateful. Rune Holm has played an absolutely invaluable role as a mentor while I was in Arm. I'd also like to thank Andrew Mundy, for collaborating with me on the Arm implementation work, Ganesh Dasika, David Mansell, and Matthew Mattina for reviewing our research and providing guidance.

This thesis is indebted to Roshin, my partner, who I met at the University of Edinburgh. Thank you for being there for me during difficult times and providing all the encouragement. Thanks also go out to your family for having welcomed me into their fold. A ton of thanks go out to my family, particularly my father, mother and brother for having believed in me and for putting up with my insistence on exploring the unknown instead of settling down. Without your groundwork much early in my academic life, this PhD simply would not have been possible.

Finally, I'd like to thank all of my ex-teachers, family and friends for being there throughout the past few years of the PhD, and before.

# **Table of contents**

| Li | st of fi | igures  | Xi                                                     | iii |

|----|----------|---------|--------------------------------------------------------|-----|

| Li | st of t  | ables   | xv                                                     | ii  |

| 1  | Intro    | duction | n                                                      | 1   |

|    | 1.1      | Motiva  | ution                                                  | 1   |

|    | 1.2      | Resear  | ch questions                                           | 2   |

|    | 1.3      | Hypotł  | nesis                                                  | 3   |

|    | 1.4      | Contril | butions                                                | 3   |

|    | 1.5      | Outline | 2                                                      | 4   |

|    | 1.6      | Publica | ations                                                 | 5   |

| 2  | Back     | ground  | l and related work                                     | 7   |

|    | 2.1      | Deep c  | convolutional neural network architecture              | 7   |

|    | 2.2      | Challer | nges of deploying ConvNets on embedded systems         | 9   |

|    | 2.3      | Arithm  | netic intensity and roof-line model                    | 11  |

|    | 2.4      | Types   | of convolutional layers                                | 2   |

|    |          | 2.4.1   | Spatial convolution                                    | 2   |

|    |          | 2.4.2   | 1 x 1 convolution                                      | 2   |

|    |          | 2.4.3   | Grouped convolution                                    | 4   |

|    |          | 2.4.4   | Depth-wise separable convolution                       | 4   |

|    | 2.5      | Charac  | teristics of convolutional layers                      | 4   |

|    | 2.6      | Data re | euse patterns                                          | 5   |

|    |          | 2.6.1   | Input stationary (IS)                                  | 17  |

|    |          | 2.6.2   | Output stationary (OS):                                | 17  |

|    |          | 2.6.3   | Weight stationary (WS):                                | 9   |

|    |          | 2.6.4   | Row stationary (RS):                                   | 20  |

|    |          | 2.6.5   | On-chip interconnect for varying reuse and flexibility | 20  |

|   | 2.7 | A surv    | vey of prior research on optimising ConvNets                        | 21 |  |  |

|---|-----|-----------|---------------------------------------------------------------------|----|--|--|

|   |     | 2.7.1     | Pruning, sparse Networks and regularisation                         | 22 |  |  |

|   |     | 2.7.2     | Model simplification and separable layers                           | 22 |  |  |

|   |     | 2.7.3     | Quantisation, low precision arithmetic and BinaryNet                | 23 |  |  |

|   |     | 2.7.4     | Data compression, hashed-net, weight sharing                        | 24 |  |  |

|   |     | 2.7.5     | Fast arithmetic, logarithmic representation, and FFT                | 25 |  |  |

|   |     | 2.7.6     | Architecture learning, hyper-parameter tuning and network architec- |    |  |  |

|   |     |           | ture search (NAS)                                                   | 25 |  |  |

|   | 2.8 | A surv    | yey of hardware-based specialisation of ConvNet                     | 26 |  |  |

|   |     | 2.8.1     | ML accelerators from academic research                              | 27 |  |  |

|   |     | 2.8.2     | ML accelerators from industry                                       | 28 |  |  |

|   |     | 2.8.3     | A power-performance comparison among ASICs, FPGA and GPU-           |    |  |  |

|   |     |           | based implementation                                                | 29 |  |  |

|   | 2.9 | Summ      | ary                                                                 | 30 |  |  |

| • |     |           |                                                                     |    |  |  |

| 3 |     | -         | misation by decomposing convolutional layers                        | 31 |  |  |

|   | 3.1 |           | dancy in the parameterisation of ConvNets                           | 31 |  |  |

|   | 3.2 |           | for energy-efficient data-reuse pattern                             | 32 |  |  |

|   | 3.3 |           | ble filters in the context of convolution                           | 33 |  |  |

|   | 3.4 |           |                                                                     | 36 |  |  |

|   | 3.5 |           | Rank search and layer-restructuring algorithm                       |    |  |  |

|   | 3.6 |           | ation                                                               | 38 |  |  |

|   |     | 3.6.1     | MNIST - Digit Recognition                                           | 40 |  |  |

|   |     | 3.6.2     | CIFAR-10 - Object Classification                                    | 41 |  |  |

|   |     | 3.6.3     | ILSVRC-2012 - Image Classification                                  | 42 |  |  |

|   |     | 3.6.4     | PASCAL VOC - Image Segmentation                                     | 44 |  |  |

|   | 3.7 | -         | arison with prior work                                              | 46 |  |  |

|   | 3.8 |           | ssion                                                               | 47 |  |  |

|   |     | 3.8.1     | Reduction of Compute and Storage Cost                               | 48 |  |  |

|   |     | 3.8.2     | Efficient Use of Memory Bandwidth                                   | 48 |  |  |

|   |     | 3.8.3     | Summary                                                             | 50 |  |  |

| 4 | Low | -level lo | ossless optimisation using fast arithmetic                          | 51 |  |  |

| - | 4.1 |           | gorithm for convolutional neural network                            | 51 |  |  |

|   | 4.2 |           | Toom algorithm for fast convolution                                 | 52 |  |  |

|   | 4.3 |           | ication to the Cook-Toom algorithm                                  | 55 |  |  |

|   | 4.4 |           | n of a modified Cook-Toom algorithm from first principles           | 57 |  |  |

|   |     | 9         |                                                                     |    |  |  |

|   | 4.5 | Varian  | ts of the modified Cook-Toom algorithm                               | 61  |

|---|-----|---------|----------------------------------------------------------------------|-----|

|   |     | 4.5.1   | Variants of the modified Cook-Toom algorithm for 3x1 filters         | 61  |

|   |     | 4.5.2   | Variants of the modified Cook-Toom algorithm for 5x1 and 7x1 filters | 63  |

|   | 4.6 | Combi   | ining lossy and lossless schemes                                     | 65  |

|   | 4.7 | Evalua  | ation                                                                | 66  |

|   |     | 4.7.1   | Comparison of multiplication intensity                               | 67  |

|   |     | 4.7.2   | Floating-point errors in the Cook-Toom algorithm                     | 68  |

|   | 4.8 | Discus  | ssion                                                                | 71  |

|   |     | 4.8.1   | Design strategies to reduce floating point error                     | 72  |

|   |     | 4.8.2   | Modified Cook-Toom versus the FFT algorithm                          | 73  |

|   |     | 4.8.3   | Modified Cook-Toom versus the Winograd algorithm                     | 73  |

|   |     | 4.8.4   | Limitations of the modified Cook-Toom algorithm                      | 75  |

|   |     | 4.8.5   | Summary                                                              | 76  |

| 5 | Imp | lementa | ation of the Cook-Toom class of fast convolution                     | 77  |

|   | 5.1 | Multi-  | channel implementation of the modified Cook-Toom algorithm           | 78  |

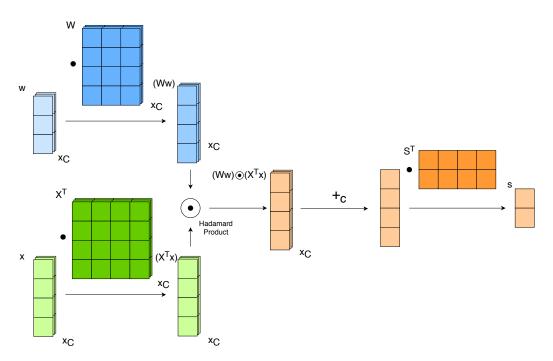

|   | 5.2 | An ove  | erview of the Armv8-A SIMD architecture                              | 80  |

|   |     | 5.2.1   | Data layout for SIMD computation                                     | 80  |

|   | 5.3 | MCM     | R: Multi-channel multi-region Cook-Toom algorithm                    | 81  |

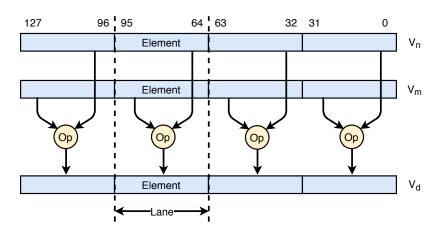

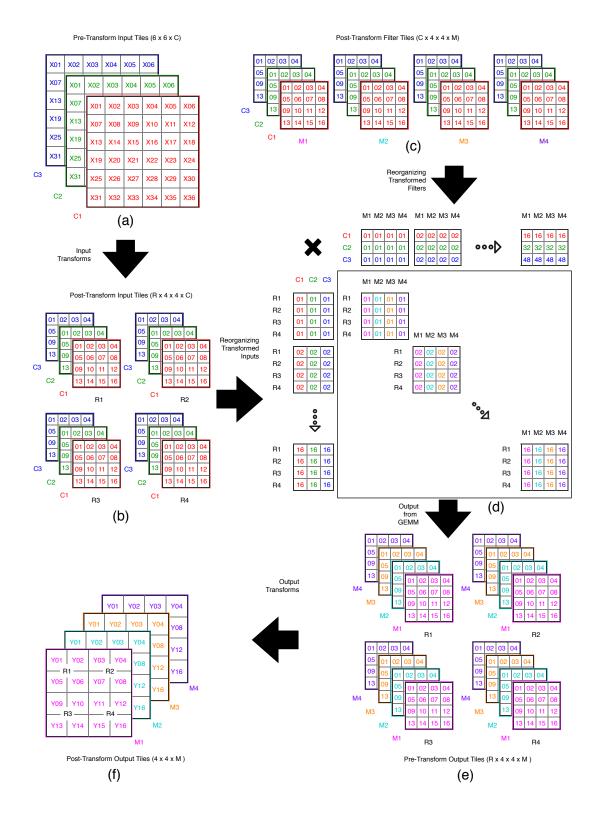

|   |     | 5.3.1   | Input transformation                                                 | 82  |

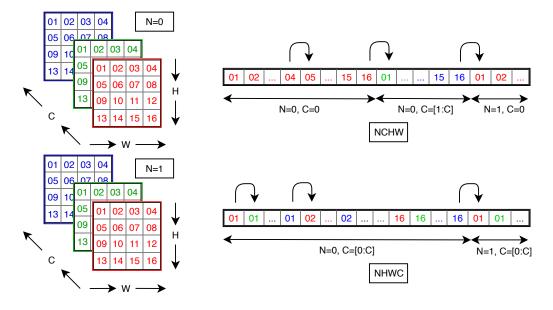

|   |     | 5.3.2   | Choice to vector orders: NCHW vs NHWC                                | 83  |

|   |     | 5.3.3   | Filter or weight transformation                                      | 84  |

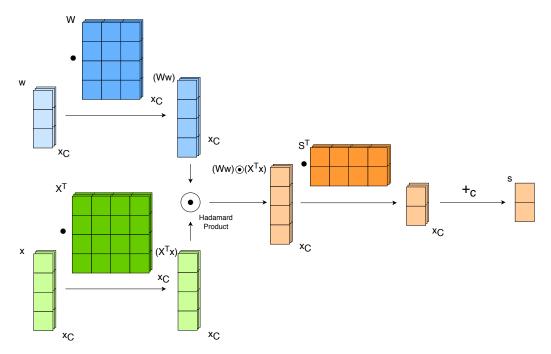

|   |     | 5.3.4   | Using GEMM to compute Hadamard product                               | 84  |

|   |     | 5.3.5   | Efficient tensor ordering for ARMv8 core                             | 89  |

|   |     | 5.3.6   | Output transformation                                                | 90  |

|   | 5.4 | Evalua  | ation                                                                | 92  |

|   |     | 5.4.1   | Evaluation setup - models and platform                               | 92  |

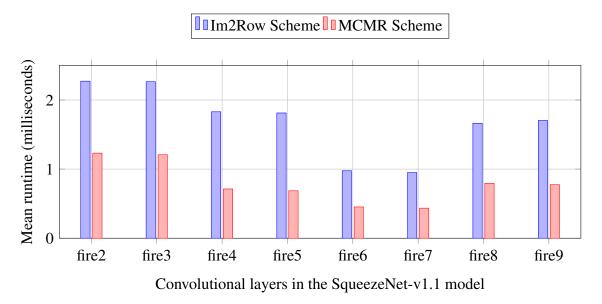

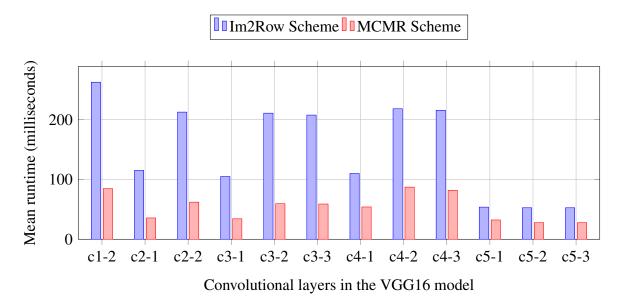

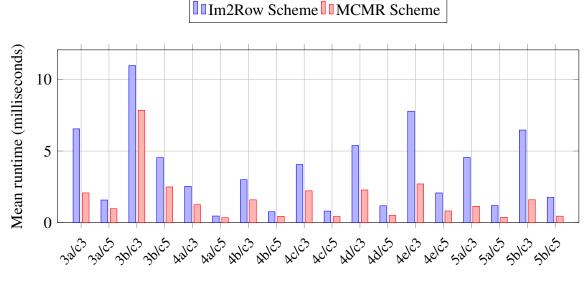

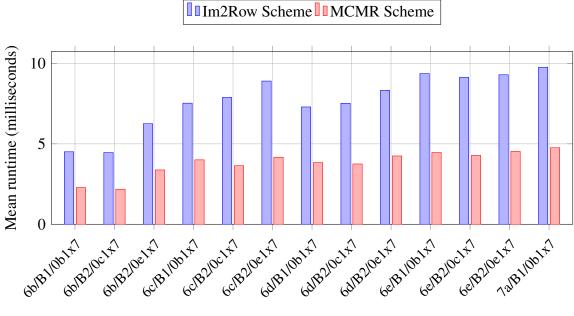

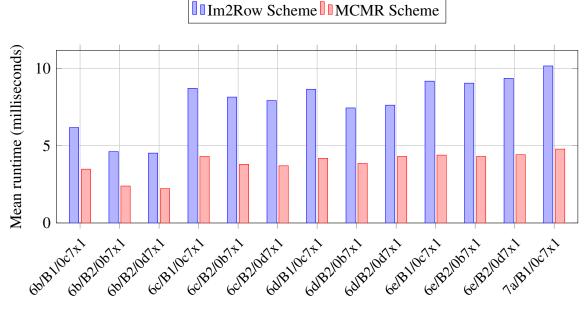

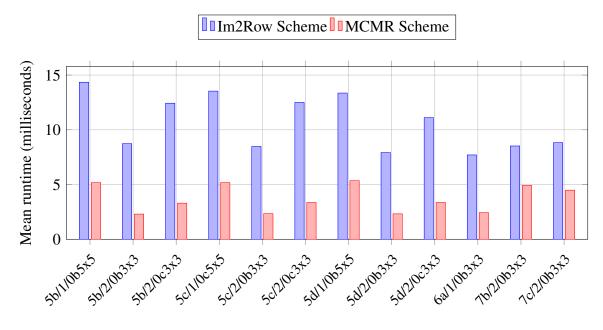

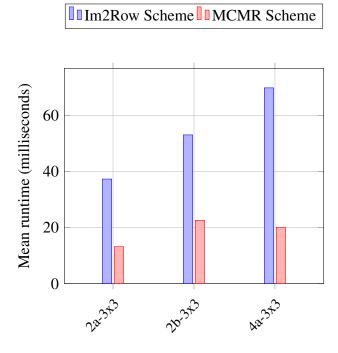

|   |     | 5.4.2   | Results – per-layer speedup                                          | 93  |

|   |     | 5.4.3   | Results – whole-network speedup                                      | 95  |

|   | 5.5 | Discus  | ssion                                                                | 99  |

|   |     | 5.5.1   | Speedup gap due to the cost of transforms                            | 99  |

|   |     | 5.5.2   | Speedup gap due to the limitations of hardware architecture          | 99  |

|   |     | 5.5.3   | Challenges in implementing the Cook-Toom convolution using lower-    |     |

|   |     |         | precision arithmetic                                                 | 100 |

|   |     | 5.5.4   | Summary                                                              | 100 |

| 6  | Scal   | able ar | chitecture for the Cook-Toom class of convolutions                  | 103  |

|----|--------|---------|---------------------------------------------------------------------|------|

|    | 6.1    | Design  | n principles                                                        | 103  |

|    | 6.2    | High-l  | level architecture of the Cook-Toom accelerator                     | 106  |

|    |        | 6.2.1   | The architecture of the Hadamard Engine                             | 107  |

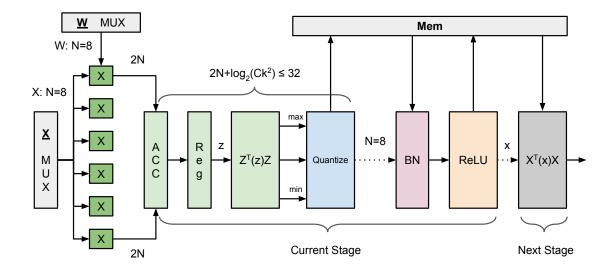

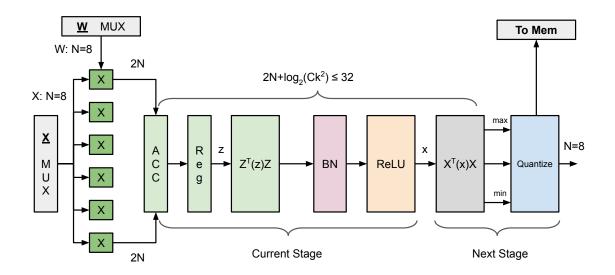

|    |        | 6.2.2   | Fused MAC architecture                                              | 112  |

|    |        | 6.2.3   | Input-transformation engine                                         | 112  |

|    | 6.3    | On-ch   | ip SRAM, hold buffers and data layout                               | 113  |

|    | 6.4    | Mappi   | ing convolutions to the Hadamard Engine                             | 116  |

|    | 6.5    | High-l  | level flow: z- and xy-phase of computations                         | 118  |

|    | 6.6    | Evalua  | ation                                                               | 119  |

|    |        | 6.6.1   | Evaluation setup and the baseline                                   | 119  |

|    |        | 6.6.2   | Performance analysis – per-layer                                    | 122  |

|    |        | 6.6.3   | Performance analysis – whole network                                | 124  |

|    |        | 6.6.4   | Comparison between different data-reuse patterns                    | 126  |

|    |        | 6.6.5   | Scalability property of the Hadamard engine                         | 127  |

|    | 6.7    | Discus  | ssion                                                               | 127  |

|    |        | 6.7.1   | Support for widely used 1x1 convolution in the Cook-Toom accelerato | r128 |

|    |        | 6.7.2   | Optimisation using a mixed-precision data path                      | 128  |

|    |        | 6.7.3   | Overhead of on-chip interconnect in the accelerator                 | 129  |

|    |        | 6.7.4   | Summary                                                             | 130  |

| 7  | Con    | clusion |                                                                     | 131  |

|    | 7.1    | Future  | e research scope                                                    | 134  |

|    |        | 7.1.1   | Extension of the ADaPT scheme using tensor decomposition            | 134  |

|    |        | 7.1.2   | Extension of the Cook-Toom algorithm for efficient training         | 134  |

|    |        | 7.1.3   | Mixed-precision implementation on a low-power Arm processor         | 134  |

|    |        | 7.1.4   | Extension of the custom accelerator to support other emerging types |      |

|    |        |         | of convolutional layers                                             | 135  |

| Re | eferen | ices    |                                                                     | 137  |

| Aŗ | opend  | lix A L | Lagrange polynomial interpolation                                   | 145  |

# List of figures

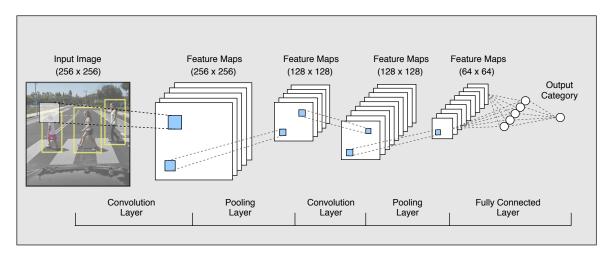

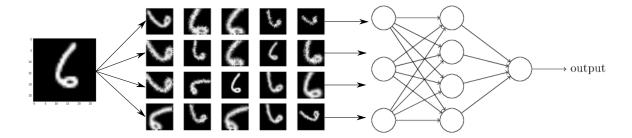

| 2.1  | A generic deep convolutional neural network (ConvNet)                               | 8  |

|------|-------------------------------------------------------------------------------------|----|

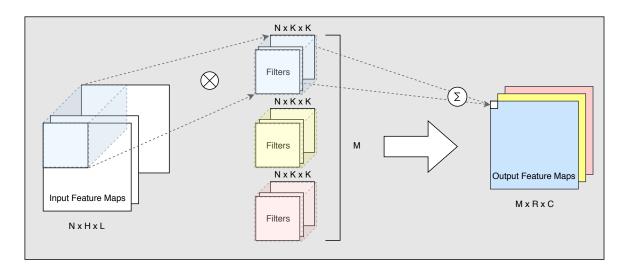

| 2.2  | A generic convolutional layer                                                       | 9  |

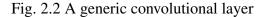

| 2.3  | Compute vs Memory bound                                                             | 11 |

| 2.4  | Spatial convolution                                                                 | 13 |

| 2.5  | 1-by-1 convolution                                                                  | 13 |

| 2.6  | Group convolution                                                                   | 13 |

| 2.7  | Depth-wise convolution                                                              | 15 |

| 2.8  | Input-stationary data-reuse patterns in modern ConvNets                             | 17 |

| 2.9  | Output-stationary data-reuse patterns in modern ConvNets                            | 18 |

| 2.10 | Weight-stationary data-reuse patterns in modern ConvNets                            | 18 |

| 2.11 | Row-stationary data-reuse patterns in modern ConvNets                               | 18 |

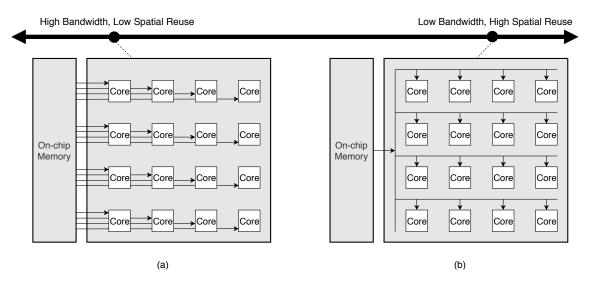

| 2.12 | Trade-off between on-chip interconnect complexity and spatial reuse. (a)            |    |

|      | Unicast network, (b) Broadcast network                                              | 21 |

| 3.1  | A Typical data augmentation used during training ConvNet for MNIST dataset          | 32 |

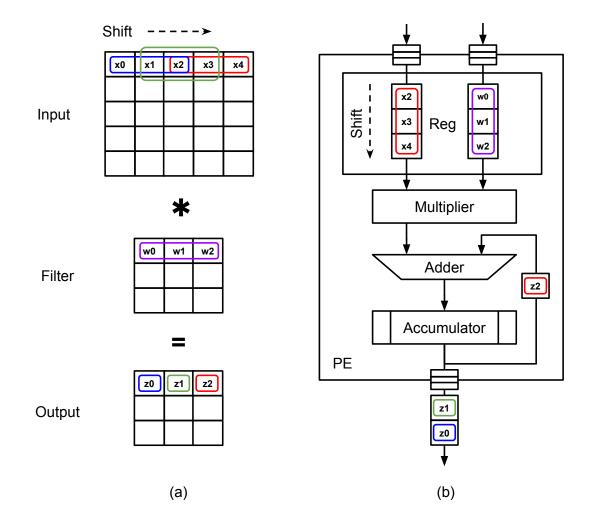

| 3.2  | Mapping of one-dimensional convolution primitive to a Processing Engine             |    |

|      | (PE). (a) Input:x is shifted right and multiplied with one-dimensional filter:w     |    |

|      | (b) In the PE, the filter:w stays stationary and input:x is shifted down, the       |    |

|      | partial sum is accumulated and shifted out of the PE                                | 34 |

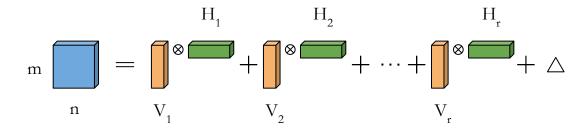

| 3.3  | A two-dimensional (2D) matrix can be represented by the sum of $r$ rank-1           |    |

|      | updates                                                                             | 36 |

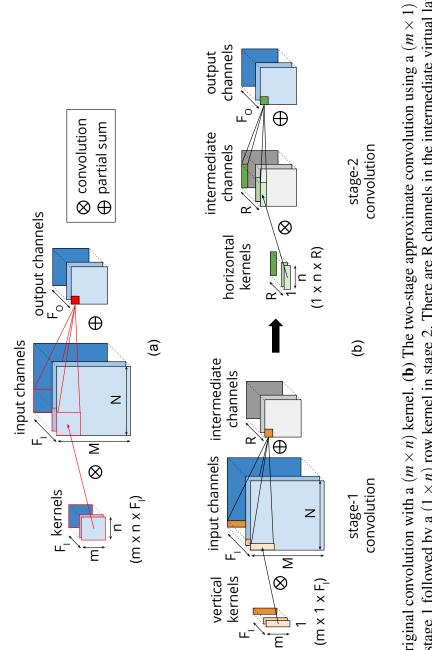

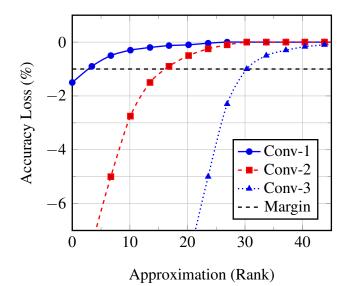

| 3.4  | (a) The original convolution with a $(m \times n)$ kernel. (b) The two-stage        |    |

|      | approximate convolution using a $(m \times 1)$ column kernel in stage 1 followed    |    |

|      | by a $(1 \times n)$ row kernel in stage 2. There are R channels in the intermediate |    |

|      | virtual layer.                                                                      | 39 |

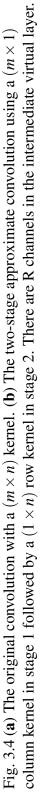

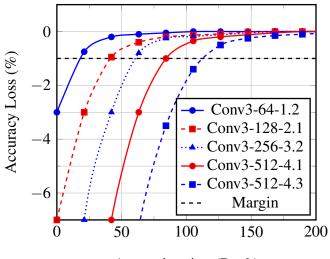

| 3.5  | Layerwise accuracy loss vs rank-approximation trade-off for the CIFAR-10            |    |

|      | model                                                                               | 42 |

| 3.6  | Accuracy loss vs rank approximation trade-off in selected layers from VGG16         | 43 |

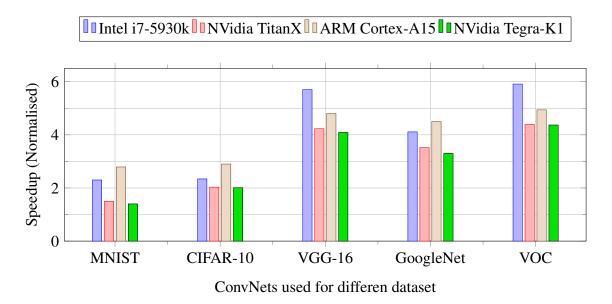

| 3.7  | Speed-up of selected ConvNets on different target platforms solely by ap-        |    |

|------|----------------------------------------------------------------------------------|----|

|      | proximating the convolutional layers without any loss of baseline accuracy .     | 45 |

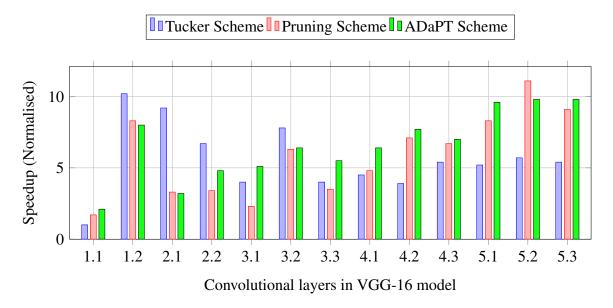

| 3.8  | VGG layerwise compute complexity (number of FLOPs) comparison be-                |    |

|      | tween Tucker Decomposition [55], Pruning [41] and ADaPT scheme                   | 47 |

| 3.9  | (a) The original convolution with a $(m \times n)$ 2-D kernel. The yellow marked |    |

|      | apron is all around the input tile. (b) The column-stage convolution using a     |    |

|      | $(m \times 1)$ column 1-D kernel. The apron is only at the top and bottom. (c)   |    |

|      | The row-stage convolution using a $(1 \times n)$ row 1-D kernel. The apron is    |    |

|      | only at the left and right.                                                      | 49 |

| 4.1  | Steps involved in the Cook-Toom algorithm                                        | 53 |

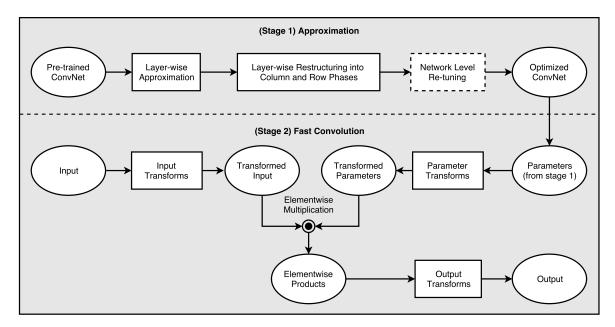

| 4.2  | 1D-FALCON: The high-level optimisation pipeline consists of two main             |    |

|      | stages - (1) a lossy approximation stage, (2) a lossless fast convolution stage  | 66 |

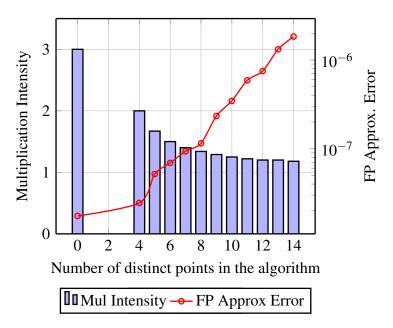

| 4.3  | As the number of points increases multiplication intensity (i.e. number          |    |

|      | of multiplications per output point) drops while floating-point error grows      |    |

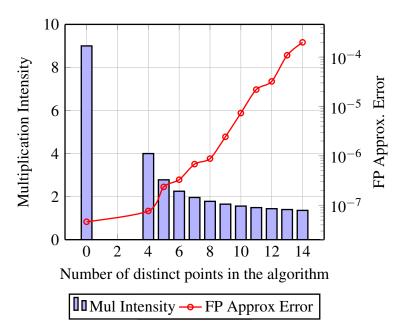

|      | (example: 1D convolution with filter size of 3)                                  | 70 |

| 4.4  | As the number of points increases multiplication intensity (i.e. number          |    |

|      | of multiplications per output point) drops while floating-point error grows      |    |

|      | (example: 2D convolution with filter size of $3 \times 3$ )                      | 70 |

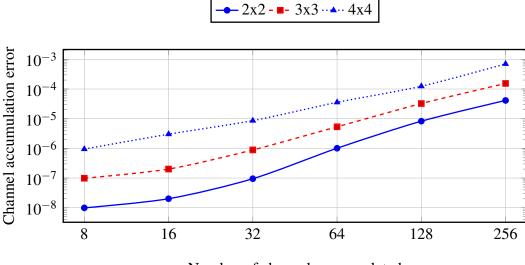

| 4.5  | Channel-accumulation error for different numbers of feature maps                 | 72 |

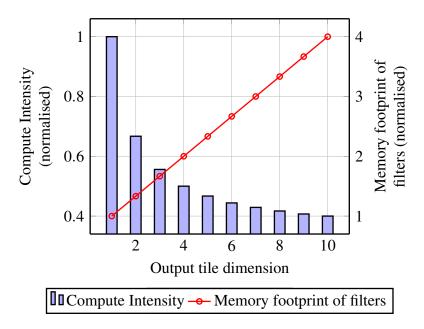

| 4.6  | With larger tile/block size, the cost of intermediate filter-memory footprint    |    |

|      | grows (Example: 1D convolution with filter size of 3)                            | 74 |

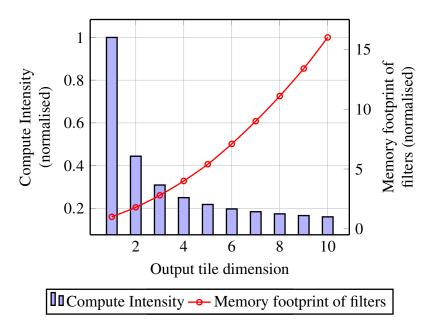

| 4.7  | With larger tile/block size, the cost of intermediate filter-memory footprint    |    |

|      | grows (Example: 2D convolution with filter size of $3 \times 3$ )                | 74 |

| 5.1  | Channel-by-channel implementation of the Cook-Toom convolution                   | 79 |

| 5.2  | Multi-channel implementation of the Cook-Toom convolution                        | 79 |

| 5.3  | Armv8-A SIMD processing                                                          | 81 |

| 5.4  | High-level diagram of the MCMR Cook-Toom scheme                                  | 88 |

| 5.5  | NCHW vs NHWC layout                                                              | 90 |

| 5.6  | Layerwise comparison of the runtime of the SqueezeNet-v1.1 model with a          |    |

|      | batch size of 1                                                                  | 92 |

| 5.7  | Layerwise comparison of runtime of the VGG16 model with a batch size of 1        | 93 |

| 5.8  | Layerwise comparison of runtime of the GoogLeNet model with a batch size         |    |

|      | of 1                                                                             | 94 |

| 5.9  | Comparison of runtime of 1x7 layers of the Inception-v3 with a batch size of 1   | 95 |

| 5.10 | Comparison of runtime of $7x1$ layers of the Inception-v3 with a batch size of 1 | 96 |

| 5.11 | Comparison of runtime of 3x3 and 5x5 layers of the Inception-v3 with a                              |     |

|------|-----------------------------------------------------------------------------------------------------|-----|

|      | batch size of 1                                                                                     | 97  |

| 5.12 | Comparison of runtime of $3x3$ layers of the Inception-v3 with a batch size of 1                    | 98  |

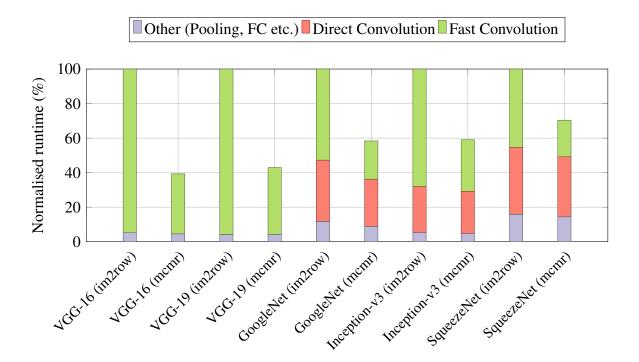

| 5.13 | Speed-up achieved in the Cook-Toom-suitable layers as a fraction of the                             |     |

|      | entire model (batch size = 1)                                                                       | 98  |

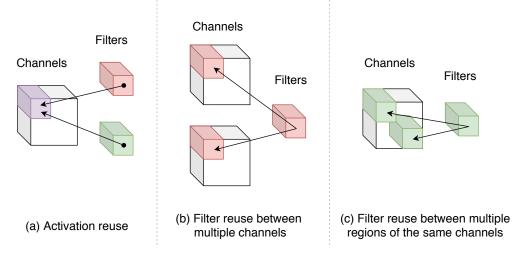

| 6.1  | Data-reuse patterns in modern ConvNets                                                              | 104 |

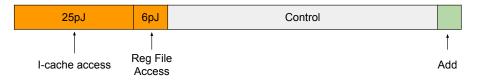

| 6.2  | Energy cost of DRAM access vs arithmetic operation at 45nm technology [47]                          | 105 |

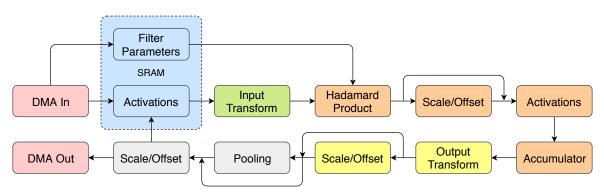

| 6.3  | High Level Functional Diagram of the Accelerator                                                    | 106 |

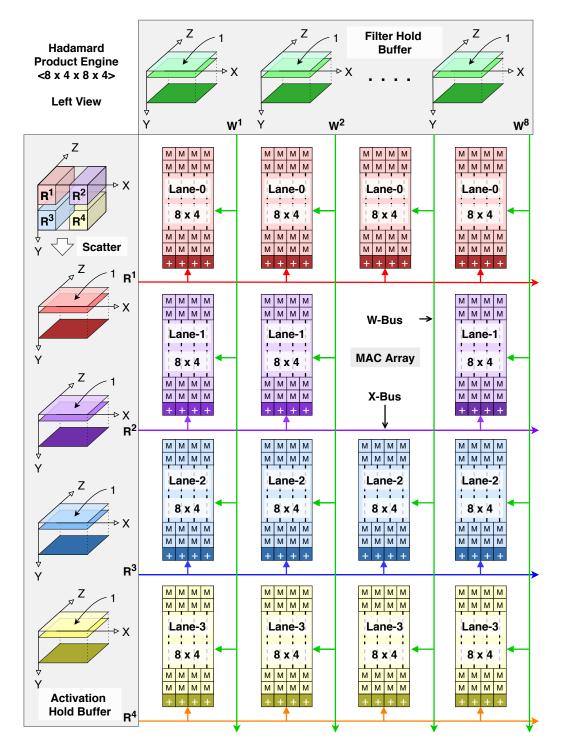

| 6.4  | The left view of the architecture of the central Hadamard Product Engine                            |     |

|      | (Config: $\langle 8 \times 4 \times 8 \times 4 \rangle$ ); 'M' is a MAC unit, '+' is an accumulator | 108 |

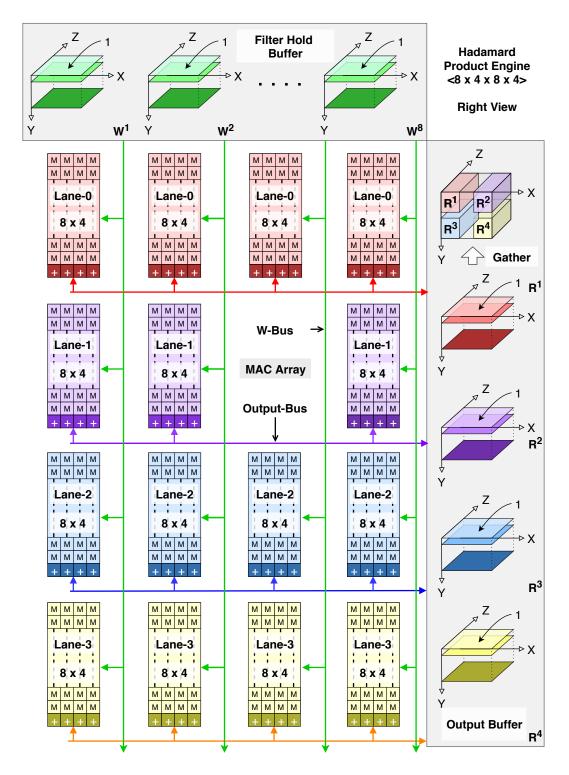

| 6.5  | The right view of the architecture of the central Hadamard Product Engine                           |     |

|      | (Config: $\langle 8 \times 4 \times 8 \times 4 \rangle$ ); 'M' is a MAC unit, '+' is an accumulator | 109 |

| 6.6  | The architecture of the fused MAC unit - generic                                                    | 111 |

| 6.7  | The architecture of the fused MAC unit - optimised                                                  | 111 |

| 6.8  | The architecture of the input transform Engine                                                      | 113 |

| 6.9  | Activation-buffer layout                                                                            | 114 |

| 6.10 | Filter-buffer layout                                                                                | 115 |

| 6.11 | Tiles mapped to the Hadamard Engine in each cycle                                                   | 116 |

| 6.12 | High-level flow of the MCMR scheme                                                                  | 118 |

| 6.13 | On-chip interconnect in (a) NVDLA, (b) Cook-Toom accelerator                                        | 119 |

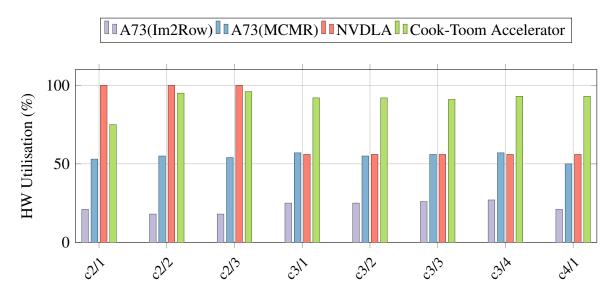

| 6.14 | Layerwise HW utilisation of the GoogLeNet with a batch size of 1 (Group-A)                          | 120 |

| 6.15 | Layerwise HW utilisation of the GoogLeNet with a batch size of 1 (Group-B)                          | 120 |

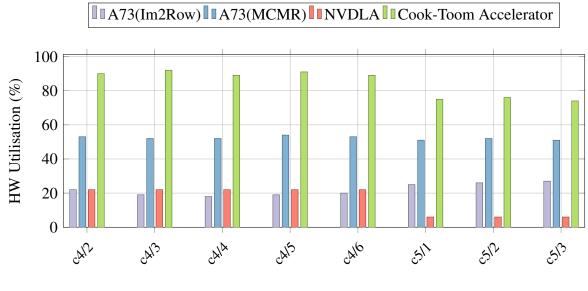

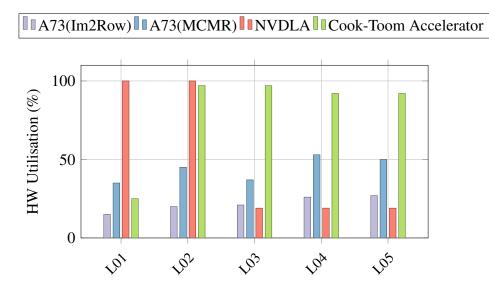

| 6.16 | Layerwise HW utilisation of the ResNet50 with a batch size of 1 (Group-A)                           | 122 |

| 6.17 | Layerwise HW utilisation of the ResNet50 with a batch size of 1 (Group-B)                           | 123 |

| 6.18 | Layerwise HW utilisation of the AlexNet with a batch size of 1                                      | 124 |

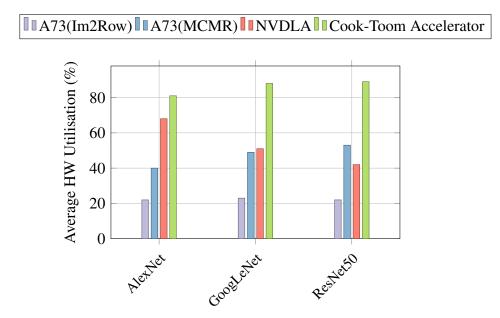

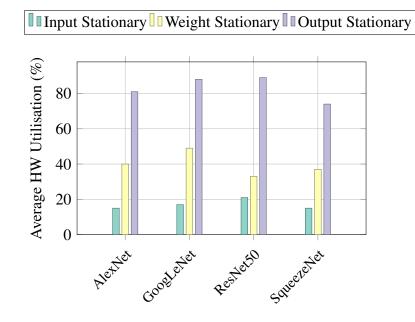

| 6.19 | Average HW utilisation of selected ConvNets with a batch size of 1                                  | 125 |

| 6.20 | Comparison between different data-reuse patterns - IS, WS, and OS                                   | 126 |

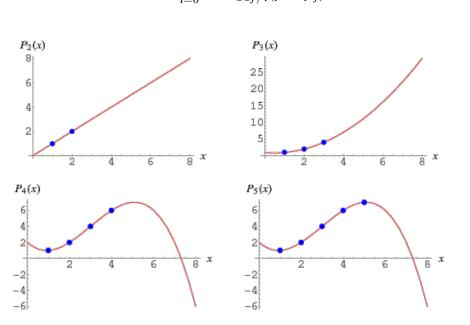

| A.1  | Lagrange interpolation polynomials                                                                  | 145 |

# List of tables

| gy cost comparsion at 45nm node                                           | 10                                         |

|---------------------------------------------------------------------------|--------------------------------------------|

| inance of small kernels in modern ConvNets                                | 16                                         |

| metic intensity of different types of convolutional layers                | 16                                         |

| er-Performance comparison of different hardware implementations           | 30                                         |

| igurations of the target platforms                                        | 40                                         |

| ST model approximation summary                                            | 40                                         |

| ST speedup of convolution layers on the Arm Cortex A15 without loss       |                                            |

| se-line accuracy of 99.23%                                                | 41                                         |

| AR-10 model approximation summary                                         | 41                                         |

| AR-10 layerwise speedup of convolutions on the Arm Cortex A15 with-       |                                            |

| ny loss of base-line accuracy of 86%                                      | 41                                         |

| 16 layerwise speed-up of convolution on the i7-5930k (per image) with     |                                            |

| ss of base-line accuracy of 90.5%                                         | 43                                         |

| 316 model approximation summary                                           | 45                                         |

| 16 layerwise comparison of the number of strong operations, i.e. multi-   |                                            |

| tions (MULs) between (a) a direct 2-D approach, (b) Tucker decomposi-     |                                            |

| [55], (c) Pruning [41], and (d) the ADaPT                                 | 46                                         |

| dup achieved using the 1D-FALCON scheme                                   | 67                                         |

| parison of speedup of the VGG-16 network using different schemes,         |                                            |

| imisations schemes that are part of this PhD                              | 68                                         |

| parison of multiplication intensity (i.e. number of strong operations per |                                            |

| ut point) between direct and the Cook-Toom convolution for varying        |                                            |

| at dimensions for filter size 3 (1D) and $3x3(2D)$                        | 69                                         |

|                                                                           | inance of small kernels in modern ConvNets |

| 4.4 | Comparison of multiplication intensity (i.e. number of strong operations per  |     |

|-----|-------------------------------------------------------------------------------|-----|

|     | output point) between direct and the Cook-Toom convolution for varying        |     |

|     | output dimensions for filter size 5 (1D) and $5 \times 5$ (2D)                | 69  |

| 5.1 | Summary of mean absolute runtime of the whole network in milliseconds         |     |

|     | (msec) for a batch size of 1 in VGG-19/-16 and GoogLeNet                      | 97  |

| 5.2 | Summary of mean absolute runtime of the whole network in milliseconds         |     |

|     | (msec) for batch size of 1 in Inception-v3 and SqueezeNet-v1                  | 99  |

| 6.1 | Activation and filter hold-buffer allocation table for various configurations |     |

|     | of the Hadamard Engine $\langle f_i \times T \times f_o \times L \rangle$     | 115 |

| 6.2 | Summary of mean absolute runtime of the whole-network in milliseconds         |     |

|     | (msec) for batch size of 1 in AlexNet, GoogLeNet and ResNet                   | 126 |

| 6.3 | Typical configurations of a Cook-Toom accelerator                             | 128 |

# Chapter 1

# Introduction

This dissertation describes a collection of co-optimisation schemes that help to reduce the overall inference time of a deep convolutional neural network. The schemes aim to exploit co-optimisation of model, algorithm and underlying hardware structure.

In this chapter I outline the motivation for this work. I also summarise the contributions of the dissertation and list the contents of the following chapters that describe the contributions in detail.

# **1.1 Motivation**

Recent advances in deep learning have greatly changed the way that computing devices process human-centric contents such as images, videos, speech, and audio [61]. At the same time, the proliferation of mobile and embedded devices leads to visions of the internet of things (IoT), giving rise to a sensor-rich world where physical things in our everyday environment are increasingly enriched with computing [83]. Indeed, in recent years significant research efforts have been spent toward building cloud-based infrastructure to enable emerging deep-learning-based applications for edge devices [98]. The agility of cloud computing is great - but it simply isn't sufficient. In the near future there will be more demand for machine learning at the edge than in the cloud. As people need to interact with their digitally-assisted technologies (e.g. personal assistants, wearables, autonomous car, healthcare, and other smart IoT devices) in real-time, waiting on a datacentre many miles away isn't going to work. Not only the latency matters, but often these edge devices are not within the range of the cloud needing them to operate autonomously for the most part. Even when these devices are connected in the cloud, moving high-volumes of data to the centralised datacentre is not scalable, due to communication costs that impact performance and energy consumption [87]. Since the latency and security risk of relying on the cloud are intolerable, we need a significant portion of computation closer to the edge to permit secure, autonomous, and real-time decision making. This poses an enormous challenge in terms of implementing emerging machine-learning workloads on resource-constrained low-power embedded devices. When it comes to image and video, the performance of many modern embedded applications is enhanced by application of neural networks, and more specifically by convolutional neural networks or ConvNets. Furthermore, with continuous progress made in research in the area of deep learning, the architecture of modern ConvNet is still evolving rapidly. As a consequence, many of the earlier results from model or hardware optimisation research became ineffective in the long run [35, 12, 93, 18, 6]. Over specialising during implementation often leads to loss of generalisation. For example, deep neural network with 6-bit implementations are efficient for some specific cases, but do not generalise well for medium to large datasets. Finding solutions that generalise well for the majority of the application datasets and deep models is extremely difficult. Over the last few years, we have seen a proliferation of innovative and more efficient ConvNet architectures. Although there has been a lot of research done either on model optimisation and hardware design in isolation, little attention has been paid to the model-algorithm-hardware co-design approach. As a result, the research in this space is quite fragmented and the outcome is not always the optimum. The aim of this dissertation is to fill this gap and investigate if emerging compute-heavy deep convolutional networks can benefit from co-design of model architecture, low-level algorithms and underlying hardware architecture.

## **1.2 Research questions**

- Considering the rapidly evolving architecture of convolutional neural network and strong demands of such emerging architectures in industry, is it possible to find and accelerate the most commonly occurring layer structures within widely used models?

- How can the co-design of model, low-level algorithm and underlying hardware help in effectively harnessing the full potential of optimisation at the algorithmic level?

- Is it possible to combine lossy and lossless compression schemes to achieve a more efficient implementation compared to applying them in isolation?

- Building a new custom accelerator is an expensive solution and is not always practical due to rapidly changing characteristics of ConvNets. Arm processor-based solutions are ubiquitous across embedded applications and billions of such platforms are already in use. Is it feasible to implement a modern compute-heavy deep ConvNet on an existing mobile platform such as in Arm?

• Finally, considering the architecture of deep networks is still evolving, is it possible to build an efficient custom accelerator for modern ConvNets that is configurable, scalable and flexible enough to support a wide variety of emerging layer types?

# 1.3 Hypothesis

Model-algorithm-architecture co-design of deep convolutional neural networks can produce highly optimised implementations of inference for embedded applications that meet the limited compute, memory and power budgets of the target hardware. By aiming at the most commonly occurring layer architectures within widely used models, and applying such co-optimisations, we can enable the deployment of sophisticated deep-learning models on cutting-edge mobile and embedded systems.

## **1.4 Contributions**

This dissertation provides four main contributions to research in the area of efficient deepneural-network implementation on embedded systems.

First, an easy to implement three-step approximation scheme which can be applied on the commonly occurring spatial convolutional layers in many state-of-the-art pre-trained deep models in use today. The novel ADaPT approximation scheme is mathematically well grounded, easily reproducible and can be applied on ConvNets statically. This has resulted in a publication that illustrates the effectiveness of this scheme primarily in the IoT and embedded application space [68].

Second, a lossless scheme for computing convolution that reduces the total number of required multiplications. The novel scheme uses a modified version of the Cook-Toom algorithm and is very effective on small size filters which are very common in modern ConvNets. Furthermore, the lossless scheme does not require any structural changes to the pre-trained model, unlike the ADaPT approximation scheme. For this particular reason, the Cook-Toom class of algorithm are highly suitable for environments where training data is not available. This work was shortlisted for the best paper award in the ICANN conference organised by the European Neural Network Society (ENNS) [69].

Third, an efficient implementation of the Cook-Toom class of algorithms on one of Arm's ubiquitous low-power cortex processors. Unlike direct convolution, computing convolutions using the modified Cook-Toom algorithm requires a different data-processing pipeline. I introduce a multi-channel multi-region (MCMR) scheme to enable an efficient implementation of the fast Cook-Toom algorithm. The novel MCMR scheme can also be extended to other

similar resource-constrained SIMD processors. The speed up achieved from the MCMR scheme is significant for embedded systems and has been adopted by Arm for their Cortex class of processors. This work resulted in a joint publication with Arm holdings [71].

Fourth, a custom architecture for accelerating convolutional neural network using the Cook-Toom class of fast arithmetic, that addresses some of the limitations of a traditional general-purpose processor. The novel architecture is designed from the ground up based on a few fundamental design principles. The accelerator is designed based on the previously introduced MCMR scheme and it uses a core Hadamard engine. The accelerator is configurable, scalable and handles the most commonly occurring spatial convolutional layers efficiently.

### 1.5 Outline

I now outline the organisation of the rest of this dissertation.

In Chapter 2, I provide all the necessary technical background on convolutional neuralnetwork architectures that is required to understand the rest of the thesis. I also highlight various challenges involved when implementing modern neural networks on low-power embedded systems. In this chapter, I also survey previous research work on model optimisation and hardware accelerators.

In Chapter 3, I explore redundancies in modern deep networks. I show how these redundancies can be exploited to compress deep models significantly. I introduced the concept of separable filters that builds up the background for the ADaPT approximation algorithm. Finally, I illustrate how layers in deep convolutional neural networks can be decomposed and approximated across two consecutive stages to reduce overall compute complexities of the model.

In Chapter 4, I focus on a lossless scheme to speed up convolution. Convolution with small filter size is the fundamental building block of modern convolutional neural networks and thus speeding up such convolution will improve the overall performance of the model. I introduce the Cook-Toom fast arithmetic scheme that can be used in modern convolutional neural network to reduce the total number of multiplications. I then extend the base version with a modified version and illustrate many variants of the algorithm that can help to accelerate modern convolutional neural networks.

In Chapter 5, I present an implementation of the modified Cook-Toom fast convolution algorithm on a widely used low power Arm mobile processor. I then introduce a novel multi-channel multi-region (MCMR) scheme that enables efficient implementation of the algorithm on Arm's SIMD architecture. By implementing several widely used ConvNets I illustrate the effectiveness of the MCMR scheme for SIMD processors. I conclude this chapter discussing several limitations of implementing the modified Cook-Toom algorithm on a resource-constrained mobile processor that motivates the need for a custom accelerator.

In Chapter 6, I tackle the limitations discussed in the previous chapter by introducing a novel Cook-Toom custom accelerator. I start by introducing a number of design principles for domain specific accelerator design. I then describe the details of the Cook-Toom accelerator and the core Hadamard engine. I show a few example passes on how to map convolutional layers to the core Hadamard engine. In the evaluation section, I illustrate the effectiveness of the custom accelerator through benchmarking a number of widely used ConvNets today.

In Chapter 7, I conclude and provide some suggestions for further research on model/hardware co-design of deep neural networks.

## **1.6 Publications**

Some of the research described in this dissertation also appears in the following publications:

- Partha Maji, Daniel Bates, Alex Chadwick, and Robert Mullins. ADaPT: Optimizing CNN inference on IoT and mobile devices using approximately separable 1-D kernels. In the Proceedings of the ACM International Conference on Internet of Things and Machine Learning, ACM-IML, 2017 [68].

- Partha Maji, and Robert Mullins. 1D-FALCON: Accelerating deep convolutional neural network inference by co-optimization of models and underlying arithmetic implementation. In *the Proceedings of the International Conference on Artificial Neural Networks, ICANN, 2017* [69].

- Partha Maji, and Robert Mullins. On the Reduction of Computational Complexity of Deep Convolutional Neural Networks. In *the Proceedings of the Journal Entropy*, 2018 [70].

- Partha Maji, Andrew Mundy, Jesse Beu, Ganesh Dasika, Matthew Mattina, and Robert Mullins. Efficient Winograd or Cook-Toom Convolution Kernel Implementation on Widely Used Mobile CPUs. In the Proceedings of the Workshop on Energy Efficient Machine Learning and Cognitive Computing for Embedded Applications, IEEE HPCA.EMC2, 2019 [71]

# Chapter 2

# **Background and related work**

This chapter focuses on the background literature of deep convolutional neural networks and a survey of prior research on the optimisation of modern deep networks. I begin by introducing the detailed architecture of a convolutional neural network or ConvNet. I then illustrate various types of convolutional layers widely used today. This section is followed by an overview section on different data-reuse patterns which builds up a strong background for the chapters on hardware implementation. I end this chapter with a brief survey on prior work on model optimisation and hardware acceleration.

# 2.1 Deep convolutional neural network architecture

ConvNets are generally used in computer-vision tasks. However they've shown promising results when applied to various other tasks as well, including various natural-language-processing tasks, text based sentiment analysis, generating time-series data, speech emotion detection, audio classification [54, 53, 26, 74, 27, 90]. More and more diverse and interesting use cases are being found for ConvNet architectures [32, 91, 45]. A typical convolutional neural network (ConvNet) architecture consists of a series of stages. The first few stages are composed mostly of two types of layers: convolutional layers and pooling layers. As illustrated in Figure 2.1 there are a number of feature maps within a convolutional layer, within which each output feature map is connected to local patches in the feature maps of the previous layer through a set of weights called a filter (or a kernel) bank. The output of this weighted sum is then passed through a non-linearity layer. In most ConvNets, the non-linearity layer is a rectifier linear unit or, in short, ReLU. The role of the convolutional layer is to detect local conjunctions of features in a layer, whereas the role of the pooling or sub-sampling layer is to merge semantically similar features into one. Pooling also helps in reduction of feature size in the subsequent layers.

layer combinations are then followed by fully-connected layers as shown in the figure. The choice of depth or number of layers of each type is one of the widely studied ConvNet design parameters. In the ImageNet competition, the accuracy of the classification task has improved year-over-year using deeper networks. For example, in 2012, AlexNet [56] achieved a top-5 error rate of 16.4% using 8 layers, whereas, in 2015, Microsoft's ResNet [44] achieved a staggering error rate of just 3.57% using 152 layers. The choice of connections across multiple layers is also an important area of model architecture research. For example, the ResNet architecture introduced bypass connections which skip over multiple layers. The ResNet model achieves a 2% improvement over the baseline architecture on top-5 accuracy. The ConvNet architecture design space is still evolving rapidly.

Fig. 2.1 A generic deep convolutional neural network (ConvNet)

Convolution and the convolutional layer are the major building blocks used in modern deep ConvNets and they are extremely compute heavy. Many modern deep ConvNets often require billions of FLOPs to compute a single frame of image. In this thesis, I am primarily interested at optimisation and efficient implementation of the convolutional layers. Figure 2.2 illustrates a typical convolutional layer in deep ConvNets. The example layer consists of *M* 3-dimensional  $N \times K \times K$  kernels and  $N \times H \times L$  input feature maps. Each kernel performs a convolution on the input maps with a sliding stride of S, which generates a  $R \times C$  output map. Since there are M sets of kernels *M* output maps are produced. The computation of a convolutional layer can be expressed as the multi-layer loop shown in listing 2.1, where *X*, *W* and *Out* are the input maps, kernels and the output maps.

```

for (r = 0; r < R; r++) //Loop R

for (c = 0; c < C; c++) //Loop C

for (n = 0; n < N; n++) //Loop N

for (m = 0; m < M; m++) //Loop M

for (i = 0; i < K; i++) //Loop K

for (j = 0; j < K; j++) //Loop K

Out[m][r][c] += W[m][n][i][j]*X[n][r*S+i][c*S+j]; // Convolution</pre>

```

Listing 2.1 Pseudo code of a convolution layer

# 2.2 Challenges of deploying ConvNets on embedded systems

Today, ConvNets are very popular in image classification tasks and already used in many cloud-based services, such as Google Image Translate and Prisma - an instagram like app. Although in the commercial sector many companies deploy them using on-line large clusters of GPUs and server-grade CPUs, large-scale adoption of state-of-the-art ConvNet-based off-line solutions on mobile and embedded consumer products is still not yet prominent. The majority of the existing off-line solutions support inference using cut-down versions of the state-of-the-art models. These devices are battery powered, with very limited resources and power budget, and thus pose a significant challenge on deploying ConvNets in embedded platforms. A desktop or server grade CPU or GPU consumes about 60 - 200Watts, whereas a smart-phone is limited at approximately 5 - 6Watts. For wearable consumer products the power margin even gets worse and usually is limited to 1Watt or less.

In contrast, current state of the art ConvNets are extremely power hungry due to their size, in both the number of layers and parameters. Table 2.1 summarises the storage requirement

| Release<br>Year | CNN<br>Model | #Conv<br>layers | #MACC<br>[millions] | #Weights<br>[millions] | #Activations<br>[millions] | ImageNet<br>[top-5 err%] |

|-----------------|--------------|-----------------|---------------------|------------------------|----------------------------|--------------------------|

| 2012            | AlexNet      | 5               | 1140                | 62.4                   | 2.4                        | 19.7                     |

| 2014            | VGGNet-16    | 16              | 15470               | 138.3                  | 29.0                       | 8.1                      |

| 2014            | GoogLeNet    | 22              | 1600                | 7.0                    | 10.4                       | 9.2                      |

| 2015            | ResNet-50    | 50              | 3870                | 25.6                   | 46.9                       | 7.0                      |

| 2015            | Inception-v3 | 48              | 5710                | 23.8                   | 32.6                       | 5.6                      |

| 2016            | SqueezeNet   | 18              | 860                 | 1.2                    | 12.7                       | 19.7                     |

Table 2.1 A snapshot of complexity in winning CNNs

Table 2.2 Approximate energy cost of common operations and data transfers (at 45nm process node) Source: [42]

| Operation          | Energy (pJ) | Relative cost |

|--------------------|-------------|---------------|

| 16b Int ADD        | 0.06        | 1             |

| 16b Int MULT       | 0.8         | 13            |

| 16b FP ADD         | 0.45        | 8             |

| 16b FP MULT        | 1.1         | 18            |

| 32b FP ADD         | 1.0         | 17            |

| 32b FP MULT        | 4.5         | 80            |

| Register File, 1kB | 0.6         | 10            |

| L1 Cache, 32kB     | 3.5         | 58            |

| L2 Cache, 256kB    | 30.2        | 500           |

| DRAM               | 640         | 10667         |

| Wireless Transfer  | 60000       | 1000000       |

of the most popular state-of-the-art ConvNets from the ImageNet competition. As the table depicts, to achieve any realistic performance they would require lot of on-chip memory, significant memory bandwidth and lots of computational resources. Table 2.2 shows an approximate estimate of the energy costs of basic arithmetic operations and data transfers at a 45nm process node. Using those estimates, for example, a ConvNet with 1 billion connections to run at just 30Hz would require a minimum (30Hz)(1Billion)(640pJ) = 19.2Watts just to access the parameters from off-chip storage, which is well beyond the limit of any mobile device. So, the current approach to alleviate the power-performance challenge is to run them in the cloud and download the result on client devices. This significantly limits the real-time performance that an application can achieve and also raises serious privacy concerns. In addition, sending an 720p or 1080p HD image at 30fps over the wireless network consumes a lot of power. As a result, the true potential of ConvNets can never be achieved without being able to run them on mobile platforms.

### 2.3 Arithmetic intensity and roof-line model

In analysing system performance bottlenecks, a roof-line model [97], a visually intuitive tool, is often used in multicore, manycore, or accelerator architectures. Using the roof-line model, one can examine the resultant ceilings in order to determine both the implementation and inherent performance limitations. The computational roof provides just an upper bound (the theoretical maximum) to performance. The computational ceilings impose a limit on the attainable performance that is below the actual roof-line, and indicate that the application cannot break through any one of these ceilings without first performing the associated optimisation. Computation and communication are two main constraints in achieving system throughput. As shown in Figure 2.3, a system can either be compute-bound or memory-

Computational intensity (ops/byte)

Fig. 2.3 Compute vs Memory bound

bound. The roof-line sets an upper bound on performance of a model depending on its computational or arithmetic intensity (ops/byte). If we think of computational intensity as a column that hits the roof, either it hits the flat part of the roof, meaning performance is compute-bound, or performance is ultimately memory-bound.

Using the roof-line model (see Figure 2.3),  $P_2$  reflects the compute bound limit in convlayers and  $P_1$  reflects the memory bound limit in FC-layers. One has to be careful about which bottleneck to improve first. We can think of each optimisation as a performance ceiling below the appropriate roof-line, meaning you cannot break through a ceiling without first performing the associated optimisation.

In case of ConvNets, both types of limitation exist depending on the architecture - either the system can be ill designed so as to be starved or its peak compute capability is very limited. Ideally, a system should be tuned in such a way that it coincides with point  $P_0$  as this is the break-even point. In the following section, I discuss different types of convolutional layer architectures that are commonly used on modern ConvNets. I then compare those layer types using the arithmetic intensity metric.

# 2.4 Types of convolutional layers

Convolution is a widely used technique in signal processing. Although convolution in ConvNets is named after generic convolution, it is essentially the cross correlation in signal processing. In ConvNets, the filters in convolution are not reversed and elementwise multiplication and addition are performed to obtained the result. In deep learning, several variants of basic convolution are used within the convolutional layers. In this section, I summarise several types of convolution commonly used in deep convolutional neural networks.

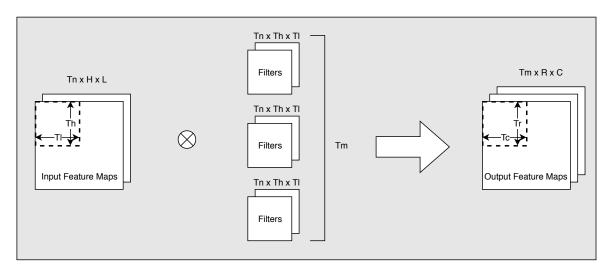

#### 2.4.1 Spatial convolution

The most common form of convolutional layer used in ConvNets is spatial convolution. Figure 2.4 illustrates an example spatial convolution layer. In this example, there are Tm filters each of size  $Tn \times Th \times Tl$ . These are applied on the three dimensional input tensor of size  $Tn \times H \times L$ . After accumulation of the results for all the input channels it produces output of size  $Tm \times R \times C$ . As a concrete example, let us consider an input  $5 \times 5$  RGB image which has 3 channels. Each set of filters has a dimension of  $3 \times 3 \times 3$ . First, each of the filters are applied to three channels in the input layer, separately. Three convolutions are performed, which result in 3 channels with size  $3 \times 3$ . Then these three channels are summed together using element-wise addition to form one single channel of size  $3 \times 3 \times 1$ . If there are multiple output channels then this process is repeated for each of the output channels.

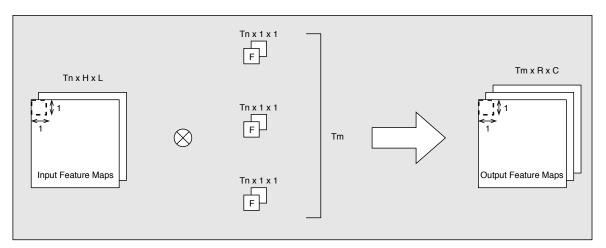

#### 2.4.2 1 x 1 convolution

$1 \times 1$  convolution is a special case of spatial convolution which is mainly used for dimensionality reduction for efficient computation [63]. By applying  $1 \times 1$  convolution, the depth-wise dimension can be reduced significantly. It also can be used as an efficient low dimensional embedding or feature pooling. For example, if the original input layer has 512 channels, the  $1 \times 1$  convolution will embed these channels (or features) into a single channel. Figure 2.5 illustrates an example  $1 \times 1$  convolutional layer. The operation is trivial for layers with only one feature map. In this case, every pixel is multiplied by a number. In the example in

Fig. 2.4 Spatial convolution

Fig. 2.5 1-by-1 convolution

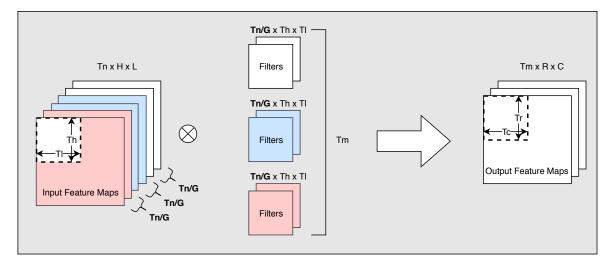

Fig. 2.6 Group convolution

the figure, Tm sets of  $Tn \times 1 \times 1$  filters are applied on a three dimensional input tensor of dimension  $Tn \times H \times L$ . This operation produces an output tensor of size  $Tm \times R \times C$ .

#### 2.4.3 Grouped convolution

Grouped convolution helps to exploit model parallelisation by grouping channels. It was first introduced in AlexNet in 2012 to allow model training over two GPUs with limited memory [57]. In grouped convolution, the filters are separated in multiple groups. Each group is responsible for a conventional spatial convolution with a certain depth. Figure 2.6 illustrates an example layer of a group convolution. In this example, input feature maps are divided into G separate groups. In a similar manner, each set of filters has dimensions of  $Tn/G \times Th \times Tl$  which are applied on the input tensors. This operation produces an output tensor of size  $Tm \times R \times C$ . One of the drawbacks of grouped convolution is a reduction in arithmetic intensity. As input channels are grouped into a small number of sets and they don't interact among different groups, filters are not reused across all the input channels.

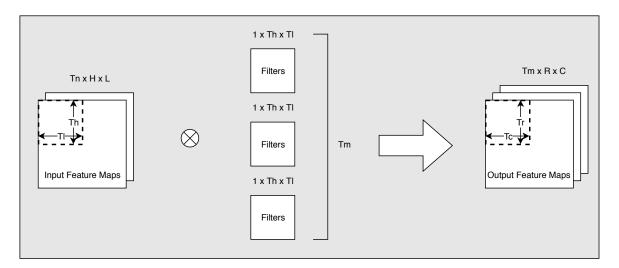

#### 2.4.4 Depth-wise separable convolution

Depth-wise separable convolution became a popular choice with the introduction of MobileNet and Xception [17]. The depth-wise separable convolutions consist of two phases: depth-wise convolutions and  $1 \times 1$  convolutions. I have introduced  $1 \times 1$  convolution earlier (see Figure 2.5). Figure 2.7 illustrates an example of a depth-wise convolution layer. The key property of the depth-wise convolution is that each kernel is applied to only one input channel. In the example, each filter of size  $Th \times Tl$  is applied only on corresponding input channels. This process produces  $Tm \times R \times C$  output maps. As the second phase of depth-wise separable convolution, to extend the depth,  $1 \times 1$  convolution is applied. By separating the spatial convolution into two separate phases, the depth-wise separable convolution reduces the total number of operations. But, this comes at the cost of reduced arithmetic intensity (ops/byte).

### 2.5 Characteristics of convolutional layers

Modern deep ConvNets are dominated by small filters (e.g.  $3 \times 3$ ,  $1 \times 3$  etc.). They are the fundamental building blocks of many widely used ConvNets today. Therefore, optimising convolutions consisting of small kernels would help the overall performance of most models. The next most common filters in use in modern ConvNets are  $1 \times 1$ s. Table 2.3 presents the percentage of small and  $1 \times 1$  kernels present in some of the widely used ConvNets.

Fig. 2.7 Depth-wise convolution

There is no way the computation involved in a  $1 \times 1$  convolution can be reduced further mathematically as it is just a pointwise multiplication between a pixel value and coefficient. I introduced a few other types of convolutional layers earlier. The magnitude of data reuse is defined by a metric called arithmetic intensity. Arithmetic intensity is the ratio between number of operations and memory accesses. The higher the number the more data reuse is possible. Unfortunately, many of the emerging convolution layer architectures do not yield high enough arithmetic intensity. Therefore, although theoretically they need fewer operations, accelerating them on hardware is difficult. Table 2.4 illustrates this point by comparing normalised arithmetic intensity between four widely used convolutional layer architectures. To compute the numbers in this table, it is assumed a generic case with 512 input and output channels. It also assumed that the input image has a dimension of  $14 \times 14$ . The group size is assumed to be 4 in the grouped convolution and 512 in the depth-wise convolution. As can be seen from the table, depth-wise convolution layers have 50 times poorer arithmetic intensity than that of basic spatial convolution.

# 2.6 Data reuse patterns

The diverse layer architectures and sizes of ConvNets result in substantial and varying data movement among the processing cores, on-chip storage and off-chip DRAM. To improve power efficiency an appropriate data-reuse pattern is required for ConvNet. The aim of the data-reuse pattern is to reduce redundant memory access to off-chip DRAM and maximise the utilisation of the already available data. In this section, I introduce the most common and widely used data-reuse patterns for ConvNets.

| ConvNet      | Percentage of 3x3, 5x5,<br>1x3, 1x5, 1x7 kernels | Percentage of 1x1 kernels |

|--------------|--------------------------------------------------|---------------------------|

| VGG16        | 100                                              | 0                         |

| Inception-v3 | 57                                               | 43                        |

| Inception-v4 | 59                                               | 41                        |

| GoogLeNet    | 35                                               | 65                        |

| ResNet50     | 32                                               | 68                        |

| MobileNet    | 7                                                | 93                        |

| SqueezeNet   | 75                                               | 25                        |

| DenseNet     | 50                                               | 50                        |

| Yolo-v3      | 55                                               | 45                        |

Table 2.3 Dominance of small kernels in modern ConvNets

Table 2.4 Arithmetic intensity of different types of convolutional layers

| Convolution Types           | Arithmetic<br>FLOPs<br>(Millions) | Memory Ops<br>Parameters + Activations<br>(Millions) | Arithmetic<br>Intensity<br>(FLOPs/Mem Ops) | Normalised<br>Arithmetic<br>Intensity |

|-----------------------------|-----------------------------------|------------------------------------------------------|--------------------------------------------|---------------------------------------|

| Spatial Convolution (3x3)   | 462                               | 2.56                                                 | 180                                        | 1.0                                   |

| Pointwise Convolution (1x1) | 51                                | 0.463                                                | 110                                        | 0.6                                   |

| Group Convolution           | 116                               | 0.79                                                 | 146                                        | 0.8                                   |

| Depthwise Convolution       | 0.9                               | 0.205                                                | 4.3                                        | 0.02                                  |

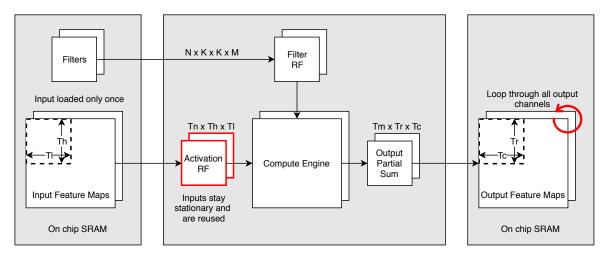

#### 2.6.1 Input stationary (IS)

Input stationary is the first basic data-reuse pattern that requires minimum access to the input feature maps stored in on-chip SRAM. Figure 2.8 illustrates the typical usage of the input tiles for the input stationary data-reuse pattern. The compute engine loads input maps that are necessary to the activation register file (shown in red). These input maps are then fully reused to update all corresponding partial sums stored in the output partial-sum register file. The partial sums are sent back to the output on-chip SRAM buffer. The partial sums are later fetched by the processing engine to continue accumulation in depth when the next input feature map is loaded. Listing 2.2 presents the corresponding loop order for the input stationary data reuse. In the IS reuse pattern, loop N is the outer loop of loop M, meaning each input feature map is fully reused for computation before loading the next feature map.

Fig. 2.8 Input-stationary data-reuse patterns in modern ConvNets

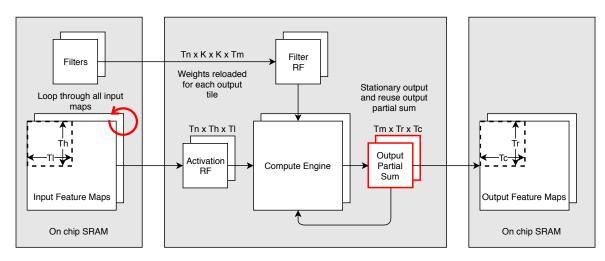

#### 2.6.2 Output stationary (OS):

If the underlying algorithm requires frequent access to the partial sum, then the outputstationary reuse pattern reduces the overall memory accesses to the output feature maps stored in on-chip SRAM. Figure 2.9 illustrates how the output partial sum is reused in the OS reuse pattern. In OS reuse, different input feature maps of the same tile region are successively loaded by the compute engine. The partial sums in the output register files are reused until all the corresponding input feature maps are completed (shown in red). The final output activations are stored back to the on-chip SRAM and no further access is required. Any algorithms that require inverse transforms may benefit from the OS data-reuse pattern. Listing 2.3 presents the corresponding loop order for the output-stationary data-reuse. In OS

Fig. 2.9 Output-stationary data-reuse patterns in modern ConvNets

Fig. 2.10 Weight-stationary data-reuse patterns in modern ConvNets

Fig. 2.11 Row-stationary data-reuse patterns in modern ConvNets

reuse pattern, loop M is the outer loop of loop N, meaning each output feature map is fully reused for computation before loading the next target output map.

```

for (r = 0; r < R; r += Tr)

for (c = 0; c < C; c += Tc)

for (n = 0; n < N; n += Tn)

for (m = 0; m < M; m += Tm)

{/* Inside the compute engine */

for (tm = m; tm < min(m + Tm, M); tm++)

for (tn = n; tn < min(n + Tn, N); tn++)

for (tr = r; tr < min(r + Tr, R); tr++)

for (tc = c; tc < min(c + Tc); tc++)

for (i = 0; i < K; i++)

for (j = 0; j < K; j++) {

Out[tm][tr][tc] += W[tm][tn][i][j]*X[tn][tr*S+i][tc*S+j];

}/* End of single run inside the compute engine*/</pre>

```

Listing 2.2 Input-stationary data-reuse pattern

```

for (r = 0; r < R; r += Tr)

for (c = 0; c < C; c += Tc)

for (m = 0; m < M; m += Tm)

for (n = 0; n < N; n += Tn)

{/* Inside the compute engine */

for (tm = m; tm < min(m + Tm, M); tm++)

for (tn = n; tn < min(n + Tn, N); tn++)

for (tr = r; tr < min(r + Tr, R); tr++)

for (tc = c; tc < min(c + Tc); tc++)

for (i = 0; i < K; i++)

for (j = 0; j < K; j++) {

Out[tm][tr][tc] += W[tm][tn][i][j]*X[tn][tr*S+i][tc*S+j];

}

}/* End of single run inside the compute engine*/</pre>

```

Listing 2.3 Output-stationary data-reuse pattern

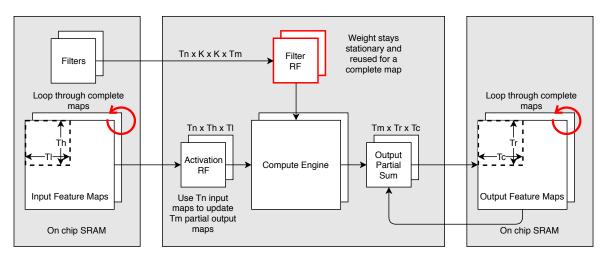

# 2.6.3 Weight stationary (WS):

In both input-stationary and output-stationary reuse patterns, repeated weight access to off-chip DRAM would be necessary if the total number of required parameters exceeds the filter buffer size in the on-chip SRAM. In these cases the weight-stationary data-reuse pattern would minimise off-chip accesses due to a lack of on-chip space for the parameters. Figure 2.10 illustrates the typical reuse pattern of weight-stationary computing. The compute

engine loads Tn tiled input feature maps to the activation register file. These input feature maps are used to compute Tm output target maps. The  $Tn \times Tm$  filter weights in the filter register file are reused to compute Tm target output maps. Listing 2.3 presents the corresponding loop order for weight-stationary data reuse. In the WS reuse pattern, both the loop M and loop N are switched to the outer-most loops to maximise the reuse of the filter parameters.

```

for (m = 0; m < M; m += Tm)

for (n = 0; n < N; n += Tn)

for (r = 0; r < R; r += Tr)

for (c = 0; c < C; c += Tc)

{/* Inside the compute engine */

for (tm = m; tm < min(m + Tm, M); tm++)

for (tn = n; tn < min(n + Tn, N); tn++)

for (tr = r; tr < min(r + Tr, R); tr++)

for (tc = c; tc < min(c + Tc); tc++)

for (i = 0; i < K; i++)

for (j = 0; j < K; j++) {

Out[tm][tr][tc] += W[tm][tn][i][j]*X[tn][tr*S+i][tc*S+j];

}/* End of single run inside the compute engine*/</pre>

```

Listing 2.4 Weight-stationary data-reuse pattern

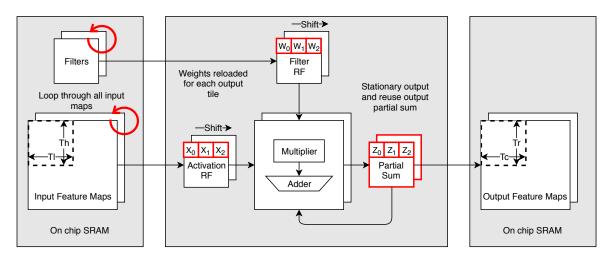

### 2.6.4 Row stationary (RS):

The row-stationary data-reuse pattern was introduced in the Eyeriss system by reducing the size of the local register file [15]. By reducing the size of the local registers the RS data-reuse pattern helped the Eyeriss system to achieve an additional 25% energy savings. Figure 2.11 illustrates the row-stationary data-reuse pattern. The RS reuse pattern divides the MAC (multiply-accumulate) units into mapping primitives. Each mapping primitive performs a 1D (one-dimensional) row convolution in this setting. The row-stationary reuse pattern also exploits partial-sum reuse as in output stationary data-reuse pattern described earlier. The compute engine loads a row of filter weights and applies them to a row of input feature maps. This process generates a row of partial sums as shown in the figure.

### 2.6.5 On-chip interconnect for varying reuse and flexibility

The complexity of the on-chip interconnect depends on the level of data reuse supported by the hardware. In order to build a flexible accelerator the design must be able to adapt to a wide range of bandwidth requirements. When data reuse is low, a unicast network can

Fig. 2.12 Trade-off between on-chip interconnect complexity and spatial reuse. (a) Unicast network, (b) Broadcast network

provide high bandwidth from the memory and can keep the cores busy. However, when data reuse is high, the interconnect must support multicast or broadcast to exploit spatial data reuse. This helps to improve energy efficiency and processing array (or core) utilisation [86]. If the hardware is not required to support high reuse, then unicast is sufficient. Figure 2.12 shows these two extreme cases side-by-side as a comparison. Ideally to support any type of data-reuse pattern, an all-to-all interconnect is needed. But, for a realistic system this is very expensive and often not scalable. Therefore a trade-off is required between the amount of data-reuse necessary and the complexity of the interconnect that can be supported in the hardware.

# 2.7 A survey of prior research on optimising ConvNets

Recent research on ConvNets has focused primarily on improving accuracy. As more and more companies try to deploy deep-learning in their products and services, in the last couple of years, attention started to shift towards efficient implementation. There has been some fragmented research work conducted in both the machine learning and computer architecture communities to reduce the size and complexity of a ConvNet such that the overall storage and computation requirements can be reduced. In this section, I will highlight some of these initial research efforts.

### 2.7.1 Pruning, sparse Networks and regularisation

Model pruning has been the most widely studied topic among the various model optimisation techniques. Pruning introduces sparsity in the model, which can be exploited in the low level implementation. In an early work LeCun et al. [21] proposed pruning as an effective method to reduce over-fitting. Recently, Srivastava et al. proposed Dropout [85], a new technique to address the problem of over-fitting, which helps pruning models over time during the training process. The key idea in Dropout is to randomly drop activations along their connections from models during training. This prevents units from co-adapting too much. Today, Dropout is very common and believed to be one of the best methods for regularisation. While in Dropout a randomly selected subset of activations are set to zero, in DropConnect [95] a randomly selected subset of weights are set to zero. Dropconnect is a generalisation of dropout for regularising fully-connected layers. Goodfellow et al. proposed a new activation function called Maxout [35] that is particularly well-suited for training with Dropout, and they have shown Maxout improves accuracy of Dropout by exploiting model averaging behaviour. A more mathematically grounded work by Denton et al. showed how singular value decomposition (SVD) [24] can be used on a pre-trained network to speed up the bottleneck convolution operations in the first few layers with very negligible loss of performance. Their method also reduces the memory footprint of weights in the first two layers by 2-3x and the fully-connected layers by a factor of 5-13x.

In **ElasticNet** [101], Zou et al. proposed a novel shrinkage and selection method which produces a sparse model with good prediction accuracy. In this method, the authors use a complex cost function to train a model which consists of a  $l_1$  penalty part and a quadratic part which encourages a grouping effect. Han et al. developed **Deep Compression** [40], a heuristic-based pruning technique, which begins with a pre-trained model, and then replaces weights that are below a certain threshold with zeros to form a sparse matrix. If the accuracy drops significantly, then they re-train the network with a few iterations to gain back the accuracy. Liu et al. [64] proposed the **Sparse Convolutional Neural Networks (SCNN)** model that exploits both inter-channel and intra-channel redundancy to maximise sparsity in a model. This procedure zeros out more than 90% of parameters, with a drop in accuracy less than 1% on ImageNet dataset. The authors also propose an efficient sparse matrix multiplication algorithm on CPU to further accelerate the optimised model.

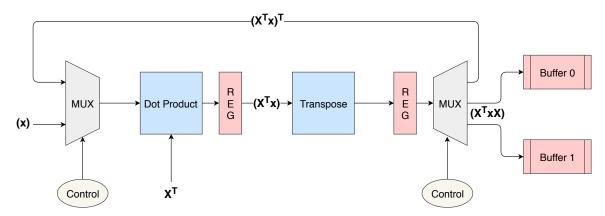

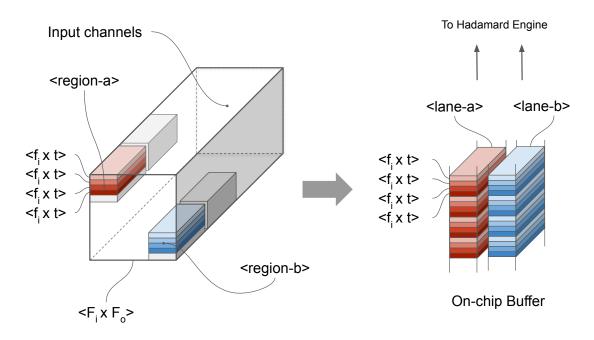

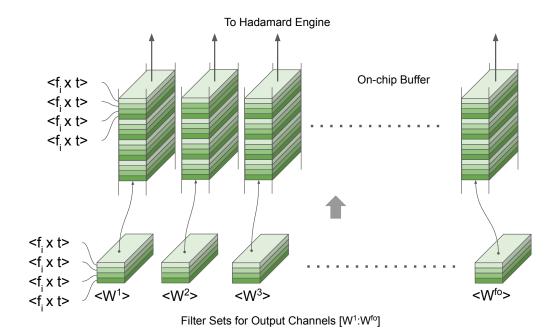

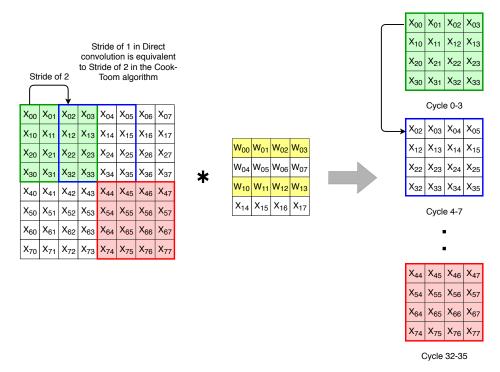

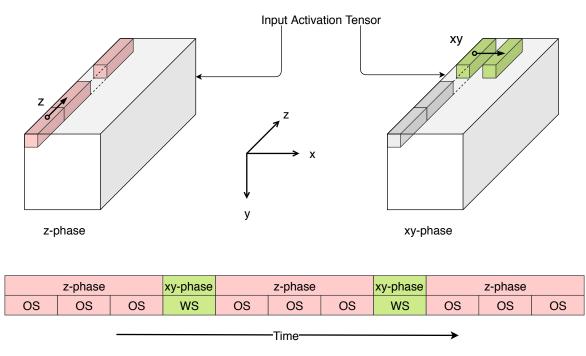

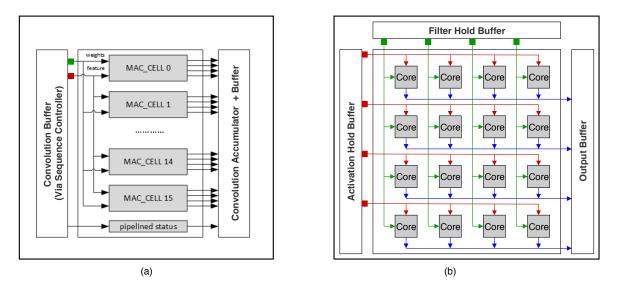

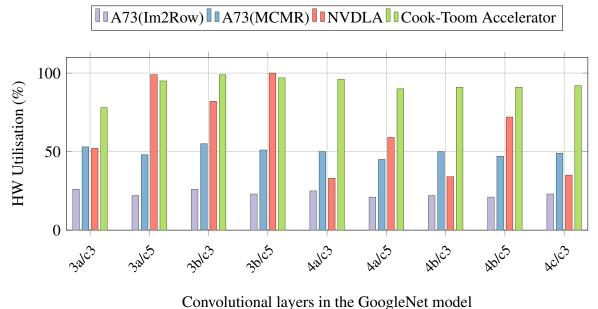

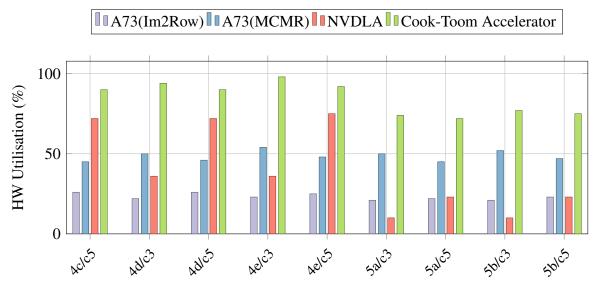

### 2.7.2 Model simplification and separable layers