## **THESIS / THÈSE**

MASTER IN COMPUTER SCIENCE

Computer-Aided Reasoning for Product-Line Model Checking

Dawagne, Bruno

Award date: 2014

Awarding institution: University of Namur

Link to publication

General rights Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal ?

#### Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

UNIVERSITÉ DE NAMUR Faculté d'informatique Année académique 2013–2014

### Computer-Aided Reasoning for Product-Line Model Checking

Bruno Dawagne

Maître de stage : Vijay Ganesh

| Promoteur : |                 | _ (Signature pour | approbation | du dépôt - | · REE art. | 40) |

|-------------|-----------------|-------------------|-------------|------------|------------|-----|

|             | Patrick Heymans |                   |             |            |            |     |

Co-promoteur : Maxime Cordy

Mémoire présenté en vue de l'obtention du grade de Master en Sciences Informatiques.

#### Acknowledgements

I would like to thank Prof. Patrick Heymans for all the opportunities he gave me. I would also like to thank Maxime Cordy for all his support and the time he took helping me through the redaction of this master thesis. Finally, I would like to thank Prof. Vijay Ganesh for its guidance and valuable advice.

## Contents

| ITheoretical Background61The Satisfiability Problem71.1Boolean Functions and Satisfiability Problem71.2Normal forms81.2.1Negation Normal Form81.2.2Conjunctive Normal Form91.2.3Disjunctive Normal Form101.3Satisfiability over CNF111.3.1The DPLL Algorithm111.3.2The CDCL Algorithm131.4Binary Decision Diagrams181.4.1Principles and Canonicity181.4.2Operations on BDD's212Satisfiability Modulo Theories232.1First-Order Logic232.1.1Syntax And Semantics232.2.2Theories262.3Common Theories262.3Common Theories262.3.1Theory of Equality with Uninterpreted Functions262.3.2Preato arithmetic272.3.3Peano arithmetic272.3.3Peano arithmetic282.4.1The Eager Approach292.4.3The DPLL(T) Architecture303Software Product Line Model Checking313.1.1Program Graphs and Transition Systems313.1.2Linear Time Properties and Temporal Logic343.1.3Büchi Automata353.1.4Verifying $\omega$ -ergular Properties37                                                                                                                                                                                                                                                                                                     | In | trod                       | uction                                       | 3  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----------------------------|----------------------------------------------|----|--|

| 1.1       Boolean Functions and Satisfiability Problem       7         1.2       Normal forms       8         1.2.1       Negation Normal Form       8         1.2.2       Conjunctive Normal Form       9         1.2.3       Disjunctive Normal Form       10         1.3       Satisfiability over CNF       11         1.3.1       The DPLL Algorithm       11         1.3.2       The CDCL Algorithm       13         1.4       Binary Decision Diagrams       18         1.4.1       Principles and Canonicity       18         1.4.2       Operations on BDD's       21 <b>2</b> Satisfiability Modulo Theories       23         2.1       First-Order Logic       23         2.1.1       Syntax And Semantics       23         2.1.2       The Satisfiability Problem       25         2.2       Theories       26         2.3       Common Theories       26         2.3       Presburger Arithmetic       27         2.3.3       Peano arithmetic       27         2.3.3       Peano arithmetic       28         2.4       SMT Solvers       28         2.4.1       The Eager Approach       2                                                                                                             | Ι  | Tł                         | neoretical Background                        | 6  |  |

| 1.2       Normal forms       8         1.2.1       Negation Normal Form       8         1.2.2       Conjunctive Normal Form       9         1.2.3       Disjunctive Normal Form       10         1.3       Satisfability over CNF       11         1.3.1       The DPLL Algorithm       11         1.3.2       The CDCL Algorithm       13         1.4       Binary Decision Diagrams       18         1.4.1       Principles and Canonicity       18         1.4.2       Operations on BDD's       21         2       Satisfiability Modulo Theories       23         2.1       First-Order Logic       23         2.1.1       Syntax And Semantics       23         2.1.2       The Satisfiability Problem       25         2.2       Theories       26         2.3       Common Theories       26         2.3.1       Theory of Equality with Uninterpreted Functions       26         2.3.2       Presburger Arithmetic       27         2.3.3       Peano arithmetic       28         2.4.3       The Eager Approach       28         2.4.1       The Eager Approach       28         2.4.2       The Lazy Approach </th <th>1</th> <th colspan="3">The Satisfiability Problem</th>                             | 1  | The Satisfiability Problem |                                              |    |  |

| 1.2.1       Negation Normal Form       8         1.2.2       Conjunctive Normal Form       9         1.2.3       Disjunctive Normal Form       10         1.3       Satisfiability over CNF       11         1.3.1       The DPLL Algorithm       11         1.3.2       The CDCL Algorithm       13         1.4       Binary Decision Diagrams       18         1.4.1       Principles and Canonicity       18         1.4.2       Operations on BDD's       21 <b>2</b> Satisfiability Modulo Theories       23         2.1       First-Order Logic       23         2.1.1       Syntax And Semantics       23         2.1.2       The Satisfiability Problem       25         2.2       Theories       26         2.3       Common Theories       26         2.4       Theory of Equality with Uninterpreted Functions       26         2.3.1       Theory of Equality with Uninterpreted Functions       26         2.3.3       Peano arithmetic       27         2.3.3       Peano arithmetic       28         2.4.1       The Eager Approach       28         2.4.2       The Lazy Approach       29         2.4.3 </th <th></th> <th>1.1</th> <th>Boolean Functions and Satisfiability Problem</th> <th></th> |    | 1.1                        | Boolean Functions and Satisfiability Problem |    |  |

| 1.2.2       Conjunctive Normal Form       9         1.2.3       Disjunctive Normal Form       10         1.3       Satisfiability over CNF       11         1.3.1       The DPLL Algorithm       11         1.3.2       The CDCL Algorithm       13         1.4       Binary Decision Diagrams       18         1.4.1       Principles and Canonicity       18         1.4.2       Operations on BDD's       21         2       Satisfiability Modulo Theories       23         2.1       First-Order Logic       23         2.1.1       Syntax And Semantics       23         2.1.2       The Satisfiability Problem       25         2.2       Theories       26         2.3       Common Theories       26         2.4       Theory of Equality with Uninterpreted Functions       26         2.3.1       Theory of Equality with Uninterpreted Functions       26         2.3.2       Presburger Arithmetic       27         2.3.3       Peano arithmetic       28         2.4       SMT Solvers       28         2.4.1       The Eager Approach       28         2.4.2       The Lazy Approach       29         2.4.3                                                                                           |    | 1.2                        | Normal forms                                 |    |  |

| 1.2.3 Disjunctive Normal Form       10         1.3 Satisfiability over CNF       11         1.3.1 The DPLL Algorithm       11         1.3.2 The CDCL Algorithm       13         1.4 Binary Decision Diagrams       18         1.4.1 Principles and Canonicity       18         1.4.2 Operations on BDD's       21         2 Satisfiability Modulo Theories       23         2.1 First-Order Logic       23         2.1.1 Syntax And Semantics       23         2.1.2 The Satisfiability Problem       25         2.2 Theories       26         2.3 Common Theories       26         2.3.1 Theory of Equality with Uninterpreted Functions       26         2.3.2 Presburger Arithmetic       27         2.3.3 Peano arithmetic       28         2.4 SMT Solvers       28         2.4.1 The Eager Approach       29         2.4.3 The DPLL(T) Architecture       30         3 Software Product Line Model Checking       31         3.1.1 Program Graphs and Transition Systems       31         3.1.2 Linear Time Properties and Temporal Logic       34         3.1.3 Büchi Automata       35                                                                                                                       |    |                            | 1.2.1 Negation Normal Form                   |    |  |

| 1.3       Satisfiability over CNF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |                            | 1.2.2 Conjunctive Normal Form                | 9  |  |

| 1.3.1The DPLL Algorithm111.3.2The CDCL Algorithm131.4Binary Decision Diagrams181.4.1Principles and Canonicity181.4.2Operations on BDD's212Satisfiability Modulo Theories232.1First-Order Logic232.1.1Syntax And Semantics232.1.2The Satisfiability Problem252.2Theories262.3Common Theories262.3.1Theory of Equality with Uninterpreted Functions262.3.2Presburger Arithmetic272.3.3Peano arithmetic282.4SMT Solvers282.4.2The Lazy Approach292.4.3The DPLL(T) Architecture303Software Product Line Model Checking313.1.1Program Graphs and Transition Systems313.1.2Linear Time Properties and Temporal Logic343.1.3Büchi Automata35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |                            | 1.2.3 Disjunctive Normal Form                | 10 |  |

| 1.3.2       The CDCL Algorithm       13         1.4       Binary Decision Diagrams       18         1.4.1       Principles and Canonicity       18         1.4.2       Operations on BDD's       21         2       Satisfiability Modulo Theories       23         2.1       First-Order Logic       23         2.1.1       Syntax And Semantics       23         2.1.2       The Satisfiability Problem       25         2.2       Theories       26         2.3       Common Theories       26         2.3.1       Theory of Equality with Uninterpreted Functions       26         2.3.2       Presburger Arithmetic       27         2.3.3       Peano arithmetic       28         2.4.1       The Eager Approach       28         2.4.2       The Lazy Approach       29         2.4.3       The DPLL(T) Architecture       30         3       Software Product Line Model Checking       31         3.1.1       Program Graphs and Transition Systems       31         3.1.2       Linear Time Properties and Temporal Logic       34         3.1.3       Büchi Automata       35                                                                                                                             |    | 1.3                        | Satisfiability over CNF                      | 11 |  |

| 1.4Binary Decision Diagrams181.4.1Principles and Canonicity181.4.2Operations on BDD's212Satisfiability Modulo Theories232.1First-Order Logic232.1.1Syntax And Semantics232.1.2The Satisfiability Problem252.2Theories262.3Common Theories262.4Theory of Equality with Uninterpreted Functions262.3.2Presburger Arithmetic272.3.3Peano arithmetic282.4SMT Solvers282.4.1The Eager Approach292.4.3The DPLL(T) Architecture303Software Product Line Model Checking313.1.1Program Graphs and Transition Systems313.1.2Linear Time Properties and Temporal Logic343.1.3Büchi Automata35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |                            |                                              |    |  |

| 1.4.1Principles and Canonicity181.4.2Operations on BDD's212Satisfiability Modulo Theories232.1First-Order Logic232.1.1Syntax And Semantics232.1.2The Satisfiability Problem252.2Theories262.3Common Theories262.3.1Theory of Equality with Uninterpreted Functions262.3.2Presburger Arithmetic272.3.3Peano arithmetic282.4.1The Eager Approach282.4.2The Lazy Approach292.4.3The DPLL(T) Architecture303Software Product Line Model Checking313.1.1Program Graphs and Transition Systems313.1.2Linear Time Properties and Temporal Logic343.1.3Büchi Automata35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |                            | 1.3.2 The CDCL Algorithm                     | 13 |  |

| 1.4.2       Operations on BDD's       21         2       Satisfiability Modulo Theories       23         2.1       First-Order Logic       23         2.1.1       Syntax And Semantics       23         2.1.2       The Satisfiability Problem       25         2.2       Theories       26         2.3       Common Theories       26         2.3.1       Theory of Equality with Uninterpreted Functions       26         2.3.2       Presburger Arithmetic       27         2.3.3       Peano arithmetic       28         2.4       SMT Solvers       28         2.4.1       The Eager Approach       28         2.4.2       The Lazy Approach       29         2.4.3       The DPLL(T) Architecture       30         3       Software Product Line Model Checking       31         3.1.1       Program Graphs and Transition Systems       31         3.1.2       Linear Time Properties and Temporal Logic       34         3.1.3       Büchi Automata       35                                                                                                                                                                                                                                                 |    | 1.4                        | Binary Decision Diagrams                     | 18 |  |

| 2 Satisfiability Modulo Theories       23         2.1 First-Order Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |                            | 1.4.1 Principles and Canonicity              | 18 |  |

| 2.1       First-Order Logic       23         2.1.1       Syntax And Semantics       23         2.1.2       The Satisfiability Problem       25         2.2       Theories       26         2.3       Common Theories       26         2.3.1       Theory of Equality with Uninterpreted Functions       26         2.3.1       Theory of Equality with Uninterpreted Functions       26         2.3.2       Presburger Arithmetic       27         2.3.3       Peano arithmetic       28         2.4       SMT Solvers       28         2.4.1       The Eager Approach       29         2.4.2       The Lazy Approach       29         2.4.3       The DPLL(T) Architecture       30         3       Software Product Line Model Checking       31         3.1       LTL Model Checking       31         3.1.1       Program Graphs and Transition Systems       31         3.1.2       Linear Time Properties and Temporal Logic       34         3.1.3       Büchi Automata       35                                                                                                                                                                                                                               |    |                            | 1.4.2 Operations on BDD's                    | 21 |  |

| 2.1       First-Order Logic       23         2.1.1       Syntax And Semantics       23         2.1.2       The Satisfiability Problem       25         2.2       Theories       26         2.3       Common Theories       26         2.3.1       Theory of Equality with Uninterpreted Functions       26         2.3.1       Theory of Equality with Uninterpreted Functions       26         2.3.2       Presburger Arithmetic       27         2.3.3       Peano arithmetic       28         2.4       SMT Solvers       28         2.4.1       The Eager Approach       29         2.4.2       The Lazy Approach       29         2.4.3       The DPLL(T) Architecture       30         3       Software Product Line Model Checking       31         3.1       LTL Model Checking       31         3.1.1       Program Graphs and Transition Systems       31         3.1.2       Linear Time Properties and Temporal Logic       34         3.1.3       Büchi Automata       35                                                                                                                                                                                                                               | 2  | Sat                        | isfiability Modulo Theories                  | 23 |  |

| 2.1.1       Syntax And Semantics       23         2.1.2       The Satisfiability Problem       25         2.2       Theories       26         2.3       Common Theories       26         2.3.1       Theory of Equality with Uninterpreted Functions       26         2.3.2       Presburger Arithmetic       27         2.3.3       Peano arithmetic       27         2.3.3       Peano arithmetic       28         2.4       SMT Solvers       28         2.4.1       The Eager Approach       28         2.4.2       The Lazy Approach       29         2.4.3       The DPLL(T) Architecture       30         3       Software Product Line Model Checking       31         3.1       I.TL Model Checking       31         3.1.1       Program Graphs and Transition Systems       31         3.1.2       Linear Time Properties and Temporal Logic       34         3.1.3       Büchi Automata       35                                                                                                                                                                                                                                                                                                          | _  |                            | 0                                            |    |  |

| 2.1.2The Satisfiability Problem252.2Theories262.3Common Theories262.3.1Theory of Equality with Uninterpreted Functions262.3.2Presburger Arithmetic272.3.3Peano arithmetic272.3.3Peano arithmetic282.4SMT Solvers282.4.1The Eager Approach282.4.2The Lazy Approach292.4.3The DPLL(T) Architecture303Software Product Line Model Checking313.1LTL Model Checking313.1.2Linear Time Properties and Temporal Logic343.1.3Büchi Automata35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |                            |                                              |    |  |

| 2.2       Theories       26         2.3       Common Theories       26         2.3.1       Theory of Equality with Uninterpreted Functions       26         2.3.2       Presburger Arithmetic       27         2.3.3       Peano arithmetic       27         2.3.3       Peano arithmetic       28         2.4       SMT Solvers       28         2.4.1       The Eager Approach       28         2.4.2       The Lazy Approach       29         2.4.3       The DPLL(T) Architecture       30         3       Software Product Line Model Checking       31         3.1       LTL Model Checking       31         3.1.1       Program Graphs and Transition Systems       31         3.1.2       Linear Time Properties and Temporal Logic       34         3.1.3       Büchi Automata       35                                                                                                                                                                                                                                                                                                                                                                                                                     |    |                            |                                              |    |  |

| 2.3       Common Theories       26         2.3.1       Theory of Equality with Uninterpreted Functions       26         2.3.2       Presburger Arithmetic       27         2.3.3       Peano arithmetic       28         2.4       SMT Solvers       28         2.4.1       The Eager Approach       28         2.4.2       The Lazy Approach       29         2.4.3       The DPLL(T) Architecture       30         3       Software Product Line Model Checking       31         3.1       LTL Model Checking       31         3.1.1       Program Graphs and Transition Systems       31         3.1.2       Linear Time Properties and Temporal Logic       34         3.1.3       Büchi Automata       35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    | 2.2                        | •                                            |    |  |

| 2.3.1       Theory of Equality with Uninterpreted Functions       26         2.3.2       Presburger Arithmetic       27         2.3.3       Peano arithmetic       28         2.4       SMT Solvers       28         2.4.1       The Eager Approach       28         2.4.2       The Lazy Approach       29         2.4.3       The DPLL(T) Architecture       30         3       Software Product Line Model Checking       31         3.1       LTL Model Checking       31         3.1.1       Program Graphs and Transition Systems       31         3.1.2       Linear Time Properties and Temporal Logic       34         3.1.3       Büchi Automata       35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    | 2.3                        | Common Theories                              |    |  |

| 2.3.2       Presburger Arithmetic       27         2.3.3       Peano arithmetic       28         2.4       SMT Solvers       28         2.4.1       The Eager Approach       28         2.4.2       The Lazy Approach       29         2.4.3       The DPLL(T) Architecture       30         3       Software Product Line Model Checking       31         3.1       LTL Model Checking       31         3.1.1       Program Graphs and Transition Systems       31         3.1.2       Linear Time Properties and Temporal Logic       34         3.1.3       Büchi Automata       35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |                            |                                              | -  |  |

| 2.3.3       Peano arithmetic       28         2.4       SMT Solvers       28         2.4.1       The Eager Approach       28         2.4.2       The Lazy Approach       29         2.4.3       The DPLL(T) Architecture       30         3       Software Product Line Model Checking       31         3.1       LTL Model Checking       31         3.1.1       Program Graphs and Transition Systems       31         3.1.2       Linear Time Properties and Temporal Logic       34         3.1.3       Büchi Automata       35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |                            |                                              |    |  |

| 2.4       SMT Solvers       28         2.4.1       The Eager Approach       28         2.4.2       The Lazy Approach       29         2.4.3       The DPLL(T) Architecture       30         3       Software Product Line Model Checking       31         3.1       LTL Model Checking       31         3.1.1       Program Graphs and Transition Systems       31         3.1.2       Linear Time Properties and Temporal Logic       34         3.1.3       Büchi Automata       35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |                            | 0                                            | 28 |  |

| 2.4.1       The Eager Approach       28         2.4.2       The Lazy Approach       29         2.4.3       The DPLL(T) Architecture       30         3       Software Product Line Model Checking       31         3.1       LTL Model Checking       31         3.1.1       Program Graphs and Transition Systems       31         3.1.2       Linear Time Properties and Temporal Logic       34         3.1.3       Büchi Automata       35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    | 2.4                        |                                              | 28 |  |

| 2.4.2       The Lazy Approach       29         2.4.3       The DPLL(T) Architecture       30         3       Software Product Line Model Checking       31         3.1       LTL Model Checking       31         3.1.1       Program Graphs and Transition Systems       31         3.1.2       Linear Time Properties and Temporal Logic       34         3.1.3       Büchi Automata       35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |                            | 2.4.1 The Eager Approach                     |    |  |

| 2.4.3       The DPLL(T) Architecture       30         3       Software Product Line Model Checking       31         3.1       LTL Model Checking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |                            | 0 11                                         | 29 |  |

| 3.1LTL Model Checking313.1.1Program Graphs and Transition Systems313.1.2Linear Time Properties and Temporal Logic343.1.3Büchi Automata35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |                            | • ==                                         | 30 |  |

| 3.1LTL Model Checking313.1.1Program Graphs and Transition Systems313.1.2Linear Time Properties and Temporal Logic343.1.3Büchi Automata35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3  | Sof                        | tware Product Line Model Checking            | 31 |  |

| 3.1.1Program Graphs and Transition Systems313.1.2Linear Time Properties and Temporal Logic343.1.3Büchi Automata35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0  |                            |                                              |    |  |

| 3.1.2Linear Time Properties and Temporal Logic343.1.3Büchi Automata35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    | 0.1                        | •                                            |    |  |

| 3.1.3 Büchi Automata                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |                            |                                              |    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |                            |                                              |    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |                            |                                              |    |  |

|          | 3.2          | Product Lines and Feature Diagrams |                                                                    |            |  |  |

|----------|--------------|------------------------------------|--------------------------------------------------------------------|------------|--|--|

|          | 3.3          | 3 Product Line Model Checking      |                                                                    |            |  |  |

|          |              | 3.3.1                              | Featured Program Graphs and Transition Systems                     | 41         |  |  |

|          |              | 3.3.2                              | Verifying $\omega$ -regular Properties on Featured Transition Sys- |            |  |  |

|          |              |                                    | tem                                                                | 43         |  |  |

|          |              | 3.3.3                              | SNIP                                                               | 45         |  |  |

|          |              | 3.3.4                              | ProVeLines 2                                                       | 48         |  |  |

|          | 3.4          | Objec                              | tives                                                              | 48         |  |  |

| II       | $\mathbf{C}$ | ontril                             | bution                                                             | 50         |  |  |

| 4        |              |                                    | ntegration of a SAT Solver into ProVeLines                         | 51         |  |  |

|          | 4.1          |                                    | e Production                                                       | 51         |  |  |

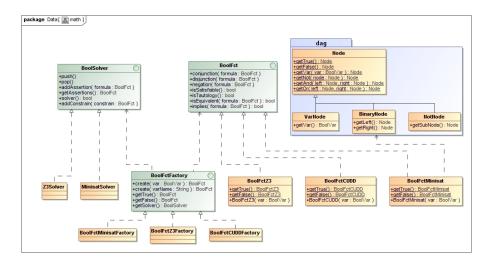

|          |              | 4.1.1                              | Tree Representation of Boolean Formulas                            | 51         |  |  |

|          |              | 4.1.2                              | Conversion into Equivalent CNF                                     |            |  |  |

|          |              | 4.1.3                              | Equisatisfiability and Tseitin Transformation                      |            |  |  |

|          |              | 4.1.4                              | Graph Representation of Boolean Formulas                           |            |  |  |

|          |              | 4.1.5                              | Cache Mechanism                                                    | 57         |  |  |

|          | 4.2          |                                    | nental Solving                                                     | 60         |  |  |

|          |              | 4.2.1                              | Principle of Incremental Solving                                   | 60         |  |  |

|          |              | 4.2.2                              | Solving Under Assumptions                                          | 61         |  |  |

|          |              | 4.2.3                              | Incremental Algorithms                                             | 62         |  |  |

|          |              | 4.2.4                              | SMT Solvers and Incremental Solving                                | 62         |  |  |

| <b>5</b> | -            |                                    | ntal Results                                                       | 67         |  |  |

|          | 5.1          | -                                  | mentation                                                          | 67         |  |  |

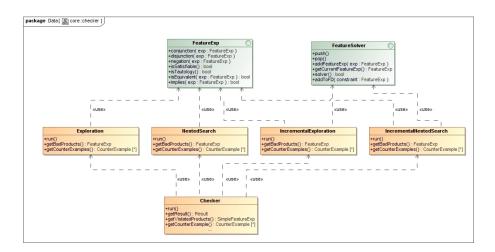

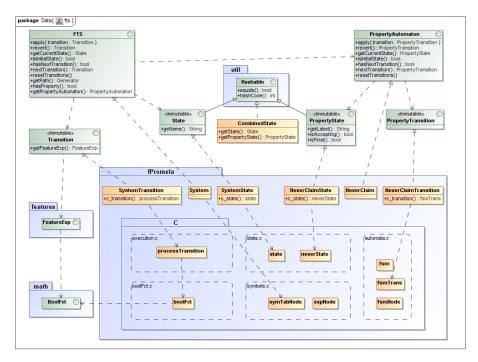

|          |              | 5.1.1                              | Integrating SAT and SMT solvers                                    | 67         |  |  |

|          |              | 5.1.2                              | Integrating fPromela in ProVeLines 2                               | $68 \\ 71$ |  |  |

|          | 5.2          | 1                                  |                                                                    |            |  |  |

|          |              | 5.2.1                              | Minisat-based Configurations                                       |            |  |  |

|          |              | 5.2.2                              | Z3-based Configurations                                            | 72         |  |  |

|          |              | 5.2.3                              | Observations                                                       | 73         |  |  |

|          |              | 5.2.4                              | Limitation                                                         | 73         |  |  |

| Co       | onclu        | sion                               |                                                                    | 75         |  |  |

### Introduction

A software system is considered correct if it meets its design requirements. In the case of a distributed software, made of several processes working together, it is not always easy, or even practically possible, to verify that the system matches its functional requirements. The most common approach to ensure its correctness is testing. Tests can be realized on several abstraction levels: Unit tests verify the correctness of individual modules, integration tests check their proper cooperation and acceptance tests validate the functionalities of the complete system with respect to the end user's expectations. However, even with an high test coverage, some bugs can survive. Errors like race conditions and deadlocks are sometime hard to detect. They might for instance be triggered due to the scheduling policy of the running operating system. In this case, they might not even be reproducible on another platform.

Model checking is a formal verification technique that can, in some way, prove the absence of mistakes. It requires two inputs: A behavioral specification of the software system and a property in temporal logic. In return, a model checker yields an example of execution of the system that violates the property, or the certainty that no such execution exists. As one may expect, modeling a distributed system is a critical step. The behavioral model should indeed include all the information needed to decide on its correctness, as the communication sequences between processes, and avoid computation details, as the complete processing of the exchanged messages.

Model-checking tools have been applied with success in thousands of projects [Hol04]. For instance, they can prove the validity of mutual exclusion algorithms, such as Peterson's Algorithm. Before the appearance of model checking, proving or disproving such algorithm could lead to long and ponderous hand-written proofs. Now, concrete models of these algorithms can be checked against several temporal properties. This set of properties can include the effectiveness of mutual exclusion, i.e. that only one process at a time can enter a critical section, the absence of deadlocks or the fairness between processes induced by the verified algorithm.

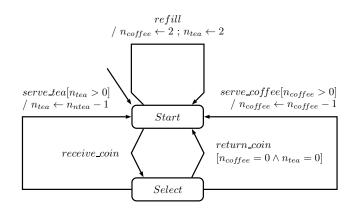

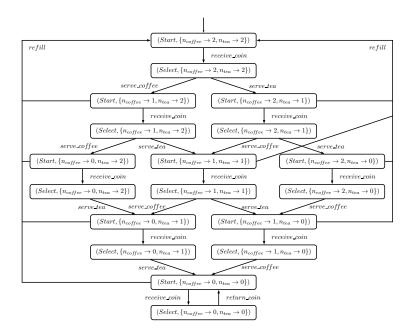

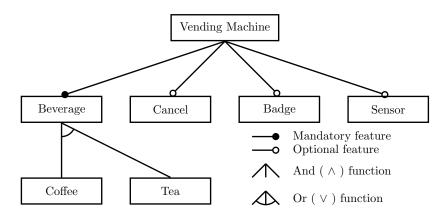

A limitation of model checking is that it only allows one to verify the correctness of one single product. A modern approach when building software systems is however to create a set of strongly correlated products called a product line. Variants of a product line share common pieces or behaviors, and are built from a common, managed set of assets. Reusing core assets from one product to another allows one to benefit from economies of scale when developing a large number of products. A software product line is a product line of software-intensive systems. The variability that can take place in a product line is usually expressed in terms of features. Simply said, a feature is an asset that can be included in a product and be missing in another. It usually defines some set of additional functionalities that can be inserted to a specific product to enhance it, or retrieved from another for incompatibility, economical or even simplicity reasons. Developing a software product line is like developing a highly configurable software system in which features can be activated or deactivated depending on the target's needs or specificities. Relations between features, as dependencies or incompatibilities, are usually expressed in a feature diagram.

Verifying properties on a software product line requires to specify the behavior of every single product of the product line and to verify them individually. However, the number of variants in a product line tends to grow exponentially with the number of features. Therefore, verifying products individually may require a huge amount of time and be unfeasible in practice. To workaround this, researchers from the University of Namur have adapted model-checking algorithms to software product lines. The process requires three inputs: A behavioral specification of the software product line, the feature diagram representing the variability of this product line, and a temporal property. In return, it yields the set of products that violate the property or the certainty that no such product exists. It also delivers an example of execution violating the property for each concerned product. The proposed algorithms have been implemented in a tool, named ProVeLines.

The aforementioned algorithms work as follows. The state-space of the product line is explored starting an initial state and following a nested depth-first search. On the other hand, the set of products that are actually able to go through a particular path is represented using boolean formulas. In order to avoid the verification of non existing products, these boolean formulas are often checked for satisfiability.

The boolean satisfiability problem is arguably the most famous example of NP-complete problem. Different algorithms and techniques have been proposed to solve it. In ProVeLines, the retained approach is to represent boolean formulas using Binary Decision Diagrams (BDDs). However, ProVeLines has recently been extended to support, in addition to standard boolean features, two additional types that are intensively used in practice: multi-features, i.e. features that may appear several times in a given product, and numeric features. The former entails changes only to the semantics of feature diagrams. The latter, however, also raises the need for non boolean expressions. To this end, an SMT solver has been integrated into ProVeLines to replace the BDD implementation.

SMT solvers are somehow the result of centuries of history in automated reasoning. Philosophers like George Boole have for long tried to formalize the law of thought, some of them dreaming about a machine to think, able to compute the result of any problem, or to prove any theorem. Unfortunately, the first order logic has been proved to be undecidable. In this context, SMT solvers might be the most evolved tools that we can get. This kind of solvers work by considering some subsets of the first order logic, like linear arithmetics over the integers, called theories.

The integration of an SMT solver into ProVeLines revealed a large overhead in verification time compared to the BDD implementation. Verifying a temporal property, even on a fully boolean model, could indeed take until 96,144 % more time using the SMT solver [CSHL13]. However, the cause of this problem is unclear. The present thesis is an attempt to investigate and solve that problem.

In the Chapter 1, we expand on the boolean satisfiability problem. We in-

troduce several ways of representing boolean formulas and different algorithms that we can use to quickly solve this problem. In particular, we mention BDDs and SAT solvers, which are at the heart of SMT solvers. Chapter 2 introduces the notion of theories, gives some examples, and presents the core algorithms running SMT solvers. Chapter 3 briefly explain the theories and practices behind ProVeLines and the mentioned software product-line model-checking algorithms. Among others, the link between these algorithms and the satisfiability problem is clarified. Chapter 4 presents a theoretical approach to efficiently integrate a SAT solver into ProVeLines. This is seen as an intermediary step between a BDD-based and an SMT-based implementation. As we shall see, this allows us to define new model-checking algorithms aimed at better integrate themselves with SAT and SMT solvers. In Chapter 5, we undertake the implementation of this theoretical approach and a concrete empirical study.

## Part I

# **Theoretical Background**

### Chapter 1

### The Satisfiability Problem

The boolean satisfiability problem, often denoted SAT, was the first known example of NP-complete decision problem. Other NP-complete problems have been proved to be by direct or indirect reduction to this first one. Understanding the satisfiability problem is therefore of paramount importance in the field of computational complexity. It is also the starting point of this thesis.

Due to its theoretical hardness, people sometime considered pointless to look for an efficient algorithm to solve it. However, different breakthroughs have, in the late 90's, renewed a common interest in solving the SAT problem on large formulas. This chapter aims at introducing this problem and several techniques to solve it, including the core algorithm of these so-called modern SAT solvers.

#### 1.1 Boolean Functions and Satisfiability Problem

This section introduces the basic definitions needed in this chapter. These definitions are adapted from [SS96] and [MMZ<sup>+</sup>01].

Let  $X = \{x_i\}_{i=1}^n$  be a set of  $n \in \mathbb{N}$  boolean variables. A boolean function is a function of the form  $f : \mathbb{B}^n \to \mathbb{B}$ , where  $\mathbb{B} = \{\bot, \top\}$  is the boolean domain. It can be represented by a well-formed formula. Any variable  $x \in X$ , as well as both constants  $\bot$  and  $\top$  are well-formed formulas. Moreover, if F and G are both well-formed formulas, their negations  $\neg F$  and  $\neg G$ , their conjunction  $F \land G$ , their disjunction  $F \lor G$ , their implication  $F \Rightarrow G$  and their equivalence  $F \Leftrightarrow G$ are all well-formed formulas. Henceforth, we simply call formula a well-formed formula.

Let  $Y = \{y_i\}_{i=1}^m$  be a set of  $m \in \mathbb{N}$  boolean variables. A truth assignment A over Y is a mapping from the variables of Y to values from the boolean domain. It can be equally represented by a function  $A : Y \to \mathbb{B}$  or by a set  $A = \{y \to v_y\}_{y \in Y}$ , where each variable  $y \in Y$  is mapped to the value  $v_y \in \mathbb{B}$ . Let F be a formula over a set of variable X. The assignment A is complete with respect to F if  $X \subseteq Y$ . It is partial otherwise.

Under a complete truth assignment, any formula F evaluates to either  $\perp$  or  $\top$ . The evaluation of F under A, denoted [A]F, is determined according to the

following rules:

| [A]	op                     | $= \top$ |                  |                                       |

|----------------------------|----------|------------------|---------------------------------------|

| $[A] \bot$                 | $= \bot$ |                  |                                       |

| [A]x                       | $=\top$  | if, and only if, | $A(x) = \top$                         |

| $[A] \neg F$               | $=\top$  | if, and only if, | $[A]F = \bot$                         |

| $[A](F \wedge G)$          | $=\top$  | if, and only if, | $[A]F = \top$ and $[A]G = \top$       |

| $[A](F \lor G)$            | $=\top$  | if, and only if, | $[A]F = \top \text{ or } [A]G = \top$ |

| $[A](F \Rightarrow G)$     | $=\top$  | if, and only if, | $[A]F = \top$ implies $[A]G = \top$   |

| $[A](F \Leftrightarrow G)$ | $=\top$  | if, and only if, | [A]F = [A]G                           |

If  $[A]F = \top$ , A is called a *satisfying assignment* for F, and F is said to be *satisfied* by A. If  $[A]F = \bot$ , A is called an *unsatisfying assignment* for F, and F is said to be *unsatisfied* by A. A formula F is said to be *satisfiable* if there exists a satisfying assignment for it. It is said to be *unsatisfiable* otherwise. F is also said to be *valid*, or *tautological*, if it is satisfied by any complete assignment. It follows that a valid formula is always satisfiable.

The *satisfiability problem*, denoted SAT, is concerned with finding a satisfying assignment for a formula, or with proving that this formula is unsatisfiable. This problem has been proved to be NP-complete by Cook [Coo71].

The validity problem is concerned with proving that a formula is valid, or with finding an unsatisfying assignment for it. The validity problem is dual with the satisfiability problem, as a formula F is satisfiable if, and only if,  $\neg F$  is not valid. Moreover, a satisfying assignment for the former is an unsatisfying one for the latter.

#### **1.2** Normal forms

A boolean function can be represented by an infinite number of formulas. Among those formulas, however, several subsets can be defined to enclose all those that share a common syntactical form. These formulas are said to be in a *normal form*. Keeping formulas in a normal form facilitates their manipulation and allows one to easily determine some of their properties, as satisfiability and validity. In this section, three kinds of normal forms are discussed: Negation Normal Form, Conjunctive Normal Form and Disjunctive Normal Form.

#### 1.2.1 Negation Normal Form

A formula is in Negation Normal Form, or NNF, if any negation operator  $\neg$  appears before a single variable. A literal is a boolean variable or the negation of one. Any literal is a formula in NNF. Moreover, if F and G are both formulas in NNF, their conjunction  $F \wedge G$ , their disjunction  $F \vee G$ , their implication  $F \Rightarrow G$  and their equivalence  $F \Leftrightarrow G$  are all formulas in NNF. Their negations  $\neg F$  and  $\neg G$ , however, are not necessarily in NNF.

Any formula can easily be transformed in NNF by pushing the negation

symbols toward the variables, using the following set of transformation rules:

$$\neg \left(\bigwedge_{i=1}^{n} F_{i}\right) \longrightarrow \bigvee_{i=1}^{n} \neg F_{i}$$

$$\neg \left(\bigvee_{i=1}^{n} F_{i}\right) \longrightarrow \bigwedge_{i=1}^{n} \neg F_{i}$$

$$\neg \neg F \longrightarrow F$$

In these rules, the symbol  $\longrightarrow$  should be read as "is transformed in". The equivalence between the left hand side and right hand side of each of these rules relies on the validity of either one of the De Morgan's laws or the double negation rule.

$$\neg \left(\bigwedge_{i=1}^{n} F_{i}\right) = \bigvee_{i=1}^{n} \neg F_{i}$$

$$\neg \left(\bigvee_{i=1}^{n} F_{i}\right) = \bigwedge_{i=1}^{n} \neg F_{i}$$

$$\neg \neg F = F$$

(Double negation rule)

We will see that formulas in Disjunctive Normal Form or Conjunctive Normal Form are also, by definition, in Negation Normal Form. This form can consequently be seen as less restrictive than, or a generalization of, the two hereafter mentioned normal forms.

**Example 1.2.1.** The formula  $F = \neg(\neg a \lor (a \land \neg b))$  is not in Negation Normal Form, as the first negation symbol applies to the whole remaining formula. The formula  $G = a \land (\neg a \lor b)$ , however, is in NNF. G is actually obtained from F by iterated application of the mentioned transformation rules. This process can be observed in the following series of steps:

$$\neg (\neg a \lor (a \land \neg b)) \longrightarrow (\neg \neg a \land \neg (a \land \neg b)) \longrightarrow (\neg \neg a \land (\neg a \lor \neg \neg b)) \longrightarrow (a \land (\neg a \lor b))$$

The two first transformation steps rely on the De Morgan's laws while the last step is obtained by application of the double negation rule.

#### **1.2.2** Conjunctive Normal Form

A formula is in *Conjunctive Normal Form*, or CNF, if it consists of a conjunction of clauses. A *clause* is a disjunction of literals. Any formula F in CNF is therefore of the form

$$F = \bigwedge_{i=1}^{n} \bigvee_{j=1}^{m_i} l_{i,j}$$

where  $\forall i \in \{1, 2, \dots, n\} : \forall j \in \{1, 2, \dots, m_i\} : l_{i,j}$  is a literal. As stated before, a formula in CNF is also in NNF. The negation operator  $\neg$  indeed appears only in literals.

A formula in CNF is *canonical* if each of its clauses contains at most one occurrence of a variable. Henceforth, we consider that any formula in CNF is actually canonical. This goes without loss of generality given that

- 1. If a literal *l* appears several times in a clause, only one of these appearances can be kept.

- 2. If, for a variable x, both literals x and  $\neg x$  appear in a clause, then this clause is satisfied by any complete assignment and can be removed from the original CNF.

This hypothesis allows us to consider the following result. A formula in CNF is valid if, and only if, it is reduced to the empty conjunction of clauses. Indeed, let us consider a formula F in CNF with a clause C such that

$$C = \bigvee_{i=1}^{m} l_i$$

Then any unsatisfying assignment for C is also an unsatisfying assignment for F. Such assignment is easy to find. It only need to include the set  $\{x_i \to v_i\}_{i=1}^n$ , where for any  $i \in \{1, \ldots n\}$ ,  $x_i$  is the variable of the literal  $l_i$  and  $v_i$  the boolean value that, assigned to this variable, makes this literal being evaluated to  $\bot$ , i.e.

$$v_i = \left\{ \begin{array}{ll} \bot & \text{if} \quad l_i = x_i \\ \top & \text{if} \quad l_i = \neg x_i \end{array} \right.$$

A formula in CNF is often called, throughout this thesis, a *clause database*.

**Example 1.2.2.** Let us consider the formula  $F = (\neg a \lor c) \land (\neg b \lor \neg c \lor d) \land (\neg d \lor f) \land (\neg d \lor g) \land (\neg f \lor \neg g)$ . This formula is obviously in Conjunctive Normal Form. Moreover, it is canonical. As it is not reduced to the empty conjunction of clauses, i.e. it contains at least one clause, it is not valid. The first clause  $\neg a \lor c$  is indeed unsatisfied by the assignment  $\{a \to \top, c \to \bot\}$ . Any complete superset of it is therefore an unsatisfying assignment for F.

#### 1.2.3 Disjunctive Normal Form

A formula is in *Disjunctive Normal Form*, or DNF, if it consists of a disjunction of cubes. A *cube* is a conjunction of literals. Any formula F in DNF is therefore of the form

$$F = \bigvee_{i=1}^{n} \bigwedge_{j=1}^{m_i} l_{i,j}$$

where  $\forall i \in \{1, 2, \dots, n\}$ :  $\forall j \in \{1, 2, \dots, m_i\}$ :  $l_{i,j}$  is a literal. As stated before, a formula in DNF is also in NNF.

A formula in DNF is *canonical* if each of its cubes contains at most one occurrence of a variable. Henceforth, we consider that any formula in CNF is actually canonical. As for formulas in CNF, this goes without loss of generality. Considering this hypothesis, a formula in CNF is unsatisfiable if, and only if, it is reduced to an empty disjunction of cubes.

Conjunctive Normal Form and Disjunctive Normal Form are dual. Indeed, negating a formula in CNF and transforming it in NNF by iterated application

of the rules mentioned in Section 1.2.1 yields a formula in DNF. Moreover, the validity problem is easy to solve on CNF while the satisfiability problem is easy on DNF. The duality between these two normals forms is therefore correlated to the duality between these two problems. The actual hard remaining problem is to solve the satisfiability problem over formulas in CNF, or in an equivalent way, the validity problem over formulas in DNF. This challenge will be tackled in the next section.

#### 1.3 Satisfiability over CNF

The satisfiability problem over formulas in CNF is tackled by application programs often called *SAT solvers*. As we shall see, these tools have known major improvements during the last decades. This section first introduces the classical DPLL alogrithm before presenting the breakthroughs of the CDCL algorithm, which is the core algorithm of most modern SAT solvers.

#### 1.3.1 The DPLL Algorithm

The satisfiability problem over a clause database can be solved using a backtracking search algorithm. This was first published by Davis and Putnam as part of a solver for the first order logic [DP60] [DLL62]. It is now known as the *Davis-Putnam-Logemann-Loveland*, or *DPLL*, algorithm.

This algorithm maintains a truth assignment and tries to expand it until reaching a complete and satisfying assignment for a clause database. During this process, conflicts can arise that will force it backtrack. The algorithm actually iterates through different sub-processes.

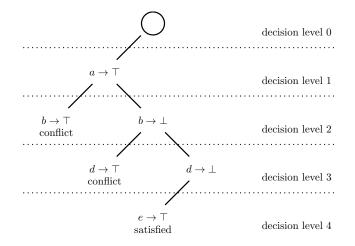

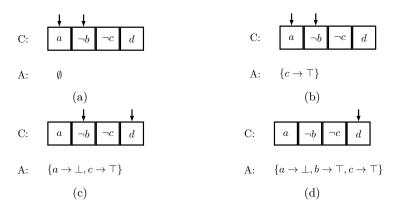

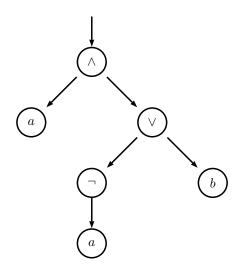

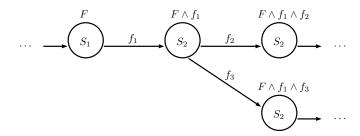

The decision process first extends the current truth assignment by making a decision assignment, i.e. by selecting a free variable and a value for it. At this stage, a decision tree is maintained. Each node in the decision tree specifies a decision assignment. The decision level of a decision assignment is defined as its depth in the decision tree. If no free variable remains, then the current assignment is complete and satisfies the clause database. An example of decision tree is shown in Figure 1.1.

Once a decision has been made, the *deduction process* extends the current truth assignment by inferring some logical implications of this decision with respect to the clause database. This inference mechanism relies on the presence of *asserting clauses*. A clause is said to be asserting if all of its literals are assigned to  $\perp$ , except one. During the deduction process, the last free literal of each asserting clause is assigned to  $\top$ . This principle is called *Basic Constraint Propagation*, or *BCP*. It is iterated until no asserting clause remains or until a conflict arises. A conflict occurs when a clause is unsatisfied by BCP, i.e. when all of its literals are propagated to  $\perp$ .

**Example 1.3.1.** Let us consider the clause database  $F = a \land (\neg a \lor b) \land (\neg a \lor \neg b)$ . Under the empty truth assignment, the first clause a is asserting and the assignment  $a \to \top$  can be derived by BCP. The two other clauses then become asserting. From the second clause,  $\neg a \lor b$ , the assignment  $b \to \top$  is propagated. However, this leads to a conflict as all the literals of the third clause are afterward assigned to  $\bot$ .

Figure 1.1: Decision tree created by the DPLL algorithm in the example 1.3.2

The additional variable assignments derived during the deduction process are called *deduction assignments*. The decision level associated with a deduction assignment is defined as the decision level of the decision assignment that has led to it.

If a conflict occurred during the deduction process, the *backtracking process* undoes all the assignments made at the current decision level and go back to the previous level in order for the opposite assignment to be tried. If it is not possible to backtrack any further, then the clause database is not satisfiable.

The overall process is formalized in Algorithm 1. This procedure determines whether a formula F in CNF is satisfiable or not. The procedure *propagate* first applies BCP to the partial assignment A, which is initially empty, with respect with the clause database F. If a conflict occurred during BCP, the process tries to backtrack. The procedure *backtrack* undoes all variable assignments made at the current decision level and returns the last decision assignment, so that it can be reverted. If it is not possible to backtrack any further, the process ends, returning false. If no conflict occurred, and if A is a complete and satisfying assignment for F, the process stops, returning true. Finally, if no conflict occurred and if A is not complete with respect to F, a decision is made. The function *decide* returns an arbitrary variable assignment  $x \to v$  where x is a free variable of F and  $v \in \mathbb{B}$ . The process then restarts from the top of the algorithm.

**Example 1.3.2.** Let us suppose that a satisfying assignment need to be found for the clause database  $F = (\neg a \lor c) \land (\neg b \lor \neg c \lor d) \land (\neg d \lor e) \land (\neg d \lor f) \land (\neg e \lor \neg f)$ . Let us also suppose that the decision process picks the variables alphabetically and always tries to assign  $\top$  first.

The decision tree produced by this scenario is shown in Figure 1.1. The algorithm first decides the assignment of a to  $\top$  and derives, as the first clause  $\neg a \lor c$  becomes asserting,  $c \to \top$ . It then decides the value of b as being  $\top$ , propagates the assignment  $d \to \top$  due to the second clause, and runs into a conflict, as e and f are propagated to  $\top$  by the third and fourth clauses, leading the last clause  $\neg e \lor \neg f$  to be unsatisfied. This last decision is consequently reverted. The process decides next to assign d to  $\top$ , and runs into the exact

#### Algorithm 1 The DPLL Algorithm

```

boolean DPLL(\operatorname{cnf} F)

Integer decisionLevel \leftarrow 0

Assignment A \leftarrow \emptyset

loop

\operatorname{propagate}(A, F)

if a conflict occurred then

if decisionLevel = 0 then

return false

else

(x \to v) \leftarrow \text{backtrack}(A, decisionLevel)

decisionLevel \leftarrow decisionLevel - 1

A \leftarrow A \cup \{x \to \neg v\}

end if

else if A is complete then

return true

else

(x \to v) \leftarrow \text{decide}(A, F)

decisionLevel \leftarrow decisionLevel + 1

A \leftarrow A \cup \{x \to v\}

end if

end loop

```

same conflict, i.e. both e and f are propagated to  $\top$ . This decision is therefore also reverted. The last decision taken by the process,  $e \to \top$ , leads to a complete solution by propagating f to  $\bot$ . The satisfying assignment found is  $\{a \to \top, b \to \bot, c \to \top, d \to \bot, e \to \top, f \to \bot\}$ .

This algorithm actually falls twice into the same trap, as both conflicts occurring during this run have the same root cause: d cannot, and should not, be assigned to  $\top$ . As we shall see, part of the power of modern solvers relies on their ability to learn from that kind of mistakes.

#### 1.3.2 The CDCL Algorithm

Over the past twenty years, several improvements have been made on top of the DPLL algorithm. The most noticeable are clause learning and backjumping [SS96], efficient propagation by use of lazy data structures and activity-based heuristics [MMZ<sup>+</sup>01]. They result in what is commonly named the *Conflict-Driven Clause Learning*, or *CDCL*, algorithm, which we present in this section.

#### Clause learning and backjumping

Clause learning and backjumping have first been introduced by Silva and Sakallah with the GRASP (Generic seaRch Algorithm for the Satisfiability Problem) solver [SS96]. Both mechanisms make use of a specific data structure maintained during the deduction process called the *implication graph*.

Let the deduction assignment  $x \to v_x$  be the result of an asserting clause C. The antecedent assignments of x, denoted A(x), are defined as the set of assignments over variables of C that have led C to become asserting. The

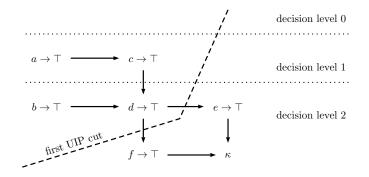

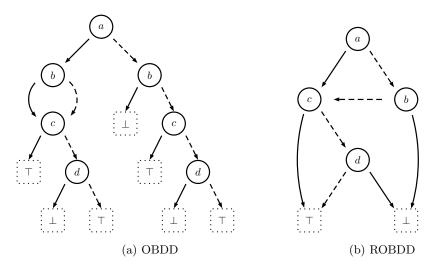

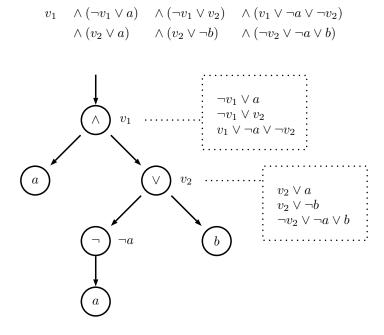

implication graph is a Directed Acyclic Graph (DAG) such that each vertex is either a variable assignment or a special conflict vertex, denoted  $\kappa$ . The set of predecessors of an assignment vertex  $y \to v_y$  correspond to the antecedent assignments A(y). An assignment vertex without any predecessor therefore corresponds to a decision assignment. A special conflict vertex  $\kappa$  is introduced when a conflict occurs. Its predecessors are all the assignments over variables of a clause which have led this clause to be unsatisfied. The implication graph created from the first conflict occurring in example 1.3.2 is presented in Figure 1.2.

Figure 1.2: Implication graph produced by the first conflict occurring in example 1.3.2

When a conflict arises, a so-called *conflict clause* is generated by the *analysis process* and added to the clause database. The analysis process creates a partition of all the nodes in the implication graph by cutting it in half, putting all the decision assignments on one side, called the *reason side*, and the conflict vertex  $\kappa$  on the other side, called the *conflict side*. The conflict clause is then generated by taking all the assignments in the reason side that have at least one outgoing edge targeting an element of the conflict side. Let  $A_c$  be this set of assignments. The conflict clause  $C_c$  is then defined as

$$C_c = \bigvee_{(x \to v) \in A_c} l_x$$

where

$$l_x = \begin{cases} x & \text{if } v = \bot \\ \neg x & \text{if } v = \top \end{cases}$$

Several learning schemes have been introduced in the literature, each one characterized by its way of creating the aforementioned partition. In the *First Unique Implication Point*, or *FUIP*, scheme [SS96], the reason side is the largest set such that only one assignment made at the highest decision level in which a variable of the unsatisfied clause has been assigned has an outgoing edge targeting an element of the conflict side. This scheme is by far the most widely used and has empirically proved its efficiency [ZMMM01]. This clause can be further strengthened by a minimizing process [SB09], which we do not detail here.

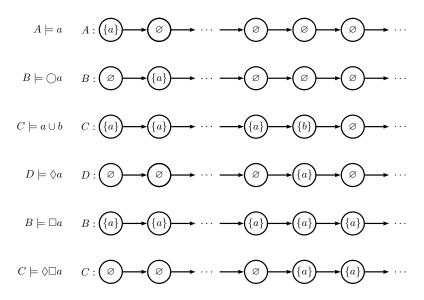

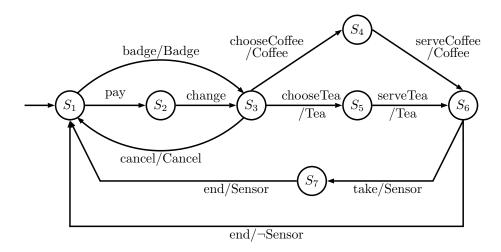

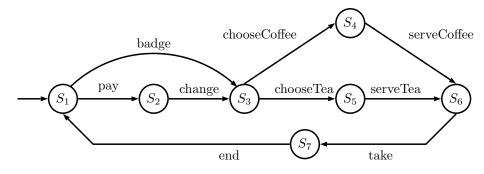

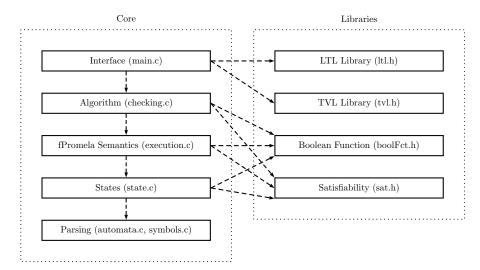

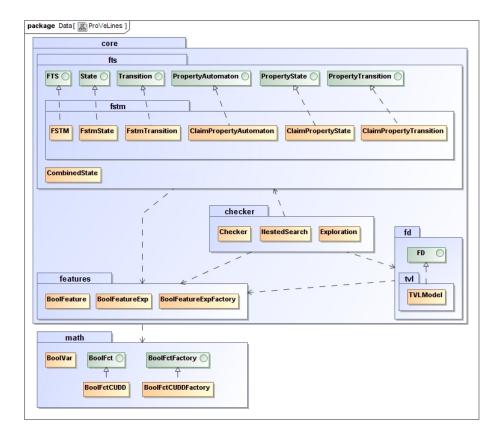

**Example 1.3.3.** The implication graph created from the first conflict occurring in Example 1.3.2 is presented in Figure 1.2. It is partitioned according to the