## **THESIS / THÈSE**

#### MASTER IN COMPUTER SCIENCE

Power reduction techniques for TFT LCD displays

Decostre, Alain

Award date: 2003

Link to publication

General rights Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal ?

#### Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

Facultés Universitaires Notre-Dame de la Paix, Namur Institut d'Informatique Année académique 2002-2003

> Power Reduction Techniques for TFT LCD Displays

> > Alain DECOSTRE

Mémoire présenté en vue de l'obtention du grade de Maître en Informatique

## UBS 10027165

#### Abstract

Energy consumption has become a major concern in portable devices design. The power minimization has traditionally focused on circuit design. More recently, software based techniques, named Dynamic Power Management (DPM), have emerged as attractive approaches to save energy.

The display is one of the main contributor to the overall power budget. In this dissertation we show how to integrate such DPM techniques in a Linux device driver controlling a TFT liquid crystal display. We also detail the implementation of the techniques "Variable dot clock" and "Variable frame refresh" on a Personal Digital Assistant (PDA) using the Linux operating system. A power consumption reduction of respectively 6.4 % and 10 % is observed. Finally we outline a solution for a third technique : the "Liquid crystal orientation shift".

By this work we demonstrate that a software adaptation in the operating system, without modifying the hardware, can lead to an appreciable reduction of the power consumption in a portable system. Therefore the DPM techniques can be applied to improve the lifetime of existing portable system batteries.

#### Résumé

La consommation d'énergie est devenue un centre d'intérêt majeur dans la conception d'appareils portables. La minimisation de l'énergie s'est traditionnellement concentrée sur la conception de circuits. Plus récemment, des techniques orientées logiciel, appelées gestion dynamique de la consommation d'énergie (en anglais DPM), se sont révélées être une approche intéressante pour économiser de l'énergie.

L'écran est l'un des principaux consommateurs d'énergie du système. Dans ce mémoire, nous montrons comment intégrer de telles techniques DPM dans un pilote de périphérique Linux contrôlant un écran TFT à cristaux liquides. Nous détaillons aussi l'implémentation des techniques "Variable dot clock" et "Variable frame refresh" sur un Assistant Personnel Digital (en anglais PDA) utilisant le système d'exploitation Linux. Une réduction de la consommation électrique de respectivement 6.4 % et 10 % est observée. En dernier lieu, nous esquissons aussi une solution pour une troisième technique appelée "Liquid crystal orientation shift".

Par ce travail, nous démontrons qu'une adaptation logicielle du système d'exploitation, sans modification du matériel, peut apporter une réduction appréciable de la consommation électrique dans un système portable. Les techniques peuvent donc être appliquées pour améliorer la durée de vie des batteries des systèmes portables existants.

### Acknowledgements

I would like to express my gratitude to all those who gave me the possibility to realize this work. First, I want to thank my supervisor, Professor Jean Ramaekers, for his very relevant advice and comments, and the reading of my successive drafts.

I would like also to thank all the members of the Micrel laboratory of the University of Bologna for their welcome and their help throughout my stay in Bologna. In particular, I am grateful to Professor Luca Benini who facilitated my integration in his team and supervised my training, and Assistant Professor Andrea Acquaviva whose help, stimulating advice and encouragement were greatly useful.

Finally, I would like to express a special thank you to my family for its support during my studies and particularly during the preparation of my dissertation.

## Contents

| In | trod | uction | 13                                                                   |  |  |  |  |  |  |  |

|----|------|--------|----------------------------------------------------------------------|--|--|--|--|--|--|--|

| 1  | Dyı  | namic  | power management 17                                                  |  |  |  |  |  |  |  |

|    | 1.1  | Introd | uction                                                               |  |  |  |  |  |  |  |

|    | 1.2  | Dynai  | nic power management at component level                              |  |  |  |  |  |  |  |

|    |      | 1.2.1  | Power state model                                                    |  |  |  |  |  |  |  |

|    |      | 1.2.2  | Under the black box                                                  |  |  |  |  |  |  |  |

|    |      | 1.2.3  | Internal controller and external controller                          |  |  |  |  |  |  |  |

|    | 1.3  | Dynai  | nic power management at system level                                 |  |  |  |  |  |  |  |

|    |      | 1.3.1  | Structure of a system-level power manager                            |  |  |  |  |  |  |  |

|    |      | 1.3.2  | Power manager controller 22                                          |  |  |  |  |  |  |  |

|    |      | 1.3.3  | Power manager observer                                               |  |  |  |  |  |  |  |

|    |      | 1.3.4  | Power manager policies                                               |  |  |  |  |  |  |  |

|    | 1.4  | Dynai  | nic power management at network level                                |  |  |  |  |  |  |  |

|    | 1.5  |        |                                                                      |  |  |  |  |  |  |  |

|    |      | 1.5.1  | Battery-driven dynamic power management                              |  |  |  |  |  |  |  |

|    |      | 1.5.2  | Power management for the processor: Dynamic voltage scaling 29       |  |  |  |  |  |  |  |

|    |      | 1.5.3  | Selective instruction compression for memory energy reduction 32     |  |  |  |  |  |  |  |

|    |      | 1.5.4  | Power management for hard disks                                      |  |  |  |  |  |  |  |

|    |      | 1.5.5  | Transport protocol optimization for energy efficient wireless embed- |  |  |  |  |  |  |  |

|    |      |        | ded system                                                           |  |  |  |  |  |  |  |

| 2  | Sys  | tem de | escription 39                                                        |  |  |  |  |  |  |  |

|    | 2.1  | Overv  | iew of the Assabet                                                   |  |  |  |  |  |  |  |

|    | 2.2  | Frame  | buffer and palette memory organization                               |  |  |  |  |  |  |  |

|    | 2.3  | Refres | hing the screen                                                      |  |  |  |  |  |  |  |

|    | 2.4  | The L  | CD controller                                                        |  |  |  |  |  |  |  |

|    |      | 2.4.1  | The LCD Controller registers                                         |  |  |  |  |  |  |  |

|    |      | 2.4.2  | The LCD Controller Control Registers (LCCR) 44                       |  |  |  |  |  |  |  |

|    |      | 243    | The LCD Controller Status Begister $(LCSB)$ 45                       |  |  |  |  |  |  |  |

|   |      | 2.4.4   | The LCD Controller DMA Registers $(DBAR \text{ and }$ | L  | )(  | A | R            | 2)           | • | · |   |   | ÷  | 45 |

|---|------|---------|-------------------------------------------------------|----|-----|---|--------------|--------------|---|---|---|---|----|----|

| 3 | The  | Linux   | operating system                                      |    |     |   |              |              |   |   |   |   |    | 47 |

|   | 3.1  | Introd  | uction                                                |    |     |   |              |              |   |   |   |   |    | 47 |

|   | 3.2  | User n  | node and kernel mode $\ldots$                         |    |     |   |              |              |   |   |   |   |    | 48 |

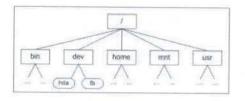

|   | 3.3  | Filesys | stem                                                  |    | i,  |   |              |              |   |   |   |   |    | 49 |

|   | 3.4  | Device  | e driver and device file                              |    |     |   |              |              |   |   |   |   |    | 52 |

|   |      | 3.4.1   | Device driver                                         |    | 2   |   | -            | 6            |   |   |   |   |    | 52 |

|   |      | 3.4.2   | Device file                                           |    |     |   |              |              |   |   |   |   |    | 52 |

|   | 3.5  | The co  | oncept of module                                      | 8  | 3.0 |   | 8            | 2            | • |   | 1 |   | 1  | 54 |

| 4 | The  | Linux   | device drivers                                        |    |     |   |              |              |   |   |   |   |    | 57 |

|   | 4.1  | Genera  | al description of a Linux device driver               | ę. | 2   |   |              |              |   |   | 2 | 2 | -2 | 57 |

|   |      | 4.1.1   | Definition and roles of a device driver               |    |     |   |              |              |   |   |   |   |    | 57 |

|   |      | 4.1.2   | Level of kernel support to hardware device            |    |     |   |              |              |   |   |   |   |    | 58 |

|   |      | 4.1.3   | Classes of devices                                    |    |     |   |              |              |   |   |   |   |    | 59 |

|   | 4.2  | Char d  | lrivers                                               |    |     |   |              |              |   |   |   |   |    | 61 |

|   | 4.3  |         | hodology for device driver designing                  |    |     |   |              |              |   |   |   |   |    | 66 |

|   |      | 4.3.1   | The ideal device driver                               |    |     |   |              |              |   |   |   |   |    | 66 |

|   |      | 4.3.2   | Design methodology                                    |    |     |   |              |              |   |   |   |   |    | 66 |

| 5 | Inte | rrupts  |                                                       |    |     |   |              |              |   |   |   |   |    | 69 |

|   | 5.1  | Polling | g mode and interrupt mode                             |    |     |   |              |              |   |   |   |   |    | 69 |

|   | 5.2  |         | pts handling                                          |    |     |   |              |              |   |   |   |   |    | 70 |

|   |      | 5.2.1   | Interrupts detection                                  |    |     |   |              |              |   |   |   |   |    | 70 |

|   |      | 5.2.2   | Interrupt handler selection                           |    |     |   |              |              |   |   |   |   |    | 71 |

|   |      | 5.2.3   | Interrupt handler role and working                    |    |     |   |              |              |   |   |   |   |    | 72 |

|   | 5.3  | The in  | itialization                                          |    |     |   |              |              |   |   |   |   |    | 73 |

|   | 5.4  | Botton  | n and top half parts of an interrupt handler          |    |     |   |              |              |   |   |   |   |    | 74 |

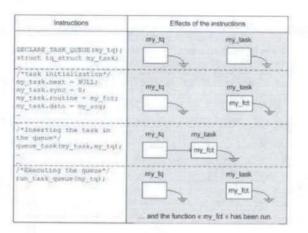

|   | 5.5  |         | ueues                                                 |    |     |   |              |              |   |   |   |   |    | 75 |

|   | 5.6  | Kernel  | task queues                                           |    |     |   |              |              |   |   |   |   | _  | 77 |

|   | 5.7  | Tasklet | ts                                                    |    | •   |   | 94 )<br>94 ) | 0 <b>1</b> 8 |   | • | • | • | ÷  | 78 |

| 6 | The  | LCD     | controller frame buffer driver                        |    |     |   |              |              |   |   |   |   |    | 79 |

|   | 6.1  | Device  | dependent and independent levels                      |    |     |   |              |              |   |   |   |   |    | 79 |

|   | 6.2  |         | itialization                                          |    |     |   |              |              |   |   |   |   |    | 80 |

|   |      | 6.2.1   | Initializing the main device-related data structures  |    |     |   |              |              |   |   |   |   |    | 80 |

|   |      | 6.2.2   | Inserting the "controller task" into the task queue   |    |     |   |              |              |   |   |   |   |    | 82 |

|   |      | 6.2.3   | Initializing the frame buffer memory                  |    |     |   |              |              |   |   |   |   |    | 83 |

|   |      | 6.2.4   | Installing the interrupt service routine              |    |     |   |              |              |   |   |   |   |    | 83 |

|    |        | 6.2.5   | Defining the content of the LCD controller registers              | 83  |

|----|--------|---------|-------------------------------------------------------------------|-----|

|    |        | 6.2.6   | Registering the frame buffer driver                               | 85  |

|    |        | 6.2.7   | Registering the device power management function                  | 85  |

|    |        | 6.2.8   | Updating the controller registers and enabling the LCD screen and |     |

|    |        |         | the controller                                                    | 85  |

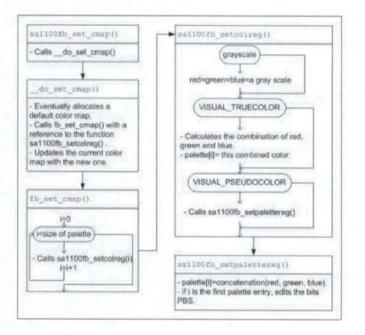

|    | 6.3    | Updat   | ting the palette                                                  | 88  |

| 7  | Dri    | ver ad  | aptation for power reduction of a TFT LCD display                 | 91  |

|    | 7.1    |         | are techniques for low-power TFT LCD displays                     | 91  |

|    |        | 7.1.1   | Variable dot clock                                                | 92  |

|    |        | 7.1.2   | Variable frame refresh                                            | 92  |

|    |        | 7.1.3   | Liquid crystals orientation shift                                 | 92  |

|    |        | 7.1.4   | Backlight shifting                                                | 93  |

|    | 7.2    | Imple   | mentation                                                         | 93  |

|    |        | 7.2.1   | Variable dot clock                                                | 93  |

|    |        | 7.2.2   | Variable frame refresh                                            | 95  |

|    |        | 7.2.3   | Liquid crystals orientation shift                                 | 96  |

|    | 7.3    | Exper   | imental results                                                   | 97  |

|    |        | 7.3.1   | Variable dot clock                                                | 97  |

|    |        | 7.3.2   | Variable frame refresh                                            | 99  |

| C  | onclu  | ision   |                                                                   | 101 |

|    |        |         |                                                                   | 101 |

| B  | ibliog | graphy  |                                                                   | 103 |

| Та | able o | of acro | onyms                                                             | 107 |

|    |        |         |                                                                   |     |

| G  | lossa  | ry      |                                                                   | 109 |

| A  | ppen   | dix     |                                                                   | 115 |

| A  | LCI    | ) Con   | troller Registers                                                 | 117 |

|    | A.1    | LCD (   | Controller Control Register 0 (LCCR0)                             | 117 |

|    |        |         | Controller Control Register 1 (LCCR1)                             | 118 |

|    | A.3    |         | Controller Control Register 2 (LCCR2)                             | 118 |

|    | A.4    |         | Controller Control Register 3 (LCCR3)                             | 119 |

|    | A.5    |         | Channel 1 Base Address Register                                   | 120 |

|    | A.6    |         | Channel 1 Current Address Register                                | 120 |

|    | A.7    |         | Channel 2 Base Address Register                                   | 120 |

|    | A.8    |         | Channel 2 Current Address Register                                | 120 |

|    | A 9    |         | Controller Status Register                                        | 191 |

| В | Applications | 123 |

|---|--------------|-----|

|   | B.1 PCD.c    | 123 |

|   | B.2 LENON.c  |     |

|   | B.3 LENOFF.c | 125 |

| С | fbmem.c      | 127 |

| D | sa1100fb.c   | 147 |

| Е | fb.h         | 187 |

| F | sa1100fb.h   | 199 |

# List of Figures

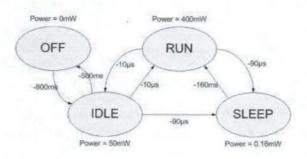

| 1.1  | Example of power state machine.                                             | 19 |

|------|-----------------------------------------------------------------------------|----|

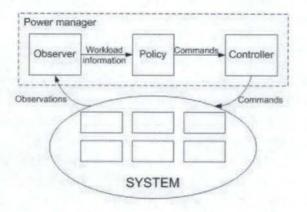

| 1.2  | Structure of a system-level power manager                                   | 22 |

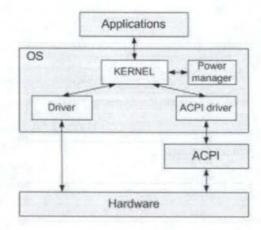

| 1.3  | ACPI interface                                                              | 23 |

| 1.4  | The power manager observes requests.                                        | 24 |

| 1.5  | Applications control power states directly.                                 | 25 |

| 1.6  | Timeout-based policy.                                                       | 27 |

| 1.7  | Predictive shutdown policy.                                                 | 27 |

| 1.8  | Processor-memory normal architecture (a) and power-saving architecture (b)  | 33 |

| 1.9  | Processor-Memory second power-saving architecture                           | 34 |

| 1.10 | Example of sessions for different thresholds.                               | 36 |

| 9.1  |                                                                             | 10 |

| 2.1  | The Assabet.                                                                | 40 |

| 2.2  | Frame buffer organization with a palette.                                   | 41 |

| 2.3  | Frame buffer organization without palette.                                  | 41 |

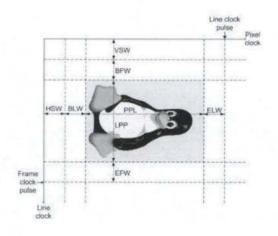

| 2.4  | The display timings.                                                        | 42 |

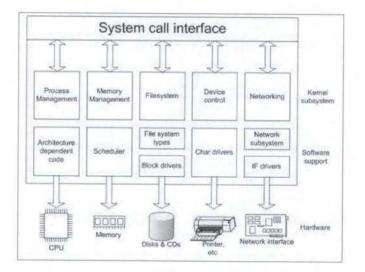

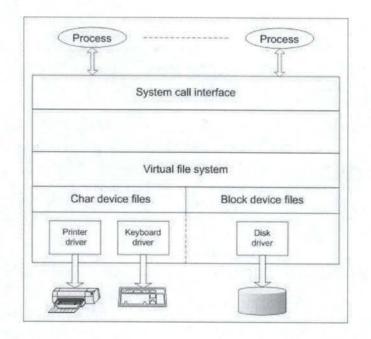

| 3.1  | A view of the kernel.                                                       | 50 |

| 3.2  | An example of filesystem.                                                   | 50 |

| 3.3  | The device driver interface.                                                | 53 |

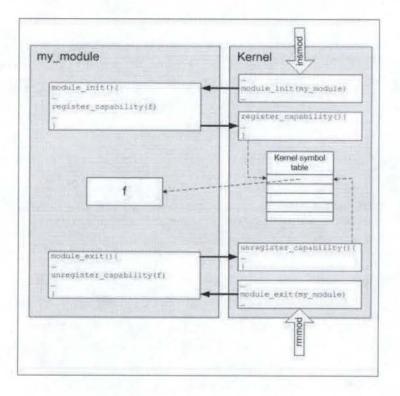

| 3.4  | Access to the modules symbols                                               | 56 |

| 4.1  | Level of kernel support (Left: No support at all. Central: Minimal support. |    |

|      | Right: Extended support)                                                    | 59 |

|      | rught. Extended support)                                                    | 99 |

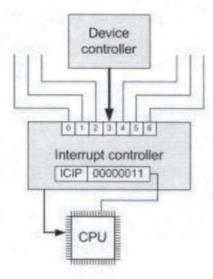

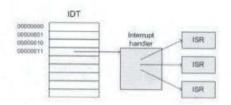

| 5.1  | Detection of an interrupt by the processor.                                 | 71 |

| 5.2  | Selection of the interrupt handler and access to the ISRs                   | 73 |

| 5.3  | A task queue.                                                               | 75 |

| 5.4  | Initialization and execution of a task queue.                               | 76 |

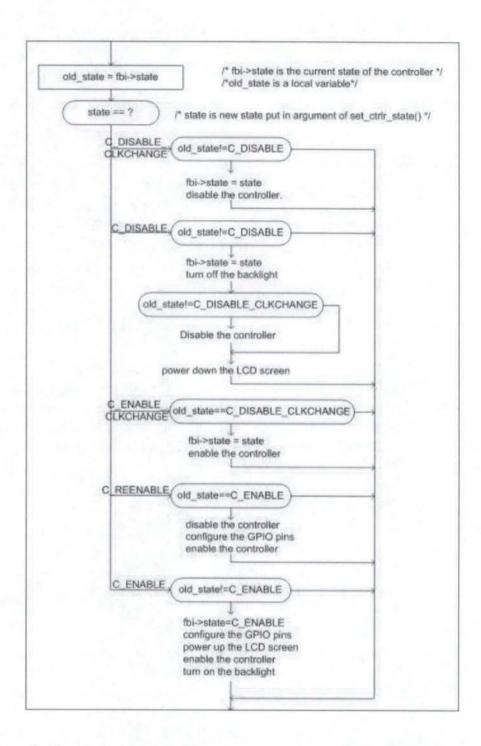

| 6.1  | Defining the content of the LCD controller register.                        | 84 |

| 6.2  | Updating the controller registers and enabling the LCD screen and the con-  |    |

|      | troller                                                                     | 87 |

|      |                                                                             |    |

| 6.3 | Updating the palette                     | 39 |

|-----|------------------------------------------|----|

| 7.1 | Updating the fb_var_screeninfo structure | 94 |

| 7.2 |                                          | 96 |

### Introduction

Energy consumption has become one of the primary concerns in electronic systems design due to the recent popularity of portable devices such as laptop computers, Personal Digital Assistants (PDAs) and cellular phones. The battery capacity has improved very slowly while the computational demand (for instance multimedia applications) has drastically increased over the same time. Some low-power circuit design techniques have helped to increase battery lifetime. On the other hand, managing power dissipation at higher levels can significantly reduce energy consumption and increase battery lifetime. That is the reason why power management techniques, under the name of Dynamic Power Management (DPM), have recently emerged as an attractive alternative to inflexible hardware solutions.

Dynamic Power Management is in fact a design methodology aiming at controlling performance and power levels of digital circuits and systems, with the goals of extending the operational autonomy time of battery-powered systems, providing acceptable performance degradation when energy supply is limited, and adapting power dissipation to satisfy environmental constraints. DPM encompasses a set of techniques that achieve energy-efficient computation by selectively turning off (or reducing the performance of) system components when they are idle (or partially unexploited).

DPM applies to the various components of a system, in particular to the Liquid Crystal Display (LCD) of portable systems, such as laptop computers and PDAs. Display power consumption is often one of the most significant contributor to the overall power budget for many portable devices, especially when multimedia applications are run. There are four main software techniques to reduce power consumption of a LCD display. These techniques do not require hardware changes. Therefore they are applicable on existing systems by simply modifying the driver in the operating system.

The first technique, called *Variable dot clock*, reduces the dot clock frequency used for processor-display communication, decreasing the display refresh rate as a side effect. The second technique is named *Variable frame refresh* and exploits the property of liquid crystals of the display, which maintains their orientation for a while when they are not polarized.

Advantage of this time is taken to reduce power consumption by disabling the LCD controller. The third method, the *liquid crystal orientation shift* technique, is based on the observation that LCD power consumption is proportional to the image luminance. The luminance of useless parts of the screen can therefore be reduced in order to save energy. Finally, the fourth method, called *Backlight shifting*, proposes to adapt the luminance intensity of the display according to the environment luminance. This method derives from the observation that the display has a high visibility in poorly illuminated environment because of the high contrast.

A driver including these techniques is implemented in the ECOS real-time embedded operating system [1]. The present dissertation reports our implementation work of the first two techniques in a device driver for the Linux operating system and outlines a solution for the third technique. Implementing these techniques was performed during my training period at the Department of Electronics, Computer Science and Systems (DEIS) of the University of Bologna (Italy), from September 2002 to January 2003.

This dissertation is organized as follows. The first chapter describes the basic concepts of Dynamic Power Management. Three DPM levels are considered: the component level, the system level and the network level. Examples of power reduction techniques are also included. Each example concerns one of the main elements of a classical electronic system. This chapter has been written in cooperation with Benjamin Briquet.

The second chapter gives an overview of the hardware platform, the Assabet, used to implement the power reduction techniques. We explain the frame buffer memory organization and the LCD controller registers, because these elements are driven by the driver we have adapted.

In the third chapter we present the Linux operating system which was installed on the Assabet. In particular we describe how Linux allows applications to manage I/O devices and emphasize the notion of file, which is the basic concept of the Linux system.

The fourth chapter is related to the basic concepts of a Linux devices driver. We introduce the three main classes of device drivers and describe the basic functions of a char driver, since the LCD driver we have adapted owns to this class. We also propose a methodology for device driver designing.

The fifth chapter describes how the processor detects an interrupt and launches the appropriate interrupt handler. It also explains the concept of task queue, which is used to implement the Variable frame refresh technique.

In the sixth chapter we give a description of the sal100fb.c driver, i.e. the driver we have enhanced for power management. We explain how a configuration change is effectively performed. This is another personal contribution to this dissertation subject.

The last chapter develops the power reduction techniques for a  $TFT^1$  LCD display. The implementation and observed measurements are described for the Variable dot clock and the Variable frame refresh techniques. A solution is outlined for the Liquid crystal orientation shift technique.

In conclusion we emphasize the effectiveness of DPM methodology for reducing power consumption in electronic systems.

<sup>1</sup>Thin-Film Transistor.

### Chapter 1

### Dynamic power management

#### 1.1 Introduction

One of the most important technical evolution of the last decade has been the emergence of portable systems, such as laptop computers, cellular phones and PDAs. The increasing popularity of such systems encourages the development of more and more sophisticated devices. Designing a portable system requires to tackle about the problem of delivering high performance with a limited consumption of electric power. High performance is required to support complex applications (for instance multimedia) that are running on these portable systems. Low-power consumption is required to achieve acceptable autonomy in battery-powered systems, as well as to decrease battery weight. Stationary systems<sup>1</sup> are also concerned with power conservation, because of the cost and noise of cooling systems, the cost of electric power (especially for large systems) and stricter environmental impact regulations.

The battery capacity has improved very slowly while the demands of computation capacity have drastically increased over the same time. Better low-power circuit design techniques have helped to increase battery-lifetime, but benefits obtained by such techniques do not compensate all the needs. In addition, the pressure for fast time-to-market has become extremely high, and it is often unacceptable to completely redesign a system merely to reduce its power dissipation.

Electronic systems are generally designed to deliver peak performance, but in many cases peak performance levels are not needed for most of the operation time. Cellular phones and portable computers are two examples of systems with non-uniform workload. When the user is sending or receiving a call with a cellular phone (or is running an application on

<sup>&</sup>lt;sup>1</sup>i.e. non portable systems.

a laptop computer), he wants to have the maximum performance. However, when the user is carrying the phone in his pocket (or is thinking to what to write during a text-editing session on a laptop computer), he does not need the full computational power of the system.

Power management for computer systems is traditionally focused on regulating the power consumption by switching the system in a low-power state, which does not allow to use the system. This state is a de-activating state, generally requiring a user action to re-activate the system. More recently, some researches focus on the development of power management techniques performed while programs are running.

Dynamic power management (DPM) is a design methodology that dynamically reconfigures an electronic system to provide the requested services and performance levels with a minimum number of active components or a minimum load of such components. Dynamic power management encompasses a set of techniques that achieve energy-efficient computation by selectively turning off (or reducing the performance of) system components when they are idle (or partially unexploited). A component is in an *idle* state if it has no request to serve; it can then be put in a *sleep* state to reduce its power consumption. When a request arrives, the component wakes up and switches into a *run* state in order to serve this request<sup>2</sup>. Moreover, a component can be completely shut down in order to not consume power. The component is thus in the *off* state.

The fundamental premise for the applicability of DPM is that systems (and their components) have to support a non uniform workload during their operation times. Such an assumption is valid for most systems, both when considered in isolation and when internetworked. A second assumption of DPM is that it is possible to predict, with a certain degree of confidence, the fluctuations of workload. Finally, a third assumption is that the workload observation and prediction should not consume significant energy.

We examine hereafter the three levels where dynamic power management (DPM) can be applied: first at component level, then at system level and finally at network level.

#### 1.2 Dynamic power management at component level

We can see a system like a set of interacting components. The definition of a component is general and abstract. It may be a chip (such as the CPU) or a board (hard disk, memory, wireless interface, video display,...) but in the current context, it is a black box: no detailed knowledge of its internal structure is needed.

<sup>&</sup>lt;sup>2</sup>Other names for these states are sometimes used in the literature, such as active, disable, on, work,....

A power manageable component (PMC) is characterized by multiple states of operation that span the power-performance trade-off. This allows to distinguish these components from those always operating at a given performance level and power consumption. The ideal case for a PMC is always to have a lot of states of operation in order to minimize the power by calibrating perfectly the performance needed by the requests served by the component. Nevertheless, a problem appears when the number of states increases because the hardware complexity and overhead become more pronounced. In fact, the PMC's cannot switch from a state to another one without a cost. The cost may be a performance lost, a delay or even a power transition cost. The relation that we often note is: low-power states (such as sleep) have lower performances and larger transition costs, with respect to states with higher power. The transition cost has an important impact and has to be taken into account in the power management models.

#### 1.2.1 Power state model

We can thus define for each component a power/performance behavior. In other words, it can be defined for each PMC the power states it accepts (for instance run, off, sleep, and idle), the associated performances, the transition costs and the power consumptions when it switches from one power-state to another one. We can represent this information with a power state machine for example (see figure 1.1). To summarize, we can say that a PMC

Figure 1.1: Example of power state machine.

is needed to develop some power management techniques and that a component cannot switch from one of its state to another one without a cost. This leads us to consider the power management model as a non-trivial optimization problem.

#### 1.2.2 Under the black box

We have defined a component as a black box. It is time to see now how DPM is implemented inside the *box*. We examine in this section two of the most dynamic techniques implemented in components themselves: the *clock gating* technique and the *power off supply* technique. In reality, these techniques are generally implemented in the hardware circuit of the component. That is why they are also called physical mechanisms.

One of the most common DPM techniques at the component level is the clock gating. This addresses digital components that are clocked (CPU, display,...). Power can be saved by reducing the frequency of the component clock (or some component clocks, if the component uses several clocks), and at the limit by stopping the clock. Clock gating can be applied both during idleness periods or activity periods. During activity periods, slowing the clock decreases the performance and, for some components (like the CPU), extends the execution time to perform a task. In this case, power saving is generally weak. For this reason, power saving can be more important during idleness period. The main challenge is then efficient idleness detection. Moreover, to go back to normal system activity, clock gating requires a short transition time: the clock should be re-initialized in one or a few clock periods.

Even by stopping the clock, power dissipation is not completely eliminated. Power consumption of an idle component can be avoided by the technique of powering off the component. This radical solution requires controllable switches inserted in the electrical line supplying the component. A major disadvantage of this method is the recovery time, which is typically higher than in the case of clock gating because the component's operation must be re-initialized.

#### **1.2.3** Internal controller and external controller

We have said above that the transition latency can have an important impact on the power management model. In reality, when it is possible to switch a component to a *sleep* state without compromising the performance (or with little performance degradation) because the transition between the *sleep* state and the *run* state is nearly instantaneous, an *internal controller* - internal to the component - can be implemented. This internal controller decides for example to decrease the frequency (clock gating) or shut down the component (supply shutdown) if there are no requests to serve. Internally managed components are also called self-managed components. The main drawback is the lack of observability of the overall system operation and of the need of tolerating little or no performance degradation, since no assumptions can be made on how demanding the component's environment will be.

Clock gating is often implemented in a component with an *internal controller* while supply shutdown will be rather implemented with an external controller. The difference between the two techniques resides in the transition time to switch the component into its normal state. Indeed, when power transitions take a long time or consume a lot of energy, it is needed to take into account the workload of the system and decide when it is worthwhile to switch to a low-power state. Otherwise, the performance could be disastrous. The example that we have in mind is the limit case of workload with no idle periods longer than the time required to enter and exit the sleep state. If we decide to shut down the component as soon as an idle period is detected and if the power consumption associated with state transitions is of the same order of that of the run state, this could reduce the performance without saving any power. Workload information is thus required for all advanced power management approaches. The goal is even to predict the workload to identify exactly the idle periods. Several approaches and models can be produced to capture the workload information. Diverse techniques based on predictive approach or stochastic control have already been developed. We can easily imagine that these models are very complex. It is thus the role of an external controller - external to the component - to control transitions based on the workload of the system.

Let's see now how an external controller can be implemented at the system level by a power manager.

### 1.3 Dynamic power management at system level

#### 1.3.1 Structure of a system-level power manager

The power management idea is to profit from idle periods (e.g., when the component is not used) to put the component in its *sleep* state, or in one of its *sleep* states if multiple low-power states are available, without compromising too much the performance of the whole system. Regarding the system, the assumption made here is that it is not always entirely active; this means there are some periods during which some components are idle.

The activity of components (PMC and also non-PMC) is coordinated by a *system controller*, which is generally implemented in a software routine of the operating system. That is why the control of the system consumption is also implemented in software and especially in operating system as a module of the system controller.

We call *power manager* (PM) the system part (hardware or software) that performs DPM at system level. A power manager is composed of an *observer* monitoring the workload of

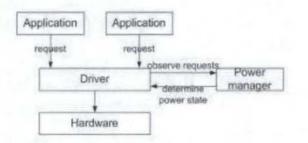

the system and its resources, a *controller* issuing commands for forcing state transitions in system resources, and at least one *policy*, which is a control algorithm for deciding when and how to force state transitions (based on information provided by the observer). The figure 1.2 depicts the general structure of a power manager.

Figure 1.2: Structure of a system-level power manager.

There are some reasons for implementing the power manager at software level. Software power managers are easy to write and to reconfigure. Then, in most cases, the designer cannot or does not want to interfere with and modify the underlying hardware platform. Finally, as DPM implementations are still a novel art, the experimentation with software is easier than with hardware.

#### 1.3.2 Power manager controller

The power manager must be able to control the state of each PMC. In order to develop a power manager as generic as possible, it should be interesting to dispose of an interface between the power manager and a PMC. This interface should be able to understand each command from the power manager and to effectively perform it. The way to control the state of a component is very hardware dependent. For this reason, the interface should be implemented in the component-closest software part, which is generally the *driver* of the component.

Industrial designs have been also proposed to encourage the standardization of interfaces. For instance, Intel, Microsoft and Toshiba propose a standard called *advanced configuration and power interface*, in short ACPI. ACPI is an OS-independent general specification that defines the interface between the operating system and an ACPI-compliant hardware. This interface can be used both for hardware configuration and power management. The front-end of the ACPI is the ACPI driver, which is OS-specific. The OS kernel interacts with hardware through the ACPI driver, which maps each OS request to an ACPI command and each ACPI response/message to a signal/interrupt (see figure 1.3).

The ACPI allows the operating system to put the system in five possible *global power* states:

- Working: The system is ON and fully usable.

- *Sleeping*: The system appears to be OFF and the power consumption is reduced. The system returns to the working state in an amount of time inversely proportional to the power consumption.

- Soft off: The system appears to be OFF and power consumption is very low. A full OS reboot is needed to restore the working state.

- *Mechanical off*: The system is OFF, with no power consumption. It needs to be reconnected to the power supply to go back to the working state after a full reboot.

- Legacy: This state is entered when the system does not comply with ACPI.

Additionally, the ACPI specifications define power states for system components. There are two types of system components, *devices* and *processor*, for which four power states are defined in the Table 1.1:

23

|           | Device power states                                                                                                                                                                               |           | Processor power states                                                                                                                                                                       |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0        | This state has the highest level of<br>power consumption. The device is<br>fully active.                                                                                                          | CO        | The processor is fully operational and executes instructions.                                                                                                                                |

| D1,<br>D2 | The details of these states are device<br>dependent. A device in D1 is ex-<br>pected to save less power than in D2,<br>but it preserves more context (hence,<br>wake-up is faster).               | C1,<br>C2 | The processor is not executing in-<br>structions. The processor in C1 is ex-<br>pected to save less power than in C2,<br>but switching from C1 to C0 is per-<br>formed in a negligible time. |

| D3        | Power has been fully removed from<br>the device. The device cannot be used<br>in this state and has the longest re-<br>store time. The OS will re-initialize<br>the device when powering back on. | <i>C3</i> | This state offers improved power sav-<br>ings with respect to C2. The hard-<br>ware latency to resuming execution is<br>larger than that in C2.                                              |

Table 1.1: Devices and processor power states

#### 1.3.3 Power manager observer

A power manager needs information to predict future workloads. Two extreme approaches allow to collect this information. In the first approach, the power manager observes the requests soliciting the managed component and try to predict the future idleness length, and on this basis determines the best power state. It selects the power state without direct interaction with requesting application. The figure 1.4 depicts this approach.

Figure 1.4: The power manager observes requests.

In reality, however, requests may be generated by multiple requesters. For example, requests for a network interface card may come from different programs (such as ftp, telnet or netscape). These programs work differently and have different performance requirements. Without information about requester programs, the power manager cannot precisely predict the exact moment when the component is not used anymore and thus wastes energy to maintain performance unnecessarily or cause delays and performance waste to save power.

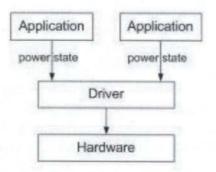

At the other extreme, requester programs directly control power management through an application programming interface (API). For example, programs can keep a component in a run state, wake up a component in the sleep state or know the current state of a component. The figure 1.5 describes this approach. The main disadvantage of this ap-

Figure 1.5: Applications control power states directly.

proach is that programs must include specific power management instructions. Moreover, programs do not know very well the components, especially the transition costs of each of them. They are not aware if changing state saves power.

Other solutions have been proposed, like in [2], which are generally situated between the two previous extreme approaches. Generally, in these other solutions, programs provide to the power manager an information about their needs of components. The power manager decides, according to the programs needs and its knowledge of the components transition costs, to put some components in sleep state if their are idle for a sufficient long period.

#### 1.3.4 Power manager policies

A power management *policy* is an algorithm that selectively shuts down idle resources based on the observation of present and past workload and operating conditions. We survey here two different approaches to policy optimization, the *predictive techniques* and the *stochastic control*.

The rationale in all *predictive approaches* is to take DPM decisions based on predictions concerning the duration of idle periods. A generic predictive method observes the time-varying workload, and, based on this observation, computes a predicted duration  $T_{pred}$  of

the upcoming idle time. The power manager then decides the transition to the sleep state if  $T_{pred} \geq T_{BE}$ , where  $T_{BE}$  is the *break-even time*, the minimum idle time amortizing the state transition cost.

Good predictive approaches should minimize the time for which the system wastes power because it does not immediately detect the beginning of an idle period. They also should minimize the mis-predictions  $T_{pred} \neq T_{idle}$ , where  $T_{idle}$  is the actual duration of an idle period. Predicting a too small  $T_{pred}$  ( $T_{pred} < T_{idle}$ ) wastes power, while a too long  $T_{pred}$ ( $T_{pred} > T_{idle}$ ) decreases performance.

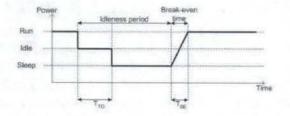

The most common predictive PM policy is the *fixed timeout*. The policy can be summarized as follows: when an idle period begins, a timer is started with a certain duration  $T_{T0}$ . If after  $T_{T0}$  the system is still idle, then the PM forces the transition to the sleep state. The system remains in sleep state until it receives a request from the environment that signals the end of the idle period. The fundamental assumption in the fixed timeout policy is that the probability of  $T_{idle}$  being longer than  $T_{BE} + T_{T0}$ , given that  $T_{idle} > T_{T0}$ , is close to one. Hence, this policy assumes that if the idleness duration is longer than the timeout duration ( $T_{idle} > T_{T0}$ ), the idleness duration will continue a sufficiently long time to allow the system to save power by changing the power state ( $T_{idle} > T_{T0} + T_{BE}$ ). Timeouts are "implicitly" predictive even if they never generate an actual  $T_{pred}$ , in the sense that they predict a long idle time if the system has been idle for a while. The critical design decision is obviously the choice of the timeout value  $T_{T0}$ .

Timeouts have three main limitations: fixed timeouts may be ineffective when the workload is non-constant. Moreover, power is wasted while waiting for the expiration of the timeout. Finally, performance penalty is always paid upon wake-up. *Adaptive timeouts* have been developed to improve effectiveness, by dynamically reducing/increasing the timeout value when idleness duration increases/decreases. The figure 1.6 illustrates the timeout-based policies.

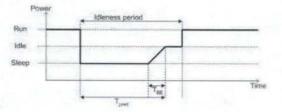

Another predictive policy consists of shutting down or putting in sleep state the system or a component as soon as it becomes idle, if the policy predicts  $T_{pred} > T_{BE}$ . A prediction of idle time duration is made available as soon as the idle period begins. Predictions are made based on past idle and activity period durations. The system wakes up either only upon arrival of a request from the environment, or at the end of the predicted idle period. The *predictive shutdown policy* is illustrated in the figure 1.7.

Predictive approaches have some limitations: first, they do not precisely take into account the workload variations. Then, predictive algorithms are based on a two-state system

Figure 1.6: Timeout-based policy.

Figure 1.7: Predictive shutdown policy.

model, while real-life systems have multiple power states. Policy involves not only the choice of when to perform state transitions, but also the choice of which transition should be performed.

The stochastic control approach considers the workload as a Markov chain of R states. A Markov chain is a probability function of the evolution of the system state, according to the state at present time. A Markov chain defines probabilities for the system to enter into a state at a moment t + 1, according to the system state at the moment t. Thus, the workload can be represented by a two-state Markov chain, where the two states are: R0when no request is issued by the environment and R1 when a request is issued.

In the same way, power states are also represented by a Markov chain of S states. The transitions are probabilistic, and probabilities are controlled by commands issued by the power manager. A power manager is then a function  $R \times S \to A$  where A is a command to control the future state of the system. Such function is an abstract representation of a decision process: the PM observes the power state S of the system and the state R representing the workload, takes a decision, and issues a command A to select the next state of the system.

#### 1.4 Dynamic power management at network level

In many cases, the systems are not isolated and interact between them. We call network a set of communicating systems. We can thus imagine a power manager that tries to minimize the global consumption of the whole network, rather than the individual consumption of each system. The power manager is so implemented as a *distributed* algorithm. This distributed algorithm takes autonomous decisions for each system in the network based either on local information, or on incomplete global network status data.

Currently, the DPM in such networked systems is not really still well developed.

### 1.5 Examples of dynamic power management techniques

This section describes some examples where dynamic power management techniques are used. Each subsection is focused on one of the main components of a portable computing system. Thus, we present here low-power techniques concerning respectively the battery, the processor, the memory, the hard disk and the network card.

#### 1.5.1 Battery-driven dynamic power management

Battery lifetime extension is a primary design objective for portable systems. Traditionally, battery life-time has been prolonged mainly by reducing average power consumption of system components. An analysis of battery discharge characteristics has allowed to develop new opportunities for life-time extension. [3] and [4] propose a class of policies, whose decision rules controlling the system operation state are based on the observation of both system workload and battery output voltage.

The proposed policies are based on three battery physical properties. First, the effective voltage of a battery decreases as the state of charge decreases. As a matter of fact, a battery is considered exhausted when its output voltage falls below a given voltage threshold (such as 80% of the nominal voltage). The second property is that the actual usable capacity (Number of Amps  $\times$  Number of hours) depends on the discharge current. More clearly, in a theoretical battery, requiring more power (for example twice more power) reduces battery lifetime proportionally (for example a reduction of a factor two). In a real battery, the lifetime reduction is more accentuated. The reason is that at higher discharge current, a battery is less efficient to convert its chemically stored energy into available electrical energy. The third property says that a battery can recover some of its deliverable charge if discharge periods are interleaved with rest periods (i.e. periods in which no current is drawn).

The simplest policy is threshold-based. It aims at maximizing battery lifetime by lowering the performance when the battery is almost discharged. If the battery is fully charged, the system is kept in a normal-performance state. When the battery output voltage falls below a threshold, the system is forced into a low-performance and low-power state until the battery is fully discharged. The rationale for this policy is to provide acceptable degradation of system performance as the battery discharges.

Some modern portable appliances can accommodate two batteries in the same case. The batteries are normally used sequentially: The second battery starts supplying the current only when the first battery is totally discharged. As a battery can recover some of its deliverable charge if it is let at the rest, a dual-battery system can alternatively use each battery to draw its energy. In this way, the battery temporarily disconnected from the load can recover, while the other one powers the system. An efficient policy to manage the batteries alternation consists of defining three regions of operation. In the first region, the switching between the two batteries has constant frequency, and the system works in a normal-performance state. The second region is entered when the output voltage of one battery first reaches a threshold. The system still works in normal state, but switching between batteries is voltage-controlled. When the output voltage of the loaded battery reaches the threshold, it is disconnected from the load (to give it some recovery time). The second region is exited when the output voltage of the battery temporarily disconnected from the load does not reach a level close enough to the threshold during the recovery time. In the third region, the fixed frequency-switching scheme is restored, and the system is transitioned into a low-performance state until both batteries are fully discharged.

The battery-driven policies proposed here, applied in isolation or altogether with another technique(s), allow a very important lifetime extension in some systems.

## 1.5.2 Power management for the processor: Dynamic voltage scaling

DPM aims at reducing energy consumption at the system level by selectively placing components into low-power states during idle periods. The power manager can completely turn off the component (power off supply) or disable some clocks to do that (clock gating). In the microprocessors, other techniques have been developed to decrease significantly the energy consumption. If clock gating is an efficient technique to reduce the energy in clocked components, *dynamic voltage scaling* (DVS) is often an additional technique that can more reduce the power consumption. DVS can be used simultaneously to the clock gating.

We can compare in fact DVS to a kind of DPM at the component level except that DVS is targeting specifically the processor. DVS is close to clock gating because both act on the clock frequency except that DVS does not turn off the clock but changes the frequency of the processor (the speed of the processor) and voltage at run-time, depending on the needs of the running application. Thus DVS do not thus detect idleness period but rather estimate the needs of the running application. When peak performance is needed (e.g. peak computational loads), the processor operates at its normal voltage and frequency (which is also its maximum frequency). During the rest of the time, when the load is lower, the operating frequency is reduced to meet the computational requirements (performance). In fact, once again, it is assumed implicitly that the *workload* is not constant and that the average computational throughput is often much lower than the peak computational capacity needed for adequate performance.

DVS algorithms modify the frequency according to the needs of the running application and go beyond that because they scale the operating voltage of the processor along with the frequency. In fact, the vast majority of microprocessors today has a voltage-dependent maximum operating frequency, so that when they are used at a reduced frequency, the processor can operate at a lower supply voltage. In other words, the maximum operating frequency increases (within certain limits) with the increased operating voltage; when the processor is run slower, a reduced operating voltage suffices. The interest of reducing the operating voltage along the frequency is obviously to save energy. There is a second characteristic also shared by the vast majority of microprocessors today, allowing saving energy: the energy consumed by the processor per clock cycle scales quadratically with the operating voltage, so that even a small change in voltage can have a significant impact on energy consumption. Moreover, important energy savings can be got because high performance is needed only for a small fraction of the time, while for the rest of the time, a low-performance and low-power processor would suffice. By dynamically scaling both voltage and frequency of the processor based on computation load, DVS can provide the performance to meet peak computational demands, while on average, providing the reduced power consumption benefits typically available on low-power performance processors.

To decrease the frequency along with the needs of the application, the processor must operate over a range of frequencies. For that, it must be specifically hardware-designed to support dynamic clock frequency adjustment. The number of frequencies is thus predefined by the design of the microprocessor. As we have already pointed it out in previous sections for the different *states* in the DPM model, there is also some overhead here when switching from a frequency to another one. This overhead is also called transition time, like in the DPM model. Nevertheless, even if it depends a lot from the hardware, the transition time overhead is often very short.

If DVS relies on a specific hardware design, we can say that it relies also on software at the system level, or even at the task level. DVS algorithms have in fact two main functions: the first one identifies the needs of the application and the second one adjusts effectively the CPU frequency and voltage. To accomplish the first "mission", the execution time of the application has to be predicted (by analyzing the workload). It is important to note that this execution time can be increased (performance decreases) if the frequency is decreased, but the main challenge is to respect the needs of the running application or, in other words, to keep an *adequate* performance. In fact, "respect the needs" or "keep an adequate performance" can be formulated like the respect of the deadline of a task in a real-time environment where tasks must be completed before a deadline, or like keeping a frame delay constant for a MPEG or MP3 streaming application. There are in fact a lot of models implemented in software (at the system level or at the task level) that try to get accurate information on the workload in order to adapt the frequency of the processor on the basis of this information while keeping an adequate performance . We can also define for DVS the notion of *policy*, which is an algorithm that selectively adjusts the clock frequency and voltage of the processor based on the observation of the workload.

In fact, we can easily integrate the DVS technique into the DPM model presented in previous sections at the system level. We can consider that the processor *remains* in a *run* state when the DVS algorithm is applied. It allows reducing the energy consumption of the processor when the processor is in a *run* state. Let us remind that, when in previous sections, we talk about the *run* state, the component consumes a lot of energy because it is fully powered on. In reality, we can see here the *run* state like a set of sub-states.

If the model describing the *run* state is the same as the one characterizing the other states, the transformation, from the "original" DPM *run* state into multiple "new" *run* states taking into account the different performance and power levels of DVS, is completely compatible with the rest of the model and so, the power management *policy* that we develop can make decisions for both dynamic voltage setting and the transition into the low-power states. For example, in the case of a MPEG streaming application where keeping an adequate performance consists in maintaining the frame delay constant, the power manager can check if the rate of incoming or decoding frames has changed, and then adjusts the CPU frequency and voltage accordingly. Once the decoding is completed, the system enters in an *idle* state. At this point, the power manager observes the time spent in the idle state, and depending on the policy, it decides when transiting into one of the *sleep* states. When a request arrives for video decoding (after receiving a new frame on the network interface), the power manager switches the system back into the active state and starts the decoding process. That is actually the ratio between the rate of incoming frames and the rate of decoding frames that determines the frequency and the voltage levels of the processor.

It is to be noted that a dilemma appears and can be stated as follow: lowering the threshold voltage to reduce *run* power can increase *sleep* power. In fact, increasing the execution time of applications by reducing the frequency causes the system to be more often in the *run* state than in the *sleep* state. In other words, if a system is frequently *idle*, it could be more interesting to save power by putting the system in the *sleep* state instead of decreasing the frequency and the voltage of the processor.

#### 1.5.3 Selective instruction compression for memory energy reduction

We have already seen that power management can be applied to several embedded components. It is time now to see how we can save power in the memory management.

The first developed techniques are bus encoding techniques and memory organization techniques. Both are based on a reduced switching activity on the processor-memory bus. In fact, the first technique changes the format of the information transmitted on the processor-memory bus. Thus, it reduces the switching activity on the bus and so, in the same way, reduces the power consumption. The second techniques change the way information is stored in memory so that the address streams between the processor and the memory cause a low-transition activity on the bus. The processor-memory interface is a major contributor in the power consumption and so, these techniques can be efficient.

Other techniques have been additionally developed through instruction memory bandwidth. These techniques use a set of special instructions which are smaller in size (e.g., contain less bits than normal instructions) and hence, achieve to reduce the bandwidth needed to run the program. Either these special instructions are another set of instructions supported by the processor but in this case it often requires additional software tools to allow users to generate these special machine instructions from the task level, or these special instructions are simply a subset of the original instructions supported by the processor. In this latter case, if we consider only a subset of the original instructions, we decrease the number of potentially instructions. Thus this subset of instructions can be replaced by binary patterns of limited width. For example, if we identify in an application the utilization of 512 distinct instructions among the 8192 instructions offered by the processor, we can then only use 9 bits to encode the 512 instructions ( $log_2 512 = 9$ ) instead of 13 bits needed to encode 8192 distinct instructions ( $log_2 8192 = 13$ ). The 9-bit instructions take less place in memory than 13-bit instructions. It thus reduces the memory bandwidth usage and in consequence the total energy because the unused memory banks can be disabled.

We suppose in fact that the processor can disable the memory banks that are not currently used in order to save energy. It is an hardware requirement to save energy. For example, if the memory consists of four 8-bit banks and that we have succeeded in reducing the size of the instructions from 32 to 8 bits, it requires only one memory bank instead of 4. The 3 unused banks can be disabled to save energy. Moreover, if we assume that the memory access is 8-bit wide, the number of fetching between the processor and the memory passes from 4 to 1: the total bus utilization is thus also reduced, which improves performance (i.e., the program utilization time decreases).

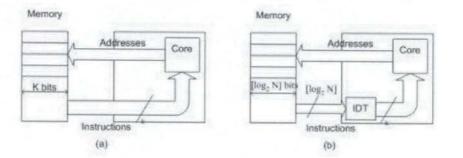

We can simply implement a table whose the role is to match the original instructions of the subset with the compressed instructions. In reality, the program is stored in memory in compressed format, i.e., each instruction is replaced with a  $[log_2N]$ -bit binary pattern which is in one-to-one correspondence with the original instruction. Every time an instruction is fetched from the memory, it is first decompressed (i.e., the original format is restored) by means of the *instruction decompression table* and then passed to the processor's decoding logic. The advantage of the table is that we do not modify the architecture of the processor. The figure 1.8(b) depicts the solution and especially the *instruction decompression table* (IDT). The main drawback of this technique is the energy saving depends on

Figure 1.8: Processor-memory normal architecture (a) and power-saving architecture (b)

the ratio between the number of different instructions that forms the subset (compressed instructions) and the total number of machine instructions. The more distinct instructions are used, the more there are instructions in the subset and therefore, fewer energy is saved. Indeed, the bit-width of these instructions may become similar to the bit-width of the original instructions, thus making negligible the reduction in memory bandwidth. The second drawback is the implementation of the table because this can be very complicated to encode and decode instructions especially if the size of the compressed instructions is not compatible with the byte-addressable memory. Indeed, usually memories can be only accessed for example by a multiple of 8 bits. If we refer to the example in the previous paragraph where the application uses only 512 instructions among the 8192 instructions supported by the processor, the 9-bit instruction is not compatible with the 8-bit access scheme of the memory. In fact, two bytes are needed to store each compressed instruction and so, it results in a waste of space and consequently in a waste of energy. Moreover, it requires two operations to store this 9-bit instruction in memory and so, it does not decrease the program utilization time.

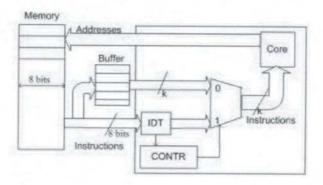

One solution consists of taking a subset of fixed cardinality. That does not depend anymore on the number of distinct instructions used by each application running but rather on the probabilities of the instructions to be used. In fact, an assumption is indirectly made: the number of machine instructions used by most software programs, although limited with respect to the total number of instructions supported by the processor, has a highly nonuniform statistical distribution. In other words, some instructions are usually much more used than others. We can hence consider a subset of original instructions that are executed more often whatever the applications; less probable instructions are left unchanged and stored as they are in memory. As there are as well non-compressed (few) instructions as compressed (many) instructions in memory, that requires a controller which properly handles instruction fetching. The figure 1.9 depicts the second power-saving architecture in the case where the compressed instruction has 8-bit width.

Figure 1.9: Processor-Memory second power-saving architecture

The percentage of energy that can be saved depends mainly on the architecture and espe-

cially on the way in which the memory is organized and accessed. The technique presented here is indeed a new way of managing and accessing the memory since there are different bit-width instructions. We have not presented all the implementation and changes that this technique required in the memory management. However, it is directly implemented in hardware and so, it is application-independent. It is important to say also that, like in all other power management techniques, there are some *costs* to take into account in this power management technique. In fact, the *instruction decompression table* (IDT) consumes a certain time to decode and to encode instructions, and therefore it consumes power. This cost in power and performance of the decompression block is not still well-known and is currently under investigation. In addition to that, to distinguish compressed and original instructions, it is needed to put sometimes some bits in memory and this causes also some overheads in the number of memory accesses, as well as a waste of space. Thus, the costs in term of performance or energy exist also for these techniques aiming at reducing the consumption of energy by the memories. Like in all other power management techniques, there is always a trade-off between performance and power.

#### 1.5.4 Power management for hard disks

The hard disk drive is one of the major power consuming subsystems in a computer, since it can consume more than one fifth of the total power used by the computer. The main way to reduce power consumption of hard disks consists of stopping plates spinning during the periods when no disk requests are made. However, this approach encounters three problems: first, when a request occurs while plates are not spinning, it can not be performed before the plates have taken back a sufficient speed. This delay strongly decreases the performance of the system. Moreover, accelerating the plates generates extra power dissipation. Finally, too frequent on/off cycles tend to accelerate the degradation of the hardware systems, causing a problem of reliability. Now a desirable power management scheme should save energy while providing high performance and low failure rates.

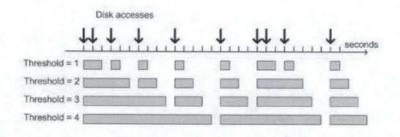

Disks accesses generally occur in burst: the activity of a disk is often characterized by sets of close requests, separated by long idle periods. It can be made use of these idle periods to reduce power consumption. In [5], a method is proposed to do that, on the basis of the concept of *sessions*, which are time intervals when requests frequently occur. A session starts with a disk access, and is separated from the previous one by a long period of inactivity. Requests close in time are regrouped in the same session. A threshold  $\tau$  is used to separate sessions. If no requests occurs during  $\tau$  seconds after a request occurrence, the current session ends. The figure 1.10 depicts an example of sessions with different  $\tau$ .

A first observation is that, during inter-session periods, there are no disk activities, and

Figure 1.10: Example of sessions for different thresholds.

then the system can spin down the plates to save power. Moreover, smaller  $\tau$  may separate adjacent requests into two sessions, while a larger value can regroup them into one. Hence, a large  $\tau$  allows to reduce the number of inter-sessions, while a small  $\tau$  increases their occurrences. Thus, a variable  $\tau$  can be used to improve performance according to the access frequency: by increasing  $\tau$  during access bursts, one increases the waiting time before the session ends, and thus reduces the risk to spin down the plates before the end of the burst. In the same way,  $\tau$  can be decreased when the disk activity is characterized by long idleness periods separated by short bursts.

# 1.5.5 Transport protocol optimization for energy efficient wireless embedded system

For wireless portable systems, the power consumption in the network interface plays an important role for the battery lifetime. Although there are already some DPM techniques allowing to put the network interface card in several possible states (receive state, transmit state, idle state, sleep state,...), the power consumption can be optimized by developing techniques at an upper level, and in particular at the network protocols level. Indeed, the higher sub-layers of the protocol (IP, TCP, UDP,...) allow to estimate the long-term workload, while the Medium Access Control (MAC) sub-layer allows to know the channel state. This optimization is especially needed since transition costs are very important. Hence, the challenge in developing an effective power management strategy is to identify the times during which the sub-system can be placed in a particular power mode, by observing the workload.

The IEEE 802.11 protocol describes how the physical and MAC sub-layers must be implemented. IEEE 802.11 defines two modes: a normal mode and a low-power mode. When the network card is in low-power mode, it is shut down and the received data packets are lost. Fortunately, these packets are kept by the access point. IEEE 802.11 specifies that the network card must be periodically awaken to check if the access point keeps data packets. The main drawback of this technique is that the card wakes up to check the access point, even if no packets are waiting. It generates thus a power consumption overhead.

A transport protocol optimization of wireless LAN interfaces has been proposed in [6]. The proposed technique is based on the TCP buffer. It consists of monitoring the TCP receive buffer occupancy and exploiting in-built signaling mechanisms of TCP, such as window advertisement<sup>3</sup> and silly window syndrome<sup>4</sup> (SWS) avoidance, to identify scenarios where low power modes can be triggered with minimal overheads. Two extreme cases can occur: TCP receive buffer full and TCP receive buffer empty.

TCP disposes of a mechanism preventing the receive buffer from overflowing. When the receive buffer is full, the receiver sends a zero window<sup>5</sup> to the sender. This message signals to the sender that it has to stop sending packets. As the application reads data out of the receive buffer, the window becomes non-zero, but it is not immediately advertised to avoid the silly window syndrome. In fact, the receiver has to wait until its window has considerably increased, to prevent the inefficient exchange of small amounts of data across the connection (instead of full-sized segments). Hence, in order to avoid the silly window syndrome, the receiver waits before requesting to the sender to resend data packets. The receiver can take advantage of this waiting time to save power by switching off the network card. Indeed, the receiver knows that it will not receive data packet during this period. Generally, this period can last several seconds before the receive buffer is sufficiently empty to allowing the sender to resend data packets.

Another idleness condition that can be exploited at the transport layer occurs when the buffer is empty. However, power management actions have to be taken carefully when the buffer is empty because, even if no packets are presently stored, they might be in transit over the network. Ensuring that incoming packets are not dropped can be performed by a predictive approach. Thus, the traffic flow can be predicted considering the status of the outstanding TCP sockets. If no socket is actively used by the receiver, the network card is considered as idle and can be shut down. When the buffer of the receiver is empty, a timer is started. If the timer expires, the card is shut down until a read/write operation

$<sup>^{3}</sup>$ To avoid overflowing the buffer, TCP sets a Window Size field in each packet it transmits. This field contains the amount of data that may be transmitted into the buffer. If this number falls to zero, the remote TCP can send no more data. It must wait until buffer space becomes available and it receives a packet announcing a non-zero window size.

<sup>&</sup>lt;sup>4</sup>The silly window syndrome occurs when the receiver authorizes too early the sender to continue the transmission. "Too early" means that the receive buffer is not sufficiently empty yet. As a consequence, the receiver signals a "small window", so that the sender will send small data packets in burst, a situation to be avoided.

<sup>&</sup>lt;sup>5</sup>Message signaling to the sender that the receive buffer is full.

on the buffer occurs. At this moment, the card is switched on. If a read/write operation on the buffer occurs before the timer expiration, the timer is cancelled and then restarted.

# Chapter 2

# System description

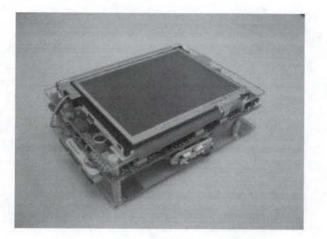

This chapter describes the system Assabet used for this work. The first section presents the PDA concerned by the power management. The second section explains what is and how is organized the frame buffer memory. The third section gives more details about the displaying of pixels, and the last section describes the LCD controller registers.

# 2.1 Overview of the Assabet

LCD power management has been implemented on a PDA plateform, the Assabet, supplied by HP. The Assabet disposes of a StrongARM 1110 Microprocessor [7], which can operate with an internal clock frequency up to 221 MHz. The Assabet has 8 MBytes FLASH and 32 MBytes DRAM. The screen used for the experimentation is a Sharp 3.9" TFT LCD touch screen which supports either 8-bit or 16-bit color at  $320 \times 240$  pixels.