## LOW-COST TEST AND CHARACTERIZATION PLATFORM FOR MEMRISTORS

by

Lyle Jones

A thesis

submitted in partial fulfillment

of the requirements for the degree of

Master of Science in Electrical and Computer Engineering

**Boise State University**

May 2020

© 2020

Lyle Jones

ALL RIGHTS RESERVED

## BOISE STATE UNIVERSITY GRADUATE COLLEGE

## DEFENSE COMMITTEE AND FINAL READING APPROVALS

of the thesis submitted by

Lyle Jones

Thesis Title: Test and Characterization Platform for Memristors

Date of Final Oral Examination: 12 December 2019

The following individuals read and discussed the thesis submitted by student Lyle Jones, and they evaluated the student's presentation and response to questions during the final oral examination. They found that the student passed the final oral examination.

| Nader Rafla, Ph.D.      | Chair, Supervisory Committee  |

|-------------------------|-------------------------------|

| Maria Mitkova, Ph.D.    | Member, Supervisory Committee |

| Benjamin Johnson, Ph.D. | Member, Supervisory Committee |

The final reading approval of thesis was granted by Nader Rafla, Ph.D., Chair of the Supervisory Committee. The thesis was approved by the Graduate College.

DEDICATION

To My Dad, Richard Jones.

### ACKNOWLEDGEMENTS

I have a deep admiration for my advisor, Dr. Nadar Rafla, who advised me and gave me constant encouragement. Dr. Rafla supplied my research with equipment and gave me a sense of belonging to the department. His belief that I could learn anything he put in front of me, and ingraining into me a just "Learn it Attitude", inspires me today. I would have not completed my course work, and research with personal growth without him being my advisor.

Dr. Maria Mitkova supplying the research with parts (memristors), having me package the memristors with a vendor, allowing me access to her lab, working as a team with her students, having me mentor students with projects with a calm and steady hand, taught me leadership. Her deep knowledge of the physics of the device was invaluable to the understanding of results and forming hypotheses in the research. Dr. Mitkova's overall guidance in situational issues, organization of the projects, and her willingness to let me try, allowed me to grow as an Engineer and I am grateful to her.

Steve Wald as my peer researcher, showed incredible patience to listen to every idea that I came up with. This helped me to sift through the ideas, to pick out the good ones, and not to waste time on the bad. Many hours Steve sat with me to debug a new test or setup of equipment that I came up with. These long debug sessions would lead to debates of what really happened, did it work right, is the data good, and did I get the right data to finally come to a conclusion. I will always remember his generosity in his time and thought. My lab mates, coworkers, friends, and family, thank you for your continuous support with the ear you lent me. Your listening was invaluable to me, as it allowed me to express my frustration, my excitement, my ideas in why something happened, my doubts if I could do it again, and did I really get something to work. This support was my bedrock of my research.

## ABSTRACT

The electrical Testing and Characterization of the devices built under research conditions on silicon wafers, diced wafers, or package parts have hampered research since the beginning of integrated circuits. The challenges of performing electrical characterization on devices are to acquire useful and accurate data, the ease of use of the test platform, the portability of the test equipment, the ability to automate quickly, to allow modifications to the platform, the ability to change the configuration of the Device Under Test (DUT) or the Memristor Based Design (MBD), and to do this within budget. The devices that this research is focused on are memristors with unique test challenges. Some of the tests performed on memristors are Voltage sweeps, pulsing of Voltages, and threshold Voltages. Standard methods of testing memristors usually require hands-on experience, multiple bulky work stations, and hours of training.

This work reports a novel, low-cost, portable test and characterization platform for many types of memristors with a voltage range from -10V to +10V, which is portable, low-cost, built with off-the-shelf components, and with configurability through software and hardware. To demonstrate the performance of the platform, the platform was able to take a virgin memristor from "forming" to operation voltages, and then incrementally change resistances by Voltage Pulsing. The platform within this work allows the researcher flexibility in electrical characterization by being able to accept many memristor types and MBDs, and applying environmental conditions to the MBD, with this flexibility of the platform the productivity of the researcher will increase.

# TABLE OF CONTENTS

| DEDICATIONiv                                                    |

|-----------------------------------------------------------------|

| ACKNOWLEDGEMENTSv                                               |

| ABSTRACTvii                                                     |

| TABLE OF CONTENTS viii                                          |

| LIST OF TABLES xi                                               |

| LIST OF FIGURES xii                                             |

| LIST OF ABBREVIATIONS xvii                                      |

| CHAPTER 1 : INTRODUCTION                                        |

| Device variability1                                             |

| Motivation2                                                     |

| Problem Statement                                               |

| Impacts of memristor life cycle on electrical characterization5 |

| Thesis Organization                                             |

| CHAPTER 2 : A REVIEW OF OPERATING VOLTAGES AND LITERATURE       |

| Introduction: Memristors7                                       |

| The Polarity of Memristors10                                    |

| Types of Memristors12                                           |

| Anion Memristors13                                              |

| Cation Memristor17                                              |

| Carbon-based Memristor                                                                                               | 19 |

|----------------------------------------------------------------------------------------------------------------------|----|

| Spin-Based and Magnetic Memristive Systems                                                                           | 22 |

| Thermal (Phase Change) Memristor                                                                                     | 24 |

| Conclusion                                                                                                           | 27 |

| CHAPTER 3 : THE MEMRISTOR USED TO TEST THE TEST<br>CHARACTERZATION PLATFORM                                          | 29 |

| Introduction                                                                                                         | 29 |

| The Memristor Fabricated for the Development of the Test and Characterizat                                           |    |

| Bottom Electrode (Cathode) Layer                                                                                     | 32 |

| Via Layer                                                                                                            | 32 |

| Active Layer                                                                                                         | 33 |

| Top Electrode (Anode) Layer                                                                                          | 34 |

| Exposing Cathode layer                                                                                               | 34 |

| CHAPTER 4 : ELECTRIAL CHARACTERIZATION AT WAFER LEVEL AND PACKAGING                                                  | 36 |

| The Electrical Characterization Details                                                                              | 36 |

| Electrical Characterization of the Direct Current Station: Virgin Sweep and Forming the Cationic Columnar Memristor. | 37 |

| The Packaging of Memristors                                                                                          | 41 |

| CHAPTER 5 : THE PULSE GENERATOR STATION                                                                              | 45 |

| Introduction                                                                                                         | 45 |

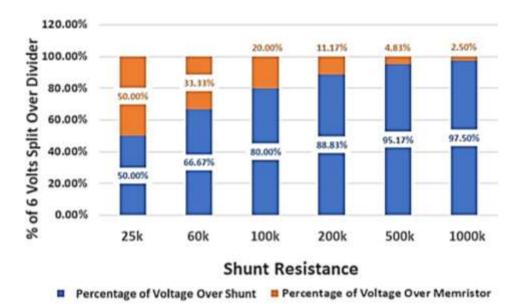

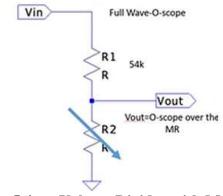

| The Voltage Divider (Shunt Resistor)                                                                                 | 45 |

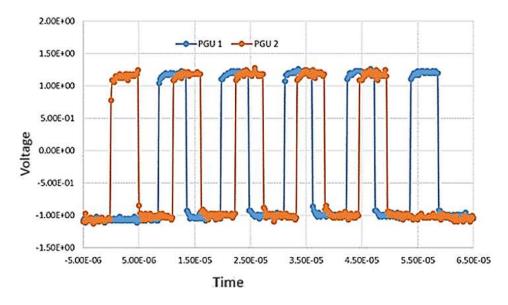

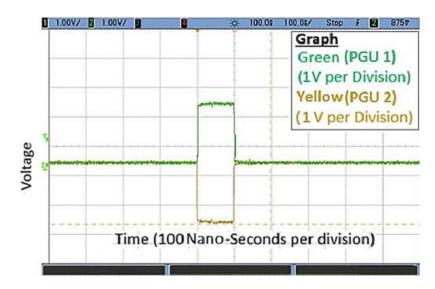

| Pulsing Synchronization of Two PGU's                                                                                 | 49 |

| PGU Testing with a MBD                                                                                               | 53 |

| PGU Setup Conclusion59                                                  |

|-------------------------------------------------------------------------|

| CHAPTER 6 : THE TEST AND CHARACTERIZATION PLATFORM60                    |

| Introduction                                                            |

| The Test and Characterization Platform Design60                         |

| Parts List of the Test and Measure Platform67                           |

| The Build of the Test and Characterization Platform                     |

| The Programming of the Platform73                                       |

| The Experiments Performed with the Test and Characterization Platform75 |

| Reducing the Virgin Memristor to a Low Resistive State76                |

| Forming of the Memristor77                                              |

| Operation of the Memristor79                                            |

| Multiple MBDs Constructed for the Test and Characterization Platform82  |

| The Build of the Test and Characterization Platform Conclusion85        |

| CHAPTER 7 : SUMMARY AND CONCLUSION                                      |

| REFERENCES                                                              |

| APPENDIX A100                                                           |

| APPENDIX B                                                              |

## LIST OF TABLES

| Table 1.1 | Memristors Operating Voltages Polarity [6]                                      | .4 |

|-----------|---------------------------------------------------------------------------------|----|

| Table 2.1 | Types of Memristors and Operating Voltages                                      | 13 |

| Table 6.1 | Enabling Outputs of the MAX5661 (1-Pin Set to VCC, 0-Pin Set to Ground) [78]    | 67 |

| Table 6.2 | Part List for the Test and characterization Platform [74, 75, 76, 77, 78, 7 80] |    |

## LIST OF FIGURES

| Figure 1.1  | Example of PCM Memristor type [4]                                                                                                                                                                                |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.1  | How a Memristor fits with a Resistor, Capacitor, and Inductor [14] 7                                                                                                                                             |

| Figure 2.2  | Chua's Memristor and its Φ-q Curve [2]8                                                                                                                                                                          |

| Figure 2.3  | I-V Curve of a Resistor, a Capacitor, an Inductor, and a Memristor [16]. 10                                                                                                                                      |

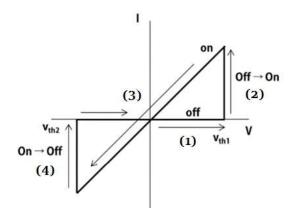

| Figure 2.4  | Voltage Sweep Measuring Current: Bipolar Memristors [18]11                                                                                                                                                       |

| Figure 2.5  | Voltage Sweep Measuring Current: Unipolar Memristors 11                                                                                                                                                          |

| Figure 2.6  | Voltage Sweep Measuring Current: Near Unipolar Memristors                                                                                                                                                        |

| Figure 2.7  | Anion Memristor's Operation [17] 14                                                                                                                                                                              |

| Figure 2.8  | Vertical Sandwich of the HP Memristor [15]15                                                                                                                                                                     |

| Figure 2.9  | Diagram of the Electrical Operation of Titanium Dioxide Memristors [15]<br>                                                                                                                                      |

| Figure 2.10 | I-V Characteristics of Titanium Dioxide Memristors [15] 16                                                                                                                                                       |

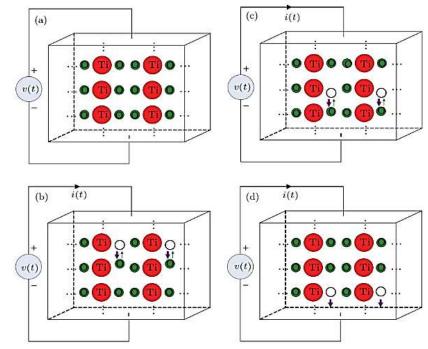

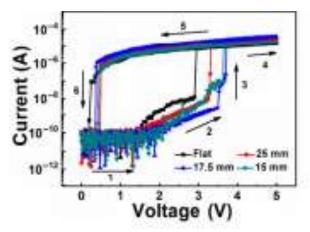

| Figure 2.11 | TiN/ZHO/IGZO Flexible Anion Memristor: Flexed with IV (0 V $\rightarrow$ 5 V $\rightarrow$ 0 V (with the Numbered Arrows 1 $\rightarrow$ 2 $\rightarrow$ 3 $\rightarrow$ 4 $\rightarrow$ 5 $\rightarrow$ 6) [35] |

| Figure 2.12 | Filament Forming in a Cation Memristor [41] 18                                                                                                                                                                   |

| Figure 2.13 | Different Cation Memristor Voltage Sweeps [41] 18                                                                                                                                                                |

| Figure 2.14 | Scanning Tunneling Microscope of Vertically Aligned Carbon Nanotube<br>Array [45]                                                                                                                                |

| Figure 2.15 | Bundling of Carbon Tubes [45] 20                                                                                                                                                                                 |

| Figure 2.16 | Electrical Characterization of Tip [45] 20                                                                                                                                                                       |

| Figure 2.17 | Some Types of Carbon Memristors [47]                                                                                                                                                                             |

| Figure 2.18 | IV Characteristics of Different Carbon Stacks [47]                                                                                                            | 22 |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.19 | Magnetic Cell [50]                                                                                                                                            | 22 |

| Figure 2.20 | Switching Voltage vs Pulse Width of a MJt Memristor [53]                                                                                                      | 23 |

| Figure 2.21 | Spin Based Memristors: (a) Electrical Hookup of Spintronic Memristo<br>Voltage Pulse in Time vs Current Density [54]                                          |    |

| Figure 2.22 | High/Low Resistivity Compared to the Lattice Structure of the PCM Device [57]                                                                                 | 25 |

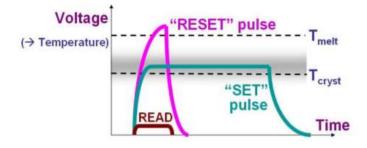

| Figure 2.23 | Reset and Set Pulses for PCM Resistance [57]                                                                                                                  | 25 |

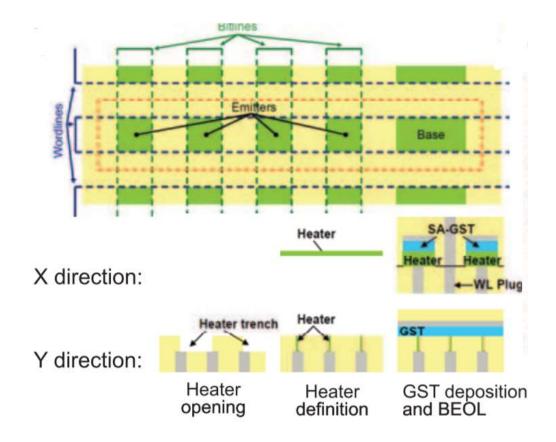

| Figure 2.24 | Typical PCM Integration into an Array [57]                                                                                                                    | 26 |

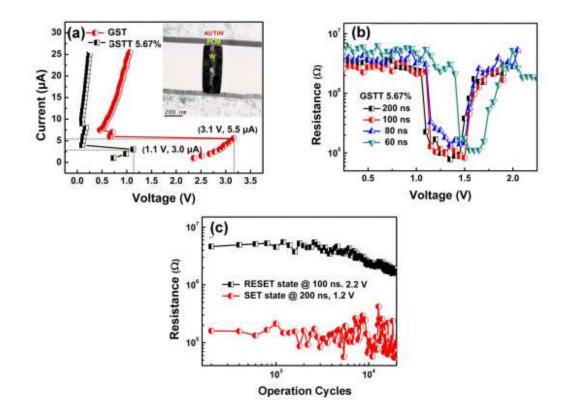

| Figure 2.25 | Ge2Sb2Te5 (GST) PCM Device: a) Non-Doped vs Doped with Ti:<br>Current Forced b) Pulse Width vs Voltages c) Doped at 5.67% of Ti: S<br>and Reset Voltages [44] |    |

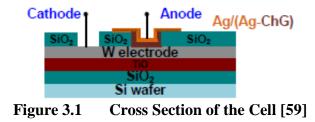

| Figure 3.1  | Cross Section of the Cell [59]                                                                                                                                | 30 |

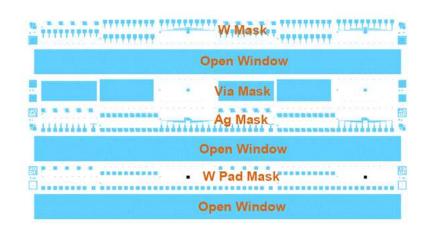

| Figure 3.2  | Mask (All in one Layer) [59]                                                                                                                                  | 30 |

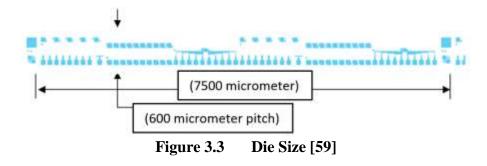

| Figure 3.3  | Die Size [59]                                                                                                                                                 | 31 |

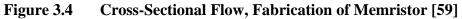

| Figure 3.4  | Cross-Sectional Flow, Fabrication of Memristor [59]                                                                                                           | 31 |

| Figure 3.5  | Via Angle Overview [59]                                                                                                                                       | 32 |

| Figure 3.6  | AFM Images of the Columnar Structure [60]                                                                                                                     | 33 |

| Figure 3.7  | Anodes with Pads [59]                                                                                                                                         | 34 |

| Figure 3.8  | Exposing Bottom Cathode [59]                                                                                                                                  | 34 |

| Figure 3.9  | Photos of Devices and Pads Produced by the 3-1 Mask that was Physic<br>Shifted Vertically (a) Active Die Area Boxed in Red                                    | •  |

| Figure 4.1  | 6200 Micromanipulator Probe Station and DCM210 [62]                                                                                                           | 36 |

| Figure 4.2  | Hewlett Packard 4155B [63]                                                                                                                                    | 37 |

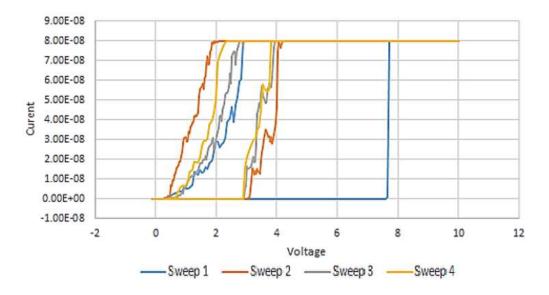

| Figure 4.3  | Forming: First 4 Sweeps at 80nA Compliance                                                                                                                    | 39 |

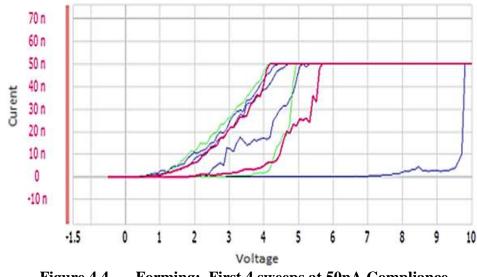

| Figure 4.4  | Forming: First 4 sweeps at 50nA Compliance                                                                                                                    | 40 |

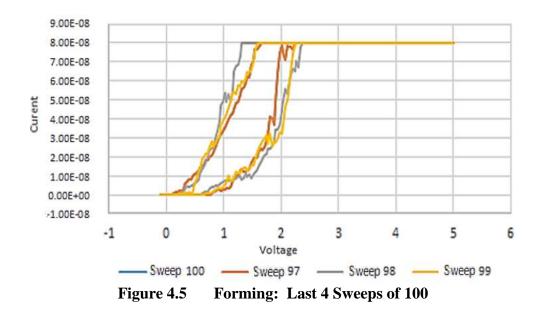

| Figure 4.5  | Forming: Last 4 Sweeps of 100 40                                                                                                                                                                                                                                                                  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4.6  | Singulation of the Memristor Wafer (Blue Arrows=Saw lines)                                                                                                                                                                                                                                        |

| Figure 4.7  | Testing of the Package Part on the Micro-Manipulator Probe Station 42                                                                                                                                                                                                                             |

| Figure 4.8  | Forming: Voltage Sweep of a Virgin Device after Packaging                                                                                                                                                                                                                                         |

| Figure 4.9  | Forming: Voltage Sweep 98 to 100 after Packaging 43                                                                                                                                                                                                                                               |

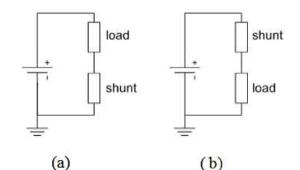

| Figure 5.1  | Setup of Shunt Resistor (a) Load First Memristor (b) Load Last Memristor [71]                                                                                                                                                                                                                     |

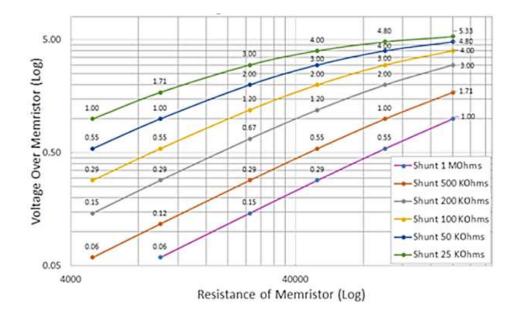

| Figure 5.2  | Different Shunt Resistors vs. Memristor's Resistance Varied in Voltage<br>Divider (Voltage Applied over the Divider at 6V):                                                                                                                                                                       |

| Figure 5.3  | Percent Voltage Drop Over the Memristor at 25 kOhms vs. Shunt<br>Resistance                                                                                                                                                                                                                       |

| Figure 5.4  | Voltage Divider with Memristor                                                                                                                                                                                                                                                                    |

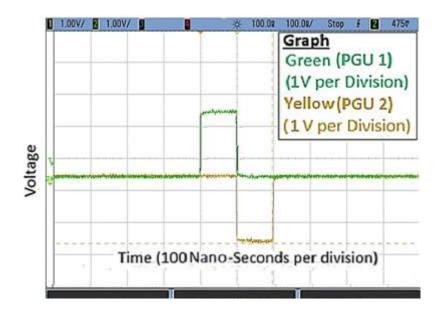

| Figure 5.5  | PGU's Without Synchronization Clock Both PGUs Triggered for Five<br>Pulse Burst                                                                                                                                                                                                                   |

| Figure 5.6  | 2 PGU's Using Synchronized Clock (External Clock)                                                                                                                                                                                                                                                 |

| Figure 5.7  | Offset Negative and Positive Pulses Synchronized                                                                                                                                                                                                                                                  |

| Figure 5.8  | Multiple Pulsing vs. Single Pulsing                                                                                                                                                                                                                                                               |

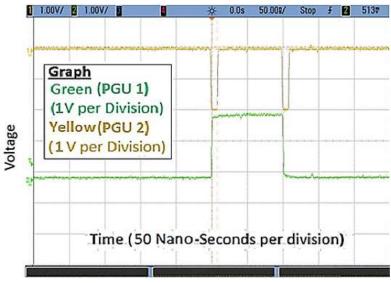

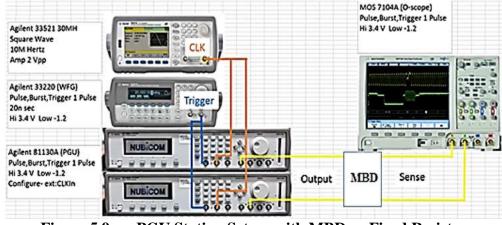

| Figure 5.9  | PGU Station Set up with MBD or Fixed Resistor                                                                                                                                                                                                                                                     |

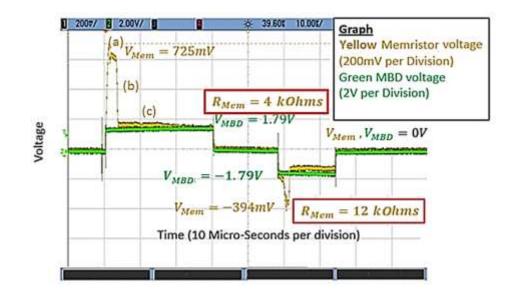

| Figure 5.10 | PGU Station Pulsing: MBD (Divider-Memristor) PGU1 (Positive<br>Voltage) PGU2 (Negative Voltage) (a) Adjustment to Resistance in Near-<br>off State-Forming Filament (b) Rapid Change in Resistance-Filament<br>Formed (c) Adjustment to Resistance in Near-On State-Thickening of<br>Filament. 54 |

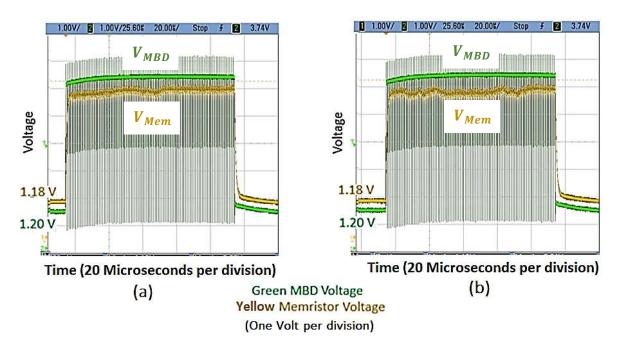

| Figure 5.11 | Recovery from High Resistance: 100 Voltage Pulses in 0.50 Microsecond<br>Width with 50% Duty Cycle. Voltage over MBD is Approximately 6.2<br>Volts. (a) Voltage over Memristor is Approximately 5 Volts (b) Voltage<br>over Memristor is Approximately 5 Volts                                    |

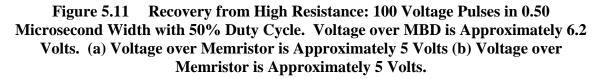

| Figure 5.12 | Recovery from High Resistance: 150 Voltage Pulses in 0.50 Micro-<br>Second Width with 50% Duty Cycle. Voltage over MBD is                                                                                                                                                                         |

|             | Approximately 6 Volts. (a) Voltage over Memristor is Approximately 5 Volts. (b) Voltage over Memristor is Approximately 0.6 Volt |    |

|-------------|----------------------------------------------------------------------------------------------------------------------------------|----|

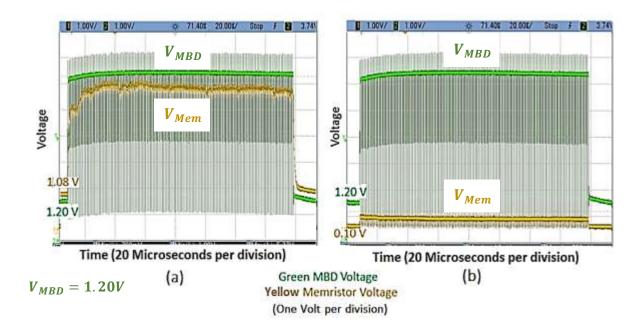

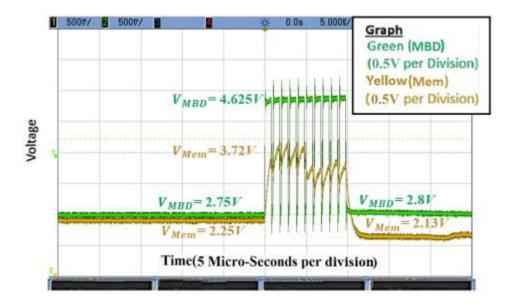

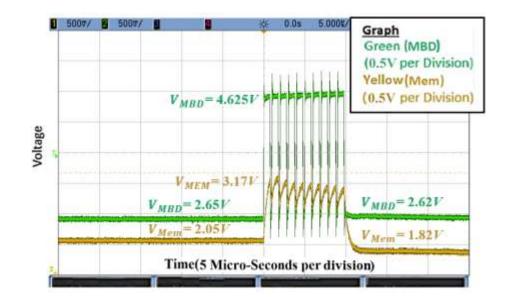

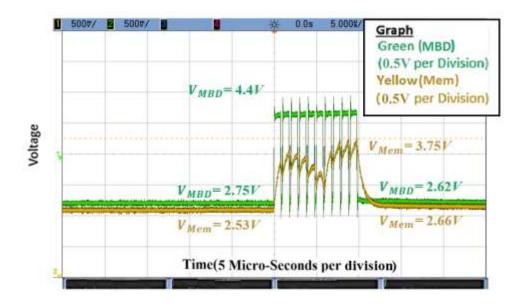

| Figure 5.13 | Pulsing the MBD (1) (Divider): 2.75 Volts floor, and 10 pulses of 1.9 Volts with a Width of 4 Micro-Seconds at 80% Duty Dycle.   | 57 |

| Figure 5.14 | Pulsing the MBD (2) (Divider): 2.75 Volts floor, and 10 Pulses of 1.9 Volts with a Width of 4 Micro-Seconds at 80% Duty Cycle    | 58 |

| Figure 5.15 | Pulsing the MBD (3) (Divider): 2.75 Volts Floor, and 10 Pulses of 1.7 Volts with a Width of 4 Micro-Seconds at 80% Duty Cycle    | 58 |

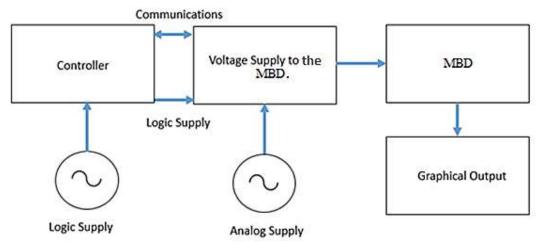

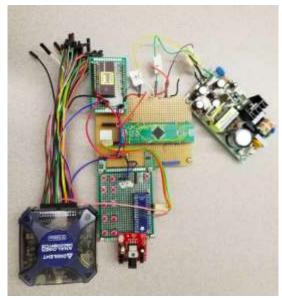

| Figure 6.1  | The Abstract Design of the Test and Characterization Platform                                                                    | 61 |

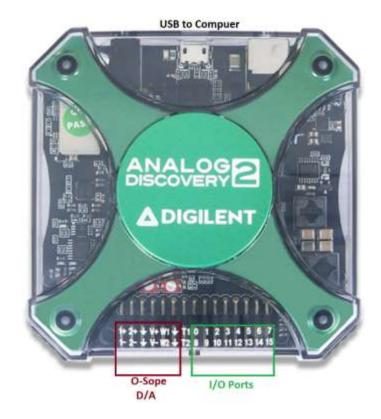

| Figure 6.2  | Digilant Discovery 2: Digital and Analog Oscilloscope [78]                                                                       | 64 |

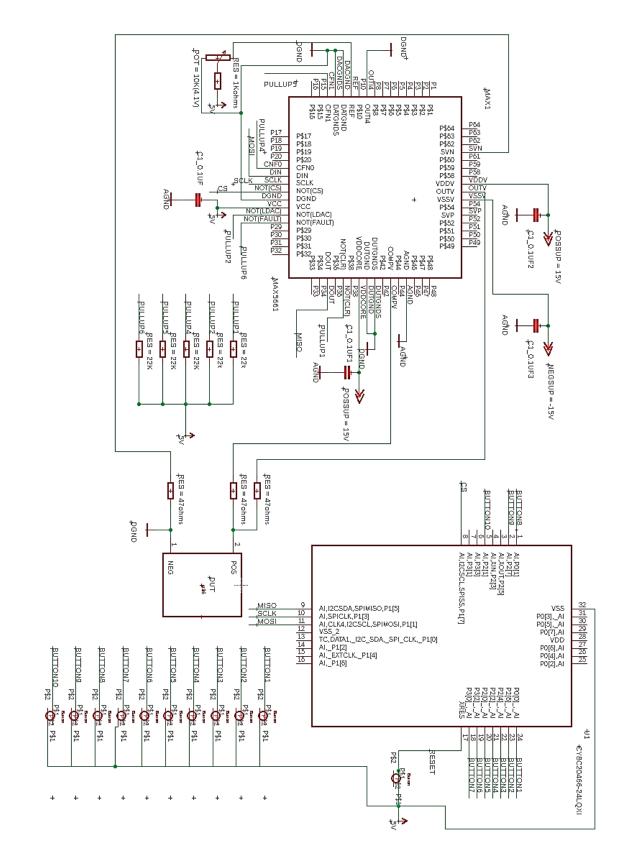

| Figure 6.3  | The Test and Characterization Platform Electrical Design                                                                         | 65 |

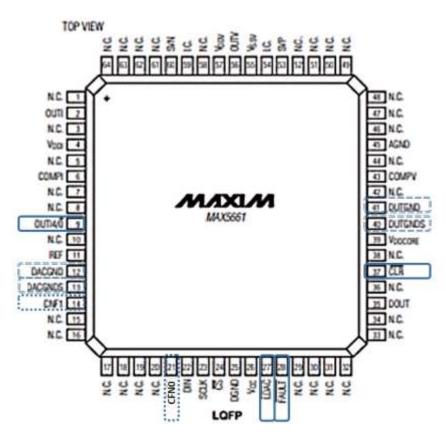

| Figure 6.4  | Pin Reference for the MAX5661 [78]                                                                                               | 66 |

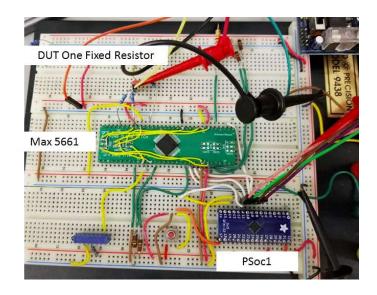

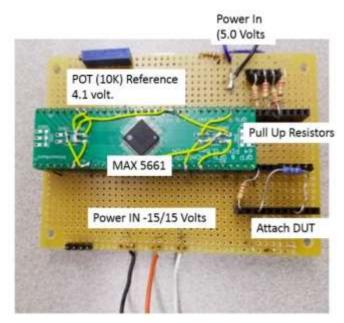

| Figure 6.5  | Daughter Board of the Max 5661                                                                                                   | 69 |

| Figure 6.6  | Breadboard of the Design                                                                                                         | 70 |

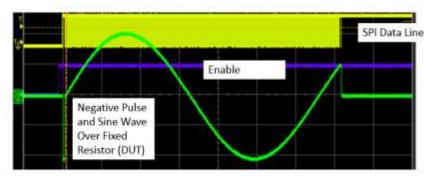

| Figure 6.7  | MAX 5661 Sin Wave +/-10 Volts over a Fixed 22 kOhms Resistor                                                                     | 70 |

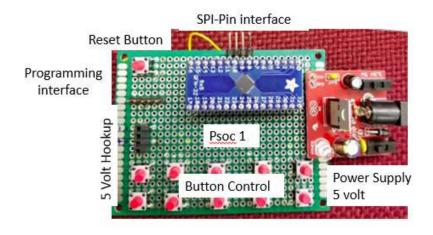

| Figure 6.8  | PSoC 1 and Power Supply                                                                                                          | 71 |

| Figure 6.9  | MAX 5661 Voltage Supplied to the MBD                                                                                             | 71 |

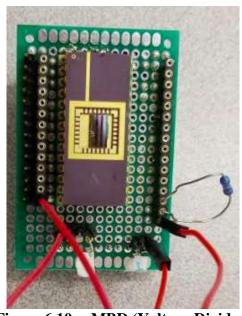

| Figure 6.10 | MBD (Voltage Divider)                                                                                                            | 72 |

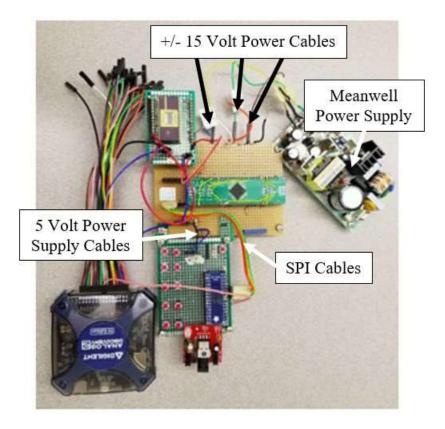

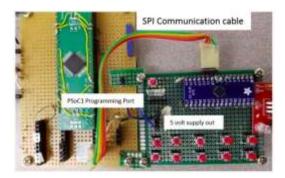

| Figure 6.11 | The Test and Characterization Platform                                                                                           | 73 |

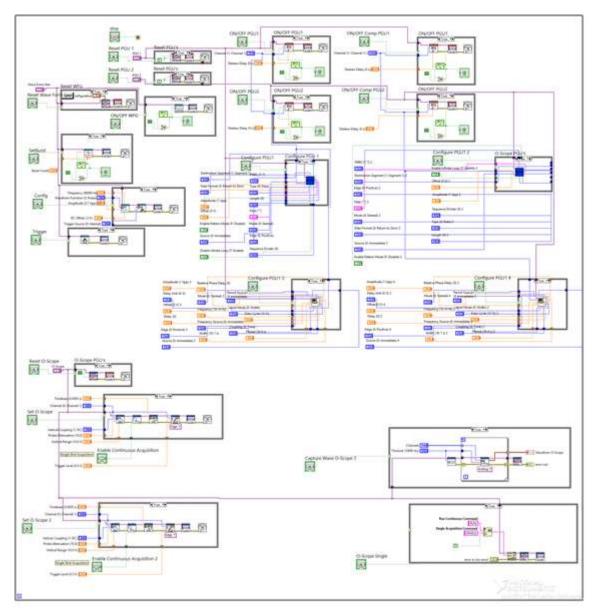

| Figure 6.12 | Test and Characterization Platform for Programming Description                                                                   | 74 |

| Figure 6.13 | Programming Setup on the Test and Characterization Platform                                                                      | 74 |

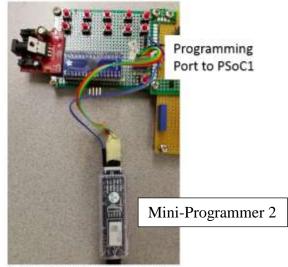

| Figure 6.14 | The Researcher Interface of the Test and Characterization Platform<br>(Firmware Defined)                                         | 75 |

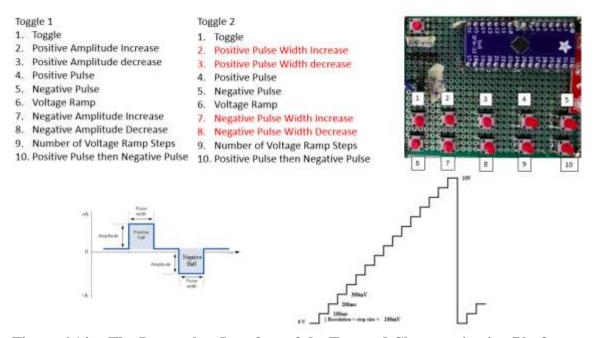

| Figure 6.15 | Virgin Step Voltage on Near Unipolar Memristor (Duration of Ramp<br>Voltage Ramp 0.029 Seconds)                                  | 76 |

| Figure 6.16 | Memristor's Second Step Voltage on Near-Unipolar Sweep Memristor<br>(Duration of Voltage Ramp=2.6 Seconds)                       | 77 |

| Figure 6.17 | Memristor Forming (Cycling Resistance in a Low Stress Method):<br>Positive Voltage Ramp: Voltage Step of a 100 Milli-Volts with a 12 Milli-Second Hold Time (a) Negative Voltage Pulse of -3.4 Volts Held for 80<br>Milli-Seconds (b) Negative Voltage Pulse of -3.4 Volts Held for 190 |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | Milli-Seconds78                                                                                                                                                                                                                                                                         |

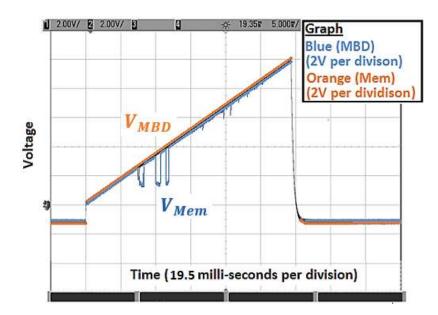

| Figure 6.18 | Test and Characterization Platform Voltage Pulsing (Increase Memristor to a High Resistance):                                                                                                                                                                                           |

| Figure 6.19 | Test and Characterization Platform Voltage Pulsing (Decrease Memristor<br>to a Low Resistance):                                                                                                                                                                                         |

| Figure 6.20 | The Test and Characterization Platform can be Attached to a Micro-<br>Manipulators for Wafer and Die Level Characterization                                                                                                                                                             |

| Figure 6.21 | Test and Characterization Platform with Voltage Divider MBD with a<br>Memristor Package                                                                                                                                                                                                 |

| Figure 6.22 | Test and Characterization Platform with MBD for Bare Die with a Heated<br>Chuck                                                                                                                                                                                                         |

# LIST OF ABBREVIATIONS

| BIT     | Binary digIT                                        |

|---------|-----------------------------------------------------|

| DAC     | Digital to Analog Converter                         |

| DC      | Direct Current                                      |

| DUT     | Device Under Test                                   |

| FPGA    | Field Programmable Gate                             |

| PGU     | Pulse Generator Unit                                |

| HP      | Hewlett Packard                                     |

| IC      | Integrated Circuits                                 |

| I/O     | input/output                                        |

| LabVIEW | Laboratory Virtual Instrument Engineering Workbench |

| MBD     | Memristor Based Design                              |

| O-scope | oscilloscope                                        |

| РСВ     | Printed Circuit Board                               |

| РСМ     | Phase Change Materials                              |

| SMU     | Source Measure Unit                                 |

| SVM     | Support Vector Machine                              |

| VCC     | Voltage at the Common Collector                     |

### **CHAPTER 1: INTRODUCTION**

#### **Device variability**

Electrical testing and characterization of devices that are fabricated on silicon wafers, diced wafers, or package parts have hampered research from the beginning of integrated circuits. This is due to a large variety of devices being developed and modified, that are not well known with different electrical characteristics that require time of the researcher to develop and execute tests, and this time cannot be devoted to the development of the device [1]. The devices considered in this research are memristors, which are two-terminal devices that change resistance as a function of Voltage and retain their resistance when the Voltage is removed [2].

There are a variety of challenges in developing memristors that come from the different mechanisms of changing resistance found in many types of memristors, that may require new or modification of standard electrical characterization methods [3]. Even when memristors have the same mechanism of operation, the life cycle of the memristor from first creation, virgin (high Voltage), to operation (low Voltage) causes multiple electrical test equipment to be used. The changes in the device under test (DUT) and Memristor Based Designs (MBD) require different tooling for the test and characterization process, e.g., direct current in Voltage or current based tooling, and alternating Voltages in time base for pulse-based tools. This creates problems if the test equipment cannot adapt to the DUT or MBD, by requiring the researcher to modifying existing tooling or buy new tooling. Even though there exist some development boards for testing memristors or

MBD, they have limited Voltages, are not flexible for a variety of tests, and cannot accommodate a variety of designs operating under different operating conditions. To increase the productivity of researchers, or even enable a novice to do characterization, the Engineering community needs a flexible electrical test and characterization platform that can be easily automated, possess the ease of re-configuration, accommodate different DUTs and MBDs, be cost-efficient, and be portable when the laboratory environment changes.

### Motivation

According to Dave Peterson, a senior test engineer, "Creation of a device is not where the work ends, but where it begins." Dave Peterson was saying that electrical characterization is a large part of the research for implementation of a device into integrated circuits. Currently, memristor's electrical characterization is not fully defined to allow implementation into applications. Memristor's electrical characterizations are largely ignored because of the pressure to create a new memristor in research environments. This is due to the lack of time to learn what electrical characterization is needed, time for test platform setups, and the cost of test equipment.

## **Problem Statement**

The creation of a test and characterization platform that can define the electrical characterization of a memristor is needed. There is a great need for an off-the-shelf, programmable, testing-board that can accommodate different types of DUTs and MBDs, has a large Voltage range, low cost, is easily learned, and can test an assortment of memristor variations with variety of operating characteristics. Such a test platform will cut costs, reduce setup time of tests, and allow generating improved test data, which can

increase research productivity. So, an electrical characterization platform with these attributes will allow researchers to characterize the memristor for applications.

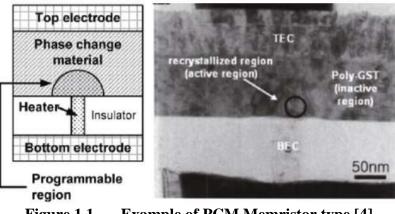

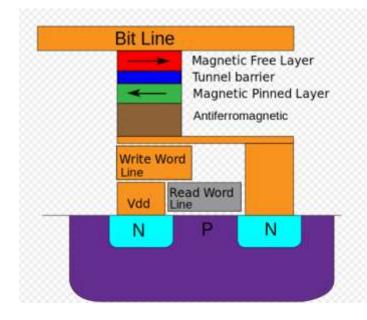

The variety of memristor types make electrical testing challenging. Memristors have different mechanisms to change resistance. Some use conducting filaments that connect two plates separated by an insulator, others use heaters to change the crystalline structure, or use carbon nanotubes [3]. Figure 1.1 shows an example of a cross-section of the mechanism of using the heater to change crystalline structure to manipulate resistance, known as a Phase Change Material (PCM) memristor [4].

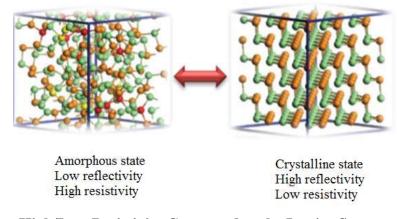

Figure 1.1 Example of PCM Memristor type [4]

The variety of memristors create different Voltages of operation, different current limits that can be applied, add heat components to the setup of the test platform, and these options change how the memristor could be used in MBD (sensor, logic, or weight [5]). All these options will affect the electrical test conditions. Because of this variability of memristor types, they can have operating characteristics that can be classified as unipolar (only positive Voltage operation), near unipolar (mostly positive Voltage operation) and bipolar (positive and negative Voltage operation), as listed in Table 1.1 [6].

| Polarity      | Voltage Operation                 |

|---------------|-----------------------------------|

| Unipolar      | Only positive Voltage operation   |

| Near unipolar | Mostly positive Voltage operation |

| Bipolar       | Positive and negative Voltage     |

Table 1.1Memristors Operating Voltages Polarity [6].

These operational differences require a new flexible electrical test and characterization platform which is modular in design, and with software operating the test platform that can be updated easily.

Current test platforms can only accept a limited number of different DUTs and MBDs, and this limits the tests that can be performed. The MBD could be configured as a Voltage divider, a circuit element, an array of memristors, a logic setup of memristors, a feedback controller, and a detection method [7, 8, 9, 10]. These MBDs require flexibility of the test and characterization platform to propagate a signal with signal access points for an oscilloscope (O-scope), and feedback circuits for the controller of the test platform. An MBD needs to be easily replaced while protecting its connection to the Voltage source of the test platform. Having flexible DUTs allows the researcher to run the same tests for different configurations of MBDs (single, logic and array), test conditions (heat and radiation), and at different stages of the manufacturing process and packaging of the memristors (partial fabricated, wafer level, die, or package die). In conclusion, current test and characterization tools are inadequate to accept the variety of DUTs and MBDs that are constructed.

Another issue of electrically testing and characterizing memristors in an experimental lab environment, is that the test platforms currently used are for conventional types of devices like transistors, resistors and so on. Having no particular tool that is

specifically designed for memristor testing, researchers spend time deciding which test and characterization platform could perform the test needed, as well as time spent training for the characterization tool. This process re-occurs until the researcher has a battery of tests to perform [11]. This battery of test solutions is spread out over many electrical test platforms and often are only available in different lab locations. The movement among these labs may require a reservation for the test platform if not owned by the researcher, access to the lab if not their own; even just moving a DUT or MBB from one test platform to another requires time. In addition, performing the full battery of tests developed may require a long time. The execution of the battery of tests takes time away from the development of a memristor device or design, so often only minimal electrical tests and characterization can be done on the devices to allow more time for development. So, electrical testing suffers: too little testing, too little verification, and too little integration of the device into a working system. Therefore, a new electrical test and characterization platform is needed to be able to perform many types of characterization, i.e., Voltage pulsing and Voltage sweeps.

#### Impacts of memristor life cycle on electrical characterization

Memristors can have different operating Voltages in their lifecycle. Memristor devices that are tested in this research are ionic devices in chalcogenide glass. This type of memristor has states of electrical performance in the lifetime of the device that require application of different Voltages across its terminals. When an ionic memristor is first made, it requires high positive Voltage to decrease its resistance in many types of ionic memristors, and within this research, this state is referred to as a "virgin device". The next stage of the device is to cycle the resistance, i.e. apply positive Voltage across the memristor terminal to obtain a low resistance, then a negative Voltage for a high resistance. The cycling of resistance is to stabilize the operating Voltages, and this is referred to as "forming" [12]. Once the memristor is "formed", it can be used in "operational mode". In "operational mode", direct current (DC) characterization will have an equivalent threshold Voltage (rapid decrease in resistance with rapid increase in current) paired with a standard negative Voltage to reduce resistance and a constant maximum allowed current, known as "current compliance". Characterization of a memristor in a pulsing environment, in "operation mode", will have a similar movement in resistance when a pulse (positive or negative) is applied from a similar starting resistance. So, the electrical test and characterization platform must have not only a large enough Voltage to decrease resistance for many types of memristors throughout their lifecycle, but also necessary negative Voltage to increase the resistance, and with the ability to pulse the DUT or MBD [13].

### **Thesis Organization**

The thesis organization is structured as follows: Chapter 2 describes the memristor theory, polarity, and types of memristors, with a survey of the operational Voltages of the types of memristors. The type of memristor that will be used in this research, with the fabrication and layout of the memristors used is presented in Chapter 3. Chapter 4 describes singulation of a silicon wafer into its packaging with initial DC Voltage sweeps. Chapter 5 describes the pulse generating station that was used to understand the Voltage pulsing over a memristor to enable the characterization and test platform. The characterization platform requirements, design, list of parts, results, and conclusion are in Chapter 6.

## CHAPTER 2: A REVIEW OF OPERATING VOLTAGES AND LITERATURE

## **Introduction: Memristors**

Memristors have different operational Voltages because of the type of memristor used to change the resistance, the fabrication methods of the type of memristor, the geometric shape of the memristor, the impurities introduced into the memristor, the materials used in the memristor and the electrical connections to the memristor. To design a test and characterization platform that is successful for the researcher, the platform must encompass as many types of memristors and the variations of each type of a memristor as possible. To achieve a global test and characterization platform for memristors, this chapter will review memristor theory, the equations that govern the change of resistance, the polarity variations of memristors, and the types of memristors, as well as operating Voltages.

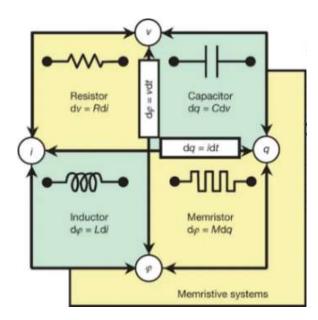

Figure 2.1 How a Memristor fits with a Resistor, Capacitor, and Inductor [14].

Memristor theory had its origin with Leon Chua when he published "Memristor-The Missing Circuit Element" in 1971 [2]. Chua described how a memristor, a twoterminal device, fits into the other three basic electrical elements (resistor, capacitor, and inductor), by bridging flux and electric charge as illustrated in Figure 2.1 [15].

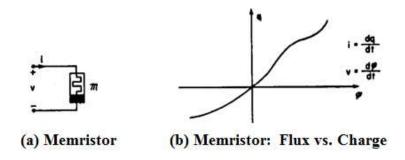

Figure 2.2 shows Chua's curve for charge and the flux in a non-linear relationship based on the memristor which bridges flux and charge. But it is not reasonable to use flux and charge to change the resistance of a memristor, because most applications will not have those sources. So the equations will be put in terms of current and Voltage, as most applications of memristors will use these sources.

Figure 2.2 Chua's Memristor and its Φ-q Curve [2]

The given equations by Chua [2], (2.1) and (2.2), shows current (*i*) equal to charge with respect to time and Voltage (v) equal to flux with respect to time, respectively. *M* is the memristance for equations (2.3) to (2.6). But within this work, memristance is equivalent to the resistance at a certain time of the memristor. Examining "instantaneous power dissipated by memristor" as shown by Chua, equation (2.3), shows that dividing  $[I(t)]^2$  into v(t)i(t) yields equation (2.5). Substituting equations (2.1) and (2.2) into equation (2.5) generates equation (2.6). Therefore, the memristance is affected by forcing current or Voltage across the memristor.

$$i = \frac{dq}{dt} \tag{2.1}$$

$$v = \frac{d\Phi}{dt} \tag{2.2}$$

$$p(t) = v(t)i(t) = M(q(t))[i(t)]^2 (Instantanous Power)$$

(2.3)

$$M(q) = \frac{v(t)i(t)}{[I(t)]^2}$$

(2.4)

$$M(q) = \frac{v(t)}{i(t)} \tag{2.5}$$

$$M(q(t)) = \frac{d\Phi_m/dt}{dq/dt} = \frac{v(t)}{i(t)}$$

(2.6)

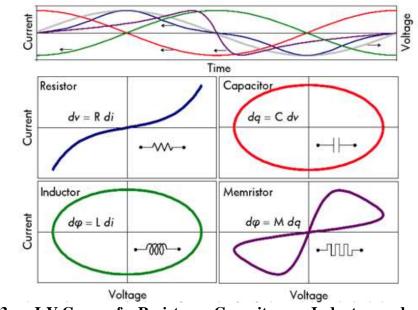

The Voltage-current characteristics described above by Chua's theory and formulas, illustrated in Figure 2.3, demonstrates the standard pinch hysteresis [16]. Chou's theorem, Passivity Criterion, proves that a change in Voltage or current the resistance is change of the memristor is continuous. The equations and the generated I-V curve give the researcher a guide to memristors' behavior according Chua's theory. But as different memristors have been developed, they show different shapes of their I-V curves and their operating polarities.

Figure 2.3 I-V Curve of a Resistor, a Capacitor, an Inductor, and a Memristor [16].

### **The Polarity of Memristors**

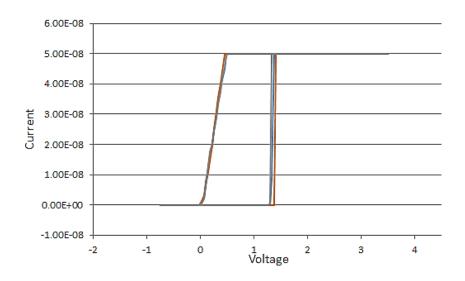

Chua's theory shows the polarity of the operating Voltage as bipolar, as positive Voltage and a negative Voltage to change resistance. Memristors can also display a unipolar behavior in the operating Voltage, as described by Akikhito Sawa [17]. Another category introduced in this research is a near unipolar category to fill the gap of memristors that need a very small Voltage to decrease resistance. The test and characterization platform must be able to perform within these Voltage polarities, as described by the forcing Voltage and the measuring current (I-V) in the graphs below.

Figure 2.4 shows a bipolar memristor's I-V characteristics. Figure 2.4 Label "1" on the graph, the Voltage increased from 0 to a positive Voltage. When the Voltage reaches  $V_{TH_1}$  on the graph, a rapid increase in current happens, this is known as the threshold Voltage ( $V_{TH}$ ), labeled "2". The rapid increase in the current is the result of the resistance of the memristor rapidly decreasing because of the Voltage potential across the memristor.

At Label "3" on the graph, the Voltage is swept back to 0 with no change in the slope, which indicates that the resistance stays constant. On the graph labelled "4", the Voltage is swept from 0 to a negative Voltage towards  $V_{TH_2}$ , a rapid decrease in current takes place as the result of a rapid increase of resistance. The decrease of current is the result of a rapid increase in resistance of the memristor induced by the negative Voltage. For the rest of this work,  $V_{TH_1}$  will be the threshold Voltage when the current increases rapidly, and  $V_{TH_2}$  will be the threshold Voltage for when the current decreases rapidly.

Figure 2.4 Voltage Sweep Measuring Current: Bipolar Memristors [18]

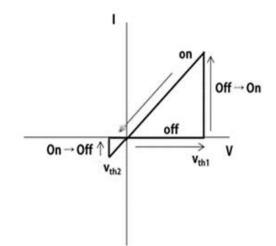

In a unipolar memristor, the device can be brought to high resistance or low resistance in one Voltage polarity, as shown in Figure 2.5.

Figure 2.5 Voltage Sweep Measuring Current: Unipolar Memristors

The thresholds Voltages,  $V_{TH_1}$  and  $V_{TH_2}$ , are within the same polarity of negative or positive Voltage. The Voltage is driven to  $V_{TH_2}$  and then rapidly dropped to 0 Volts to increase the resistance of the memristor, and then to decrease the resistance of the memristor the Voltage is driven to  $V_{TH_1}$  [17, 19].

With different construction methods of memristors, a bipolar device, Figure 2.4, can have a much lower  $V_{TH_1}$  amplitude than  $V_{TH_2}$  amplitude showing a near unipolar Voltage operation characteristic, as shown in Figure 2.6. By having such a low  $V_{TH_1}$  the near unipolar memristor will have lower power consumption, but be more susceptible to negative Voltage noise in the circuit.

Figure 2.6 Voltage Sweep Measuring Current: Near Unipolar Memristors

### **Types of Memristors**

The first device published as a memristor was a bipolar device shown in the magazine *Nature* in 2008 in the article, "The missing memristor found". The bipolar device was produced in the Hewlett Packard laboratories [15]. The HP memristor, anion type (described later in this text), sparked a race to create new memristors. These new types of memristors and different fabrication methods within the type of memristors have

different operating Voltages and polarities. To define the electrical output of the test and characterization platform, a review of the publications on the types of memristors, as well as their operating Voltages and their polarities will be discussed below. Table 2.1 contains a list of the types of memristors with their corresponding mechanisms, and operating Voltage range.

| Types                | Mechanism                                                                                   | Operating<br>Voltages |

|----------------------|---------------------------------------------------------------------------------------------|-----------------------|

| Anion                | Oxygen vacancies, and negatively charged oxygen ions.                                       | -0.7 to 3.7           |

| Cation               | Conductive bridging, reox reaction and<br>migration of metal ions with a positive<br>charge | -1 to 1               |

| Carbon-<br>based     | Carbon Nano-tube bundles or car-<br>bon switching layer (Carbon-DLC).                       | -3.7 to 4             |

| Spin and<br>Magnetic | Electron spin as the switching mecha-<br>nism.                                              | -1.5 to 1.5           |

| Thermal              | Crystalline state to induce high/low re-<br>sistive state.                                  | 0 to 2.2              |

Table 2.1Types of Memristors and Operating Voltages

### Anion Memristors

In 1962 Hikmott observed resistive switching with an anion mechanism [20], that was documented well before Chua's memristor theory was published. Resistive switching is defined as creating a low resistance path in an insulator from an anode to a cathode. Some of the reasons the device created by Hikmott was not acknowledged as a memristor at the time of Chua's publication, were that the device was large, and it had a negative resistance that was not allowed under Chua's theory. As the cation device (memristor) advanced, the first implantation was as memory that was call resistive random access memory (RRAM) in the 2000s [21, 22].

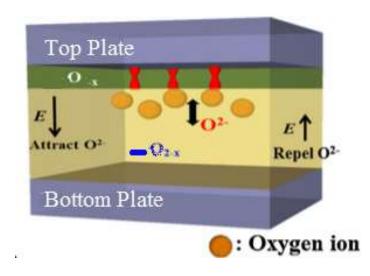

Anion memristors are a sandwich of materials containing a bottom and a top conductive plate with oxide base material in between. The variation in resistance is achieved by generating oxygen vacancies and displacing oxygen ions, as illustrated in Figure 2.7 [15, 17, 23, 24, 25].

Figure 2.7 Anion Memristor's Operation [17]

To lower the resistance, oxygen vacancies must form a conductive path from the top plate to the bottom plate. To regain a high resistance, the oxygen ions will recombine with the vacancies. To build an anion memristor, there is a requirement of a layer that is rich in oxygen ions and a depleted layer that are metal oxides and doped oxides. The anion oxygen base memristor is split up into anion and cation memristors, and is usually bipolar in operation. Examples of metal oxide depletion layer chemistries are:  $WO_X$ , HFO<sub>X</sub>, TaO<sub>X</sub>, TiO<sub>X</sub> and AlO<sub>X</sub> [15, 26, 27, 28, 29]. Doped oxide and silicon-rich oxide [30] is an oxide material that has been sputtered with impurities of metal or silicon. This allows the same mechanism of low and high resistance shown in Figure 2.7 [31]. Some of the metal-

doped oxide memristor chemistries are Ta:  $SiO_2$ , Cu:  $SiO_2$ , Pt:  $SiO_2$ , Zn:  $SiO_2$ , and Ni:  $SiO_2$  [32, 33, 34].

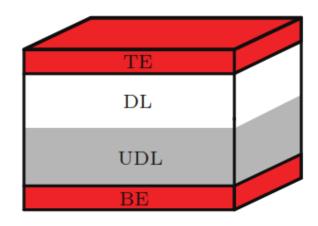

An example of an anion memristor with metal oxide films is a memristor that was fabricated by HP laboratories. The HP memristor is a type of bipolar anion memristor. The HP memristor was fabricated as a Titanium-Dioxide Titanium vertical sandwich. The bread, or outer layers of the sandwich, are the top electrode (TE) and bottom electrode (BE) made of Platinum, shown in Figure 2.8 [15].

Figure 2.8 Vertical Sandwich of the HP Memristor [15]

The DL, in Figure 2.8, is the doped layer with plentiful oxygen vacancies, and the UDL has fewer vacancies with a one to one ratio of Titanium and Oxygen. When "write" Voltage or low resistance Voltage is applied, the oxygen vacancies will migrate to the UDL. This will decrease the resistance by a magnitude or several magnitudes, creating an "ON" state. A reverse Voltage potential, "erase" Voltage, will reverse the direction of oxygen vacancy drift, migrating them toward the DL, creating a high resistance "OFF" state of the device. The diagram below, Figure 2.9, demonstrates the "ON-OFF" states of the Titanium dioxide memristors [15].

Figure 2.9 Diagram of the Electrical Operation of Titanium Dioxide Memristors [15]

The waveforms generated below show the electrical characteristics of the HP memristor. Figure 2.10 shows a Voltage sweep in time and current that demonstrates memristor behavior, in a pinched hysteresis. The highest operating Voltages of this type of memristor is under positive one Volt to negative one Volt.

Figure 2.10 I-V Characteristics of Titanium Dioxide Memristors [15]

Some anion memristors have operation Voltages from zero to approximately 3.7 Volts. The unipolar device shown in Figure 2.11 was fabricated out of a sandwich of TiN/Zr0.5Hf0.5O2/In-Ga-Zn-O (or TiN/ZHO/IGZO) on a flexible substrate of mica [35].

Figure 2.11 TiN/ZHO/IGZO Flexible Anion Memristor: Flexed with IV (0 V→5 V→0 V (with the Numbered Arrows 1→2→3→4→5→6) [35]

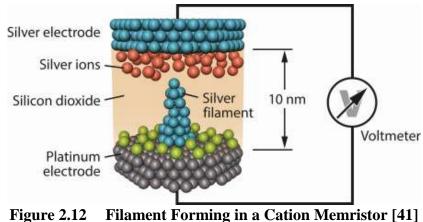

## Cation Memristor

A cation memristor is based on a metal filament, grown and reversible, to bridge two metal plates separated by an insulator [36]. Cation memristors were developed at Arizona State University by Professor Michael Kozicki and his research group in the 1990s [37, 38]. Micron and Infineon announced cation memristor development in the early 2000s [39], and in 2011 Adesto Technologies was developing a cation memristor in memory. Adesto marketed the cation memristor as a conductive-bridging RAM (CBRAM) that was sampled memory in 2013 [40].

A cation memristor takes advantage of solid-state Ionics, and their performance is based on an electrochemical oxi-reduction process. Using thin layers, a metallic bottom plate (Electrochemically Inert) is created with an insulating middle layer and then a metallic top plate that is ion donating [37]. The ion donating film has highly mobile ions and high electrochemical potential. After Voltage potential is placed on the two thin-film electrodes, ions start to move across the insulating barrier to the bottom plate, where the ions undergo a reduction on the bottom electrode to become a metal. The metal builds in the direction of the electrical field towards the top plate, creating a filament (Examples: Ag or Cu) to connect the bottom plate to the top plate, and changing the resistance by orders of magnitude, as seen in Figure 2.12 [41].

Figure 2.12 Finament For hing in a Cation Mennistor [41]

A reverse Voltage potential is applied across the device to bring the device to a high resistance. Then the silver filament deconstructs into silver ions and recombines to the silver electrode [41].

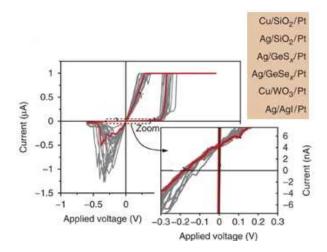

Figure 2.13 Different Cation Memristor Voltage Sweeps [41]

The positive operational Voltages of a typical cation memristor are no more than one Volt with a negative of Voltage no more than negative 0.7 Volts, as seen in Figure 2.13.

### Carbon-based Memristor

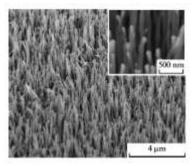

In 2009, the carbon oxide switching memristor was first published by He et al [42]. The carbon switching layer is an insulator so that a filament can be formed between the conductive plates. A carbon bundle based memristor was published in 2011 by A. Radio et al [43]. The carbon nanotubes used in the device are composed of silicon carbide (SiC), that were arranged in Vertically Aligned Carbon NanoTube arrays (VA CNT), as shown in Figure 2.14 [44]. The nanotubes use stress to affect current when a Voltage is applied to create memristor characteristics.

Figure 2.14 Scanning Tunneling Microscope of Vertically Aligned Carbon Nanotube Array [45]

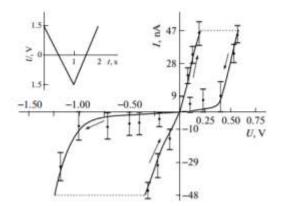

In carbon bundle based memristors, the conducting tip of the Scanning Tunneling Microscope (STM) induces an electric field and is brought near to the VA CNT to create bundles, shown in Figure 2.15 (a) and (b). The Voltage is swept on the tip of the STM and then this induces a stress on the bundle. This stress of the bundles causes a current flow of the tip from the STM. The current and Voltage on the tip are measured and graphed.

This graph has the shape of a pinch hysteresis curve, which is shown in Figure 2.16. If the probe tip Voltage potential is reduced to zero at any time of the hysteresis curve, the bundle will retain the induced stress [46, 45]. The operating Voltage range of the carbon nanotube memristor is negative 1.25 Volts to .75 Volts.

Figure 2.15 Bundling of Carbon Tubes [45]

Figure 2.16 Electrical Characterization of Tip [45]

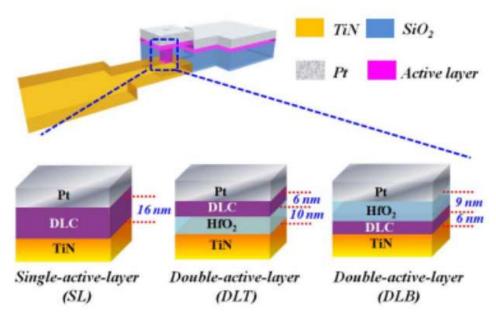

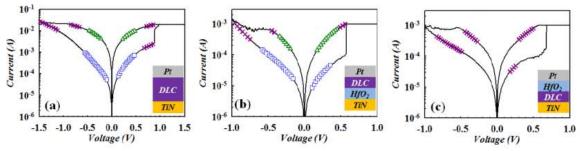

Carbon-based memristors that have a switching layer of Diamond-Like Carbon (DLC) use conductive filaments to change resistance. The fabrication of the DLC memristor has two metal electrodes with a DLC layer between the electrodes. There are

several different variations of these types of carbon sandwiches, and some of these variations are shown in Figure 2.17, from the publication "Resistance Switching Induced by Hydrogen and Oxygen in Diamond-Like Carbon Memristor" [47]. The figure shows a hydrogen-induced (Single-active-Layer) conductive filament and an oxygen-induced conductive filament (Double-active-Layer) with the order of the layers adjusted to understand the electrical characteristics of each variation. Figure 2.18 shows the electrical results of the pinched hysteresis curve in log scale, showing the impact of fabrication changes in the shape of the I-V curve and the operating Voltages. The operating Voltage range in this publication is from -1.5 to 0.7 Volts [47]. In another publication, "Memristive devices based on graphene oxide", a variation of fabrication methods resulted in operating Voltages of - 3.7 Volts to 4.0 Volts [48]. Within memristor types, it shows the importance of fabrication methods to the electrical operation of the memristor and the electrical characterization of the memristor.

Figure 2.17 Some Types of Carbon Memristors [47]

Figure 2.18 IV Characteristics of Different Carbon Stacks [47]

#### Spin-Based and Magnetic Memristive Systems

In 1995, the Magnetic Tunnel junction (MTj) layer was discovered independently by Moodera and Miyazaki which enables magnetic memristive systems [49]. The fabrication of a magnetic memristive system is based on two ferromagnetic plates. One plate is magnetized in a certain polarity, usually in the manufacturing process, and the other plate changes its polarity because of the electrons tunneling through the MTj. The same polarity of the plates allows the current to flow with low resistance. Then, having the opposite polarity of the plates slows electron flow and increases the resistance. A crosssection of a typical bit cell in a magnetic memristor is seen in Figure 2.19 [50, 51, 52].

Figure 2.19 Magnetic Cell [50]

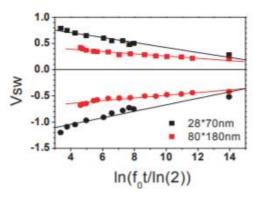

An example of the switching Voltages, high to low resistance and low to high resistance, are displayed in Figure 2.20. This figure shows the switching Voltage differences in the size of the device (s28nm×70nm and 80nm×180nm) and the pulse width [53]. These systems have a typical operating Voltage range of a negative 1.5 Volt to 1 Volt.

Figure 2.20 Switching Voltage vs Pulse Width of a MJt Memristor [53]

The ability of the spin of an electron to transfer to another is known as Spin Transform Torque (STT). STT was predicted by John Slonzewski from IBM research in 1996 and observed in 2000 by J.A. Katine, et al, [49] (2019). The observation led to the development of the spin-based memristor.

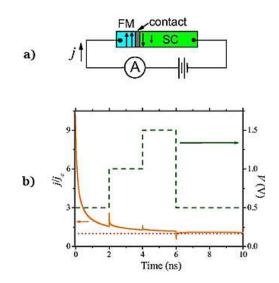

Spintronic memristors use electron spin as the switching mechanism. Controlling the spin of the electron allows changes in the polarity of the magnetization state of the device that will change resistance. Figure 2.21 (a) shows the electrical connections for a spintronic memristor with current density (j is measured). In Part (b) of the same figure, Voltage pulses are applied to the spintronic memristor which decreases the ratio of the current density of the source over the current density of the contact  $(j/i_c)$ . Since the current

density is reduced by a positive Voltage, this implies that the resistance of the system is reduced. A negative pulse will increase resistance in the same way. The publication shows that the magnetization state of the device can be used to control the resistance of the device. Spintronic memristors have an operating Voltage range of negative 1 to 1.5 [54].

Figure 2.21 Spin Based Memristors: (a) Electrical Hookup of Spintronic Memristor (b) Voltage Pulse in Time vs Current Density [54]

#### Thermal (Phase Change) Memristor

A. V. Pohm first published, in 1970, using chalcogenide glasses for nonvolatile memory, because of the ability of the material to retain the state of resistance (Phase-change Random Access Memory-PRAM) [55]. With the change of resistance of the Phase Change Material (PCM), the optical properties change, and this forms the foundations of the Digital Versatile Disc (DVD) and the Compact Disc ReWritable (CD-RW) that is used today [56]. The phase change memristor can be used as a Voltage induced heated memristor, discussed in this work, an optical memristor, or heat memristor.

Some of the different materials which can be used for the formation of Phase change memory (PCM) devices are Antimony (Sb), Tellurium (Te) and Germanium (Ge).

The phase-change memristor (Phase-change Memory), PCM, uses the crystalline state to induce the low resistive state, amorphous state, to a high resistive state, as seen in Figure 2.22 [57].

Figure 2.22 High/Low Resistivity Compared to the Lattice Structure of the PCM Device [57]

Figure 2.23 shows the pulsing of a PCM device that will cause the temperature to change across the device (Joules Heating). The heating will change the phase of the material, inducing a resistance change. A "Set" pulse will heat the amorphous PCM material to a state that will crystalize the material to reduce the resistance to a certain delta. Then a "Reset" pulse, higher than the "Set" pulse, would be applied to the device above the melting point to change the material to amorphous, creating a high resistance [58].

Figure 2.23 Reset and Set Pulses for PCM Resistance [57]

Figure 2.24 shows a typical integration of PCM material into memory. Each memory cell has a heater to allow "Reset" and "Set" in the crossbar array.

Figure 2.24 Typical PCM Integration into an Array [57]

Figure 2.25 shows the electrical operations of a Ge2Sb2Te5 PCM device. The paper describes how doping, introducing an element into the lattice structure, affects the electrical operation of the device. Figure 2.5 (a) shows that doping with Ti will affect the operational Voltages by shifting the set Voltage from 3.1 Volts, non-doped, to 1.1 Volts doped. In (b) the pulse width can also affect the operational Voltages of the devices, but this will be dominated by the fixed capacitances of the device. (C) shows the standard operation Voltages for the new doped device, Ge2Sb2Te5 (5.67% of Ti) at 0 to 2.2 Volts.

Figure 2.25 Ge2Sb2Te5 (GST) PCM Device: a) Non-Doped vs Doped with Ti: Current Forced b) Pulse Width vs Voltages c) Doped at 5.67% of Ti: Set and Reset Voltages [44]

#### Conclusion

As memristors have developed over many decades, several types of memristors with different operating Voltages and polarities have been created. If the past is an indication of the future many more types of memristors will be created with variations that will impact Voltage operation. In many of the publications reviewed, the electrical characterization tool and the corresponding setups used to electrically characterize the memristor were not mentioned. Where the tool was mentioned, the tool classes were semiconductor parameter analyzers used for I-V sweeps and waveform generators for pulsing Voltage. These tools cost several thousand dollars to tens of thousands of dollars. Research for a global test and characterization platform for memristors is needed that is portable, uses off the shelf components, and is low cost. This platform would cover many types and variations of memristors, which would have a range of Voltage output of -3.7 Volts to 5 Volts (+3 Volts if Forming is needed [12]).

# CHAPTER 3: THE MEMRISTOR USED TO TEST THE TEST CHARACTERZATION PLATFORM

#### Introduction

Before the work of the design of the test and characterization platform, a memristor was fabricated on a silicon wafer to enable the design and electrical characterization of the platform. The memristor that was fabricated was a cation memristor with a chalcogenide glass matrix of  $Ge_{20}Se_{80}$  in a columnar vertical configuration that has larger columns of glass than originally fabricated and removal of the photo-diffusion of silver step to set the silver into the silicon lattice. These modifications were done to have a high initial Voltage than most types of memristors with a life cycle Voltage range of approximately -0.4 Volts to ten Volts [59]. The understanding of the processing of the memristor will allow the electrical characterization to be differentiable from the device and the platform, as the materials and the shape of the device will influence the electrical performance [60, 61]. The layout of the device shows how to connect electrical connections to the device. The fabrication and layout of the device were done as follows:

## The Memristor Fabricated for the Development of the Test and Characterization

## Platform

The cationic columnar memristor was fabricated using silver as a cation source to form a conductive bridge (filament) within the columnar structure of the chalcogenide glass to adjust resistance. The device processing, was guided by Dr. Maria Mitkova, done by Muhammad Rizwan Latif, and the layout of the layers (the glass, the silver, and the electrodes) was done by Steve Wald. Processing was done at Boise State University and then shipped to Advotech for singulation and packaging. The layers of the device were glass columns sandwiched between electrodes of silver and tungsten, as shown in Figure 3.1.

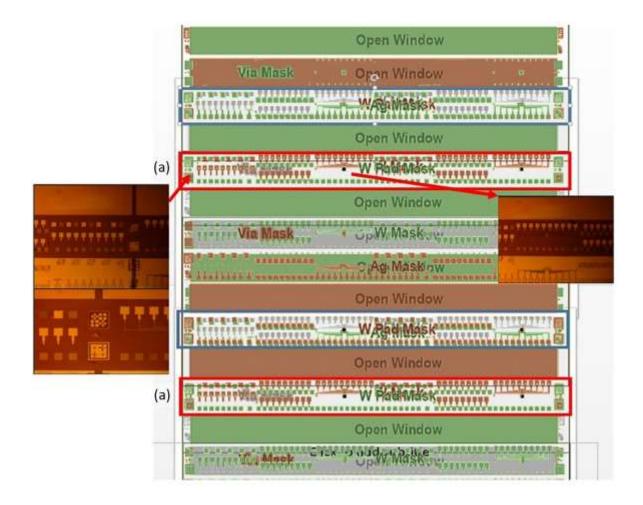

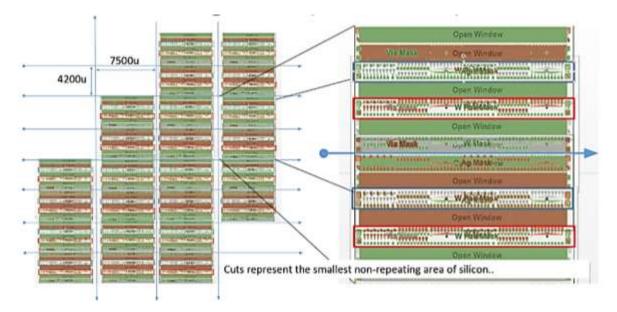

The silicon wafer was a 4" (100 orientation) diameter boron-doped (p-type) 380 micrometers thick. The 3 in 1 reticle, mask, was shifted that contained all the layers' geometries to build the cationic columnar memristor. The layers on the 3 in 1 mask, seen in Figure 3.2, are used to define the cathode (W Mask), the hole through the oxide to the cathode (Via Mask), anode of silver (Ag Mask) and another hole through the oxide for the cathode electrical access (W Pad Mask).

Figure 3.2 Mask (All in one Layer) [59]

The 3 in 1 mask avoided the need for individual masks for each layer and reduced cost, but did waste a portion of the silicon wafer surface. The usable die size is 7500

micrometers by 600 micrometers Figure 3.3, with an unusable area of 13 times of the usable area [59].

This novel approach of using the 3 in 1 mask was developed by Steve Wald and Rizwan Latif [59]. The process flow for fabrication of the cationic columnar memristor, that will guide the next sections, is shown in Figure 3.4.

#### Bottom Electrode (Cathode) Layer

To isolate the devices from the p-type substrate, so a leakage path would not exist, a thermal Oxide layer  $(SiO_2)$  was grown at a thickness of 200-300nm. Titanium oxide (TiO) was deposited to promote adhesion for the tungsten bottom electrode. The bottom electrode was created by sputtering tungsten (W) and was not defined. Since the bottom electrode was not defined it made the cathode continuous, known as a "common bottom electrode" for all devices on the wafer, shown in Figure 3.4 part (a).

#### <u>Via Layer</u>

On top of the tungsten, an oxide was deposited to isolate each device from one another. This was done by spinning photoresist onto the wafer and using the pattern glass (3 in 1 mask) to transfer the geometric shapes into the resist by ultraviolet light. This process is known as photolithography. After a geometric shape was defined in the resist, the hole patterned was transferred from the resist to the oxide layer, by etching only the oxide. This created a hole through the oxide to the tungsten, shown in the flow of process presented in Figure 3.4 part (b) and (c). The hole in the oxide was formed for locations for the memristor devices to reside. Thus, each device had electrical contact to the bottom electrode and was isolated from the other surrounding devices. The hole, called a via, was etched with a Buffered Oxide Etch (BOE) a mixture of HF and  $NH_4F$ . A scanning electron image of the via is shown in Figure 3.5.

Figure 3.5 Via Angle Overview [59]

The photoresist used in the etching of the via, usually removed, was kept to enable a liftoff process for the active layer, described later.

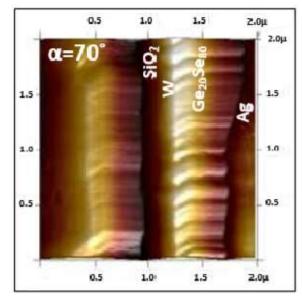

#### Active Layer

Chalcogenide matrix,  $Ge_{20}Se_{80}$ , was thermally evaporated over the photoresist which is the active layer (ChG). Using a specialized technique to deposit the chalcogenide glass, a columniated structure can be formed, shown in Figure 3.6, with one exception, the columns have a larger width so the device requires forming within its life cycle. This columniation has unique electrical characteristics of a near unipolar device. After the active layer, a thin layer of silver (Ag) was evaporated on top of the chalcogenide glass as the source of silver ions, shown in Figure 3.4 part (d). A lift-off process was used to dissolve the resist and lift off (remove) the active layer and silver over the resist that was not needed. This process left the active layer and silver only in the via over the tungsten, shown in Figure 3.4 part (e) [59, 60, 61].

Figure 3.6 AFM Images of the Columnar Structure [60]

### Top Electrode (Anode) Layer

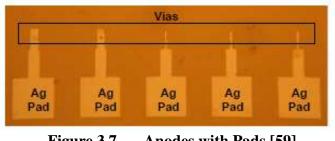

Using standard photolithography, the resist was defined to have a pad shape opening with a lead that extends over the via. After that silver (Ag) was evaporated over the resist and into the openings of the resist. Then the same lift-off process was done to remove unwanted silver and to isolate the pads and leads from one another, as shown in Figure 3.4 part (f) to (h). The pads of silver allowed a wire to adhere to the memristor or tungsten pin to touch the memristor, to have electrical access to the top of the device (Anode), as shown in Figure 3.7.

Figure 3.7 Anodes with Pads [59]

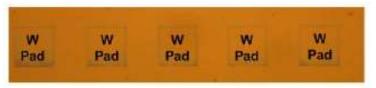

## Exposing Cathode layer

To make electrical contact with the cathode, tungsten (W) common bottom electrode, a creation of holes through the oxide is necessary. Another photolithography and etch is done through the oxide to allow electrical contact to the two-terminal device, as shown in Figure 3.8. Shown in Figure 3.9 is a vertically shifted 3 in 1 mask from the layout with pictures of the actual die after the final processing.

Figure 3.8 **Exposing Bottom Cathode [59]**

# Figure 3.9 Photos of Devices and Pads Produced by the 3-1 Mask that was Physically Shifted Vertically (a) Active Die Area Boxed in Red

The understanding of the device processing and layout will guide the wafer electrical characterization, the packaging processing and the post packaging electrical characterization. Modification to the active layer of thicker columns will require forming to be done. Adding forming to the cation columnar memristor will allow the test and characterization platform to show that it is able to handle a variety of memristors.

# CHAPTER 4: ELECTRIAL CHARACTERIZATION AT WAFER LEVEL AND

## PACKAGING

#### **The Electrical Characterization Details**

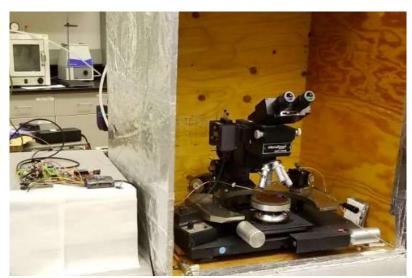

After the near-unipolar cationic columnar memristor devices were fabricated on a silicon wafer, the wafer was electrically characterized for functionality and to guide the design of the test and characterization platform. The electrical characterization of the silicon wafers was carried out on the Micromanipulator 6200 Probe Station with a Cascade Microtech DCM 210 Series Precision Positioner XYZ Micromanipulator [62] with tungsten tips, shown in Figure 4.1.

Figure 4.1 6200 Micromanipulator Probe Station and DCM210 [62]

The parametric analyzer used was the Hewlett Packard (HP) 4155B [63] connected by coaxial cables to the probes shown in Figure 4.2. The control software of the parametric analyzer was Easy Expert Software [64], provided by Agilent. All measurements were carried out at room temperature to verify the operating Voltages and the lifetime Voltages of the cationic columnar memristor. The wafer was placed on the chuck, the micromanipulators used to make contact with the pads of the device (Forcing Voltage on the cathode), and the parametric analyzer used to sweep Voltage.

Figure 4.2 Hewlett Packard 4155B [63]

# Electrical Characterization of the Direct Current Station: Virgin Sweep and

# Forming the Cationic Columnar Memristor.

The lifecycle of a memristor may impact electrical characterization, as the Voltages required to change resistance may change as the memristor cycles resistance. Part of the lifecycle may be forming when a memristor needs to cycle from high to low resistance many times to have a stable positive threshold Voltage for a given current compliance. Most cation filament devices [65, 66] must go through a forming cycle, and with the original columnar cationic structure developed [59] forming was not necessary. But the columnar cationic memristor developed for this research has larger columns in diameter that will need forming.

With the larger columns in the device, the silver ions  $(Ag^+)$  travel through the glass column down to the inert cathode and undergo reduction by which a filament of silver starts

growing towards the anode in an electrochemical oxidation mechanism [67]. With the column being larger the filament will have many potential areas in the lattice of the glass to grow horizontal nodules of silver, requiring more silver ions to form silver than the smaller in diameter columns. The energy required to produce the nodules of silver will translate into a high positive threshold Voltage ( $V_{TH_1}$ ), but the larger columns do not affect the negative threshold Voltage ( $V_{TH_2}$ ), since the energy is the same to break the filament in any diameter size of columns in the cationic columnar memristor. Having only one conductive path to break, oxidation, makes the columnar cation memristor to have a low  $V_{TH_2}$ , giving its near-unipolar polarity. After the silver filament is broken in the thicker column, the silver remains where the nodules were formed but multiple cycles are required to fill all the potential areas where the nodules could grow. During each filament growth the  $V_{TH_1}$  will decrease until the positive threshold Voltage stabilizes to an operating Voltage. The first sweep on a device will be called a virgin sweeps.

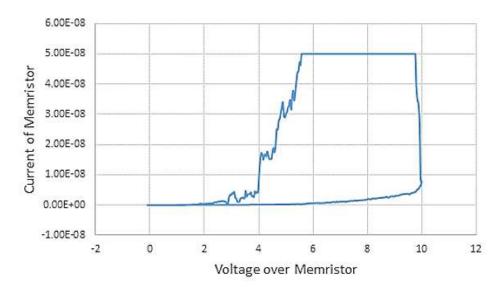

The first sweep on a virgin device requires the largest threshold Voltage for the modified cationic columnar memristor that will range from 3 to 10 Volts. Figure 4.3 shows the first four sweeps of a near unipolar device with a compliance of 80 Nano-Amps to prevent the breakdown of the device's active layer.

Figure 4.3 Forming: First 4 Sweeps at 80nA Compliance

The virgin device, "sweep 1", shows a much higher threshold Voltage at 7.8 Volts than the next three sweeps which have a threshold Voltage at about 3.8 Volts.

Changing to 50 Nano Amp compliance and moving to another memristor on the silicon wafer showed differences in the IV curves, displayed in the Figure 4.4 compared to Figure 4.3. The first sweep, shown in Figure 4.4, has a much higher threshold Voltage than the first sweep, shown in Figure 4.3. The average slope of the shifted resistance of the last three sweeps is 20/1 (Nano-amps/Volt) shown in Figure 4.3 and 45/1 (Nano-amps/Volt) shown in Figure 4.4 that has a difference of 25/1 (Nano-amps/Volt). At the early forming of a memristor, including the virgin sweep, the threshold Voltage varies drastically. Because of this variation of potential sites to form nodules, it would be hard to conclude that the compliance current has influenced the variability.

Figure 4.4 Forming: First 4 sweeps at 50nA Compliance

The number of forming sweeps needed to reach operating Voltages vary because of the processing of the memristor and how it was fabricated. The Voltage sweep was set at negative 100 milli-Volts to five Volts at 50nA. After one hundred Voltage sweeps, the threshold Voltage stabilized at 1.9 Volts with a compliance of 50nA. The last four sweeps are shown in Figure 4.5. The lifetime Voltages of the cationic columnar memristor were approximately -0.5 Volts to 10 Volts.

#### The Packaging of Memristors

Memristors on silicon wafers cannot be integrated into Printed Circuit Board boards (PCB) for applications. So, the wafer needs to be cut to small pieces (singulation), which is known as a die so that they can be placed into packages. The singulation of a wafer into a die is where the wafer is physically sawed into individual IC's (Integrated Circuits) or a group of devices for packaging, as shown in Figure 4.6.

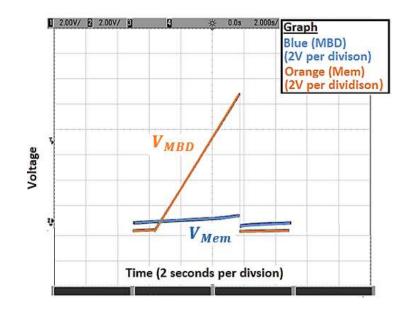

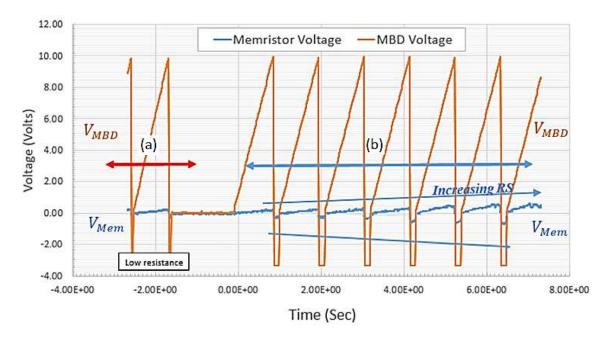

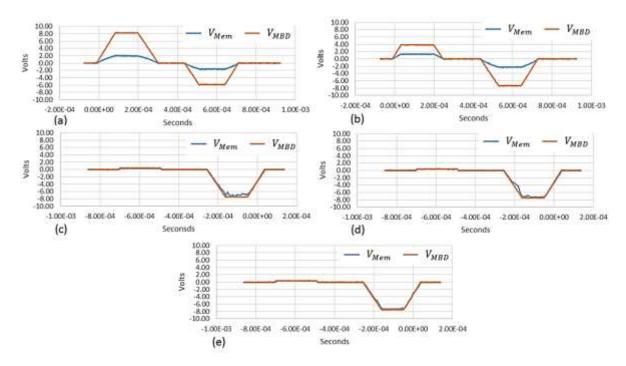

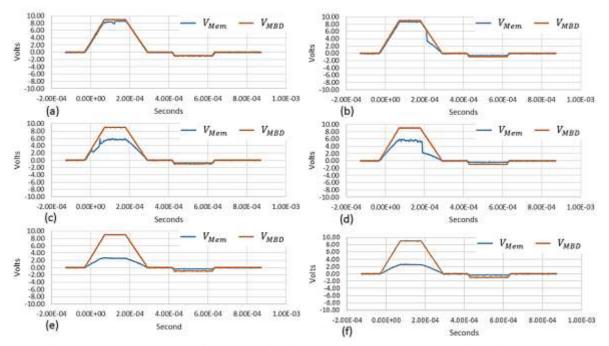

Figure 4.6 Singulation of the Memristor Wafer (Blue Arrows=Saw lines)