## SYNTHESIS, TESTING AND TOLERANCE IN REVERSIBLE LOGIC

## MD ASIF NASHIRY Bachelor of Science, Islamic University, 2006 Master of Science, Islamic University, 2008

A Thesis Submitted to the School of Graduate Studies of the University of Lethbridge in Partial Fulfillment of the Requirements for the Degree

### **DOCTOR OF PHILOSOPHY**

Department of Mathematics and Computer Science University of Lethbridge LETHBRIDGE, ALBERTA, CANADA

© Md Asif Nashiry, 2017

# SYNTHESIS, TESTING AND TOLERANCE IN REVERSIBLE LOGIC

# MD ASIF NASHIRY

Date of Defence: December 19, 2017

| Dr. J. E. Rice<br>Supervisor                                  | Professor           | Ph.D. |

|---------------------------------------------------------------|---------------------|-------|

| Dr. S. Wismath<br>Committee Member                            | Professor           | Ph.D. |

| Dr. W. Osborn<br>Committee Member                             | Associate Professor | Ph.D. |

| Dr. H. Li<br>Internal Member                                  | Associate Professor | Ph.D. |

| Dr. G. W. Dueck<br>External Examiner                          | Professor           | Ph.D. |

| Dr. H. Kharaghani<br>Chair, Thesis Examination Com-<br>mittee | Professor           | Ph.D. |

# Dedication

To my beloved parents and my daughter, Sarah Ibtida.

# Abstract

In recent years, reversible computing has established itself as a promising research area and emerging technology. This is motivated by a widely supported prediction that conventional computer hardware technologies will reach their limits in the near future. This thesis focuses on three important areas of reversible logic, which is an area of reversible computing. Firstly, this thesis proposes a transformation based synthesis approach for realizing conservative reversible functions using SWAP and Fredkin gates. The proposed SWAP and Fredkin gates approach is compared with NOT, CNOT and Toffoli gates approach. Experimental results show that synthesizing conservative reversible functions using SWAP and Fredkin gates is more efficient than comparable approaches using NOT, CNOT and Toffoli gates.

Most existing synthesis approaches in reversible logic result in circuits that may not be optimal in terms of cost metrics such as the gate count, the number of garbage lines or the quantum cost. Hence, post synthesis optimization approaches are used to generate simplified circuits. This thesis proposes ten templates for optimizing SWAP and Fredkin gates-based reversible circuits. We have applied these templates in SWAP and Fredkin gates-based circuits, and achieved (on average) a 16% reduction in quantum cost.

Secondly, this thesis proposes an approach for the design of online testable reversible circuits. A reversible circuit composed of NOT, CNOT and Toffoli gates can be made online testable by adding two sets of CNOT gates and a single parity line. The performance of the proposed approach for detecting a single bit fault, a crosspoint fault and a family of missing gate faults has been observed. Discussion around the correctness of our approach and its overhead is also provided.

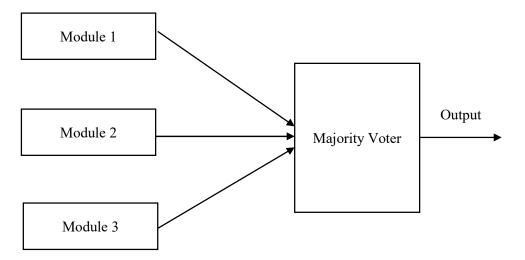

Thirdly, we have proposed an approach to achieve fault tolerance in reversible circuits. A design of a 3-bit reversible majority voter circuit is presented. The proposed majority voter circuit is simpler and of lower cost in terms of the gate count and the quantum cost than existing designs in the literature. This voter circuit can be used to design fault tolerant reversible circuits. We also provide designs for extending the voter circuit.

# Acknowledgments

First and foremost, I would like to thank the Almighty for giving me the opportunity, strength, and patience to undertake this research. This work would not have been possible without His blessing.

I am using this opportunity to express my gratitude to everyone who supported me throughout this thesis. I would like to express my deepest gratitude and sincere appreciation to my supervisor, Dr. Jacqueline E. Rice, for her patience, support, effort, and engagement throughout this thesis. She provided necessary guidance and strategic direction to pursue my thesis, and helped me to navigate every aspect of my journey.

I would like to express my gratitude to my thesis committee members, Dr. Shelly Wismath, and Dr. Wendy Osborn, for their timely suggestions and useful remarks during my research. I would like to thank Dr. Mozammel Khan for his suggestion and guideline. I would like to extend my thanks to Dr. Hadi Kharaghani, Dr. Gerhard Dueck, and Dr. Hua Li for being part of my thesis committee.

I am thankful to the Natural Sciences and Engineering Research Council of Canada (NSERC), the Pacific Institute for the Mathematical Sciences (PIMS)-Alberta, and the School of Graduate Studies (SGS) of the University of Lethbridge for their financial support.

It is hard to express how grateful I am to my parents for their support and sacrifice. I would like to thank my wife, daughter, brothers, relatives, friends, and lab mates for their love, support and encouragement. Last but not least, I am also grateful to the researchers for their ideas and contributions in reversible logic.

# Contents

| Co | onten      | ts            |                                                    |   |     |   | vii    |

|----|------------|---------------|----------------------------------------------------|---|-----|---|--------|

| Li | st of [    | <b>Fables</b> |                                                    |   |     |   | ix     |

| Li | st of l    | Figures       |                                                    |   |     |   | x      |

| 1  | Intr       | oductio       |                                                    |   |     |   | 1      |

|    | 1.1<br>1.2 | 0             | tives                                              |   |     |   | 2<br>3 |

| 2  | Bac        | kgroun        | d                                                  |   |     |   | 5      |

|    | 2.1        | Logic         | Computation                                        |   |     |   | 5      |

|    |            | 2.1.1         | Traditional Logic Computation                      |   |     |   | 5      |

|    |            | 2.1.2         | Reversible Logic Computation                       |   |     |   | 7      |

|    | 2.2        | Logic         | Gates and Circuits                                 |   |     |   | 9      |

|    |            | 2.2.1         | Traditional Logic Gates                            |   |     |   | 9      |

|    |            | 2.2.2         | Reversible Logic Gates                             |   |     |   | 10     |

|    | 2.3        | Synthe        | esis Approaches in Reversible Logic                |   |     |   | 16     |

|    | 2.4        | Cost N        | Metrics in Reversible Logic                        |   |     |   | 18     |

|    | 2.5        | Faults        | and Fault Testing in Reversible Logic              |   |     |   | 21     |

|    | 2.6        | Fault         | Tolerance in Reversible Logic                      | • | • • | • | 22     |

| 3  | Synt       | thesis a      | nd Post-Synthesis                                  |   |     |   | 23     |

|    | 3.1        |               | Synthesis in Reversible Logic                      |   |     |   | 23     |

|    |            | 3.1.1         | Transformation Based Synthesis Approach            |   |     |   | 24     |

|    |            | 3.1.2         | A Proposed Transformation Based Synthesis Approach |   |     |   | 28     |

|    |            | 3.1.3         | Comparison of Transformation Based Approaches      |   |     |   | 30     |

|    | 3.2        | Post S        | ynthesis Optimization                              |   |     |   | 36     |

|    |            | 3.2.1         | Proposed Templates                                 |   |     |   | 41     |

|    |            | 3.2.2         | Reversible Circuits Optimization                   |   |     |   | 51     |

|    | 3.3        | Chapte        | er Summary                                         |   |     |   | 55     |

|    |            | 3.3.1         | Contribution                                       |   |     |   | 55     |

|    |            | 3.3.2         | Conclusion                                         |   |     |   | 56     |

|    |            | 3.3.3         | Future Directions                                  |   |     |   | 57     |

| 4   | Faul   | t Testing                                         | 50 |

|-----|--------|---------------------------------------------------|----|

|     | 4.1    | Fault Models and Fault Testing: An Overview       | 50 |

|     | 4.2    | Fault Models for Reversible Logic                 | 51 |

|     |        | 4.2.1 Crosspoint Fault Model                      | 52 |

|     |        |                                                   | 53 |

|     | 4.3    | Fault Testing in Reversible Circuits              | 59 |

|     |        | 4.3.1 Offline Approaches                          | 59 |

|     |        | 4.3.2 Online Approaches                           | 74 |

|     | 4.4    | New Online Testing Approach                       | 33 |

|     |        | 4.4.1 Design                                      | 33 |

|     |        | 4.4.2 Analysis                                    | 35 |

|     |        | 4.4.3 Testing: Fault Detection                    | 88 |

|     |        | 4.4.4 Comparison and Limitation                   | 95 |

|     | 4.5    | Chapter Summary                                   | 98 |

|     |        | 4.5.1 Contribution                                | 98 |

|     |        | 4.5.2 Conclusion                                  | 98 |

|     |        | 4.5.3 Future Directions                           | 99 |

| 5   | Faul   | t Tolerance in Reversible Logic 10                | 00 |

|     | 5.1    | Principle of Fault Tolerance                      | 00 |

|     | 5.2    | Techniques to Achieve Fault Tolerance             |    |

|     | 5.3    | Testing vs. Tolerance                             |    |

|     | 5.4    | Approaches to Achieve Fault Tolerance             |    |

|     | 5.5    | Fault Tolerance in Reversible Circuits            |    |

|     |        | 5.5.1 Existing Reversible Majority Voter Circuits | )8 |

|     |        | 5.5.2 A Proposed Reversible Majority Voter        | )9 |

|     |        | 5.5.3 Fault Tolerant Full Adder Design            | 11 |

|     | 5.6    | Extension of Reversible Majority Voter            | 12 |

|     | 5.7    | Chapter Summary                                   | 17 |

|     |        | 5.7.1 Contribution                                | 17 |

|     |        | 5.7.2 Conclusion                                  | 17 |

|     |        | 5.7.3 Future Directions                           | 18 |

| 6   | Cond   | clusion 1                                         | 19 |

|     | 6.1    | Contribution and Conclusion                       | 19 |

|     | 6.2    | Future Works                                      | 21 |

| Bił | oliogr | aphy 12                                           | 24 |

|     | U      |                                                   | 30 |

| A   | Expe   | eriment Result 1.                                 | 30 |

# **List of Tables**

| 2.1  | Truth tables of traditional logic functions.                              | 6   |

|------|---------------------------------------------------------------------------|-----|

| 2.2  | Truth tables of reversible logic functions.                               | 7   |

| 2.3  | Parity preserving and conservative reversible functions.                  | 9   |

| 2.4  | Truth table of a $3 \times 3$ Toffoli Gate.                               | 13  |

| 2.5  | Truth table of a $3 \times 3$ positive controlled Fredkin gate            | 14  |

| 2.6  | Transformation of an irreversible function to a reversible one            | 17  |

| 2.7  | Quantum cost of $n \times n$ Toffoli gates.                               | 19  |

| 2.8  | A 3-bit reversible function.                                              | 20  |

| 3.1  | Truth table of a $(3 \times 3)$ reversible function                       | 25  |

| 3.2  | Transformation stages of the function from Table 3.1                      | 27  |

| 3.3  | Stages of SF based transformation of the function in Table 3.1            | 30  |

| 3.4  | Comparison between two circuits shown in Figures 3.1 and 3.2              | 31  |

| 3.5  | Performance comparison of NCT gate transformation based synthesis and     |     |

|      | SF gate transformation based synthesis.                                   | 32  |

| 3.6  | Performance comparison of the minimal circuits generated using exact syn- |     |

|      | thesis [67] with the circuits generated using SF gate based synthesis     | 35  |

| 3.7  | Percentage of reduction in GC and QC when using SF based transformation   |     |

|      | as compared to NCT based transformation.                                  | 37  |

| 3.8  | Truth table for Template 5                                                | 46  |

| 3.9  | Results after applying the proposed templates on benchmark circuits       | 55  |

| 3.10 | Results after applying templates on randomly generated circuits           | 59  |

| 4.1  | Truth table of the circuit shown in Figure 4.1.                           | 62  |

| 4.2  | Output values at the different levels of the circuit shown in Figure 4.2  | 65  |

| 4.3  | Output values at the different levels of a circuit shown in Figure 4.3    | 67  |

| 4.4  | Output values at the different levels of the circuit in Figure 4.4        | 68  |

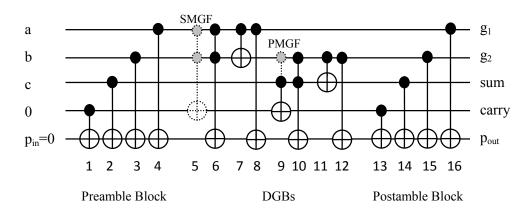

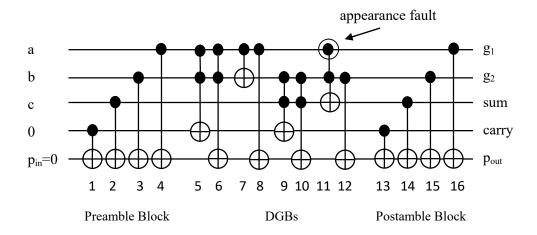

| 4.5  | Test vector to detect appearance fault in the circuit shown in Figure 4.7 | 71  |

| 4.6  | Test vector to identify a SMGF for the circuit, as shown in Figure 4.8    | 72  |

| 4.7  | Logic values at different levels to detect MGFs for the circuit, shown in |     |

|      | Figure 4.9                                                                | 74  |

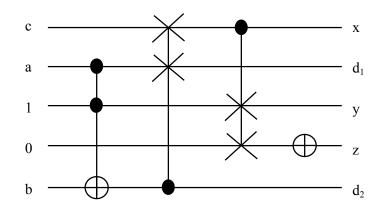

| 4.8  | Truth tables of the circuits shown in Figure 4.18.                        | 83  |

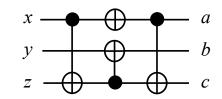

| 4.9  | Truth table for the circuit shown in Figure 4.20(a)                       | 86  |

| 4.10 | Overhead for selected benchmark circuits                                  | 96  |

| 5.1  | Truth table for the reversible voter circuit.                             | 110 |

| 5.2  | Truth table of the 4-bit majority voter shown in Figure 5.12.             | 115 |

| A.1  | Results after applying templates on randomly generated circuits           | 130 |

# **List of Figures**

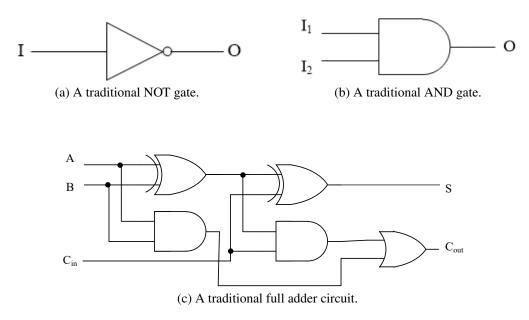

| 2.1  | Some traditional circuits.                                                | 10 |

|------|---------------------------------------------------------------------------|----|

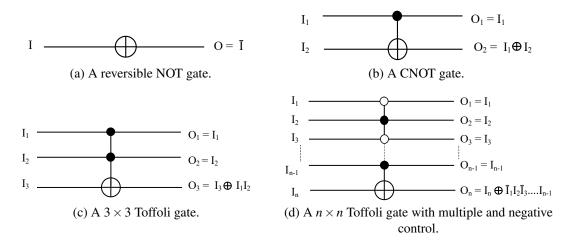

| 2.2  | Some reversible gates of NCT gate family                                  | 12 |

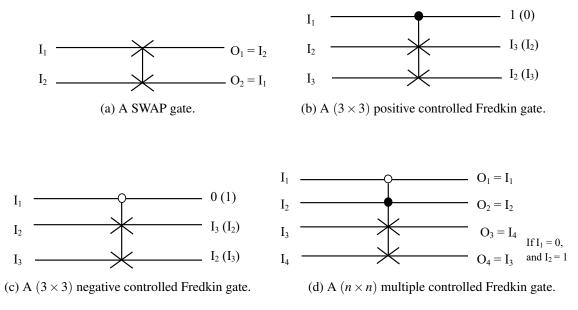

| 2.3  | Some reversible logic gates of the SF gate family.                        | 15 |

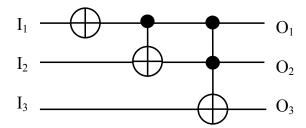

| 2.4  | A reversible circuit consisting of three gates                            | 16 |

| 2.5  | A $3 \times 3$ -Toffoli gate operating as an AND gate.                    | 18 |

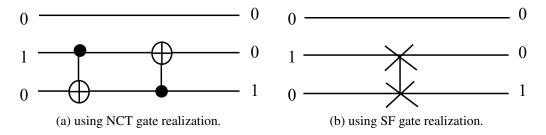

| 2.6  | Two different realizations of the same function using the SF gate family  | 20 |

| 3.1  | The circuit obtained from the function shown in Table 3.1                 | 27 |

| 3.2  | Circuit resulting from SF based synthesis of the function from Table 3.1  | 30 |

| 3.3  | Circuit realization using NCT and SF gate families.                       | 31 |

| 3.4  | Further simplified circuits for the function shown in Table 3.1           | 34 |

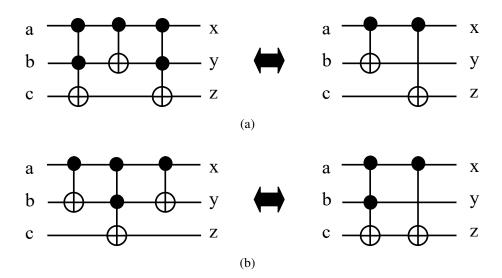

| 3.5  | Two templates presented in [41]                                           | 37 |

| 3.6  | An example to demonstrate the deletion rule in a reversible circuit       | 38 |

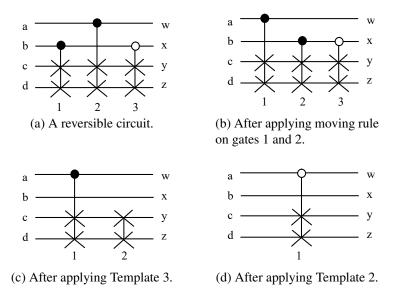

| 3.7  | An example to demonstrate the moving rule for circuit simplification      | 39 |

| 3.8  | A SF circuit where the moving rule does not work.                         | 40 |

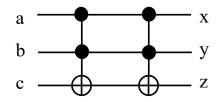

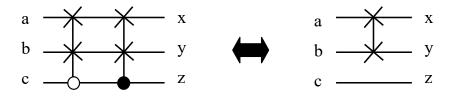

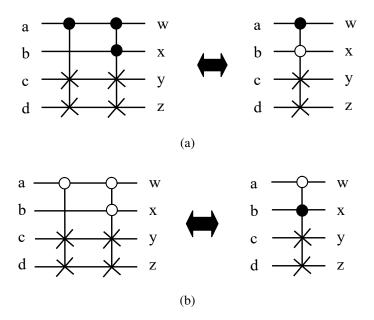

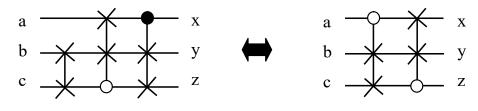

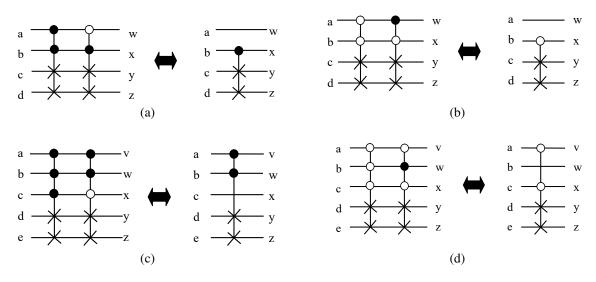

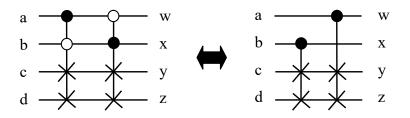

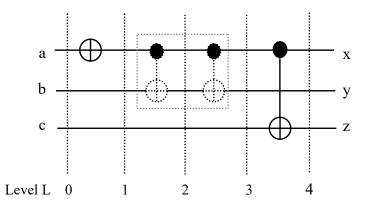

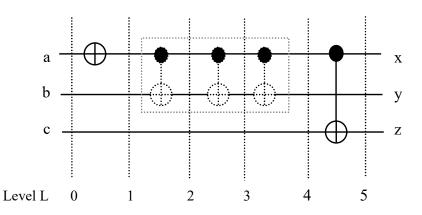

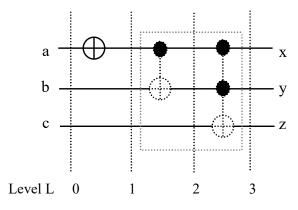

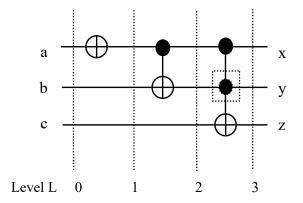

| 3.9  | Template 1                                                                | 42 |

| 3.10 | Template 2                                                                | 43 |

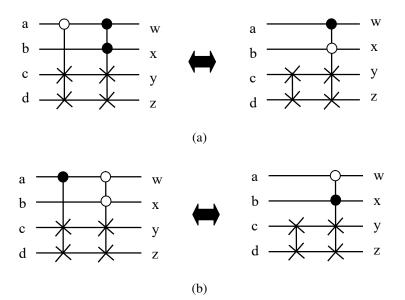

| 3.11 | Template 3                                                                | 44 |

| 3.12 | Template 4                                                                | 45 |

|      | Template 5                                                                | 46 |

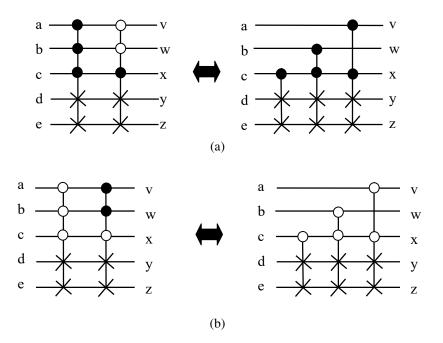

| 3.14 | Template 6                                                                | 47 |

|      | Template 7                                                                | 48 |

|      | Template 8                                                                | 49 |

| 3.17 | Template 9                                                                | 50 |

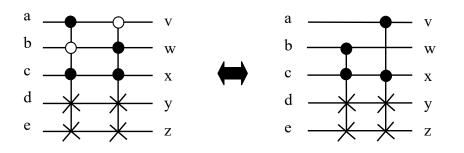

| 3.18 | Template 10                                                               | 51 |

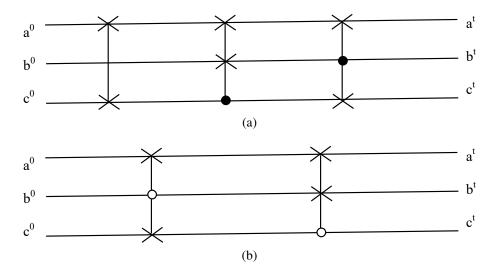

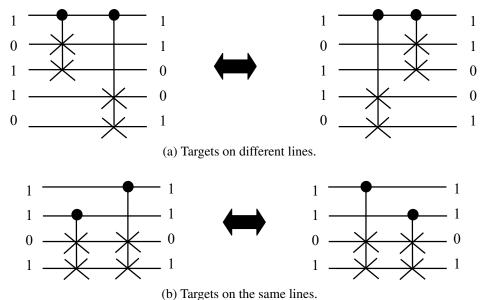

|      | Moving rules for the SF gate families                                     | 52 |

| 3.20 | An example to show the role of the moving rule in circuit optimization    | 53 |

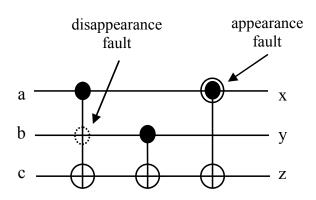

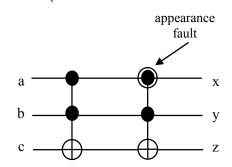

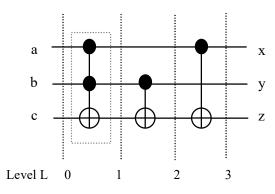

| 4.1  | Appearance and disappearance faults in a reversible circuit               | 62 |

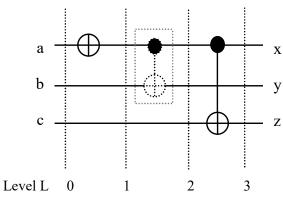

| 4.2  | SMGF in a reversible circuit.                                             | 64 |

| 4.3  | A RGF where a gate is replaced by an even number of instances of the same |    |

|      | gate                                                                      | 66 |

| 4.4  | A RGF where a gate is replaced by an odd number of instances of the same  |    |

|      | gate                                                                      | 66 |

| 4.5  | An example of the occurrence of a MMGF.                                   | 69 |

| 4.6  | A reversible circuit with the occurrence of a PMGF                        | 69 |

| 4.7  | An example of a single appearance crosspoint fault.                       | 70 |

| 4.8  | An example of SMGF in a reversible circuit                                | 72 |

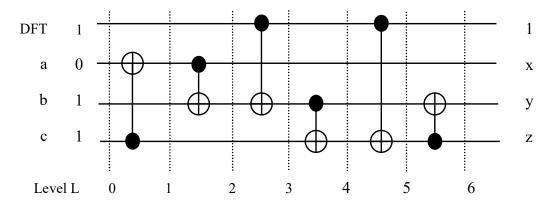

| 4.9                                                                                 | DFT based approach for missing gate testing [20]                           | 73                                                                        |

|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------|

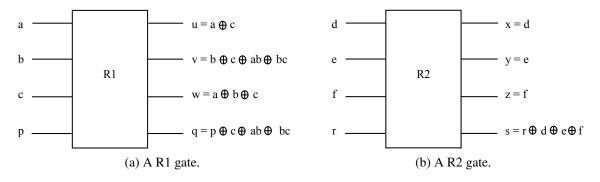

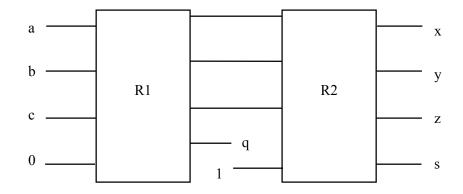

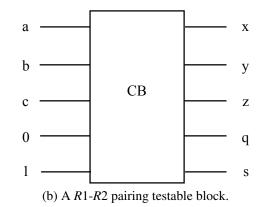

|                                                                                     | R1 and R2 gates proposed in [69].                                          | 75                                                                        |

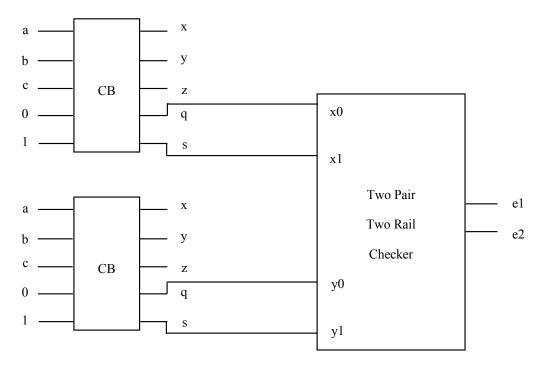

| 4.11                                                                                | Block diagrams of pairing of <i>R</i> 1 and <i>R</i> 2 reversible gates    | 76                                                                        |

| 4.12                                                                                | An online testable circuit based on the approach proposed in [69]          | 77                                                                        |

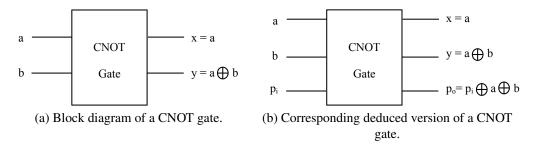

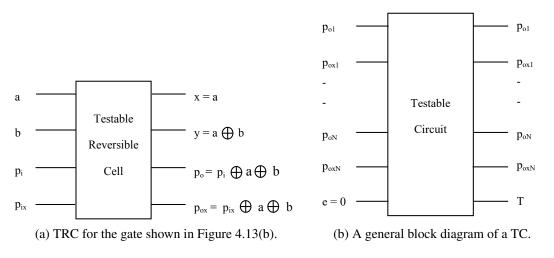

| 4.13                                                                                | A CNOT gate and its deduced version for online testing                     | 77                                                                        |

| 4.14                                                                                | TRC and TC for online testability.                                         | 78                                                                        |

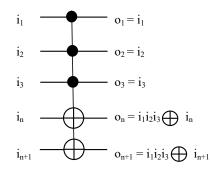

| 4.15                                                                                | A $(3+1)$ -bit ETG gate                                                    | 79                                                                        |

| 4.16                                                                                | An example of online testable reversible circuit based on [49].            | 79                                                                        |

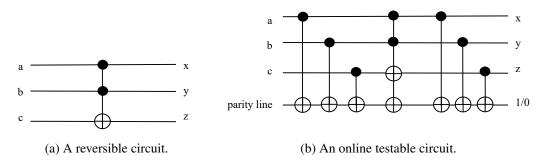

| 4.17                                                                                | An example of online testable reversible circuit based on [28].            | 80                                                                        |

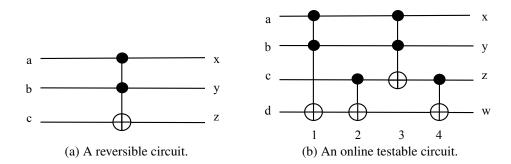

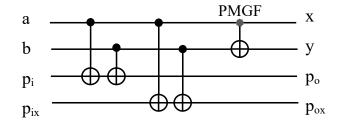

| 4.18                                                                                | Two existing reversible online testing approaches for PMGF.                | 82                                                                        |

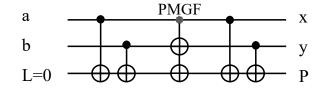

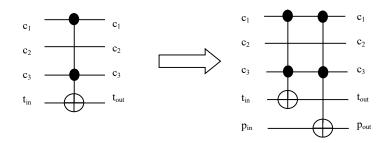

| 4.19                                                                                | Conversion of a Toffoli gate into a Duplicate Gate Block.                  | 84                                                                        |

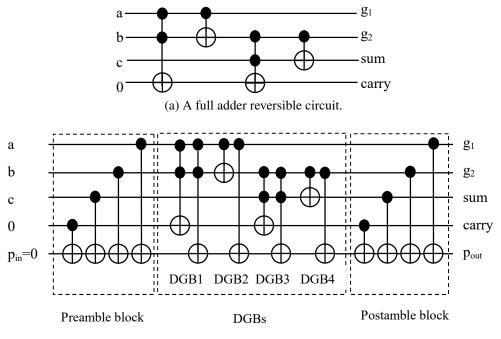

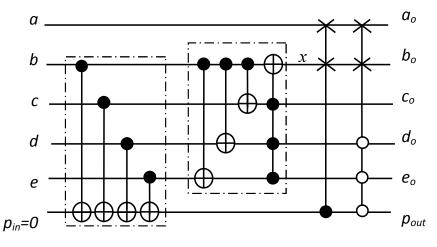

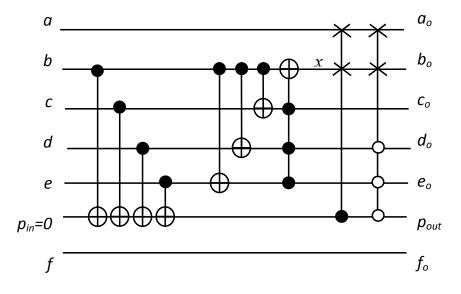

|                                                                                     | Transformation of a reversible circuit into its online testable equivalent | 85                                                                        |

|                                                                                     | Block diagram of an online testable reversible circuit.                    | 86                                                                        |

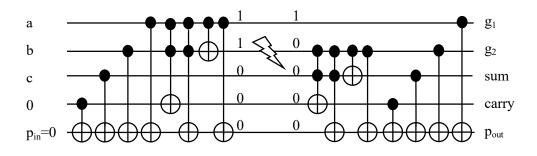

| 4.22                                                                                | Testing for the occurrences of SMGF and PMGF.                              | 89                                                                        |

| 4.23                                                                                | Testing for the occurrences of appearance crosspoint fault.                | 93                                                                        |

| 4.24                                                                                | Testing for an occurrence of a single bit fault.                           | 94                                                                        |

|                                                                                     |                                                                            |                                                                           |

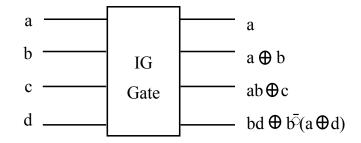

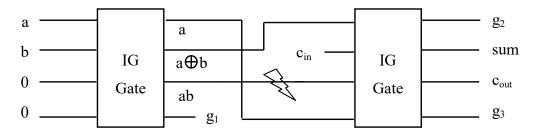

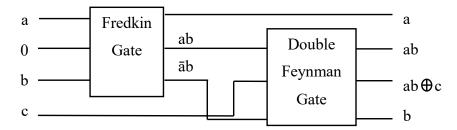

| 5.1                                                                                 | IG gate presented in [23].                                                 | 103                                                                       |

|                                                                                     |                                                                            |                                                                           |

| 5.1                                                                                 | IG gate presented in [23]                                                  | 103                                                                       |

| 5.1<br>5.2                                                                          | IG gate presented in [23]                                                  | 103<br>104                                                                |

| 5.1<br>5.2<br>5.3                                                                   | IG gate presented in [23]                                                  | 103<br>104<br>105                                                         |

| 5.1<br>5.2<br>5.3<br>5.4                                                            | IG gate presented in [23]                                                  | 103<br>104<br>105<br>108                                                  |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5                                                     | IG gate presented in [23]                                                  | 103<br>104<br>105<br>108<br>108<br>109                                    |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6                                              | IG gate presented in [23]                                                  | 103<br>104<br>105<br>108<br>108<br>109                                    |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7                                       | IG gate presented in [23]                                                  | 103<br>104<br>105<br>108<br>108<br>109<br>110                             |

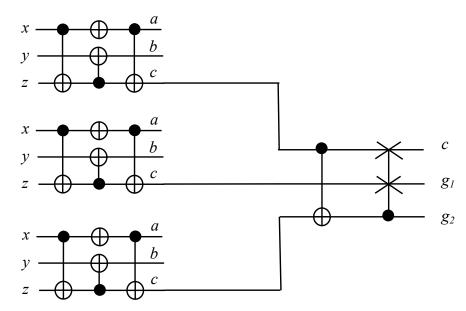

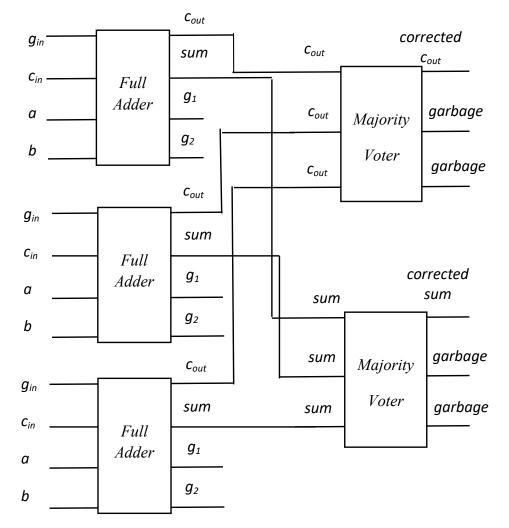

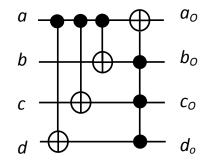

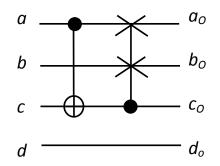

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8                                | IG gate presented in [23]                                                  | 103<br>104<br>105<br>108<br>108<br>109<br>110<br>111                      |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9                         | IG gate presented in [23]                                                  | 103<br>104<br>105<br>108<br>108<br>109<br>110<br>111<br>112               |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11         | IG gate presented in [23]                                                  | 103<br>104<br>105<br>108<br>108<br>109<br>110<br>111<br>112<br>113        |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12 | IG gate presented in [23]                                                  | 103<br>104<br>105<br>108<br>108<br>109<br>110<br>111<br>112<br>113<br>114 |

# Chapter 1 Introduction

We are living in an age where there is an ever growing dependency on digital devices. The amount of information processed by digital devices continues to increases over time. In order to process this increasing volume of information, the number of components fabricated on integrated circuits of a digital device is also increasing over time. Over the past few decades, the size of the components has been reduced in order to increase the density of these components on integrated circuits. However, this pattern cannot continue forever because the current technology is approaching the physical limits of computing [14].

Limitations of traditional computing, such as heat dissipation, can become an obstacle for the further development of current technology [14, 15]. Logic in traditional computing is irreversible. In most cases, bits of information are destroyed during the logical operations that are performed in traditional computing. One of the fundamental limitations of traditional computing is that each time information is lost, energy is dissipated regardless of the underlying technology. In 1961 R. Landauer showed that *KT1n*2 joules are dissipated each time an information bit is lost during a logical operation, where *K* is Boltzmann's constant and *T* is the operating temperature in Kelvin [30]. At room temperature, the amount of dissipated heat becomes  $2.9 \times 10^{-21}$  joules. For instance, when a two-input AND gate produces a single bit of output, this amount of energy is dissipated as heat. The amount of generated heat may not seem significant at present. However, as Moore's law [62], predicting a doubling of components every few years, has held true over the last several decades, this heat dissipation is becoming a major concern in traditional irreversible systems. Reversible computing [15] offers a solution to this potential deadlock of further development in traditional computing.

It was also shown by Charles Bennett that theoretical zero power dissipation can only be achieved if the circuit is logically reversible [5]. Reversible computing is bijective, and by definition reversible circuits are information-lossless [10]. Thus, by using reversible computation, the power dissipation which results according to Landauer's principle can be decreased or even eliminated. For this reason, in recent years reversible computation has established itself as a promising research area and emerging technology. Other reasons for research into reversible systems include connections to quantum computing [21], and applications in cryptography [64], nano-computing technologies [40] and digital processing [51]. It is widely believed that the next generation computers will be quantum computers. Quantum computations are reversible, and the circuits in quantum computing work on reversible functions [51]. Therefore, research on reversible logic is inevitable from various points of view.

# 1.1 Objectives

Most logic gates used in traditional computation are not reversible. In most cases, the relationship between the input and the output of a traditional gate is many-to-one. For example, an AND gate has two or more inputs and one output. However, the relationship between the input and the output of a reversible gate is one-to-one. Over the past few years, several reversible logic gates and synthesis methods have been proposed [11, 16, 37, 68]. However, analysing the logic gates and the synthesis approaches in order to optimize reversible circuits is still an active area of research. We hypothesize that one particular set of reversible gates can be more useful than another for realizing specific reversible functions. One of the objectives of this thesis is to develop a synthesis approach for realizing conservative reversible functions.

The number of gates of a circuit is considered an important complexity measure in tradi-

tional computing. In addition to this measure, the quantum cost and the number of garbage lines are two additional factors to consider in measuring the complexity of a reversible circuit. Template matching and rule based simplifications are two commonly used postsynthesis methods for optimizing reversible circuits. This thesis introduces new templates for simplifying reversible circuits.

The testing of reversible circuits is another important area. The physical implementation of quantum circuits will be different than the implementations of traditional circuits. Therefore, fault models designed for traditional circuits will not work for reversible circuits. Proposing a cost-effective testing approach for reversible fault models is another objective of this thesis.

Since a reversible circuit maintains a one-to-one relationship between inputs and outputs, achieving fault tolerance in such a system is not an easy task. A fault tolerant system can correctly perform its specified operations even in the presence of faults. This thesis also investigates the existing work on the design of fault tolerant reversible circuits and presents an efficient approach for achieving fault tolerance in reversible circuits.

### **1.2 Thesis Organization**

The remainder of this dissertation is organized as follows.

Chapter 2 provides a detailed introduction to reversible logic and presents the required background knowledge necessary for this dissertation.

Chapter 3 discusses transformation based synthesis in reversible logic. A proposed approach based on this technique is presented in this chapter. The performance of this proposed approach is evaluated and compared with an existing approach. This chapter also introduces templates and presents a post synthesis optimization approach for simplifying reversible circuits.

Chapter 4 describes reversible fault models and fault testing approaches. The existing testing approaches in reversible circuits are analysed and the limitations of these approaches

are identified. A testing approach for three reversible fault models is proposed later in this chapter.

Chapter 5 focuses on fault tolerance. The requirements for achieving fault tolerance in reversible circuits are discussed in this chapter. A majority voter circuit is presented, which can be used to design fault tolerant reversible circuits. An extension of this voter circuit and other areas of application of the proposed voter are also discussed in this chapter.

Chapter 6 highlights the contributions, concludes with discussions and provides directions for possible future work.

# Chapter 2

# Background

This chapter describes the fundamental concepts of reversible logic as well as the principles of synthesis, fault testing and fault tolerance in reversible logic.

# 2.1 Logic Computation

Logic plays a major role in modern day computation. Digital logic is a logic for representing and manipulating digital information. Logic in computer science deals with defining a problem in terms of Boolean functions, and designing a circuit in order to implement the functions. Logic in today's digital devices follows the principle of Boolean logic, which is also known as classical or traditional logic. As discussed in Chapter 1, there exists limits to the existing physical components of a digital system that implement traditional logic. Reversible logic offers one possible model to design a digital system to overcome such limitations.

#### 2.1.1 Traditional Logic Computation

Like any other function, a traditional logic function maps one or more inputs to one or more outputs. More specifically, a traditional logic function, f, takes the form  $f : B^n \longrightarrow B^m$ , where n and m are non-negative integers, and  $B = \{0,1\}$  is a Boolean domain. The values of n and m may or may not be equal and in most cases n > m. For example, a simple circuit consisting of only one AND gate has two (or more) inputs, but has only one output. That is, logic computations in traditional approaches often map multiple inputs to fewer outputs. A convenient way to represent the relationship between inputs and outputs is by using a truth table. A truth table shows all possible input and output combinations for a specific logic function. A truth table for a Boolean logic function uses (n+m) columns and  $2^n$  rows to show the behaviour of a function for all possible input instances of the function of *n* input and *m* output.

Table 2.1: Truth tables of traditional logic functions.

(a) NOT operation. (

| Ι | 0 |

|---|---|

| 0 | 1 |

| 1 | 0 |

| ( | b) AN | D oper | ation |

|---|-------|--------|-------|

|   | $I_1$ | $I_2$  | 0     |

|   | 0     | 0      | 0     |

|   | 0     | 1      | 0     |

|   | 1     | 0      | 0     |

|   | 1     | 1      | 1     |

|   |       |        |       |

(c) Full adder operation.

| $I_1$ | $I_2$ | Cin | sum | <i>c</i> <sub>out</sub> |

|-------|-------|-----|-----|-------------------------|

| 0     | 0     | 0   | 0   | 0                       |

| 0     | 0     | 1   | 1   | 0                       |

| 0     | 1     | 0   | 1   | 0                       |

| 0     | 1     | 1   | 0   | 1                       |

| 1     | 0     | 0   | 1   | 0                       |

| 1     | 0     | 1   | 0   | 1                       |

| 1     | 1     | 0   | 0   | 1                       |

| 1     | 1     | 1   | 1   | 1                       |

One of the simplest examples of a traditional logic function is a logical NOT operation, which takes one input and generates one output, as shown in Table 2.1(a). Tables 2.1(b) and 2.1(c) show functions for which the relationship between inputs and outputs is not one-to-one. Hence, for these functions it is not possible to determine the input states by observing only the output of a function. For example in Table 2.1(b), the output values are 0 for the input states (0,0), (0,1), and (1,0). By observing this output value, 0, it is not possible to determine whether the input values are (0,0), (0,1), or (1,0). A similar observation can be made from the truth table shown in Table 2.1(c) and most other traditional or classical logic functions. The relationship between inputs and outputs of a traditional function is not bijective (with the only exception being a NOT operation). This means that the relationship between inputs and outputs of a traditional function. Since bijective relationships between inputs and outputs do not exist for most traditional functions, it is not possible to determine an input instance from an output instance of a traditional function. For this reason traditional logic is sometimes referred to as irreversible

logic.

### 2.1.2 Reversible Logic Computation

A reversible logic function has the form  $f: B^n \longrightarrow B^n$ , where *n* is a non-negative integer and the domain  $B = \{0, 1\}$ , with the key feature being that the function is bijective. More specifically, the number of inputs and the number of outputs of a reversible function are exactly the same. In particular, there is always a distinct output state for each of the possible input states.

Table 2.2: Truth tables of reversible logic functions.

| (a) NOT | operation. |

|---------|------------|

|---------|------------|

| I | 0 |

|---|---|

| 0 | 1 |

| 1 | 0 |

(b) Contolled NOT operation.

| $I_1$ | $I_2$ | <i>O</i> <sub>1</sub> | <i>O</i> <sub>2</sub> |

|-------|-------|-----------------------|-----------------------|

| 0     | 0     | 0                     | 0                     |

| 0     | 1     | 0                     | 1                     |

| 1     | 0     | 1                     | 1                     |

| 1     | 1     | 1                     | 0                     |

| 8 in | c <sub>in</sub> | $i_1$ | <i>i</i> <sub>2</sub> | Cout | sum | gout 1 | gout2 |

|------|-----------------|-------|-----------------------|------|-----|--------|-------|

| 0    | 0               | 0     | 0                     | 0    | 0   | 0      | 0     |

| 0    | 0               | 0     | 1                     | 0    | 1   | 1      | 1     |

| 0    | 0               | 1     | 0                     | 0    | 1   | 1      | 0     |

| 0    | 0               | 1     | 1                     | 1    | 0   | 0      | 1     |

| 0    | 1               | 0     | 0                     | 0    | 1   | 0      | 0     |

| 0    | 1               | 0     | 1                     | 1    | 0   | 1      | 1     |

| 0    | 1               | 1     | 0                     | 1    | 0   | 1      | 0     |

| 0    | 1               | 1     | 1                     | 1    | 1   | 0      | 1     |

| 1    | 0               | 0     | 0                     | 1    | 0   | 0      | 0     |

| 1    | 0               | 0     | 1                     | 1    | 1   | 1      | 1     |

| 1    | 0               | 1     | 0                     | 1    | 1   | 1      | 0     |

| 1    | 0               | 1     | 1                     | 0    | 0   | 0      | 1     |

| 1    | 1               | 0     | 0                     | 1    | 1   | 0      | 0     |

| 1    | 1               | 0     | 1                     | 0    | 0   | 1      | 1     |

| 1    | 1               | 1     | 0                     | 0    | 0   | 1      | 0     |

| 1    | 1               | 1     | 1                     | 0    | 1   | 0      | 1     |

(c) Full adder operation.

The work in this thesis is restricted to Boolean reversible logic functions. For a Boolean reversible function of n variables, a truth table requires 2n columns and  $2^n$  rows in order to represent the function. Table 2.2(a) shows that a NOT operation in reversible logic has the same functionality as that of a traditional NOT operation (Table 2.1(a)). In fact, a NOT operation in traditional logic is reversible in nature. As long as there is a unique output for each input instance of a function, the function is reversible (Table 2.2). This relationship between the input and the output allows the determination of input values of a function from the output values. In order to transform an irreversible function into a reversible one, it is often necessary to include one or more extra variables on the output and/or input sides of a truth table of the irreversible function. For example, the truth table of a reversible full adder shown in Table 2.2(c) consists of extra variables on both the input and output as compared to the truth table of its irreversible counterpart shown in Table 2.1(c). The additional inputs are called constant inputs, or ancilla inputs. The additional outputs are non-functional outputs because these are not the output of interest of the reversible function. In a full adder, sum and carry are the two output bits of interest. In Table 2.2(c), two outputs, sum and  $c_{out}$ , represent the sum and the carry bits of a full adder. The other two outputs,  $g_{out1}$  and  $g_{out2}$ , are used to maintain the bijective relationship between the inputs and the outputs of this reversible full adder function. These non-functional outputs are known as garbage outputs, as they do not contribute to the property of the original output of a function.

Two important properties of reversible functions are the parity preserving property and the conservation property. A parity preserving reversible function, as the name suggests, preserves the parity of the input vectors to the corresponding output vector. For example, in a parity preserving reversible function, if the parity of an input vector is even, the parity of the output vector will also be even. Every output vector of the function shown in Table 2.3(a) preserves the parity (either odd or even) of the corresponding input vector. Hence, the function shown in Table 2.3(a) is an example of a parity preserving function. However, this function is not a conservative function. A reversible function is called a conservative function if and only if the number of 1s in the output vector is the same as that of the corresponding input vector, for all inputs. The function shown in Table 2.3(b) is an example of a conservative reversible function. Chapter 4 shows the role of the parity preserving property in the fault detection and testing of reversible circuits. A synthesis approach based on the conservation property is presented in Chapter 3.

| (a) A parity preserving function. |       |       |                       |       |                       |  |  |

|-----------------------------------|-------|-------|-----------------------|-------|-----------------------|--|--|

|                                   | inpu  | t     |                       | outpu | t                     |  |  |

| $I_1$                             | $I_2$ | $I_3$ | <i>O</i> <sub>1</sub> | $O_2$ | <i>O</i> <sub>3</sub> |  |  |

| 0                                 | 0     | 0     | 0                     | 0     | 0                     |  |  |

| 0                                 | 0     | 1     | 0                     | 1     | 0                     |  |  |

| 0                                 | 1     | 0     | 1                     | 1     | 1                     |  |  |

| 0                                 | 1     | 1     | 1                     | 1     | 0                     |  |  |

| 1                                 | 0     | 0     | 0                     | 0     | 1                     |  |  |

| 1                                 | 0     | 1     | 0                     | 1     | 1                     |  |  |

| 1                                 | 1     | 0     | 1                     | 0     | 1                     |  |  |

| 1                                 | 1     | 1     | 1                     | 0     | 0                     |  |  |

Table 2.3: Parity preserving and conservative reversible functions.

(b) A conservative function.

| j     | inpu       | t | output |       |                       |  |  |

|-------|------------|---|--------|-------|-----------------------|--|--|

| $I_1$ | $I_1  I_2$ |   | $O_1$  | $O_2$ | <i>O</i> <sub>3</sub> |  |  |

| 0     | 0          | 0 | 0      | 0     | 0                     |  |  |

| 0     | 0          | 1 | 0      | 1     | 0                     |  |  |

| 0     | 1          | 0 | 1      | 0     | 0                     |  |  |

| 0     | 1          | 1 | 1      | 1     | 0                     |  |  |

| 1     | 0          | 0 | 0      | 0     | 1                     |  |  |

| 1     | 0          | 1 | 0      | 1     | 1                     |  |  |

| 1     | 1          | 0 | 1      | 0     | 1                     |  |  |

| 1     | 1          | 1 | 1      | 1     | 1                     |  |  |

### 2.2 Logic Gates and Circuits

A logic gate performs one or more logical operations in order to implement a logical function. A circuit consists of one or more logic gates, which are connected by some form of interconnected media (e.g. wire). This section describes some logic gates as well as logic circuits in traditional and reversible logic computation.

#### 2.2.1 Traditional Logic Gates

Several logic gates exist for designing circuits in traditional logic. The gates AND, OR and NOT are the primary logic gates. Figure 2.1 shows both a NOT and an AND logic gate. These two gates are used to implement the traditional NOT (Table 2.1(a)) and AND (Table 2.1(b)) functions, respectively. A NOT gate works as an inverter, which always

takes one input and produces one output after inverting the input value. An AND gate, on the other hand, works on more than one input and produces a single output. A full adder circuit, which consists of traditional logic gates, is shown in Figure 2.1(c), and implements the function represented by Table 2.1(c). A traditional full adder circuit has three input lines and two outputs lines to generate sum and carry bits.

Figure 2.1: Some traditional circuits.

#### 2.2.2 Reversible Logic Gates

A reversible circuit consists of one or more reversible gates that are connected in cascade. That is, the output(s) of a prior gate is/are connected as input(s) to the following gate. For example, consider a reversible circuit  $g_2(g_1(x_1,x_2))$  where the outputs of a logic gate  $g_1$  are connected as the inputs of the gate  $g_2$  in order to implement a 2-bit reversible function,  $f(x_1,x_2)$ . Like a reversible logic function, one of the fundamental characteristics of a reversible gate is that the relationship between inputs and outputs is one-to-one. This implies that the output values of a reversible gate are distinct for any given input. So unlike a traditional irreversible gate, it is always possible to restore the input values of a reversible gate from the outputs. A traditional NOT gate is also a reversible gate, since it is possible to deduce the input of a NOT gate from its output. For example, 1 at the output of a NOT gate for a particular instance indicates that the input of that instance is 0.

A number of reversible gates exist in order to implement reversible functions. The two most widely used categories of reversible logic gates are [71] : the NCT (NOT-CNOT-Toffoli) gate family and the SF (SWAP-Fredkin) gate family.

#### NCT gate family

The NCT gate family (Figure 2.2) consists of NOT, CNOT and Toffoli gates. This is one of the most widely used gate families in reversible computing. The simplest possible reversible logic gate is a NOT gate. A NOT gate (Figure 2.2(a)), like a NOT gate in traditional logic, consists of one input and one output, which inverts the value of the input to generate the output. A CNOT gate and a Toffoli gate are variations of a NOT gate.

A CNOT gate [12] is a controlled-NOT gate with a control input and a target input. The value presented at the control point determines when to invert the value of the target input, or simply transfers the target input value to the output. Figure 2.2(b) shows a CNOT gate. The (•) symbol in the CNOT gate represents a control point and the ( $\oplus$ ) symbol indicates the target of a reversible gate. When the value of the control of a CNOT gate is 1, the gate inverts the value of the input that is connected to the target line. If the value of the control point is 0, the value of the target input remains unchanged to the target output. For example, when the inputs of a CNOT( $I_1$ ,  $I_2$ ) gate in Figure 2.2(b) are (1,0), the output ( $O_1, O_2$ ) will be  $(1, 1 \oplus 0) \equiv (1, 1)$ . Unlike a NOT gate, a CNOT gate can control the inversion of an input value, hence its name is controlled-NOT or CNOT. A CNOT gate is also known as Feynman gate. A variation of a Feynman gate is a double Feynman gate. A variation of a Feynman gate is a double Feynman gate. A total point is 1, the double Feynman gate inverts both input values that are connected to the target lines [53].

A Toffoli gate [68] is a form of the CNOT gate where the number of control points is

Figure 2.2: Some reversible gates of NCT gate family.

more than 1. For example, Figure 2.2(c) shows a  $3 \times 3$  Toffoli gate with two control points and one target line. The two input lines,  $I_1$  and  $I_2$ , are connected to the two control points and the third input  $I_3$  is connected to the target line. The values of the inputs, which are connected to the control lines, remain unchanged at the output. The values presented at the input of these control lines determine when the gate will invert the value presented at the target input line. The target line in Figure 2.2(c) has the function:  $O_3 = I_3 \oplus I_1 I_2$ . This means the value of the target line will be inverted when both inputs that are connected to the control points have the value 1. For example, when  $(I_1, I_2, I_3) \equiv (0, 1, 1)$ , the output of the Toffoli gate will be  $(O_1, O_2, O_3) \equiv (0, 1, 1)$ . In this case there is no change on the value of the target input, since one of the control points  $(I_1)$  is equal to 0. However, when  $(I_1, I_2, I_3) \equiv (1, 1, 1)$ the gate output will be  $(O_1, O_2, O_3) \equiv (1, 1, 1 \oplus 1 \cdot 1) \equiv (1, 1, 1 \oplus 1) \equiv (1, 1, 0)$ . In this case both control points have the value 1, which is the required condition for inverting the input values at the output. The truth table of a  $3 \times 3$  Toffoli gate is shown in Table 2.4.

Based on the number *k* of control points of a gate, a logic gate in the NCT family is also referred to as a *k*-CNOT gate. For example, based on the number of control lines the NOT, CNOT and  $3 \times 3$  Toffoli gates are also known as 0-CNOT, 1-CNOT and 2-CNOT gates respectively. A Toffoli gate with multiple controls is referred to as a multiple controlled Toffoli (MCT) gate. In addition, a Toffoli gate or a Feynman gate can have one or more

|       | inpu  | t     | output |       |                       |  |

|-------|-------|-------|--------|-------|-----------------------|--|

| $I_1$ | $I_2$ | $I_3$ | $O_1$  | $O_2$ | <i>O</i> <sub>3</sub> |  |

| 0     | 0     | 0     | 0      | 0     | 0                     |  |

| 0     | 0     | 1     | 0      | 0     | 1                     |  |

| 0     | 1     | 0     | 0      | 1     | 0                     |  |

| 0     | 1     | 1     | 0      | 1     | 1                     |  |

| 1     | 0     | 0     | 1      | 0     | 0                     |  |

| 1     | 0     | 1     | 1      | 0     | 1                     |  |

| 1     | 1     | 0     | 1      | 1     | 1                     |  |

| 1     | 1     | 1     | 1      | 1     | 0                     |  |

Table 2.4: Truth table of a  $3 \times 3$  Toffoli Gate.

negative control points. For example, a negative control Feynman (1-CNOT) gate inverts the input value at the target line if and only if the value of the control point is 0. A negative control is represented by a ( $\circ$ ) symbol in the NCT gate library. For example, Figure 2.2(d) shows a multiple controlled Toffoli gate where two input lines  $I_1$  and  $I_3$  are connected to the two negative control lines. A negative control, like a positive control of a logic gate, does not affect the value on the line to which it is connected. The output function of the target of a  $n \times n$ -Toffoli gate, as shown in Figure 2.2(d), is  $O_n = I_n \oplus \overline{I_1}I_2 \overline{I_3}I_{n-1}$ . This means that when the values of all negative control points are 0, and the values of all positive control points are 1, the gate will invert the value that is connected to its target input.

Another common way to represent the gates of the NCT family is in the form of Toffoli gates. A TOF(C;T) notation is used to indicate a Toffoli gate with C control points and T target lines. For instance, TOF(0;T), TOF(1;T) and TOF(2;T) represent a NOT, a CNOT and a  $3 \times 3$  Toffoli gates, respectively. An important property of a Toffoli gate is that it can be used to implement any reversible function. For this reason, a Toffoli gate is known as a universal gate in reversible logic [52].

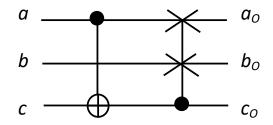

#### SF Gate Family

Two other important reversible logic gates are SWAP and Fredkin gates. A Fredkin gate [16] is a variation of SWAP gate with one or more control points. A Fredkin gate is also a

universal gate in reversible logic, since it is possible to implement the three basic operations (NOT, AND and OR) using only Fredkin gates [52]. As discussed above, the logic gates in the NCT gate family invert the value of the target input based on certain conditions (in the case of CNOT, Toffoli gates) or without any condition (in the case of NOT gates). Instead of inverting the input value on a target line, the target lines of an SF gate interchange their values. Generally, a gate of the SF gate family has two target lines. When a gate interchanges the values of the target lines at the output without any condition, the gate is called a SWAP gate. However, if the swap or interchange of the target values occurs based on the values presented on the control lines, the gate is called a Fredkin gate. The truth table of a  $3 \times 3$  positive controlled Fredkin gate is shown in Table 2.5. Figures 2.3(a) and 2.3(b) Table 2.5: Truth table of a  $3 \times 3$  positive controlled Fredkin gate.

|       | input |       |       | output |                       |  |  |

|-------|-------|-------|-------|--------|-----------------------|--|--|

| $I_1$ | $I_2$ | $I_3$ | $O_1$ | $O_2$  | <i>O</i> <sub>3</sub> |  |  |

| 0     | 0     | 0     | 0     | 0      | 0                     |  |  |

| 0     | 0     | 1     | 0     | 0      | 1                     |  |  |

| 0     | 1     | 0     | 0     | 1      | 0                     |  |  |

| 0     | 1     | 1     | 0     | 1      | 1                     |  |  |

| 1     | 0     | 0     | 1     | 0      | 0                     |  |  |

| 1     | 0     | 1     | 1     | 1      | 0                     |  |  |

| 1     | 1     | 0     | 1     | 0      | 1                     |  |  |

| 1     | 1     | 1     | 1     | 1      | 1                     |  |  |

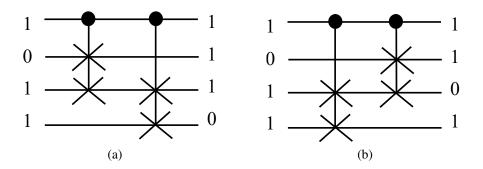

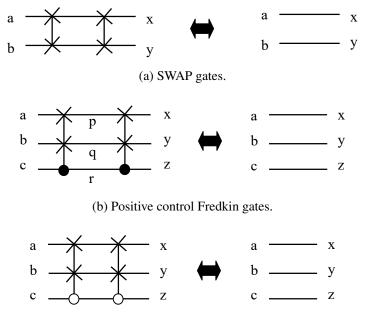

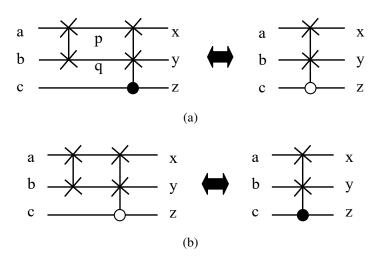

$\begin{vmatrix} 1 & 1 & 1 \\ \end{vmatrix}$   $\begin{vmatrix} 1 & 1 & 1 \\ \end{vmatrix}$   $\begin{vmatrix} 1 & 1 & 1 \\ \end{vmatrix}$   $\begin{vmatrix} 1 & 1 & 1 \\ \end{vmatrix}$  show a SWAP gate and a 3 × 3 positive controlled Fredkin gate respectively. A SWAP gate always swap the values which are connected to its targets lines. For an input vector  $(I_1, I_2)$ , the output of the SWAP gate will be  $(O_1 = I_2, O_2 = I_1)$ , as shown in Figure 2.3(a). However, a positive controlled Fredkin gate interchanges two target input values  $(I_2, I_3)$  if the value of the other input,  $I_1$ , which is connected to a control line (•), is 1. If the value of  $I_1$  equals to 0, the Fredkin gate simply transfers all the input values to the corresponding output values without interchanging the target values. A 3 × 3 positive controlled Fredkin gate with a control point connected to  $I_1$ , and two target lines,  $I_2$  and  $I_3$ , has the following output functions at

- 1. control point:  $O_1 = I_1$

- 2. target line:  $O_2 = \overline{I_1}I_2 \oplus I_1I_3$ , and

- 3. target line:  $O_3 = I_1 I_2 \oplus \overline{I_1} I_3$ .

Figure 2.3: Some reversible logic gates of the SF gate family.

When a Fredkin gate consists of more than one control point, the Fredkin gate is called a multiple controlled Fredkin (MCF) gate. Like a Toffoli gate, a Fredkin gate can also have one or more negative controls (Figure 2.3(c)). In this case the gate swaps the values connected to the target lines if and only if a 0 value is presented at the negative control point. Figure 2.3(d) shows an example of a multiple controlled Fredkin gate consisting of both positive and negative control points. In this case a 1 at the positive control and a 0 at the negative control point activate the gate to interchange the values on the target lines.

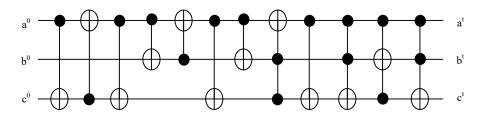

One or more reversible gates can be used to generate a circuit in order to implement a reversible function. For example, consider a reversible function  $f(I_1, I_2, I_3) \equiv (O_1, O_2, O_3)$  where  $(O_1, O_2, O_3)$  are defined as  $(\overline{I_1}, \overline{I_1} \oplus I_2, (\overline{I_1} \oplus \overline{I_1}I_2) \oplus I_3)$  respectively. These three output functions can be implemented by the circuit  $TOF(TOF(TOF(I_1); I_2); I_3)$  consisting of three reversible gates as shown in Figure 2.4. As seen in this example the outputs of one

gate  $g_i$  are connected as the inputs for the gate  $g_{i+1}$  which appears immediately next to  $g_i$ in the circuit. The output of the NOT gate,  $TOF(I_1)$ , is  $\overline{I_1}$  which is connected as an input of the following CNOT gate. This then computes  $TOF(TOF(I_1); I_2) = TOF(\overline{I_1}; I_2) =$  $(\overline{I_1}, \overline{I_1} \oplus I_2)$ . Finally, the outputs of this CNOT gate are connected as the inputs of the 3bit Toffoli gate, which computes  $TOF(TOF(TOF(I_1); I_2); I_3) = TOF(TOF(\overline{I_1}; I_2); I_3) =$  $TOF(\overline{I_1}, \overline{I_1} \oplus I_2; I_3) = (\overline{I_1}, \overline{I_1} \oplus I_2, \overline{I_1} \cdot (\overline{I_1} \oplus I_2) \oplus I_3) = (\overline{I_1}, \overline{I_1} \oplus I_2, \overline{I_1} \oplus \overline{I_2} \oplus I_3)$ .

Figure 2.4: A reversible circuit consisting of three gates.

# 2.3 Synthesis Approaches in Reversible Logic

The concept of synthesis is very important in designing reversible logic circuits. Synthesis refers to the transformation of a logic function into a corresponding logic circuit. According to some synthesis approaches, if a logic function is irreversible, the first step of a logic synthesis is to transform the function into its reversible equivalent. One or more garbage lines and/or constant inputs are included in the original irreversible function in order to make the function reversible. The final step is to transform the reversible function into a logic circuit consisting of one or more reversible gates which are connected in cascade. The resulting circuit is a reversible circuit. There can be more than one reversible circuit for implementing a single function. Two important factors play a significant role in transforming irreversible functions into reversible circuits: (1) the number of garbage lines and/or constant inputs, which are included in order to transform the irreversible function to a reversible one; and (2) the use of different reversible logic gates for realizing the reversible function by a reversible circuit. During the process of transforming an irreversible function into the corresponding reversible function, it is necessary to observe the output of the irreversible function. If the output of an irreversible function has a maximum number of k identical patterns, the minimum number of garbage lines required to make the function reversible is  $\lceil log_2k \rceil$  [35]. For instance, consider the irreversible AND function in Table 2.6(a). The output of this irreversible function has 3 occurrences of logic 0. Thus the minimum number of garbage lines required in order to transform the function into its reversible counterpart is  $\lceil log_23 \rceil = 2$  as shown in Table 2.6(b). For the input line,  $I_3 = 0$  in Table 2.6(b), the function performs the AND operation of input lines,  $I_1$  and  $I_2$ , and generates the output at  $O_3$ . The other two output lines,  $O_1$  and  $O_2$ , do not contribute to the final output, and hence these two lines are considered garbage lines. An important fact to observe is that the behaviour of the function in Table 2.6(b) is the same as the behaviour of a  $3 \times 3$ -Toffoli gate (Table 2.2(c)). Thus, a 2-input traditional AND operation can be implemented by a  $3 \times 3$ -Toffoli gate, as shown in Figure 2.5. Chapter 3 covers more regarding synthesis and post synthesis approaches in reversible logic.

Table 2.6: Transformation of an irreversible function to a reversible one.

| (a) Irreversible AND function. |       |        |  |  |  |  |

|--------------------------------|-------|--------|--|--|--|--|

| inj                            | out   | output |  |  |  |  |

| $I_1$                          | $I_2$ | 0      |  |  |  |  |

| 0                              | 0     | 0      |  |  |  |  |

| 0                              | 1     | 0      |  |  |  |  |

| 1                              | 0     | 0      |  |  |  |  |

| 1                              | 1     | 1      |  |  |  |  |

11 .....

( ) T

| (b) One possible corresponding | ng |

|--------------------------------|----|

| reversible AND function.       |    |

| input |       |       | output                |       |                       |  |  |

|-------|-------|-------|-----------------------|-------|-----------------------|--|--|

| $I_1$ | $I_2$ | $I_3$ | <i>O</i> <sub>1</sub> | $O_2$ | <i>O</i> <sub>3</sub> |  |  |

| 0     | 0     | 0     | 0                     | 0     | 0                     |  |  |

| 0     | 0     | 1     | 0                     | 0     | 1                     |  |  |

| 0     | 1     | 0     | 0                     | 1     | 0                     |  |  |

| 0     | 1     | 1     | 0                     | 1     | 1                     |  |  |

| 1     | 0     | 0     | 1                     | 0     | 0                     |  |  |

| 1     | 0     | 1     | 1                     | 0     | 1                     |  |  |

| 1     | 1     | 0     | 1                     | 1     | 1                     |  |  |

| 1     | 1     | 1     | 1                     | 1     | 0                     |  |  |

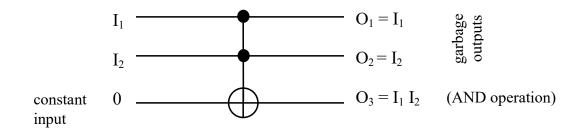

Figure 2.5: A  $3 \times 3$ -Toffoli gate operating as an AND gate.

### 2.4 Cost Metrics in Reversible Logic

Since a reversible function can be synthesized in multiple ways, it is necessary to evaluate the cost of the synthesis approaches. A number of metrics can be used to evaluate the efficiency of circuits for realizing the same reversible function [45]. Gate count is one of the most common cost metrics, particularly in traditional logic design. As the name suggests, gate count refers to the number of gates required in a circuit to realize a function. For example, one Toffoli gate is used to implement the AND operation, as shown in Figure 2.5. In this case the gate count is 1. However, gate count is not a useful parameter when the circuits consist of different types of gates. Gate count does not consider gate complexity; it instead simply counts the number of gates of the same size and complexity. Mohammadi et al. [45] proposed a new form of gate count by giving some weight to the gates based on the complexity of the gates of a circuit.

The number of garbage outputs in a circuit is another important cost metric. During the synthesis process in reversible logic, one or more garbage outputs may be needed for maintaining reversibility. The values of the garbage lines are not significant to the final output of a circuit. Therefore, it is desirable to minimize the number of garbage outputs. A circuit design with fewer garbage lines is considered a desirable design.

For many, quantum cost is the most important parameter for evaluating a reversible circuit from a design standpoint. Quantum cost is defined as the number of basic or primitive quantum gates which are required to design a reversible gate. The  $1 \times 1$  and  $2 \times 2$  quan-

| Size ( <i>n</i> ) | Garbage      | Name       | Quantum Cost |

|-------------------|--------------|------------|--------------|

| 1                 | 0            | NOT,t1     | 1            |

| 2                 | 0            | CNOT,t2    | 1            |

| 3                 | 0            | Toffoli,t3 | 5            |

| 4                 | 0            | Toffoli,t4 | 13           |

| 5                 | 0            | t5         | 29           |

| 5                 | 2            | t5         | 26           |

| 6                 | 0            | t6         | 61           |

| 6                 | 1            | t6         | 52           |

| 6                 | 3            | t6         | 38           |

| 7                 | 0            | t7         | 125          |

| 7                 | 1            | t7         | 80           |

| 7                 | 4            | t7         | 50           |

| 8                 | 0            | t8         | 253          |

| 8                 | 1            | t8         | 100          |

| 8                 | 5            | t8         | 62           |

| 9                 | 0            | t9         | 509          |

| 9                 | 1            | t9         | 128          |

| 9                 | 6            | t9         | 74           |

| 10                | 0            | t10        | 1021         |

| 10                | 1            | t10        | 152          |

| 10                | 7            | t10        | 86           |

| <i>n</i> > 10     | 0            | tn         | $2^{n}-3$    |

| <i>n</i> > 10     | 1            | tn         | 24n - 88     |

| <i>n</i> > 10     | <i>n</i> – 3 | tn         | 12n - 34     |

Table 2.7: Quantum cost of  $n \times n$  Toffoli gates.

tum gates are considered primitive quantum gates. For example, quantum NOT, CNOT, V and  $V^+$  gates are considered primitive quantum gates, and the quantum cost of these gates is considered to be 1. The quantum cost of a Toffoli gate and a Fredkin gate is 5, since five primitive gates are required for designing these gates. Barenco et al. [4] showed a realization of a  $3 \times 3$  Toffoli gate consisting of 2 positive control points using five primitive quantum gates. Smolin and DiVincenzo [66] presented an implementation of a  $3 \times 3$ positive-controlled Fredkin gate using five 2-qubit (quantum bit) elementary quantum gates.

Quantum compution and quantum gates are beyond the scope of this thesis. A detailed discussion on quantum gates can be found in [4, 43, 51]. In addition, there have been a

number of works such as [2, 4, 34, 35, 39, 33, 58] on minimizing the quantum cost for designing a reversible circuit. Table 2.7 shows the quantum cost of positive control Toffoli gates [71].

| j     | inpu  | t     | output                |       |                       |  |  |

|-------|-------|-------|-----------------------|-------|-----------------------|--|--|

| $I_1$ | $I_2$ | $I_3$ | <i>O</i> <sub>1</sub> | $O_2$ | <i>O</i> <sub>3</sub> |  |  |

| 0     | 0     | 0     | 0                     | 0     | 0                     |  |  |

| 0     | 0     | 1     | 1                     | 0     | 0                     |  |  |

| 0     | 1     | 0     | 0                     | 0     | 1                     |  |  |

| 0     | 1     | 1     | 1                     | 1     | 0                     |  |  |

| 1     | 0     | 0     | 0                     | 1     | 0                     |  |  |

| 1     | 0     | 1     | 1                     | 0     | 1                     |  |  |

| 1     | 1     | 0     | 0                     | 1     | 1                     |  |  |

| 1     | 1     | 1     | 1                     | 1     | 1                     |  |  |

Table 2.8: A 3-bit reversible function.

Another important factor to consider when designing reversible circuits is to minimize the number of garbage outputs. However, there are some cases where the quantum cost of a circuit can be reduced by adding garbage lines [33]. For example, as seen from Table 2.7, the quantum cost of a  $6 \times 6$  Toffoli gate without including any extra line as a garbage line is 61. However, after adding 1 and 3 lines as garbage lines the quantum cost of a  $6 \times 6$  Toffoli gate can be reduced to 52 and 38 respectively. Therefore, a large number of garbage lines does not always yield a higher quantum cost.

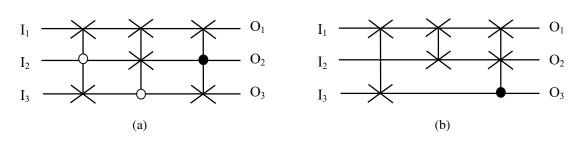

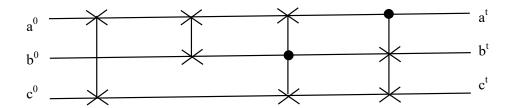

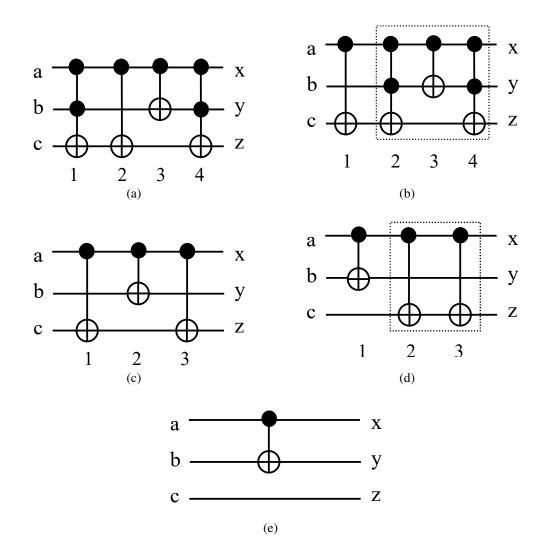

Figure 2.6: Two different realizations of the same function using the SF gate family.

Similarly a higher gate count for a circuit does not necessarily mean a higher quantum cost. Consider the  $3 \times 3$  reversible function shown in Table 2.8. Figure 2.6 shows

two different implementations of this function using only SWAP and Fredkin gates. Both implementations have a gate count of 3. The realization in Figure 2.6(a) uses two negative-controlled Fredkin gates and one positive-controlled Fredkin gate. The quantum cost of the first implementation is (5+5+5) = 15. The circuit in the second implementation, shown in Figure 2.6(b), uses two SWAP gates and one  $3 \times 3$  positive-controlled Fredkin gate. Here the quantum cost is (3+3+5) = 11. Both circuits consist of 3 logic gates; however, the second circuit offers a more efficient circuit design, from the perspective of the quantum cost, than the first circuit.

### **2.5** Faults and Fault Testing in Reversible Logic

A fault leads to a failure of a system. A fault can be defined as an imperfection within some hardware and/or software components. Therefore, a fault leads the system to produce an incorrect output. This incorrect output is known as an error, which is a deviation from the accurate outcome [26]. Faults are the unwanted events for a system and, therefore, must be detected and removed.

A fault model is a model that considers the potential faults which may occur in a system [59]. An ideal fault detection method can detect all the faults of a particular fault model. A common fault model in traditional logic is the stuck-at fault model. Sometimes a wire can pass only high or low voltage signals due to the malfunction of some part of a circuit. That is, a path of a circuit is "*stuck at*" a particular voltage level. When a line of a circuit passes only high voltage due to the occurrence of a fault, the fault is considered to be a stuck-at 1 fault. When a line of a circuit passes only low voltage, the fault is considered to be a stuck-at 0 fault. As a consequence the circuit generates an incorrect output. For example, if a line is broken, it is considered open and the output of that line will always be 0. The fault in this situation is refered to be stuck-at 0. However, research suggests that the stuck-at fault model is not an appropriate fault model in reversible computing [20, 73]. A number of fault models for reversible logic have been proposed [20, 56, 73].

A method of testing is required in order to identify the occurrence of a fault in a circuit. Testing indicates whether a system is faulty or fault-free. Fault coverage is an important concept in testing which relates fault models to testing strategies. Fault coverage is a ratio of the number of faults detected by a testing method to the total number of detectable faults for a given fault model. Methods of testing in reversible computation are divided into two categories: offline testing and online testing [59]. Each has its own benefits and drawbacks. Online testing approaches apply the testing operations in real time. That is, online testing methods determine whether the output of a system is correct or incorrect while the system is performing its normal operations. However, this is not the case for an offline testing method. In offline testing, the system under consideration is taken out of its normal mode of operation, and then the method of testing is applied. Fault models and testing approaches in reversible logic are described in detail in Chapter 4 of this thesis.

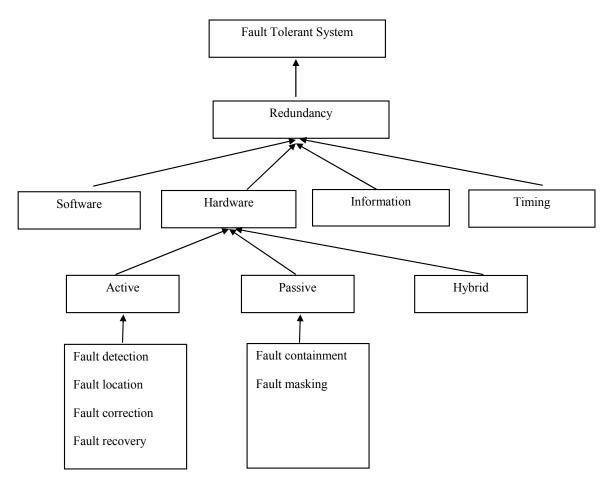

# 2.6 Fault Tolerance in Reversible Logic

The difference between fault testing and fault tolerance is that fault testing is a process of error identification whereas fault tolerance is a process of error correction. Fault tolerance is an attribute that enables a system to generate correct output even in the presence of faults in the system. One or more techniques may be required in order to achieve fault tolerance. These may include fault detection, fault diagnosis, fault containment, fault recovery and fault masking. Each of these techniques requires additional logical or physical components of the system such as hardware, software and/or information [26]. For example, one way to achieve fault tolerance in a system is to replicate one or more physical components of the system. The techniques and approaches that can be used to achieve fault tolerance in reversible circuits are described in Chapter 5.

# Chapter 3 Synthesis and Post-Synthesis

This chapter begins with providing the basic concepts of synthesis in reversible logic. A transformation-based synthesis is proposed in this chapter. This chapter also introduces templates for optimizing reversible circuits. Experimental results that evaluate the proposed templates are provided at the end of the chapter.

## 3.1 Logic Synthesis in Reversible Logic

Logic synthesis is the process of generating a circuit design, described as a cascade of gates, that can implement the desired logic function. The relationship between the inputs and the outputs of a logic function determines the number of the logic gates, type of logic gates used, and the order in which the logic gates appear in the circuit. If a logic function is already reversible, the synthesis process can take place immediately. However, if a logic function is not reversible, the first step in most synthesis algorithms is to transform the irreversible function into a reversible one. One or more garbage outputs and/or constant inputs are added to an irreversible function in order to transform the irreversible logic function. Section 2.3 in Chapter 2 shows an example of transforming an irreversible AND function into a reversible function. In most cases, a reversible circuit design with fewer garbage outputs and/or constant inputs is considered a desirable design. The minimum number of garbage outputs which are required in order to transform an irreversible function into a reversible function is  $\lceil log_2 K \rceil$ , where *K* is the maximum number of a repeated pattern in the output of an irreversible function [35].

A number of logic synthesis techniques in reversible logic have been proposed as described in [60]. In this work we focus on transformation based logic synthesis.

#### 3.1.1 The Transformation Based Synthesis Approach [41]

A transformation based approach takes as its input a truth table of a reversible function, and applies reversible logic operations to transform the function into an identity function. The gates which perform these logic operations during the tranformation constitute the circuit that implements the input reversible function. The gates appear in the circuit in the same order in which the logical operations are performed during transformation. Before the synthesis takes place if a function is not reversible, the first step is to transform the irreversible function into a reversible function. Works such as proposed by Maslov et al. [35] and Miller et al. [42] describe techniques for this. One of the major advantages of a transformation-based synthesis approach is that the process of generating circuits based on this approach does not create any garbage output or constant input lines. Thus, in terms of the number of inputs and outputs lines, the size of the circuit generated by a transformation based synthesis is minimal.

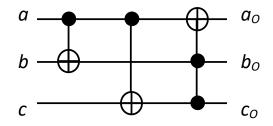

The transformation based synthesis algorithm was proposed by Miller et al. [41]. The authors demonstrated two variations: a basic algorithm and a bidirectional algorithm, both based on the NCT gate library. In the basic algorithm, the reversible logic operations are applied to the output of the function's truth table. We assume that we are applying the algorithm to a reversible function of *n* variables. The objective is to make f(i) = i, for i = 0 to  $2^n - 1$ , where *i* is the *i*-th row of a reversible function, *f*. The following is the basis of the transformation based logic synthesis approach (from [41]):

Step 0: If f(0) = 0, no transformation is required and go to step 1. Otherwise, if  $f(0) \neq 0$ , apply one or more  $(1 \times 1)$  Toffoli gates (i.e. NOT gates) in order to achieve f(0) = 0. After applying the NOT gate(s), the value 000 will be at the top row of the output truth table, as shown in Table 3.1.

Step 1: Repeat for i = 1 to  $2^n - 1$ : If f(i) = i, no transformation is required. If  $f(i) \neq i$ , apply the smallest  $(k \times k)$  Toffoli gate, k = 2 to n in order to make f(i) = i. One or more gates may be required in order to achieve f(i) = i.

The choice of a gate during each step of the transformation is crucial in order to maintain convergence. The gate in one step of transformation must not change the bits of the previous steps. Consider the  $(3 \times 3)$  reversible function shown in Table 3.1. The transformation based synthesis transforms this function to an identity function.

|     | input |       |       | C     | output |       |     |

|-----|-------|-------|-------|-------|--------|-------|-----|

|     | $a_i$ | $b_i$ | $c_i$ | $a_o$ | $b_o$  | $C_O$ |     |

| (0) | 0     | 0     | 0     | 0     | 0      | 0     | (0) |

| (1) | 0     | 0     | 1     | 1     | 0      | 0     | (4) |

| (2) | 0     | 1     | 0     | 0     | 0      | 1     | (1) |

| (3) | 0     | 1     | 1     | 0     | 1      | 1     | (3) |

| (4) | 1     | 0     | 0     | 0     | 1      | 0     | (2) |

| (5) | 1     | 0     | 1     | 1     | 0      | 1     | (5) |