## Pedro Miguel Ribeiro Machado

Sonar Ultrassónico para cegos com Sonificação de obstáculos

Ultrasonic Sonar for the Visually Impaired with Obstacles Sonification

"Homem culto é aquele que, de tudo a que assiste aumenta, não os seus conhecimentos, mas o seu estado de alma."

— Fernando Pessoa

## Pedro Miguel Ribeiro Machado

Sonar Ultrassónico para cegos com Sonificação de obstáculos

Ultrasonic Sonar for the Visually Impaired with Obstacles Sonification

Dissertação apresentada à Universidade de Aveiro para cumprimento dos requesitos necessários à obtenção do grau de Mestre em Engenharia Eletrónica e Telecomunicações, realizada sob a orientação científica do Professor Doutor José Neto Vieira e coorientação do Professor Doutor Arnaldo Oliveira, Professores Auxiliares do Departamento de Eletrónica, Telecomunicações e Informática da Universidade de Aveiro.

To my father, thanks to whom I feel (and know) I will never walk alone.

#### o júri / the jury

presidente / president Professor Doutor José Maria Amaral Fernandes

Professor Auxiliar da Universidade de Aveiro (por delegação da Reitora da Univer-

sidade de Aveiro)

vogais / examiners committee Professor Doutor José Manuel Neto Vieira

Professor Auxiliar da Universidade de Aveiro (orientador)

Professor Doutor Diamantino Rui da Silva Freitas

Professor Associado da Faculdade de Engenharia da Universidade do Porto

# agradecimentos / acknowledgements

Gostaria de iniciar este pequeno trecho de texto por deixar expresso o meu agradecimento aos Professores Doutor José Vieira e Doutor Arnaldo Oliveira, orientador e coorientador, respetivamente, não só pela valiosa oportunidade que me concederam de realizar este trabalho, mas também por toda a orientação científica e prática ao longo destes meses, bem como pelo esforço empregue na transmissão de seus conhecimentos e experiência, que se revelaram imprescindíveis no decorrer do projeto.

A nível académico, devo deixar também um agradecimento a todos os meus colegas com os quais, ao longo do curso, eu trabalhei, discuti, errei, partilhei frustrações, desesperei e, como consequência, aprendi, ganhei conhecimento e experência que me ajudaram ao longo destes meses.

Gostaria de agradecer também ao Eduardo Miranda, à Catarina Santa Comba e ao Daniel Almeida, meus colegas de laboratório destes últimos tempos, não só pela ajuda disponibilizada, mas também pelas ocasionais gargalhadas que permitiram os instantâneos alívio e descompressão do estado de espírito, fundamentais para a melhoria da minha produtividade e bem-estar.

Não poderei esquecer-me de todas as pessoas que contribuíram para a formação do meu Ser, nomeadamente família e amigos mais íntimos. Todas as características do meu carácter foram moldadas pelas experiências e vivências, sejam elas boas ou más, que partilhei com as mesmas. Destas deverei destacar a minha Mãe, cuja resiliência e capacidade de luta me permitiram ter a oportunidade de elaborar este documento.

Por fim, e não menos importante (de todo), quero deixar um especial agradecimento à minha namorada Susana, não só pelo incondicional apoio que me porporcionou, mas também pela inabalável fonte de motivação que revelou ser para mim durante a elaboração desta Dissertação.

#### Resumo

Nesta tese de mestrado pretende-se desenvolver um dispositivo portátil que possa ser usado por pessoas com deficiência visual na ecolocalização de obstáculos. Este dispositivo deverá ser dotado de capacidade de emissão e deteção de ultrassons para funcionar como um sonar e permitir ainda o seu funcionamento como altifalante paramétrico capaz de realizar a sonificação dos obstáculos. Para tal, foi necessário desenvolver uma ADC Sigma-Delta em FPGA que permita uma alta densidade na aquisição independente de um grande número de canais num dispositivo de pequenas dimensões. Os testes realizados com a ADC Sigma-Delta revelaram uma baixa distorção e uma boa relação sinal ruído, comparáveis às ADCs do mesmo tipo existentes no mercado. Está assim preparado o caminho para a construção do dispositivo.

#### **Abstract**

In this master's thesis it is intended to develop a portable device that can be used by people with visual impairment in the echolocation of obstacles. This device must be capable of transmitting and detecting ultrasound signals to work as a sonar and still allow its operation as a parametric speaker capable of performing the sonification of obstacles. To do this, it was necessary to develop a Sigma-Delta ADC in FPGA that allows a high density in the independent acquisition of a large number of channels in a small device. Tests performed with the developed Sigma-Delta ADC revealed low distortion and good signal-to-noise ratio, comparable to same type ADCs available on the market. The path for the construction of the device is, then, open.

# Contents

| C  | Contents |                                      |    |  |

|----|----------|--------------------------------------|----|--|

| Li | st of    | Figures                              | v  |  |

| Li | st of    | Tables                               | ix |  |

| Li | st of    | Acronyms                             | x  |  |

| 1  | Intr     | roduction                            | 1  |  |

|    | 1.1      | Motivation                           | 1  |  |

|    | 1.2      | Proposed Work and Objectives         | 2  |  |

|    | 1.3      | Organisation                         | 5  |  |

| 2  | Sta      | te of the Art                        | 5  |  |

|    | 2.1      | Blindness and vision impairment      | Ę  |  |

|    |          | Mobility and Environment Sensing     | F  |  |

|    |          | Hearing and Echolocation             | 7  |  |

|    | 2.2      | Assisting Devices                    | 7  |  |

|    |          | Cane equipped with sonar             |    |  |

|    |          | Sunglasses with Sonar                |    |  |

|    |          | NAVIG                                |    |  |

|    | 2.3      | Parametric Speaker                   | ξ  |  |

| 3  | Sign     | ma-Delta Converter                   | 11 |  |

|    | 3.1      | Introduction                         | 11 |  |

|    |          | 3.1.1 Sampling Methods               | 11 |  |

|    |          | 3.1.2 Quantization noise             | 12 |  |

|    |          | 3.1.3 Performance                    | 13 |  |

|    |          | Signal-to-Noise Ratio                | 13 |  |

|    |          | Signal-to-Noise and Distortion Ratio | 13 |  |

|    |          | Spurious-free Dynamic Range          |    |  |

|    |          | Total Harmonic Distortion            | 14 |  |

|    |          | Resolution                           |    |  |

|    |          | 3.1.4 Delta Modulation               |    |  |

|    |          | 3.1.5 Sigma-Delta Modulation         | 17 |  |

|    |          | First Order                          | 17 |  |

|    |          | High-Order Sigma-Delta               | 18 |  |

|   | 3.2 | Design of the Modulator                                         |

|---|-----|-----------------------------------------------------------------|

|   | 3.3 | Implementation of the Sigma-Delta Modulator $(\Sigma \Delta M)$ |

|   |     | 3.3.1 Digital Interface                                         |

|   |     | Input Differential Buffer                                       |

|   |     | Sampling                                                        |

|   |     | Output buffer                                                   |

|   |     | 3.3.2 Analog interface                                          |

|   | 3.4 | Tests and Results                                               |

|   |     | 3.4.1 Experimental Set-up                                       |

|   |     | 3.4.2 Results                                                   |

|   |     | Output Power Spectrum Density                                   |

|   |     | Performance Indicators                                          |

|   | 3.5 | Results Analysis and Discussion                                 |

|   |     | ·                                                               |

| 4 | Bea | mforming 35                                                     |

|   | 4.1 | Introduction                                                    |

|   |     | 4.1.1 Uniform Linear Array                                      |

|   |     | 4.1.2 Planar Array                                              |

|   | 4.2 | Analog Reception, Digital Down Conversion and Processing        |

|   |     | 4.2.1 Analog Reception                                          |

|   |     | 4.2.2 Coherent Detection/Downconversion                         |

|   |     | 4.2.3 Quadrature Amplitude Modulated Signals                    |

|   |     | 4.2.4 Downconverter mixer                                       |

|   |     | Moving Average Filter                                           |

|   |     | Oscillator                                                      |

|   |     | Final Downsampling                                              |

|   |     | Receiver Channel                                                |

|   | 4.3 | Implementation                                                  |

|   |     | 4.3.1 Analog Reception                                          |

|   |     | 4.3.2 Digital Downconversion                                    |

|   |     | CIC Filter                                                      |

|   |     | Local Oscillator                                                |

|   |     | Mixer                                                           |

|   |     | Frequency Shift                                                 |

|   |     | Low Pass Filter                                                 |

|   |     | Trigger Generator                                               |

|   | 4.4 | Tests and Results                                               |

|   |     | 4.4.1 Analog Reception                                          |

|   |     | 4.4.2 Digital Downconversion                                    |

|   |     | CIC Filter                                                      |

|   |     | Downconversion followed by low-pass-filtering                   |

|   | 4 - | Downconverter                                                   |

|   | 4.5 | Results Analysis and Discussion                                 |

|   |     | 4.5.1 Analog Reception                                          |

|   |     | 4.5.2 Digital Downconversion                                    |

|   |     | CIC Filter                                                      |

|              |                | Downconverter                                                     | 3  |

|--------------|----------------|-------------------------------------------------------------------|----|

| 5            | Con            | aclusions 6                                                       | 5  |

|              | 5.1            | Conclusions                                                       | 5  |

|              | 5.2            | Future Work                                                       | 5  |

| Al           | PPE            | NDICES 6                                                          | 7  |

| $\mathbf{A}$ | Per            | formance Indicators 6                                             | 7  |

|              | A.1            | Introduction                                                      | 7  |

|              |                | A.1.1 Discrete-time Random Processes                              | 7  |

|              |                | Stationarity                                                      | 8  |

|              |                | Ergodicity                                                        | 8  |

|              |                | A.1.2 The Power Spectrum                                          |    |

|              |                | A.1.3 Welch's Method of Power Spectral Density (PSD) Estimation 6 |    |

|              | A.2            | Spectral Analysis of the Output of the $\Sigma\Delta M$           |    |

|              |                | Performance Indicators Computation                                |    |

|              | 11.0           | A.3.1 Signal-to-Noise-Ratio                                       |    |

|              |                | A.3.2 Signal-to-Noise and Distortion Ratio                        |    |

|              |                | A.3.3 Spurious Free Dynamic Range                                 |    |

|              |                | A.3.4 Total Harmonic Distortion                                   |    |

|              | A 4            | Validation                                                        |    |

| _            |                |                                                                   |    |

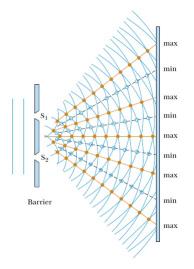

| В            |                | erference of Ultrasonic Waves 8                                   |    |

|              | В.1            | Introduction                                                      |    |

|              |                | B.1.1 Double-Slit Experiment                                      |    |

|              |                | B.1.2 Lloyd's Mirror                                              |    |

|              | B.2            | Experimental Verification                                         | ,4 |

| $\mathbf{C}$ | $\Sigma\Delta$ | Modulator – VHDL implementation 8                                 | 7  |

|              | C.1            | Top-level file                                                    | 7  |

|              | C.2            | Sampling                                                          | 8  |

|              |                | C.2.1 D-type Flip-flop                                            | 8  |

|              |                | C.2.2 Frequency Division                                          | 9  |

|              | C.3            | Shift-Register                                                    | 0  |

|              | C.4            | Constraint File                                                   | 1  |

| D            | Dov            | vnconverter - VHDL Implementation 9                               | 3  |

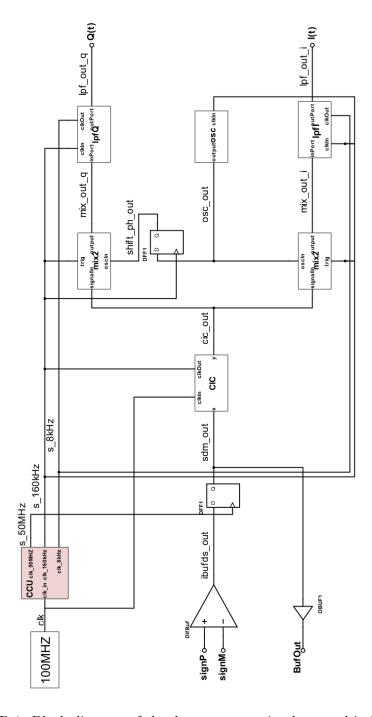

|              | D.1            | Top-Level File                                                    | 3  |

|              | D.2            | Trigger Generator                                                 | 6  |

|              | D.3            | 1 bit D Flip-Flop                                                 | 8  |

|              | D.4            | CIC Filter                                                        | 9  |

|              | D.5            | Oscillator                                                        |    |

|              | D.6            | Mixer                                                             |    |

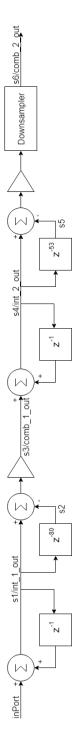

|              | D.7            | Low-Pass Filter with Downsampling                                 |    |

|              | D.8            | Delay Block                                                       |    |

|              | D.9            | 23 bits D Flip-Flop                                               |    |

|              | _              | 0.16 bits D Flip-Flop                                             |    |

| D.11 Constraint File                    | 105 |

|-----------------------------------------|-----|

| D.12 Block Diagrams                     | 107 |

| D.12.1 Downconverter - Top-level file   | 107 |

| D.12.2 CIC filter                       | 108 |

| D.12.3 Low-pass Filter with Downsampler | 109 |

| Bibliography                            | 111 |

# List of Figures

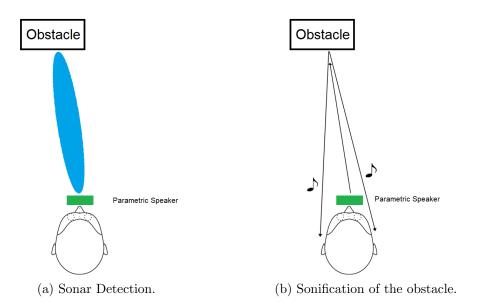

| 1.1  | Basic graphic description of the system's operation where both detection and warning modes are depicted |

|------|---------------------------------------------------------------------------------------------------------|

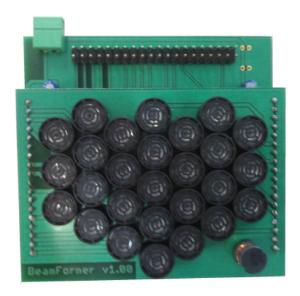

| 1.2  | Parametric Speaker developed by [2]                                                                     |

| 2.1  | Traditional cane that facilitates blind people mobility [5]                                             |

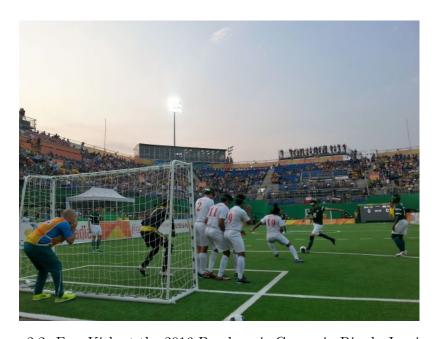

| 2.2  | Free Kick at the 2016 Paralympic Games in Rio de Janeiro [7]                                            |

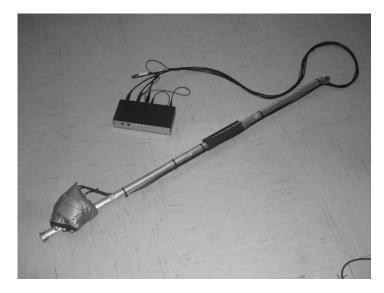

| 2.3  | Prototype of the Cane Equipped with Sonar [12]                                                          |

| 2.4  | Prototype of the Sunglasses Equipped with Sonar                                                         |

| 2.5  | Prototype of the NAVIG system [13]                                                                      |

| 2.6  | Sennheiser's Audiobeam Parametric Speaker                                                               |

| 2.7  | Sound pressure distribution in a plane for a centered beam [2]                                          |

| 3.1  | Aliasing Effect                                                                                         |

| 3.2  | PSD of a sinusoidal signal with noise and harmonic components                                           |

| 3.3  | Delta Modulator block diagram                                                                           |

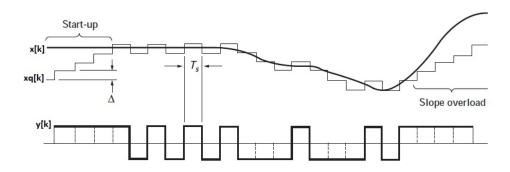

| 3.4  | Delta Modulator's signals [20]                                                                          |

| 3.5  | Delta Modulator followed by its demodulator                                                             |

| 3.6  | Delta Modulator's linear model                                                                          |

| 3.7  | Sigma-Delta Modulator                                                                                   |

| 3.8  | Simplified Sigma-Delta Modulator                                                                        |

| 3.9  | The Sigma-Delta Modulator linear model                                                                  |

| 3.10 | Two Different High-order Sigma Delta Modulators                                                         |

| 3.11 | Linear model of a $2^{\rm nd}$ order $\Sigma\Delta M$                                                   |

| 3.12 | Noise Shaping for different orders $\Sigma\Delta M$ , a Nyquist sampling ADC and a simple               |

|      | oversampling ADC[16]                                                                                    |

| 3.13 | Simulink topology of the designed $\Sigma\Delta M$                                                      |

| 3.14 | Bitstream modulation and noise shaping characteristic for a 40 kHz input sine                           |

|      | wave and 10 MHz sampling frequency                                                                      |

| 3.15 | Simulated performance indicators for different input frequencies                                        |

| 3.16 | Designed $\Sigma\Delta M$                                                                               |

| 3.17 | RC integrator and low-pass filter                                                                       |

| 3.18 | Audio Precision Portable One Plus audio test set                                                        |

| 3.19 | Signal conditioning circuit for offset addition                                                         |

| 3.20 | Calibratable offset signal conditioning circuit                                                         |

| 3.21 | $\Sigma\Delta M$ , with the calibratable signal conditioning circuit, DC supply LPF filter,             |

|      | integrators and digital interface                                                                       |

| 3.22 | PMOD input ports front view on the Nexys 4 board [22]                                                                                                                                                           | 29 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

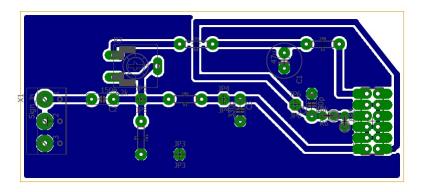

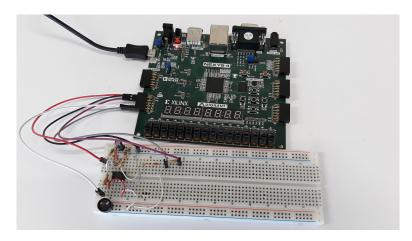

| 3.23 | Board layout of the circuit used to take measurements to the $\Sigma\Delta M$                                                                                                                                   | 30 |

| 3.24 | Experimental set-up for measuring the $\Sigma\Delta M$ performance                                                                                                                                              | 30 |

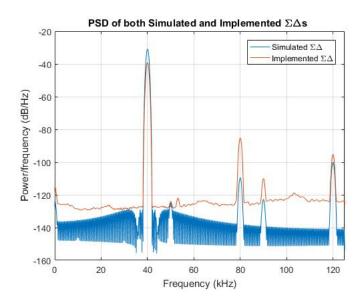

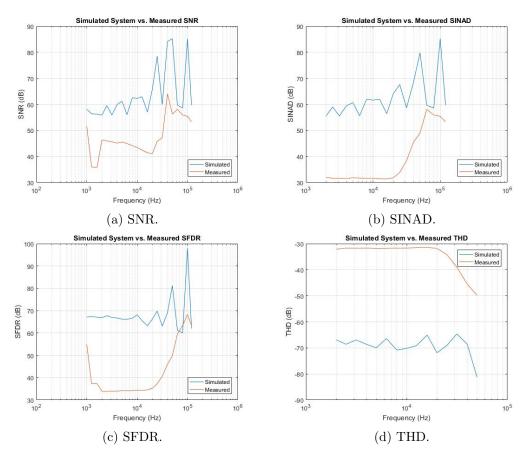

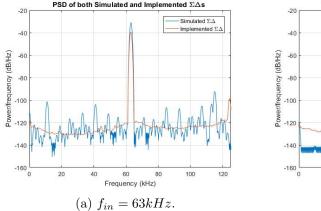

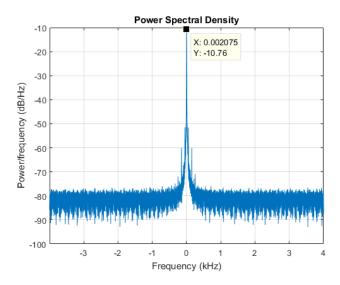

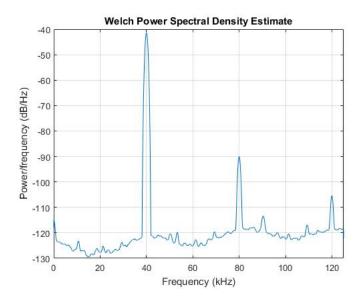

| 3.25 | Estimated PSD for both the hardware implemented and simulated $\Sigma\Delta Ms$ , when $f_{in}=40kHz$                                                                                                           | 31 |

| 3.26 | Measured performance indexes for both hardware implemented and simulated $\Sigma \Delta Ms.$                                                                                                                    | 32 |

| 3.27 | Unpredictable behaviour of the simulated $\Sigma\Delta M$ outside the signal and harmonics band for some input frequencies                                                                                      | 33 |

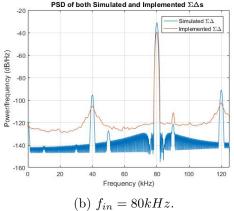

| 4.1  | Uniform Linear Array configuration [26]                                                                                                                                                                         | 35 |

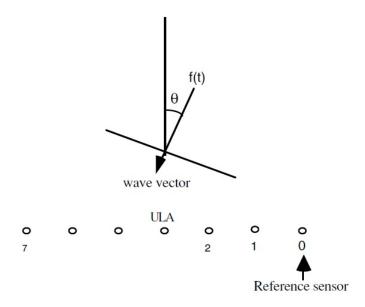

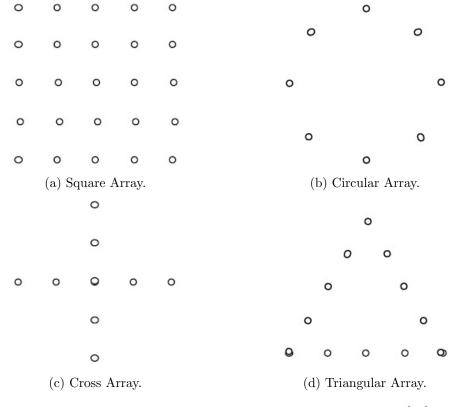

| 4.2  | Some different geometries for the Planar Array [26]                                                                                                                                                             | 37 |

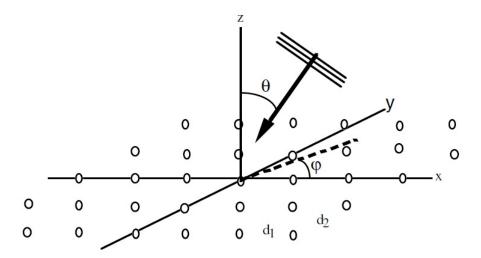

| 4.3  | Azimuth $(\varphi)$ and Elevation $(\Theta)$ Estimation in a Planar Array [26]                                                                                                                                  | 38 |

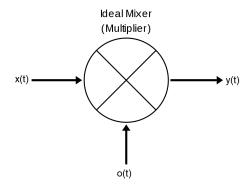

| 4.4  | Block diagram of a mixer [28]                                                                                                                                                                                   | 39 |

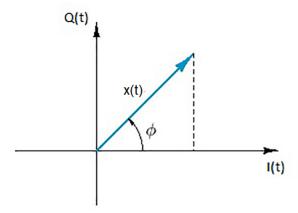

| 4.5  | Representation of the passband in the form of a phasor dependent on its In-                                                                                                                                     |    |

|      | phase and Quadrature components                                                                                                                                                                                 | 41 |

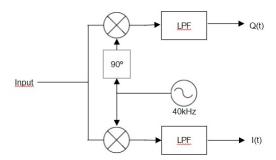

| 4.6  | Basic downconverter                                                                                                                                                                                             | 41 |

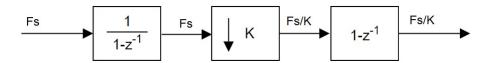

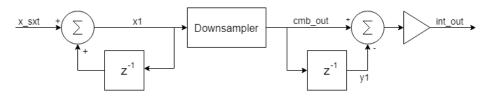

| 4.7  | Block diagram of the One-Stage Recursive Moving Average Filtering Process.                                                                                                                                      | 43 |

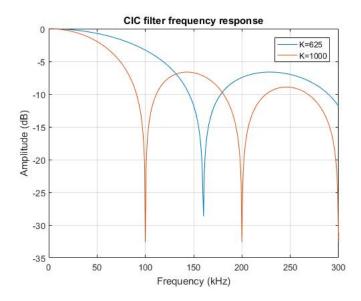

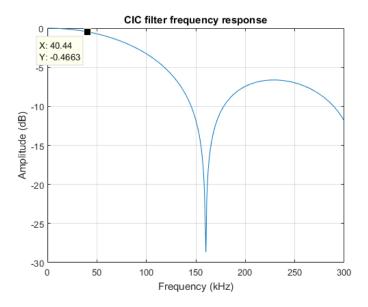

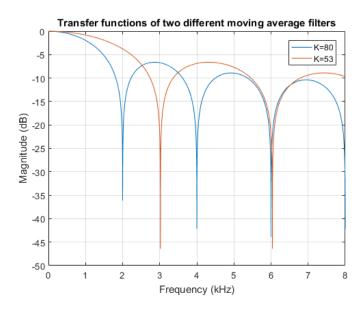

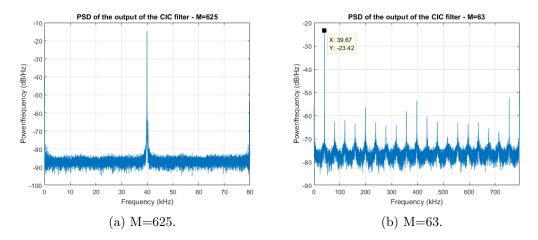

| 4.8  | CIC Filter Frequency Response for two different values of $K$                                                                                                                                                   | 44 |

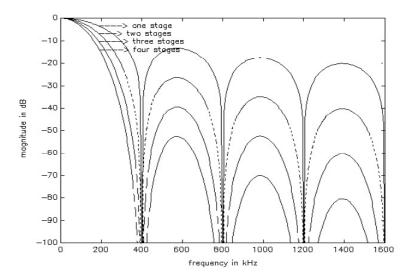

| 4.9  | N-stage CIC Filter frequency response for different values of $N$ [16]                                                                                                                                          | 45 |

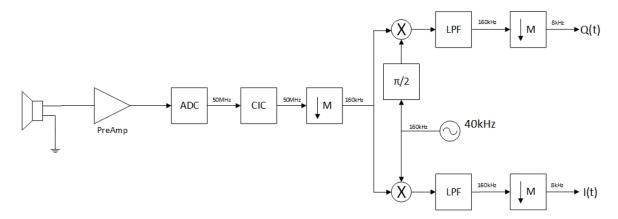

| 4.10 | Theoretical version of each receiving channel of the Planar Array                                                                                                                                               | 45 |

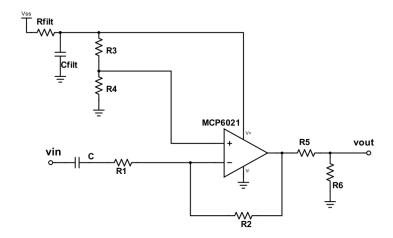

| 4.11 | Designed Preamplifier for each reception channel                                                                                                                                                                | 46 |

| 4.12 | Computed Transfer Function of the Filter                                                                                                                                                                        | 48 |

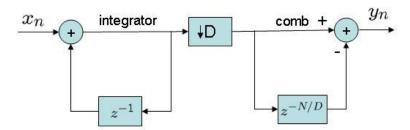

| 4.13 | Efficient Implementation of a CIC Filter [30]                                                                                                                                                                   | 48 |

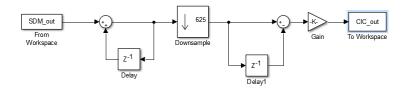

|      | CIC Filter Block Diagram in Simulink                                                                                                                                                                            | 48 |

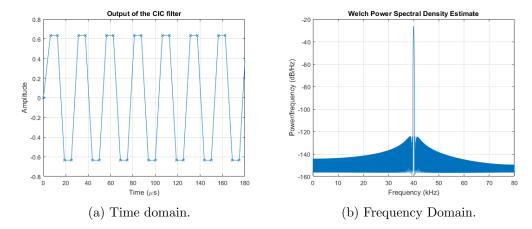

| 4.15 | Output Signal of the CIC Filter                                                                                                                                                                                 | 49 |

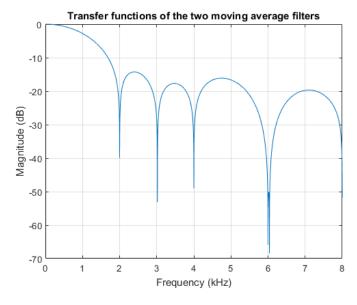

|      | Frequency Responses of Both Moving Average Filters of the LPF                                                                                                                                                   | 51 |

| 4.17 | Frequency Response of LPF Composed by the Two Cascaded Moving Average                                                                                                                                           |    |

|      | Filters                                                                                                                                                                                                         | 51 |

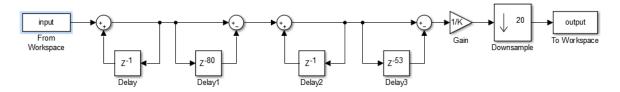

|      | LPF implemented in Simulink.                                                                                                                                                                                    | 52 |

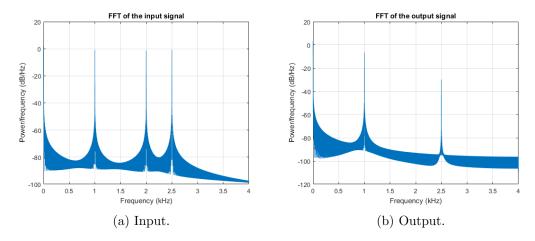

|      | FFT of the input and output signals of the LPF                                                                                                                                                                  | 52 |

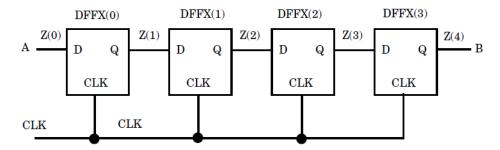

|      | Delay Block implemented as a FIFO Shift Register [31]                                                                                                                                                           | 53 |

|      | Receptor Implemented in a Breadboard                                                                                                                                                                            | 54 |

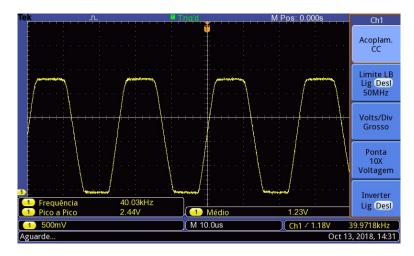

|      | Measured saturation on the output of the Preamplifier                                                                                                                                                           | 54 |

| 4.23 | Experimental setup for the measurement of the received signal strength as a function of distance; the emitter is on the left side, laying against the function generator, and the receptor is on the right side | 55 |

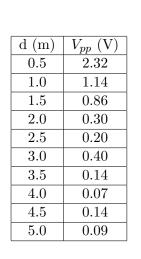

| 4.24 | Peak-to-peak voltage at the output of the Preamplifier as a function of distance.                                                                                                                               | 55 |

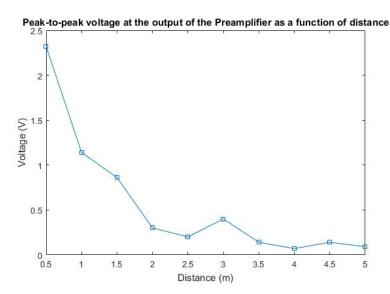

| 4.25 | PSD of the output of the $\Sigma\Delta M$ when its input signal is a preamplified signal with the source at a distance of 5m                                                                                    | 56 |

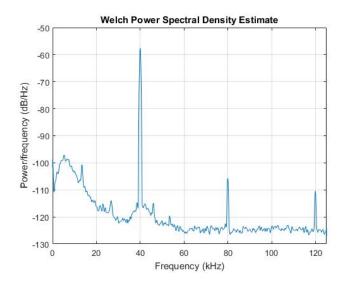

| 4.26 | Signals recorded at the output of the CIC filter                                                                                                                                                                | 56 |

|      | PSD of the signals recorded at the output of the CIC filter                                                                                                                                                     | 57 |

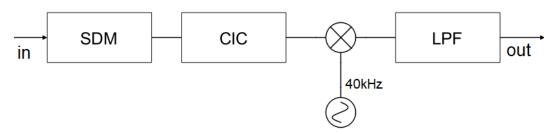

|      | Experiment to test the LPF proper operation                                                                                                                                                                     | 57 |

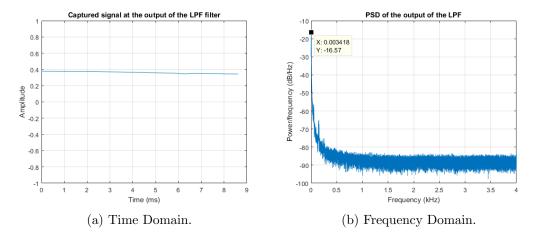

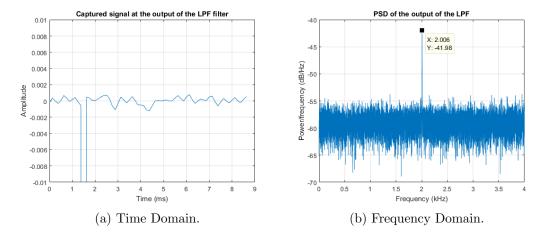

|      | Output signal of the LPF when at input is a sine wave of frequency 40kHz                                                                                                                                        | 58 |

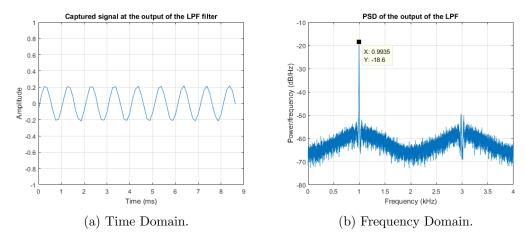

|      | Output signal of the LPF when at input is a sine wave of frequency 41kHz                                                                                                                                        | 58 |

|      | Output signal of the LPF when at input is a sine wave of frequency 42kHz                                                                                                                                        | 58 |

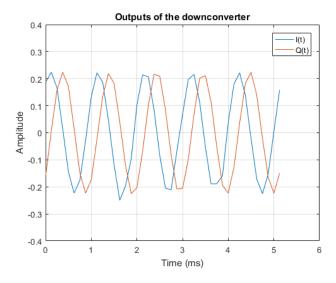

| 4.32 | Recorded $In-Phase - I(t)$ - and $Quadrature - Q(t)$ - signals for an input sine      |     |

|------|---------------------------------------------------------------------------------------|-----|

|      | wave of 41kHz                                                                         | 59  |

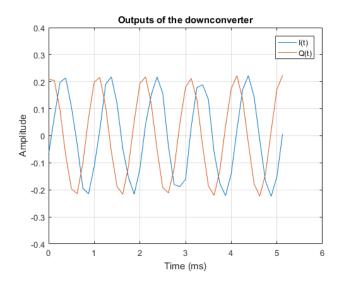

| 4.33 | Recorded $In$ -Phase - $I(t)$ - and $Quadrature$ - $Q(t)$ - signals for an input sine |     |

|      | wave of 39kHz                                                                         | 60  |

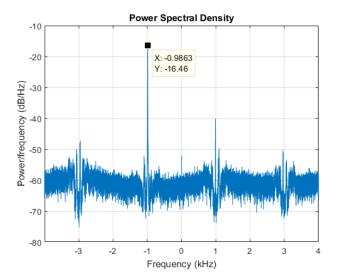

| 4.34 | PSD of the downconverted signal when the input is a 39kHz sine wave                   | 60  |

| 4.35 | PSD of the downconverted signal when the input is a 40kHz sine wave                   | 61  |

| 4.36 | PSD of the downconverted signal when the input is a 41kHz sine wave                   | 61  |

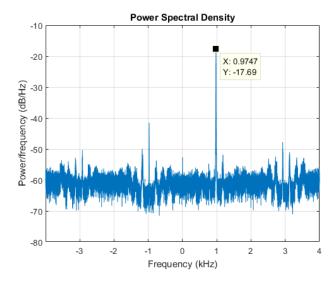

| A.1  | Estimated PSD of the same signal, with different segment sizes                        | 69  |

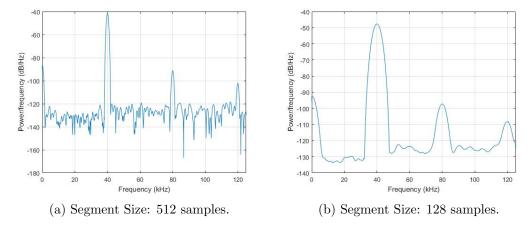

| A.2  | Different 64 sample length Windows Frequency Response                                 | 70  |

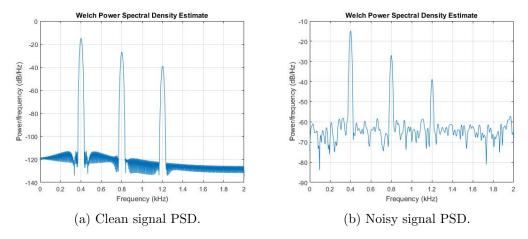

| A.3  | Estimated PSD for a 40 kHz input sine wave                                            | 71  |

| A.4  | Power spectra of the generated signals                                                | 77  |

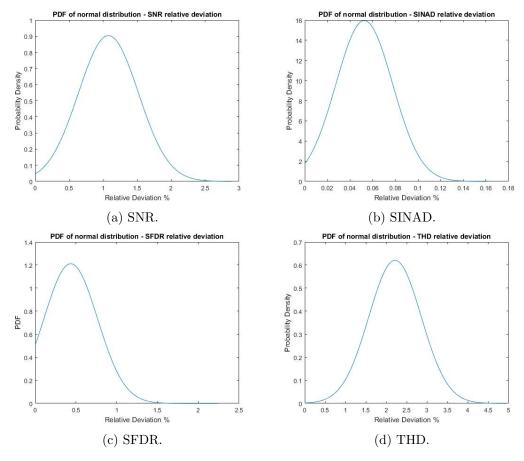

| A.5  | Normal Distribution PDF's                                                             | 78  |

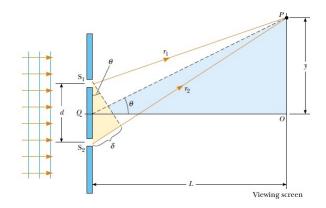

| B.1  | Thomas Young's Double-slit Experiment[36]                                             | 82  |

| B.2  | Geometric reference for the Double-Slit Experiment Analysis[36]                       | 82  |

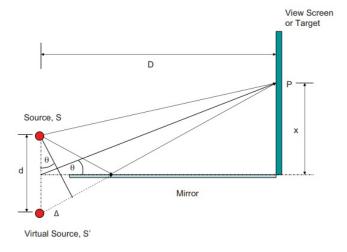

| B.3  | Visualisation of the Lloyd's Mirror phenomenon[37]                                    | 83  |

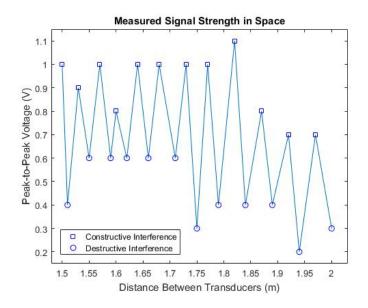

| B.4  | Results from the Interference Measurement Experience                                  | 86  |

| D.1  | Block diagram of the downconverter implemented in VHDL                                | 107 |

| D.2  | Block diagram of the CIC filter implemented in VHDL                                   | 108 |

| D.3  | Block diagram of the LPF filter implemented in VHDL                                   | 109 |

# List of Tables

| 3.1 | Performance indicators computed in the simulation for different sampling frequencies, with input frequency of 40 kHz.                       | 22 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Performance indicators measured with 50 MHz of sampling frequency and 40kHz of input frequency                                              | 33 |

| 4.1 | PSD peaks for every input sine wave                                                                                                         | 59 |

|     | Computed and estimated through Welch's Method Performance Indicators of the MATLAB generated signal                                         | 78 |

| A.2 | Parameters of the normal distributions (Mean - $\mu$ - and Standard Deviation - $\sigma$ ) and extremes of the measured relative deviations | 79 |

| B.1 | Some Constructive and Destructive points in space computed in MATLAB                                                                        | 85 |

# List of Acronyms

$\Sigma \Delta \mathbf{M}$  Sigma-Delta Modulator.

**ADC** Analog-to-Digital Converter.

**BRAM** Block Random-Access Memory.

CIC Cascaded Comb-Integrator.

dB Decibel.

**DM** Delta Modulator.

**DoA** Direction of Arrival.

**DTFT** Discrete-time Fourier Transform.

**ENOB** Effective Number of Bits.

**FFT** Fast Fourier Transform.

**FIFO** First in, First out.

FPGA Field-Programmable Gate Array.

**GBDP** Gain-Bandwidth Product.

**GIS** Geographic Information System.

**GPS** Global Positioning System.

**HPF** High-Pass Filter.

**HW** Harware.

**IBSF** International Blind Sports Federation.

ILA Integrated Logic Analyser.

LPF Low-Pass Filter.

LSB Least Significant Bit.

LVDS Low Voltage Differential Signalling.

MSB Most Significant Bits.

NS Noise Shaping.

**NTF** Noise Transfer Function.

**OPAMP** Operational Amplifier.

PCB Printed Circuit Board.

**PDF** Probability Density Function.

**PMOD** Peripheral Module.

**PSD** Power Spectral Density.

PWM Pulse-Width Modulation.

**RF** Radio-Frequency.

**RMS** Root Mean Square.

**SFDR** Spurious Free Dynamic Range.

**SINAD** Signal-to-Noise and Distortion Ratio.

**SNR** Signal-to-Noise Ratio.

**STF** Signal Transfer Function.

**THD** Total Harmonic Distortion.

**ULA** Uniform Linear Array.

**UPA** Uniform Planar Array.

VHDL VHSIC Hardware Description Language.

VHSIC Very High Speed Integrated Circuit.

WHO World Health Organisation.

**ZOH** Zero-Order Hold.

# Chapter 1

# Introduction

#### 1.1 Motivation

Blindness and visual impairment are disabilities that greatly increase the hazard of accidents that might often result in injury and/or damage. The interaction of a person with the surroundings involves the use of all senses in order to avoid dangerous incidents and vision is, if not the most, one of the most important senses. Due to this fact, the independence of a blind person is greatly affected.

Blind people often adapt to the disability and end up relying on other senses, being one of them hearing. However, the sole reliance on this sense does not replace the safety that vision bestows upon sighted people.

One important characteristic of hearing is echolocation, that is the ability to detect an object at a distance and its relative position by sensing echoes. This sense is not quite developed in humans. However, some outstanding cases of blind people have been reported where they are able to safely navigate in the surroundings, successfully identifying objects by sensing the echo of sounds such as mouth-clicks, mainly in cases of people that were born blind or developed the disability in very early stages of their infant life, such as the case of Daniel Kish[1].

That said, it is apparent that a person that develops this disability at a more advanced age very seldom will develop the ability of echolocation.

Nowadays, it is relatively easy to identify electronically the direction of arrival of an echo. This means that identifying the relative position of an object by sensing an echo can be made with accuracy much superior to that of the untrained human hear. The technique that achieves this is called *beamforming* and allows to both direct a beam of ultrasonic or even Radio-Frequency (RF) waves as well as identify the Direction of Arrival (DoA) of the same carrier coming from a source with some relative position.

Using a parametric speaker, both can be done and, thus, achieve a system that can identify the location of an obstacle as well as direct a beam of ultrasonic waves towards it, that will reflect on the object and *sonify* it, where it creates the semblance of being the obstacle the sound source.

Such a system might be important in the adaptation of visually impaired people that developed the ailment at a more advanced stage of life, when their echolocation sense is underdeveloped and, thus, are not able to distinguish an echo coming from an obstacle from the remaining echoes from the harmless surroundings.

### 1.2 Proposed Work and Objectives

It is intended to develop a portable sonar with *parametric speaker* that aids blind people to detect obstacles.

An ultrasound emitter should emit ultrasonic pulses that radiate in a wide field, in order to detect as much obstacles as possible with the echoes, whose DoA will be determined by the sonar. However, only in very specific situations should danger be encountered and that is when an obstacle is radially approaching the carrier of the system. In that case, due to the *Doppler Effect*, the received echoes will present a slightly different and greater frequency, because of a positive relative velocity. This frequency shift is the condition to look for in order to activate the warning mode. In this mode, a *Parametric Speaker* will direct towards the obstacle a beam of ultrasonic wave modulating an audible warning signal that will demodulate due to non-linear effects of its interaction with the air. This way, it creates the illusion that the obstacle is emitting an audible signal, easing its detection.

Figure 1.1 depicts the basic operation of the system.

Figure 1.1: Basic graphic description of the system's operation where both detection and warning modes are depicted.

The *Parametric Speaker* that is shown in Figure 1.2 has been previously designed and implemented to perform this function [2], as well as the software to direct the beam using the *beamforming* technique. The proposed work is to complement it with a sonar (that is a phased array of ultrasound transducers) capable of receiving the said echoes, compute the DoA and detect the risk of collision with an obstacle.

The following tasks should be completed:

Figure 1.2: Parametric Speaker developed by [2].

Analog-to-Digital Converter Estimating the DoA involves digital signal processing techniques and, thus, the received echos must be sensed and sampled in order to perform such task. The main objective in this task is to develop an Analog-to-Digital Converter (ADC) that is as compact as possible, with the least hardware complexity that is possible to attain without compromising good performance.

**Downconversion** For each received echo, it is needed to evaluate the frequency, phase and amplitude of the received signal. In the downconversion process, where *In-Phase* and *Quadrature* components of the received signal are extracted, allow to compute the phase of the received signal, as well as its amplitude.

**Beamformer** From the data extracted from several downconverted received signals (from each transducer of the array), it is possible to determine the DoA of the echo. This computation is done by the beamformer.

### 1.3 Organisation

This document is divided in five chapters, which are briefly described here.

- **Chapter 1** A small introduction on the motives, objectives and organisation of this Thesis is done.

- Chapter 2 A brief description of the state-of-the-art on the subject. What is known about blindness and echo location and some recent electronic aids.

- Chapter 3 Some theory is introduced on the operation of a  $\Sigma\Delta M$ . The design and implementation of a  $\Sigma\Delta M$  is described, as well as the tests made. The results are presented and analysed.

- **Chapter 4** The theory of DoA is presented. A reception channel is designed, implemented, subjected to testing. The results are presented and discussed.

- **Chapter 5** Conclusion of the thesis and discussion of the objectives accomplished. Future work is also discussed.

# Chapter 2

## State of the Art

### 2.1 Blindness and vision impairment

Vision impairment "refers to deficits in the ability of the person to perform vision-related activities of daily living, such as: reading, orientation and mobility, and other tasks" [3].

Vision impairment, is classified having in mind the degree of difficulty the impairment brings in the near and far fields of vision [4]. At a distance, the degrees of impairment are:

- Mild

- Moderate

- Severe

- Blindness

Thus, blindness is the most severe form of vision impairment, where the sense of vision is diminished to none or close to it.

World Health Organisation (WHO) estimates that nearly 1.3 billion people in the world suffer from some kind of vision impairment, 36 million of which suffer from blindness [4].

It is also expected that the risk of more people being affected by some sort of vision impairment increases in the near future due to population increase and ageing.

#### Mobility and Environment Sensing

Mobility is the ability to move freely and easily between different locations in space. It is safely done with a good interaction with the environment and such requires a precise sensing of all the elements in the surrounding space.

The main challenge of people with severe vision impairment is the safe interaction with their surroundings, due to the fact that vision is the most important sense that facilitates this. Reliability on other senses is the key to a healthy interaction with the physical environment.

Nowadays, mobility for blind people is mainly possible due to the use of the traditional cane, depicted in Figure 2.1.

The cane allows a person with visual disabilities to detect obstacles that might present themselves at the ground level, like stairs or even posts. The sense that is most used with the cane is touch, because an obstacle is detected when the cane hits is and, thus, vibrates.

Figure 2.1: Traditional cane that facilitates blind people mobility [5].

Other good example on how blind people rely on other senses is Blind Football, that is currently regulated by International Blind Sports Federation (IBSF). The pitch must be uncovered to allow optimum acoustics; the ball has a sound system inside that makes a jiggling or rattling sound whenever it moves, so that players can better locate it; the field has kickboards that run along the side lines in order to be physically sensed; and there are specific areas for the presence of a guide that verbally guides the players [6]. Figure 2.2 depicts a Free Kick during a Blind Football match. Notice the kickboard parallel to the sideline on the left and the guide standing behind the goal, guiding the striking team.

Figure 2.2: Free Kick at the 2016 Paralympic Games in Rio de Janeiro [7].

#### **Hearing and Echolocation**

Hearing is the capability of perceiving sounds. Blind people, not being able to see, usually end up relying to a greater extent on their hearing capabilities when comparing to non visually impaired people. In fact, neuroimaging studies have suggested that the brains of early-blind people suffer structural changes due to this fact [8].

Echolocation is the ability to detect obstacles in the environment by sensing an echo. Bats are known to move in space through such sensing. Some dolphin species navigate in murky waters in the same way.

Humans are not so sensitive to these stimuli. However, a small number of blind people was reported to have outstandingly applied echolocation to interact with the surroundings, through the emission of sound signals such as mouth-clicks [9]. In fact, Bo N. Schenkman and Mats E. Nilsson [10] showed that both blind and sighted people can effectively locate obstacles at a near distance (less than 2 m), although blind people scored better, and that outstanding echolocators' performance was superior as well for greater distances.

Lore Thaler *et al.*, studied this sense in expert echolocators with neuroimaging scans and the findings suggest that the processing of the mouth-click echoes in the brain is similar to that of vision in sighted people [11], adding evidence that states that blind brains adapt to the lack of vision with other senses to increase capability of obstacles detection and navigation.

### 2.2 Assisting Devices

Besides the traditional cane shown in Figure 2.1, other kind of devices, technically more advanced, have been emerging recently. Some examples will be discussed in this section.

#### Cane equipped with sonar

The traditional cane most blind people use allows one to sense a surface with its tip. As a blind person moves in space and scans the surface with the tip of the cane with a circular motion, a lot of area is left unprobed. This flaw leads to the danger of not detecting small holes on the ground, and so the carrier of the cane might step on it and fall.

This cane, depicted in Figure 2.3, developed at University of Aveiro, is equipped with a sonar probe in the middle of its length and detects holes in areas not probed with the tip of the cane in an effort to complement the traditional white cane's features. It then warns the carrier of the hole existence through a vibration.

However, the major disadvantages it presents have to do with portability, given the fact that it is relatively heavy and it does not detect obstacles at levels higher than the ground.

#### Sunglasses with Sonar

This device, also developed at the University of Aveiro, consists on sunglasses that are equipped with sonar detection. Its main feature is to detect obstacles at head level and the system is shown in Figure 2.4.

The glasses are equipped with two ultrasonic emitters that generate ultrasound pulses and one receiver that receives the echoes. Whenever it detects an obstacle at head level approaching it will send a sound warning to the carrier.

Figure 2.3: Prototype of the Cane Equipped with Sonar [12].

Figure 2.4: Prototype of the Sunglasses Equipped with Sonar.

The main disadvantage is that the equipment has no speaker and, thus, the sound warning is sent to headphones. This way, whenever an obstacle is detected, the blind carrier will momentarily lose his ability to listen to other ambient noises in order to focus on the warning signal. Most blind people are not comfortable with this trade-off.

#### **NAVIG**

This device is intended to help visually impaired people avoid obstacles, while mapping the carrier's location using Global Positioning System (GPS), adapted Geographic Information System (GIS) and computer vision. Its prototype is depicted in Figure 2.5.

The fusion of GPS, GIS and computer vision is mainly intended to precisely locate the users position. Besides that, the computer vision module detects relatively small and unexpected objects that might appear, as well as guide the blind person towards an intended object (mail box, for example), through a sound system that needs headphones to correctly operate.

Figure 2.5: Prototype of the NAVIG system [13].

### 2.3 Parametric Speaker

A Parametric Speaker is a device that enables to project sound waves in a very specific direction, as opposed to a conventional speaker, that scatters around the sound waves.

Its applications vary creatively and it is mainly intended to place the sound in a very specific location, preserving a degree of privacy. In a commercial brochure [14], Sennheiser recommends its Parametric Speaker, depicted in Figure 2.6, in situations like Museum exhibitions, some automatic machines, like ATM's and voting booths, workspaces and other situations where confidential information might be transmitted in audio signals.

Figure 2.6: Sennheiser's Audiobeam Parametric Speaker.

The same brochure states that the parametric speaker, whenever targeting the beam to a place where it is supposed to reflect, it becomes also audible. This way it creates the illusion that a sound is coming from that point of reflection.

This phenomenon is intended to be explored in this project, once it should be easier to

detected an obstacle in space by "hearing it" when it is the only one in the surrounding space emitting a certain audible signal.

The *Parametric Speaker* developed in [2] and depicted in Figure 1.2, that is intended to be used in this system, showed an overall good behaviour. It was shown to be able to correctly steer a modulated beam of ultrasound waves towards the intended direction, according to user inputs, although minor deviations were detected.

In fact, tests revealed that the angle resolutions in both *azimuth* an *elevation* angles were measured to be around 1°, at a distance of 85cm from the transducer array.

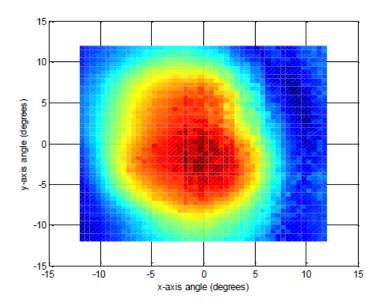

Figure 2.7 shows the result of an experiment made in [2]. The sound pressure was measured at a distance of 85cm from the *Parametric Speaker*, when it was emitting a centered beam, *i.e.*, set with 0° azimuth and elevation angles. It shows the higher sound pressure zones in red and the lower pressure zone in blues. It is visible that the higher pressure zones are around the origin, as it is intended.

Figure 2.7: Sound pressure distribution in a plane for a centered beam [2].

# Chapter 3

# Sigma-Delta Converter

## 3.1 Introduction

The detection of objects in a sonar system involves the reception of some ultrasonic system and its posterior processing. This said, one fundamental step of this process involves Analog-to-Digital conversion.

In this chapter, a brief overview on some ADC systems is made, specially the  $\Sigma\Delta$  ADC, whose main characteristics are explored and, later, it is implemented in Field-Programmable Gate Array (FPGA) and analog electronics and its performance measured and analysed.

# 3.1.1 Sampling Methods

Sampling is the method used to convert an analog signal into a digital one, extracting several samples from the first at a constant rate, called sampling frequency, and there are two main ways to do it.

The first way, and the most conventional, is done at a rate higher, although near, the double of the signal's highest frequency, its Nyquist rate. The Nyquist Theorem states that a signal should be sampled at a frequency greater than the double of its highest frequency, avoiding the so called *aliasing* phenomenon.

Let's consider a generic and analog signal in the time domain,  $x_a(t)$ , and its Fourier Transform,  $X_a(f)$ . Sampling the analog signal with a stream of unit impulses (delta function), separated from each other by a constant time period,  $T_s$ , meaning a constant sampling frequency,  $F_s$ , results in a discrete signal [15]:

$$x_a(n) = x(nT_s), \quad -\infty < n < \infty$$

(3.1)

And, in the frequency domain:

$$X_a(f) = F_s \sum_{k=-\infty}^{\infty} X(f - kF_s)$$

(3.2)

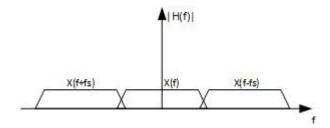

This means that the frequency spectrum of the original signal gets shifted of  $kf_s$  frequency units and so it is replicated an infinite number of times, each replica centred at multiples of the sampling frequency. In the case that  $f_s$  is smaller than twice the bandwidth of the baseband spectrum, every replicas overlap, creating the *aliasing* phenomenon, as illustrated in Figure

3.1, resulting in added frequency components to the baseband spectrum and, thus, undesired interferences.

Figure 3.1: Aliasing Effect.

Therefore, considering non-idealities in practice, it is necessary to always sample a signal with a sampling frequency slightly greater than its Nyquist frequency.

This leads to the need of a Low-Pass Filter (LPF) with a narrow transition band to filter the continuous signal, protecting the output from *aliasing*. This filter will be called *aliasing* filter and its required transition band is not just difficult to implement, but also expensive.

The second way to sample a signal is less demanding on the LPF's transition band requirements. It's called *oversampling* and it consists on sampling with a frequency much higher than the signal's bandwidth. Considering a generic signal x(t), with a baseband bandwidth B, sampling with a rate  $f_s$  implies that the low-pass filter's transition band will begin at B and end at frequency  $f_s - B$ . In *oversampling*, beeing that  $f_s \gg B$ , the transition band required is wide, comparing to the Nyquist rate sampling case, resulting in a need of a less complex and cheaper filter[16].

#### 3.1.2 Quantization noise

Usually, quantization follows the sampling process, rounding the sampled value to the nearest value of previously specified quantization levels, *i.e.*, the division of the analog signal amplitude range by several equally spaced levels.

Considering  $\Delta$  as the amplitude of level separation, *i.e.*, the space between quantization levels, the largest quantization error occurs when the quantized sample, before being rounded, has a value that falls exactly in between two levels so, for some quantized value, the error can be measured from  $-\Delta/2$  to  $\Delta/2$ , and it is assumed to be uniformly distributed along this interval. Thus, the noise power is [17]:

$$P_n = \sigma^2 = \int_{-\Delta/2}^{\Delta/2} \frac{r^2}{\Delta} dr = \frac{1}{\Delta} \left[ \frac{r^3}{3} \right]_{-\Delta/2}^{\Delta/2} = \frac{1}{\Delta} \frac{2\Delta^3}{24} = \frac{\Delta^2}{12}$$

(3.3)

Being r the value of the quantization error or, in other words, the distance of the sampled value from the nearest quantization level.

Considering that the quantization error is uniformly distributed along  $\Delta$ , it adds white noise and is not related to the analog signal. As such, both *oversampling* and Nyquist rate sampling processes will be affected with the same noise power, dependent only on the quantization resolution.

However, in *oversampling*, the noise power spreads over a wider frequency band, due to its much greater sampling frequency[16]. Thus, inside the input signal's baseband, comparing

to a Nyquist rate ADC, an *oversampling* converter has a smaller fraction of noise uniformly distributed, reducing noise power inside the baseband and increasing Signal-to-Noise Ratio (SNR).

#### 3.1.3 Performance

#### Signal-to-Noise Ratio

The SNR quantifies the ratio between the power of a given signal and the power of the noise it contains. It is usually expressed in Decibel (dB) and is calculated according to the following equation:

$$SNR = 10 \times log_{10} \left(\frac{P_{signal}}{P_{noise}}\right) [dB]$$

(3.4)

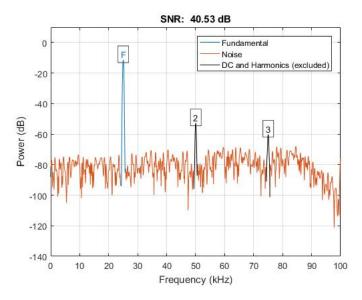

One way to compute the powers that make up the fraction in Equation 3.4 is to determine the PSD of a signal, which is what characterises the scattering of power in the frequency spectrum, find the frequency components correspondent to signal and to noise (and, eventually, to harmonics), and then sum the power present in the respective frequencies. It is usual to find in a PSD harmonic components of the input signal, as illustrated in Figure 3.2. The harmonic components can be discarded out of this computation, as they add power in the noise band to a great extent, not being noise components, but the result of non-linear effects imposed by a system.

Figure 3.2: PSD of a sinusoidal signal with noise and harmonic components.

#### Signal-to-Noise and Distortion Ratio

The Signal-to-Noise and Distortion Ratio (SINAD) measures the ratio between the signal power and the noise and harmonics powers added together. Also often expressed in dB, it is,

so, given by:

$$SINAD = 10 \times log_{10} \left( \frac{P_{signal}}{P_{noise} + P_{harmonics}} \right)$$

(3.5)

#### Spurious-free Dynamic Range

Spurious free dynamic range (SFDR) is the ratio of the Root Mean Square (RMS) value of the signal to the RMS value of the worst spurious interference, regardless of where it falls in the frequency spectrum, and it represents the smallest value of signal that can be distinguished from a large interfering (spurious) signal.[18]. It is computed by:

$$SFDR = 10 \times log_{10} (P_{fund}) - 10 \times log_{10} (P_{spur})$$

(3.6)

#### **Total Harmonic Distortion**

The Total Harmonic Distortion (THD) is the ratio between the power in all the harmonic components and the fundamental power and relates to the linearity of the ADC, meaning that a lower THD value means less signal dependent distortion.[19]. Thus, its value in dB is given by:

$$THD = 10 \times log_{10} \left( \frac{\sum_{n=1}^{N} P_{harm_n}}{P_{signal}} \right)$$

(3.7)

## Resolution

The resolution of an ADC quantifies the number of possible outputs when compared to the input range. For example, given a N-bits ADC, its resolution is  $\frac{1}{2^N}$  of its input peak-to-peak value. It can also be stated that it measures the amount of voltage that a Least Significant Bit (LSB) quantizes.

Due to introduced noise and distortions, however, some LSBs might be encoding noise amplitudes that are greater than the resolution. Given this fact, only a portion of the N bits encodes the input signal and it is named Effective Number of Bits (ENOB). The ENOB tells the number of bits that encode useful information and can be computed by:

$$ENOB = \frac{SINAD - 1.76}{6.02} \tag{3.8}$$

#### 3.1.4 Delta Modulation

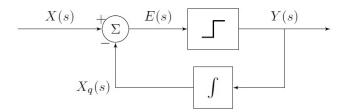

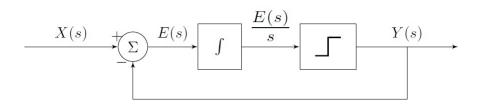

A Delta Modulator (DM) is an example of an *oversampling* converter. Its block diagram is depicted in Figure 3.3.

The DM, through a feedback loop, is intended to perform periodically a two-level quantization of the difference between an input signal, X(s), and its approximation,  $X_q(s)$ . Considering that the integrator acts as a LPF, when the mentioned difference is positive, meaning that the input is greater than its approximation signal, the output sample, Y(s), is set to the logic level 1 and so the integrator will increase its output by a small amount,  $\Delta$  (hence its

Figure 3.3: Delta Modulator block diagram.

name), getting it closer to the input sampled value. On the other way, if the difference is negative, the output of the modulator will be set to 0, decreasing the value of the approximated signal by  $\Delta$  units. Such process is depicted in Figure 3.4.

Figure 3.4: Delta Modulator's signals [20].

The demodulation of the output signal is based on the modulator's principle. An integrator converts the pulses from the modulator output to a stair shapped approximation of the input signal and a LPF converts the later into the regenerated input signal. Figure 3.5 portrays a DM immediately followed by its demodulator.

Figure 3.5: Delta Modulator followed by its demodulator.

On the right-hand side of Figure 3.4 is evident the biggest limitation of this type of modulators. The input signal must have its frequency very well delimited, otherwise it might change at a rate in which the modulator is not able to match with successive  $\Delta$  additions/subtractions, unless sampling frequency or the  $\Delta$  increased/decreased by the integrator are adapted (which is highly unpractical) and thus creating undesired distortions to the modulated signal. This phenomenon is called *slope overload* and is caused by the modulator's

topology.

Taking into account Figure 3.6, and considering the respective signals in the  $\mathcal{Z}$  domain, it's easy to understand that the output signal is given by the error signal, E(z), added with quantization noise, N(z):

$$Y(z) = E(z) + N(z) = X(z) - X_q(z) + N(z)$$

It is fair to assume that the noise introduced by quantization is negligible when compared to the other signals:

$$Y(z) \approx X(z) - X_q(z)$$

Given the fact that the integration in the  $\mathcal{Z}$  domain involves a delay (one sampling period), and having in mind that  $X_q(z)$  is an approximation of the input signal, the output of the DM can be considered as approximately the difference between two consecutive input samples:

$$Y(z) \approx X(z) - X(z-1) \tag{3.9}$$

It is now possible to conclude that the output of the DM is roughly a differentiation of the input signal, making it highly sensitive to it's variations and thus allowing input frequency related phenomena, such as *slope overload*, to happen.

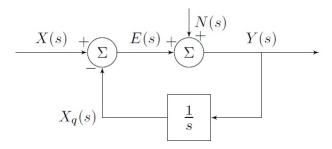

Being that the noise added to the system during quantization is a result of stochastic process, it shows a non linear behaviour. Being so, in order to analyse its impact on the system, the modulator is approximated to is linear model, illustrated in Figure 3.6, whose signals are represented in the  $\mathcal{S}$  domain.

Figure 3.6: Delta Modulator's linear model.

The output of the modulator is given by:

$$Y(s) = E(s) + N(s) = X(s) - \frac{1}{s}Y(s) + N(s)$$

Solving for Y(s), it is obtained:

$$Y(s) = \frac{s}{s+1} [X(s) + N(s)]$$

(3.10)

Being  $s = j\omega$ , it is easy to note that the DM acts as a High-Pass Filter (HPF) for both the input signal and the quantization noise.

#### 3.1.5 Sigma-Delta Modulation

#### First Order

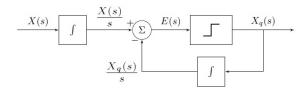

The  $\Sigma\Delta M$ , also referred to as Delta-Sigma, is a variation of the previous *oversampling* modulator. Considering Figure 3.5, the signal at the input of the demodulator's LPF is:

$$X_q(s) = \frac{1}{s}Y(s) \approx \frac{1}{s}[X(s) - X_q(s)] = \frac{1}{s}X(s) - \frac{1}{s}X_q(s)$$

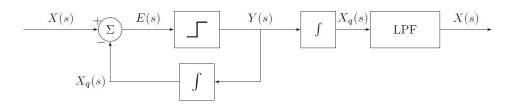

Therefore, it is roughly equivalent to sample the difference between the input signal and the modulated output, both separately integrated, and later recover with a LPF. In other terms, the  $\Sigma\Delta M$  samples the difference between the integrated input and the approximated output. This is the  $\Sigma\Delta M$  mathematical principle, and this modulator is depicted in Figure 3.7.

Figure 3.7: Sigma-Delta Modulator.

Given the fact that:

$$E(s) = \frac{X(s)}{s} - \frac{X_q(s)}{s} = \frac{1}{s} (X(s) - X_q(s))$$

The  $\Sigma\Delta M$  represented in Figure 3.7 can be simplified by combining both integrators into one, placed right after the adder, as depicted in Figure 3.8, now with the output named Y(s).

Figure 3.8: Simplified Sigma-Delta Modulator.

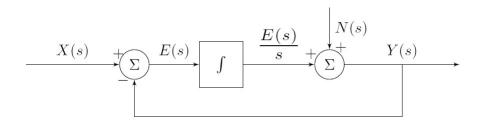

The quantization noise added by the comparator is a stochastic process. Being so, the noise added to the system is non-linear and can not be described through some mathematical relationship. In order to perform the noise impact analysis on the modulator, it's topology is approximated to a linear model, depicted in Figure 3.9, where the noise is referred to as N(s) and so a linear behaviour is attained, which depends on the noise signal, that is non-linear.

The output of this block diagram is given by:

$$Y(s) = \frac{E(s)}{s} + N(s) = \frac{1}{s} [X(s) - Y(s)] + N(s)$$

Figure 3.9: The Sigma-Delta Modulator linear model.

Solving for Y(s), the following result is obtained:

$$Y(s) = \frac{1}{s+1}X(s) + \frac{s}{s+1}N(s)$$

(3.11)

Considering the fact that  $s = j\omega$  and the absolute value of  $\frac{1}{s+1}$  tends to infinity, the term (also known as Signal Transfer Function (STF)) has a transfer function similar to one of a LPF and the term  $\frac{s}{s+1}$  (the Noise Transfer Function (NTF)) represents a transfer function similar to one of a HPF. Given this fact, it is possible to infer that the  $\Sigma\Delta M$  will not affect the input signal, as long as its frequency content does not exceed the LPF cut-off frequency, and the quantization noise will be pushed towards higher frequencies of the spectrum, reducing the noise in the baseband to a greater extent. This occurrence is known as *Noise Shaping* and it can be verified in Figure 3.12.

Considering Figure 3.8 and its signals in the  $\mathcal{Z}$  domain, the output is:

$$Y(z) = \frac{1}{1 - z^{-1}} E(z) = \frac{1}{1 - z^{-1}} [X(z) - Y(z)]$$

Solving for Y(z), the expression results in:

$$Y(z) = \frac{X(z) + Y(z-1)}{2}$$

(3.12)

Therefore, opposing to the conclusions reached in equation 3.9, it is inferred that, contrary to the DM, the  $\Sigma\Delta M$ 's output is not sensitive to its input variation and, therefore, it will not exhibit the slope overload effect.

In conclusion, the  $\Sigma\Delta M$  is to perform better than the DM for it will present under no circumstances slope overload distortion and it has the ability to significantly decrease the noise density in the bandwidth of interest, that is, the baseband, increasing even more the SNR of the recovered signal.

#### High-Order Sigma-Delta

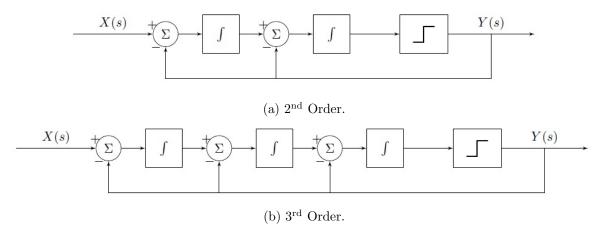

High-order  $\Sigma\Delta Ms$  are implemented by cascading N integrators fed-back with the output signal. Figure 3.10 depicts two examples of high-Order  $\Sigma\Delta M$ .

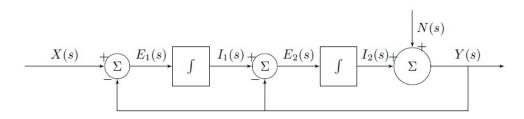

Figure 3.11 depicts a second order  $\Sigma\Delta M$  reduced to its linear model, where some non-linear quantization noise, N(s), is added in the place of the comparator, which also acts as a 1 bit quantizer.

Figure 3.10: Two Different High-order Sigma Delta Modulators.

Figure 3.11: Linear model of a  $2^{\rm nd}$  order  $\Sigma \Delta M$ .

Let its output be defined as the sum of N(s) and  $I_2(s)$ :

$$Y(s) = I_2(s) + N(s) = \frac{E_2(s)}{s} + N(s)$$

Being  $E_2(s) = I_1(s) - Y(s)$  and  $I_1(s) = \frac{E_1(s)}{s}$ , the previous expression can be stated as:

$$Y(s) = \frac{\frac{E_1(s)}{s} - Y(s)}{s} + N(s)$$

Which, considering that  $E_1(s) = X(s) - Y(s)$ , and solving for Y(s), the transfer function of the system can be obtained:

$$Y(s) = \frac{1}{s^2 + s + 1}X(s) + \frac{s^2}{s^2 + s + 1}N(s)$$

Following the same procedure for the  $3^{\rm rd}$  order  $\Sigma\Delta M$ , it yields the transfer function defined as:

$$Y(s) = \frac{1}{s^3 + s^2 + s + 1}X(s) + \frac{s^3}{s^3 + s^2 + s + 1}N(s)$$

It is, then, easily deducted that, for a N-order  $\Sigma\Delta M$ , its transfer function, as a function

of the input signal (X(s)) and the quantization noise (N(s)) is given by:

$$Y(s) = \frac{1}{\sum_{n=0}^{N} s^n} X(s) + \frac{s^N}{\sum_{n=0}^{N} s^n} N(s)$$

(3.13)

In terms of absolute value of the transfer function, being  $s=j\omega$ , for high frequencies, the STF tends to zero, acting as a LPF. On the other hand, the term with greater power on the denominator of the NTF gets much greater than the remaining terms, so  $\sum_{n=0}^{N} s^n \approx s^N$ , reducing the NTF to  $\frac{s^N}{s^N}$ , and, thus, it acts as a HPF. Since the STF has N poles and the NTF has N poles and N coincident zeros, as the order of the  $\Sigma\Delta M$  increases, the number of poles of the STF and the number of poles and zeros of the NTF also increase, increasing the attenuation outside of the passband.

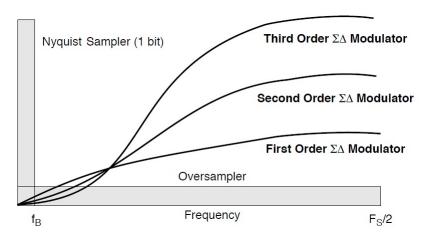

In practice, higher-order  $\Sigma\Delta Ms$  are more effective to filter the input signal higher frequencies and quantization noise at lower frequencies. The effect of the  $N^{th}$  order  $\Sigma\Delta M$  on the noise (Noise Shaping (NS)) is the most notable one and it is depicted in Figure 3.12, as well as the distribution of quantization noise in a Nyquist sampling ADC and a simple oversampling ADC.

Figure 3.12: Noise Shaping for different orders  $\Sigma\Delta M$ , a Nyquist sampling ADC and a simple oversampling ADC[16].

In conclusion, the higher the order of the  $\Sigma\Delta M$ , the more effective it is at pushing the quantization noise towards high frequencies, at the expense of hardware simplicity. However, stability problems might also occur, due to the increasing number of poles of both STF and NTF.

# 3.2 Design of the Modulator

Given the desired portability of the overall system, hardware simplicity is a main goal of the project. For that reason a FPGA implemented  $\Sigma\Delta M$  must be as simple as possible in terms of hardware external to the FPGA.

That said, the implemented  $\Sigma\Delta M$  was a first-order one, having in mind that the benefits are not worth the added complexity brought by a higher-order  $\Sigma\Delta M$ .

Initially, it was planned to implement the topology depicted in Figure 3.8. However, given the need of an analog integrator in the feedback loop, so was needed an analog adder block, that should be implemented with an Operational Amplifier (OPAMP) in a difference configuration with unity gain. Thus, the topology depicted in Figure 3.7 was chosen, implementing the adder block with a differential input buffer, programmed in the FPGA. Although the number of integrators doubled (a total of two resistors and two capacitors), the need for a difference amplifier was eliminated and, so, the need for one OPAMP and four resistors. This way, a simplified and equally functional  $\Sigma\Delta M$  was designed, with a minimum number of electronic components outside of the FPGA.

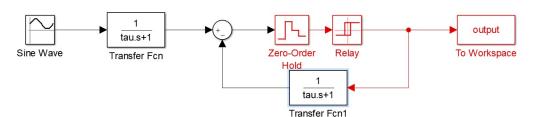

After the selection of the topology, a simulation of the system followed in MATLAB's Simulink environment.

The integrators were simulated according to an RC transfer function:

$$H_{RC}(s) = \frac{1}{1 + sRC} = \frac{1}{1 + s\tau}$$

(3.14)

The comparator implemented on the simulation was composed of a Zero-Order Hold (ZOH), with the intention to hold an input value for a duration equal to the sampling period, and a relay that would read the output of the ZOH and round it to its nearest digital value. Therefore, these two blocks cascaded act as a 1-bit quantizer operating at a fixed sampling frequency. Figure 3.13 depicts the Simulink block diagram of the simulated system, where the red components correspond to the digital part of the modulator and the black ones to the analog part.

Figure 3.13: Simulink topology of the designed  $\Sigma \Delta M$ .

Due to the fact that the differential input buffer on the Artix-7 FPGA does not support 3.3V Low Voltage Differential Signalling (LVDS) I/O standard, the system was designed for a voltage range from 0V to 2.5V. As such, the sine wave at the  $\Sigma\Delta M$ 's input has an amplitude of 1.25V and DC component of equal value. In the simulation, the input signal has frequency of 40kHz, given the fact that the used ultrasound transducers operate at this central frequency.

Having in mind this central frequency, the RC integrators, which also act as LPF, were designed for a cut-off frequency slightly above this frequency (approximately 48.2Hz, that is a time constant  $\tau = RC = 3.3\mu s$ ).

The simulation was run for different sampling frequencies and the performance indicators (SNR,SINAD, Spurious Free Dynamic Range (SFDR) and THD) where computed, while a  $40 \mathrm{kHz}$  sine wave was at the input of the  $\Sigma \Delta M$ . The results are shown on Table 3.1

The irregularity of the SNR results is due to the fact that some sampling frequencies (like 12.5MHz) introduced a great amount of spurious in the noise band, raising the total noise power and degrading SNR.

| $f_s$ (MHz) | SNR (dB) | SINAD (dB) | SFDR (dB) | THD (dB) |

|-------------|----------|------------|-----------|----------|

| 10          | 103.4    | 43.0       | 43.1      | -43.0    |

| 12.5        | 48.2     | 47.4       | 52.7      | -55.1    |

| 20          | 107.0    | 64.2       | 64.2      | -64.2    |

| 25          | 51.9     | 49.3       | 52.9      | -52.7    |

| 50          | 90.4     | 68.5       | 69.1      | -68.6    |

| 100         | 88.6     | 71.6       | 71.9      | -71.9    |

Table 3.1: Performance indicators computed in the simulation for different sampling frequencies, with input frequency of 40 kHz.

Given the results, 50MHz of sampling frequency were chosen because of the greater SNR measured, in spite of the slightly lower remaining performance indicators.

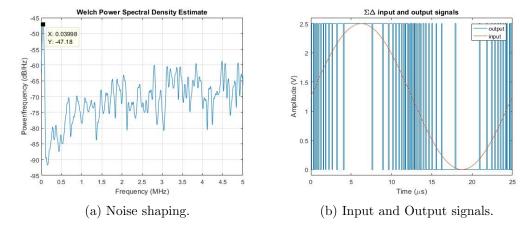

Figure 3.14 shows the input and output signals, for a sampling frequency of  $10 \mathrm{MHz}$  (chosen so a better visualisation of the output signal could be obtained) and an input frequency of  $40 \mathrm{kHz}$ , as well as the NS characteristic.

Figure 3.14: Bitstream modulation and noise shaping characteristic for a 40 kHz input sine wave and 10 MHz sampling frequency.

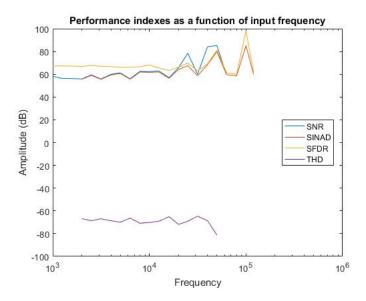

Finally, with the sampling frequency set, the simulation was run for different input signal frequencies. The results are shown in Figure 3.15.

Figure 3.15: Simulated performance indicators for different input frequencies.

# 3.3 Implementation of the $\Sigma\Delta M$

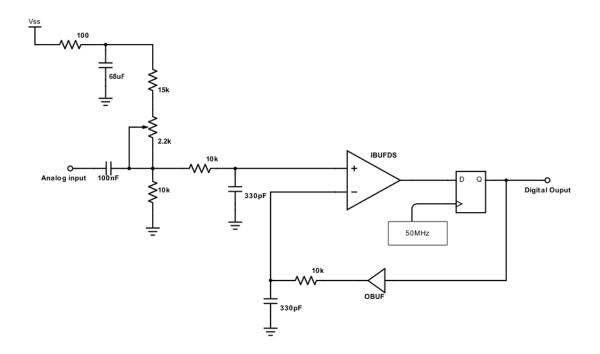

The design proposal for the  $\Sigma\Delta M$  is depicted in Figure 3.16. Inside the blue box lay the digital components, implemented in VHDL and outside are the analog components that make up the integrators.

Figure 3.16: Designed  $\Sigma \Delta M$ .

# 3.3.1 Digital Interface

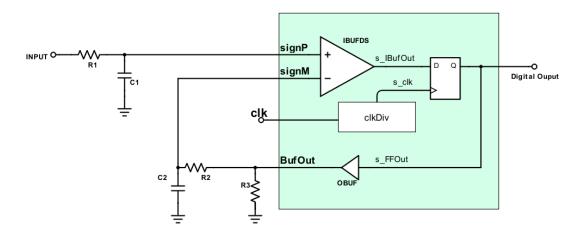

The digital interface of the  $\Sigma\Delta M$  was implemented in a VHSIC Hardware Description Language (VHDL) programmed FPGA and Figure 3.16 depicts its block diagram inside the blue box, with inputs signP, signM and clk, a single output BufOut (bold letters) and internal signals  $s\_IBufOut$ ,  $s\_clk$  and  $s\_FFOut$ .

The VHDL implementation of the digital interface can be found in Appendix C.

#### Input Differential Buffer

As stated previously, the adding block of the chosen  $\Sigma\Delta M$  topology was implemented as an input differential buffer (IBUFDS). This way, the output of the buffer would be the nearest digital value to the difference between its inputs. A VHDL primitive, part of UNISIM library, was available and used to implement this part of the circuit in a simple way, on the top level file. The differential termination was chosen to be off, once the frequencies at both inputs are expected to be relatively low (around 40kHz), not causing the reflection phenomenon expected when high-frequency signals reach the buffer inputs. The low power attribute was set to FALSE in order to improve the buffer's performance and the IOSTANDARD was defined to be LVDS-25, as  $V_{CCO}=3.3V$  powered LVDS signaling is not supported in Xilinx's 7 series FPGA families [21], as it is the case with the used Artix-7 (due to this fact, the remaining inputs and outputs were set to a LVCMOS25 IOSTANDARD).

## Sampling

However, the output of the differential buffer is in no way synchronised with any clock signal. In order to perform this, a D-type flip-flop was cascaded with the differential buffer. A D-type flip flop sets its output as the input digital value at very specific time instants (in this case, at its clock signal rising edge), remaining unaltered at other instants, independently of the input value. Both the input differential buffer and the D-type flip-flop combined perform the 1-bit quantization at sampling frequency  $f_s = 50MHz$ . The output of the D flip-flop is to be fed-back to the negative input of the differential buffer, right after being integrated.

The clock signal controlling the sampling moments, of frequency 50MHz, corresponds to half the frequency of the internal clock of the FPGA used (division factor of 2). To implement it, a frequency divider was described. The principles behind its operation is that, dividing the input clock frequency by a division factor of N, the output signal is off during  $\frac{N}{2}$  input periods and on during the remaining. Provided that N is even, the output signal is a Pulse-Width Modulation (PWM) signal with exactly 50% duty-cycle. Otherwise, it is on for  $\frac{N}{2}-1$  periods and off for  $\frac{N}{2}$  input clock periods.

#### Output buffer

The remaining VHDL component is an output buffer that allows the output signal of the  $\Sigma\Delta M$  to be fed-back, through an analog circuit that is external to the FPGA. This output buffer is also a primitive that is part of the UNISIM library and, as with the input differential buffer, it was programmed in the top-level file. The drive attribute was set to 16, the IO/standard was set to LVCMOS25 to maintain compatibility between the pins used and the SLEW attribute, which sets the slew rate of the output buffer, was set to HIGH, so that it could get a faster response and thus improving signal quality throughout the feedback loop.

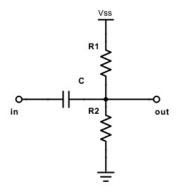

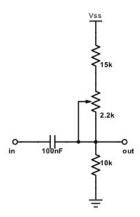

#### 3.3.2 Analog interface

Given the fact that the input differential buffer was set to have the LVDS\_25 IOSTAN-DARD, the output of the digital interface should have a digital high level of 2.5V. To achieve this objective, experimentally, the output impedance of the *BufOut* output was measured at

DC to be  $220\Omega$ . Once the output range would vary from 0V to 3.3V, given this measured output impedance, a resistor was connected with one terminal at the output and the other at the ground. This resistor is depicted in Figure 3.16 with the reference R3. The purpose of this resistor was to act alongside with the measured output impedance as a voltage divider and, thus, lower the output voltage when on from 3.3V to 2.5V. As such, the value of this resistor is given by the voltage divider expression:

$$2.5 = \frac{R_3}{R_3 + 220} \times 3.3$$

Solving for  $R_3$ , its value is then computed:

$$R_3 = \frac{220 \times 2.5}{3.3 - 2.5} = 687.5\Omega$$

And so the connected resistor was one of  $680\Omega$ .

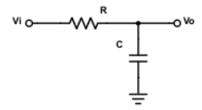

The integrators were chosen to be simple RC circuits. Let the circuit in Figure 3.17 be considered.

Figure 3.17: RC integrator and low-pass filter.

The output voltage is:

$$v_o(t) = \frac{1}{C} \int i(t)dt = \frac{1}{C} \int \frac{v_i(t) - v_o(t)}{R} dt$$

For high input frequencies, as the circuit acts as a low-pass filter, the output voltage is negligible when compared to the input voltage, and so:

$$v_o(t) \approx \frac{1}{C} \int \frac{v_i(t)}{R} dt$$

Thus, the circuit behaves as a voltage integrator at high frequencies, which is the required operation for the feedback loop. At low frequencies  $(s = j\omega \approx 0)$ , the output of the circuit is approximately the same as the input signal:

$$V_o(s) = \frac{Z_C}{R + Z_C} V_i(s) = \frac{\frac{1}{sC}}{R + \frac{1}{sC}} V_i(s) = \frac{1}{1 + sRC} V_i(s) \approx V_i(s)$$

This is the desired behaviour because it is intended to subtract the input signal to its approximation and later quantize it. This is a characteristic from a DM and, as it was

previously stated, a  $\Sigma\Delta M$  is a variation of the first, so some characteristics are mutual to both.