## DISSERTATION

#### submitted

to the

Combined Faculty for the Natural Sciences and Mathematics

of the

Ruperto-Carola University of Heidelberg, Germany

for the degree of

**Doctor of Natural Sciences**

Put forward by

Richard Donald Sylvère Leys Born in: Croix, France

# Raising the abstraction level of hardware software co-designs

Advisor: Prof. Dr. Ulrich Brüning

Date of Oral Examination: .....

# Abstract

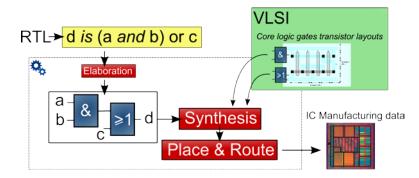

As lithographic processes' size to manufacture transistors shrink, the number of available transistors on integrated circuits (IC) increases. Newly manufactured ICs require innovations to leverage improved performances or area occupation, and feature more and more components on the same chip, which work together and/or independently to provide an advanced set of functions.

The complexity of hardware design flows consequently increased: from circuit description to functional verification and in-system interface, every stage is now more and more driven by a cross-product function between a set of reusable functional units and constraints to target a specific technology (ASIC, FPGAs etc...) and configuration.

This diversity in the possible outputs for a set of components calls for the development of new methodologies to raise the abstraction level in the design flows. A better abstraction allows optimizing and automating more processes, from component specification to final implementation and interfacing.

New Abstraction levels have always emerged through industry standards like Verilog and VHDL for digital circuit description, SystemVerilog/UVM/e for functional verification, or by vendor specific toolchains. However, standards and software toolchains usually lack flexibility as they operate for a bounded range of functionalities.

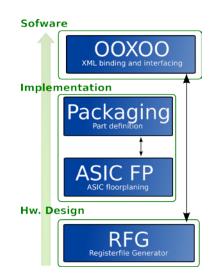

This thesis presents some novel applications covering various stages of the design flow, ranging from digital design input (register file generator) and ASIC circuit implementation (Hierarchical Floorplaning), up to in-system IC integration (Part design language). They are backed by a generic software design methodology based on functional programming used to develop domain specific languages embedded in the TCL interpreter.

To complete the design flow path from circuit implementation to software integration, a hardware-software interfacing point linked with the Register File Generator design tool will be presented. It is based on a generic and innovative XML-Data binding technology which was developed during this work.

The iterative loop between application definition and flexible software components reuse presented along this work also provides a general guideline to develop future design flow components, and guarantee their integration in any target environment.

# Zusammenfassung

Die menge von Transistoren, die auf einen Integriertes Schaltung (IS) zu Verfügung stehen steigt mit die Verkleinerung der lithographischem Prozesse. Neue erstellte IS benötigen Innovationen um Performanz und Fläche auszunutzen, und bitten immer mehr Komponente auf den gleichen Chip, die miteinander oder unabhängig von einander arbeiten müssen, um ein fortgeschrittenes Satz von Funktionalitäten anzubieten.

Als Konsequenz davon, steigt die Komplexität der Design Flows mit: von Schaltung Beschreibung bis Funktionale Verifikation und In-System Integration, jede Stufe ist immer mehr abhängig von ein Satz von wiederverwendbarer Funktionale Einheiten und so einfach wie möglich Einschränkungen, die zu einen bestimmte Technologie und Ausstattung gezielt sind.

Diese Vielfältigkeit der möglichen Ausgaben für einen gegebenen Satz von Komponente spricht für die Entwicklung von Methodik, die den Abstraktion Grad in Design Flows erhöht. Einen besseren solchen Abstraktion Grad erlaubt eine Optimierung und verbesserte Automatisierung der Design Prozesse, von Spezifikation bis Endgültigen Implementierung und Integrierung.

Neuen Abstraktion Grade stellen sich typischerweise heraus durch Industrie Standarte, wie Verilog oder VHDL für Digitale Schaltungen Beschreibung, SystemVerilog/UVM/e für Funktionale Verifikation, oder durch Vendor eigentümliche Lösungen. Standarte und Software greifen allerdings immer auf einen bestimmten Untersatz der Design Flows zu, und fehlen dadurch die benötigte Flexibilität um sich mit anderen Aktoren geschickt zu integrieren.

Diese Dissertation stellt eine ausgewählten Satz von neuen Anwendung vor, die verschiedenen Design Flow Stufen decken: Digital Schaltung Beschreibung (Register File Generator), ASIC Implementierung (Hierarchical Floorplaning) und PCB Design (Part Language). Diese werden von einen Generischen Software Programmierung Methodik unterstützt, die sich auf Funktional Programmierung Konzepte bezieht, um Domain Specific Languages in dem TCL Interpreter einzukapseln.

Um den Design Flow Pfad zu vervollständigen, einen Hardware-Software Schnittstelle, die sich mit dem Register File Generator integrieren lässt wird eingeführt. Sie greift auf einen generischen und bahnbrechende XML-Data Binding Technology, die währen diese Thesis entworfen wurde.

Die Entwicklung Schleife, zwischen Anwendung Spezifikation und anpassungsfähige Software Komponente Wiederverwendung hin und her, die durch dieser Arbeit vorgestellt wird, bittet sich als Leitfaden für zukünftige Entwicklungen von Design Flow Aktoren.

# **Table of Contents**

| 1 | In     | troduct | uction1                                                |    |  |  |

|---|--------|---------|--------------------------------------------------------|----|--|--|

|   | 1.1    | Stak    | kes 4                                                  |    |  |  |

|   | 1.2    | Con     | ntributions                                            |    |  |  |

| 2 | Fu     | unction | al programing and domain specific languages            | 7  |  |  |

|   | 2.1    | Imp     | Imperative and Functional Programming styles           |    |  |  |

|   | 2.     | 1.1     | The Imperative programming style                       | 9  |  |  |

|   | 2.     | 1.2     | The Functional programming style                       | 11 |  |  |

|   | 2.1.2. |         | An example in CLISP                                    | 13 |  |  |

|   |        | 2.1.2.2 | 2 Recursive function call                              | 14 |  |  |

|   |        | 2.1.2.3 | B List/Elements Array processing                       | 15 |  |  |

|   | 2.     | 1.3     | Discussion                                             | 16 |  |  |

|   | 2.2    | Mer     | ging styles: The Scala programming language example    | 19 |  |  |

|   | 2.     | 2.1     | Type definition and Type Inference                     | 19 |  |  |

|   |        | 2.2.1.1 | Type Inference                                         | 19 |  |  |

|   |        | 2.2.1.2 | 2 Implicits                                            | 20 |  |  |

|   | 2.     | 2.2     | Closures and high-order functions                      | 22 |  |  |

|   |        | 2.2.2.1 | Anonymous functions                                    | 22 |  |  |

|   |        | 2.2.2.2 | 2 Closures                                             | 22 |  |  |

|   |        | 2.2.2.3 | B High-order functions                                 | 23 |  |  |

|   | 2.     | 2.3     | Currying and Partial Functions                         | 24 |  |  |

|   | 2.     | 2.4     | Discussion                                             | 25 |  |  |

|   | 2.3    | Dom     | nain Specific Language design: LL and LR-based parsing | 27 |  |  |

|   | 2.     | 3.1     | LL Parsing in Java: ANTLR                              | 29 |  |  |

|   | 2.     | 3.2     | Parsing in Scala                                       | 31 |  |  |

|   | 2.     | 3.3     | Discussion                                             | 32 |  |  |

|   | 2.4    | Emb     | pedded Domain Specific Language (EDSL)                 | 33 |  |  |

|   | 2.     | 4.1     | Functional Programming for EDSL                        | 36 |  |  |

|   | 2.     | 4.2     | Discussion                                             |    |  |  |

| 3 | Er     | nbedde  | ed Domain Specific Language design in TCL              | 41 |  |  |

|   | 3.1    | The     | TCL programming language                               | 42 |  |  |

|   | 3.1.1   | Namespaces and packages                                        | 45 |

|---|---------|----------------------------------------------------------------|----|

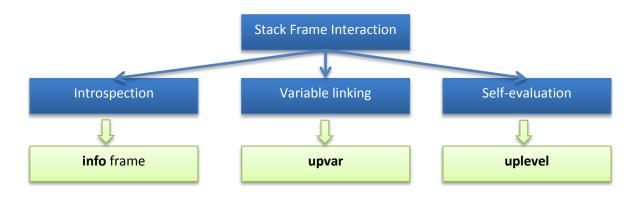

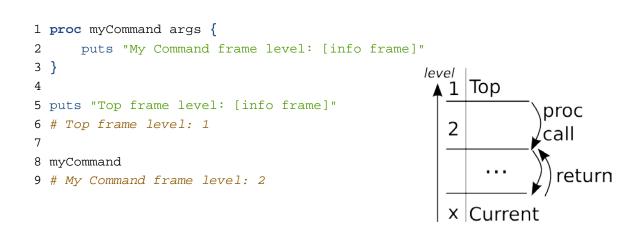

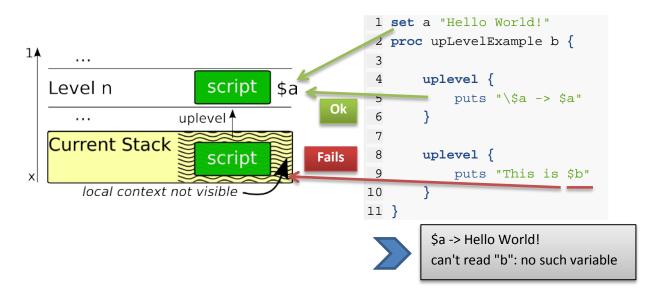

|   | 3.1.2   | Self evaluation                                                | 47 |

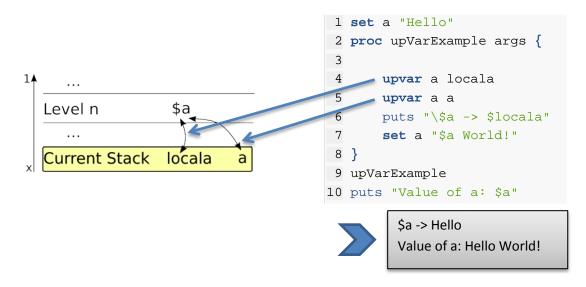

|   | 3.1.3   | Stack frame and execution level                                | 48 |

|   | 3.1.4   | Pitfalls                                                       | 51 |

|   | 3.2 Imp | lementation of Closures in TCL                                 | 53 |

|   | 3.2.1   | First implementation (v1 and v2)                               | 55 |

|   | 3.2.1.1 | Implementation                                                 | 55 |

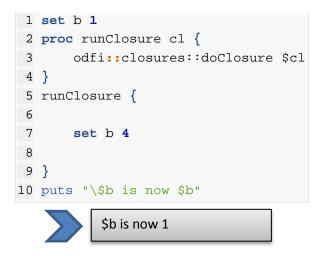

|   | 3.2.1.2 | 2 Variable detection issue                                     | 57 |

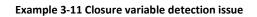

|   | 3.2.1.3 | 8 Run level selection                                          | 58 |

|   | 3.2.1.4 | Variable protection and implicit naming                        | 59 |

|   | 3.2.1.5 | 5 Limitations                                                  | 61 |

|   | 3.2.2   | Second implementation (v3)                                     | 61 |

|   | 3.2.2.1 | Variable value resolution                                      | 62 |

|   | 3.2.2.2 | 2 Variable update resolution                                   | 63 |

|   | 3.2.2.3 | B Lambda support                                               | 63 |

|   | 3.2.    | 2.3.1 Implementation                                           | 65 |

|   | 3.2.3   | Discussion                                                     | 67 |

|   | 3.3 Emb | pedded DSL in TCL                                              | 68 |

|   | 3.3.1   | Introduction with the incrTCL library                          | 68 |

|   | 3.3.2   | Improved extensibility with the Next Scripting Framework (NSF) | 73 |

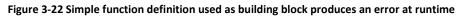

|   | 3.3.2.1 | Switching frameworks: semantic and feature issues              | 77 |

|   | 3.3.2.2 | 2 Dynamic API Enrichment                                       | 79 |

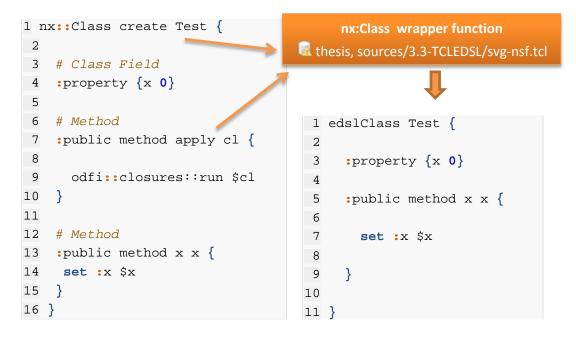

|   | 3.3.    | 2.2.1 Special procedures                                       | 79 |

|   | 3.3.    | 2.2.2 NX mixins                                                | 80 |

|   | 3.3.3   | Discussion and outlook                                         | 82 |

| 4 | Compone | ents for Hardware Software co-design                           | 83 |

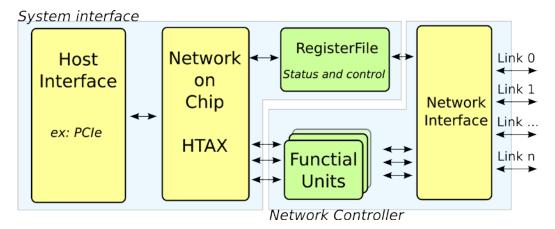

|   | 4.1 Reg | ister file generator                                           | 85 |

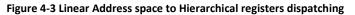

|   | 4.1.1   | RFS: Workflow and limitations                                  | 87 |

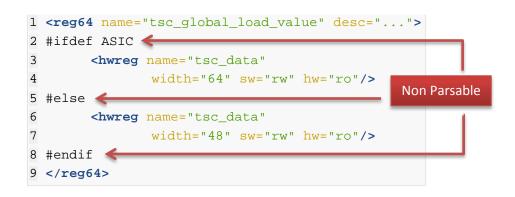

|   | 4.1.1.1 | XML Format issues                                              | 87 |

|   | 4.1.1.2 | 2 Implementation in C                                          | 88 |

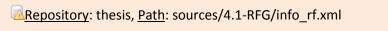

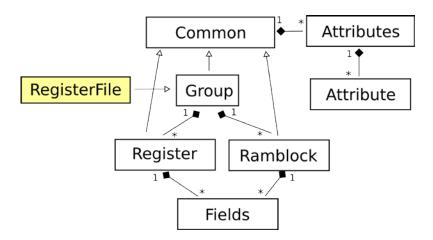

|   | 4.1.2   | RFG implementation                                             | 90 |

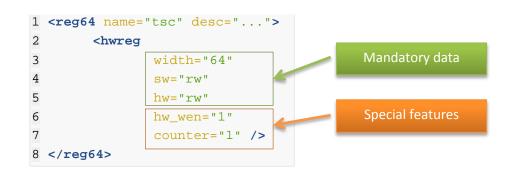

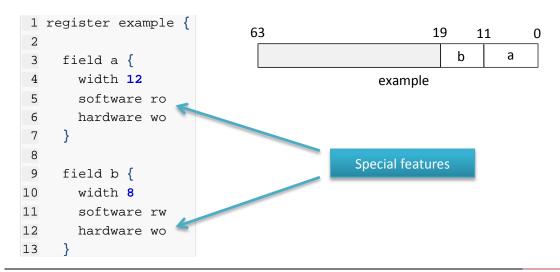

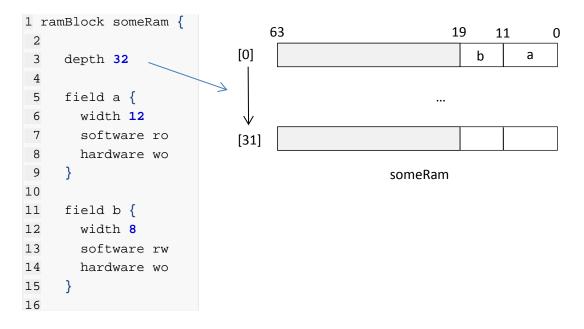

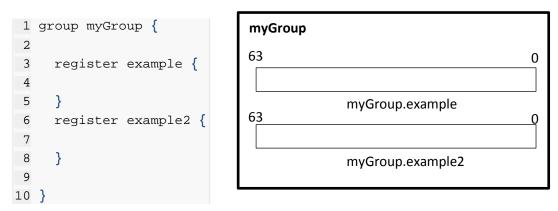

|   | 4.1.2.1 | Language elements                                              | 90 |

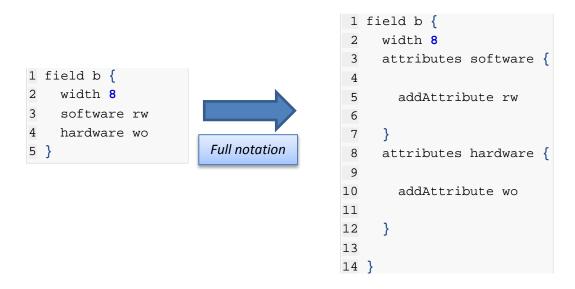

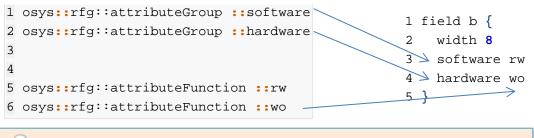

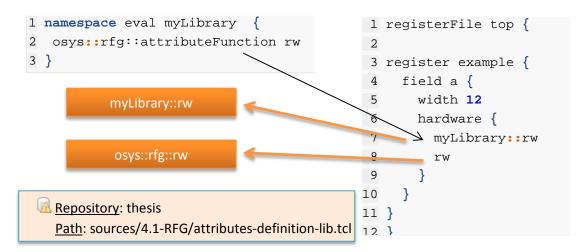

|   | 4.1.2.2 | 2 In-depth customisation: Attributes specification             | 94 |

|   | 4.1.2.3 | 8 An example                                                   |    |

| 4.1.3    | RFS b   | ackward compatibility                                     | 97            |

|----------|---------|-----------------------------------------------------------|---------------|

| 4.1.4    | Proce   | essing chain components                                   | 97            |

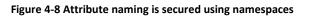

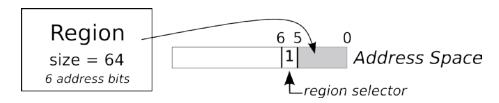

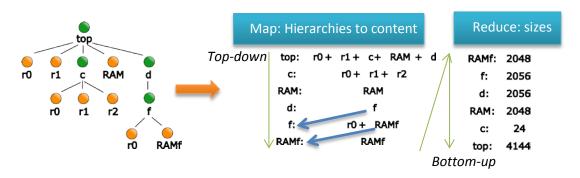

| 4.1.4.1  | L Hie   | erarchical address calculation                            | 97            |

| 4.1.     | 4.1.1   | Addressing strategies selection                           | 100           |

| 4.1.4.2  | 2 Ve    | rilog HDL                                                 | 101           |

| 4.1.4.3  | B Do    | cumentation                                               | 101           |

| 4.1.4.4  | 1 XN    | 1L output                                                 | 102           |

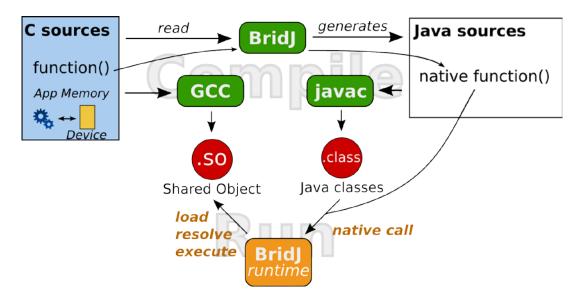

| 4.1.5    | Softw   | vare interface for the Java Virtual Machine using Scala   | 104           |

| 4.1.5.1  | L Sin   | nple device interfacing using mmap                        | 104           |

| 4.1.5.2  | 2 Na    | tive function binding in the Java Application Space       | 105           |

| 4.1.5.3  | B Sca   | ala API for RFG                                           | 106           |

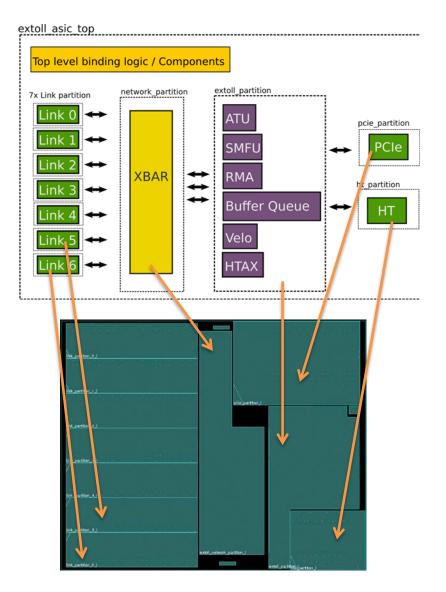

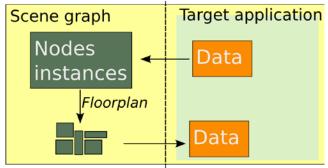

| 4.2 Hier | rarchic | al floorplanning for Integrated Circuits                  | 107           |

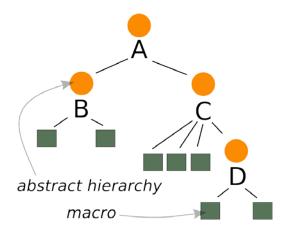

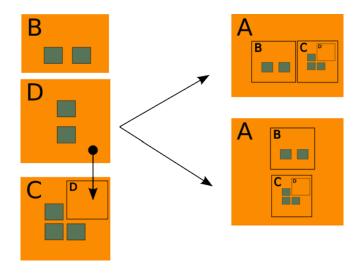

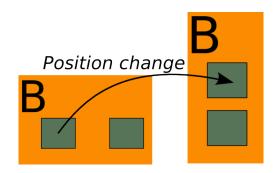

| 4.2.1    | Hiera   | rchy-centric macro placement                              | 110           |

| 4.2.2    | Moti    | vation for a generic programming interface                | 113           |

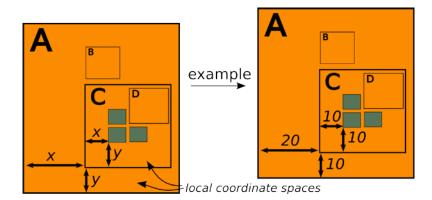

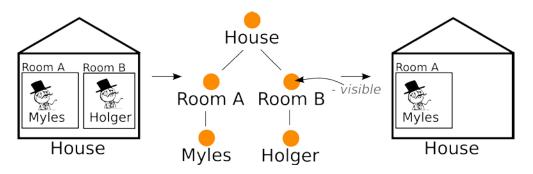

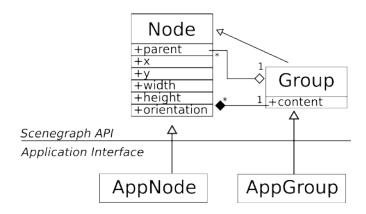

| 4.2.3    | A sce   | ne graph programming interface                            | 114           |

| 4.2.3.1  | L Flo   | orplanning properties requirements                        | 114           |

| 4.2.3.2  | 2 Ab    | stract API in TCL                                         | 116           |

| 4.2.     | 3.2.1   | Abstract class hierarchy                                  | 116           |

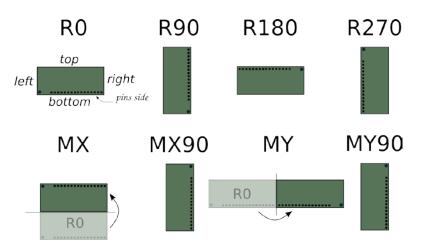

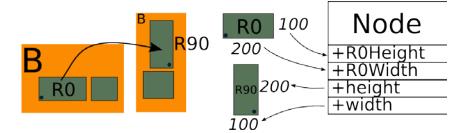

| 4.2.     | 3.2.2   | Container shape and orientation                           | 117           |

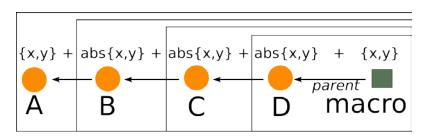

| 4.2.     | 3.2.3   | Absolute coordinates resolution                           | 118           |

| 4.2.3.3  | B Ap    | plication interface                                       | 118           |

| 4.2.     | 3.3.1   | Example: Floorplan prototyping using Library Exchange For | mat files 119 |

| 4.2.4    | Gene    | ric building blocks for floorplanning                     | 122           |

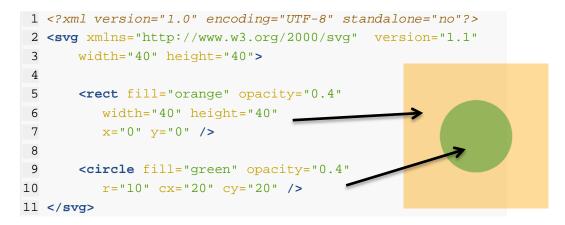

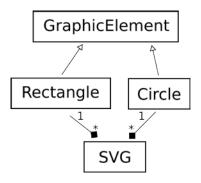

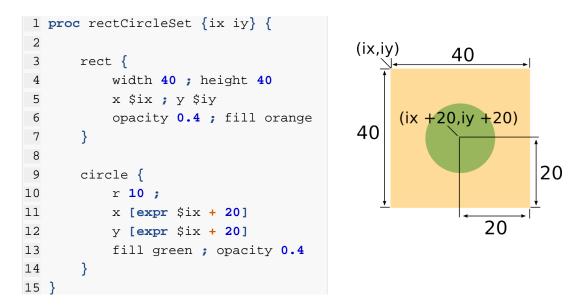

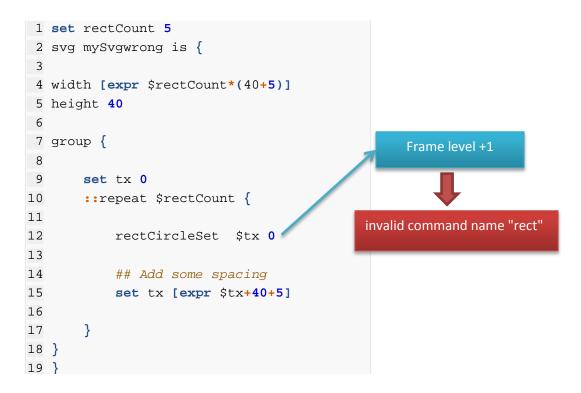

| 4.2.5    | Gene    | ric data representation using SVG                         | 124           |

| 4.2.6    | Real    | placement in Cadence Encounter                            | 125           |

| 4.2.6.1  | L Ap    | plication interface                                       | 127           |

| 4.2.7    | Outlo   | ook                                                       | 127           |

| 4.2.7.1  | L Mu    | ultiple tree-view support                                 | 127           |

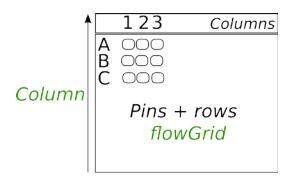

| 4.3 Part | t descr | iption language                                           | 129           |

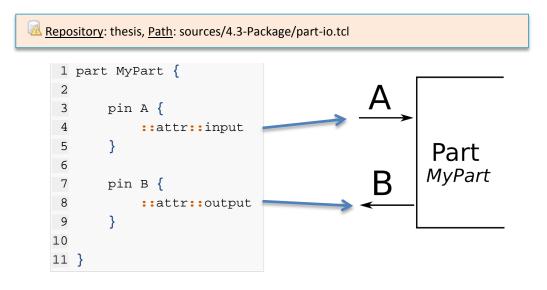

| 4.3.1    | Lang    | uage description                                          | 130           |

| 4.3.1.1  | L Att   | ributes                                                   | 130           |

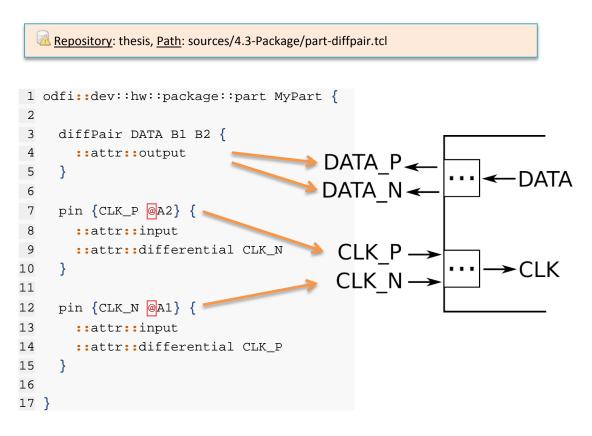

| 4.3.1.2  | 2 Ab    | straction level improvement example: Differential Pairs   | 131           |

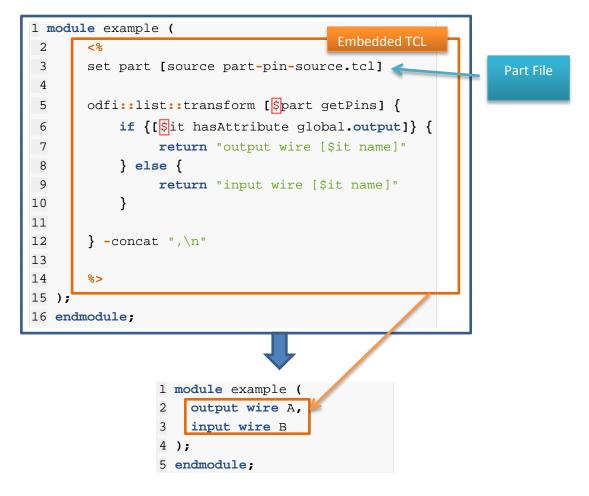

| 4.3.1.3  | 3 Ou    | tput generator rules                                      | 131           |

| 4.3.2    | Hard    | ware description language (HDL) integration scenarios     | 132           |

|          |         |                                                           |               |

| 4.3.3   | Tool i | integration examples                                             | 133 |

|---------|--------|------------------------------------------------------------------|-----|

| 4.3.3.1 | SV     | G View                                                           | 133 |

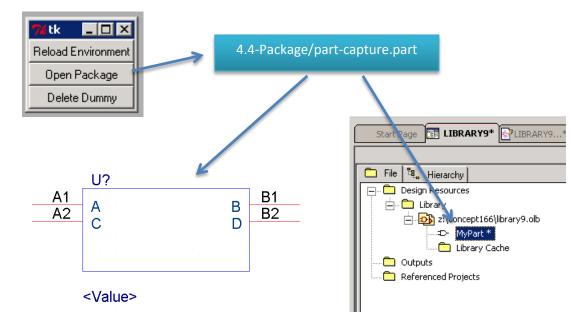

| 4.3.3.2 | Ca     | dence capture integration                                        | 136 |

| 4.3.3   | 3.2.1  | Large part support: usage example of the generic group attribute | 137 |

| 4.3.4   | Outlo  | ook and integration in actual work                               | 138 |

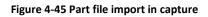

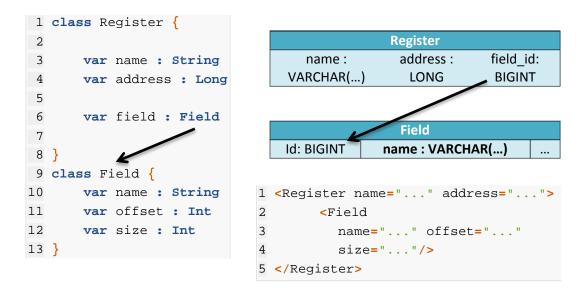

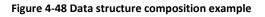

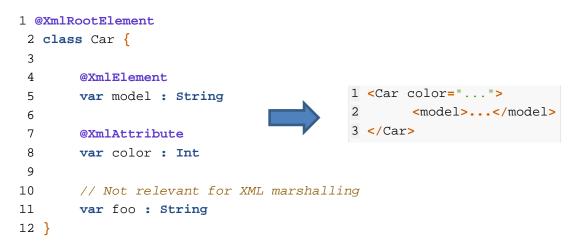

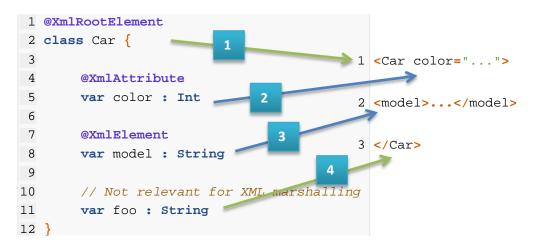

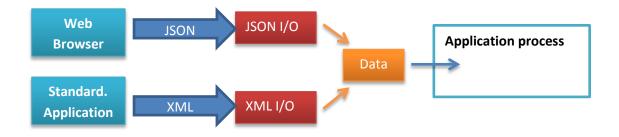

| 4.4 OOX | (00: A | dynamic XML data binding interface                               | 139 |

| 4.4.1   | Data   | binding for XML                                                  | 139 |

| 4.4.1.1 | Au     | tomatic data model generation and validation                     | 140 |

| 4.4.1.2 | Fla    | t binding                                                        | 142 |

| 4.4.1.3 | Ар     | plication Binding                                                | 143 |

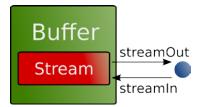

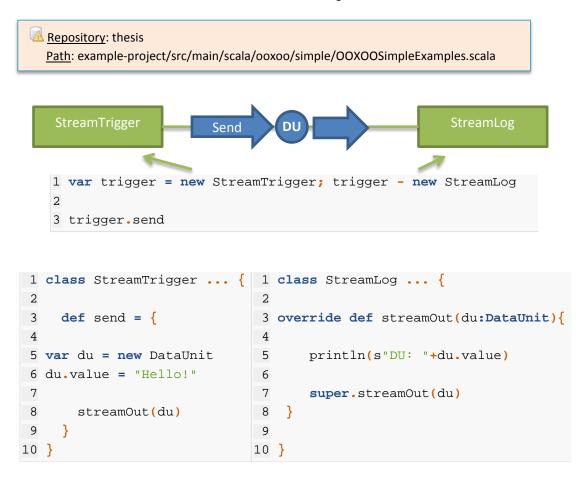

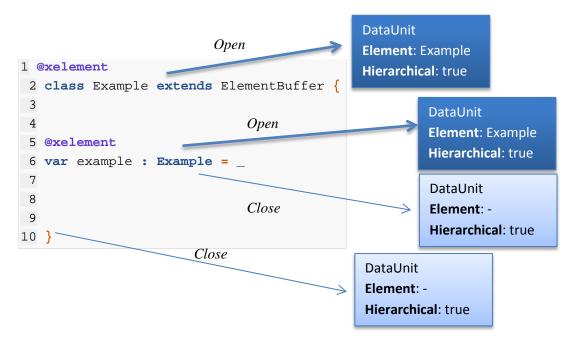

| 4.4.2   | Dyna   | mic hierarchy                                                    | 144 |

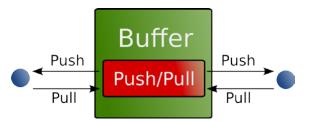

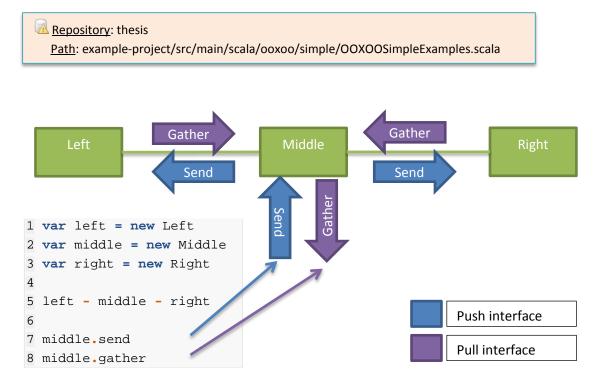

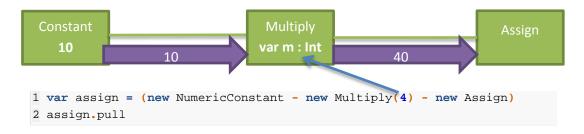

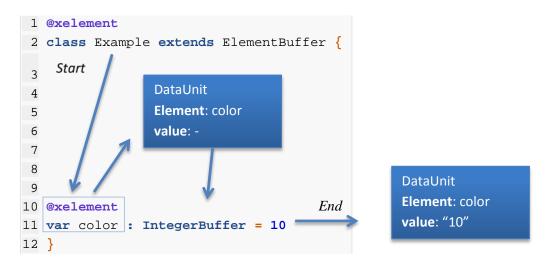

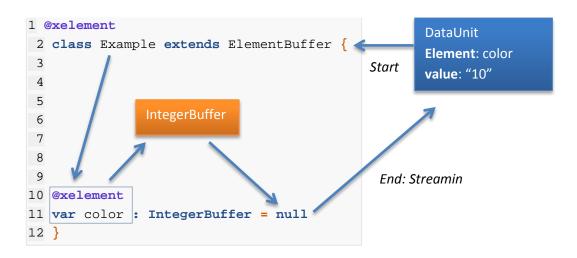

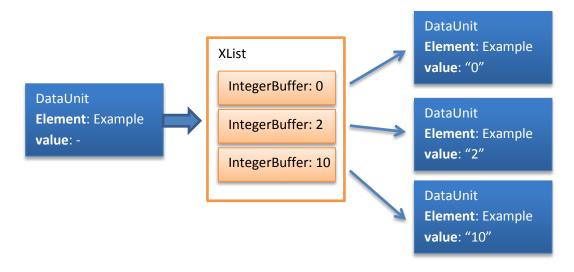

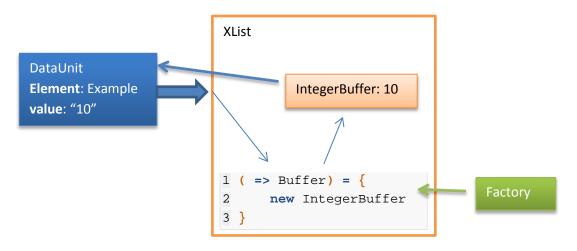

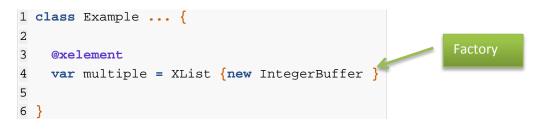

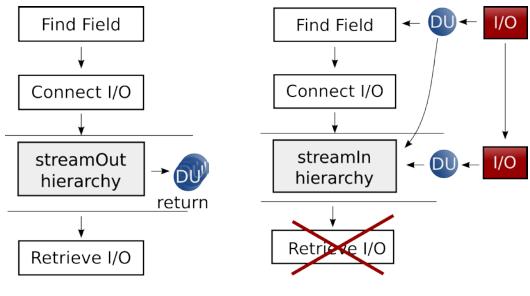

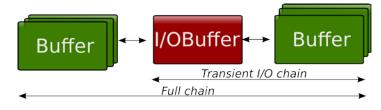

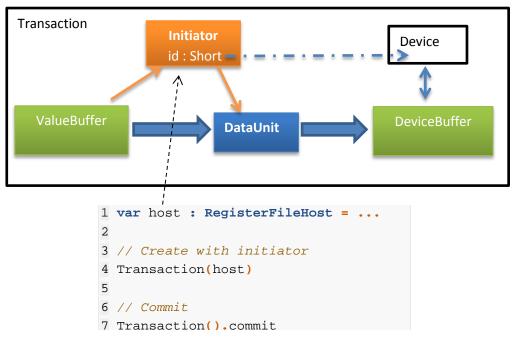

| 4.4.2.1 | Bu     | ffers and Data units                                             | 145 |

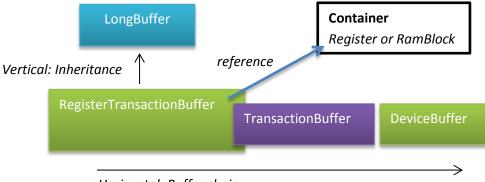

| 4.4.2   | 2.1.1  | Buffers                                                          | 146 |

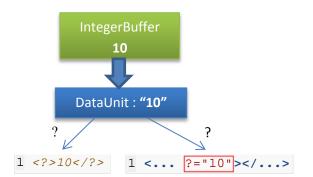

| 4.4.2   | 2.1.2  | DataUnits                                                        | 148 |

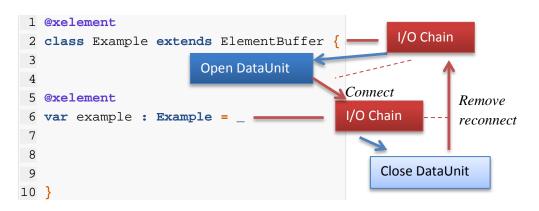

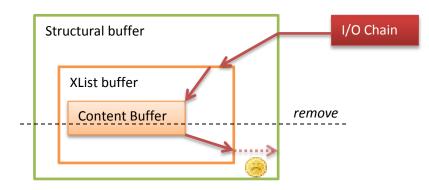

| 4.4.2.2 | Ele    | ment Structural Buffer                                           | 148 |

| 4.4.2   | 2.2.1  | Simple Data handling                                             | 148 |

| 4.4.2   | 2.2.2  | Hierarchy handling                                               | 150 |

| 4.4.2.3 | Th     | e simple data types issue                                        | 150 |

| 4.4.2   | 2.3.1  | Implicit conversion trap                                         | 151 |

| 4.4.2.4 | Со     | llections                                                        | 152 |

| 4.4.2   | 2.4.1  | DataUnit production                                              | 153 |

| 4.4.2   | 2.4.2  | DataUnit consumption                                             | 153 |

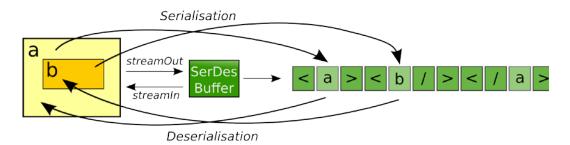

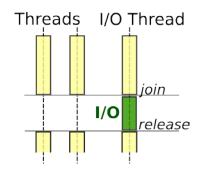

| 4.4.3   | Mars   | halling and un-marshalling: the I/O layer                        | 155 |

| 4.4.3.1 | На     | ndling non hierarchical buffer levels: the collection case       | 158 |

| 4.4.3.2 | XIV    | 1L I/O                                                           | 159 |

| 4.4.3.3 | JSC    | DN I/O                                                           | 160 |

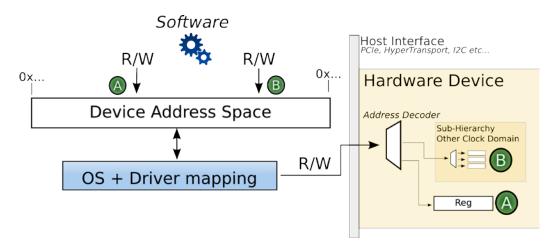

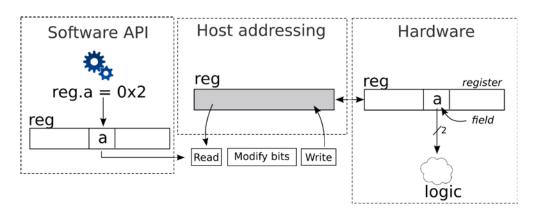

| 4.4.4   | Regis  | ter file application interface                                   | 161 |

| 4.4.4.1 | Re     | gister file software interaction characteristics                 | 161 |

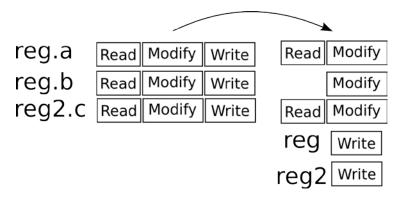

| 4.4.4   | 4.1.1  | Read-Modify-Write support                                        | 161 |

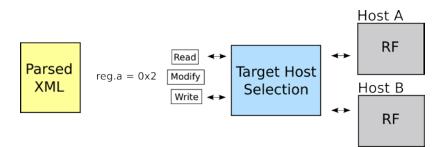

| 4.4.4   | 4.1.2  | Scalable Multiple register file access                           | 162 |

| 4.4.4.2 | The    | e Register file OOXOO interface                                  | 162 |

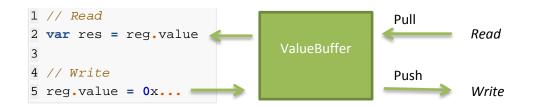

| 4.4.4   | 4.2.1  | The value buffer                                                 | 163 |

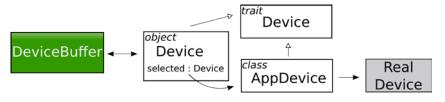

| 4.4.4   | 4.2.2  | The Device Buffer                                                | 164 |

| 4.4.4   | 4.2.3  | The Field value                                                  | 165 |

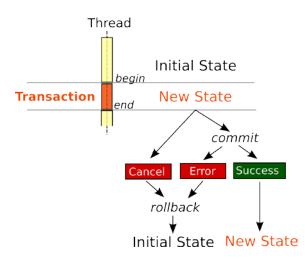

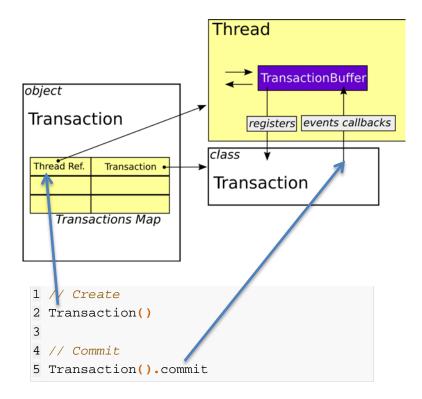

| 4.4.4.3 Th                 | ne generic transaction extension             | 165 |

|----------------------------|----------------------------------------------|-----|

| 4.4.4.3.1                  | The transaction buffer                       | 166 |

| 4.4.4.3.2                  | Transaction State management                 | 167 |

| 4.4.4.3.3                  | Target host selection: Transaction initiator | 167 |

| 4.4.4.4 Fir                | nal ValueBuffer configuration                | 168 |

| 4.4.5 Conc                 | clusion                                      | 169 |

| 5 Conclusion and           | d Outlooks                                   | 171 |

| 5.1 Abstractio             | on in hardware description languages         | 172 |

| 5.2 Design flo             | ow libraries open sourcing                   | 174 |

| Appendix A. Software setup |                                              |     |

# **1** Introduction

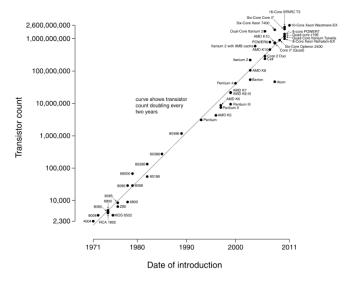

ollowing the famous Moore's law on the growth of transistor count in an integrated circuit, the complexity of hardware designs has grown over time, as more fields of application developed: microcontrollers, mobile processors, graphics processors, application specific co-processors etc...

Microprocessor Transistor Counts 1971-2011 & Moore's Law

Figure 1-1 Moore's law applied to microprocessor transistors count [1] (Logarithmic scales)

Meanwhile, complexity in terms of number of transistors also means complexity in terms of number of features that are integrable in a system on a chip (SOC), and by extension, it impacts a project's design space in terms of:

- ✓ Architecture specification

- ✓ Integration of components

- Testing and verification

- ✓ Feasibility

- ✓ Human resources and time to market costs

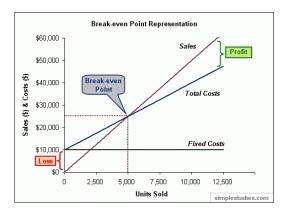

This last criterion being quite prominent, especially in the context of a startup, as business financing entities tend to look for a rapid high margin return on investment, underscoring the need to reach the breakeven point [2] [3] as fast as possible.

Figure 1-2 Break-even point representation [3]

This surge in complexity has forced research and industry over the past 25 to 30 years to develop new tools, languages and methodologies to help tackle issues at each step in the design flow, a few examples being:

- ✓ Digital Hardware design input

- o Hardware description language (HDL)

- o Finite state machine editors

- o Linting etc...

- ✓ Simulation and verification

- o Simple simulation

- o Advanced verification

- ✓ Technology mapping

- o Synthesis

- o Timing analysis

- Signal integrity

- Power analysis

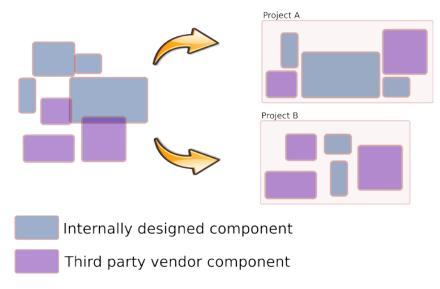

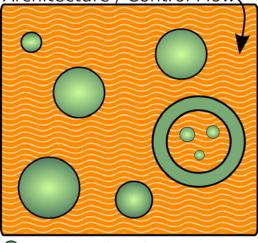

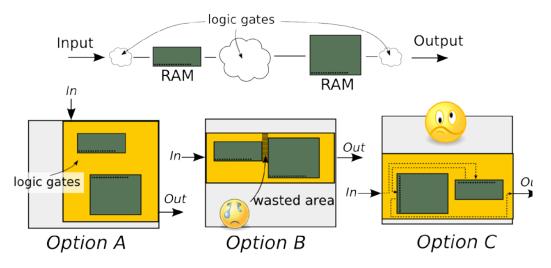

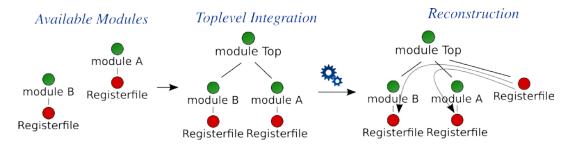

On the other hand, with the help of these new design methodologies, sub-designs became more and more reusable, allowing the optimisation of the engineering costs by sharing them over multiple product lines, and/or buying some from third parties (they are then called IP Blocks), as illustrated in Figure 1-3.

Figure 1-3 Component reusability in designs

Therefore, more than ever, engineering teams have to implement features that are likely to be integrated in different designs and mapped to various technologies, while keeping up with the constraints of all possible configurations.

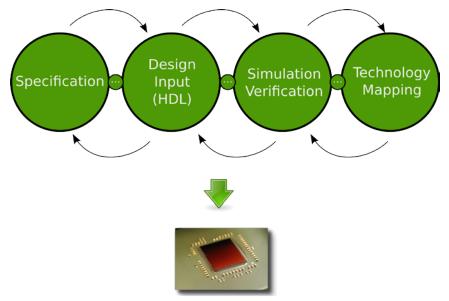

In Figure 1-4, some of the main design flow steps to produce an integrated circuit are presented (each also embeds its own sub-flow). We can see that each stage is connected to its previous and next through an evaluation loop, building a transversal dependency across the processes. This leads the engineering teams to facing a great variety of software to handle each step from hardware design input to technology mapping, each of them with varying degrees of compatibility to its successor/predecessor.

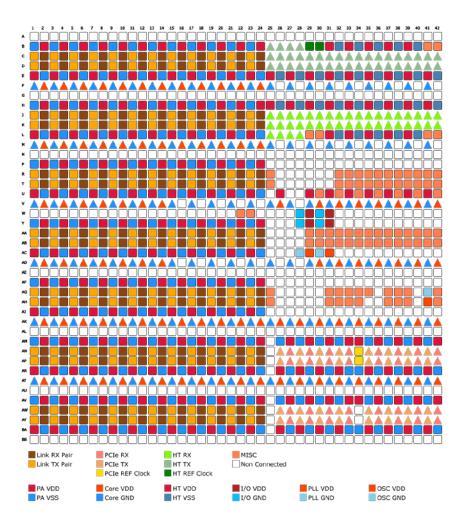

Package with flip-chip mounted die

Figure 1-4 Design Flow example with major steps to produce an integrated circuit

Typically, designers try to leverage this issue by creating various sets of custom software (simple scripts for most), quite often written in a different language, or even develop some Domain Specific Languages (DSL), that only have a localised usage, and little interoperability.

Although modern software design tends to maximise function reusability, hardware designers tend to throw suspicion at software experts, who usually try to create a perfect tool that solves too many problems. Probably they are right to do so, as the typical cost and complexity of industrial tools does not give credit to the idea of constraining any design flow under a single solution, creating an illusion of freedom by enslavement.

# 1.1 Stakes

As seen so far, hardware designs are exposed to quite complex and fast evolving design flows, and have to meet multiple constraints while minimizing redesign needs, justifying the difficulty to offer efficient tools able to follow a project along all its implementation phases. But moreover, software concepts trying to offer "one tool to rule them all" are unrealistic, and contra-productive in regard to modern software designs. What we are looking for would be then to be able to:

- ✓ Bridge the gap between abstract design concepts (Top-Down view) and implementation (Bottom-Up construction)

- ✓ Easily specialise the design as the requirements are getting clearer

- ✓ Efficiently analyse the design at each flow step, to outline refinement iteration to be done based on specification changes, and specification feasibility issues.

We can try to sum up those issues in one question:

# Can we marginalise the implementation of a specification, while consistently guaranteeing behaviour and feasibility?

In this thesis, we propose a set of open software design principles, inspired from functional programming paradigms, applied to hardware design flow challenges, in an attempt to raise the global design abstraction level, while not stealing control from the designer. Although focus will be given to the TCL programming language, which is present in most of the Electronic Design software in the industry, and the Scala programming language for hardware-software interfacing, the presented concepts are meant to be translatable to other technologies.

This work is structured around a presentation of the core concepts of functional programming and domain specific language development, which lead to defining a methodology for creation of Embedded Domain Specific Languages.

In a second time, some functional programming extensions to the TCL language are introduced to support Embedded Domain Specific Languages in TCL.

Finally a set of chosen applications covering digital hardware design input, physical floorplanning for integrated circuit, and high-level software interfacing are presented.

For readers not familiar with Functional Programming, it is advisable to focus on the presented applications, and come back to the lower level concepts iteratively.

# **1.2 Contributions**

This work shows how learning from functional programming and domain specific language development allowed us to build very creative and elegant software solutions to create abstract programming interfaces inside the TCL interpreter.

The choice of the TCL dynamic language offered direct interoperability with existing industry software, showing how applications could be developed to nicely integrate inside existing design flows.

Beyond the applications, the proposed abstract methodologies for embedded domain specific language development can be used as basis to develop abstract programming interfaces, not only using the TCL language but in every possible context.

The architectures of the presented applications moreover prove that flexibility in software can be reached by reusing generic building blocks, and actually pushing the application-specific behaviour mostly to the binding logic layers.

# 2 Functional programing and domain specific languages

he guiding thread of this thesis is the development of software design paradigms that are flexible enough to be adapted to design flow specifications. In this perspective, the technological choices made when developing a software component have an impact on the flexibility degree that can be reached. Indeed, three main criterions will have a major impact:

- 1. <u>Language features</u>: Is the base programming language good enough to limit the human costs of development and maintenance?

- 2. <u>Acceptance</u>: In the case of programming interfaces, are the users going to be willing to use them, or be reluctant to learn new paradigms and syntaxes.

- 3. <u>Integration</u>: If multiple software pieces must work together, how well are they going to integrate with each other? Are we going to need extra data exchange formats and protocols to cover incompatibilities?

Starting from imperative programming knowledge (C/C++, Java etc...), we explored alternative ways to design programming interfaces that would closely match design issues encountered by hardware designers. Classical C/C++ or Java library development is a way to go, but they provide a low level programming view to solve a problem, and are not very well adapted to the flexibility required by top level views of designs. Moreover, non-software experts tend to be very reluctant to verbose languages and to the usage of standard software programming patterns.

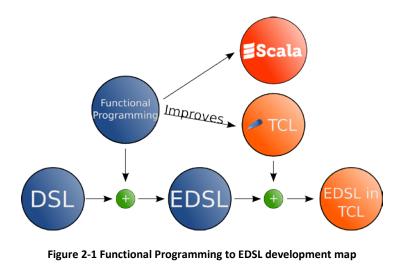

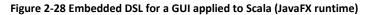

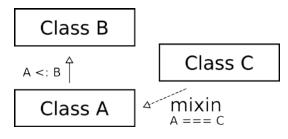

Figure 2-1 shows the development path followed along this work. Through experimentations with Domain Specific Language (DSL) design, which have the chance to correctly answer issues 1 and 2, and learning about functional Programming, we developed a way to create programming interfaces called Embedded Domain Specific Language (EDSL), which address the three mentioned challenges. The main implementation focus will be set in chapter 3 on the TCL programming language, as it is the first-choice language for most concrete applications presented in chapter 4. The functional language Scala will be used as an existing technology to support and illustrate the design patterns ported into TCL.

# 2.1 Imperative and Functional Programming styles

istorically, computers were designed to perform computations in an automated and faster way than humans could on their own. That is to say, basically solve mathematical problems. Programming languages emerged as a humanunderstandable way to describe some computations to be performed by computing units, just like scientists write down and solve equations. However, those computing units (commonly called processors) can't understand human languages, as they are only electric circuits which can process a simple instruction (in the form of binary digital signals [4]) and produce outputs for the next ones. This instruction format is called a machine code, and modern processors as well as the first one ever build still work by running such machine code.

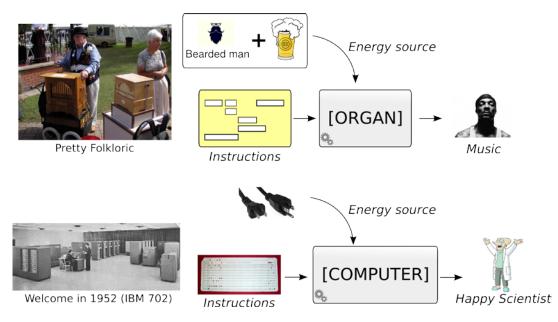

An interesting analogy to this concept, presented in Figure 2-2, can be made with fairground or street mechanical organs. They use a "mechanical" representation of music notes, taking the form of a barrel or a punchcard music book, which triggers actuators producing the desired note. The first computers were also built the same way, at the time when computer programs would be translated to punchcards, then run by the machinery to produce computation results.

Figure 2-2 Computers and punchcards organs are not so different

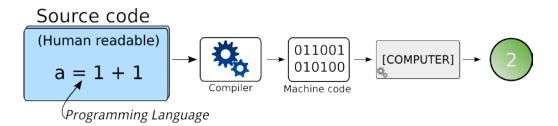

Because the machines they are running on have special requirements related to their architecture, the instructions present at the machine code level are not tightly related to the initial problem description. Programming languages must therefore be compiled from a human understandable text representation to an executable machine code format, as presented in Figure 2-3.

Figure 2-3 Simplified compile-execute flow for a program computing "1+1"

This is where the story of computer programming languages begins. The goal of a good programming language is to allow the user to clearly and efficiently write a computer program, while compiling to the most efficient possible instruction set for the target machine (we define efficiency by the amount of instructions required for a computation and the inducted power consumption)

Therefore, a trade-off at the language design has to be made, so that it will remain easy enough for the compiler to understand and produce optimal machine code. The first reference book on compiler design cover (Figure 2-4, from the second edition) [5], featured a dragon fighting with a knight, illustrating the language syntax and associated compiler design challenge

Figure 2-4 "Compilers" book [5] cover

#### 2.1.1 The Imperative programming style

The first developed languages were designed to mirror the sequential control flow of a program, in each of its step. This model is called *imperative programming*, and mostly requires the programmer to describe the computation in its various steps that produce a desired result. This approach makes programming quite close to the underlying computing architecture and machine code instructions (which in turn are all the steps the machine has to go through to produce the desired output), and keeps compiler design complexity acceptable.

To describe all the steps of a computation, the user has to manage two aspects:

- ✓ The state, which is represented by data values hold in memory which allows keeping track of the computation flow.

- $\checkmark$  The instructions, which work on the state and update it.

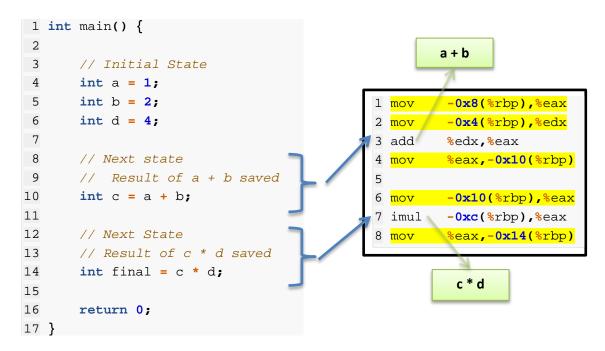

Data and instructions are the base building block of the original Von Neumann computer architecture and its extension the Harvard architecture, in which instructions are executed on data as fast as possible. By expressing the data and instruction flow explicitly, the language limits the possible semantic abstraction, and thus is easily to optimise to run fast on the underlying processor. To be more concrete, we are going to analyse a trivial program written in C [6], which performs two operations: c = a + b followed by final = c \* d. The first equation will need an initial state which is defined statically, but could be requested from a user interface. The source code is shown in Figure 2-5 on the left, while on the right side the actual *machine instructions* generated by the compiler (GCC [7] on an x86-64 [8] architecture) is presented. We can see that both source code and machine instructions follow the same flow. On the machine side, **add** (+) and **imul** (\*) are the actual computations performed by the processor, while **mov** performs memory copies and relocations which manage the state in the computation machine (yellow highlights).

Figure 2-5 Imperative C program with associated machine instructions excerpt

This imperative programming style is the most widely used, and many programming languages are designed following this logic. The piece of code we just used as illustration is of course not useful for real applications, and most languages offer advanced features like object-oriented programming [9] and complex design patterns [10] to structure a program and scale it efficiently as it grows.

#### 2.1.2 The Functional programming style

We just defined two aspects of an imperative program: State and Instructions. In other words, we can say that we had to specify:

- 1. What do we want to reach? This is the final = (a + b) \* d specification.

- 2. How do we reach the goals? This is the way we wrote the source code, i.e. the control flow.

The idea behind Functional Programming is that the user only focuses on writing the composition of functions that will lead to a result, just like solving equations. A function, as pure mathematical object, therefore only produces an output based on a set of immutable inputs. This way, the source code can more closely express the desired result and be safer to manipulate by avoiding state management, like temporary results saving, and forbidding side effects (a function cannot modify its input arguments or surrounding context).

Historically, this concept goes back to the 1930's and research on lambda ( $\lambda$ ) calculus. First published by A. Church [11] and extended by A.M. Turing [12],  $\lambda$ -calculus defines a representation of computable functions as anonymous terms, which can be composed to form transformation expressions. Programming models and  $\lambda$ -calculus are extensively presented by Kluge [13], we will only give here the basic notation elements which are relevant to understanding most of  $\lambda$ -calculus' implications in functional programming.

If we consider an algebraic function, defined by an expression expr applied to a set of input parameters  $x_1 \dots x_n$ , it can be noted :

$$f(x_1 \dots x_n) \to expr$$

The general form of such a function in  $\lambda$ -notation is:

$$f = \lambda x_1 \dots x_n . expr$$

short  $\lambda x_1 \dots x_n . expr$

- $\checkmark$   $x_1 \dots x_n$  are variables representing the input parameters of f

- ✓ *expr* is the function body, which may contain references to the  $x_1...x_n$  input parameters, called free occurrences of  $x_1...x_n$

- λx<sub>1</sub>...x<sub>n</sub> is called the binder for the free occurrences of x<sub>1</sub>...x<sub>n</sub> present in *expr*.

It defines the names of variable occurrences in *expr* which can be bound to an input parameter.

Applying the function to some input parameters is written:

$$(\lambda x_1 \dots x_n . expr arg_1 \dots arg_n)$$

This notation can be further refined in a n-fold nested form, or curried form, named after Curry and Schönfinkel who introduced it in [14], [15]. They stated that a function f of n arguments can be rewritten as a nested call to n functions of each 1 argument:

$$f = \lambda x_1 \dots x_n . expr = \lambda x_1 \dots \lambda x_r \dots \lambda x_n . expr$$

for  $n \le r$

The latter has two important technical implications, both of which are presented using concrete examples in 2.2:

- ✓ Partial function definitions: It is possible to apply f to r arguments, with 1 ≤ r < n. The result is a partial function of f, to which the remaining 1 ≤ r' ≤ (n - r) arguments can be later applied. For example, a simple addition can be performed in two steps:

- Create the curried form of  $\lambda abc. (a + b + c) : \lambda a \lambda b \lambda c. (a + b + c)$

- Apply only two input arguments to it:  $temp = (\lambda b \lambda c. (a + b + c) 2 3)$

- Apply the last input argument to *temp*:  $(\lambda a (a + 2 + 3) 4)$

- o The result is 9

- ✓ <u>Function arguments currying</u>: Following the same rules, the formal notation of a function definition can be revisited to:

$$f(x_1 \dots x_n) \rightarrow expr == f(x_1)(x_2)(\dots)(x_n) \rightarrow expr$$

✓ <u>High-Order functions</u>: Each of the curried  $\lambda_r$  functions for r < n is a binder for the  $x_r$  variable, and takes as body the next  $\lambda_{r+1}$  function to be applied. A function which takes another function as input argument is called a High-Order function.

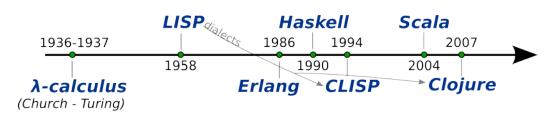

The first clear statement that posed Functional Programming as a hierarchy of function composition, in opposition to imperative programming, was made in 1977 by John Backus in "Can programming be liberated from the von Neumann style?: a functional style and its algebra of programs" [16], although the very first language that was inspired from  $\lambda$ -calculus is LISP [17], first released in 1958 for the IBM 704 (one of the world's first language together with Fortran).

LISP influenced many programming languages, and is itself at the origin of various forked languages, which sometimes remerged over time. The most notable and still active ones are Common LISP [18] (CLISP, ANSI specification in 1994), Scheme [19] (1975) and Clojure [20] (2007). As we will see later, LISP base concept also inspired TCL [21], presented in 3.1. Other languages inspired from functional concepts are quite popular and still active although less visible to the masses, like Haskell [22] (~1990) or Erlang [23] (~1986), the most recent one being Scala [24](2004), presented in 2.2.

Figure 2-6 Chronology of a few functional programming languages

#### 2.1.2.1 An example in CLISP

To give a glimpse on functional programming style, we will reproduce the example of Figure 2-5 using the Common LISP language. We thus need to adapt our source code to define the composition of functions that describes the computation:

✓ Formulate the computation function (a + b) \* d in code. LISP uses a *parenthesized polish prefix notation*, which means that operators precede operands. In our case, the operators are + and \* , with operands a b c, thus (+a b) for the addition and (\* result of addition d) for the multiplication. Composition precedence is achieved by parenthesizing:

1 (\* (+ 2 2) 4)

- ✓ In pure functional programming style, there is no state. However, if we want to use variables in our equation, we can do so:

- 1. First replace constants by variables

1 (\* (+ a b) d)

2. Compose the function with the let function, which binds variables to constant values when required

```

1 (let

2 ((a 2) (b 2) (d 4))

3

4 (* (+ a b) d)

5 )

```

Illustrating the concept of lambda function in CLISP is also very easy, as it is natively supported. We can rewrite our example in the following way:

1. Bind the computation formula to a function definition:  $(x, y, z) \rightarrow (x + y) * z$

1 (lambda (x y z) (\* (+ x y) z))

2. Apply the function to a set of input parameters called a, b and d

1 ((lambda (x y z) (\* (+ x y) z) ) a b d)

3. Compose the lambda with the let function, which binds variables to values to have a state to work on. Here *a* is set to 2, *b* to 4 and *d* to 8.

```

1 (let

2  ((a 2) (b 4) (d 8))

3

4  ((lambda (x y z) (* (+ x y) z) ) a b d)

5

6 )

```

4. The result of the let call is thus the result of the lambda applied to 2, 4 and 8, so 48.

### 2.1.2.2 Recursive function call

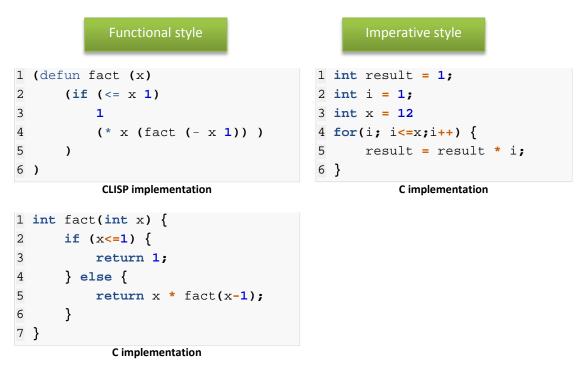

Recursive function call is a classical concept for all kind of programming style, and is a base building block for functional programming. The factorial function, a typical illustration example, is easy to write both using functional recursive calls and imperative style:

- Recursive decomposition of factorial:  $x! \rightarrow (x-1)! * x$

- Sequential decomposition of factorial:  $x! \rightarrow 1 * ... * (x n) * ... * x$ ; 1 < n < x

Recursive versions in LISP and C are presented in Figure 2-7, as well as imperative style C implementation using a loop (sequential decomposition)

Figure 2-7 Functional and imperative style factorial

#### 2.1.2.3 List/Elements Array processing

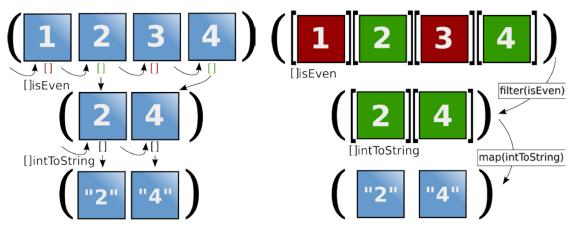

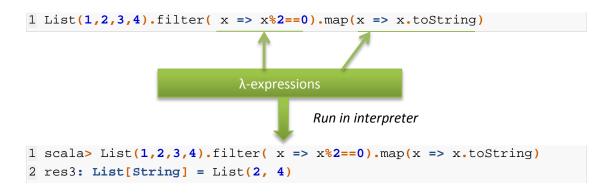

Collections processing is a classical example of how functional programming can be used to write code in a different way. It is indeed very common to work on collection of data in order to find elements matching specific criterions, extract parameters (in case of collections of structured data) etc.... To take a simple example, given a list of numbers, we would like to extract the subset of the even values, and represent them as strings. We define two high-order functions to perform these tasks:

1. <u>Filter</u>: returns the elements of a list, for which the  $\lambda$  function applied to them returned true:

$$f(\lambda x. expr \{y_1 \dots y_n\}) \xrightarrow{yields} \{y'_1 \dots y'_r\}; \ r \le n \ for \ each \ (\lambda x. expr \ y_v \ ) == true$$

2. <u>Map</u>: returns a list, whose each element is the result of applying a  $\lambda$  function to the input list:

$$f(\lambda x. expr, \{y_1 \dots y_v \dots y_n\}) \xrightarrow{yields} \{y'_1 \dots y'_v \dots y'_n\}; \ \forall v \ y'_v = (\lambda x. expr \ y_v)$$

In imperative programming style, the control flow would have to be implemented per hand as in Figure 2-8, while in functional style, only the composition of functions matters (Figure 2-9):

$$\forall x = \{y_1 \dots y_v \dots y_n\}; f(x) \xrightarrow{yields} map(intToString, filter(isEven, x))$$

Figure 2-8 List filter and map imperative view

Figure 2-9 List filter and map functional view

A data-flow oriented representation of this composition can be achieved with an Object-Oriented programming interface. A concrete example is shown in 2.2, and refines the previous formula as:

$$\forall x = List \{y_1 \dots y_v \dots y_n\}; f(x) \xrightarrow{yields} x. filter(isEven). map(intToString)\}$$

#### 2.1.3 Discussion

As we have just seen, functional programming abstraction level is very interesting, as it allows the user to write the solution to a particular problem the way it should be described, instead of having to go down specifying the implementation's control flow. However, wide adoption of pure functional programming has not already happened for various reasons:

The control flow is hidden

The natural way to create a software still consists in defining the various features it has to offer, and how they relate to each other. This orchestration requires a minimal state management. Sometimes computations are also very complex, and need an explicit state management to stay understandable by the programmer himself, but also by other human beings. Control flow and computations cannot completely be hidden from each other.

Figure 2-10 "Basic modus of operation of all computational models" [13] p.75

For example, the language Erlang tried to solve this issue by proposing an implementation of an "Actors" model, where some Actor objects exchange messages to trigger reactions [25].

✓ Performance

Functional Programming basically relies on stack execution, as it proceeds by reducing a function tree. Languages like LISP additionally featured paradigms like runtime type checking, which requires an overhead to check function calls arguments before the actual computation. In early computer science days the hardware was slow and expensive, and this lead to requiring the development of machines dedicated to functional languages, like the LISP machine [26]. For this reason, most programmers desired, or had to keep control of the execution flow of their software to optimise performances, and stick to imperative languages like C. Moreover, the concurrent standard Von Neumann architectures became fast

and cheap, and allowed running LISP programs even faster than dedicated hardware.

✓ Syntax

A strength of imperative style programming is still that reading the code provides understanding of the direct execution flow. In functional style, the result is provided by the composition of functions, which makes it more difficult to understand if the code is large, even if the formal definition is more powerful.

Moreover, the syntax definition is often a challenge for most users. Dialects of LISP are very uncomfortable to read due to the prefix notation. So

stated Alan Kay in his Ph.D. Thesis "programs written

Figure 2-11 Letter from Burniburiach to Amenhotep IV [66]

in them look like King Burniburiach's letter to the Sumerians done in Babylonian cuneiform" [27]

To summarize, computation algorithms are better expressed in functional style, which in turn is less adapted to architecture definition and orchestration in larger designs. In facts, strict and efficient software design always tries to avoid state management and side effects at the lowest levels, to maximize code stability and reusability. Over time though, some imperative languages started improving their compilers to support functional style constructs. A lot of developers are indeed already applying functional concepts to their imperative code.

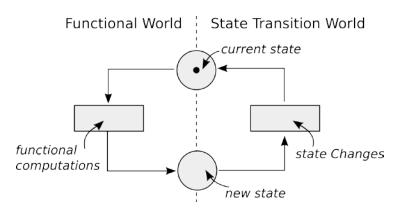

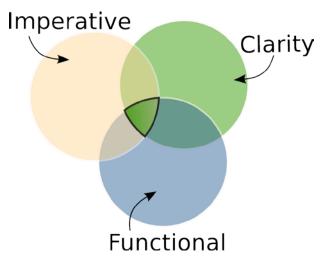

A trend can actually be seen in merging of imperative and functional styles, where functional features are used to implement elegant abstraction to problem statements, while imperative state management remains the glue binding the application world together (Figure 2-12).

Functional code

Figure 2-12 Functional islands in an imperative style ocean

Among the most popular languages following this path, we can mention:

- ✓ Python [28], which is very popular, although the functional features are limited and not very attractive as they were added on the existing language definition

- ✓ Groovy [29] has a good visibility, it runs on the Java virtual machine and was designed from ground up with functional features in mind.

- Even some newer languages, although not designed with functional programming in mind, naturally offer some features. An example of which is the experimental Rust language from the Mozilla foundation (it still may "eat your laundry" according to the official website) [30].

The most visible one over the past few years though is Scala, which we are going to use in section 2.2 to present some important functional programming paradigms applied to an imperative-looking language.

# 2.2 Merging styles: The Scala programming language example

Created in 2001 (first released in 2004) at the Programming Methods Group [31] of the École Polythechnique de Lausanne (Switzerland) by Martin Odersky's Team, Scala stands for "Scalable Language" [24]. It is a new programming language whose main design road is to unite imperative with functional programming paradigms introduced by earlier languages (LISP, Haskell, SmallTalk etc...).

The starting point of Scala's design is based on three assumptions:

- ✓ The programmer writes too many keywords for obvious statements (so-called boilerplate code).

- ✓ Functional paradigms can be integrated in the language in an elegant way

- ✓ One can Import elegant concepts from existing languages and improve them, without reinventing something totally new each time.

Scala features its own compiler which mainly targets the Java Virtual Machine (JVM) for runtime, and allows taking advantage of the wide base of existing Java libraries and projects. It can be discussed if Scala could be the next Java, but the latter follows its own path, and the basic syntax of Scala can be repulsive for programmers used to state of the art C/C++ or Java-like languages. In the next sections, we are going to present a few features of Scala which proves the flexibility it brings to traditional imperative programming, without requiring the user to think in an unthinkable way.

## 2.2.1 Type definition and Type Inference

## 2.2.1.1 Type Inference

In Scala, the data type definition of a term follows it's name, unlike most usual imperative languages (C/Java etc...).

The *TERM* can be:

- $\checkmark$  A variable : *var NAME* : *TYPE* = *expr*

- $\checkmark$  A value (or constant) : *val* NAME : TYPE = expr

- ✓ A function definition: def NAME (ARGS) : TYPE = expr

A type checker typically checks the equivalence of type between the term specification, and the expression: type(expr) == TYPE. By adding a type inference mechanism, the TYPE specification can be dropped and delegated to the type of the expression: type(expr) $\xrightarrow{yields}$  TYPE. The common term specification becomes:

A few concrete examples for simple numerical data types are presented below (simply run in the Scala interpreter):

```

1 scala> var a : Int = 42

2 a: Int = 42

3

4 scala> var a = 42

5 a: Int = 42

6

7 scala> var b = 42L

8 b: Long = 42

9

10 scala> var c = 42.0

11 c: Double = 42.0

```

## 2.2.1.2 Implicits

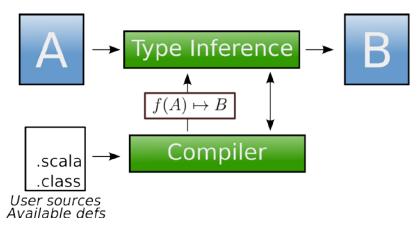

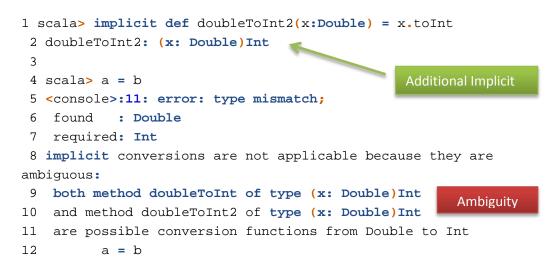

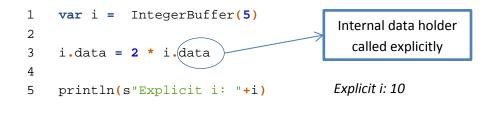

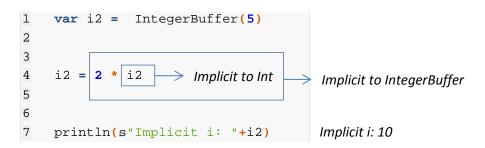

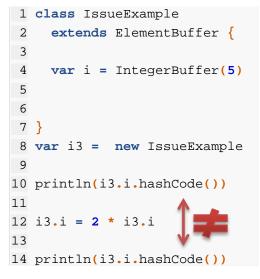

The type inference mechanism in Scala is not static, as presented in Figure 2-13, and can be enriched by user provided conversion functions, called *implicits*, which simply take an input of type A to produce an output of type B (i.e. specifies an  $A \rightarrow B$  conversion). This feature is of great use to create flexible language interfaces, although it can sometimes lead to bad designs if too generic and possibly clashing implicit conversion functions are defined.

Figure 2-13 Type inference with dynamic type conversion

To illustrate this mechanism, let's consider the data types Integer and Float. The Integer  $\rightarrow$  Float conversion is trivial, as an Integer can be represented as a floating point number with a mantis set to 0. The other way round is not possible, and requires an explicit rounding. To simplify an application where a rounding to the lowest integer would be the rule, we could define an implicit. Figure 2-14 provides the illustration, with an invalid Double to Integer assignment on the left-hand side made valid on the right-hand side by the implicit definition.

Figure 2-14 Double-to-Int implicit type inferring example

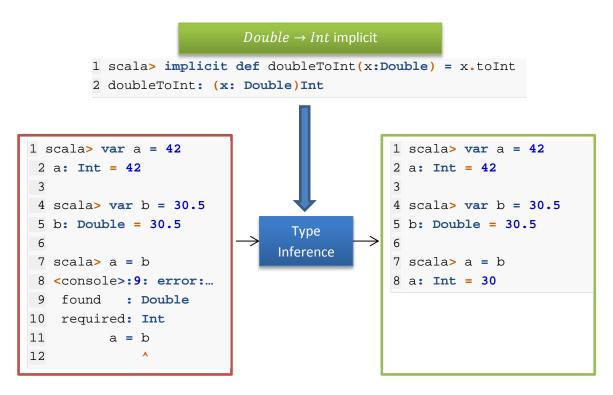

But if another application part or a library had decided to provide its own inference function, we might run into ambiguity. In the following example, the type inference mechanism cannot decide if the *Int* to *Double* conversion should be performed by the *doubleToInt* method, or the newly added *doubleToInt*.

Figure 2-15 Double to Int ambiguous erroneous implicit type inferring

#### 2.2.2 Closures and high-order functions

#### 2.2.2.1 Anonymous functions

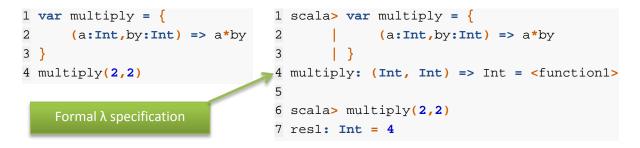

Functions are in functional programming "first class citizens". They can be declared anonymously, as  $\lambda$ -expressions (i.e. inline without the **def** keyword), and be considered as simple values. The Scala syntax follows the function definition presented in 2.1.2 ( $\rightarrow$  is replaced by  $\Rightarrow$ ):

$$f = \{ (args) \Rightarrow expr \}$$

The following example creates a  $\lambda$  expression which multiplies two integers:

#### 2.2.2.2 Closures

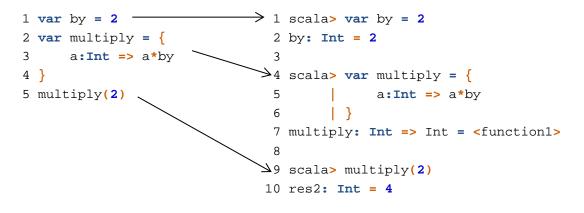

Closures are a key construct in functional programming. A good and understandable definition can be given based on [32] and [33]:

**Definition 2.1** A closure is a  $\lambda$ -expression associated with an environment, which may contain occurrences of variables bound to the environment, not to the  $\lambda$  binder (i.e. the input arguments)

This next example defines a  $\lambda$ -expression which multiplies an integer by a coefficient defined in the environment surrounding the closure (*by* is not a *multiply* input parameter):

# 2.2.2.3 High-order functions

**Definition 2.2** A high order function is a function which takes a  $\lambda$ -expression (i.e. another function) as one of its input arguments, or returns one as result.

A very recurrent example is encountered when processing collection of elements. In Figure 2-16 we implemented the list processing example from 2.1.2.3.

Figure 2-16 List filter and map in Scala

# 2.2.3 Currying and Partial Functions

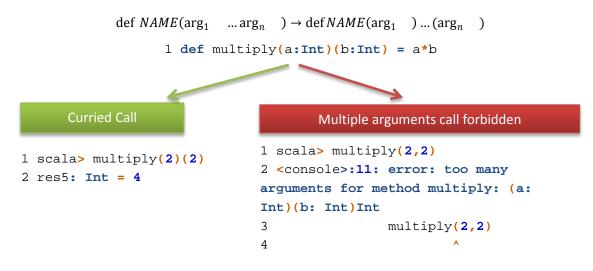

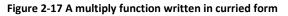

Currying is implemented in Scala and allows splitting the input arguments of a function definition to take the form of nested call, as presented in 2.1.2.

Figure 2-17 presents the previous multiply function definition example rewritten in a curried form. The other consequence of currying that was mentioned earlier is that it allows using partial function calls:

However a return on experience showed that partial calls are rarely used, but can be very convenient to raise the abstraction level by making a curried function call with default values for the first arguments, while hiding them from the final call. One could write a multiply by two function, which would be a partial call to multiply with a = 2, waiting for the final call to have *b* bound. As can be seen in figure, the multiply by 2 function is not a new definition, but a partial from the generic multiply definition.

```

1 scala> def multiplyBy2 = multiply(2)_

2 mby2: Int => Int

3

4 scala> multiplyBy2(4)

5 res13: Int = 8

```

# 2.2.4 Discussion

Scala being a young language, some critics have been raised against it. One of the most prominent, which can be sensed after reading this section, is that the compiler gets assigned a lot of tasks, by trying to support many features. Type checking and inference slows down compilation and can lead to confusions, real generic runtime language reflection is a pain and not clearly specified (users have to use the standard Java introspection instead) and so on...

On the other hand, the language design choices are clearly targeted at giving the developer the tools he needs to use and not defining constructs which reduces errors possibilities by constraint. More pressure is put on the designer to think about clear and correct way to write code, rather than solving problems using a syntax not adapted and not adaptable. The science in Scala resides in finding the sweet spot between imperative flow, functional constructs and code clarity (which impacts robustness).

Figure 2-19 Finding the code quality sweet-spot in Scala

A Typical example for this is the type inference mechanism. Not specifying explicit types in the source code makes debugging more difficult, but Scala doesn't force anyone to not specify the type. That kind of decision is given back to the programmer, who needs to think for example:

- → Is the type obvious?

- Yes: Let type inference work

- No: Specify the type

- → Should I make the type obvious?

- Yes: Specify the type, and provide type inference specification for the enduser

- No: Specify the type

This kind of options is not thinkable in Java for example, where the type must be explicit and is non flexible.

During this thesis, some projects have been developed using Scala, on of them being the XML binding library presented in 4.4. Many lines of code have been written and we found true that syntax lightening, architecture design features (traits, object etc...) and functional paradigms (closure, type inference) brings an important speed-up in implementation phases, giving more time for unit testing, consequently improving applications stability.

To conclude, we can state that functional programming presents tremendous improvements for designer choices, if correctly flavoured in a traditional language. However, the way functions are composed with each other, especially in the case of closures for data flow programming, requires a change in the way we think algorithms. Developers need an adaptation period, but experience also shows that the benefits gained from using Scala strictly as an imperative language are quite limited. It only brings the language closer to Dynamic Languages because of its light syntax, while lacking their flexibility.

In the next two following sections, we are going to explore two techniques for abstract design language: Domain Specific Language and Embedded Domain Specific Language. Scala will be used as support for implementation examples in both cases.

# 2.3 Domain Specific Language design: LL and LR-based parsing

n our quest to optimizing software development methodologies for domain specific applications, we need to present some parsing algorithms which are often used to create languages. Programing languages usually try to follow a limited set of constructs, which are semantically different enough from each other to make parsing by compilers feasible and possibly with a complexity approaching O(n). These languages thus usually are context-free languages in the Chomsky-Hierarchy [34].

Context-free languages are defined by grammars, which describe the allowed words for a language. A grammar is written as a set of rules, which a parser uses to determine if a character input is part of the defined language or not. Besides accepting or rejecting an input, parsers are used to produce an output, which can be for example an abstract representation of the input, or a transformation. The output creation is driven by actions run when encountering specific language constructs.

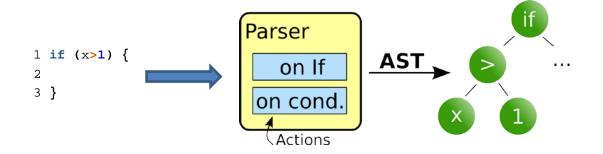

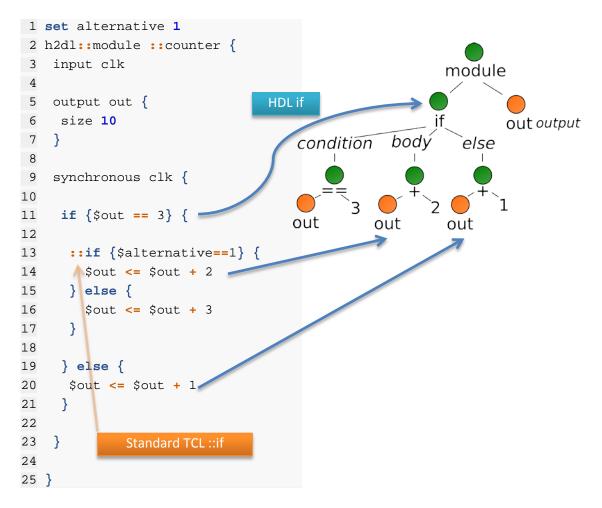

Analysing a very simple example is the best way to understand the way parsers work. We present in Figure 2-20 a C language *if* construct, which is parsed and transformed to generate an in-memory tree representation of the input, called an Abstract Syntax Tree (AST). This AST representation of the text input can then be processed by other software components like compilers, optimisers etc...

Figure 2-20 A simple C "if" parsing rewritten in an AST form

### How can we parse such an input?

We are going to briefly focus here on LL(k) and LR(k) parsers [35], which are two kind of algorithms designed for context-free languages. They work by reading an input from the left to the right, with a *k* number of look-ahead characters in their buffer. A language is said to be deterministic LL(k) / LR(k) defined if it exists an LL(k) / LR(k) parser that can recognises it without backtracking, that is to say, without having to rewind the stream to try another parsing path. LL(k) / LR(k) both implement two different approaches:

✓ An LR parser produces a right-most derivation, meaning that the terminal grammar rules are first matched then reduced to find the top most rule.

✓ An LL parser produces a left-most derivation, meaning that the top level grammar rule to follow is predicted based on the input look-ahead, which is then compared to the expected following rules.

LR(k) parsers performances are linear in time, and generically support more languages than LL(k) ones (as there is no prediction issue), and are more prone to error detection because they always wait for a grammar pattern to be fully recognised before "pushing the result up". However, they are more difficult to write than LL(k) parsers, and their complexity rises in front of languages which would need to rely on look-ahead and prediction to decide which rule path must be followed.

# LL and LR applied to Domain specific languages

Fortunately, *LL(k)* and *LR(k)* parsers can be generated from a textual representation of a grammar in a Backus Normal Form (BNF, first introduced in [36]). Creating a new language can thus be as simple as writing a definition grammar and generate the parsing code. Two of the most famous parser generators tools are *YACC+Lex* for *LR* parsers and *ANTLR* for *LL* parsers, the later of which we are going to present. The Scala language also features an interesting simple *LL(k)* API which allows to represent a grammar using a composition of functions and objects, without *BNF* notation and generation of parser code.

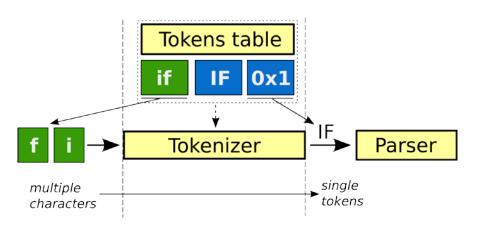

To better understand how parser generators work, it is interesting to note that parsers work on a single character input basis, while languages usually present lexical elements, or tokens, which are composed of multiple characters (like *if* in our example). It is thus efficient to pre-parse a character input in order to represent those multiple characters tokens as single "virtual" characters.

Figure 2-21 Tokenizer output to parser for "if" characters

As presented in Figure 2-21, a parsing chain thus normally first converts the textual representation of an input stream to a "tokenized" stream, using a lexical analyser and a token table. This stream is then fed to the parser which only sees single "characters".

## 2.3.1 LL Parsing in Java: ANTLR

ANTLR is a very popular LL(k) lexical analyser and parser generator [37][38] targeted at the Java Programming Language (some backend exist for other languages like C/C++ but they are not supported from ground up). It introduces the concept of LL(\*) parsers, for which the number of look-ahead characters k is not fixed. Additionally, to help tackle the weaknesses of LL parsers against left recursive languages and context-sensitive constructs, it introduces syntax and semantic predicates, which allow the user to define rules whose matching results drive the choice of the main grammar rule path to be followed.

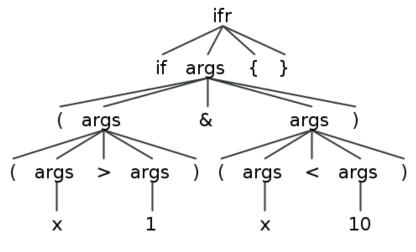

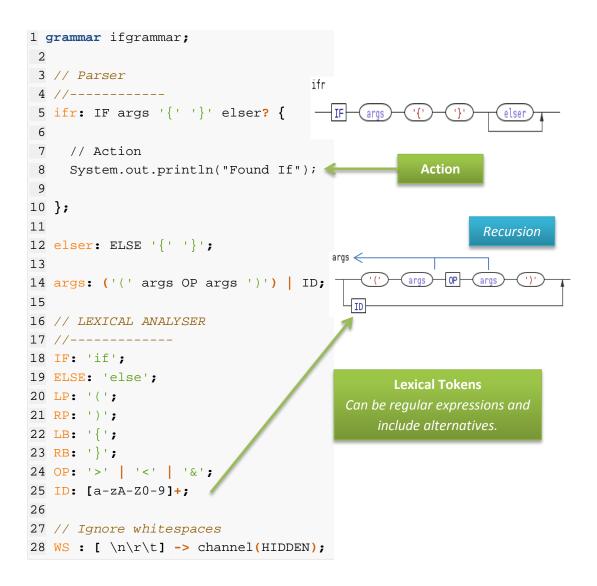

Context sensitivity and left recursion issues can become quite cumbersome to solve, but ANTLR is backed by a powerful set of tools to analyse and debug a language. To illustrate the usage of ANTLR, we wrote a small grammar supporting the *if* construct presented earlier. It has been improved to support recursive condition expressions. As showed in Figure 2-22, the condition for *if* can be represented as *OPERAND OPERATOR OPERAND*. The *OPERATOR* element is defined by the language, and will be for example an arithmetic operator like +, &, < or >. The *OPERAND* can in turn itself be an *OPERAND OPERATOR OPERAND* sub-expression, until it is only a sole identifier, like a variable name or a constant.

1 if ( (x > 1) & (x < 10) ) { 2 3 }

#### Figure 2-22 Simple If definition with recursive condition

The parsing tree produced against this input by the grammar definition, using the ANTLRWorks 2 debugging environment is show in Figure 2-23, while Figure 2-24 presents:

- ✓ The matching grammar in *BNF* form, containing parser rules, lexical analyser definitions, and a Java code action run at the end of the IF matching rule

- ✓ Diagram views of the *if* and *args* rules, created in ANTLRWorks.

Figure 2-23 If grammar parse tree for a given input

#### Figure 2-24 ANTLR Grammar with syntax diagrams

The lexical analyser rules, like *IF*, convert sub-parts of the text input to single-values as presented in Figure 2-21. The *args* definition is the recursive a parser rule, while the *ifr* rule contains a Java code action between curly braces, which is executed after a completed match.

ANTLR proves to be easy to use and its good tooling support makes it a good choice to develop languages in a short time. However, it mostly limited to the Java programming language environment, although some generators exist for other languages, their support and quality is not guaranteed.

## 2.3.2 Parsing in Scala

Both previously presented ANTLR and YACC+Lex generate a parser source code for a grammar described in BNF form. Taking advantage of its advanced type inferring features (see 2.2.1), the Scala language provides a parser library in its standard distribution[39]. It is not a generator-based parser, which means that the user instantiates a set of generic objects which basically integrate and repeat the logic a parser would generate for each a new input parsing process.

This strategy allows embedding parser code right where it belongs in the sources, with no additional tool-chain, but lacks the separate language design stage, and no specific debugging environment is available at the moment. Additionally, the Scala parsers are not like *ANTLR* or YACC *LR(k) /LL(\*)* designs, but simple recursive top-down parsers which employ backtracking (stream rewind) for alternative decisions. For example, if a rule is written:  $S \rightarrow P \mid Q$ , matching Q will first require to fail matching P, then rewind and match Q.

To show how this performs, the following code example implements the *args* rule from previous ANTLR example using a Scala parser:

We can see in this case, that the Lexical tokens (> and & for example) and the rules (*argsr*) are chained directly using Scala function operators ( ~ or / ). For example, some implicit type inferring rules are defined in the Parser library to convert the String data types (ex: "(") to Parser objects which recognise the converted string. Using this mechanism, the developer can ignore the actual parsing class hierarchy, and focus on the rules content.

The Scala parsing API is well adapted for applications requiring simple parsing with flexible integration, and with little performance requirements. Those criterions should match a lot of use cases, but as we will see in 2.4, parsers are quite often not really required for language development in Scala, because the language itself is flexible enough to avoid requiring DSL parsers.

## 2.3.3 Discussion

Domain Specific Languages basically follow the principle of standard programming languages design, which involves defining a grammar and an associated parser to produce an output. Instead of producing runnable applications, DSLs typically are parsed within an existing one, where the embedded actions are used for control and configuration purpose, or to produce data structures to be used later by the runtime.

However, a few criterions need to be analysed when determining is a DSL should be considered for a precise application:

- Language design: language grammars are not so trivial to design, because when using a DSL to raise the semantic abstraction level of the language, the user rapidly falls in context-sensitivity and recursion issues which can lead to long parsing times, high development costs, and moreover, the testing complexity raises rapidly with the number of allowed language constructs.

- ✓ <u>Supported Runtime</u>: In the end, as we have seen with YACC+Lex (for C), ANTLR ( for Java) and Scala, the parser generators tend to be adapted to one underlying language, making the choice of the parsing technology dependent on the chosen application language.

- ✓ <u>Performance</u>: Depending on the size and complexity of the typical input to be parsed, YACC+Lex/ANLTR or Scala behave differently. When Parsing small sized inputs, the performances are comparable, but as the input data grows, a linear *LR* parser performs better, assuming it can parse the language. A less optimised Scala parser will behave badly for large inputs, but similarly to generated parsers for small inputs. The performance criterion must also be compared to the context of usage. A DSL driving very long running processes in the application runtime won't require to be very performant for example, and the first-choice will be driven by the underlying runtime requirement (Native application, Java-based etc...) and the maintenance cost function.

In the next section, an alternative way to create domain specific languages, called Embedded Domain Specific Language will be presented. It differentiates from traditional parsing-based language design by using concepts from Functional Programming languages, to reach a syntax quality close to DSLs without parsers.

# 2.4 Embedded Domain Specific Language (EDSL)

xploration of Functional Programming and language parsing technologies gives us so far knowledge about different ways to structure traditional code, and ways to define new language semantics. Still, most of the flexibility we want to reach using Domain Specific Language and Functional Programming revolves around hierarchy of problems (to complete control flow based or imperative programming, which focuses on sequence), and usually an existing application exists and constraints the technology choice for DSL development.

Embedded Domain Specific Languages, as presented by Paul Hudak in [40], serve the same purpose as traditional DSL design, but instead of parsing a language input on which reactions will trigger a behaviour in the host application, the process is reversed by defining the behaviour of the created language using functions, and try to allow valid function calls in the host language which will look like a new language. This approach presents one main advantage and one main drawback:

- ✓ <u>Be embedded in the host language</u>: The new definitions only need to focus on the core aspects of the language. Traditional control structures, for example, are already present and the user can mix the language elements with other libraries.

- ✓ <u>Be embedded in the host language</u>: Some limitations in the allowed syntax will be required to fit the host language, and the language usage validity mostly has to be proven by the implementation, as no parser can be configure to forbid specific semantic combinations.

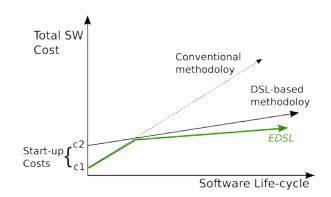

In our sense, the main criterions we will retain for EDSL design should lead to reaching a Software development cost as presented in Figure 2-25 (base graphic from [40]):

- ✓ Ease of development:  $(C2 C1) \rightarrow 0$ , better maintainability in time than DSL methodology

- ✓ Clear Syntax

- ✓ Hierarchy mirroring

Figure 2-25 Domain specific language cost gain [40], with EDSL projection

To illustrate our purpose, we are going to analyse a simple concrete example of how to build a DSL to create a Graphical User Interface (GUI), and then analyse the creation of an EDSL extension to the Scala language.

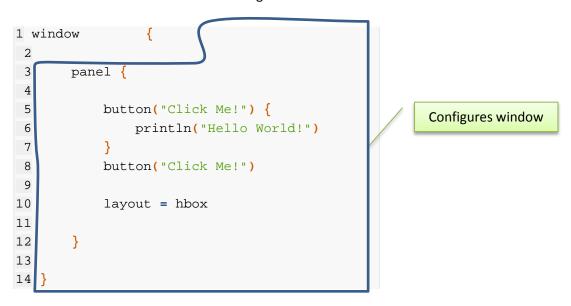

GUIs are typically component graphs with actions (like button clicks), in other words: A component hierarchy with function composition. Figure 2-26 shows a window with two buttons which we want to be able to design efficiently. This first step is to define in clear text what we see:

| EDSL Window         | Х |

|---------------------|---|

|                     |   |

| Click Me! Click Me! |   |

| CIICK ME! CIICK ME! |   |

|                     |   |

|                     |   |

Figure 2-26 Window output of Designed DSL

- ✓ Alternative 1 : The buttons placement is dynamic

- o A window

- A Content Panel

- A button

- Another button

- The panel is laid out using an Horizontal Box algorithm

- ✓ Alternative 2: The placement of the buttons is static

- o A window

- An horizontal box

- A button

- Another Button

From this perspective, we can try to write the two alternatives down using a new language:

| 1 window("EDSL Window") { |                                    | 1 window("EDSL Window") {            |  |

|---------------------------|------------------------------------|--------------------------------------|--|

| 2                         |                                    | 2                                    |  |

| 3                         | panel <mark>{</mark>               | 3 hbox {                             |  |

| 4                         |                                    | 4                                    |  |

| 5                         | <pre>button("Click Me!") {</pre>   | <pre>5 button("Click Me!") {</pre>   |  |

| б                         | <pre>println("Hello World!")</pre> | <pre>6 println("Hello World!")</pre> |  |

| 7                         | }                                  | 7 }                                  |  |

| 8                         | <pre>button("Click Me!")</pre>     | <pre>8 button("Click Me!")</pre>     |  |

| 9                         |                                    | 9 }                                  |  |

| 10                        | layout = hbox                      | 10 }                                 |  |

| 11                        |                                    |                                      |  |

| 12                        | }                                  |                                      |  |

| 13                        |                                    |                                      |  |

| 14                        | }                                  |                                      |  |

|                           | Alternative 1                      | Alternative 2                        |  |

Using tools presented in 2.3, we could now write a grammar definition to parse the input. However, some interesting issues can already be seen:

- ✓ The parser actions must build the hierarchy using a stack. The software complexity is just hidden and moved to the parser maintainer.

- Some code is embedded for the buttons actions. This case is very problematic, as it forces to define a programming syntax, or handle action nodes as simple text, and be able to evaluate it dynamically. This is feasible, but poses the issue of context binding, i.e. with which environment can the action code (button click) interact. Concretely, before running the action code, the application would have to explicitly bind some variables with which it can interact to modify the global application environment.

- ✓ Do the curly-braces-surrounded section after a button means "onClick", or can it be used to configure the button (colour, other kind of listeners etc...) ?

Those few issues illustrate the difficulty to design languages where the output has to be flexible and context sensitive interpretation is required. The efforts to maintain a classical DSL would be in this case for such a simple problem overwhelming. Can we from there on find another path?

# 2.4.1 Functional Programming for EDSL

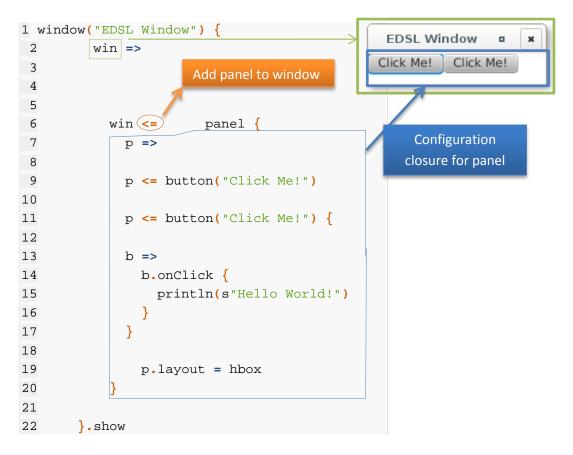

Basically, under the light of [40] or [41] (a design applied to Scala), we can review the hierarchy of the Alternative 1 example as:

- ✓ A window

- A function to configure the window

- The window title is "EDSL Window"

- A panel

- A function to configure the panel

- o A button

- o Another button

- The panel is laid-out using an Horizontal Box algorithm

Figure 2-27 Function + Configuration closure design pattern

In Figure 2-27 we can first recognise a typical  $\lambda$  -calculus pattern: Currying (see 2.2.3). The **window** function creates a Window and accepts another function as input, which will be applied to the new window for configuration.

In a second time, the presented example delegates the actual hierarchy creation to the underlying runtime. Indeed, no explicit keyword or function call explicitly places the panel in the window, and the buttons in the panel. This has to be done by maintaining the hierarchy stack while creating the components, following this simple flow:

- 1. Create new component (the panel for example)

- 2. Stack

- 3. Execute the e configuration closure

- 4. De-stack

#### Is this always true?

Various options exist depending on the type of language that is used for implementation. Basically, in the context of a compiled language, the code must be fully consistent for the compiler to validate the function calls have a clear and existing reference. This leads to two design cases:

- The hierarchy building is delegated to the runtime. This option we just described. It has the main advantage of reducing the required explicit coding, but introduces potential runtime errors.

- The hierarchy is created explicitly by appropriate function calls. This makes code writing more difficult, but triggers clearer results, and better compile-time validation.

This second option is illustrated by a concrete implementation example in Figure 2-28, where the hierarchy is constructed by calls to functions named "<=". It is based on a Scala library created to virtualise user interface creation in an appropriate programming interface, enable faster development time, while delegating the real component creation to the underlying GUI library (Java Swing or JavaFX for example). We can see that it is a bit more expressive than the proposed versions so far, but answers all the presented issues.

On the contrary, when using a dynamic (or scripted) language, it is sometimes possible to create a hybrid solution. The configuration closures would be interpreted when encountered, and thus do not need to be compiled before being passed to the object where it will be executed. In this case, the closure correctness must not be enforced at the level where it is created, but at the level where it is executed. This allows a lighter syntax without delegating any hierarchy building to a special runtime handler.

To outline the requirements of such a dynamic language design, let's have a look at the button creation in our example. The code would look like:

```

1 button("Click Me!") {

2

3 onClick {

4 println(s"Hello World!")

5 }

6 }

```

The formal software design requires:

- ✓ A Button Class with

- o An onClick method

- ✓ The *button* function:

- Creates a *Button* instance

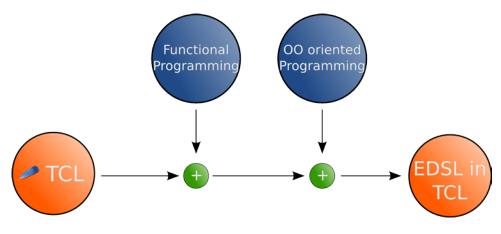

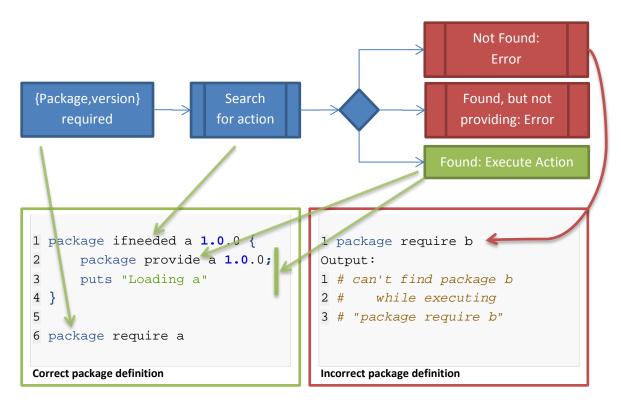

- o Runs the closure in the context of (i.e. local to) the button instance

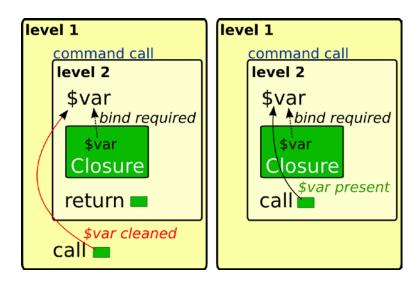

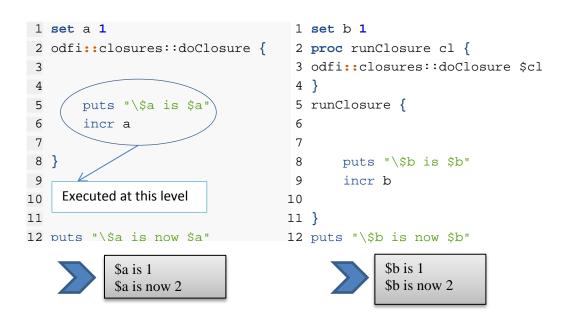

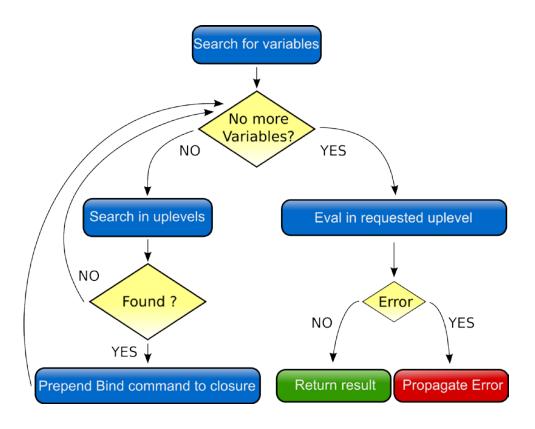

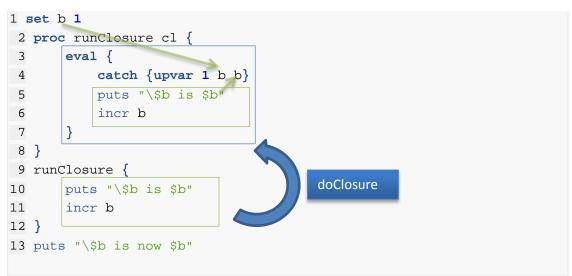

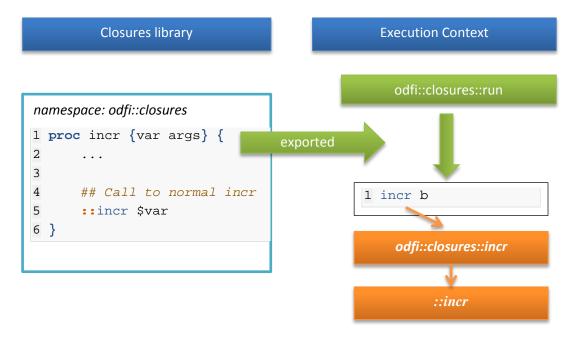

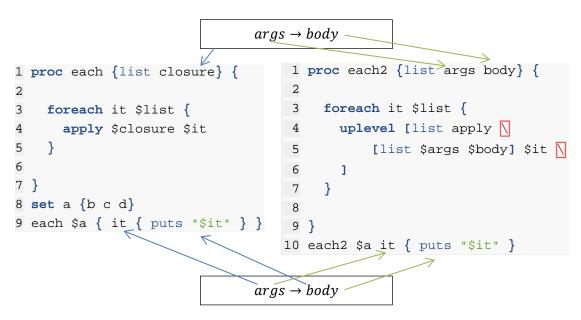

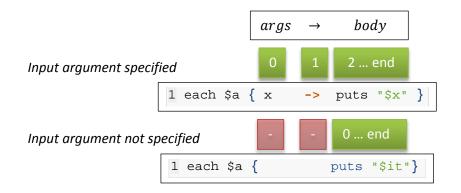

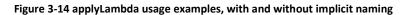

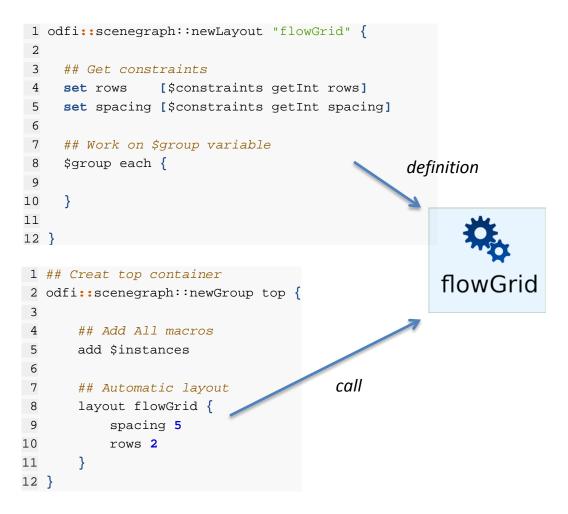

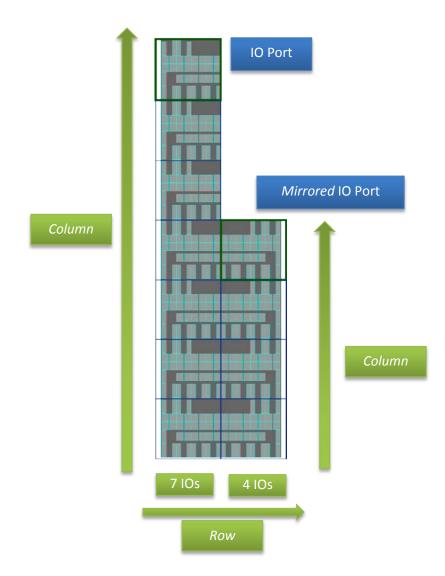

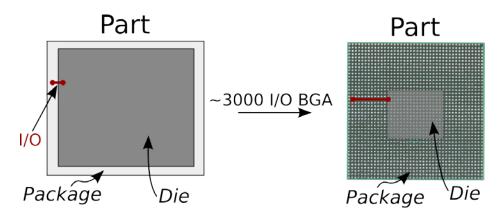

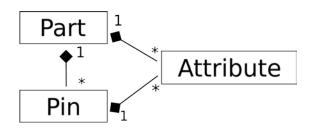

- The *onClick* method call is valid because it is then local to the closure evaluation context.