# DISSERTATION

submitted to the Combined Faculties for the Natural Sciences and Mathematics of the Ruperto-Carola-University of Heidelberg, Germany for the degree of

# doctor rerum naturalium

put forward by

# Dipl.-Phys. Christian Färber

born in Gifhorn, Germany

Oral examination: 04.02.2014

Feasibility study to use an SRAM-based FPGA in the readout electronics of the upgraded LHCb Outer Tracker detector

Referees: Prof. Dr. Ulrich Uwer

Prof. Dr. Norbert Herrmann

## Abstract:

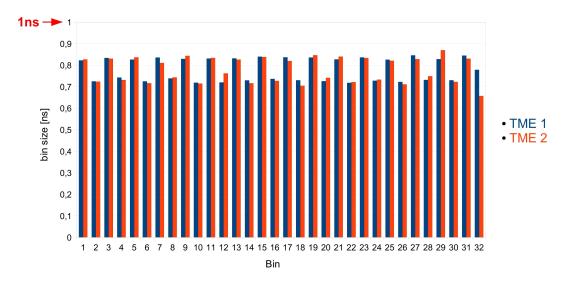

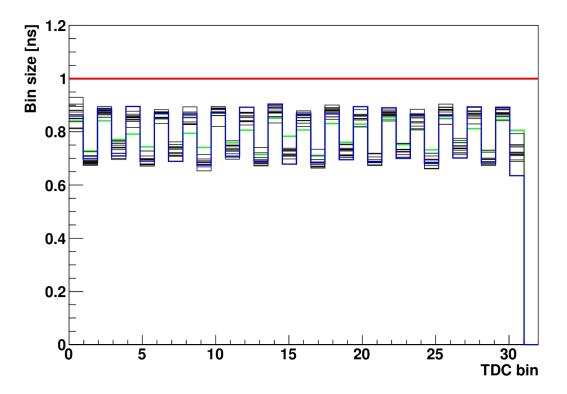

This thesis presents a study of the feasibility to use SRAM-based FPGAs as central component of the upgraded LHCb Outer Tracker readout electronics. The FPGA should contain the functionality of a TDC and should provide fast data links using multi-GBit/s transceivers. The TDC core that was developed provides 5 bit time measurements for 32 channels with a bin size of 780 ps. The TDC has the required time resolution of better than 1 ns. This was achieved by manually placing every logic element of the TDC channels and with an iterative procedure feeding timing measurements back to the Place&Route step of the router software. A transceiver and TDC card, and an adapter board for the existing readout electronics was developed. Both boards were used successfully to read out drift times from an Outer Tracker straw-tube module in a cosmic setup. To qualify the proposed electronics for the expected radiation levels an irradiation test with 22 MeV protons and two FPGA boards was performed up to a total ionization dose of 30 Mrad. Both chips sustained the irradiation expected for the full life time of the upgraded LHCb detector of up to 30 krad. After an irradiation dose of 150 krad the first deteriorations of the performance of the chips were observed. The proton cross section for configuration bit flips was determined to be  $1.6 \cdot 10^{-16} \text{ cm}^2$  per bit. The measured error rate scaled to the upgrade environment would correspond to a manageable firmware error rate.

### **Kurzfassung:**

In der vorliegenden Arbeit wird eine Machbarkeitsstudie zur Nutzung SRAM basierter FPGAs als zentrales Element für die Ausleseelektronik des LHCb Outer Tracker Detektors vorgestellt. Der FPGA soll als TDC und schneller Datenlink mit Multi-GBit/s Transceivern genutzt werden. Ein FPGA basierter 32 Kanal TDC mit 5 Bit Zeitinformation bei einer Bingröße von 780 ps wurde entwickelt. Der TDC hat die erforderliche Zeitauflösung von besser als 1 ns. Dies wurde durch manuelle Plazierung der Logikelemente des TDCs auf dem FPGA, sowie durch eine iterative Prozedur erzielt, bei der Zeitmessungen auf die Verschaltung der Logikzellen rückwirken. Die Zeitauflösung wurde mit Messungen für jeden TDC Kanal individuel optimiert. Ein TDC und GBit/s Transceiver Board sowie ein Adapter Board für die vorhandene Ausleseelektronik wurde entwickelt. Beide Boards wurden erfolgreich beim Auslesen von Driftzeiten eines Outer Tracker Moduls mit kosmischen Myonen getestet. Ein Bestrahlungstest mit 22 MeV Protonen wurde durchgeführt, bei dem 2 FPGAs mit bis zu 30 Mrad ionisierender Strahlungsdosis bestrahlt wurden. Beide Chips überstanden die für das LHCb-Upgrade erwartete Strahlungsdosis von 30 krad. Erste Verschlechterungen der Chips wurden nach einer Strahlungsdosis von 150 krad beobachtet. Der Wirkungsquerschnitt für durch Protonen induzierte Fehler der FPGA Konfiguration wurde zu  $1.6 \cdot 10^{-16} \text{ cm}^2$  pro Bit bestimmt. Die gemessene Fehlerrate zum erwarteten Strahlungsumfeld skaliert scheint den Einsatz des FPGAs möglich zu machen.

# Contents

| Intr | roduction                                                                              | 11              |

|------|----------------------------------------------------------------------------------------|-----------------|

| The  | eoretical background                                                                   | 15              |

| 2.1  | The Standard Model of particle physics                                                 | 15              |

| 2.2  |                                                                                        | 17              |

| 2.3  |                                                                                        | 18              |

|      |                                                                                        | 19              |

|      | 2.3.2 The rare decay $B_s^0 \to \mu^+ \mu^- \dots \dots \dots \dots \dots \dots \dots$ | 21              |

| LH   | Cb detector                                                                            | 23              |

| 3.1  | Large Hadron Collider                                                                  | 23              |

|      | -                                                                                      | 24              |

| 3.2  |                                                                                        | 24              |

| 0    |                                                                                        | $\overline{25}$ |

|      | -                                                                                      | 30              |

| 3.3  |                                                                                        | 32              |

| 0.0  |                                                                                        | 34              |

|      |                                                                                        | 35              |

| 3.4  | Luminosity leveling                                                                    | 39              |

| LH   | Cb upgrade                                                                             | 41              |

|      |                                                                                        | 42              |

|      |                                                                                        | 43              |

| 1.2  |                                                                                        | 43              |

|      |                                                                                        | 43              |

|      |                                                                                        |                 |

|      | <b>The</b><br>2.1<br>2.2<br>2.3<br><b>LH</b><br>3.1<br>3.2<br>3.3<br>3.4               | 2.2CKM matrix   |

|          |     | 4.2.4  | Tracking station upgrade                                      | 44  |

|----------|-----|--------|---------------------------------------------------------------|-----|

|          |     | 4.2.5  | Calorimeter upgrade                                           | 44  |

|          |     | 4.2.6  | Muon detector upgrade                                         | 46  |

|          | 4.3 | Upgra  | de of the LHCb readout electronics                            | 46  |

|          |     | 4.3.1  | Upgrade of the OT front-end box to 40 MHz readout $\ .$ .     | 46  |

|          | 4.4 | LHCb   | upgrade schedule                                              | 47  |

| <b>5</b> | FPO |        | sed time measurement                                          | 49  |

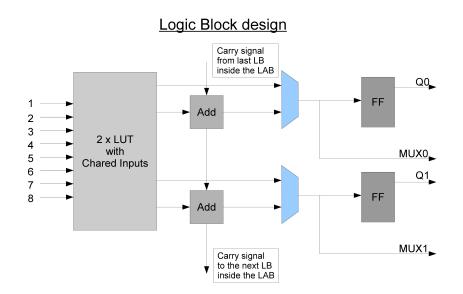

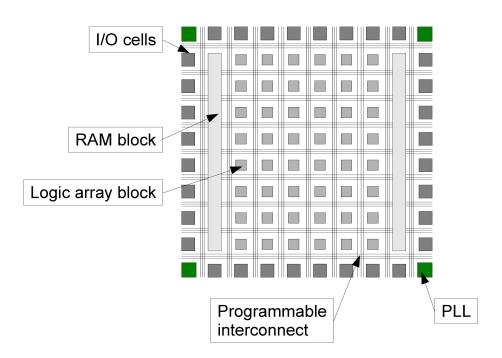

|          | 5.1 | Gener  | al description of an FPGA                                     | 50  |

|          |     | 5.1.1  | Workflow of FPGA programming                                  | 52  |

|          |     | 5.1.2  | Using an FPGA for the 40 MHz upgrade of the LHCb Outer        |     |

|          |     |        | Tracker                                                       | 53  |

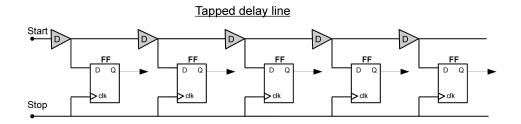

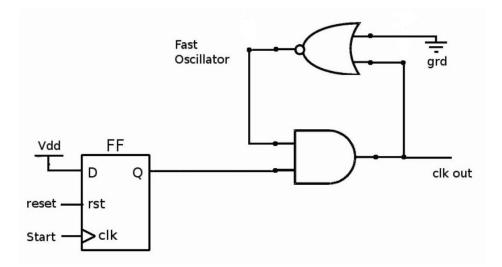

|          | 5.2 |        | ods for time measurements with an FPGA                        | 53  |

|          |     | 5.2.1  | Tapped-delay line                                             | 54  |

|          |     | 5.2.2  | Ring oscillator                                               | 55  |

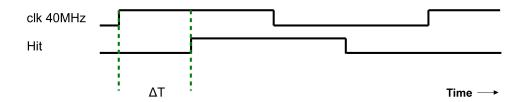

|          |     | 5.2.3  | Fast sampling with LVDS receivers                             | 57  |

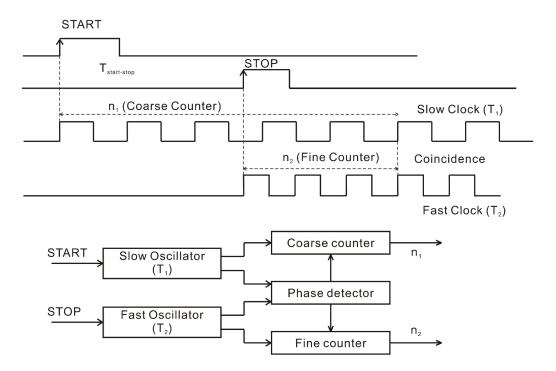

|          |     | 5.2.4  | Fast counter method                                           | 57  |

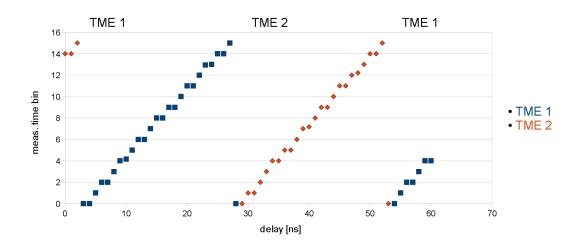

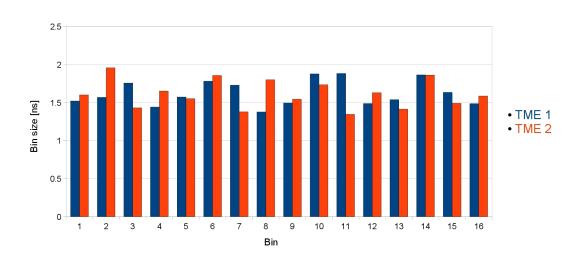

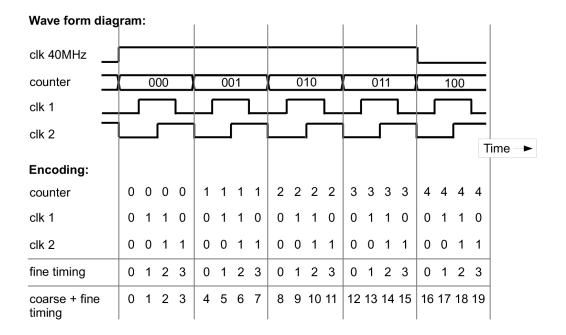

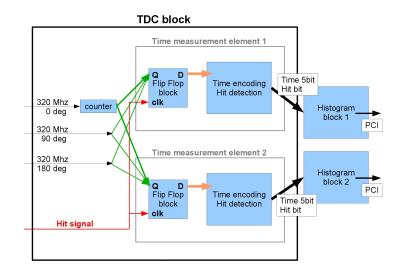

|          | 5.3 |        | measurements with the Stratix FPGA                            | 59  |

|          |     | 5.3.1  | Technical constraints for the TDC design                      | 59  |

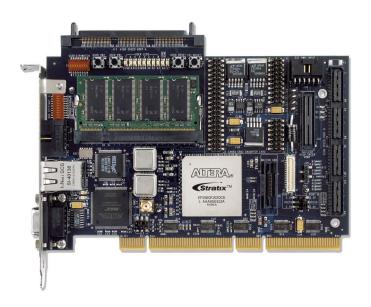

|          |     | 5.3.2  | Hardware used for the Stratix FPGA-based TDC                  | 60  |

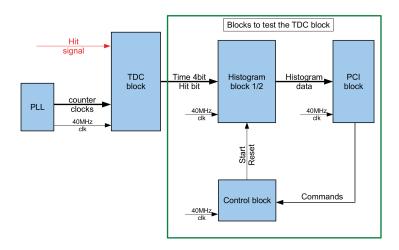

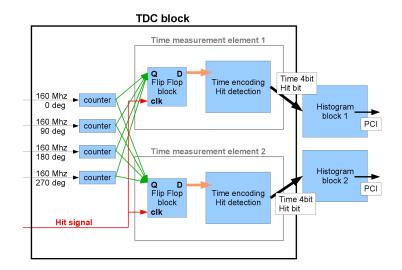

|          |     | 5.3.3  | First design of the FPGA-based TDC                            | 60  |

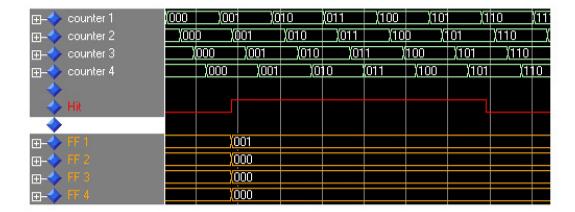

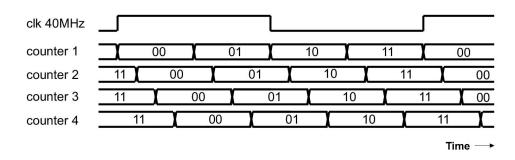

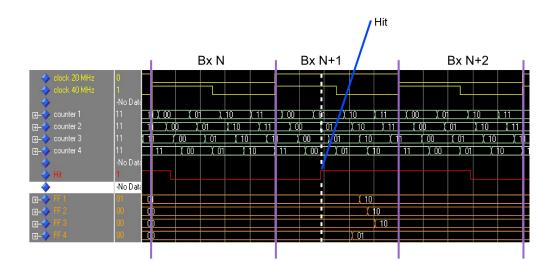

|          |     | 5.3.4  | ModelSim simulation of the 4 counter TDC                      | 64  |

|          |     | 5.3.5  | TDC performance test setups                                   | 64  |

|          |     | 5.3.6  | Results of the first FPGA-based TDC                           | 66  |

|          |     | 5.3.7  | FPGA-based TDC with manually placed logic                     | 68  |

|          |     | 5.3.8  | Results of the manually placed FPGA-based TDC                 | 71  |

|          |     | 5.3.9  | Summary for the Stratix FPGA results                          | 75  |

|          | 5.4 | Time   | measurements with the Arria GX FPGA                           | 76  |

|          |     | 5.4.1  | First TDC design for the Arria GX TDC                         | 78  |

|          |     | 5.4.2  | TDC performance test setups                                   | 81  |

|          |     | 5.4.3  | Results of the first Arria GX FPGA-based TDC                  | 82  |

|          |     | 5.4.4  | Solution for the non-linearity of the first Arria GX TDC $$ . | 82  |

|          |     | 5.4.5  | Results of the modified Arria GX FPGA-based TDC $\ . \ .$ .   | 84  |

|          |     | 5.4.6  | Summary of the Arria GX TDC results                           | 87  |

| 6        | Fun | ctiona | lity test: Outer Tracker module readout                       | 93  |

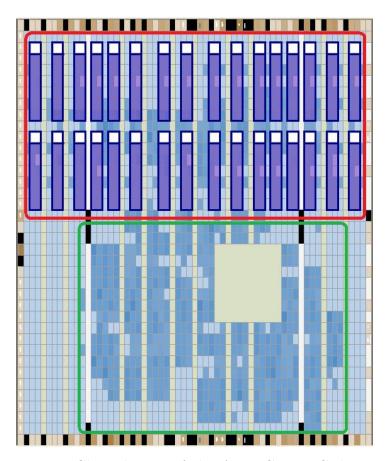

|          | 6.1 | Protot | type boards                                                   | 93  |

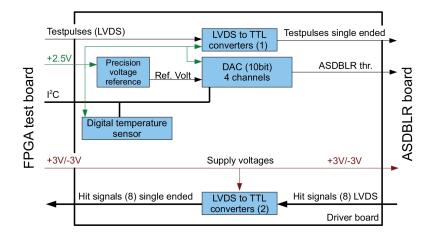

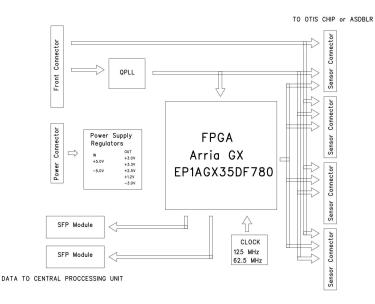

|          |     | 6.1.1  | FPGA test board                                               | 94  |

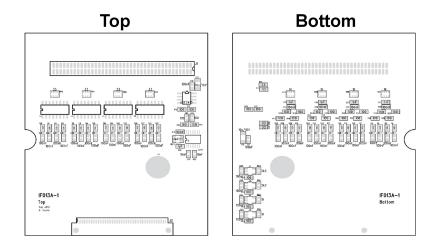

|          |     | 6.1.2  | Connection board                                              | 96  |

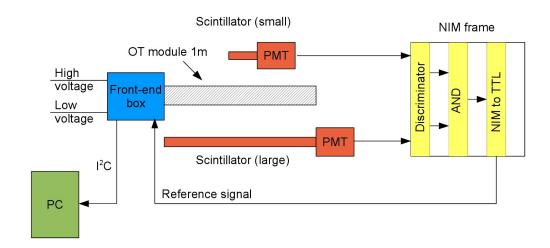

|          | 6.2 | Cosmi  |                                                               | 98  |

|          |     | 6.2.1  | Hardware                                                      | 99  |

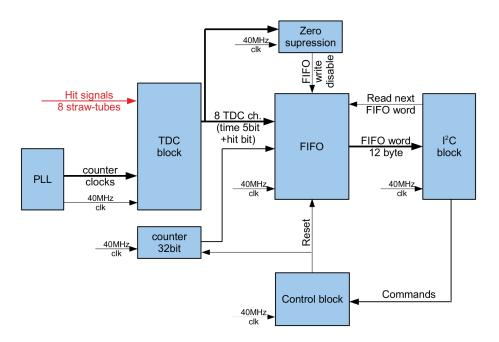

|          |     | 6.2.2  | Software and firmware                                         | 100 |

|          |     | 6.2.3  | Noise reduction                                               | 101 |

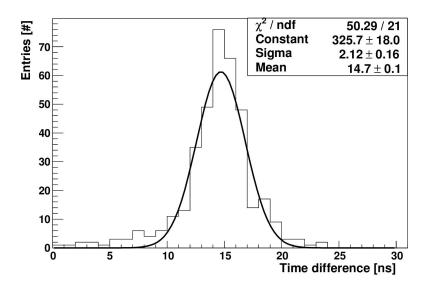

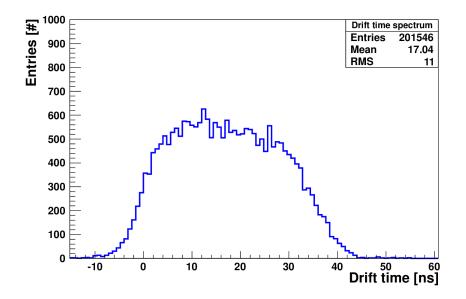

|              | C D                   | <ul> <li>6.2.4 Time resolution measurement of the readout</li></ul>          |     |

|--------------|-----------------------|------------------------------------------------------------------------------|-----|

|              | 6.3                   | Design proposal for the FPGA<br>front-end board                              | 104 |

| 7            | Irra                  | diation test of the Arria GX FPGA                                            | 107 |

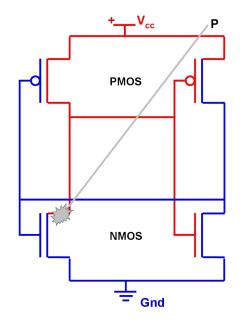

|              | 7.1                   | Radiation effects of FPGAs                                                   | 107 |

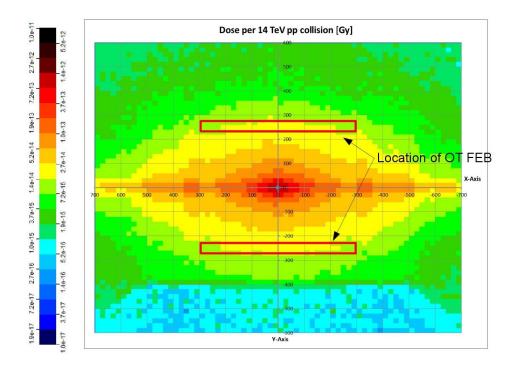

|              | 7.2                   | Expected radiation levels for the                                            |     |

|              | - 0                   | LHCb Outer Tracker upgrade                                                   | 110 |

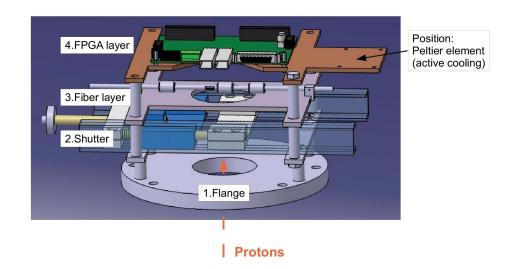

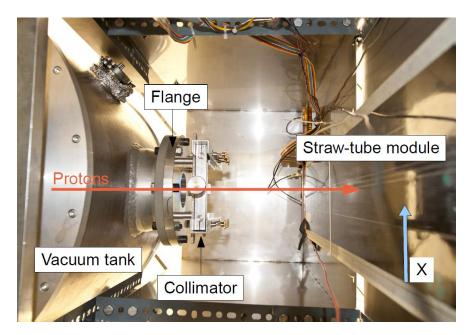

|              | 7.3                   | General setup                                                                | 112 |

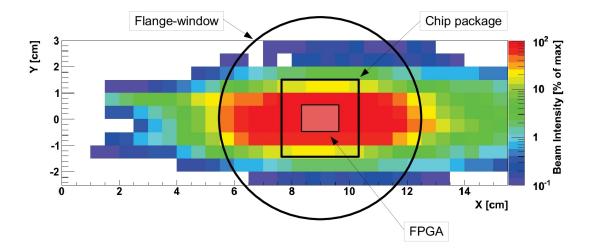

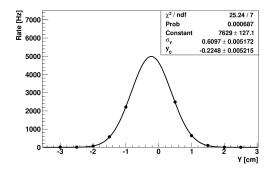

|              | 7.4                   | Total ionization dose determination                                          | 112 |

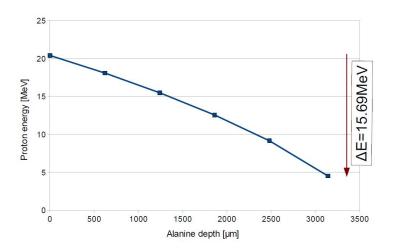

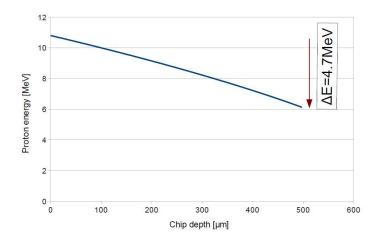

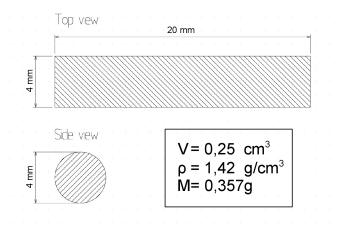

|              |                       | 7.4.1 Total ionization dose calculation                                      | 112 |

|              |                       | 7.4.2 Dose measurement $\ldots$                                              | 121 |

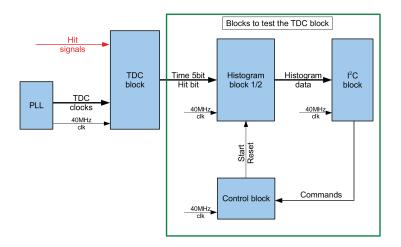

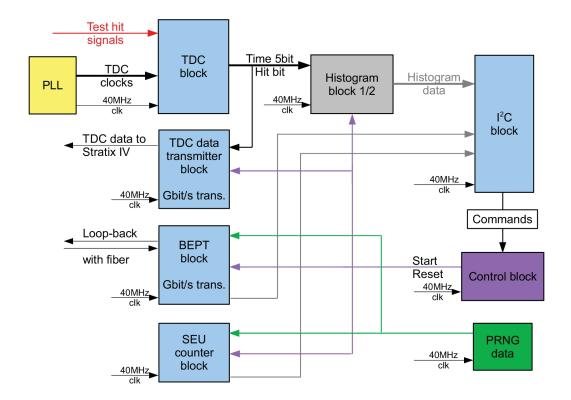

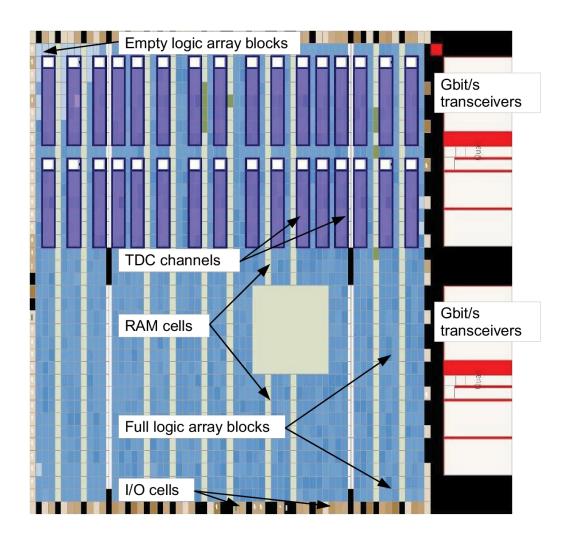

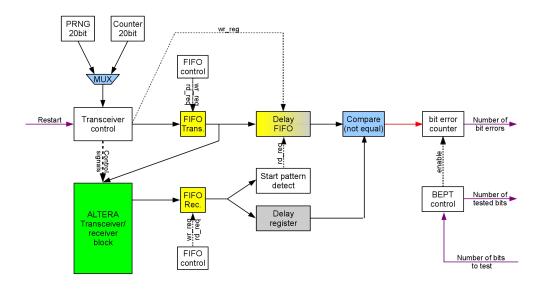

|              | 7.5                   | FPGA firmware                                                                | 122 |

|              |                       | 7.5.1 $I^2C$ bus slave $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 123 |

|              | 7.6                   | FPGA irradiation measurements                                                | 125 |

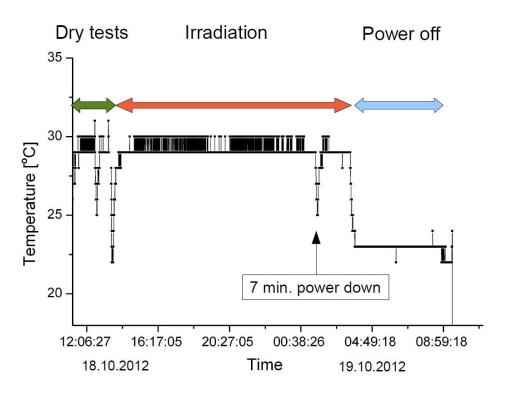

|              |                       | 7.6.1 Temperature                                                            | 125 |

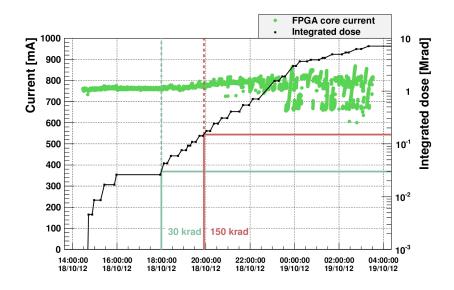

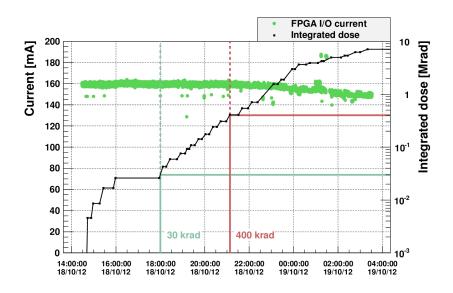

|              |                       | 7.6.2 Electric currents                                                      | 126 |

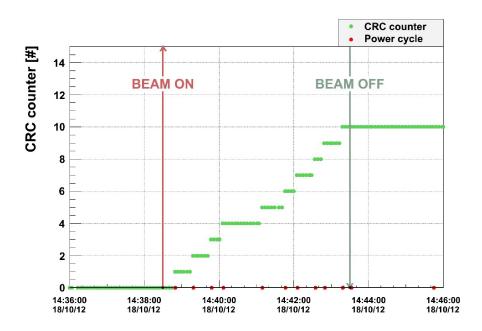

|              |                       | 7.6.3 Firmware errors                                                        | 128 |

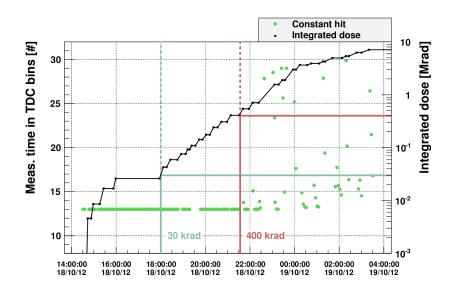

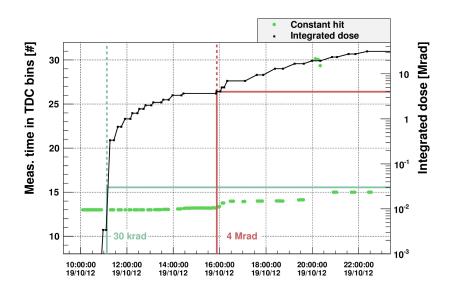

|              |                       | 7.6.4 TDC stability                                                          | 130 |

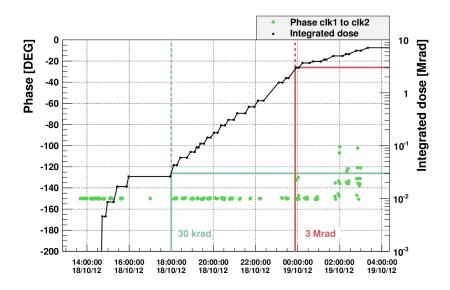

|              |                       | 7.6.5 Phase-locked loop stability                                            | 132 |

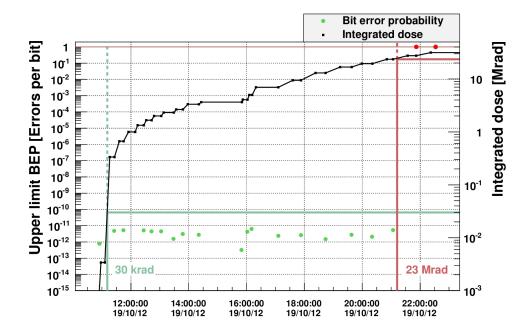

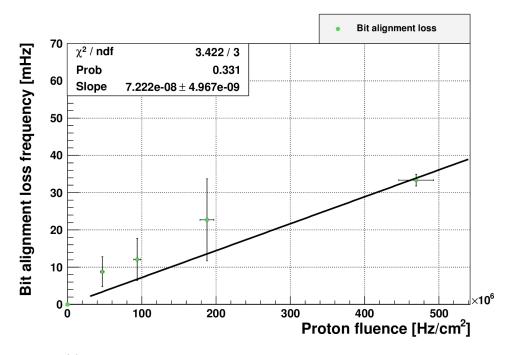

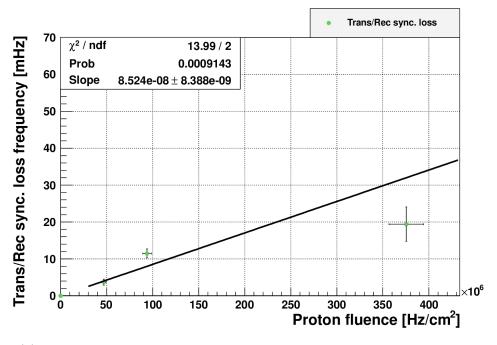

|              |                       | 7.6.6 GBit/s transceiver tests                                               | 133 |

|              |                       | 7.6.7 Single event upsets                                                    | 140 |

|              | 7.7                   | Conclusions                                                                  | 140 |

| 8            | Sun                   | nmary                                                                        | 141 |

| A            | $\operatorname{List}$ | of Acronyms                                                                  | 145 |

| в            | App                   | oendix : Outer Tracker gas monitoring                                        | 147 |

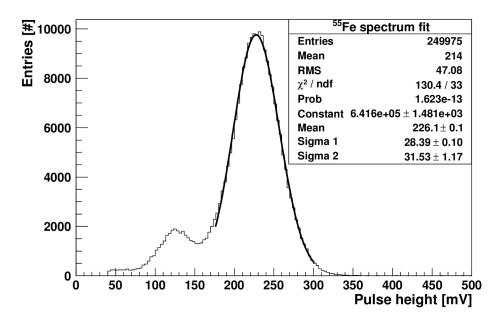

|              | B.1                   | Method                                                                       | 147 |

|              | B.2                   | Hardware                                                                     | 149 |

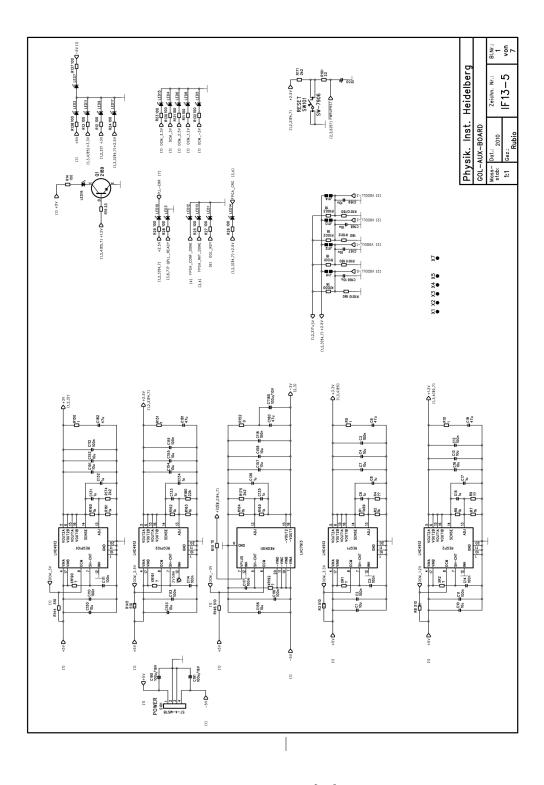

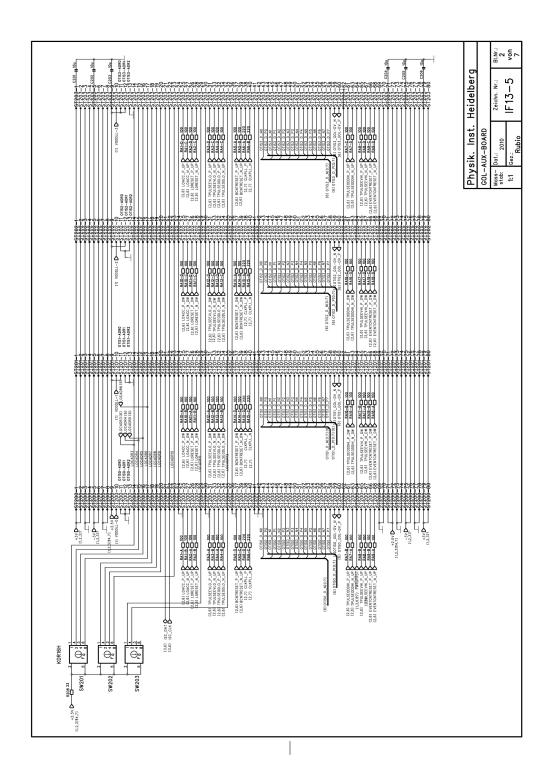

|              |                       | B.2.1 Electronics                                                            | 149 |

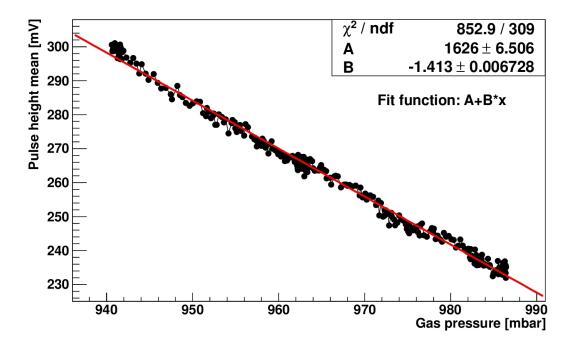

|              | B.3                   | Gas pressure correction                                                      | 149 |

|              | B.4                   | Software                                                                     | 151 |

|              |                       | B.4.1 Data acquisition                                                       | 151 |

|              |                       | B.4.2 Analysis software                                                      | 151 |

|              |                       | B.4.3 Piquet script                                                          | 153 |

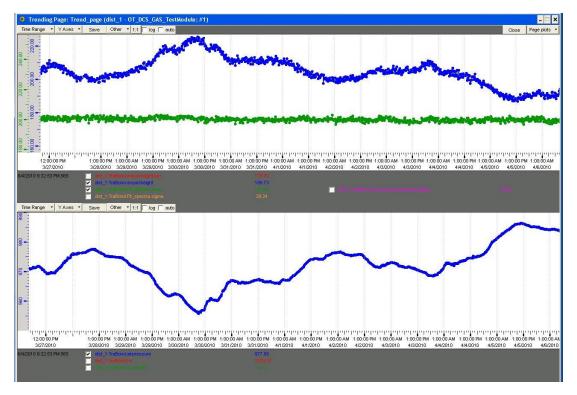

|              |                       | B.4.4 Emergency script                                                       | 153 |

|              |                       | B.4.5 Integration into the global LHCb control system                        | 153 |

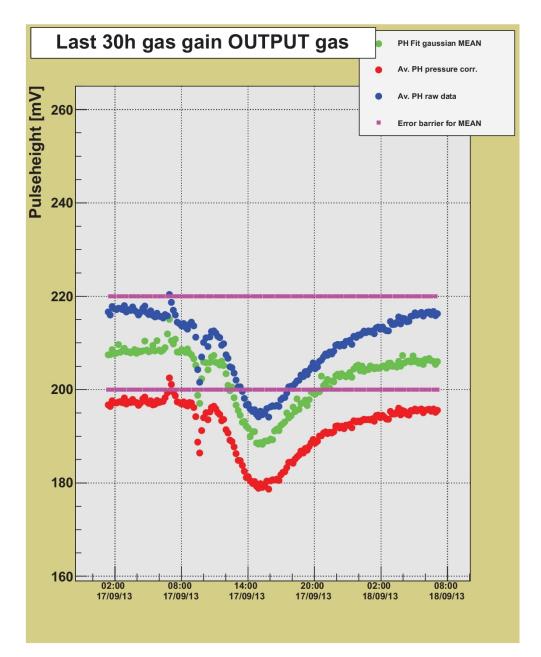

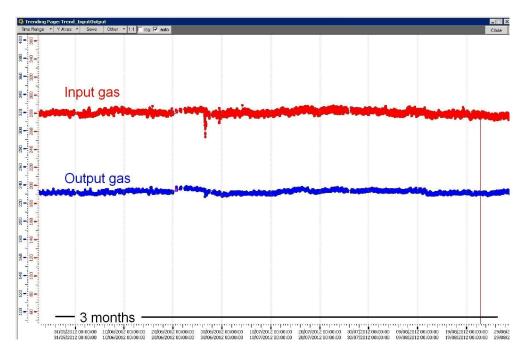

|              | B.5                   | Outer Tracker gas stability                                                  | 155 |

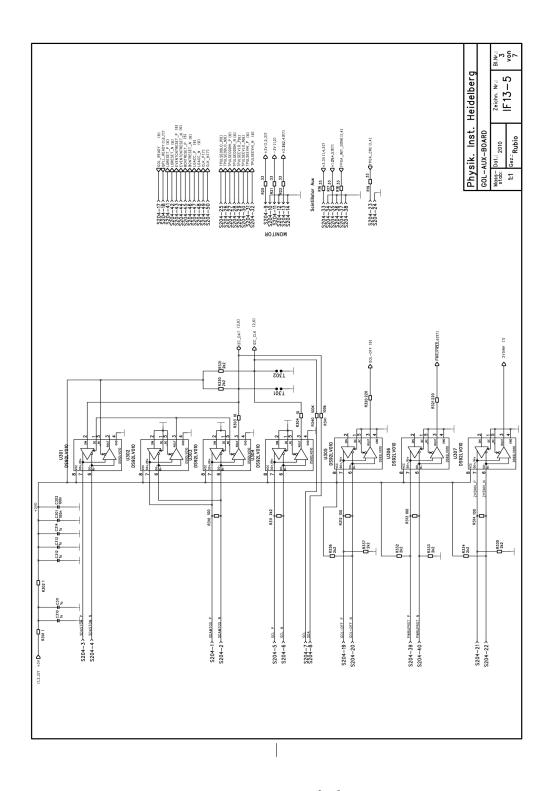

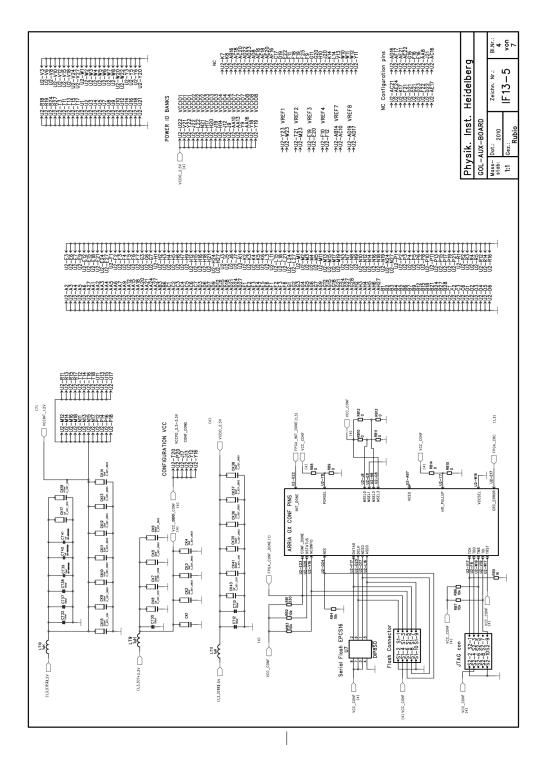

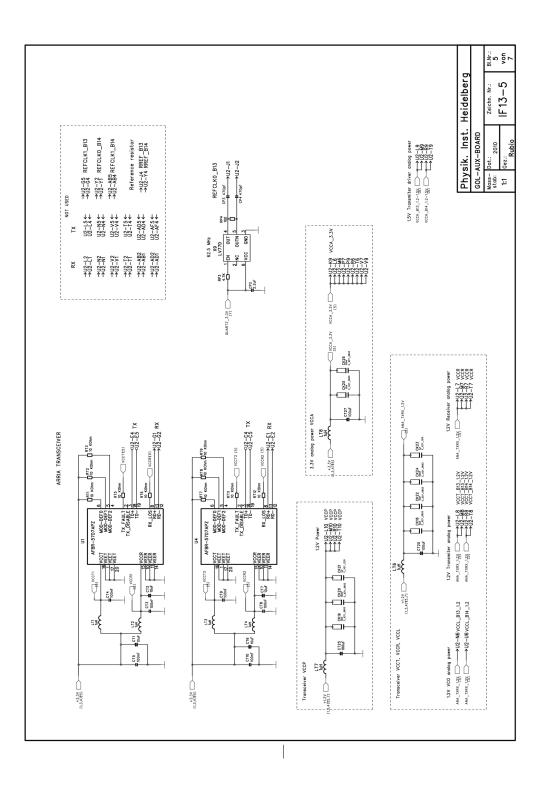

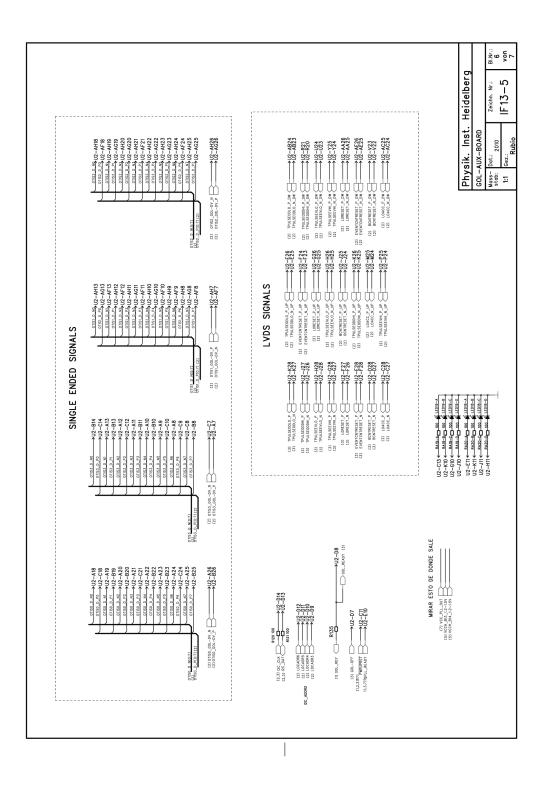

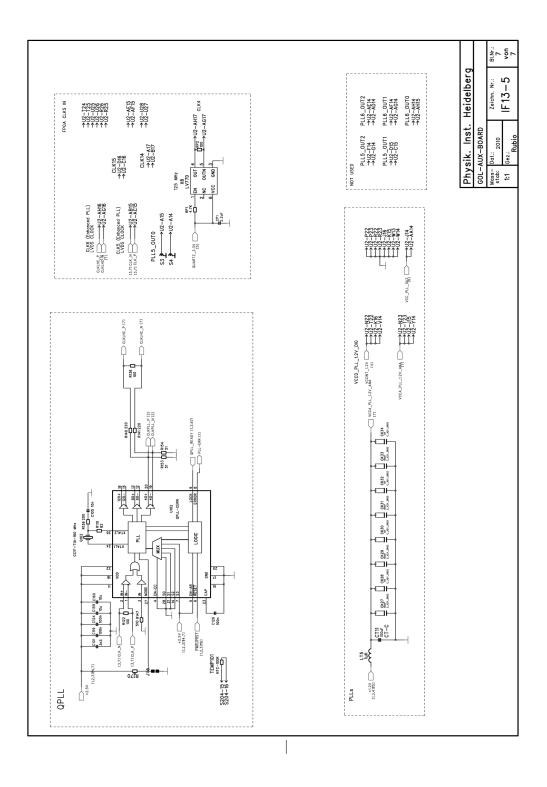

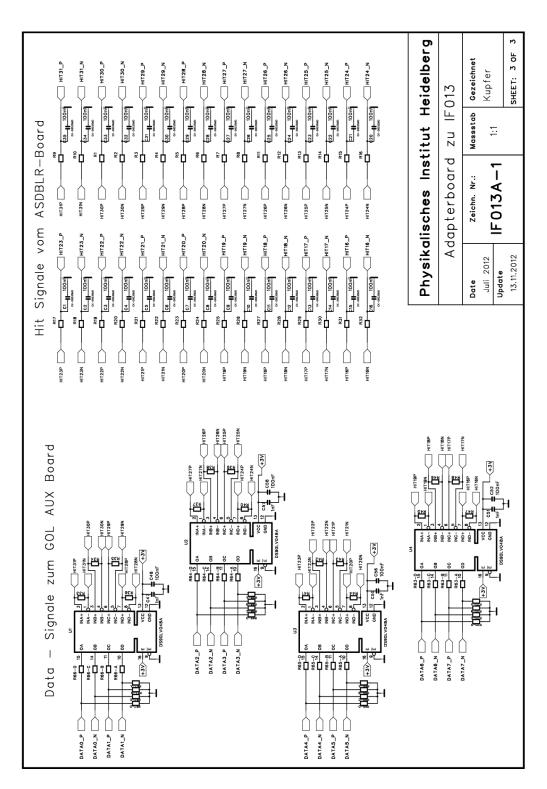

| $\mathbf{C}$ | App                   | pendix : Schematic IF13-6                                                    | 157 |

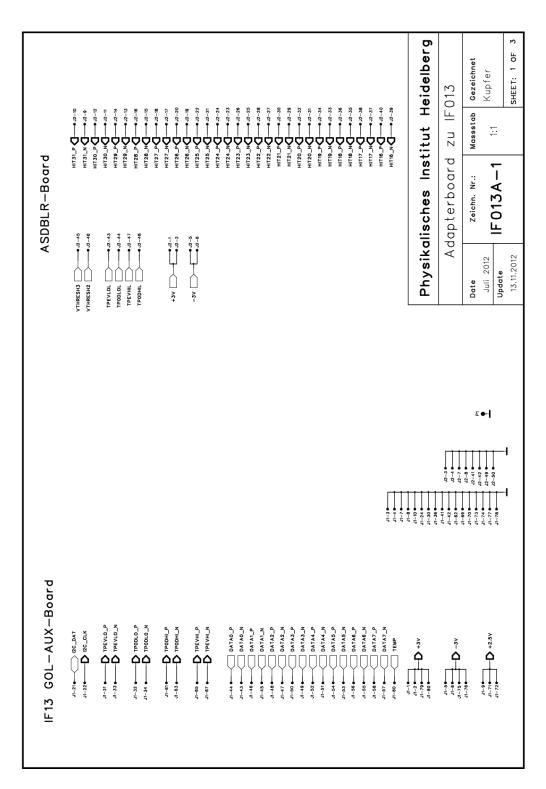

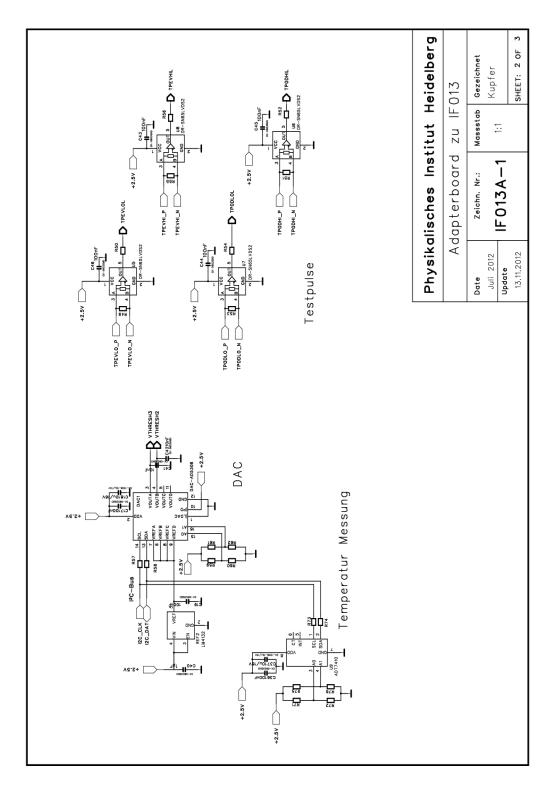

| D Appendix : Schematic IF013A | 165 |

|-------------------------------|-----|

| List of Figures               | 169 |

| List of Tables                | 173 |

| Bibliography                  | 175 |

| E Acknowledgments             | 183 |

# CHAPTER ]

# Introduction

The idea that every object in the universe is built from indivisible particles is old. Already, the Greek philosopher Democritus claimed 24 centuries ago that the natural world consists of indivisible atoms and empty void. Every object is built from these atoms which only differ in intrinsic properties like size and shape [1].

This fundamental concept for the buildup of the universe is not far from our current understanding in particle physics. In the last hundred years many fundamental particles have been found which build up the universe. Every discovery provided a deeper understanding of the microcosm than before. The current status is that matter is build from quarks and leptons. The fundamental interactions between these particles are described by the Standard Model (SM) of particle physics. It is important to note that this theory was confirmed by many experiments during the last 40 years to very high accuracy.

Although the Standard Model of particle physics is a very successful theory, some questions remain open. For example:

- In the Big Bang equal amounts of matter and antimatter were produced. Nevertheless, observations today show a matter dominated universe. The origin of this baryon asymmetry of the universe is not completely understood.

- Astronomical observations confirm the existence of Dark Matter for which the SM provides no candidate. Furthermore, the Dark Matter and the

matter described by the SM make up only  ${\sim}27~\%$  of the energy density of the universe. The remaining part of is called Dark Energy and not explicable with the SM, either.

Possible explanations of both phenomena must be theories beyond the SM which, at lower energies that we have probed, are approximated by the Standard Model. These theories are also referred to as New Physics.

Beside the search for the Higgs particle and the Quark gluon plasma the Large Hadron Collider (LHC) at CERN in Geneva has been built to search for signs of New Physics. The LHC uses proton-proton collisions with center-of-mass energies of up to  $\sqrt{s} = 14$  TeV, which is currently the highest energy for particle accelerators. Two approaches are taken to search for New Physics. In the *direct approach* experiments look for new heavy particles which are directly produced in the collision. The ATLAS and CMS experiments are following this approach. The other possibility is to measure precisely the effects of quantum loop corrections in which new particles can be present and lead to a modification of related observables. This method is sensitive to particles masses  $10 \times$  higher than the *direct approach*. The LHCb experiment uses the second approach to search for signs of new heavy particles.

The LHCb experiment exploits the enormous production rates of beauty and charmed hadrons at the LHC. Precision measurements of CP asymmetries and rare decays are performed to investigate potential effects of physics beyond the Standard Model. The recent LHCb results underline the potential of flavor physics at the LHC. Furthermore, the detector shows an excellent performance.

In order to perform studies of rare decays with even higher precision the LHCb collaboration is planning to upgrade the detector in 2018 to a 40 MHz readout with a more flexible software-based triggering system that will increase the data rate as well as the efficiency of selecting B decays with hadronic final states. It is foreseen to run the detector at instantaneous luminosities of up to  $2 \times 10^{33} \text{ cm}^{-2} \text{s}^{-1}$  and to collect >50 fb<sup>-1</sup> of data.

To increase the readout rate by a factor 36 to 40 MHz, the readout electronics of the sub-detectors must be modified. In the past, radiation hard custom made ASICs<sup>1</sup> were the only possibility to construct a high performance readout. Especially for projects which need only a small number of readout chips, the development of ASICs is time consuming and expensive. Currently, there are high performance FPGAs<sup>2</sup> available which have a large number of logic elements and multi-GBit/s transceivers. These chips open new technical possibilities for the readout of sub-detectors in regions with low radiation levels. The advantage of using FPGAs in the readout electronics is a higher flexibility and smaller cost than using ASICs.

<sup>&</sup>lt;sup>1</sup>Application Specific Integrated Circuit

<sup>&</sup>lt;sup>2</sup>Field Programmable Gate Array

This thesis presents a feasibility study to use SRAM-based FPGAs as central component in the readout electronics for the LHCb Outer Tracker detector in the LHCb upgrade. The FPGA would be used as a TDC and provide fast data links using multi-GBit/s transceivers. The TDC needs to have a time resolution smaller than 1 ns and should have 32 channels. Furthermore, the FPGA has to sustain a total ionization dose of 30 krad and the rate of radiation induced configuration register flips has to be low. Both effects were tested during an irradiation campaign with 22 MeV protons.

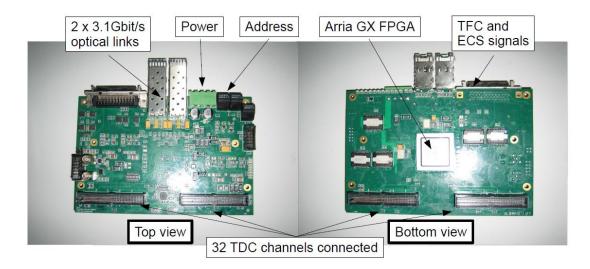

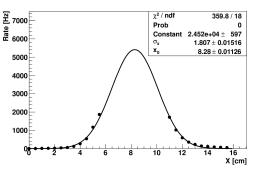

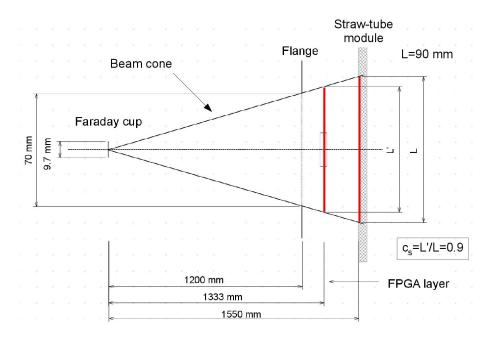

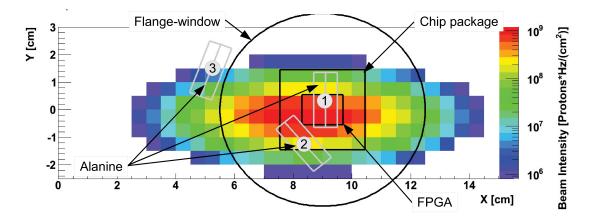

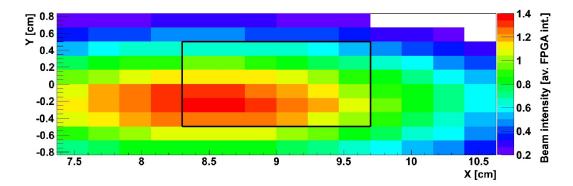

First, an FPGA-based TDC was developed on an Arria GX FPGA with 32 channels and a time resolution below 1 ns. Afterwards, the Arria GX FPGA with the TDC functionality and multi-GBit/s transceivers has been integrated in a newly developed PCB<sup>3</sup>. This board is already a prototype for the upgraded Outer Tracker readout electronics and is pin compatible to the existing readout electronics. The FPGA test board was tested with a second developed connector board in a cosmic setup to measure the LHCb Outer Tracker drift time spectrum. Furthermore, the Arria GX test board was used for an irradiation test with 22 MeV protons at the Max Planck Institute for Nuclear Physics in Heidelberg. For the dosimetry and careful assessment of the radiation induced deteriorations of the FPGAs under test, the beam profile was measured.

The thesis is laid out as follows: Chapter 2 provides an introduction to the theoretical background for the LHCb physics program, beginning with a short review of the Standard Model and presenting some measurements relevant for the LHCb upgrade. Chapter 3 describes the current LHCb detector with special focus on the Outer Tracker. The plans for the LHCb upgrade are shown in Chapter 4. Chapter 5 presents the realization of an FPGA-based TDC and Chapter 6 shows the measurement of the LHCb Outer Tracker drift time spectrum in a cosmic setup. The proton irradiation test of the Arrix GX FPGA is described in Chapter 7 and Chapter 8 summaries the thesis.

<sup>&</sup>lt;sup>3</sup>Printed circuit board

# CHAPTER 2

# Theoretical background

The beginning of this chapter shows a short introduction of the Standard Model of particle physics. Afterwards, the CKM matrix and the Unitarity Triangles are described. At the end, the physics motivation of the LHCb upgrade is given by showing two analyses from the LHCb upgrade program.

# 2.1 The Standard Model of particle physics

The Standard Model of particle physics (SM) is a successful theory for three of the four fundamental forces in the universe [3, 4, 5]. It describes the electromagnetic interaction, the weak interaction and the strong interaction in the framework of quantum field theory. The electromagnetic force is responsible for the interaction between electrically charged particles. The weak force acts between particles carrying weak charge and is seen for example in the  $\beta$ -decay of the neutron. The strong force appears between particles with color-charge and is responsible for the bindings of hadrons. The fourth force, gravity, is not described by the SM.

The interaction between particles is described via the exchange of gaugebosons which have spin 1. Table 2.1) shows the mass and relative strength of these bosons. The electromagnetic force is mediated by the photon and has unlimited range. The weak force uses the heavy  $W^{\pm}$  and  $Z^0$  bosons, and has only a very short range (~ fm). Also, the strong force which is described within Quantum Chromo Dynamics (QCD), has effectively a short range of roughly one nucleon (1 fm). A big difference between the interactions is the self-coupling of

| Interaction     | Boson     | Mass                         | Relative strength |

|-----------------|-----------|------------------------------|-------------------|

| strong          | gluons    | 0                            | 1                 |

| electromagnetic | photon    | 0                            | $10^{-2}$         |

| weak            | $W^{\pm}$ | $\sim 80  \mathrm{GeV/c^2}$  | $10^{-13}$        |

|                 | $Z^0$     | $\sim 91  { m GeV}/{ m c}^2$ |                   |

**Table 2.1:** The three forces described by the Standard Model and their corresponding gauge-bosons. The mass values are taken from [6].

|            | Quarks       |                |                                |             | Lepto      | ns                                 |

|------------|--------------|----------------|--------------------------------|-------------|------------|------------------------------------|

| Generation | Type         | Charge [e]     | Mass                           | Type        | Charge [e] | Mass                               |

| Ι          | u            | $+\frac{2}{3}$ | $1.5$ - $3.3 \mathrm{MeV/c^2}$ | $\nu_e$     | 0          | $\leq 2  \mathrm{eV}/\mathrm{c}^2$ |

|            | d            | $-\frac{1}{3}$ | $3.5$ - $6.0 \mathrm{MeV/c^2}$ | e           | -1         | $511.0 \mathrm{keV/c^2}$           |

| II         | с            | $+\frac{2}{3}$ | $\sim 1.27{ m GeV/c^2}$        | $\nu_{\mu}$ | 0          | $\leq 2  \mathrm{eV}/\mathrm{c}^2$ |

|            | $\mathbf{S}$ | $-\frac{1}{3}$ | $\sim 104~{ m MeV/c^2}$        | $\mu$       | -1         | $105.7 \mathrm{MeV/c^2}$           |

| III        | t            | $+\frac{2}{3}$ | $\sim 171.2{ m GeV/c^2}$       | $ u_{	au} $ | 0          | $\leq 2  \mathrm{eV}/\mathrm{c}^2$ |

|            | b            | $-\frac{1}{3}$ | $\sim 4.2~{ m GeV/c^2}$        | $\tau$      | -1         | $1.78~{ m GeV/c^2}$                |

**Table 2.2:** The fermions in the Standard Model consist of quarks and leptons grouped in three generations. To each particle in this table an antiparticle exists with the same mass but opposite charge. The mass values are taken from [6].

the bosons for the weak and strong force, which is a result of a non-Abelian gauge theory. The neutral photon can not couple to itself, but the  $W^{\pm}$  and  $Z^{0}$  bosons and the gluons create self-coupling vertices.

The building blocks of matter are quarks and leptons which are spin  $\frac{1}{2}$  fermions. Leptons and quarks are grouped into three families with same features but different mass which are shown in Table 2.2. The leptons react via the electromagnetic and weak forces the quarks react in addition via the strong force. The origin of the three generations has not been understood yet. In the first generation are the lightest and therefore stable elementary particles which are the main constituents of the matter of the universe. In the SM there exists to each particle an antiparticle with the same mass and lifetime but opposite charge, which is a consequence of CPT invariance, a fundamental property of Lorentz invariant quantum field theories.

Explicit mass terms in the Lagrangian to describe the massive bosons  $(W^{\pm}, Z^0)$ would violate gauge invariance. This conflict is solved by the mechanism of spontaneous symmetry breaking of the  $\mathrm{SU}(2)_L \otimes \mathrm{U}(1)_Y$  electroweak symmetry (Higgs-mechanism). The heavy gauge bosons aquire mass via the coupling to the Higgs field. The fermion masses are introduced by explicit Yukawa couplings to the Higgs. The masses of the  $W^{\pm}$  and  $Z^0$  bosons are given by the coupling constants of the theory, the masses of the fermions in the Yukava sector are not given directly from the theory, but are parameters of the theory.

The Higgs-mechanism predicts one observable massive spin 0 particle, which is called Higgs-boson. One of the main motivations for the Large Hardon Collider at CERN was the search for this particle. Results from CMS and ATLAS showed the observation of a particle consistent with the Higgs-boson in July 2012 which is a big success of particle physics [7, 8].

# 2.2 CKM matrix

For quarks the mass and weak eigenstates are not the same, the Cabibbo-Kobayashi-Maskawa (CKM) matrix was introduced to change the mass base to the weak base [9]. The Cabibbo-Kobayashi-Maskawa matrix is a unitary  $3 \times 3$  matrix  $(U^{\dagger} \cdot U = U \cdot U^{\dagger} = 1)$ , which rotates the mass-eigenstates of the down-type quarks  $(d, s, b)^T$  into the weak-eigenstates  $(d', s', b')^T$ .

$$\begin{pmatrix} d'\\s'\\b' \end{pmatrix} = V_{CKM} \cdot \begin{pmatrix} d\\s\\b \end{pmatrix} = \begin{pmatrix} V_{ud} & V_{us} & V_{ub}\\V_{cd} & V_{cs} & V_{cb}\\V_{td} & V_{ts} & V_{td} \end{pmatrix} \cdot \begin{pmatrix} d\\s\\b \end{pmatrix}$$

(2.1)

The weak eigenstates q' are a linear combination of the mass eigenstates q. The CKM matrix elements  $V_{ij}$  describe the relative transition probability ( $\sim |V_{ij}|^2$ ) of an up-type quark  $q_i$  into a down-type quark  $q_j$  or vice versa. The complex matrix has in principle 18 parameters from which 9 parameters are fixed due to the unitarity condition of the CKM matrix, 5 more parameters describe unobservable relative quark phases and can be rotated away. The remaining four parameters can be chosen as three quark mixing angels and one complex phase which is the source of CP-violation in the Standard Model.

One very common parametrization of the CKM matrix is the Wolfenstein parametrization with  $\lambda$ , A,  $\rho$  and  $\eta$  [10]. The size of each matrix element is given in the expansion of the parameter  $\lambda = \sin \theta_c \approx 0.22$  where  $\theta_c$  is the Cabibbo angle:

$$V_{CKM} = \begin{pmatrix} 1 - \frac{\lambda^2}{2} & \lambda & A\lambda^3(\rho - i\eta) \\ -\lambda & 1 - \frac{\lambda^2}{2} & A\lambda^2 \\ A\lambda^3(1 - \rho - i\eta) & -A\lambda^2 & 1 \end{pmatrix} + (\lambda^4)$$

(2.2)

Quark transitions are most common within a generation, what can be seen in the diagonal entries of the CKM matrix, which are approximately equal to one. The transition from the first to the second generation are still likely ( $\propto \lambda^2$ ), and transitions from the second and the third generation are more unlikely ( $\propto \lambda^4$ ). The most unlikely transitions are between the first and the third generation ( $\propto \lambda^6$ ).

Due to the unitarity relations it is possible to construct 6 relations of the form:

$$V_{ud}V_{ub}^* + V_{cd}V_{cb}^* + V_{td}V_{tb}^* = 0.$$

(2.3)

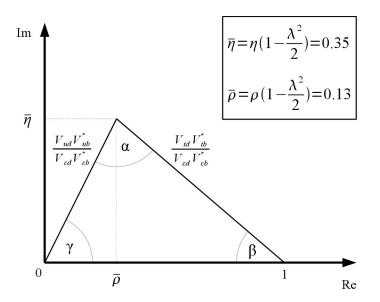

It is possible to draw the Equation 2.3 as triangles in the complex plane. The corresponding unitarity triangle is shown in Figure 2.1 normalized to  $V_{cd}V_{cb}^*$ . The area of these triangles represent the size of the CP-violation in the SM. The

Figure 2.1: Unitarity triangle, corresponding to Equation 2.3.

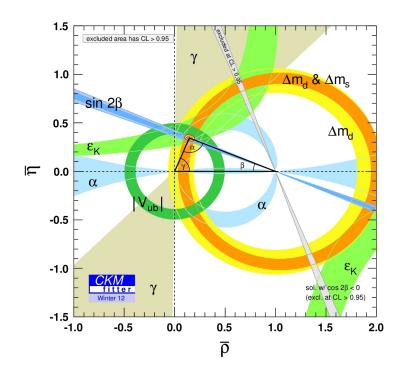

triangle parameters can be determined by measuring the different CKM matrix elements with several different physics processes. Figure 2.2 shows the current experimental status of the unitarity triangle corresponding to Equation 2.3. The results are in agreement with the Standard Model prediction. The upgrade of the LHCb detector will reduce the error of the angle  $\gamma$  to the degree-level. The theoretical errors for the two angles are negligible [2]. If a discrepancy to the unitarity prediction of the SM is observed this would be a sign of physics beyond the description of the SM (New Physics).

# 2.3 Physics with the upgraded LHCb detector

The physics program for the upgraded LHCb detector can be divided into two equally important categories [12] like for the current physics program. Firstly, the "Exploration" category. These are studies which are very sensitive to new phenomena beyond the Standard Model and have not been accessible at previous experiments. Secondly, the "Precision Studies" which are done with known decay

Figure 2.2: Current experimental status of the unitarity triangle corresponding to Equation 2.3. The figure was taken from [11].

modes or observables with improved sensitivity. These are compared with precise theory predictions.

In the following two analyses from the broad LHCb upgrade physics program are discussed as representative examples for the 2 categories.

# **2.3.1** CP-violation in the $B_s^0$ -system

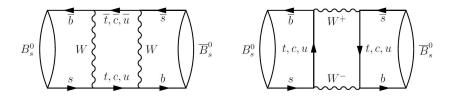

The weak eigenstates  $B_s^0$  and  $\bar{B}_s^0$  are a mixture of the mass eigenstates  $B_H$  and  $B_L^1$ . Neutral B-mesons can oscillate into their anti-mesons in the Standard Model by box-diagrams. Figure 2.3 shows the two contributing Feynman diagrams in the Standard Model. The dominating contribution comes from the top quark in the loop.

The time evolution of  $B_s^0$ -mesons with oscillation and decay can be described by the phenomenological Schroedinger equation

$$i\frac{d}{dt}\begin{pmatrix}B_s^0\\\bar{B}_s^0\end{pmatrix} = \left(\mathbf{M} - i\frac{\mathbf{\Gamma}}{2}\right)\begin{pmatrix}B_s^0\\\bar{B}_s^0\end{pmatrix}.$$

(2.4)

The mass matrix  $\mathbf{M}$  and the decay width matrix  $\mathbf{\Gamma}$  are 2×2 hermitian matrices. Their diagonal elements are identical due to the CPT invariance theorem.  $\mathbf{M}$  is

<sup>&</sup>lt;sup>1</sup>H: heavy and L: light

**Figure 2.3:** Feynman diagrams for  $B_s^0$  meson oscillation. The figure is taken from [15]

non-diagonal so the flavor eigenstates are not equal to the mass eigenstates. To get the mass eigenstates for t = 0 the matrix  $(\mathbf{M} - i\frac{\mathbf{\Gamma}}{2})$  is diagonalized:

$$|B_L\rangle = p \left| B_s^0 \right\rangle + q \left| \bar{B}_s^0 \right\rangle, \qquad (2.5)$$

$$|B_H\rangle = p \left| B_s^0 \right\rangle - q \left| \bar{B}_s^0 \right\rangle, \qquad (2.6)$$

where  $|p|^2 + |q|^2 = 1$ . The following parameters are introduced to describe the mixing:

$$\Delta m_s = m_H - m_L = 2 |M_{12}|,$$

$$\Delta \Gamma_s = \Gamma_L - \Gamma_H,$$

$$\phi_M = \arg(M_{12}).$$

(2.7)

The mass difference  $\Delta m_s$  is the oscillation frequency of the mixing process,  $\Delta \Gamma_s$  is the decay width difference between light and heavy and  $\phi_M$  is the mixing phase.

The  $B_s^0 - \bar{B}_s^0$  oscillation frequency  $\Delta m_s$  has been measured by the LHCb experiment to be  $\Delta m_s = (17.768 \pm 0.024) \text{ps}^{-1}$  [13].

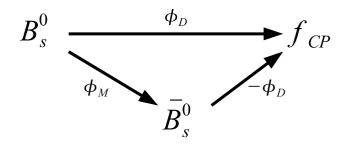

Furthermore, for the decays in which both  $B_s^0$  and  $\overline{B}_s^0$  can decay into the same CP final state, the direct decay and the decay following the mixing can interfere with each other. This allows to measure the phase difference of the two decay paths a depicted in Figure 2.4. The phase difference  $\phi_S = \phi_M - 2\phi_D$ , where the phase  $\phi_D$  is the decay phase and is approximately zero, can be determined through the measurement of the time-dependent CP asymmetry. The "golden decay mode" to perform this measurement is the decay

$$B_s^0(\bar{B}_s^0) \to J/\psi(\mu^+\mu^-)\phi(K^+K^-).$$

A 4-dimensional fit to the decay angles and the decay time allows to measure  $\Delta\Gamma_s$  and the CP-violating phase  $\phi_s$  in a simultaneous fit. For the phase  $\phi_s$ , the SM predicts a very small value (-0.0364±0.0016) rad [14] with very small uncertainty. The measurement is therefore very sensitive to possible contributions from New Physics. The LHCb experiment has already performed a measurement of  $\phi_s$  and the result is consistent with the small value predicted by the SM, however the result include still a relatively large statistical error

Figure 2.4: Illustration of the interfering amplitudes contributing to CP violation in interference of decay and mixing.

$(\phi_s=0.07\pm0.09(\text{stat})\pm0.01(\text{syst}) \text{ rad [15]})$ . To measure a small deviation from the SM prediction much higher statistics are needed. The 50 fb<sup>-1</sup> of data collected during the LHCb upgrade would reduce the statistical uncertainty for  $\phi_s$ from 0.09 rad [15] now to 0.009 rad after the LHC run 4 [2].

# 2.3.2 The rare decay $B_s^0 \rightarrow \mu^+ \mu^-$

$B_s \to \mu^+ \mu^-$  is an effective channel to search for phenomenon beyond the Standard Model which predicts a branching ratio of  $(3.23 \pm 0.72) \cdot 10^{-9}$  [16].

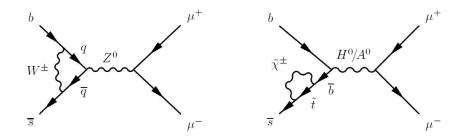

Figure 2.5: Examples for Feynman diagrams for  $B_s^0 \to \mu^+ \mu^-$  in the SM (left) and in the MSSM (right). The figure is taken from [17]

Figure 2.5 shows examples for Feynman diagrams contributing to the decay. The branching ratio increases for the MSSM<sup>2</sup> with the sixth power of  $\tan\beta$  which is the ratio of the vacuum expectation values of the Higgs bosons [18]. The recent observations of this decay by LHCb [19, 20] and CMS [21] rule out new contributions of comparable size to the SM. Since the theoretical prediction of the branching ratio has a small error of  $0.3 \cdot 10^{-9}$  and the uncertainty of the measurement would decrease to  $0.19 \cdot 10^{-9}$  with a data set of 50 fb<sup>-1</sup> [2], the LHCb upgrade is important for this study.

<sup>&</sup>lt;sup>2</sup>Minimal Supersymmetric Standard Model

Furthermore, the very rare decay  $B_d^0 \to \mu^+ \mu^-$  will also be accessible with the upgraded LHCb detector ("Exploration" category). The Standard Model prediction for the branching ratio is  $(1.07 \pm 0.10) \cdot 10^{-10}$  [16]. In addition, the ratio of the two branching ratios of  $B_s^0$  and  $B_d^0$  is given by the CKM matrix elements which makes a measurement of both branching ratios to an interesting test of the Standard Model and of minimal flavor violating new physics models.

# CHAPTER 3

# LHCb detector

The LHCb experiment is one of four big experiments at the Large Hadron Collider (LHC) at CERN<sup>1</sup> in Geneva. This chapter begins with an introduction of the Large Hadron Collider at CERN in Geneva. Followed by the different LHCb sub-systems which are briefly described. Next the Outer Tracker is described in detail, and its different readout boards are shown.

# 3.1 Large Hadron Collider

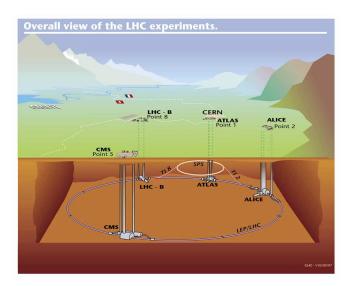

The LHC consists of two 27 km long accelerator rings which accelerate protons in opposite directions up to an energy of 7 TeV with collisions in four experimental positions. The LHC was built in the existing LEP tunnel. A schematic of the LHC can be seen in Figure 3.1. Beside the proton-proton physics there is also a heavy ion physics program at the LHC. Lead-lead or lead-proton are brought into collision in special runs. The LHC design energy is  $\sqrt{s} = 14$  TeV with a design luminosity of  $\mathcal{L} = 10^{34}$  cm<sup>-2</sup>s<sup>-1</sup>. The proton beam is separated into 2808 bunches with a bunch spacing of 25 ns. Each bunch contains ~10<sup>11</sup> protons. Superconducting magnets with a field of 8.3 T are used to force the protons on a circular orbit.

At the LHC there are four large experiments placed: ATLAS, ALICE, CMS and LHCb. ATLAS and CMS are  $4\pi$  multi-purpose detectors, ALICE is special-

<sup>&</sup>lt;sup>1</sup>Conseil Européen pour la Recherche Nucléair.

Figure 3.1: LHC tunnel with the four experiments ATLAS, AL-ICE, CMS and LHCb [22].

ized for heavy ion collisions and the LHCb experiment investigates rare heavyflavor meson decays to test the quark flavor sector of the Standard Model. CPviolation, which is small in the Standard Model, is a well suited observable for New Physics searches.

### **3.1.1** Proton-proton interaction rate

The proton-proton interaction rate R at the LHC can be calculated from the LHC luminosity  $\mathcal{L}$  at the experiment and the proton-proton cross section  $\sigma$

$$R = \mathcal{L} \cdot \sigma. \tag{3.1}$$

The design luminosity of the LHCb detector is  $4 \times 10^{32}$  cm<sup>-2</sup>s<sup>-1</sup> and the proton proton cross section at 7 TeV is 98.3 mb, from which the detector "sees" only the inelastic collisions (73.5 mb), reaction products of the elastic and single diffractive events stay inside clode to the beam axis and outside the rapidity covery of  $\eta \leq 4.9$ . This results in an average event rate of 24 MHz for the original detector design. For the LHCb upgrade in 2018, it is foreseen to increase the luminosity to  $2 \times 10^{33}$  cm<sup>-2</sup>s<sup>-1</sup>, which would result in a 5 times higher event rate.

The collision rate is important to estimate the radiation environment of the detector components.

# 3.2 LHCb sub-systems

The LHCb experiment exploits the production of b- and c-hadrons at the LHC and is dedicated to the study of rare B and D mesons decays. The b-quarks are

predominantly produced in inelastic proton-proton collisions in pairs of quark and anti-quark  $(b\bar{b})$ . The dominant processes for the  $b\bar{b}$  production are gluon fusion and quark fusion. The mass of the  $b\bar{b}$  pair is small enough that they can be produced by partons with a quite different momentum. The result is a boost of the quark pair forward or in backward direction relative to the beam line. So LHCb has been built as a single-arm forward spectrometer to maximize detection efficiency and minimize costs.

## 3.2.1 Detector design

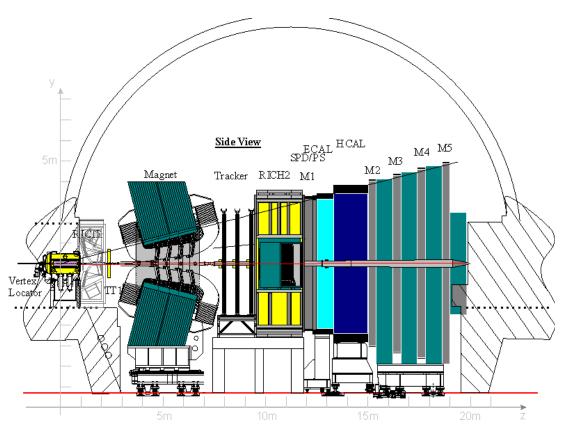

The LHCb detector consists of several sub-components, which can be grouped into a vertex and tracking system, a particle identification system and the dipole magnet. The LHCb detector is shown in Figure 3.2.

Figure 3.2: Side-view of the LHCb detector [23].

#### The Vertex and Tracking system:

The Vertex and Tracking system consists of the Vertex Locater (VELO), the Tracker Turicensis (TT), the Inner Tracker (IT) and the Outer Tracker (OT).

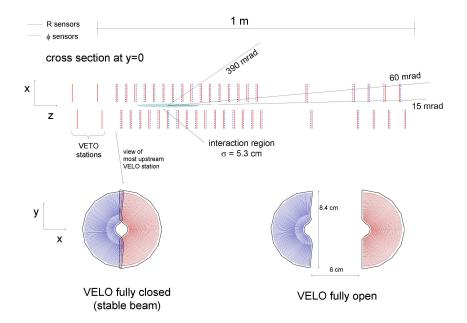

#### Vertex detector

The purpose of the Vertex Locater is the precise measurement of the tracks in the vicinity of the collision point and to detect the primary and secondary vertices of particles and their decay fragments. The VELO is built of two halves, which can be positioned very precisely around the interaction point [25]. The VELO consists of silicon strip sensors. During injection of the LHC beam, the VELO is opened and after stable beam is declared the two halves are moved closer to the beam. The minimal distance from the detector to the beam is only 5 mm, which makes the LHCb VELO the detector which is closet to the interaction point at the LHC and results into a spatial resolution of 10-20  $\mu$ m. The whole detector consists of 42 semi-circular silicon micro-strip sensors, with always two strip sensors mounted back-to-back: One sensor has strips placed in radial coordinates and the other sensor has strips in the azimuthal angle,  $\varphi$ . Each sensor contains 2048 strips with a pitch varying between 40  $\mu$ m and 100  $\mu$ m to have a similar occupancy in all strips. In the Figure 3.4, a schematic of the LHCb Vertex Detector is shown.

Figure 3.3: Schematic of the Vertex Detector [24].

#### **Tracker Turicensis**

The Tracker Turicensis (TT) is placed in between the first RICH<sup>2</sup> detector and the LHCb magnet and is also built from silicon-strip sensors. The sensors are 500  $\mu$ m thick and have a pitch of 183  $\mu$ m. The TT consists of 4 layers where two layers are rotated by a stereo angle of  $\pm 5^{\circ}$  with respect to the other two layers.

<sup>&</sup>lt;sup>2</sup>RICH: Ring Imaging Cherenkov Detector.

This makes a three dimensional measurement possible. Two layers are grouped to pairs and arranged in one station. These stations are 13 cm high and 14.5 cm wide.

#### Inner Tracker and Outer Tracker

The Inner Tracker (IT) [26] and the Outer Tracker (OT) [27] are placed behind the magnet and in front of the second RICH detector and both are arrange in three tracking stations. The charged particle tracks are measured in the area around the beam pipe with silicon-strip technology in the Inner Tracker and further outside with straw-tube technology in the Outer Tracker.

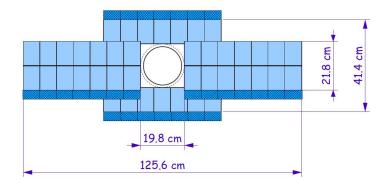

The Inner Tracker covers only 2% of the acceptance but covers 20% of the particles tracks. The IT has a cross like shape with the width of 125 cm and a height of 40 cm covering roughly 4 m<sup>2</sup>. In each station are placed four detector layers (x,u,v,x) where the u and v layer are tilted in the stereo angle by  $\pm 5^{\circ}$ . The strip pitch is 200  $\mu$ m and the detector thickness for the modules amounts to 320  $\mu$ m for the module above and below the beam pipe and to 410  $\mu$ m for the modules at the sides of the beam pipe. The modules are cooled to reduce the effects of the irradiaton and to avoid condensation the modules are flushed with nitrogen at all time.

Figure 3.4: Schematic of the Inner Tracker x-layer. Four detector boxes around the beam pipe are visible. The dark blue edges represent the readout electronics. The figure was taken from [28].

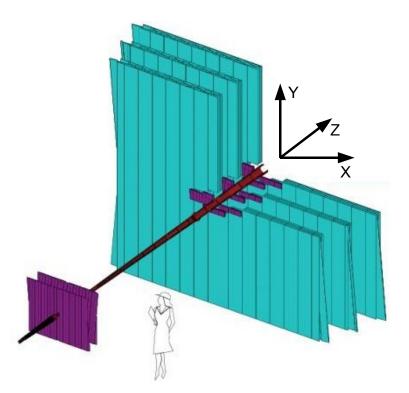

The **Outer Tracker** uses 2.5 m long straw-tubes with an inner diameter of 4.9 mm each. The area covered by the Outer Tracker is roughly  $30 \text{ m}^2$ . In the Section 3.3, the Outer Tracker is described more in detail.

#### Particle ID systems

For the particle identification (PID) two Ring Imaging Cherenkov Detector (RICH) detectors, an electromagnetic calorimeter, a hadron calorimeter and the muon stations are used. The separation of pions and kaons is very important for the physics goals of the LHCb experiment.

#### **RICH** detectors

The RICH detectors use the Cherenkov effect to identify the mass of a particle [29]. When particles pass through a medium (radiator) faster than the speed of light of the medium  $c_m$ , they radiate Cherenkov-light in a cone with an opening angle,  $\Theta_c$ , around the particle direction:

$$\cos(\Theta_c) = \frac{c_m}{v} = \frac{1}{\beta n}.$$

(3.2)

Where n is the refraction index of the medium and  $\beta$  is equal to the ratio of the velocity and the speed of light in vacuum. The measured angle  $\Theta_c$  provides a measurement of the particle velocity. In combination with the particle momentum, it is possible to identify the particle by its mass.

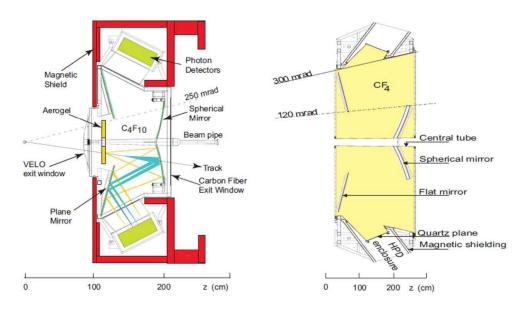

The RICH-1 detector is placed between the vertex detector and the Trigger Turicensis and consists of two radiator materials: 5 cm of silica aerogel (n=1.03) and 85 cm of  $C_4F_{10}$  gas (n=1.0014). Using the emitted light from both radiators it is possible to separate kaons and pions in the range of particle momenta from 1 GeV to 60 GeV. On the left side of Figure 3.6 is a schematic of the RICH-1 detector. Hybrid Photon Detectors (HPDs) are used to detect the emitted photons and to record an image of the resulting rings of Cherenkov light formed by the arrangement of mirrors with a 2.5 mm × 2.5 mm granularity. The RICH 2 detector is situated between the Inner Tracker/Outer Tracker and the electromagnetic calorimeter and uses  $CF_4$  gas with a refractive index of n=1.0005. On the right side of Figure 3.6 is a schematic of the RICH-2 detector. RICH-2 allows PID for particles in the momentum range of 15 GeV up to 100 GeV.

#### Calorimeter systems

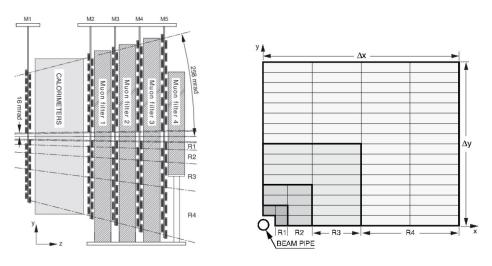

The electromagnetic and hadronic calorimeters are used to measure the energy and position of the particles and to distinguish electrons, photons and hadrons [32]. The system is divided into four components and all four are placed between the M1 and M2 muon stations.

The first component is the Scintillating Pad detector (SPD), which consists of 15 mm thick scintillator tiles used to disentangle electrons and photons. The electrons are detected in the SPD. Behind the scintillator layer a 12 mm lead layer is placed, which induces electromagnetic showers from photons.

The second component is the Pre-shower (PS), which is built with scintillators, which measure the electromagnetic showers induced in the lead layer and SPD in order to disentangle electromagnetic showers from hadronic interactions.

**Figure 3.5:** Schematic of the LHCb RICH detectors. Left: Side View of RICH 1 Right: Top View of RICH 2. [29]

The electromagnetic calorimeter (ECAL) is built as a sampling calorimeter with alternating layers of 2 mm thick lead and 4 mm thick plastic-scintillators connected to PMTs. The depth of the ECAL corresponds to 25 radiation length and about 1 interaction length for hadronic particles. The ECAL measures showers of electrons and photons which are produced through bremsstrahlung and pair-production. The energy resolution of the ECAL is:

$$\sigma(E) \sim \frac{10\%}{\sqrt{E}} \oplus 1\% \tag{3.3}$$

The hadron calorimeter (HCAL) is a sampling calorimeter build from layers of 4 mm scintillators and 16 mm thick iron. The scintillators are connected to PMTs. The total depth of the HCAL is 1.2 m, which corresponds to 5.6 hadron interaction lengths. The energy resolution for hadrons is:

$$\sigma(E) \sim \frac{80\%}{\sqrt{E}} \oplus 10\% \tag{3.4}$$

#### Muon detector

The information of the muon stations is used in the hardware and software trigger and is important for many LHCb measurements. The detector consists of 5 stations placed in front and behind the calorimeters. Four muon stations are placed behind the calorimeters, and the M1 station is placed in front of the calorimeters to improve the tracking [33]. Between all stations of M2-M5 80 cm thick iron absorbers are placed. The majority is built of Multi Wire Proportional Chambers and only around the beam pipe of M1 Gas Electron Multipliers (GEMs) are used.

Figure 3.6: Schematic of the LHCb muon stations. Left: Side View of the five muon stations. Right: Front View of a muon station showing the different granularity. [24]

#### Dipole magnet and beam pipe

The dipole magnet generates a magnet field of 1.1 T with an integrated magnet field  $\int Bdl$  equal to 4 Tm, which is sufficient to bend the charged particle tracks and measure the particle momentum with a resolution of 0.35 % to 0.5 %. The LHCb magnet is a warm magnet and must be cooled with water [31]. The weight of the magnet is 1600 tons.

The LHC beam pipe in the LHCb region is made partially of a beryllium alloy and has a length of 13 m. Beryllium is expensive, toxic and fragile, but the advantage is that beryllium has small Z and therefore a large radiation length. This minimizes the scattering of particles when they pass the beam pipe.

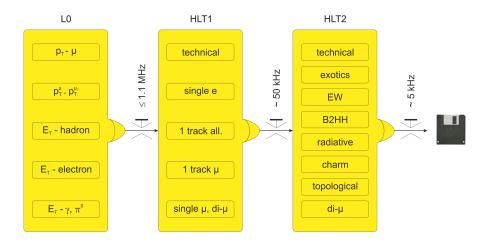

### 3.2.2 LHCb Trigger

The bunch spacing at the LHC is 25 ns with an average event rate of 24 MHz at the LHCb experiment. As it is not possible to store all these events for off-line analysis, it is necessary to trigger the data acquisition only on the interesting physics events to reduce the event rate to roughly 5 kHz [30]. This is realized with a three level trigger system: L0, the lowest trigger level is implemented in hardware, and the two HLT trigger systems are implemented in software running on a PC farm via software. A diagram of the trigger flow in LHCb, and various classes of so-called trigger lines are shown in Figure 3.7.

**Figure 3.7:** A Schematic of the different stages of the LHCb trigger. The Figure was taken from [30] and modified.

#### L0 Trigger

The L0 Trigger was built with custom electronics, and is synchronized to the 40 MHz LHC bunch clock. It reduces the event rate to 1.1 MHz, which is the input rate for the next trigger level, the HLT 1. The L0 trigger exploits the fact that B mesons have a relative large mass, which gives their decay particles a large transverse momentum  $(p_T)$  and a large transverse energy  $(E_T)$ . The decision time for the L0 Trigger is constrained by the depth of the buffers of the on-detector readout boards to buffer the events during the L0 decision, which is 160 LHC clock cycles deep. The decision time of the trigger including the time to transfer the events and the decision must be shorter than 4  $\mu$ s.

The L0 trigger decision is based on a logical OR of several requirements listed in the following:

- hadron  $E_T > 3.5 \,\mathrm{GeV}$

- electromagnetic  $E_T > 2.5 \text{ GeV}$

- muon  $p_T > 1.48 \text{ GeV/c}$

- $p_{T_1} \cdot p_{T_2} > 1.68 \text{ GeV}^2/c^2$  for di-muon events

On a positive L0 decision, the trigger is sent to all other sub-detectors to read out the full detector information of the triggered event.

### HLT Trigger

The HLT is a software trigger, running asynchronously to the LHC clock on roughly 10000 CPUs in parallel, used to select the interesting events and to reduce the output rate to 5 kHz, which is low enough to write these events to tape for the off-line analysis. The HLT is subdivided into two stages: HLT1 and HLT2.

The HLT1 decision uses a logical OR of all HLT1 trigger lines, which are the following:

- technical trigger (e.g. minimum bias)

- one track trigger

- single muon trigger

- di-muon trigger

The output rate of the HLT1, which is directly the input rate of the HLT2, is 50 kHz.

The HLT2 uses all the detector information and performs an track reconstruction. These tracks are used to reconstruct and select composite particles, based on variables like invariant mass and decay time. The different trigger lines in the HLT2 correspond to the different physics analysis of the LHCb experiment. The HLT2 decision is based on a logical OR of all the HLT2 trigger lines. After a positive HLT2 decision, the event is written to tape. It is possible to prescale the HLT rate, if the output rate does not fit the bandwidth with which it is possible to write to tape. Typically this is 5 kHz and the event size is  $\sim$ 50 kByte.

# 3.3 Outer Tracker

The Outer Tracker and the Inner Tracker provide positive information for charged particles for the tracking between the magnet and the second RICH detector [27]. The spatial resolution of the straw-tube detector is ~200  $\mu$ m and it covers an area of ~ 5×6 m<sup>2</sup> with 12 layers of straw-tube modules. The straw-tubes have a inner diameter of 4.9 mm and a length of 2.5 m. The detector is filled with a Ar/CO<sub>2</sub>/O<sub>2</sub> (70/28.5/1.5) gas mixture, which has a fast drift velocity and results into a maximum drift time of 45 ns. The oxygen was added to the detector gas mixture to prevent aging, which is caused by a contamination of the counting gas due to outgassing of the plastifier di-isopropyl-naphthalene in the epoxy glue Araldite A: AY103-1 [34], which was used for the construction of the modules. The straw-tubes work as proportional counter with an anode wire, which has a diameter of 25  $\mu$ m and is made of gold plated tungsten. The cathode of the straw-tube is a three layer foil. The two inner layers are a double layer of conducting Kapton-XC foil, where the inner Kapton layer serves as the cathode. The outer

layer is a 12.5  $\mu$ m layer of Kapton-aluminum, which guarantees gas tightness and electrical shielding. The straw-tubes are arranged in a gas-tight module, which is made of panels sealed with 400  $\mu$ m thick carbon fiber.

The complete Outer Tracker consists of 168 long and 96 short modules and comprises 53,760 single straw-tube channels. Four module layers are placed in each of the three T-stations, and results into a radiation length of only 2 % X<sub>0</sub>. The corresponding four module layers are arranged in three T-stations in an x-uv-x geometry: the modules in the x-layers are oriented vertically, whereas those in the u and v layers are tilted by  $+5^{\circ}$  and  $-5^{\circ}$  with respect to the vertical. Each T-station is divided in 4 C-frames, two on the left side of the beam pipe and 2 on the right side of the beam pipe. Each C-frame hosts two layer of modules (x-u or v-x) and it is possible to move the C-frames on rails to the outside away from the beam pipe. At the end of the C-frames all the cables and tubes for the power, high voltage, slow control and fast control, data fiber, water cooling and gas are hosted in cable chains.

Figure 3.8: Figure of the Outer Tracker (turquois) and the Inner Tracker, Trigger Tracker (purple). The modular structure of the Outer Tracker is visible. The Figure was taken from [38] and modified.

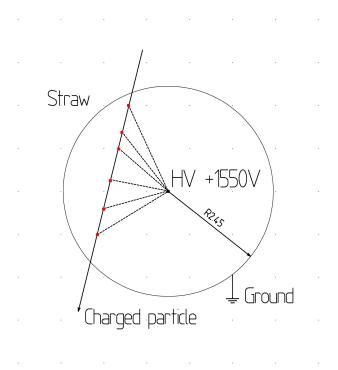

## 3.3.1 Functional principle of the straw-tubes

The charged particles traversing the gas filled straw-tube generate ionization clusters along the particle track's length. The electric field in the straw-tube separates the ions and electrons and the electrons drift to the anode wire in the center. The average drift velocity is around  $62.5 \,\mu\text{m/ns}$  [36]. When the distance to the wire is only in the order of the wire diameter, gas amplification starts. The average kinetic energy of the electrons, which they gain between two collisions from the electric field, is high enough to ionize the gas atoms in this region. The gas amplification for the Outer Tracker straw-tubes with nominal high voltage of 1550 V is roughly 50,000 [37]. This amplification results into a detectable charge, which is high enough for the sensitive ASDBLR channel input.

**Figure 3.9:** Figure of the Straw-tube. When a charged particle travels through the gas filled tube, it generates ionization clusters, which drift in the direction of the electric field.

To determine the distance of the track to the anode wire, the arrival time relation to the LHC clock is measured. With the knowledge of the time of flight of the particle and the signal propagation time, the drift time can be calculated. The distance of the track is calculated with the drift time and the r-t-relation.

## 3.3.2 Outer Tracker readout electronics

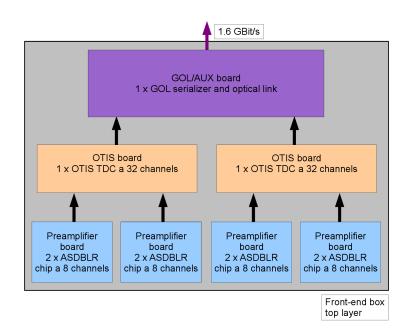

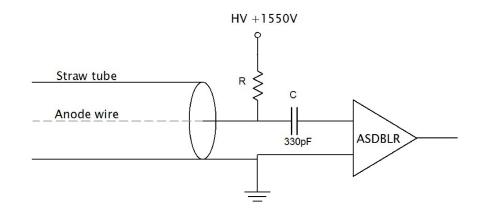

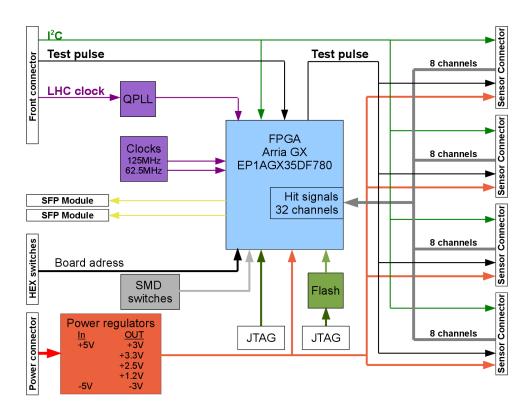

In this part, the existing readout electronics of the Outer Tracker is described. The main parts of the electronics is hosted in the on-detector front-end box. In Figure 3.10 a schematic of the front-end electronics can be seen.

Figure 3.10: Schematic of an Outer Tracker front-end box. The hit signals from the ASDBLR pre-amplifier chips are connected to OTIS TDCs which measure the timing of the hit signals. The time and hit information is transmitted to the GOL serializer chip. This chip serializes the data from 4 OTIS chips and the data are sent to the back-end electronics with a 1.6 GBit/s optical link.

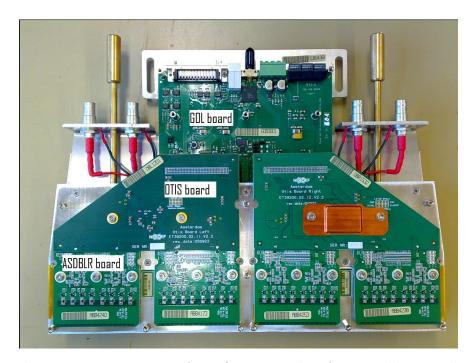

The front-end box is a metal box, which is mounted to the end of an Outer Tracker module, to read out the detector signals and to measure the drift times of the straw-tube detector. The front-end box is connected with 2 long screws to a module, which guaranties a good grounding of the readout boards. The readout electronics inside the front-end box is divided into three types of PCBs. The first board is the ASDBLR pre-amplifier board. Two of them are connected to one TDC board the OTIS board. Four OTIS boards are connected to one Gbit optical link board the GOL board. Each front-end box has only one GOL board. In addition to the readout electronics, also the high voltage of the straw-tubes, are distributed through four high voltage boards inside the front-end box. All the electronic in the front-end box has to sustain a radiation dose of 2 krad. In Figure 3.11 a picture of an opened front-end box can be seen.

Figure 3.11: Picture of an Outer Tracker front-end box. The 4 top-side ASDBLR preamplifier boards are visible, the other 4 are mounted on the down-side of the front-end box. Furthermore, the corresponding 2 TDC boards (OTIS boards) and the one GOL board for the ECS, TFC and data transmission are visible. The high voltage boards are not visible. They are mounted in the layer below the ASDBLR boards. The picture was taken from [39] and modified.

#### HV board

Each of the four HV boards in a front-end box distributes the high voltage to 32 straw-tubes, and decouples the detector signal from the anode voltage and provides it to the ASDBLR inputs with a 330 pF capacitance. A schematic picture of the signal readout is shown in Figure 3.12.

**Figure 3.12:** Schematic picture of the Outer Tracker front-end HV board. The straw-tube is grounded (cathode) and the anode wire is connected to the high voltage (1550 V). The straw signal is coupled with a 330 pF capacitance to the ASDBLR channel.

#### ASDBLR board

The ASDBLR board hosts two ASDBLR chips (Amplifier Shaper Discriminator with BaseLine Restoration) [40], which were developed for the TRT of the ATLAS experiment. The ASDBLR chip has 8 input channels, and if a pulse is higher than the threshold value, the chip generates a digital differential signal, which is used for the drift time measurement in the OTIS (TDC) chip. The threshold value is set with a DAC in the OTIS chip.

#### **OTIS** board

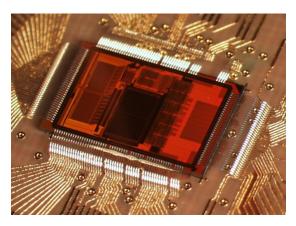

The OTIS chip (Outer Tracker Time Information System) is a custom made ASIC to measure the drift time for 32 channels with respect to the rising edge of the 40 MHz LHC clock with a precision of <1 ns [41]. To achieve this, the OTIS chip divides the LHC clock in 64 time bins with a chain of 64 inverters arranged in a DLL (delay locked loop). Each of the time bins has a size of 390 ps. For each of the 32 straw-tubes the OTIS chip has 64 register cells to store the status of the inverter chain. In case of a digital hit signal from the ASDBLR the status of the inverter chain is stored in the corresponding 64 registers for this channel and the decoder of the OTIS chip decodes the 64 time bit information for each channel to a 6 bit time stamp with an additional hit bit. In addition to this information the OTIS chip stores also the BX-counter and status information bits in the L0 buffer. This memory is 240 bit wide and 163 words deep. After a L0 decision time of 4  $\mu$ s (160 LHC clock cycles) the L0 trigger decides whether the data is read out via the GOL/AUX board or the data is overwritten by new events. The maximal average LO trigger rate is 1.1 MHz. In addition to the TDC function, the OTIS chip provides four 8 bit DAC to control the ASDBLR thresholds.

Figure 3.13: The OTIS-TDC chip developed in Heidelberg for the drift time measurement of the LHCb Outer Tracker. The TDC can measure the drift time for 32 channels with a time resolution below 1 ns. The Figure is taken from [42].

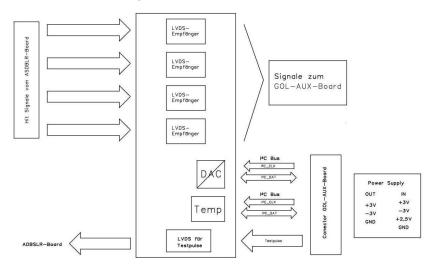

# GOL/AUX board

The GOL/AUX board connects to four OTIS boards. It provides the fast control and slow control interface as well as the power to the connected electronics. Using the GOL chip the board serializes the TDC data. An optical link with 1.6 GBit/s is used to transmit the data to the back-end electronics, the TELL1 board which is placed in the counting house behind the shielding wall. The data are 8/10 bit encoded for the transmission.

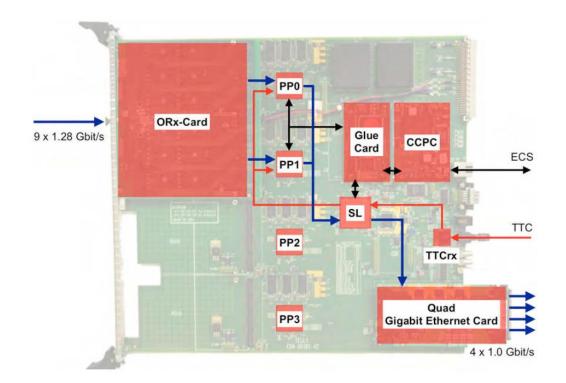

#### TELL1 buffer board

A TELL1 board in the Outer Tracker receives the data of the nine front-end boxes of one quarter layer. The main purpose of the TELL1 board is to synchronize the L0 triggered events and to do consistency checks, zero-suppression of the data and to buffer the data. The data are formatted and send to the HLT farm. In Figure 3.14 a picture of the TELL1 board is shown. The Outer Tracker TELL1 uses only one optical receiver card the ORx-card. The TELL1 is a 9U VME-PCB and is placed in a VME crate in the counting house behind the shielding wall, which makes the usage of commercial electronics possible. The TELL1 board uses 1 GBit/s Ethernet to send the data to switches which distributes the data further into the HLT farm. The maximal output bandwidth of the TELL1 board is 4 GBit/s (4  $\times$  1 GBit Ethernet) and the maximal input bandwidth is 24  $\times$  1.6 GBit/s = 38.4 GBit/s, which makes a zero-suppression very important.

Figure 3.14: Picture of the LHCb TELL1 board [43]. The data from 9 optical fibers are deserialized with one ORx card and send to the 2 pre-processing FPGAs, which perform a consistency check and suppress empty channels. After this, the data is sent to the Sync-Link-FPGA. The second FPGA stage builds the events and prepares the data package for the  $4 \times 1$  GBit/s Ethernet ports (Quad-GBE-Card). Reset and Trigger signals coming from the Timing Trigger and Control receiver (TTCrx), which is connected to the TFC system. The information of the Experiment Control System (ECS) is distributed through a Credit Card sized PC (CCPC).

# 3.4 Luminosity leveling

To maximize the event yield for the different analysis, LHCb is running at a constant luminosity of  $4 \cdot 10^{32}$  cm<sup>-2</sup>s<sup>-1</sup> during a proton fill [35]. For ATLAS and CMS the instant luminosity is higher at the beginning of a fill but it decreases exponentially during the fill. The LHCb experiment realizes the constant luminosity by displacing the two proton beams and monitoring the instant luminosity. In case the instant luminosity falls below a certain level the two beams are moved closer to each other. In this way it is possible to realize constant data tacking conditions throughout the fill and a maximum amount of high quality events can be recorded.

# $_{\text{CHAPTER}}4$

# LHCb upgrade

In the data taking period from March 2010 to December 2012, the LHCb experiment was operated at a luminosity up to  $4 \cdot 10^{32} \text{ cm}^{-2} \text{s}^{-1}$  with an average number of interactions per crossing of  $\mu \approx 1.5$ . The detector recorded a data sample which corresponds to an integrated luminosity of  $3.2 \text{ fb}^{-1}$ . Extrapolating from the 2012 operation the collaboration expects for the period 2015-2017 to record data corresponding to a total integrated luminosity of 8 fb<sup>-1</sup> [2].

After this, the plan is to upgrade the detector in 2018 to be able to collect  $>50 \text{ fb}^{-1}$  in the following years with an instantaneous luminosity of  $2 \cdot 10^{33} \text{ cm}^{-2} \text{s}^{-1}$ . As already discussed in Chapter 2.3 the data set would improve measurements which are limited by statistics so far for example the branching ratio of the decay channel  $B_d^0 \rightarrow \mu^+ \mu^-$ . It is also worth to mention that the LHCb upgrade is independent of the LHC high luminosity upgrade, because the foreseen instantaneous luminosity of  $2 \cdot 10^{33} \text{ cm}^{-2} \text{s}^{-1}$  is well below even the current LHC luminosity of  $10^{34} \text{ cm}^{-2} \text{s}^{-1}$  for ATLAS and CMS.

In March 2011, the collaboration submitted a Letter of Intent (LOI) describing the upgrade procedure [12]. In May 2012 the Framework Technical Design Report (TDR) was released and subsequently endorsed by the LHCC [45]. The informations shown in this chapter are taken from these two documents. The necessary R&D is in full progress and the corresponding subsystem TDRs will follow until early 2014.

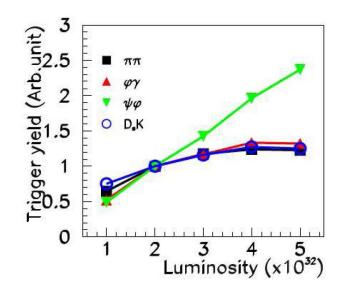

# 4.1 Upgrade of the Trigger

Only increasing the instantaneous luminosity does not guarantee a higher number of recorded heavy flavor events. First, these events have to be triggered and later to be recorded. It was investigated how the trigger yield would develop with the current readout electronics of the LHCb detector and the current trigger. In addition, the trigger yield for final states with muons was investigated which would increase linearly with an increasing luminosity, but for hadronic and semileptonic final states the trigger yield would saturate at a luminosity of above  $4 \cdot 10^{32}$  cm<sup>-2</sup>s<sup>-1</sup>. The trigger yield for final states with muons and for hadronic and semileptonic final states as function of the instantaneous luminosity can be seen in Figure 4.1. The maximum detector readout rate, which is limited to 1.1 MHz causes the described trigger yield saturation. This can be explained as follows. If the luminosity is increased the rate for hadronic and semileptonic final states would exceed 1.1 MHz. To limit the trigger rate to 1.1 MHz the L0 hadron thresholds  $E_T$  and  $p_T$  have to be increased, but this also decreases the trigger yield for these channels.

Figure 4.1: The trigger yield of final states with muons and final states with hadrons against luminosity. Muon final states increase linearly with higher luminosities but final states with hadrons approach saturation around a luminosity of above  $4 \cdot 10^{32} \text{ cm}^{-2} \text{s}^{-1}$ . The Figure was taken from [12].

To improve the trigger yields for the hadronic modes, one would like to lower the L0 hadron thresholds  $E_T$  and  $p_T$ . This cannot be done using a hardware trigger which is only based on  $E_T$  and  $p_T$  of the particles. A full event reconstruction is needed for the event selection, using the complete detector information and all the event information in a flexible software trigger (upgraded HLT). All LHCb sub-detectors have to be read out with 40 MHz.

# 4.2 Upgrade of the LHCb sub-detectors

In the following the upgrade plans for the different sub-detectors will be presented. The sequence goes from the vertex detector at the proton-proton collision point to the muon stations.

# 4.2.1 Vertex detector upgrade

The LHCb Vertex Detector has been built to collect a data set of ~10 fb<sup>-1</sup> which will be reached 2018. Afterwards, the vertex detector has to be replaced, due to radiation damages. The VELO is the LHC sub-detector with the smallest distance to the beam. The replacement for the installed vertex detector will be improved compared to the current detector to cope with the higher multiplicity and the 40 MHz readout. It is foreseen to use a smaller segmentation for a more efficient secondary vertex reconstruction in events with multiple interactions per crossing, a much higher radiation hardness (370 Mrad in 10 years) and a low material budget to avoid multiple scattering. It is planned to use the VeloPix chip with 55  $\mu$ m × 55 $\mu$ m pixels which is based on the Timepix3 and uses a 130 nm process technology, which is proven to sustain a total radiation dose of more than 400 Mrad. Extensive R&D is ongoing to investigate the optimal module layout and mechanics, sensor material like planar or 3D silicon and a possible diamond cooling substrate. Furthermore, another topic of interest is the construction of the new RF foil.

# 4.2.2 RICH detector upgrade

The RICH detectors are necessary for particle identification (PID), so the RICH detectors on both sides of the magnet will remain. The aerogel in RICH1 will be removed to reduce the occupancy. In addition, new photon detectors and new readout electronics are needed to allow the readout with 40 MHz, because the front-end electronics is embedded into the vacuum of the current used Hybrid Photon Detectors. The baseline solution for the new photon detectors are 64-channel multi anode Photomultiplier tubes with a new readout chip.

# 4.2.3 Tracker Turicensis upgrade

The Tracker Turicensis has to be replaced as the front-end electronics are part of the silicon sensors and it has a maximal readout rate of 1.1 MHz. For the optimal operation in the upgrade environment, it is being considered to have a TT nearer to the beam axis and a smaller vertical segmentation.

# 4.2.4 Tracking station upgrade

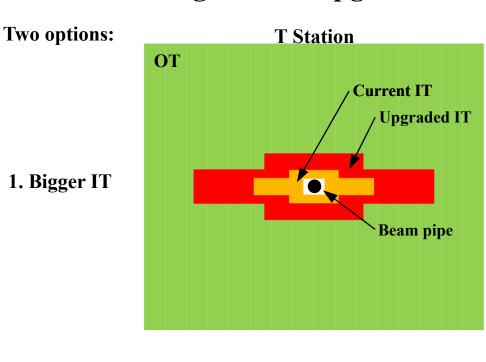

The readout electronics of the tracking system behind the magnet have to be changed to a 40 MHz readout. In addition to the new front-end development the current Outer Tracker would have to be replaced close to the beam pipe, due to the fact that the occupancy with an instantaneous luminosity of  $2 \cdot 10^{33}$  cm<sup>-2</sup>s<sup>-1</sup> can reach more than 25% where an effective tracking is not possible [12]. It should be kept in mind, that the current Outer Tracker is a gaseous detector using straw tube technology. Two options are possible to cope with the high occupancies in the inner part:

1. Double the width and height of the Inner Tracker and use shorter Outer Tracker modules in the vicinity of the beam pipe. The new Inner Tracker area would rise by a factor of 4. This option is depicted on the top of Figure 4.2.

2. Replacing the Inner Tracker and the Outer Tracker modules in the central region with a fiber tracker. This option is depicted on the bottom of Figure 4.2. The fiber modules would consists of 5 fiber layers in each module, each fiber with a diameter of 250  $\mu$ m. For the readout, silicon photo multiplier (SiPM) arrays are considered. Active R&D is ongoing to investigate the radiation hardness of the fibers and the SiPM arrays. In addition, questions regarding construction and assembly of such a detector have to be solved and a complete new readout electronics has to be developed.

In both solutions the remaining Outer Tracker modules need new readout electronics to cope with the new 40 MHz readout. It is considered to replace the custom made OTIS readout chips by an FPGA on which the time measurement is implemented. The crucial point about this design is the radiation tolerance of the FPGA, which was tested. The LHCb group of the Physikalische Institut Heidelberg tested a SRAM-based FPGA from Altera and a second group from NIKHEF<sup>1</sup> investigated the feasibility to use a flash-based FPGA from Mirosemi (Actel). The Heidelberg studies are the work of this thesis.

It should also be kept in mind that a third solution is possible, for which the whole IT and OT would be replaced by a fiber tracker. In this case no new readout electronics for the LHCb Outer Tracker is necessary. However, for the readout of the Fiber Tracker, FPGAs are also considered.

#### 4.2.5 Calorimeter upgrade

The calorimeters will keep all modules and PMTs, but the PMT gain will be reduced by a factor of 5 to keep the current constant due to higher occupancy. In addition, the front-end electronics will be changed to compensate for the lower

<sup>&</sup>lt;sup>1</sup>National Institute for Nuclear and High energy physics Amsterdam

# **Tracking Station Upgrade**

Figure 4.2: The two options for the tracking stations to replace the high occupancy part of the Outer Tracker.

1. Using an increased Inner Tracker with shortened Outer Tracker modules around the beam pipe.

2. Replacing the Inner Tracker and the the Outer Tracker modules in the central region with fiber tracker modules. gain and to allow for a readout with 40 MHz. The PS and SPD will be removed and the  $e/\gamma/hadron$  separation at the higher level will take place in the new HLT using the tracking information.

## 4.2.6 Muon detector upgrade

The muon chambers are expected to fulfill the upgrade requirements nevertheless aging and occupancy studies are ongoing to confirm the present expectations. Furthermore, the muon chambers are already readout at 40 MHz in the current L0 trigger, which results in the fact that the front-end electronics can be kept. The M1 station in front of the calorimeters will be removed, because the tracking stations will perform a better muon momentum resolution in the upgraded trigger and the M1 station is not useful any more.

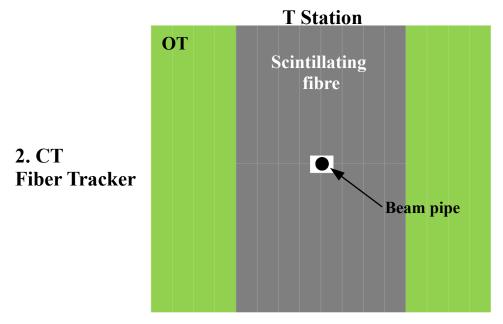

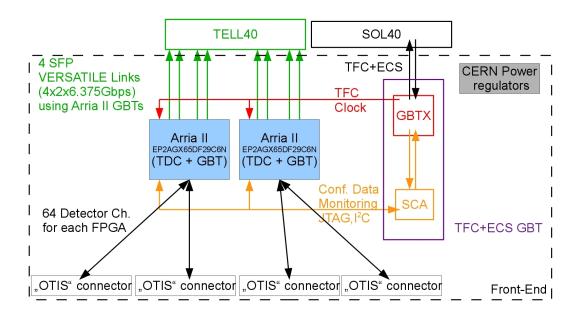

# 4.3 Upgrade of the LHCb readout electronics

To migrate the LHCb detector to a trigger-free 40 MHz front-end readout, almost all sub-detectors have to upgrade their readout electronics. The front-end electronics will host the pre-amplifiers, ADCs or TDCs, zero suppression, derandomising buffer and fast optical transceivers. Figure 4.3 shows a schematic of the readout electronics changes. The current L0 buffers in the front-end will be removed, due to the fact that all events will be transmitted to the new buffer board, namely TELL40 board. These events will be already zero-suppressed in the frontend to reduce the necessary bandwidth for the optical GBit/s transceivers. The TELL40 board is the upgraded version of the TELL1 board. The TELL40 board will host fast optical receivers and the low level trigger rate control. After the data is formated, it is transmitted to the event filter farm (upgraded HLT) using 10 GBit/s Ethernet ports. The upgraded HLT will have roughly a 5-7 times higher output rate compared to the current HLT output rate of 5 kHz. A bigger CPU farm, more disk space and more computing power will be needed to cope with the higher number of events at the output of the HLT.

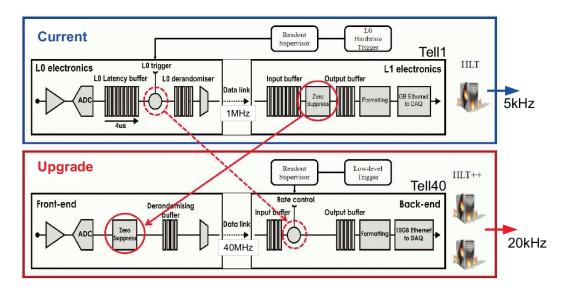

# 4.3.1 Upgrade of the OT front-end box to 40 MHz readout

The readout chips inside the front-end box of the LHCb Outer Tracker have to be exchanged for the upgrade to a 40 MHz readout. Figure 4.4 depicts a opened front-end box with the three types of PCBs visible. The ASDBLR board can be kept, as the ASDBLR chip is radiation hard beyond the radiation level of the upgrade. The OTIS TDC chip would be radiation hard enough, but the readout rate of the chip is limited to 1.1 MHz. In addition, the GOL/AUX board had also to be redeveloped. The expected bandwidth of the upgraded Outer Tracker front-end box is between 20-30 GBit/s, depending on the data formatting and the number of TDC bits used for the drift-time measurement. TDC bits for the

**Figure 4.3:** Figure of the current and upgraded LHCb readout electronics. The Figure was taken from [46] and modified.

drift-time measurement are used. A drift-time with 4 bits, corresponding to a TDC bin size of 1.6 ns, would be the lower limit to reach the spacial resolution of 200  $\mu$ m, which is the requirement for the track reconstruction.

# 4.4 LHCb upgrade schedule

In the first long LHC shutdown till 2013 - 2014 the LHCb detector will be maintained and preparations for optical fibers and cables will be done. In addition, the LHCb subsystem TDRs will be submitted to LHCC.

After the first long shutdown LHCb is to take data with a center of mass energy of 14 TeV and 25 ns bunch spacing from 2015-2017. In parallel the production and quality control of new components will be conducted.

The schedule for the LHCb upgrade sees the installation and commissioning of the upgraded detector during the second long shutdown in 2018/2019. After 2019, LHCb will run at a higher luminosity and with new sub-detector components.

**Figure 4.4:** The current front-end box with the three PCB types: the ASDBLR board, OTIS board and GOL/AUX board. The eight ASDBLR boards can be reused for the upgrade. The OTIS chip readout rate of 1.1 MHz is too low for the upgrade and also the GOL/AUX board has to be redesigned, because the bandwidth of 1.6 GBit/s is too low. The picture was taken from [47] and modified.

# CHAPTER 5

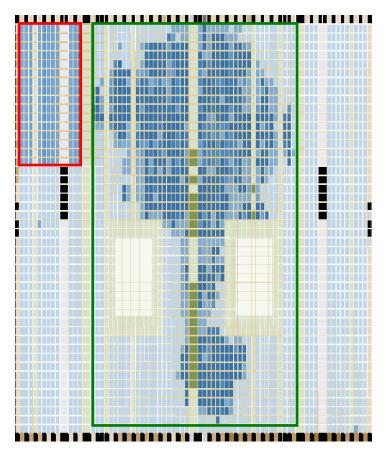

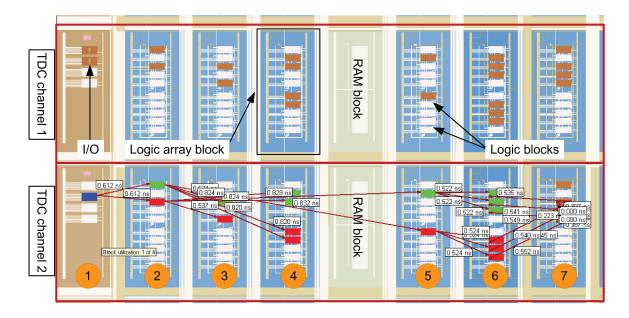

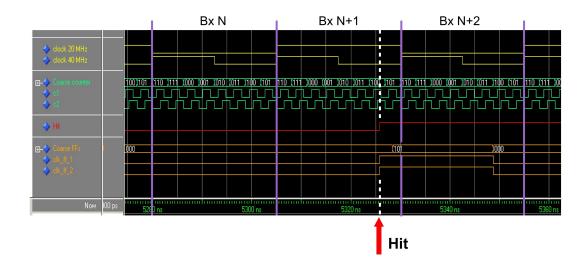

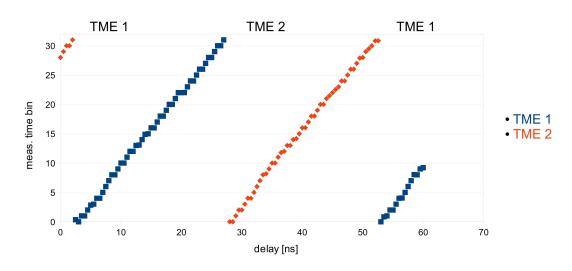

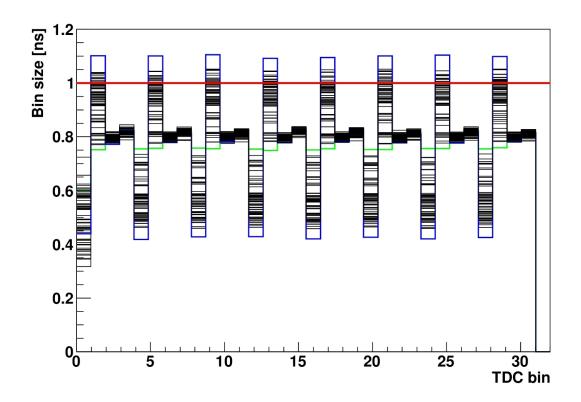

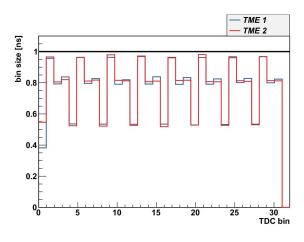

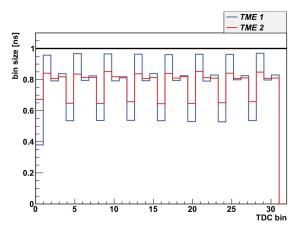

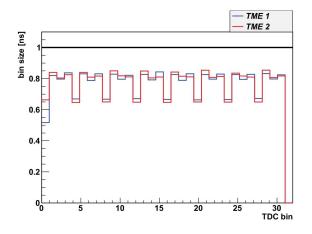

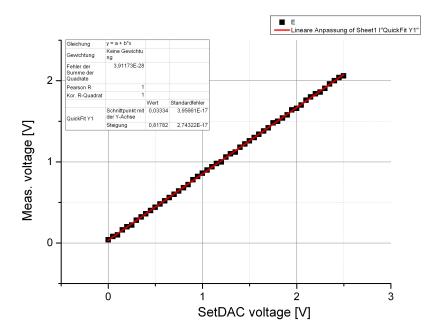

# FPGA-based time measurement