Dissertation

submitted to the

Joint Faculties for Natural Sciences and Mathematics

of the Ruperto Carola University of

Heidelberg, Germany,

for the degree of

Doctor of Natural Sciences

presented by

Dipl.Phys.: George Victor Andrei born in: Rosiori de Vede, Romania

Heidelberg, October 27, 2010

# The Data Path of the ATLAS Level-1 Calorimeter Trigger PreProcessor

Gutachter: Prof. Dr. Karlheinz Meier

Prof. Dr. Reinhard Männer

There's no problem, only solutions.

J.L.

#### ZUSAMMENFASSUNG

Der Pre-Prozessor im "ATLAS Level-1 Calorimeter Trigger" liefert digitale Werte für transversale Energie in Echtzeit an nachfolgende Prozessoren, die physikalische Reaktionsprodukte erkennen sollen. Der Eingang besteht aus mehr als 7000 analogen Signalen von Zellen reduzierter Granularität in den Kalorimetern des ATLAS-Detektors. Die "Level-1 Trigger"-Entscheidung muß überprüfbar sein. Dazu werden vom Prozessor Kopien digitalisierter Echtzeit-Daten an die ATLAS Datenaufzeichnung gereicht. Zusätzlich stellt das Pre-Prozessor System mit dem standartisierten VME-Bus eine Schnittstelle zur Computer-Infrastruktur des Experiments zur Verfügung, worüber Konfigurationsdaten geladen und Kontrol- bzw. Monitor-Daten ausgelesen werden.

Ein zweckorientiertes System, welches sowohl den Transfer zur Aufzeichnung von Ereignisdaten in ATLAS als auch Datenaustausch über VME gewährleistet, wurde auf den 124 Modulen des Pre-Prozessor Systems in Form des "Readout Managers" implementiert. Das "Field-Programmable-Gate-Array (FPGA)" findet sich auf jedem der Module. Der erste Teil dieser Arbeit beschreibt die Algorithmen, die entwickelt wurden, um die Funktionalität des "Readout Managers" zu erfüllen. Der zweite Teil behandelt die Tests, welche durchgeführt wurden, um eine korrekte Funktion der Module sicherzustellen bevor sie bei CERN in der ATLAS-Kaverne installiert wurden.

#### **ABSTRACT**

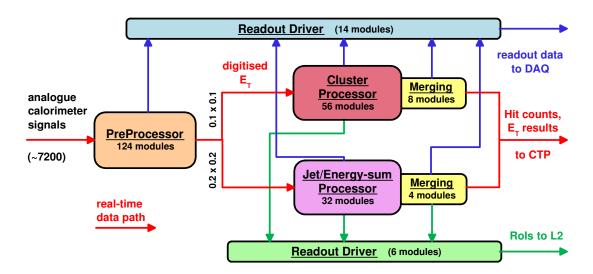

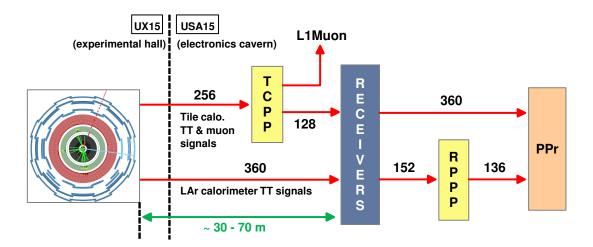

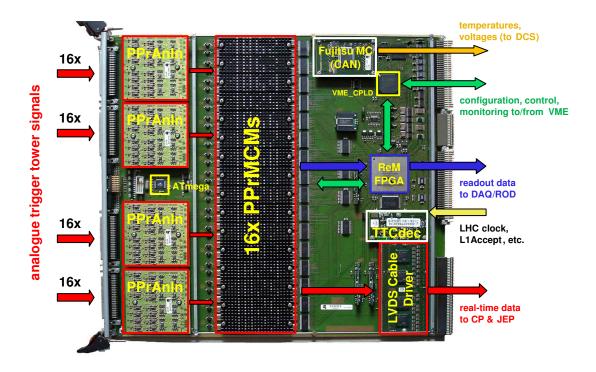

The PreProcessor of the ATLAS Level-1 Calorimeter Trigger provides digital values of transverse energy in real-time to the subsequent object-finding processors. The input comprises more than 7000 analogue signals of reduced granularity from the calorimeters of the ATLAS detector. The Level-1 trigger decision must be verified. For this, the PreProcessor transmits copies of the real-time digital data to the Data Acquisition (DAQ) system. In addition, the PreProcessor system provides a standard VMEbus interface to the computing infrastructure of the experiment, on which configuration data is loaded and control or monitoring data are read out.

A dedicated system that ensures both the transfer of event data to storage in ATLAS and the data transfer over the VME was implemented on the 124 modules of the PreProcessor system in the form of a "Readout Manager". The "Field Programmable Gate Array" (FPGA) is located on each module. The first part of this work describes the algorithms developed to meet the functionality of the Readout Manager. The second part deals with the tests that were carried out to ensure the proper functionality of the modules before they were installed at CERN in the ATLAS cavern.

# **Contents**

| 1 | Intr | oduction         | n                                                          | 1  |  |  |  |  |  |

|---|------|------------------|------------------------------------------------------------|----|--|--|--|--|--|

| 2 | Phys | ysics Motivation |                                                            |    |  |  |  |  |  |

|   | 2.1  | The Sta          | andard Model of Particle Physics                           | 3  |  |  |  |  |  |

|   |      | 2.1.1            | The Higgs Mechanism                                        | 4  |  |  |  |  |  |

|   |      | 2.1.2            | The Search for the Higgs Boson                             | 6  |  |  |  |  |  |

| 3 | The  | ATLAS            | S Experiment at the LHC                                    | 11 |  |  |  |  |  |

|   | 3.1  | The La           | arge Hadron Collider                                       | 11 |  |  |  |  |  |

|   |      | 3.1.1            | Machine Parameters                                         | 12 |  |  |  |  |  |

|   |      | 3.1.2            | Experimental Challenges at the LHC                         | 14 |  |  |  |  |  |

|   | 3.2  | The Al           | ΓLAS Detector                                              | 16 |  |  |  |  |  |

|   |      | 3.2.1            | The Coordinate System                                      | 16 |  |  |  |  |  |

|   |      | 3.2.2            | The Magnet System                                          | 18 |  |  |  |  |  |

|   |      | 3.2.3            | The Inner Detector                                         | 19 |  |  |  |  |  |

|   |      | 3.2.4            | The Calorimetry                                            | 21 |  |  |  |  |  |

|   |      | 3.2.5            | The Muon Spectrometer                                      | 26 |  |  |  |  |  |

|   |      | 3.2.6            | The Trigger, Data Acquisition and Detector Control Systems | 28 |  |  |  |  |  |

| 4 | The  | ATLAS            | 5 Trigger and Data Acquisition Systems                     | 31 |  |  |  |  |  |

|   | 4.1  | The Ar           | rchitecture of the TDAQ System                             | 31 |  |  |  |  |  |

|   | 4.2  |                  | evel-1 Trigger                                             | 33 |  |  |  |  |  |

|   |      | 4.2.1            | The Calorimeter Trigger                                    | 34 |  |  |  |  |  |

|   |      | 4.2.2            | The Muon Trigger                                           | 34 |  |  |  |  |  |

|   |      | 4.2.3            | The Central Trigger Processor                              | 35 |  |  |  |  |  |

|   | 4.3  | The Hi           | igh-Level Trigger and the DAQ                              | 36 |  |  |  |  |  |

| 5 | The  | ATLAS            | S Level-1 Calorimeter Trigger                              | 37 |  |  |  |  |  |

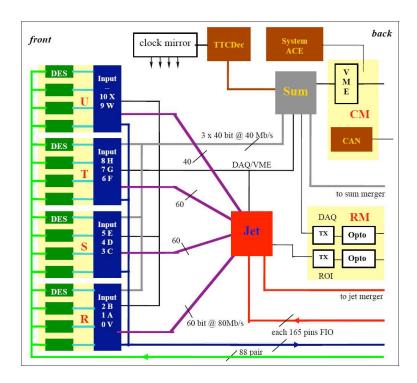

|   | 5.1  |                  | rchitecture                                                | 37 |  |  |  |  |  |

|   | 5.2  |                  | nalogue Input                                              | 38 |  |  |  |  |  |

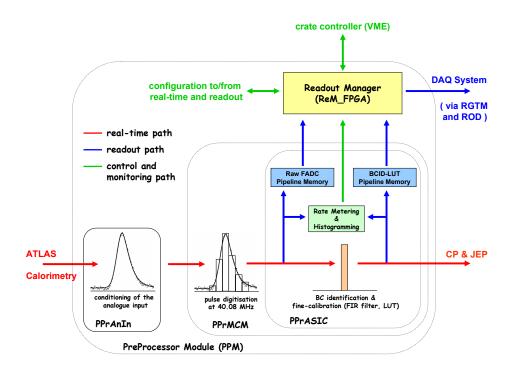

|   | 5.3  |                  | eProcessor                                                 | 41 |  |  |  |  |  |

|   |      | 5.3.1            | Tasks                                                      | 41 |  |  |  |  |  |

|   |      | 532              | Hardware Realisation                                       | 42 |  |  |  |  |  |

IV CONTENTS

|   | 5.4 | The Cl   | luster Processor                                               | 51  |

|---|-----|----------|----------------------------------------------------------------|-----|

|   |     | 5.4.1    | Trigger Algorithms                                             |     |

|   |     | 5.4.2    | Hardware Realisation                                           |     |

|   | 5.5 | The Je   | et/Energy-sum Processor                                        | 55  |

|   |     | 5.5.1    | Trigger Algorithms                                             |     |

|   |     | 5.5.2    | Hardware Realisation                                           | 56  |

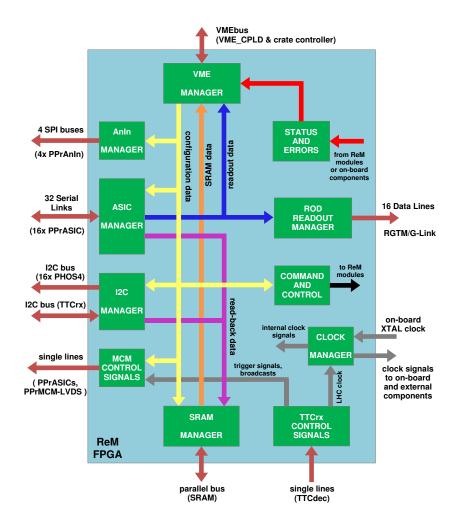

| 6 | The | Readou   | ut Manager of the PreProcessor Module                          | 59  |

|   | 6.1 | Functi   | onal Overview                                                  | 61  |

|   | 6.2 | Comm     | nunication with the On-board and External Devices              |     |

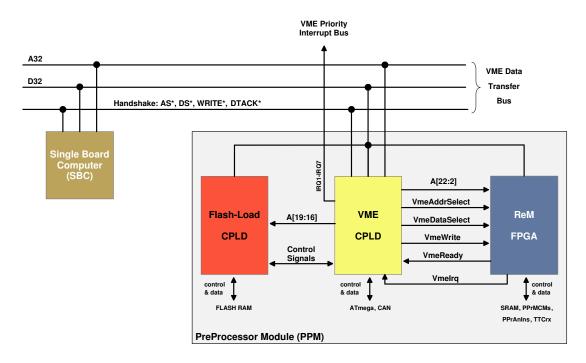

|   |     | 6.2.1    | The Interface to VME                                           |     |

|   |     | 6.2.2    | Access to the On-board SRAM                                    | 65  |

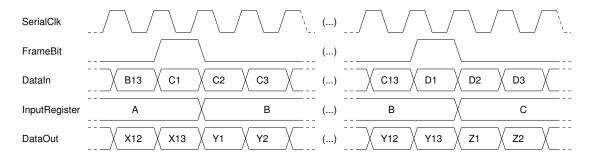

|   |     | 6.2.3    | The Serial Interfaces to the PPrASICs                          | 66  |

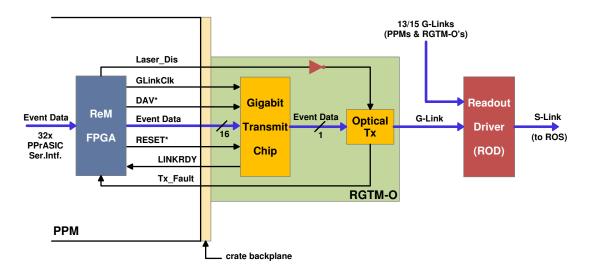

|   |     | 6.2.4    | The Interface to DAQ System                                    |     |

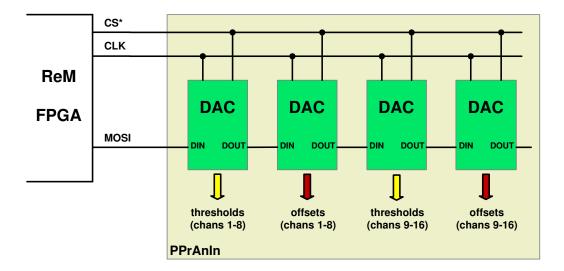

|   |     | 6.2.5    | The SPI Interface to the PPrAnIn-DACs                          | 68  |

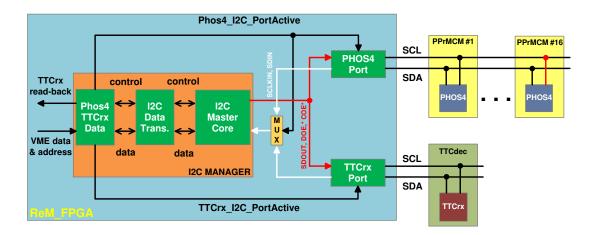

|   |     | 6.2.6    | The $I^2C$ Interfaces to the PPrPHOS4s and the TTCrx           | 70  |

|   |     | 6.2.7    | Control and Status Signals                                     |     |

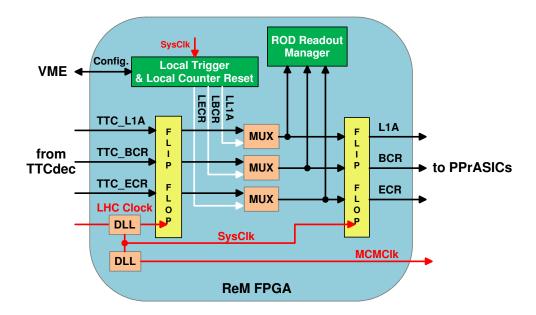

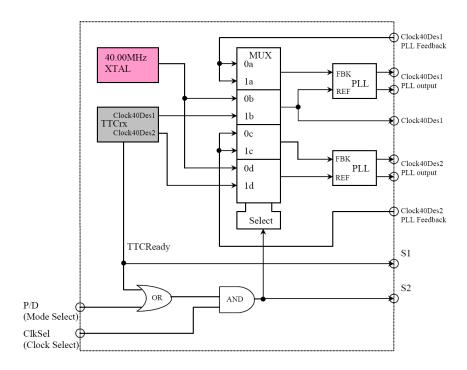

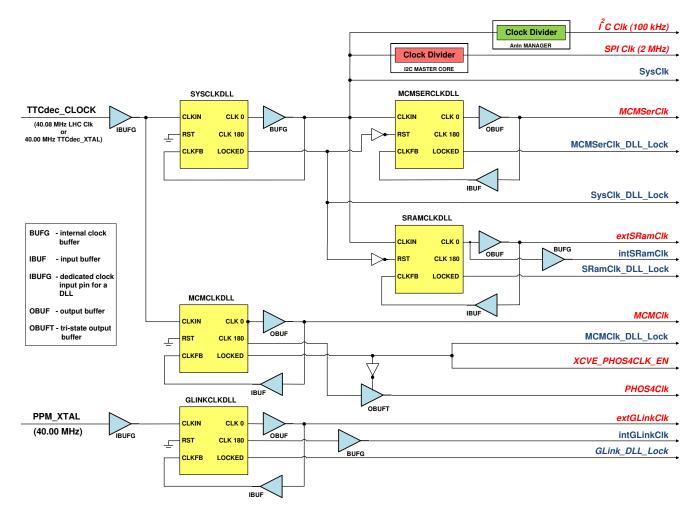

|   | 6.3 | Clock    | Management                                                     | 78  |

|   | 6.4 |          | oution of Configuration Data                                   |     |

|   |     | 6.4.1    | PPrASIC Configuration                                          | 81  |

|   |     | 6.4.2    | PPrAnIn-DAC Configuration                                      |     |

|   |     | 6.4.3    | PPrPHOS4 Configuration                                         | 89  |

|   |     | 6.4.4    | TTCrx Configuration                                            | 91  |

|   |     | 6.4.5    | PPrMCM-LVDS Configuration                                      | 92  |

|   |     | 6.4.6    | Configuration Restrictions                                     | 92  |

|   | 6.5 | PPrAS    | SIC Event Data Formatting and Transmission to DAQ              | 93  |

|   |     | 6.5.1    | PPrASIC Event Data Format and Transfer on the Serial Interface | 93  |

|   |     | 6.5.2    | Reception of PPrASIC Data in the ReM_FPGA                      | 95  |

|   |     | 6.5.3    | Collecting the PPrASIC Event Data                              |     |

|   |     | 6.5.4    | The G-Link Event Data Format                                   |     |

|   |     | 6.5.5    | The Transfer to RGTM-O                                         | 103 |

|   | 6.6 | Collec   | ting the PPrASIC Readback Data                                 |     |

|   |     | 6.6.1    | The PPrASIC Readback Data Format On the Serial Interface       |     |

|   |     | 6.6.2    | Readback of Configuration Data                                 |     |

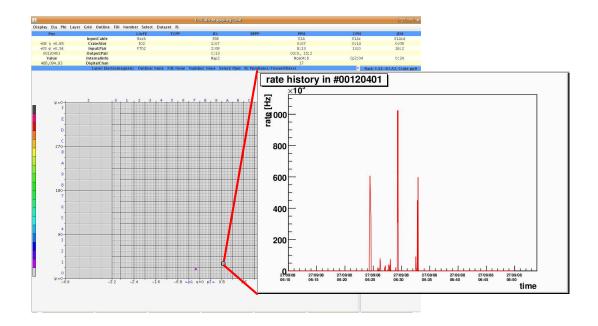

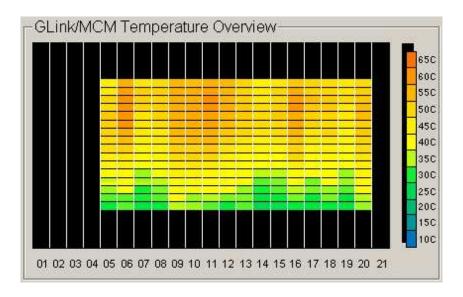

|   |     | 6.6.3    | Readout of PPrASIC Energy Rates and Spectra                    |     |

|   | 6.7 |          | ack of TTCrx Configuration Data                                |     |

|   | 6.8 | Spying   | g the PPrASIC Serial Interface Data Over the VME               | 116 |

|   | 6.9 | Design   | Implementation                                                 | 117 |

| 7 | The | Function | onal Tests of the PreProcessor Module                          | 119 |

|   | 7.1 | Overvi   | iew                                                            | 119 |

|   | 7.2 | Single   | Board Tests                                                    | 120 |

|   |     | 7.2.1    | The Test Setup                                                 | 120 |

|   |     | 7.2.2    | The DAC Scan Test                                              | 124 |

<u>CONTENTS</u> V

|   |      | 7.2.3    | The External BCID Test                                     | 127 |

|---|------|----------|------------------------------------------------------------|-----|

|   |      | 7.2.4    | The FADC Test                                              | 128 |

|   |      | 7.2.5    | Real-Time LVDS Data Tests                                  | 128 |

|   |      | 7.2.6    | Additional Tests for the ReM_FPGA                          | 136 |

|   | 7.3  | Full-cra | ate Tests                                                  | 138 |

|   | 7.4  | Summa    | ary                                                        | 140 |

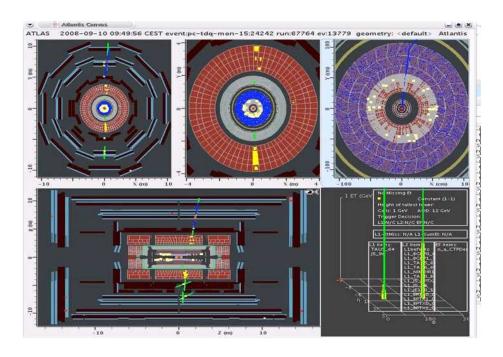

| 8 | The  | PrePro   | cessor Operation in the ATLAS Experiment                   | 141 |

|   | 8.1  | Integra  | tion and Commissioning Tests                               | 141 |

|   | 8.2  | Cosmic   | Muon Runs                                                  | 146 |

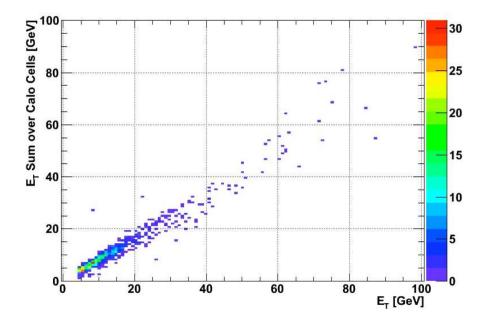

|   | 8.3  | LHC B    | eam Runs                                                   | 147 |

| 9 | Sum  | mary a   | nd Conclusions                                             | 153 |

| A | Prel | Processo | or System: Channel Mappings                                | 155 |

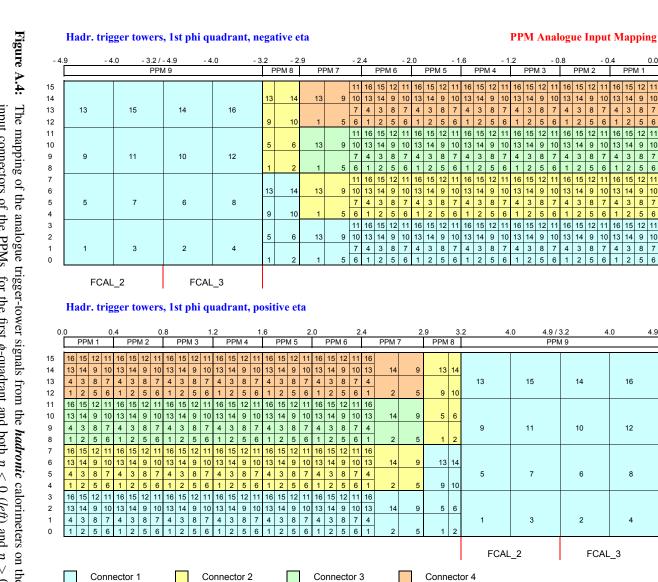

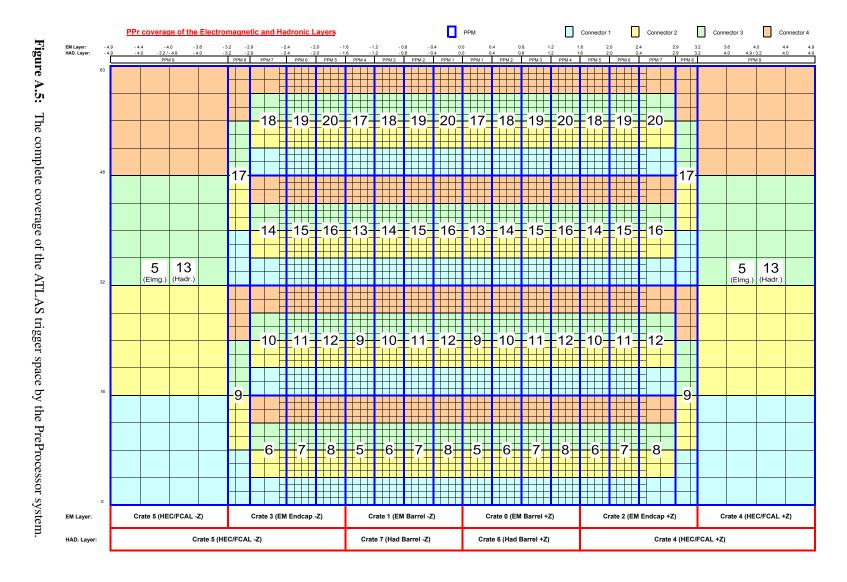

|   | A.1  | The Ma   | apping of the PPM Channels to Detector Coordinates         | 155 |

|   | A.2  | The Ma   | apping of the Analogue and Digital Channels on the PPM     | 156 |

| В | Rea  | dout Ma  | anager FPGA: Registers and Memory Locations                | 165 |

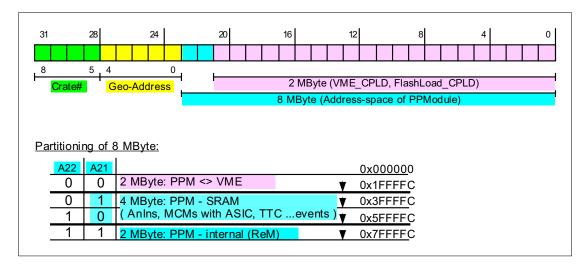

|   | B.1  | The VI   | ME Address Space for the Readout Manager                   | 165 |

|   | B.2  | Data St  | torage in SRAM                                             | 167 |

|   |      | B.2.1    | MCM Reference and Readback Blocks                          | 167 |

|   |      | B.2.2    | TTCrx Reference and Readback Blocks                        | 169 |

|   |      | B.2.3    | Reference Playback Patterns                                | 170 |

|   |      | B.2.4    | Reference and Readback Rates                               | 172 |

|   |      | B.2.5    | Reference and Readback Histograms                          | 172 |

|   | B.3  | Contro   | l, Command, Status and Error Registers                     | 172 |

|   |      | B.3.1    | The "VME Spy Buffers" Registers                            | 172 |

|   |      | B.3.2    | The "SRAM-MCM Readback Flags" Address Block                | 173 |

|   |      | B.3.3    | The "SRAM-TTCrx Readback Flags" Address Block              | 173 |

|   |      | B.3.4    | The Rate Metering & Histogramming Enable/Disable Registers | 174 |

|   |      | B.3.5    | The "PHOS4_Acknowledge" Status Register                    | 174 |

|   |      | B.3.6    | The "PHOS4-DLL Status" Register                            | 174 |

|   |      | B.3.7    | The "DAC Full-Buffered Mode" Registers                     | 175 |

|   |      | B.3.8    | The "Rate Metering Status" Registers                       | 176 |

|   |      | B.3.9    | The "Histogramming Status" Registers                       | 176 |

|   |      |          | The "Raw Pipeline Status" Registers                        | 176 |

|   |      | B.3.11   | The "BCID-LUT Pipeline Status" Registers                   | 176 |

|   |      | B.3.12   | The "Playback Status" Register                             | 177 |

|   |      |          | The "PHOS4_SerIntf Status" Register                        | 177 |

|   |      |          | The "ROD Readout Samples" Register                         | 177 |

|   |      | B.3.15   | The "G-Link DAV Gap" Register                              | 178 |

|   |      | B.3.16   | The "Disabled ASIC Channels" Registers                     | 179 |

|   |      | B.3.17   | The MCM_Control Register                                   | 179 |

VI CONTENTS

| B.3.18 The Local Trigger Registers        | 179 |

|-------------------------------------------|-----|

| B.3.19 The "Local Counter Reset" Register | 181 |

| B.3.20 The "Firmware Version" Register    | 181 |

| B.3.21 The ReM_Status Registers           | 181 |

| B.3.22 The ReM_Control Register           | 183 |

| B.3.23 The ReM_Command Register           | 184 |

| B.3.24 The "ReM_Error" Registers          | 185 |

| List of Figures                           | 191 |

| List of Tables                            | 194 |

| List of Acronyms                          | 195 |

| Bibliography                              | 199 |

| Acknowledgements                          | 207 |

## Chapter 1

## Introduction

The Large Hadron Collider (LHC) is designed to accelerate and collide protons with a centre-of-mass energy of  $\sqrt{s} = 14$  TeV, at a luminosity of  $\mathcal{L} = 10^{34} \, \mathrm{cm}^{-2} \, \mathrm{s}^{-1}$ . The unprecedented high energy and luminosity will allow to study the existence of the Higgs boson, the particle believed to be at the origin of the spontaneous symmetry-breaking mechanism in the electroweak sector of the Standard Model, as well as to probe the theories beyond the Standard Model. ATLAS is one of the four major experiments installed at the LHC. It is a general-purpose experiment designed to fully exploit the physics opportunities offered by the LHC.

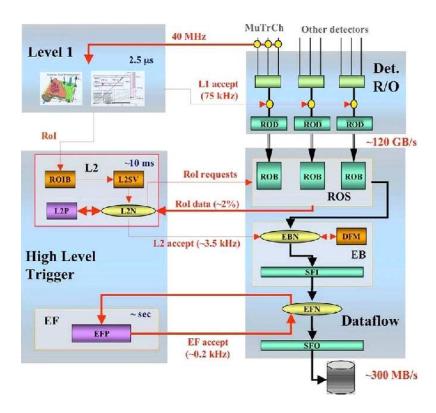

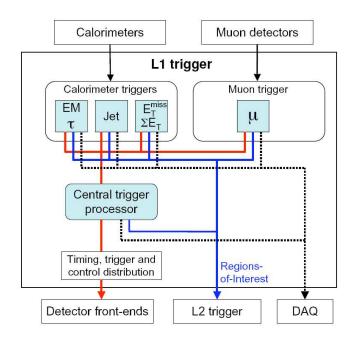

At the LHC's design luminosity, the expected event rate is in the order of 1 GHz. This raises an important experimental challenge for the ATLAS detector. The interesting physics processes occur at very small rates, in the order of a few Hz or even lower, being overwhelmed by the production of jets coming from QCD interactions. On the other hand, the raw data produced by the detector amounts to about 1 PByte/s, while the event data recording is limited by technology and resources to about 300 MByte/s. Therefore, the ATLAS Trigger and Data Acquisition systems have to reduce the initial event rate to the affordable mass storage rate, while efficiently selecting the potential rare physics events. To achieve this, the ATLAS Trigger system is organised into three levels of event selection.

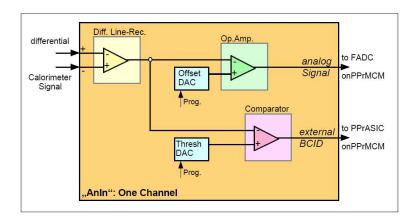

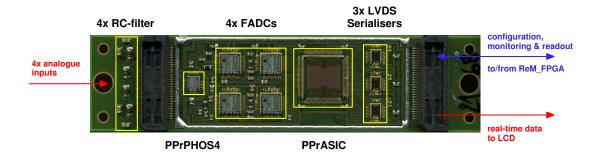

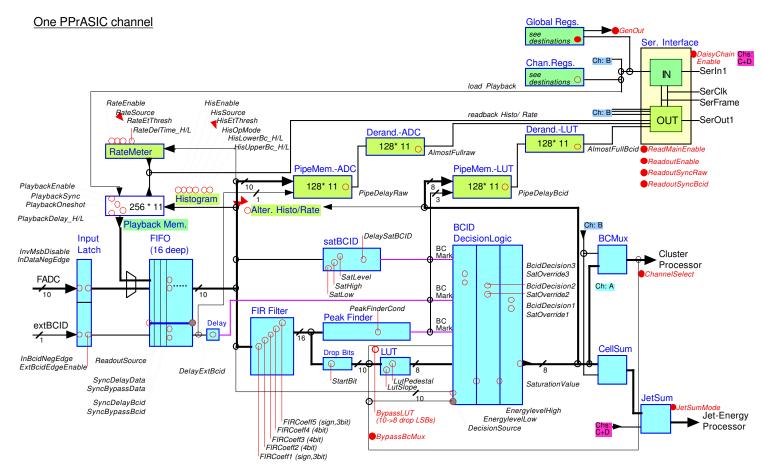

The PreProcessor system is the first stage of data processing in the Level-1 Calorimeter Trigger, a major subcomponent of the first level of event selection. It receives about 7200 analogue trigger signals that describe transverse energy deposits in the ATLAS calorimeter subdetectors. The main task of the PreProcessor is to extract a corresponding digital energy value from each pulse and assign it to a specific proton-proton collision. Additionally, in order to allow calibration, monitoring and verifications of the Level-1 trigger system, the PreProcessor has to provide copies of the digital trigger data related with the accepted event to the Data Acquisition system. The PreProcessor is a VME-based system. It mainly consists of 124 PreProcessor Modules, each of which can process 64 trigger signals. The task of transferring the event related data to the Data Acquisition system is assigned to a Readout Manager FPGA located on each PreProcessor Module. The device collects the event data from distributed locations on the board, and sends it in a predefined format to the Data Acquisition system. Apart from this, the device has the tasks to transfer configuration data from the VME interface to various on-board programmable locations, and to collect trigger-independent monitoring data, accumulated in the hardware of

2 Introduction

the PreProcessor Module, and provide it to VME. The first part of this thesis describes the algorithms developed to sustain the functionality of the Readout Manager FPGA. The second part of the thesis presents the tests that had been carried out to verify the proper functionality of the PreProcessor Modules, before they were installed at CERN in the electronics cavern of the experiment.

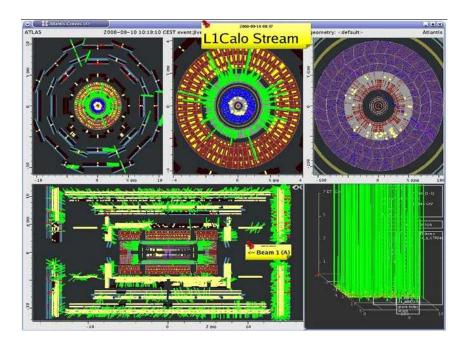

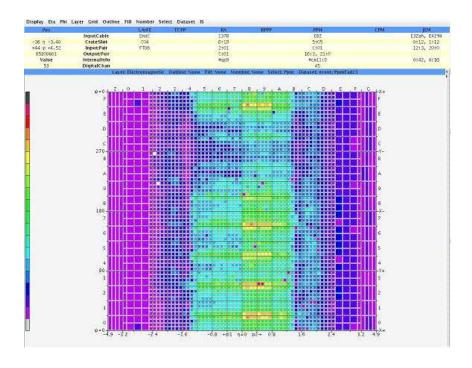

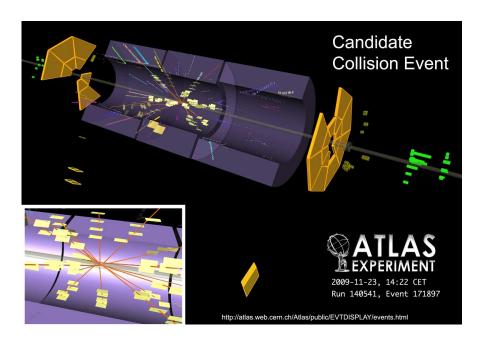

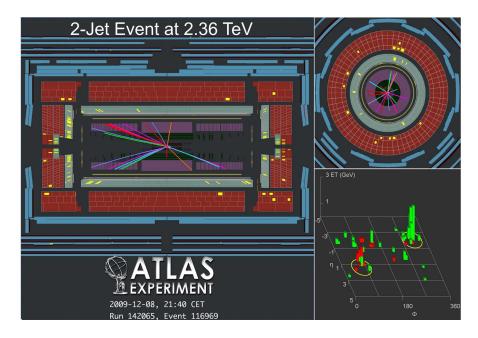

Chapter 2 provides a brief description of the Standard Model theory and of the search for the Higgs boson. The LHC machine and the ATLAS detector are described in chapter 3. An overview of the ATLAS Trigger and Data Acquisition systems is given in chapter 4, while the architecture and algorithms of the Level-1 Calorimeter Trigger are presented in more detail in chapter 5. The next two chapters form the core of this thesis. Chapter 6 is entirely dedicated to the Readout Manager FPGA, presenting in great detail the functionality of the device and the implemented algorithms, while chapter 7 describes the functional tests of the PreProcessor Module and shows examples of misbehaviours detected during the tests. Lastly, chapter 8 shows results recorded during the commissioning of the PreProcessor system at CERN, in standalone mode with the other trigger components and in combined runs with the whole ATLAS detector, and results obtained with the first LHC proton beam data.

# **Chapter 2**

# **Physics Motivation**

## 2.1 The Standard Model of Particle Physics

The Standard Model describes the physical world in terms of two kinds of particles and three fundamental forces. The particles are the *elementary fermions* and the *gauge bosons*. The fermions are half-integer spin particles that make up the matter, while the gauge bosons are integer spin particles that mediate the interactions between the fermions. The fermions are classified into two categories, *leptons* and *quarks*, according to the interactions they experience. There are six *flavours* of leptons, i.e. the electron (e), the muon( $\mu$ ), the tau (tau) and three neutrino partners ( $v_e$ ,  $v_\mu$ ,  $v_\tau$ ), and six flavours of quarks, i.e. up (u), down (d), charm (c), strange (s), top (t) and bottom (b). These 12 matter particles form together three *generations*, each of which contains one pair of leptons and one pair of quarks, as shown in table 2.1. The fermions of the first generation are stable and they represent the elementary constituents of the ordinary matter. The fermions of the other two generations appear in cosmic rays or they are manufactured in high-energy experiments, and they eventually decay into particles of the first generation. Also, for each fermion there exists an *antiparticle* of the same mass and opposite electric charge.

The three fundamental forces described by the Standard Model are: the *strong* force, which is responsible for holding the quarks together, the *electromagnetic* force, which acts on all electrically charged particles and which is responsible for the bonding in chemical elements, and the *weak* force, which determines the transmutation of quarks and leptons. Attempts to include the fourth known fundamental force of nature, the *gravitation*, in the framework of the Standard Model have so far been unsuccessful. However, the gravitation is considered to be inconsequential at the subatomic scale because it is much weaker than the other three forces. The properties of the four fundamental forces are summarised in table 2.2.

The Standard Model of particle physics is formulated as a relativistic quantum gauge field theory. Each of the three fundamental forces is described as resulting from the exchange of spin-1 gauge bosons between the matter fermions. The gauge bosons arise from the requirement of a local gauge symmetry, i.e. the Lagrangian of the system has to be invariant under different transformations applied at each point in space and time. The field theory of the strong interaction is formulated as a non-abelian gauge theory with  $SU(3)_C$  color symmetry, and it is called quantum

4 Physics Motivation

| Fermions |       | Electric   |            |              |

|----------|-------|------------|------------|--------------|

|          | 1     | 2          | 3          | Charge       |

| Leptons  | e     | μ          | τ          | -1           |

|          | $v_e$ | $ u_{\mu}$ | $ u_{	au}$ | 0            |

| Quarks   | u     | c          | t          | +2/3<br>-1/3 |

|          | d     | S          | b          | -1/3         |

**Table 2.1:** The three generations of matter fermions.

chromodynamics (QCD). The strong force is mediated by eight<sup>1</sup> massless gauge bosons called *gluons*, which, like quarks, carry color charge. The electromagnetic interaction is described as an abelian gauge theory with the symmetry group U(1). The respective theory is called quantum electrodynamics (QED). The mediator of the electromagnetic force is the *photon*, an electrically neutral and massless gauge boson. The mathematical formulation of the weak interaction is based on the gauge group SU(2). The weak force is mediated by three massive gauge bosons, i.e.  $W^+$ ,  $W^-$  and the neutral Z. In the 1960s, Glashow, Salam and Weinberg unified the description of the electromagnetic and weak interactions into one field theory called the electroweak theory. This is a non-abelian gauge theory based on the  $SU(2)_L \times U(1)_Y$  gauge symmetry group of the weak isospin (I) and the weak hypercharge (Y) [Mor04].

### 2.1.1 The Higgs Mechanism

In the 1960s, many theoretical researches were focused on formulating a relativistic field theory with local gauge symmetry that would describe both the electromagnetic and the weak interactions. The major difficulty that the physicists were trying to overcome was that in order not to destroy the gauge invariance the fermions and gauge bosons had to be massless, which was in contradiction with the experimental observations. Of a particular interest was the case of the weak interaction, which was known to be short-range, its influence being significant only up to  $10^{-18}$  m. Consequently, the carriers of the weak force had to be fairly massive rather than massless.

In 1961, Glashow proposed the first SU(2) x U(1) gauge theoretical model for the electroweak interaction [Gla61]. The theory possesses only a partial symmetry, meaning that the symmetry is broken by the addition of explicit mass terms in the Lagrangian. The theory is also notable for introducing for the first time the neutral current<sup>2</sup> carried by the Z boson, in addition to the then already known charged weak currents ( $W^{\pm}$ ) and electromagnetic current ( $\gamma$ ). The breakthrough came in 1964 when Higgs [Hig64], Englert and Brout [Eng64], and Guralnik, Hagen, and Kibble [Gur64] showed that masses can be generated dynamically by spontaneous symmetry breaking. The latter occurs when a system that is symmetric with respect to some

<sup>&</sup>lt;sup>1</sup>the number of gauge bosons is given by the number of generators of the unitary group associated with each force. For a special unitary group of degree n, i.e. SU(n), the number of generators is  $n^2 - 1$ .

<sup>&</sup>lt;sup>2</sup>i.e. the interacting particles do not change their charges

| Force           | Relative<br>Strength | Range (metres) | Mediators<br>(gauge bosons) | Dynamic Theory               |

|-----------------|----------------------|----------------|-----------------------------|------------------------------|

| Strong          | 1                    | $10^{-15}$     | 8 Gluons (g)                | Quantum Chromodynamics       |

| Electromagnetic | $10^{-2}$            | ∞              | Photon $(\gamma)$           | Electroweak Theory           |

| Weak            | $10^{-5}$            | $10^{-18}$     | $W^\pm, { m Z}$             | "_"                          |

| Gravitation     | $10^{-38}$           | $\infty$       | Graviton (G)                | General Theory of Relativity |

**Table 2.2:** Summary of the properties of the four fundamental forces in nature. The gravitation is not incorporated in the Standard Model. The mediator of this force, called the *graviton*, is a massless, spin-2 particle [Mor04].

symmetry groups goes into a vacuum state that is not symmetric or not invariant. This framework was then applied by Weinberg [Wei67] and Salam [Sal68] to the electroweak theoretical model formulated by Glashow in 1961. In their work, Weinberg and Salam introduced an SU(2) self-interacting doublet of complex scalar fields, with four degrees of freedom, of which neutral component does not vanish in vacuum, i.e. it has a non-zero value in its lowest energy state. This non-zero vacuum expectation value breaks spontaneously the electroweak  $SU(2) \times U(1)$  symmetry, but the Lagrangian of the system remains invariant under  $SU(2) \times U(1)$  transformations. Three of the four degrees of freedom of the doublet scalar field are swallowed by the  $W^{\pm}$  and Z bosons, which in this way acquire mass. The remaining degree of freedom of the doublet corresponds to a spin-0 scalar particle, which was latter named as the Higgs boson. The fermion masses are also a consequence of the electroweak symmetry breaking. The same theory postulates that the doublet scalar field couples to fermions through Yukawa interactions. The mechanism through which  $W^{\pm}$  and Z bosons acquire mass is referred to as the Higgs mechanism. A detailed account of the mathematical formalism that describes the Higgs mechanism can be found in e.g. [Djo08].

The Higgs boson is so far the only particle of the Standard Model of which existence has not been confirmed experimentally. However, experimental results achieved in the last forty years for the electroweak sector of the Standard Model provide strong support for the hypothesis of the Higgs mechanism. Of the most notable are the first observation of neutral current interactions in the Gargamelle bubble chamber detector at CERN (1973), the direct observation of the W and Z bosons by the UA1 and UA2 experiments (1983), both also located at CERN, the discovery of the top quark, which decays only through the weak force, by the CDF and DØ experiments at Fermilab (1995), or the high precision measurements of the mass of W boson and top quark by experiments at LEP<sup>3</sup> and Tevatron colliders.

6 Physics Motivation

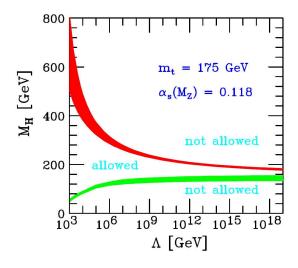

**Figure 2.1:** Triviality and vacuum stability bounds on  $m_H$  as a function of new physics scale  $\Lambda$  [Djo08].

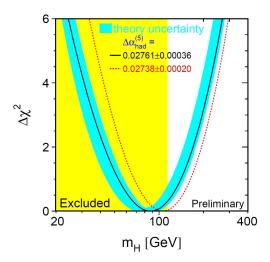

**Figure 2.2:** The  $\Delta \chi^2 = \chi^2 - \chi^2_{min}$  versus  $m_H$  from the global fit to the electroweak data [LEP02].

### 2.1.2 The Search for the Higgs Boson

### The Higgs Boson Mass

In the electroweak theory, the mass of the Higgs boson  $(m_H)$  is given as:

$$m_H = \sqrt{\frac{\lambda}{2}} \, \nu \quad , \tag{2.1}$$

where  $\lambda$  is the Higgs self-coupling parameter, while  $\nu$  represents the vacuum expectation value of the Higgs scalar field. The latter is fixed by the Fermi coupling constant  $(G_F)$  to:

$$v = \sqrt{2} G_F = 246 \ GeV \quad ,$$

(2.2)

which means that  $m_H$  scales only with  $\sqrt{\lambda}$ . Because the Higgs boson has not been yet experimentally observed, the self-coupling  $\lambda$  remains unknown, therefore  $m_H$  cannot be predicted by the Standard Model. However, theoretical limits for  $m_H$  can be derived from assumptions on the energy scale  $\Lambda$  within which the Standard Model is valid and beyond which new physics phenomena emerge. If the electroweak theory is assumed to be valid in the whole energy range, then the self-coupling  $\lambda$  will vanish when  $\Lambda \to \infty$ . Which also means that the larger the energy scale  $\Lambda$ , the smaller the self-coupling  $\lambda$ . But since the non-zero vacuum expectation value in the Higgs mechanism occurs only if  $\lambda \neq 0$ ,  $\Lambda$  has to be limited to a certain physical scale. Since  $m_H$  is proportional with  $\lambda$ , this limitation gives an upper bound on  $m_H$  (triviality bound). On the other hand, if  $\lambda$  becomes too small, i.e. smaller than the Higgs-top quark Yukawa coupling  $(\lambda_t = \sqrt{2}m_t/v)$ , the Higgs vacuum state will be unstable. Therefore,  $\lambda$  has to be large enough to balance the top quark contribution, and this gives a lower bound on  $m_H$  (vacuum stability

<sup>&</sup>lt;sup>3</sup>Large Electron Positron.

bound). Thus, based on these two requirements and on a give value of  $\Lambda$ , the minimum and a maximum Higgs mass allowed can be determined (see figure 2.1). If the Standard Model is consistent up to the Planck scale ( $\Lambda \sim M_{Planck} = 10^{19}$  GeV), beyond which gravitation effect cannot be longer neglected in respect to the other fundamental interactions, one obtains that  $m_H$  should lie within the range:

130

$$GeV \le m_H \le 180 \ GeV$$

. (2.3)

If new physics occurs at a lower mass scale, the bound on  $m_H$  becomes weaker. For example, if  $\Lambda \sim TeV$  then one expects  $m_H$  within the range [Djo08]:

$$50 GeV \lesssim m_H \lesssim 800 GeV \qquad . \tag{2.4}$$

Apart from these theoretical constraints, direct searches of the Higgs boson at LEP established a lower bound on the Higgs mass of 114.4 GeV at 95% confidence level (CL)<sup>4</sup> [ALE03], while similar investigations at Tevatron currenly exclude, in addition, the mass range of 162 to 166 GeV at 95% CL<sup>5</sup> [Tev10]. Further experimental constraints on the mass range of the Higgs boson are determined indirectly from precision fits of all measured electroweak observables. Figure 2.2 shows the  $\Delta \chi^2$  of the fit to the electroweak precision data from LEP and SLC<sup>6</sup> as a function of  $m_H$ . The shaded band around the central curve indicates the theoretical uncertainties due to unknown higher order corrections, while the vertical band indicates the 95% exclusion limit determined from direct searches. The Higgs mass obtained from the fit is  $m_H = 87^{+34}_{-26}$  GeV. Also, taking into account the 114.4 GeV lower limit, an upper limit of  $m_H \le 185$  GeV at 95% CL was obtained. [ALE08].

### The Higgs Boson at the LHC: Production and Decay Channels

The search for the Higgs boson is one of the major goals for the experiments at LHC. The proton-proton (pp) collisions at a centre-of-mass energy of  $\sqrt{s} = 14$  TeV will allow to search for the Higgs boson in a mass range from 100 GeV to about 1 TeV, in a various production and decay channels.

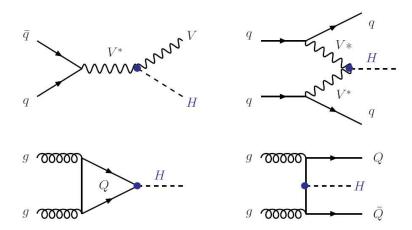

Because the coupling strengths of the Higgs boson to fermions and bosons are proportional to their masses, the Higgs production generally involves heavy particles, i.e. the W and Z bosons, the top quark and to a lesser extent the bottom quark. At the LHC, there are four main Higgs production processes:

• gluon-gluon (gg) fusion (gg  $\rightarrow$  H): the Higgs boson couples to gluons through a heavy-quark loop;

<sup>&</sup>lt;sup>4</sup>the investigations were mainly carried out through the process  $e^+e^- \to Z^* \to ZH \to (f\bar{f}+b\bar{b}/t\bar{t})$ , known as the *Higgsstrahlung*, based on collision data at centre-of-mass energies up to 209 GeV. The LEP collaborations reported an 1.7σ excess of events above the expected background, smaller than the 5σ needed to certify the discovery of the Higgs boson [ALE03]. The LEP accelerator ended its operation in November 2000.

<sup>&</sup>lt;sup>5</sup>at Tevatron, the Higgs boson is searched in  $p\bar{p}$  collisions at the centre-of-mass energy  $\sqrt{s} = 1.96$  TeV via gluon fusion production and associated production with W/Z bosons and  $t\bar{t}$  pairs.

<sup>&</sup>lt;sup>6</sup>Stanford Linear Collider  $(e^+e^-)$ .

8 Physics Motivation

**Figure 2.3:** Feynman diagrams of the four main Higgs production mechanisms at LHC: associated production with W/Z (*upper left*), vector boson fusion (VBF) (*upper right*), gluon-gluon fusion (*lower left*) and associated production with heavy quarks (*lower right*) [Djo08].

- vector boson fusion (VBF)  $(qq \rightarrow V^*V^* \rightarrow qq + H)$ : two incoming quarks, mostly light quarks, emit a pair of gauge bosons, which then fuse to form a Higgs boson;

- associated production with W/Z ( $q\bar{q} \rightarrow V + H$ ): two incoming light quarks annihilate to a weak gauge boson, which then radiates a Higgs boson;

- associated production with heavy quarks  $(gg \rightarrow QQ + H)$ : the process occurs mainly through gluon fusion, where the Higgs boson is emitted from both the external and internal quark lines.

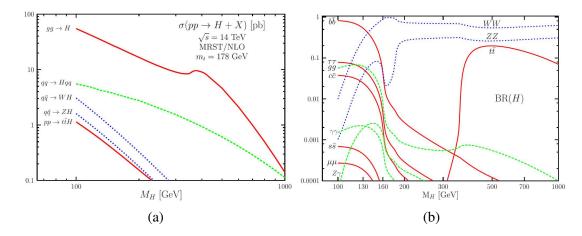

The Feynman diagrams of these production processes are shown in figure 2.3, while the corresponding cross-sections are shown in figure 2.4a. The dominant production channel over the entire mass range will be the gg fusion, due to the large gluon content possessed by the high energy protons. The cross-section of the VBF process is roughly one order of magnitude smaller, but reaches the level of the gg fusion cross-section at very large  $M_H$  values. The other two processes have much smaller cross-sections, and they are relevant only in the mass range  $m_H \lesssim 250$  GeV.

As for the production case, the coupling of the Higgs boson to mass favours the decay mode into the heaviest possible final state. This is also shown in figure 2.4b, which illustrates the branching ratios of the different decay modes of the Higgs boson. In the low mass region  $m_H \lesssim 130$  GeV, the dominant decay mode is  $H \to b\bar{b}$ , followed by  $H \to \tau\bar{\tau}/c\bar{c}$ . Above  $m_H \lesssim 180$  GeV, the Higgs boson almost exclusively decays into pairs of gauge bosons, i.e.  $H \to W^+W^-$  and  $H \to ZZ$ , where one of the gauge bosons is virtual for  $m_H < 2m_W(m_Z)$ . Also, beyond  $m_H > 2m_t$ , the branching ratio of the decay mode  $H \to t\bar{t}$  becomes significant, but it is still smaller than the branching ratios of the decay modes to  $W^+W^-$  and ZZ, due to the different dependence of the Higgs coupling with the mass scale, i.e. linear versus cubic. Although the Higgs boson does not couple to gluons or photons, its decay into these massless particles is also possible. The decay mode  $H \to gg$  is mediated by heavy-quark loops and it has a significant branching ratio only in

**Figure 2.4:** Cross-sections of the main Higgs boson production mechanisms at the LHC energies of  $\sqrt{s} = 14 \text{ TeV } (a)$  and branching ratios of the main Higgs boson decays (b) as a function of the Higgs mass.

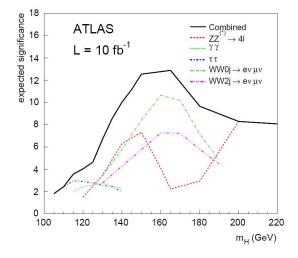

**Figure 2.5:** Expected statistical significance (expressed in  $\sigma$ 's) for the Higgs boson in various channels in ATLAS as a function of the Higgs mass.

10 Physics Motivation

the low mass region, while the decay mode  $H \to \gamma \gamma$  is very rare and it is mediated by charged fermion and W boson loops [Djo08].

Figure 2.5 shows the discovery potential for the Higgs boson in various production and decay channels, in the case of the ATLAS experiment. The highest sensitivity is given by the decays to weak gauge bosons. The  $W^+W^-$  mode dominates in the mass range of 140 to 200 GeV, while the ZZ decay to four isolated leptons  $(e/\mu)$  gives the highest sensitivity above 200 GeV. When all channels are combined together, a  $5\sigma$  discovery of the Higgs boson is possible with an integrated luminosity of  $10 \text{ fb}^{-1}$ , for  $m_H$  between the LEP limit of 114.4 GeV and  $\approx 1 \text{ TeV}$ , after the detector performance and the background systematics are understood.

# Chapter 3

# The ATLAS Experiment at the LHC

ATLAS is one of the four major experiments built on the Large Hadron Collider (LHC) accelerator ring. It is a general-purpose experiment for *pp* collisions, designed to observe the largest spectrum of physics processes expected from the LHC. This chapter gives a brief overview of the LHC machine and of the ATLAS experimental apparatus.

## 3.1 The Large Hadron Collider

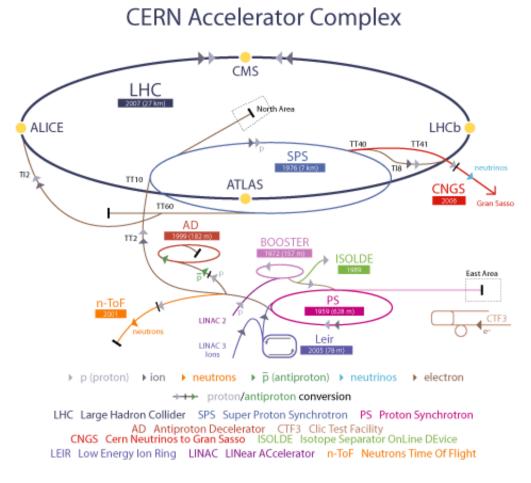

The LHC is a circular particle accelerator located at the European Organisation for Nuclear Research (CERN<sup>1</sup>) near Geneva, Switzerland. It is installed in the 26.7 km long tunnel that formerly housed the LEP collider, and it is primarily designed to collide head-on two counterrotating beams of protons with a centre-of-mass energy of  $\sqrt{s} = 14$  TeV, at an unprecedented luminosity of  $10^{34}$  cm<sup>-2</sup> s<sup>-1</sup>. As a secondary program of running, the LHC will also collide two beams of heavy ions<sup>2</sup> with a total centre-of-mass energy of  $\sqrt{s} = 1.15$  PeV and a peak luminosity of  $10^{27}$  cm<sup>-2</sup> s<sup>-1</sup> [Eva08]. The collisions occur in four interaction points, where four physics experiments are situated (see also figure 3.1):

- ATLAS (A Toroidal LHC ApparatuS) [ATL08a], designed to mainly investigate physics processes with high momentum transfer that are produced by *pp* collisions;

- CMS (Compact Muon Solenoid) [CMS08], also a general-purpose detector for *pp* collisions, designed to explore the physics at Terascale;

- LHCb (LHC beauty experiment) [LHC08a], designed for precision measurements of CP violation and rare decays of B-mesons;

- ALICE (A Large Ion Collider Experiment) [ALI08], dedicated to investigations of the quark-gluon plasma in heavy ion collisions.

Two other experiments, smaller in size, are located on either side of the ATLAS and CMS detectors respectively:

<sup>&</sup>lt;sup>1</sup>Conseil Europeen pour la Recherche Nucleaire (fr.)

<sup>&</sup>lt;sup>2</sup>i.e. <sup>208</sup><sub>82</sub>Pb (lead) ions

- LHCf (LHC forward) [LHC08b], dedicated to the measurement of neutral particles emitted in the very forward region of the LHC collisions;

- TOTEM (Total Cross Section, Elastic Scattering and Diffraction Dissociation) [TOT08], which aims to measure the total pp cross-section and to study elastic and diffractive scattering at the LHC.

### 3.1.1 Machine Parameters

The LHC is supplied with protons or heavy ions from an injector chain that mainly comprises a linear accelerator (LINAC2), a Proton Synchrotron Booster (PSB), a Proton Synchrotron (PS) and a Super Proton Synchrotron (SPS) (see again figure 3.1). The injector chain produces and pre-accelerates the protons up to the kinetic energy of 450 GeV. The LHC uses superconducting radio-frequency cavities operated at 400.8 MHz to capture and further accelerate these particles up to 7 TeV/beam, the highest energy ever reached in a particle accelerator. The trajectories of these very energetic protons are bent in the curved sections of the accelerator ring by 8.34 T magnets. The respective magnetic field is produced by 1232 niobium-titanium superconducting dipole magnets, which are cooled to 1.9 K with superfluid helium<sup>3</sup>. Additionally, in the straight sections of the ring, 386 quadrupole magnets and several thousand corrector magnets are used to focus the beams and to maximise the luminosity at the collision points.

The machine luminosity is a useful measure of the accelerator performance. In addition, the luminosity is an important factor needed to ensure that interesting physics processes, which have a small cross-section, are produced at the highest possible rate. The machine luminosity can be approximated as:

$$\mathcal{L} = \frac{N^2 \cdot n_b \cdot f_{rev}}{A_{eff}} \quad [cm^{-2}s^{-1}] \quad , \tag{3.1}$$

where N is the number of particles per bunch,  $n_b$  the number of bunches per beam,  $f_{rev}$  the particle revolution frequency (11,246 kHz), while  $A_{eff} = 4\pi\sigma_x\sigma_y$  is the effective interaction area, with  $\sigma_x$  and  $\sigma_y$  representing the Gaussian transverse profile of the bunches in the vertical and horizontal directions. For a given physics process with a known cross-section  $\sigma_{event}$ , the number of related events generated each second in the LHC collisions is:

$$N_{event} = \sigma_{event} \cdot \mathcal{L}$$

(3.2)

The proton beams are organised in *bunches*, each containing up to 1.15 x  $10^{11}$  particles. The bunches have a longitudinal spread of about 7.7 cm, and they are spaced apart by 7.48 m [Brü04]. The latter parameter determines a bunch-crossing rate of 40.08 MHz and a total number of 3564 possible bunches in the circumference of the LHC ring. However, due to technical constraints imposed by the operation of the injection, acceleration and dumping systems, only 2808/3564 bunches can be filled per LHC ring [Bai03]. The RMS beam size parameters, i.e.  $\sigma_x$  and  $\sigma_y$ , will be tuned to about 16.7  $\mu$ m for pp collisions in the centre of

<sup>&</sup>lt;sup>3</sup> for comparison, other large accelerators like Tevatron (Fermilab) or HERA (DESY) use NbTi superconducting magnets cooled with normal liquid helium at temperatures slightly above 4.2 K, which allows to reach a magnetic field of around 5 T.

Figure 3.1: The Large Hadron Collider and its four main experiments [CER10c].

the ATLAS and CMS detectors, in order to determine a peak value of the luminosity in these interaction points of  $10^{34}\,\mathrm{cm^{-2}\,s^{-1}}$ . For pp collisions at LHCb, the beam size will be enlarged by tuning the same parameters to approximatively 70.9  $\mu$ m, in order to determine a peak luminosity of  $10^{32}\,\mathrm{cm^{-2}\,s^{-1}}$  [Brü04]. The LHCb needs this lower luminosity in order to enable a high-precision reconstruction of the primary interaction vertex and of the secondary B-meson decay.

As a heavy ion collider, the LHC will accelerate the ions from the injection energy of 177.4 GeV/nucleon up to 2.76 TeV/nucleon, which determines the total collision energy of 1.15 PeV. In this operating mode, the bunches will contain up to  $7 \times 10^7$  ions. Also, the nominal filling scheme will be based on 100 ns bunch spacing, and only 592 out of 891 possible bunch positions in the LHC will be filled with ions [Bai03]. This will lead to a peak luminosity of  $10^{27}$  cm<sup>-2</sup> s<sup>-1</sup> for heavy ion collisions.

### 3.1.2 Experimental Challenges at the LHC

The total inelastic pp cross-section at  $\sqrt{s} = 14$  TeV is predicted to be approximatively 79 mb [Sjo06]. According to equation 3.2, the LHC is then expected to produce a total rate of about  $10^9$  inelastic events per second at design luminosity. This means that at each bunch-crossing, i.e.  $\sim 25$  ns, a mean of 25 pp interactions are expected to occur<sup>4</sup>. The high event rate and the high energy of the colliding protons impose several experimental challenges, which set stringent requirements on the different techniques and technologies employed by the LHC detectors:

- **Pile up**. The inelastic events produced at LHC can be divided into two categories: *minimum bias* and *hard-scattering* events. The minimum bias events arise from strong longrange interactions between the constituents of the colliding protons. They are characterised by a small momentum transfer, such that the final state particles have large longitudinal momentum  $(p_L)$  and small transverse momentum  $(p_T)$ , i.e.  $\simeq 500$  MeV. The hard-scattering events are produced via strong short-range  $p_T$  interactions. These events are characterised by a large momentum transfer, which can lead to the production of heavy particles. The high  $p_T$  processes are relatively rare with respect to the minimum bias events, but they represent the main interests for the physics researches at LHC. At each bunch-crossing, about 23 low  $p_T$  events  $(\sigma_{mb} \sim 69 \text{ mb})$  are produced simultaneously, overlapping the high  $p_T$  physics events of interest. Furthermore, the same low  $p_T$  events generate on average 1700 charged particles. This means that a response time of the detectors longer than 25 ns can lead to an overlap of signals from multiple consecutive bunch-crossings. These effects are collectively referred to as *event pile-up*.

- The pile-up of minimum bias events degrades the accuracy of the energy measurement, which consequently worsens the selection efficiency of the interesting high  $p_T$  objects. In order to be able to handle the particle fluxes and to reduce the influence of pile-up events, the LHC detectors must be segmented into finely granular readout cells. Additionally, the detectors must feature a fast response, i.e. typically  $\leq 50$  ns, in order to integrate the readout signals over a reduced number of bunch-crossing in each channel.

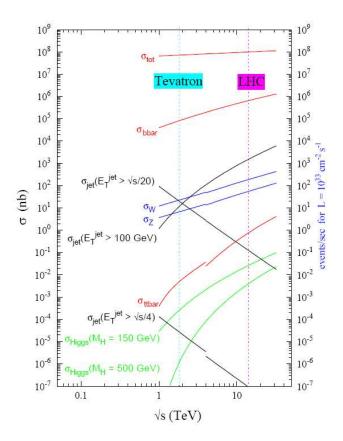

- QCD background. Another challenge for the experiments at LHC is the high production rate of QCD jets. These represent highly collimated cones of particles, which are generated in high  $p_T$  scatterings due to strong partonic interactions. Because of the large cross-sections for these processes, QCD jets are produced abundantly, overwhelming the rarer processes being sought at the LHC (QCD background). Figure 3.2 shows the cross-sections for various inelastic processes produced in both pp and  $p\bar{p}$  collisions, as a function of the centre-of-mass energy. It can be observed, for example, that the cross-section for jets with  $p_T > 100$  GeV, at  $\sqrt{s} = 14$  TeV, is about five orders of magnitude larger than the cross-section for the Higgs boson with a mass of 150 GeV. Since one of the dominant decay modes for the Higgs in that mass range is into two b-quark jets, the experimental signatures are difficult to isolate because of the QCD background. Instead, final states involving leptons or photons, or missing transverse energy ( $E_T^{miss}$ ) or secondary vertices

<sup>&</sup>lt;sup>4</sup>this takes also into account that only 2808 out of 3564 possible bunch positions are filled with protons.

**Figure 3.2:** Production cross-sections and event rates for different processes as a function of the centre-of-mass energy [Gia04].

information have to be used, in order to suppress the background generated by QCD processes. For an efficient extraction of the rare signals of new physics from the large background of known processes, the experiments at LHC must feature excellent detector and trigger performance in terms of particle identification capabilities and energy resolution.

• Radiation level. Because the flux of particles generated in *pp* collisions is very large, the detectors at LHC are expected to operate in a high radiation environment. The highest radiation levels are expected to occur in the forward regions of the detectors, which will be exposed in ten years of LHC operation to a neutron fluence of up to 10<sup>17</sup> neutrons/cm² and a γ-dose of about 10<sup>7</sup> Gy<sup>(5</sup>. Thus, in order to avoid severe radiation damages, the detection material and the on-detector readout electronics must be radiation-tolerant. Also, the high radiation levels require the LHC detectors to operate reliably in long term. In case of failures, the access for maintenance in the experimental hall will be highly restricted and time consuming, which will lead to a long detector shut-down period.

$<sup>^{5}</sup>$ the Gray (Gy) is a radiological unit, which expresses the absorbed energy per unit mass of material (1 Gy = 1 Joule/kg).

### 3.2 The ATLAS Detector

ATLAS is a general-purpose detector for pp collisions at the LHC. The detector was mainly designed to search for new particles related to the electroweak symmetry breaking mechanism. In consequence, the detector optimisation was also guided by physics issues such as the sensitivity to the largest possible Higgs mass range. Other important objectives of the ATLAS physics program refer to precise measurements of known particle properties (e.g.  $W^{\pm}$  bosons, t- and b-quark mesons) and the study of Standard Model (SM) processes at the TeV scale, as well as to investigations of the theories beyond the SM.

The necessary detection capabilities for a large spectrum of experimental signatures lead to the following set of design requirements for the ATLAS detector:

- efficient tracking and vertex reconstruction near the interaction point to measure the momentum of charged particles and to identify b-quarks and τ-decays;

- very good electromagnetic calorimetry, in terms of energy resolution and solid angle coverage, for electron and photon identification and measurements;

- hermetic hadronic calorimetry for accurate determination of the jet energy and reconstruction of the  $E_T^{miss}$ ;

- good muon identification and momentum resolution over a wide range of momenta, and the ability to determine unambiguously the charge of the high p<sub>T</sub> muons;

- fast and highly selective trigger system, to reduce the initial event rate ( $10^9$  Hz) to a level that can be handled offline ( $\sim 200$  Hz), while selecting efficiently the interesting physics processes;

- fast and radiation-tolerant electronics and sensor elements, and high detector granularity to handle the particle fluxes and to reduce the influence of overlapping events.

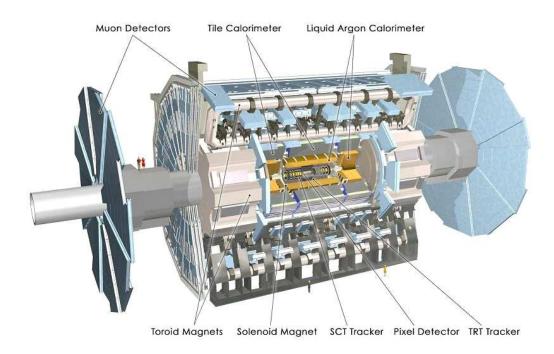

Figure 3.3 shows the layout of the ATLAS detector. It has a total diameter of 25 m, a total length of 46 m and it weighs about 7000 t, which makes it the largest of the four main detectors installed at the LHC. The detector is constructed with rotation-symmetry around the beam axis, and it consists of three complementary sub-detector systems assembled in concentric layers: an *Inner Detector*, which is immersed in a solenoidal magnetic field, an *Electromagnetic* and a *Hadronic Calorimeter* surrounding the Inner Detector, and at the outer region a *Muon Spectrometer* consisting of air core toroids with muon chambers. The following sections of the chapter give a brief overview of the different sub-detectors. A more detailed description of the ATLAS subsystems can be found in [ATL08a].

### 3.2.1 The Coordinate System

The coordinate system of the ATLAS experiment is a right-handed system, with the x-axis pointing radially towards the centre of the LHC ring, the z-axis following the beam direction<sup>6</sup>, and

<sup>&</sup>lt;sup>6</sup>the positive z-axis points to the LHCb detector (see also figure 3.1).

3.2 The ATLAS Detector 17

**Figure 3.3:** Cut-away view of the ATLAS detector [CER10a].

the y-axis pointing vertically upwards. The origin of the coordinate system is the nominal interaction point in the centre of the detector. The azimuthal angle  $\phi \in [0,2\pi]$  is measured around the beam axis, in the transverse plane formed by the x and y directions, so that the angle  $\phi$ =0 corresponds to the positive x-axis while  $\phi$ = $\pi$ /2 corresponds to the positive y-axis.

The polar angle  $\theta$  is measured from the beam axis with the positive z-axis:

$$\theta = \arctan\left(\frac{p_T}{p_z}\right) \quad , \tag{3.3}$$

where  $p_T$  and  $p_z$  represent the perpendicular and parallel components of the momentum to the z-axis. The rapidity variable (Y) is defined as:

$$y = \frac{1}{2} \left( \frac{E + p_z}{E - p_z} \right) \quad . \tag{3.4}$$

The difference in rapidity between two particles is Lorentz invariant under a boosting along the z-axis. When the mass and the momentum of the particle are not known, the pseudorapidity variable  $(\eta)$  it is used to characterise the detected particle:

$$\eta = -\ln\left[\tan\left(\frac{\theta}{2}\right)\right] \quad , \tag{3.5}$$

In the massless limit  $(p \gg m)$ , the pseudorapidity closely approximates rapidity. For the transverse plane  $(\theta = 90^{\circ})$  the pseudorapidity is zero, while for directions close to the beam axis  $(\theta \to 0^{\circ}, \theta \to 180^{\circ})$  the pseudorapidity goes to infinity.

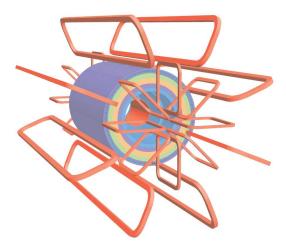

**Figure 3.4:** The geometry of the ATLAS Magnet System. The solenoid magnet system is depicted inside the calorimeter volume [ATL08a].

Three sides are defined for the ATLAS detector. The part along the negative z-axis is named as the C-side, the part along the positive z-axis is named as A-side, while B-side is the plane with z = 0.

### 3.2.2 The Magnet System

The ATLAS magnet system dominates the overall size of the ATLAS detector, being 22 m in diameter and 26 m in length. It consists of four large superconducting magnets used for particle identification and momentum measurements (see figure 3.4):

- a central *solenoid*, which provides the Inner Detector with a 2 T strong magnetic field along the beam axis;

- an outer system of three large air-core *toroids*, a Barrel Toroid (BT) and two End-Cap Toroids (ECT), which generates a magnetic field for the Muon Spectrometer of 0.5 T and 1 T respectively.

The solenoid superconducting magnet is built from a single-layer coil, and it shares the cryostat with the electromagnetic barrel calorimeter. This was done in order to reduce material thickness in front of the electromagnetic calorimeters, and thus to reduce the probability that the particles start showering before they reach the active part of the calorimeter<sup>7</sup>. For the same reason, the solenoid was designed to be shorter than the Inner Detector, i.e. 5.8 m versus 7.2 m. This geometry produces some non-uniformity in the magnetic field along the z-axis, which drops from the nominal value of 2 T at the interaction point to about 0.5 T through the ends of the Inner Detector.

The system of toroid magnets is designed to produce a magnetic field coverage in the range  $0 < |\eta| < 2.7$ . The three toroids consist each of eight coils assembled radially and symmetrically

<sup>&</sup>lt;sup>7</sup>at normal incidence, the contribution of the central solenoid assembly is 0.66 radiation lengths [ATL08a].

**Figure 3.5:** Cut-away view of the ATLAS Inner Detector [ATL10].

around the beam axis. The BT coils are contained in individual cryostats, and they are located in between the hadronic calorimeters and the Muon Spectrometer, while the eight coils of each ECT are assembled in a single large cryostat.

### 3.2.3 The Inner Detector

The Inner Detector (ID) is designed to reconstruct tracks and vertices with high efficiency. It measures the momenta of charged particle tracks and the decay vertices of short-lived particles, and it contributes, together with the calorimeters and the muon system, to the electron, photon and the muon identification. The 2 T solenoid field, in which the ID is immersed, allows to measure tracks with a transverse momentum  $p_T > 0.5$  GeV. For particles with lower transverse momentum, the track reconstruction efficiency is limited due to a large material effect in the ID [ATL08b]. The low momentum determines small bending radii, and the respective particles cannot escape the ID, looping in the solenoidal field.

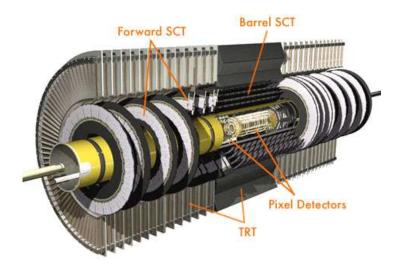

Figure 3.5 shows an overview of the ID. It consists of three different types of sub-detectors that cover the pseudorapidity range of  $|\eta| < 2.5$ . At the inner radii two high-resolution detectors, the Pixel Detector and the Semiconductor Tracker (SCT), are used for high-precision pattern recognition measurements, while at the outer radii the Transition Radiation Tracker (TRT) provides continuous tracking elements that enhance the pattern recognition and improve the momentum resolution over the pseudorapidity range  $|\eta| < 2.0$ . Each of these sub-detectors is divided into a barrel component and two end-cap components at either side. In the barrel region, the high-resolution layers are arranged in concentric cylinders around the beam axis, while in the end-cap region they are mounted on disks perpendicular on the same axis. In a similar way, the TRT components are adjusted in parallel to the beam axis in the barrel region and radially in the end-cap regions [ATL08a]. The ID sub-detectors are briefly described in the following sections.

#### The Pixel Detector

The Pixel detector is the component of the ID closest to the interaction point. It is made of 1744 modules, each of which consists of a 15.5 cm<sup>2</sup> wide and 250  $\mu$ m thick silicon sensor. The nominal size of a standard pixel is 50  $\mu$ m in the  $\phi$  direction and 400  $\mu$ m in z (barrel) or R<sup>(8)</sup> (end-cap) directions. This leads to an intrinsic accuracy of 10  $\mu$ m in the R- $\phi$  plane and 115  $\mu$ m in the z direction. The pixel modules are arranged in three layers in the barrel region, and in three disk layers in the two end-cap regions. The innermost layer in the barrel section is placed at about 5 cm around the beam axis. This provides a good vertex resolution, which is essential in order to separate the decay and production vertices of short-lived particles such as the B-mesons and the  $\tau$ -leptons.

The principle of operation of the Pixel detector is based on a p-n junction in reverse bias. A charged particle passing through the detector produces pairs of movable electrons and holes along its path. The applied electric field separates the charge carriers and drifts them to the surface of the silicon sensor, where they are detected by charge sensitive amplifying electronics. Each silicon sensor provides 46,080 readout channels, which gives a total of approximatively 80.4 million readout channels. This represents almost half of the total number of channels available in ATLAS, i.e  $\sim 10^8$ .

Due to the proximity to the interaction point, the Pixel detector has to operate in an extremely hostile environment of radiation. The expected dose for the innermost barrel layer is expected to reach 500 kGy after approximately five years of LHC operation at design luminosity. For this reason, the layer has to be replaced after approximatively five years of operation. The other two barrel layers and the end-cap disks are expected to reach the same radiation dose after ten years of LHC operation [ATL08a].

### The Semiconductor Tracker

The SCT provides four space points per track in the intermediate radial range of the ID, contributing to the measurement of the momentum, impact parameter and the vertex position. It also provides good pattern recognition by use of high resolution.

The SCT consists of 4088 silicon micro-strip modules, which are arranged in four concentric layers in the barrel region and nine disks on either end-cap side. Each layer consists of a double layer of silicon strips, with a 40 mrad stereo angle between them, in order to measure two coordinates. In the barrel section, one set of strips in each layer is arranged in parallel to the beam axis, to measure the  $\phi$  angle, while the second set of strips is tilted in order to provide the z direction. In the end-cap sections, one set is arranged radially, while the other one is tilted with the same stereo angle. This geometry provides a spatial resolution per silicon module of about 17  $\mu$ m in the R- $\phi$  plane, and 580  $\mu$ m in the z (barrel) or R (end-cap) directions.

The silicon modules cover a surface of  $63\ m^2$  and provide about  $6.3\ million$  readout channels [ATL08a].

<sup>&</sup>lt;sup>8</sup>R is the radial distance from the beam line  $(R = \sqrt{x^2 + y^2})$ .

#### The Transition Radiation Tracker

The TRT makes use of the *transition radiation effect* for particle identification, and combines it with spatial resolution for particle tracking. A relativistic charged particle emits photons when it crosses the boundary of two materials with different dielectric constants. The energy radiated by the passing particle is linearly proportional to the Lorentz factor ( $\gamma = E/m_0$ ). For electrons, the emitted transition radiation photons have energies in the X-ray range, while for heavier particles the emitted radiation has a considerably lower energy. Thus, the TRT contributes to the electron identification, by discriminating them from heavier charged particles.

The TRT is made of 4 mm diameter thin proportional drift tubes (straws). Each straw tube is equipped in the centre with a 31  $\mu$ m diameter gold-plated tungsten wire, acting as an anode, and filled with a xenon-based gas mixture<sup>9</sup>. The cathode is represented by a 0.2  $\mu$ m aluminium coating layer on the tubes.

The barrel section comprises 52,544 straws, each 144 cm long, arranged in 73 layers parallel to the beam axis. The two end-cap sections contain each 122,880 straws of 37 cm length, organised in 160 planes radially aligned to the beam axis. In both cases, the space between successive straw layers is filled with 15  $\mu$ m thick polypropylene foils, which act as radiators. The adopted geometry ensures that particles with transverse momentum  $p_T > 0.5$  GeV cross at least 36 straw tubes in the pseudorapidity range  $|\eta| < 2.0$ . Also, due to the same geometry, the TRT only provides a measurement in the R- $\phi$  plane, with an intrinsic accuracy of 130  $\mu$ m per straw [ATL08a].

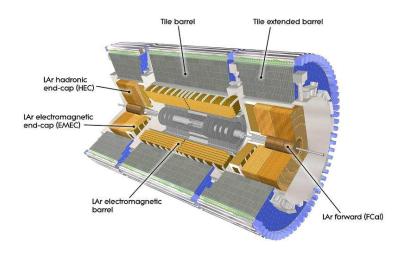

### **3.2.4** The Calorimetry

The ATLAS calorimetry plays an important role in the reconstruction of physics processes of prime interest. The calorimeters have to measure the energy and position of electrons, positrons, photons, isolated hadrons and jets, provide an accurate estimation of the missing transverse energy  $(E_T^{miss})$ , and contribute to the particle identification. Additionally, information from the calorimeters is used at the first level of triggering in order to identify the interesting physics events.

Figure 3.6 shows an overview of the ATLAS Calorimetry. The system is subdivided into an inner electromagnetic calorimeter, to measure mainly electrons, positrons and photons through their electromagnetic interactions, and an outer hadronic calorimeter, to measure mainly hadrons through their strong and electromagnetic interactions. Both subsystems are sampling calorimeters with full  $\phi$ -symmetry and coverage around the beam axis, and cover together the pseudorapidity range  $|\eta| < 4.9$ . Each subsystem consists of a barrel and two end-cap components. In addition, the hadronic calorimeter is equipped in the forward regions with a dedicated system. Table 3.1 summarises the granularity and the pseudorapidity coverage of the ATLAS calorimeters.

The components of the ATLAS calorimetry are briefly described in the following sections.

<sup>&</sup>lt;sup>9</sup>70% Xe (for an efficient absorption of the transition radiation photons), 27% CO<sub>2</sub> and 3% O<sub>2</sub> (for constant drift velocity over a large drift range, small electron deflection in magnetic fields, and ultraviolet photon quenching).

Figure 3.6: Cut-away view of the ATLAS Calorimetry system [ATL08a].

### The Electromagnetic Calorimeters

The electromagnetic calorimeters are lead-liquid argon (LAr) detectors with accordion-shape absorbers and electrodes (see e.g. figure 3.7). The absorbers are made of lead plates. They are responsible for both inducing electromagnetic showers, as well as for absorbing the shower constituents of which energy is insufficient to create new particles. The gaps between the lead plates are filled with LAr, which provides the active layer of the calorimeter. The secondary electrons and positrons created in the electromagnetic shower ionise the liquid argon atoms, and the resulting ionisation signal is collected by electrodes located in between the absorber plates. The electrodes consist of three conductive copper layers. The two outer layers distribute the

| Calorimeter              | η coverage             | $\Delta \eta \times \Delta \phi$ granularity |

|--------------------------|------------------------|----------------------------------------------|

| Presampler               | $ \eta  < 1.8$         | 0.025 x 0.1                                  |

| Electromagnetic Barrel   | $ \eta  < 1.475$       | $0.003 \times 0.1$ (S1)                      |

|                          |                        | 0.025 x 0.025 (S2)                           |

|                          |                        | $0.050 \times 0.025 \text{ (S2)}$            |

| Electromagnetic End-Cap  | $1.375 <  \eta  < 3.2$ | 0.003-0.1 x 0.1                              |

| Hadronic Barrel          | $ \eta  < 1.0$         | $0.1 \times 0.1$                             |

| Hadronic Extended Barrel | $0.8 <  \eta  < 1.0$   | 0.1 x 0.1                                    |

| Hadronic End-Cap         | $1.5 <  \eta  < 2.5$   | 0.1 x 0.1                                    |

|                          | $2.5 <  \eta  < 3.2$   | $0.2 \times 0.2$                             |

| Forward Calorimeter      | $3.1 <  \eta  < 4.9$   | $\sim 0.2 \times 0.2$                        |

**Table 3.1:** The granularity and the pseudorapidity coverage of the ATLAS calorimeters.

3.2 The ATLAS Detector 23

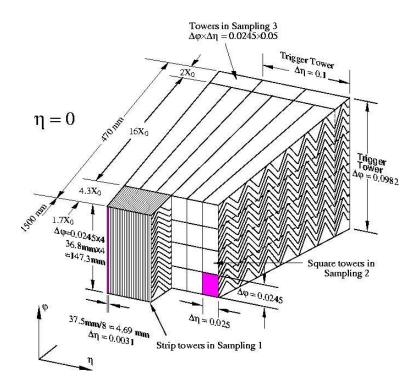

**Figure 3.7:** Segmentation of the LAr electromagnetic barrel calorimeter [ATL08a].

high-voltage across the LAr gaps, while the inner layer is used for reading out the ionisation signal via capacitive coupling.

The absorbers and the electrodes are *projective* to the interaction point in the  $\eta$  direction, and bent into an accordion shape to ensure that the incident particles cross both the absorbers and the active layers. This geometry provides a full azimuthal coverage, without any cracks, and a fast extraction of the ionisation signal at the rear or at the front of the electrodes.

The electromagnetic barrel calorimeter (EMB) is placed behind the central solenoid, inside the barrel cryostat that surrounds the ID cavity. It consists of two half-barrels, separated by a 4 mm gap at z=0. Each half-barrel consists of 1024 lead absorbers, interleaved with electrodes. In order to achieve an uniform sampling fraction in  $\phi$ , the thickness of the lead plates varies with  $\eta$ , i.e. 1.53 mm for  $|\eta| < 0.8$ , and 1.13 mm for  $|\eta| > 0.8$ . The three electrodes are positioned by honeycomb spacers at the half-distance between two neighbouring absorber plates. The folding angle of the absorbers and the electrodes varies with the radius, in order to keep constant the thickness of the LAr gap, i.e. 2.1 mm. At an operating voltage of 2 kV, this geometry determines a total electron drift time to the readout electrode of 450 ns.

Each half-barrel is mechanically divided into 16 modules, each of which covers an equal slice of the full azimuthal range. Figure 3.7 describes schematically a module of the EMB. It consists of three longitudinal sampling layers:

• Front Sampling (S1): it represents the layer closest to the interaction point. It is segmented into fine strips in the  $\eta$  direction, to provide a good resolution for  $\gamma/\pi^0$  separation. The

depth of the layer corresponds to 4.3 radiation lengths  $(X_0)$ ;

- Middle Sampling (S2): it is arranged in square cells of very fine granularity (see again table 3.1), to provide a good position measurement of the deposited energy. The thickness of the layer corresponds to  $16 X_0$ , to ensure that the largest energy fraction of the electromagnetic shower is absorbed within this layer;

- Back Sampling (S3): it is also divided into cells, but of a coarser granularity in  $\eta$  than the second sampling layer. Since only the highest energetic constituents (the tail) of the electromagnetic shower reach this layer, the energy resolution is not affected by the coarser granularity. The depth of the layer corresponds to  $2 X_0$ .

The total material seen by an incident particle in front of the EMB is about  $2.3 X_0$  at  $|\eta| = 0$ , and increases up to  $6 X_0$  at  $|\eta| = 1.475$ , since the distance travelled by the particles increases also with  $\eta$ . In order to correct for the energy lost in the ID, central solenoid and the cryostat wall, the two half-barrels are preceded by a presampler detector. This is made of an 11 mm thin LAr layer, which is subdivided into 64 identical azimuthal cells, i.e. 32 per half-barrel. The total active thickness of one EMB module is larger than 22  $X_0$ , increasing from 22  $X_0$  at  $|\eta| = 0$  up to 33  $X_0$  at  $|\eta| = 1.3$ . Also, each EMB module and the corresponding presampler cells in front of it provide together a total of 3424 readout channels.

The electromagnetic end-cap calorimeters (EMECs) are contained in two cryostats together with the hadronic end-cap and the forward calorimeters. Each EMEC consist of two co-axial wheels, each of which being subdivided into eight wedge-shaped modules, without introducing any discontinuity along the azimuthal angle. The outer wheel  $(1.475 < |\eta| < 2.5)$  consists of 768 lead absorbers, while the inner wheel  $(2.5 < |\eta| < 3.2)$  is made of 256 lead absorbers. As for the EMB, the thickness of the lead plates varies with  $\eta$ , in order to optimise the energy response of the EMECs, i.e. 1.7 mm in the outer wheel, and 2.2 mm in the inner wheel. The electrodes are again positioned in the middle of the gaps by honeycomb spacers, at 2.1 mm from the neighbouring absorber plates. In the outer wheel, the ionisation signals are read out from both sides of the electrodes, as in the case of the EMB, while in the inner wheel, the signals are read out only from the back side, due to high radiation levels at the front side.

In the pseudorapidity range  $1.5 < |\eta| < 2.5$  the EMECs are segmented in three longitudinal sampling layers, in the same way as the EMB. In the pseudorapidity ranges  $1.375 < |\eta| < 1.5$  and  $2.5 < |\eta| < 3.2$  the EMECs are segmented in only two longitudinal sampling layers, and have a coarser transverse granularity. Also, in the range  $1.5 < |\eta| < 1.8$  each EMEC is preceded by a presampler, which consists of two 2 mm thin LAr layers equipped with readout electrodes. The total active thickness of one module of the EMEC is larger than  $24 X_0$ . Also, each module provides 3984 readout channels, including 96 channels from the presampler.

The energy resolution that ATLAS expects to achieve with the LAr electromagnetic calorimeters is:

$$\frac{\sigma(E)}{E} = \frac{10\%}{\sqrt{E}} \oplus 0.7\% \quad , \tag{3.6}$$

where the first term represents the *stochastic term*, which takes into account the statistical fluctuations in the shower development, while the second term represents the *constant term*, which

3.2 The ATLAS Detector 25

**Figure 3.8:** Schematic view of a Tile module [ATL08a].

accounts for all detector imperfections and calibration imprecisions. The symbol  $\oplus$  represents the quadratic sum operator.

#### The Hadronic Calorimeters

The hadronic calorimeter covers the pseudorapidity range  $|\eta| < 4.9$  and uses two different sampling techniques: steel-scintillating tiles in the barrel region, and copper-LAr in the end-cap and forward regions.

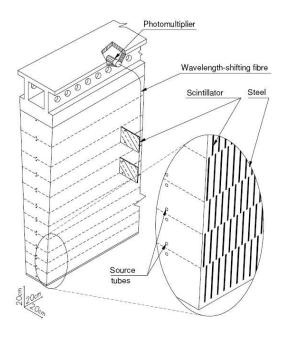

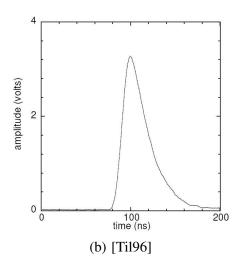

The *Tile calorimeter* uses steel as absorber and plastic scintillating plates (*tiles*) as active medium. It is located behind the LAr electromagnetic calorimeter, and it is divided into a central barrel and two extended barrels. Each component is further subdivided into 64 modules of equal azimuthal size, i.e.  $\Delta \phi = \sim 0.1$ . Figure 3.8 shows a schematic view of a module of the Tile calorimeter. Within the module, the scintillating tiles are inserted in a rigid steel structure, perpendicular on the beam axis and staggered in depth. They are 3 mm thick, and are made of optical transparent granulated polystyrene doped with scintillating additives  $^{10}$ . An ionising particle crossing the Tile module induces the production of ultaviolet light in the polystyrene material, which is then converted by the scintillating additives to visible blue light. Two wavelength-shifting fibers collect this light at the edges of each tile, shift it to a longer wavelength, and guide it to the input of two photomultipliers (PMTs). The PMTs are housed by a rigid support girder at the outer edge of the module, together with the front-end electronics. The Tile module is segmented into a three-dimensional cell structure, which provides three radial sampling depths.

<sup>101.5%</sup> para-terphenyl (PTP) and 0.44% 1,4-bis(5-phenyloxazol-2-yl) benzene (POPOP), both acting as wavelength shifters.

Each cell is obtained by grouping wavelength-shifting fibers from corresponding tiles into two bundles, i.e. one per side of the module, and coupling the bundles to two PMTs. The granularity of the cells is  $\Delta \eta = \sim 0.1$ , for the inner two cells, and  $\Delta \eta = \sim 0.2$ , for the outer one, while the thickness of the sampling depths is approximatively 1.5, 4.1 and 1.8 interaction lenghts ( $\lambda_{int}$ ) at  $\eta = 0$ .

The central barrel is separated from each extended barrels by a gap of about 70 cm. These gaps provide space for cables and services for the ID, and for power supplies and services for the LAr EMB. The respective regions are only partially instrumented, with special modules made of steel-scintillator, which provide the same sampling fraction as the rest of the Tile calorimeter, and with thin scintillator counters. These devices allow partially to recover the energy lost in the crack regions of the detector. The Tile calorimeter has a total radial length of approximatively  $7.4 \lambda_{int}$ , and provides about 10,000 readout channels.

The *hadronic end-cap calorimeters* (HECs) use copper plates as absorbers and LAr as active medium. Each HEC consists of two cylindrical wheels arranged concentrically around the beam axis. Each HEC wheel is constructed from 32 identical modules, and it is divided into two longitudinal readout segments. In the wheels closer to the interaction point the modules are made of 24 copper plates, each 25 mm thick, while in the outer wheels the sampling fraction is coarser, the modules being made of 16 copper plate, each 50 mm thick. In both wheels, the three electrodes divide the LAr gap into four equal drift zones of 1.8 mm. Each zone is supplied with a high voltage of 1.8 kV via the outer electrodes, which determines an electron drift time of about 430 ns. The two HECs provide together a total of 5632 readout channels. The active part of each HEC corresponds to approximatively  $12 \lambda_{int}$ .

The *forward calorimeters* (FCALs) are placed at high  $\eta$ , at a distance of approximatively  $\sim$ 4.7 m from the interaction point. Therefore, the FCALs have to cope with a particularly high level of radiation. Each FCAL is divided into three 45 cm deep modules. The first module (FCAL1) uses copper as absorber and is optimised for electromagnetic measurements. The other two modules (FCAL2, FCAL3) are made of tungsten and measure predominantly the energy of hadronic interactions. Each FCAL module consists of a metal matrix with regularly spaced longitudinal channels filled with electrodes. Because of the high density of the design, the LAr gaps are much smaller than in the other ATLAS LAr calorimeters, i.e. 0.25 mm (FCAL1), 0.35 mm (FCAL2), 0.5 mm (FCAL2). Consequently, the electron drift times are shorter, e.g. 60 ns in FCAL1. Each FCAL is approximately  $10 \lambda_{int}$  deep and provides 1762 readout channels.

The energy resolution expected for the hadronic calorimeters is [ATL97]:

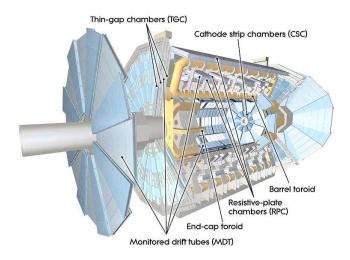

#### 3.2.5 The Muon Spectrometer

The Muon Spectrometer is designed with a twofold functionality:

• to detect the charged particles that penetrate the calorimetry, and to determine their momentum by measuring the bending of their tracks in the toroidal magnetic field;

3.2 The ATLAS Detector 27

**Figure 3.9:** Cut-away view of the ATLAS Muon Spectrometer [ATL08a].

• to trigger on the detected particles.

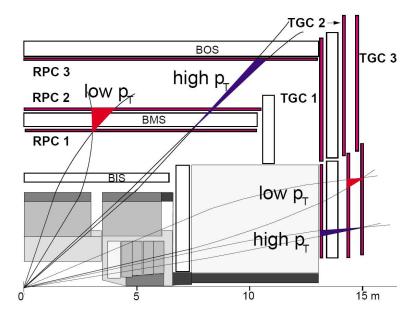

The first task is accomplished by two high precision-tracking chambers, Monitored Drift Tubes (MDTs)<sup>11</sup> and Cathode Strip Chambers (CSCs), which cover together the pseudorapidity range  $|\eta| < 2.7$ . The second task is delegated to two types of trigger chambers, Resistive Plate Chambers (RPCs) and Thin Gap Chambers (TGCs), which cover the pseudorapidity range  $|\eta| < 2.4$  (see also figure 3.9). The two subsystems of the Muon Spectrometer are briefly described in the following sections.

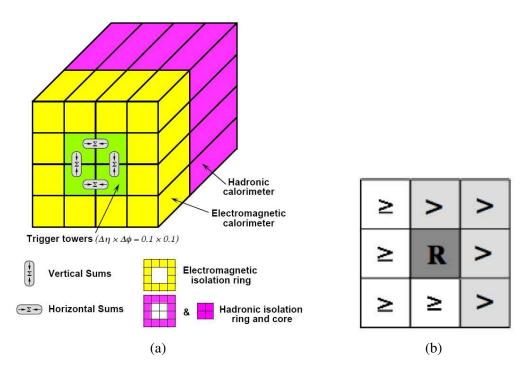

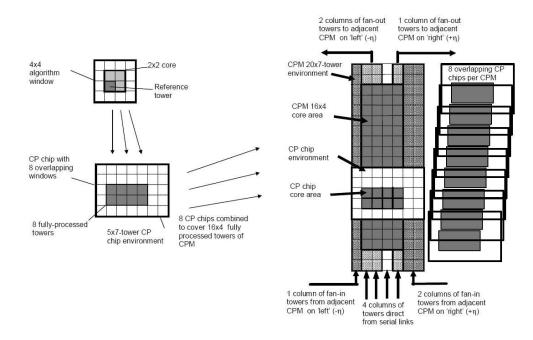

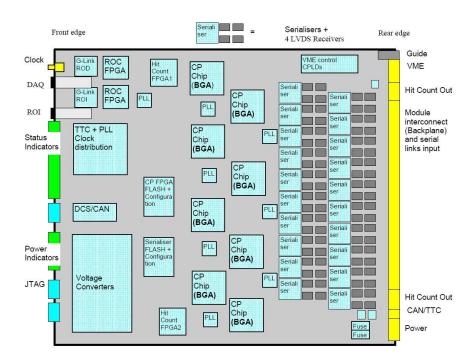

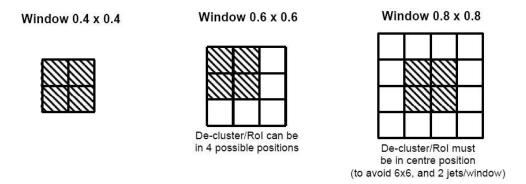

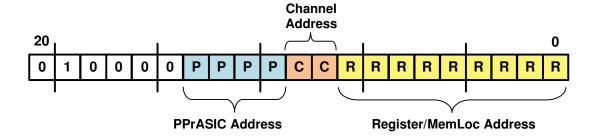

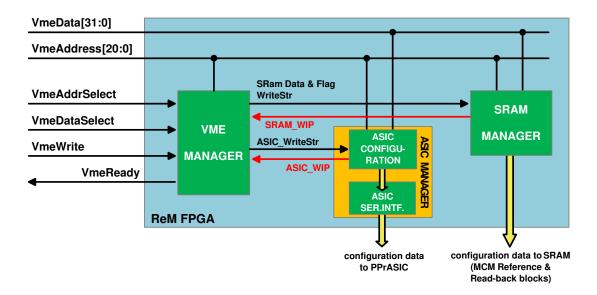

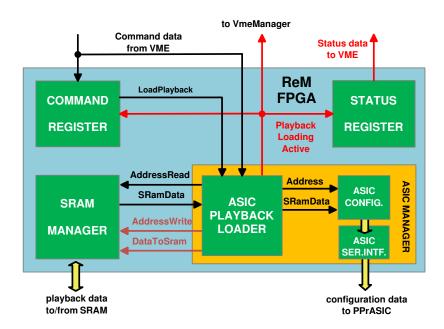

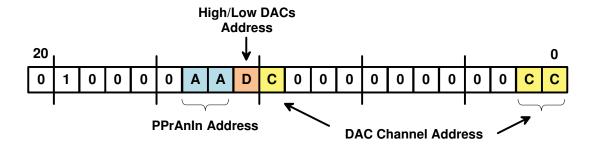

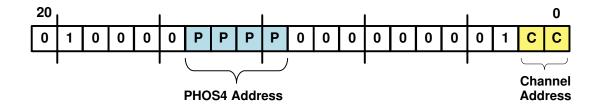

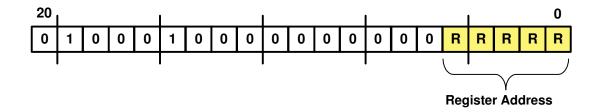

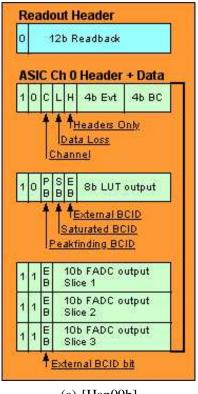

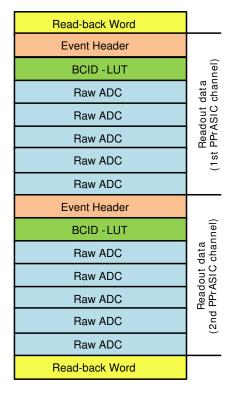

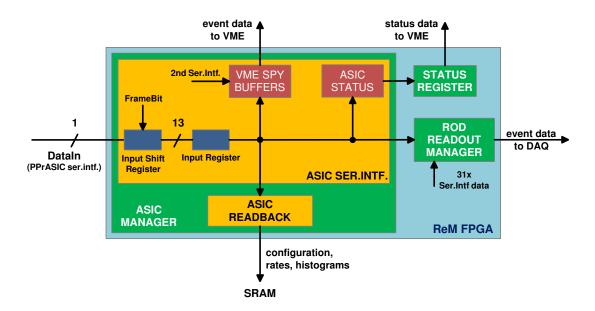

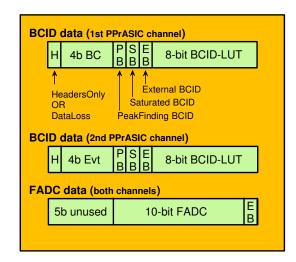

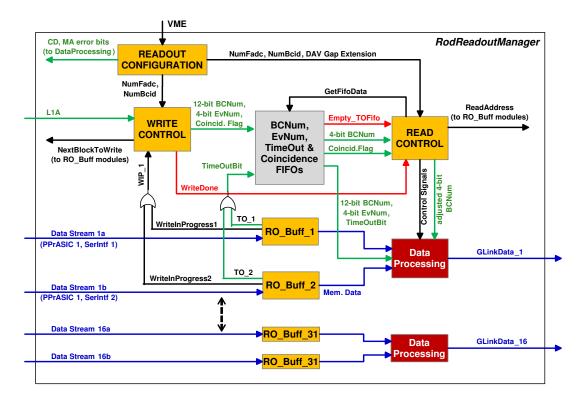

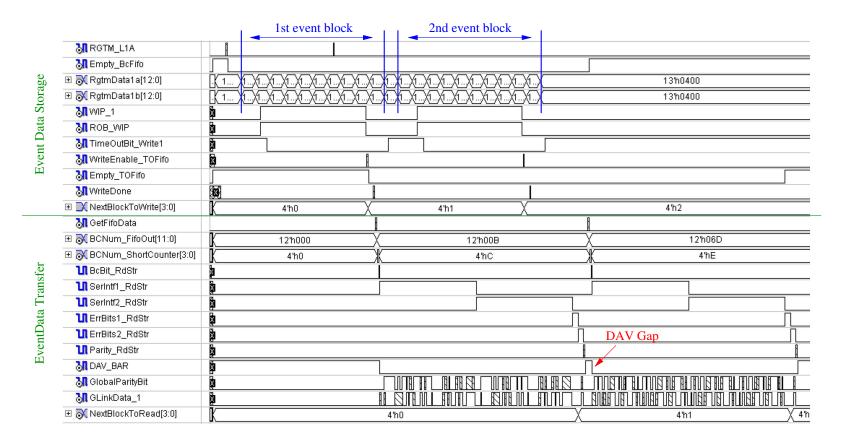

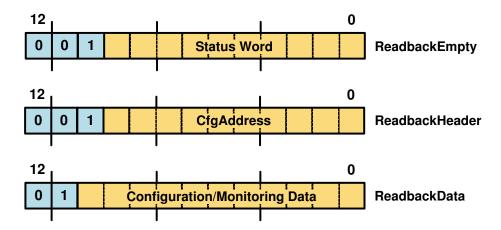

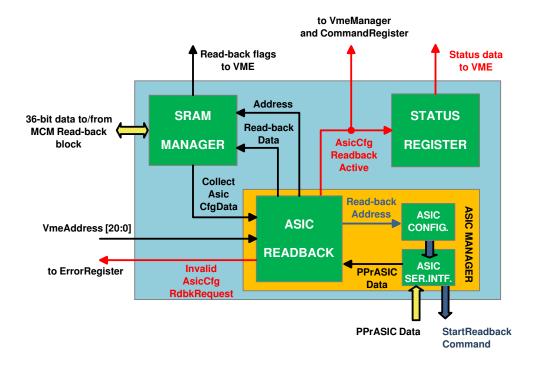

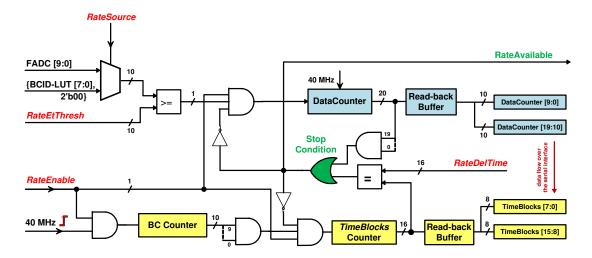

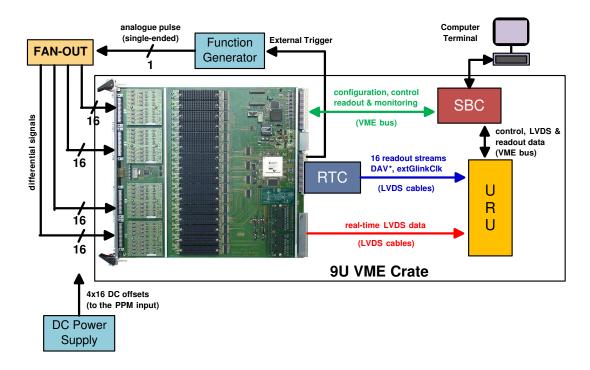

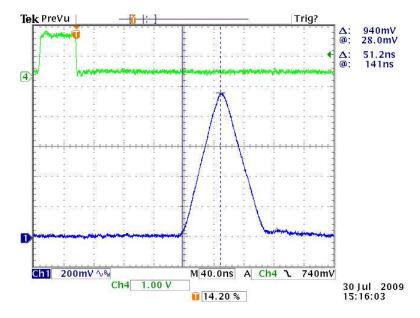

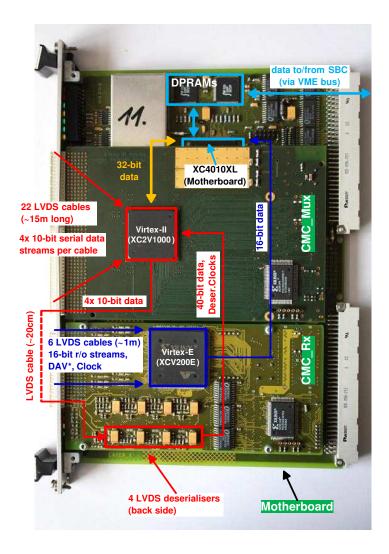

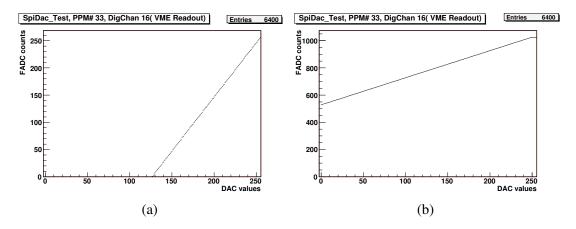

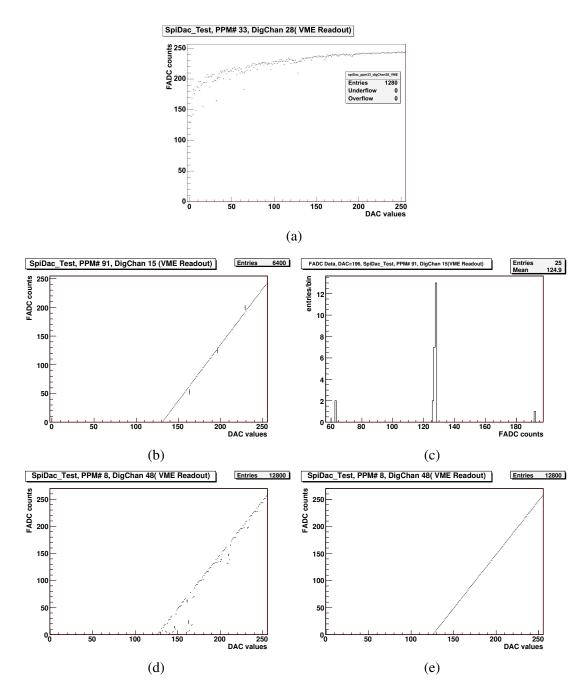

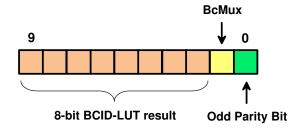

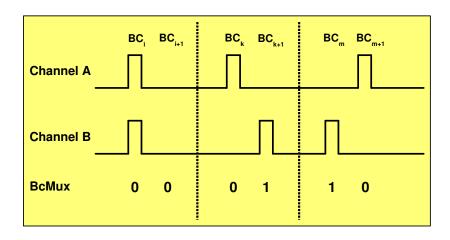

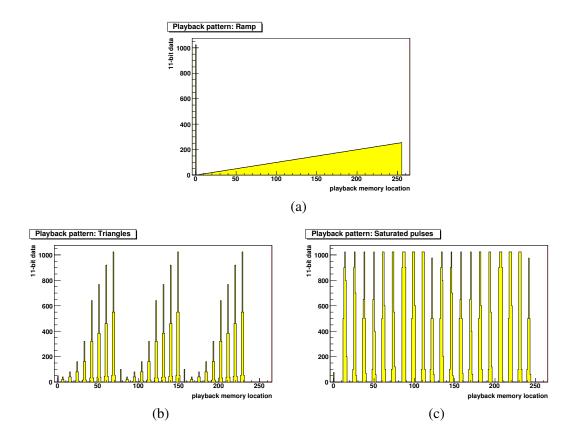

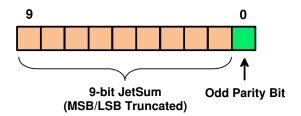

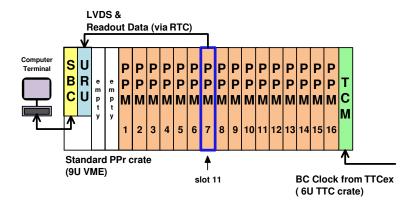

#### The Precision-tracking Chambers